Bjørg Solem

# Applying Unique Program Execution Checking in the development flow of industrial IoT devices to prevent vulnerabilities for side-channel attacks

Master's thesis in Electronic Systems Design Supervisor: Per Gunnar Kjeldsberg Co-supervisor: Joakim Urdahl & Karine Avagian June 2023

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Bjørg Solem

# Applying Unique Program Execution Checking in the development flow of industrial IoT devices to prevent vulnerabilities for side-channel attacks

Master's thesis in Electronic Systems Design Supervisor: Per Gunnar Kjeldsberg Co-supervisor: Joakim Urdahl & Karine Avagian June 2023

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

# Abstract

Recently discovered vulnerabilities in digital designs and computing systems have highlighted the increasing importance of identifying exploitable side channels to ensure secure devices. In the worst scenarios, some vulnerabilities can be maliciously exploited to get hold of passwords and other confidential data.

The Unique Program Execution Checking (UPEC) method is a formal verification technique developed to aid in the discovery of such system vulnerabilities during the early development phase. Previously, this has been tested out on several designs and it has been able to detect potential issues within these.

This master's thesis aims to use the UPEC method to search for vulnerabilities in the newest version of the PULPissimo platform, along with the nRF54L15 design from Nordic Semiconductor. The goal to be accomplished is to assess the scalability of the technique, using the measurements of time-per-proof and memory usage per proof. Additional evaluations will also be conducted, such as how much knowledge is needed beforehand, along with how much manual effort is required to either prove, or disprove, the presence of vulnerabilities in the system.

Although the application onto the nRF54L15 was not accomplished due to issues with the setup in the OneSpin 360 tool, several tests were run on the PULPissimo platform. This led to results regarding the UPEC method's potential scalability, and the discovery of a vulnerability within the system.

The methodology is quite advanced, however, the results accomplished and discussed in this experiment show that this methodology might be a good technique in the future to locate system vulnerabilities. With a bit more work, especially on tutorials to make it more available and understandable, the method could be used on industrial systems.

# Sammendrag

Nylige funn av sårbarheter i digitale design og datasystemer har understreket den økende betydningen av å klare å identifisere utnyttbare sidekanaler for å kunne produsere sikre systemer. I de verste tilfellene kan noen sårbarheter bli utnyttet for å få tak i passord og annen konfidensiell data.

Metoden Unique Program Execution Checking (UPEC) er en teknikk innen formell verifikasjon som har blitt utviklet for å hjelpe til med å finne slike systemsårbarheter tidlig i utviklingsfasen. Tidligere har denne blitt testet ut på flere design, og den har greid å identifisere mulige sårbarheter ved disse systemene.

Denne masteroppgaven har som mål å bruke UPEC metoden for å lete etter sårbarheter i den nyeste versjonen av PULPissimo plattformen samt designet nRF54L15 fra Nordic Semiconductor. Hensikten er å vurdere skalerbarheten av teknikken, ved å ta fatt i mål som tidsbruk per bevis som kjøres, samt minnebruk per bevis. Det blir også gjort ytterlige vurderinger, som å se på hvor mye forhåndskunnskap som er nødvendig, samt hvor arbeidskrevende det er å enten bevise, eller motbevise, tilstedeværelsen av sårbarheter.

Selv om implementasjonen av metoden på nRF54L15 ikke ble oppnådd på grunn av problemer med oppsettet av systemet i det benyttede verktøyet OneSpin 360, ble det kjørt flere tester på PULPissimo plattformen. Dette førte til resultater angående metodens potensielle skalerbarhet, samt oppdagelsen av en sårbarhet.

UPEC metoden er ganske avansert. Likevel viser resultatene som har blitt oppnådd og diskutert i dette eksperimentet at det kan være en god fremtidig teknikk for å finne systemsårbarheter. Med litt mer jobb, spesielt i forhold til opplæringsmaterialet som bidrar til å gjøre metoden mer forståelig og tilgjengelig, vil metoden kunne brukes på industrielle systemer.

# Acknowledgments

I would like to thank my supervisors at Nordic Semiconductor, Joakim Urdahl and Karine Avagian, for their support and motivating nature throughout. Our talks have always been enriching, and I am grateful they shared their ideas and knowledge with me throughout this process.

Furthermore, I would like to thank my supervisor here at NTNU, Professor Per Gunnar Kjeldsberg, for his encouragement and support during our conversations, and for taking the time to read through my thesis.

An enormous thanks goes to the team at the Technical University of Kaiserslautern, and especially Johannes Müller, for all the information shared about the Unique Program Execution Checking method. I could not have gotten by without all the help and guidance provided by Johannes, who has taken the time to answer all my questions.

I look forward to keeping up with the development and any further publications regarding the UPEC method.

Lastly, I would like to thank my dearest Amund for all his support and love, and my family and friends for their patience and motivation throughout my studies.

# Contents

| Ał | ostrac         | t        |                                                | i    |

|----|----------------|----------|------------------------------------------------|------|

| Sa | mme            | ndrag    |                                                | ii   |

| Ac | know           | vledgme  | ents                                           | iii  |

| Li | st of I        | Listings |                                                | vii  |

| Li | st of 🛛        | Fables   | ·                                              | viii |

| Li | st of <b>I</b> | Figures  |                                                | x    |

| Ał | obrevi         | iations  |                                                | xi   |

| 1  | Intr           | oductio  |                                                | 1    |

|    | 1.1            | Object   | ives                                           | 1    |

|    | 1.2            | Motiva   | ation                                          | 2    |

|    |                | 1.2.1    | Microarchitectural side channels               | 2    |

|    |                | 1.2.2    | Transient execution side channels              | 3    |

|    |                | 1.2.3    | Examples of side-channel attacks               | 3    |

|    |                | 1.2.4    | Some ways to detect vulnerabilities in devices | 6    |

|    | 1.3            | Limita   | tions                                          | 6    |

|    | 1.4            | Resear   | rch method                                     | 7    |

|    | 1.5            | Thesis   | structure                                      | 7    |

| 2  | Bac            | kground  |                                                | 9    |

|    | 2.1            | Genera   | al concepts in computer architecture           | 9    |

|    |                | 2.1.1    | Register-Transfer level                        | 9    |

|    |                | 2.1.2    | Instruction set architecture                   | 9    |

|    |                | 2.1.3    | RISC-V Instruction set architecture            | 10   |

|    |                | 2.1.4    | Operating system                               | 10   |

|    |                | 2.1.5    | Kernel process                                 | 10   |

|   |      | 2.1.6   | Physical memory protection                                         |

|---|------|---------|--------------------------------------------------------------------|

|   |      | 2.1.7   | Microarchitectural and architectural states                        |

|   | 2.2  | Introdu | ction to Unique Program Execution Checking                         |

|   | 2.3  |         | us work                                                            |

|   | 2.4  |         | l verification                                                     |

|   |      | 2.4.1   | Logical notations in formal verification 12                        |

|   |      | 2.4.2   | Formal property verification                                       |

|   | 2.5  |         | neSpin tool                                                        |

|   | 2.0  | 2.5.1   | Property Checking                                                  |

|   |      | 2.5.2   | Black-boxing                                                       |

|   |      | 2.5.3   | Counterexamples                                                    |

|   |      | 2.5.4   | Hold_bounded(n) result and unreachable counterexamples             |

|   |      | 2.5.5   | Vacuous result                                                     |

|   |      | 2.5.6   | Approvers and disprovers   16                                      |

|   |      | 2.5.7   | Timing Diagram Assertion Library                                   |

|   | 2.6  |         | ility                                                              |

|   | 2.0  |         | o systems                                                          |

|   | 2.1  | 2.7.1   | ,                                                                  |

|   |      | 2.7.1   | 1                                                                  |

|   |      | 2.1.2   | nRF54L15 20                                                        |

| 3 | Unic | ue Pro  | gram Execution Checking 21                                         |

|   | 3.1  |         | nique Program Execution Checking method                            |

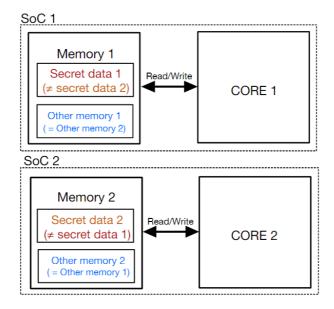

|   | 3.2  |         | SoC                                                                |

|   | 3.3  |         | ates and tutorial                                                  |

|   | 3.4  |         | in practice compared to UPEC in theory                             |

|   |      | 3.4.1   | Deeper dive into the property                                      |

|   |      | 3.4.2   | The property in relation to the logic equations describing UPEC 28 |

|   |      |         |                                                                    |

| 4 |      |         | for the project 30                                                 |

|   | 4.1  | Scalab  | ility in this experiment                                           |

|   |      | 4.1.1   | Memory and time usage 30                                           |

|   |      | 4.1.2   | Number of constraints 31                                           |

|   |      | 4.1.3   | Limitations to scalability in this experiment                      |

|   | 4.2  |         | tion of the required time and effort                               |

|   | 4.3  | Knowl   | edge beforehand                                                    |

|   |      | 4.3.1   | Security expertise                                                 |

|   |      | 4.3.2   | About the system                                                   |

|   |      | 4.3.3   | About the tool                                                     |

| _ |      | 1.0     |                                                                    |

| 5 |      |         | implementation 33                                                  |

|   | 5.1  | 5.1.1   | neral approach                                                     |

|   |      | - · ·   | e                                                                  |

|   | 5.0  | 5.1.2   | Analysis                                                           |

|   | 5.2  |         | ssimo version 7.0                                                  |

|   |      | 5.2.1   | Setup                                                              |

|   |      | 5.2.2   | Final property explained 38                                        |

|    | 5.3    | 5.2.3<br>nRF54 | Analysis       41         L15       44                            |

|----|--------|----------------|-------------------------------------------------------------------|

| 6  | Resu   | ılts           | 46                                                                |

|    | 6.1    | PULPis         | ssimo                                                             |

|    |        | 6.1.1          | Alerts discovered                                                 |

|    |        | 6.1.2          | Results in regard to scalability                                  |

|    | 6.2    | nRF54          | L15                                                               |

| 7  | Disc   | ussion         | 58                                                                |

| '  | 7.1    |                | nd effort required                                                |

|    | 7.2    |                | lity results for PULPissimo                                       |

|    | 1.2    | 7.2.1          | Constraints and states                                            |

|    |        | 7.2.2          | Proof memory-usage with and without optimizations                 |

|    |        | 7.2.2          | Proof time-usage with and without optimizations                   |

|    | 7.3    |                | ing the alerts                                                    |

|    | 1.5    | 7.3.1          | P-alerts                                                          |

|    |        | 7.3.2          | uDMA L-alerts                                                     |

|    | 7.4    |                | nces in results for the two PULPissimo versions                   |

|    | /.+    | 7.4.1          | PMP                                                               |

|    |        | 7.4.2          | HWPE                                                              |

|    |        | 7.4.3          | uDMA                                                              |

|    | 7.5    |                | nowledge                                                          |

|    | 1.5    | 7.5.1          | Need of prior knowledge regarding security and vulnerabilities 65 |

|    |        | 7.5.2          | Need of prior knowledge of the systems                            |

|    |        | 7.5.3          | Need of prior knowledge regarding the tool                        |

|    | 7.6    |                | of the UPEC method on industrial IoT devices                      |

|    | 7.0    | 7.6.1          | Experiences with PULPissimo                                       |

|    |        | 7.6.2          | The nRF54L15         67                                           |

|    | 7.7    |                | tions to ease the usage                                           |

|    | 1.1    | Sugges         |                                                                   |

| 8  | Con    | clusions       | 71                                                                |

|    | 8.1    | Future         | work                                                              |

|    | 8.2    | Conclu         | sions                                                             |

| D: | bliogr | onhy           | 74                                                                |

| DI | onogi  | арпу           | /4                                                                |

| Ap | pend   | ix             | 79                                                                |

|    |        | А              | Property file                                                     |

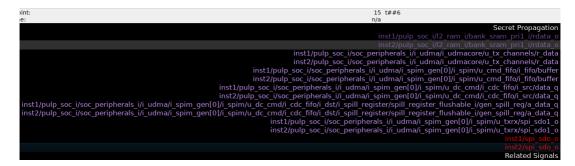

|    |        | В              | Propagation path from uDMA P-alert location                       |

|    |        | С              | Explanation to the workspace                                      |

# List of Listings

| 1 | Example of a property using an implication operator                                  | 13 |

|---|--------------------------------------------------------------------------------------|----|

| 2 | Example of a property using the 'implies' operator                                   | 13 |

| 3 | Example of an assertion                                                              | 14 |

| 4 | Example of a property that would give a vacuous result                               | 17 |

| 5 | UPEC property-shell                                                                  | 27 |

| 6 | UPEC assertion                                                                       | 27 |

| 7 | State_equivalence simplified                                                         | 28 |

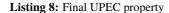

| 8 | Final UPEC property                                                                  | 39 |

| 9 | Example of a property considering a fanout state in the 'prove' part of the property | 43 |

# List of Tables

| 6.1 | Black-boxed modules used in uDMA-propagation test         | 49 |

|-----|-----------------------------------------------------------|----|

| 6.2 | State_uniqueness size without additional black-boxing     | 52 |

| 6.3 | State_uniqueness size with black-boxing used in uDMA-test | 53 |

| 6.4 | Proof runtime experiments                                 | 56 |

| 6.5 | Proof memory-usage experiments                            | 57 |

# List of Figures

| 1.1                                                            | Difference in reload time, victim cache line access vs. no victim cache line access.<br>Inspired by Yarom and Falkner (2014)            | 4              |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.2                                                            | Memory access flow in Meltdown susceptible systems. Inspired by Erik Vrielink (2019).                                                   | 6              |

| 2.1                                                            | PULPissimo architecture, inspired by The Parallel Ultra Low Power platform (n.d)                                                        | 19             |

| 3.1                                                            | UPEC computational model. Inspired by Müller et al. (2021)                                                                              | 23             |

| 5.1                                                            | Example of how to look for fanout states reached within one clock cycle                                                                 | 42             |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | All P-alerts collected in PULPissimo                                                                                                    | 47<br>48<br>49 |

|                                                                | L-alert                                                                                                                                 | 50             |

| 6.5<br>6.6                                                     | All the times at which the states for the first L-alert got different values compared to their counterparts in the other instance       | 51             |

|                                                                | L-alert                                                                                                                                 | 51             |

| 6.7                                                            | All the times at which the states for the second L-alert got different values com-<br>pared to their counterparts in the other instance | 52             |

| 6.8                                                            | Property hold without any black-boxing, using state_uniqueness. Tmax=2                                                                  | 54             |

| 6.9                                                            | Property hold with several modules black-boxed, using state_uniqueness. Tmax=2                                                          | 54             |

| 6.10                                                           | Property hold with several modules black-boxed, using state_uniqueness. Tmax=3                                                          | 55             |

| 6.11                                                           | Property hold with no black-boxing, using uDMA_obs_space. Tmax=3                                                                        | 55             |

| 6.12                                                           | Property hold with no black-boxing, using uDMA_obs_space. Tmax=4                                                                        | 56             |

| A.1                                                            | Property.sv line 2-41                                                                                                                   | 79             |

| A.2                                                            | Property.sv line 42-81                                                                                                                  | 80             |

| A.3                                                            | Property.sv line 84-115                                                                                                                 | 80             |

| A.4                                                            | Property.sv line 116-155                                                                                                                | 81             |

| A.5         | Property.sv line 155-196                                            | 82 |

|-------------|---------------------------------------------------------------------|----|

| A.6         | Property.sv line 197-222                                            | 83 |

| <b>B</b> .1 | Whole propagation path from uDMA to sdi_oen_o, shown in fanout view | 84 |

# Abbreviations

| Abbreviation | Description                                 |

|--------------|---------------------------------------------|

| BMC          | Bounded Model Checking                      |

| CTL          | Computation Tree Logic                      |

| DUT          | Device under test                           |

| HWPE         | Hardware Processing Engines                 |

| I2C          | Inter-Integrated Circuit                    |

| I/O          | Input/Output                                |

| IoT          | Internet of Things                          |

| IPC          | Interval Property Checking                  |

| ISA          | Instruction Set Architecture                |

| L-alert      | Leakage alert                               |

| P-alert      | Propagation alert                           |

| PMP          | Physical Memory Protection                  |

| PULP         | Parallel Ultra Low Power platform           |

| RTL          | Register-Transfer Level                     |

| SoC          | System-on-Chip                              |

| SPI          | Serial Peripheral Interface                 |

| SVA          | SystemVerilog Assertions                    |

| Tcl          | Tool Command Language                       |

| Tidal        | The Timing Diagram Assertion Library        |

| UART         | Universal Asynchronous Receiver-Transmitter |

| uDMA         | micro-Direct Memory Access                  |

| UPEC         | Unique Program Execution Checking           |

# Introduction

Today, secure electronic computing systems are exceedingly important. Computing systems in today's society range from tiny Internet of Things (IoT) devices, all the way to high-end servers, and can be found pretty much everywhere in day-to-day life (Bhunia and Tehranipoor, 2019b). These computing systems deal with data from a lot of aspects of everyday life, ranging from financial transactions to healthcare records, and more, and this data should not be available to everyone. If an unauthorized party gains access to such data, this could lead to theft of sensitive personal data, or the unauthorized party could potentially be able to damage the computing system. This shows the importance of implementing sufficient security measures and avoiding any vulnerabilities in the design.

Security features are often implemented at the software level, however, without functional hardware mechanics, for instance operational memory isolation, these security features could fall short, all dependent on the system's design. As shown by the discoveries of the infamous Melt-down (Lipp et al., 2018) and Spectre (Kocher et al., 2019) attacks, properties of the hardware implementation could potentially become a vulnerability that an attacker with malicious intent may exploit. Something such as a small optimization could theoretically present vulnerabilities in a system, while the system still would be regarded as functionally correct. The possible exploitation of these vulnerabilities could potentially lead to the exposure of sensitive information to an unauthorized actor, for instance.

These types of vulnerabilities, whenever found on launched products, can be difficult to fix. The reason for this is that they are rooted in the hardware, which cannot be altered in hindsight. Finding them early on can also possibly be a challenge, as it calls for a lot of knowledge regarding the systems' inner structure and design.

# 1.1 Objectives

One possible method that could hopefully alleviate the work volume needed to examine and find potential system vulnerabilities is the Unique Program Execution Checking (UPEC) method

(Fadiheh et al., 2019). This is introduced in Chapter 2 and further elaborated in Chapter 3.

Using the concept of the UPEC technique, the desired goal in this thesis is to be able to implement it on an actual industrial design, the nRF54L15 system from Nordic Semiconductor, as well as an open-source system, the PULPissimo platform (Schiavone et al., 2018). The intention behind this is to look at how this method would scale, especially in an industrial setting. This can show how feasible this technique would be in these types of systems, and whether it could be used to help improve security in such devices.

The further intention is to look at how much time and effort is needed to successfully apply the technique, run the tests, and understand the results. It will also be evaluated whether this resulting workload is reasonable. Another purpose behind this is to look at how much knowledge one needs to have beforehand, both regarding security, the tool used, and the system itself. This will, in turn, be compared to how beneficial it ends up being for the systems, in that actual vulnerabilities can be discovered or proven to be non-existent. What metrics will be used to evaluate the scalability of the method, and the effort needed to apply it to the systems, is further detailed in Chapter 4.

Another motive is to look at how the method actually works in practice and to provide an overview as to what the actual implementation of the technique looks like.

This project is done in collaboration with Nordic Semiconductor, a Norwegian semiconductor company that specializes in developing wireless communication technology for IoT solutions (Nordic Semiconductor, n.d.). The nRF54L15 system that will serve as a test case of an industrial design is a design by Nordic Semiconductor.

## **1.2 Motivation**

Below are some potential vulnerabilities and exploitations of vulnerabilities in digital designs described. These show the importance of being able to detect these design problems at an early stage. Because these problems are hardware-related, they are difficult, if not even impossible, to fix on launched products. Thus, the best mitigation to such issues could be to find them early on in development and fix them right away (Bhunia and Tehranipoor, 2019a, p. 18).

#### **1.2.1** Microarchitectural side channels

The descriptions of the logic behavior of a system at the Register-Transfer Level (RTL), which uses registers as building blocks, can be referred to as the microarchitecture of the system (Fadiheh, 2022). These microarchitectures can naturally vary a lot between systems, leaving the designer with a lot of freedom while developing the device. As a consequence, there are a lot of possibilities in regard to implementing optimizations or changing the design otherwise. This can, in some circumstances, cause overlooked functional bugs. Such functional bugs could result in microarchitectural side effects that may be exploitable by someone with malicious intent.

Simple data differences could potentially alter the behavior of the system, and these kinds of behavioral changes could then eventually end up becoming exploitable. If these differences are caused by the confidential data in the system, this could open a "microarchitectural side channel", which are channels that accidentally leak private data, without the victim system being aware. The observable or measurable change in behavior could give an attacker the opportunity to decrypt

cipher text, compute cryptographic keys, or otherwise obtain details of the system (Hutle and Kammerstetter, 2015).

There are several different ways sensitive information could leak, and thus be misused by an adversary to find secret data. Some of these ways include execution time differences, power consumption, and electromagnetic leaks (Bhunia and Tehranipoor, 2019c, p. 194).

#### **1.2.2** Transient execution side channels

Transient execution side channels are, as explained in Fadiheh (2022), a phenomenon that occurs whenever processors transiently execute instructions ahead of time, without knowing if the program flow actually reaches these executed instructions. This is also known as speculative execution. In other words, these vulnerabilities originate from the way some processors speculatively execute instructions, in order to improve performance.

In systems using such speculative execution, the system begins executing some instruction before it is known whether this will be needed in the future, based on predictions (Kocher et al., 2019). These guesses are again based on previously executed instructions, with different algorithms for making the predictions. If it turns out that the instruction is actually needed, the system will commit it, and thus have had a performance gain. The issue with this optimization, however, is that it can cause side effects, such as loading the data into the cache. The cache is a temporary storage used to easily and quickly fetch recent, or frequently used, data (Hennessy and Patterson, 2017, p. B-2). Thus, if it turns out that this instruction is not really in the execution path, the data may still be in the cache, even if the instruction is never committed. There are ways to attack a system to get hold of data residing in the cache, such as the Flush+Reload, explained in section 1.2.3.

#### **1.2.3** Examples of side-channel attacks

An attacker could make use of these side channels and potentially be able to analyze the differences in for example timing or voltage levels that these side effects lead to (Hutle and Kammerstetter, 2015). For instance, a timing analysis can be applied to cryptographic systems to extract the secret key. This is because there are some such systems that differ in execution time whenever the guessed keys are partly correct. In such an attack, the adversary can apply different inputs as guesses, and measure the timing difference in the system to determine whether part of the guessed key was correct or not (Bhunia and Tehranipoor, 2019c). Other examples of how side channels can give access to secret data are given directly below, which shows how the Flush+Reload attack and the Meltdown attack might work.

#### Flush+Reload

The Flush+Reload attack is a way an adversary could get hold of data residing in the cache of a system.

The Flush+Reload attack makes use of the CLFLUSH instruction from the Intel x86 architecture. This instruction flushes memory locations from the cache (Yarom and Falkner, 2014).

The way this attack works is that, firstly, the attacker has to map a shared object into address space, which is possible because of the Kernel Shared Memory feature. This is a feature meant to increase memory density, something that is accomplished by merging equal pages (Arcangeli

et al., 2009). Kernel shared memory allows attackers to share a page of data physically with a victim, even if they are different processes. This feature can be used by the attacker to monitor memory line accesses. Because of this, an adversary can make sure that a particular line of memory is evicted from the entirety of the cache (Yarom and Falkner, 2014). Thus, the adversary can flush the monitored memory line.

After the flush, the attacker has to wait and see whether the victim accesses the memory line once again. After the wait time, the attacker reloads this line and checks how long time it takes to load it.

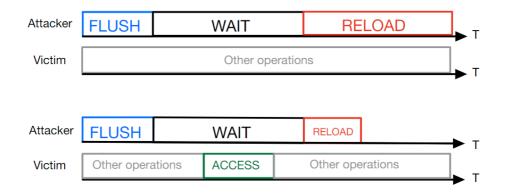

The principle is that if the victim has accessed the line of memory during the wait time, the line is located in the cache. If this is the case, the reload time is therefore shorter than if the line was not brought back into the cache. The reason for this is that a fetch from the cache would be a lot quicker than a fetch from the memory, which would be further away. This is shown in an illustration in Figure 1.1, where a CLFLUSH instruction is marked with blue text, the black text represents the waiting period for the attacker and a reload of the line is red. Any other operations performed by the victim in the meantime are marked gray.

**Figure 1.1:** Difference in reload time, victim cache line access vs. no victim cache line access. Inspired by Yarom and Falkner (2014)

This timing difference gives the attacker an opportunity to prompt in and make educated guesses of the cache content. Based on the timing difference provided by the system whether the data resides in the cache or not, the attacker could in turn be able to determine whether the prompted in guess is correct or not.

Although the cache data might not be secret data, this attack in conjunction with other attacks, could lead to the leakage of confidential data. Directly below, an attack exploiting the Meltdown vulnerability is further elaborated. This, along with the Flush+Reload attack can lead to such leakage of secret data.

Attacks using Flush+Reload have also already been successfully applied against cryptographic implementations to extract cryptographic keys by trial and error (Benger et al., 2014). While the adversary tries to prompt in guesses of such keys, the system would likely need to fetch the actual key from memory to compare to the guess. In this scenario, it is, therefore, easier to know that the data in the cache is the cryptographic key, which is confidential.

#### Meltdown

Another example of a very famous and potentially severe vulnerability that can be exploited maliciously is the Meltdown vulnerability. The functionality behind an attack exploiting this vulnerability is thus provided to fully illustrate the weight of how attacks can misuse such vulnerabilities.

This vulnerability could give attackers access to sensitive information stored in a system, such as passwords and encryption keys, because of two optimizations that are put in place in the exposed systems. This vulnerability is quite serious, as it affects nearly every Intel processor produced since 1995 (Graz University of Technology, 2018).

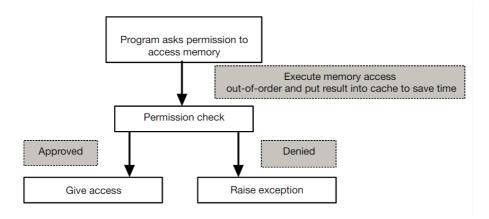

One of these optimizations that can be exploited is out-of-order processing, while the other optimization is an exception handler.

Out-of-order processing is a concept used where the processor can execute instructions in a different order than the original program sequence states (Sarangi, 2021, p. 411). This technique makes use of otherwise unused instruction cycles and hence reduces idle time. Out-of-order processing enables instructions to be executed once their operands are available. This way, the processor can execute instructions that otherwise would be stuck waiting for a previous instruction to finish, as long as these are not dependent on each other. Thus, if one instruction is waiting for resources, another one can be executed if it is ready, and it is independent of the one that is waiting.

Whenever an instruction raises an exception, the control flow should be diverted to the exception handler, and the next instruction is to be prevented from executing. This mechanism is used to manage unexpected events, called exceptions, which are special events that are created when the program executing performs an incorrect action (Sarangi, 2021, p. 379). The execution handler should then try to deal with the exception appropriately.

The issue with using both of these mechanisms simultaneously is that whenever an exception occurs, and the next instruction should be prevented from executing, it might already have been executed because of the usage of out-of-order processing. This can be seen in Figure 1.2, where a permission check would result in an exception if the process does not have the privilege to access the memory. However, the out-of-order execution has caused the memory content to be placed into the cache.

Thus, if an adversary asks to access secret memory, this memory might have been put into the cache to save time. The only thing the adversary then has to do is to make use of the Flush+Reload attack, or any similar attacks, to get hold of the data.

To summarize shortly, an attacker could be able to load the data into the cache, by exploiting the vulnerability of using the exception handler optimization along with the out-of-order processing optimization. By making use of Flush+Reload, an attacker could then try to guess the content of the cache, which now is the secret data. The adversary can be able to tell if the guess is correct or not based on the time it would take for the system to reload the monitored cache line.

There are a lot of specific design details that have to align correctly for such an attack to be feasible. However, this still shows how vulnerabilities potentially could be exploited, and how these exploitations could be quite dangerous.

Figure 1.2: Memory access flow in Meltdown susceptible systems. Inspired by Erik Vrielink (2019).

#### **1.2.4** Some ways to detect vulnerabilities in devices

The Meltdown vulnerability and Flush+Reload attack scenarios are just two examples of how various vulnerabilities can be exploited to get hold of secret data. In this case, memory contents of non-accessible memory can be read, which could potentially reveal important secrets. Since these kinds of scenarios are very important to avoid, the subject of security in IoT systems has to be evolving in line with the systems themselves.

Some techniques for finding such vulnerabilities could involve analysis through formal verification, simulation, and analysis of the code (Dessouky et al., 2019). This could require a lot of knowledge about security exploits and how these work to be able to spot any system issues that could be exploited.

There has also been development of design languages for security, such as SecVerilog (Zhang et al., 2015). This implements information flow tracking. The issue with this type of solution, however, is that it calls for changes in the design procedure. For well-established designers with well-defined routines, this can be difficult.

Other possibilities could be to try to break into a system, to see whether it is possible to obtain any confidential data this way. This method would then require a lot of knowledge regarding each system, and possibly also previously known vulnerabilities and attacks.

The reason the UPEC technique might be good for security analysis is that it simplifies the procedure of looking for vulnerabilities, as it is not necessary to have any special security expertise to use this methodology (Müller et al., 2021). The method should be able to detect vulnerabilities that are rooted in observable side effects, and thus also side channels.

# 1.3 Limitations

As this experiment intends to look into some systems at the product level of whole Systemon-Chips (SoCs), the setup and implementation of the method could be a possible challenge. Working at the product level is quite difficult as it involves a lot of modules and smaller components that have to be taken into consideration. Also, as the experiment is to be performed by someone who is not familiar with the systems beforehand, a lot of time is anticipated to go into research and understanding the environments themselves. This could potentially affect the end result, in that there will be less time to actually implement the method and perform the experiments.

The UPEC technique has already been tested on a previous version of the PULPissimo platform. Even so, an implementation onto a newer version of the platform could still be beneficial, as the environment has gone through changes since then. These differences could have resulted in newly-introduced vulnerabilities in the system, which therefore might yield interesting results.

## **1.4 Research method**

In order to perform this experiment of implementing the UPEC method onto both the PULPissimo and the nRF54L15 system, relevant literature regarding UPEC has been researched. Also, information and documentation surrounding the two systems have been studied. The most relevant information can be found in Chapter 2, which describes the general background for this work, and in Chapter 3, which details the UPEC methodology.

For the nRF54L15 system, which is a project from Nordic Semiconductor, the company's datasheet and information has been used to gain an understanding of the system's inner workings.

For the PULPissimo environment, the GitHub project sites regarding PULPissimo (Schiavone et al., 2018), and the two possible core choices, Ibex (lowRISC team, 2018) and CV32E40P (OpenHW Group, 2023) have been studied, as well as their respective documentation.

The aim to replicate the method on the PULPissimo platform first is intended to be used as a ground measure for comparison when the method is applied to the nRF54L15 system, as well as a method of getting familiar with the technique. Afterward, the results collected from the experiment with PULPissimo are supposed to be used to make decisions regarding how the application onto nRF54L15 should best be performed.

## **1.5** Thesis structure

The structure of the thesis is as follows:

- Chapter 2 gives the relevant background information regarding common concepts within computer architecture and formal verification. This chapter also presents previous work with the UPEC method, alongside a quick introduction to the method. The two systems, PULPissimo and nRF54L15, along with the OneSpin 360 tool will also be presented.

- Chapter 3 presents all the relevant information regarding the Unique Program Execution Checking method, both the theory behind it and how it is used in practice.

- Chapter 4 introduces the metrics used to evaluate the UPEC method for this experiment.

- Chapter 5 describes the methodology used to perform the experiments conducted in this thesis.

- Chapter 6 presents the results accomplished during the experiments.

- Chapter 7 provides the discussion regarding the accomplished results and the overall experience with the UPEC method.

- Chapter 8 draws conclusions and presents ideas for future work within this subject.

# 2

# Background

This background chapter will give insight into topics that are further explored or otherwise taken into account in this thesis, and thus provide an explanation regarding the relevant literature and subjects. The chapter will also provide a quick introduction to the UPEC method, before it is presented in its entirety in Chapter 3. Previous work on the method will be presented in this chapter as well. Further, the subject of formal verification, as well as the formal verification tool OneSpin 360 is explained, as these subjects are quite fundamental to the UPEC method. Finally, a deeper investigation into the systems used in the performed experiments as well as the subject of scalability is provided.

# 2.1 General concepts in computer architecture

There are some common concepts in computer architecture that are mentioned briefly throughout this thesis. This section provides the explanation needed to understand these concepts well enough to also comprehend the context in which they are used.

# 2.1.1 Register-Transfer level

Register-Transfer level abstraction is used to create portrayals of a design, where the building blocks are registers (Vahid, 2010). This gives the opportunity to implement and verify digital circuits in the design flow.

## 2.1.2 Instruction set architecture

Instruction Set Architecture (ISA) is the way that the hardware is perceived by the software, as it is the definition of all the instructions that are supported by a processor. This also includes the instruction's operands and interfaces with peripheral devices (Sarangi, 2021, p. 17).

## 2.1.3 RISC-V Instruction set architecture

The RISC-V ISA is an open and simple architecture. It is made to be expandable, in that new user-level extensions can be added (Waterman et al., 2016b).

#### 2.1.4 Operating system

The operating system consists of a set of dedicated programs that administer the device, its peripheral components, and the processes running on the device (Sarangi, 2021, p. 455).

#### 2.1.5 Kernel process

The core component of the operating system is the kernel, and its main role is to administer the processes and their execution. It also has the task of managing the memory (Sarangi, 2021, p. 455). A kernel process is thus a process with control over the rest of the system, and can therefore access the internals of the processor, which should not be available for regular user processes.

### 2.1.6 Physical memory protection

Physical memory protection (PMP) is an optional RISC-V feature that allows physical memory access privileges to be specified for each physical memory region (Waterman et al., 2016a).

#### 2.1.7 Microarchitectural and architectural states

Microarchitectural state variables include all the state variables, such as registers, buffers, flipflops, and other components that relate to the logic part of the system's microarchitecture (Fadiheh et al., 2019). These include all the state variables in the system, meaning both those that can be seen by the user, and those that are deep within the system, and thus also invisible to the user.

Architectural state variables are a subset of the microarchitectural states (Müller et al., 2021). These include only those state variables from the microarchitectural states that are programvisible. As stated in Müller et al. (2021), architectural state variables are the registers in the interface of the ISA programmer.

# 2.2 Introduction to Unique Program Execution Checking

The UPEC technique can possibly be a way to detect vulnerabilities that could eventually be misused in order to conduct attacks on a system. The developers of this method consist of a team from both the Technical University of Kaiserslautern and Stanford University, hereby referred to as the UPEC team.

UPEC is a formal verification-based method, and the idea behind it is to systematically detect vulnerabilities that could lead to possible attacks, all while doing so before product launch. This could therefore be a promising way of reducing vulnerabilities in systems. The underlying concept of the method, briefly explained, is that confidentiality violations occur whenever an attacker

is able to make use of the side effects that are generated by the secret data to uncover secret information (Fadiheh et al., 2019). Such side effects could be timing variations or other visible or measurable differences. Confidentiality in this case relates to the requirement that an untrusted user should not be able to access and read secret and protected data. Therefore, whenever secret data, such as passwords or encryption keys, for example, lead to visible side effects for an attacker, this equates to a confidentiality breach. These side effects can be measured and analyzed in order to gain an understanding of the secret data stored in the system. More details regarding how this approach actually works are presented in Chapter 3.

## 2.3 Previous work

The UPEC team has given out quite a few publications regarding the UPEC method, in which they detail the inner workings of the method and their own experiments.

A paper (Fadiheh et al., 2019) published by the UPEC team introduces the UPEC concept and explains the methodology. It also details a new kind of attack, called the Orc attack, that is possible to perform on processors with in-order pipelining.

The Ph.D. thesis written by Mohammad Rahmani Fadiheh (Fadiheh, 2022) explains the method and gives in-depth results accomplished by testing it on multiple systems, such as the Berkeley Out-Of-Order Machine (Celio et al., 2017) and Ariane (OpenHWGroup, n.d).

Another published paper (Müller et al., 2021) by the same team details the implementation of the UPEC method onto the PULPissimo platform. This was a similar experiment to the one described in this thesis, but on an older version of the platform.

This was conducted on the PULPissimo version 4.0, and resulted in the detection of vulnerabilities in the Hardware Processing Engines (HWPE) and micro-Direct Memory Access (uDMA) modules, as well as the PMP unit. The issue with the HWPE and the uDMA was that these modules were circumventing the PMP, and an attacker could potentially instruct the modules to read from the protected memory, and write this content onto unprotected outputs. For the PMP, the issue was that there were hardware bugs which resulted in the PMP not behaving according to the ISA.

The same paper also details an experiment on the RocketChip design (Asanović et al., 2016), an SoC without peripheral components which was proven to be secure by the UPEC method.

## 2.4 Formal verification

Formal verification is the process of checking a design to see if it behaves as expected in comparison to its specification. Formal verification techniques mathematically analyze the possible behaviors of a system, instead of looking only at the results for specific values (Seligman et al., 2015a). Thus, instead of simulating a specific input pattern, and checking the expected behavior for this, a computational model of the design is made and thus evaluated. This gives the developer the opportunity of looking at a larger range of behaviors, which simplifies the process of spotting errors in the design. One example of a technique is model checking, in which the modeled system is checked to see whether it is possible to reach a state in which the wanted characteristics of the system are violated.

#### 2.4.1 Logical notations in formal verification

In formal verification, there are symbols used to aid the common understanding of the concepts. In addition to a few Boolean (Boole, 1847) logical operators, one Computation Tree Logic (CTL) (Clarke et al., 1986) operator is used as notations in the explanation of the UPEC methodology later in this thesis. Thus, these are explained here.

CTL models time like a tree-like structure. The future can be realized as several different paths, but its outcome is not yet determined (Huth and Ryan, 2004, p. 208).

The notation 'AG' in CTL is essentially used to symbolize that a statement must hold for all the states on all the future paths (Clarke et al., 1986).

The 'AG' notation consists of the operator 'A' which symbolizes 'along All paths' and 'G' which symbolizes 'all future states (Globally)' (Huth and Ryan, 2004, p. 208).

For the two Boolean operator notations used, ' $\wedge$ ' and ' $\rightarrow$ ', these can be explained as follows:

The notation ' $\rightarrow$ ' is the implication operator, which expresses an implication between the right and left sides of the arrow. The notion ' $p \rightarrow q$ ' shows that there is a relationship between these statements in which q is a consequence of p (Huth and Ryan, 2004, p. 4).

Lastly, ' $\wedge$ ' is the conjunction operator, meaning that the notion ' $p \wedge q$ ' would symbolize p and q (Huth and Ryan, 2004, p. 4).

### 2.4.2 Formal property verification

Property checking can be considered a sub-branch of formal verification. The intent behind property checking is to check the behavior of a system against specific properties, to see if they are valid or not. These tests can be performed on blocks or modules to verify their functionality, but also to verify how modules work together at the system level. This type of check inputs the RTL model, along with the set of properties to prove, and the constraints into the tool. The constraints limit the set of possible system behaviors that should be considered.

The output is then represented as a list of the potential proven and disproven properties, as well as a list of the potential inconclusive proofs (Seligman et al., 2015b). This can then be used to find possible design bugs or errors. As a result, designers can identify which parts of the RTL should be redefined to end up with a system that behaves as intended.

An actual example of a property can be seen in Listing 1. Here, the name of the property is ex1, and it begins with the code word 'property' and ends with 'endproperty'. The implication operator, ' $\rightarrow$ ', states that if the left hand of the property is true, the right hand also has to be true on the very same clock edge for the property to hold (Mehta, 2021, p. 434). In order to begin checking the property, the left hand has to go true first, but the right hand should also be true

at the same clock. The notation '##2' represents a time delay of two clock cycles between two events (Institute of Electrical and Electronics Engineers, 2018, p. 342).

The property in Listing 1, therefore, checks whether signal y is set 2 clock cycles after signal x is set. Whenever this happens, the z signal should not be set on the same clock edge.

```

property ex1;

x ##2 y |-> !z;

endproperty

```

Listing 1: Example of a property using an implication operator

```

property ex2;

x ##2 y implies !z;

endproperty

```

Listing 2: Example of a property using the 'implies' operator

Instead of using the implication operator, one could also use the 'implies' operator, as seen in Listing 2. Here, the evaluation of both the right-hand side and the left-hand side would begin at the same time. This is in contrast to evaluating the property only when the left-hand side has been proven to hold. Then, the property would fail if either the right-hand side, called the 'prove' part, or the left-hand side, also referred to as the 'assumption' part, fails (Mehta, 2021, p. 510).

Also, there are some built-in functions that can be used within these properties to check specific signal transitions or look at the value of a signal in the past, and more. One such example, that is used in the property describing UPEC in later sections, is the '\$past()' function. This checks the value of the signal in the clock cycle previous to the current one (Institute of Electrical and Electronics Engineers, 2018, p. 397).

#### SystemVerilog Assertions

SystemVerilog Assertions (SVA) is a language that lets designers express what the correct behavior, or the incorrect behavior, of a design is, based on what is desirable to test. An assertion is thus a check against your design specification (Mehta, 2014, p. 9). The expression of the behavior is then verified using a formal verification tool, which simulates the possible states and inputs to determine whether the assertion holds or not.

The example assertion in Listing 3 is the associated assertion to the property 'ex1' presented in Listing 1. Here, the name of the assertion is 'ex1\_assertion', and the @(posedge clk) indicates that the property, ex1, should be checked at the positive edge of the clock. The 'assert' keyword

ex1\_assertion: assert property (@(posedge clk) ex1);

#### Listing 3: Example of an assertion

specifies the property as a requirement for the design that is to be tested (Institute of Electrical and Electronics Engineers, 2018, p. 364). If this were to be swapped with the keyword 'assume', the property would be specified as an assumption for the system (Institute of Electrical and Electronics Engineers, 2018, p. 364). Formal tools would then use this information to restrict the input stimulus.

#### Constraints

Constraints are used to describe and model the wanted behavior of the system environment (Siemens, 2023a). These are restrictions on the inputs to the device under test (DUT) and are used to ensure that it meets specific requirements and that the design is implemented accurately.

#### Counterexamples

If the formal verification tool disproves a proof, it also provides a waveform that shows a case of failure (Seligman et al., 2015b). This waveform is called a counterexample. Counterexamples in formal verification thus give examples of inputs that lead to failures in the property tested, and thus show behavior in the system that can witness this claim of failure. This helps with getting an understanding and an insight into the cause of the problem and can thus aid the user in determining a fix to the issue. By analyzing the counterexample, the designer can be able to determine what has to be altered or redesigned for the design to function as intended.

#### **Boolean satisfiability solvers**

According to Baek et al. (2021), a Boolean satisfiability solver, or SAT solver, attempts to solve the Boolean satisfiability problem. This is the problem of determining whether there is any input combination of which a Boolean formula, which consists of Boolean variables, can be evaluated to be true. If there is no such combination, the formula or function is unsatisfiable.

#### Bounded model checking and Interval property checking

Bounded model checking (BMC) (Clarke et al., 2001), is a SAT-based model checking technique in which only sequences of a finite length are investigated. If the property correctness cannot be guaranteed, BMC can still be used for finding counterexamples, which thus proves that a design fails.

As stated in (Fadiheh, 2022), the starting state is thus a known state, often reset. The end of the time window is the max time, Tmax.

Interval property checking (IPC) (Nguyen et al., 2008) is also a SAT-based model checking technique. In contrast to BMC, where the model checking problem is reduced to a finite bounded

time interval, IPC can deliver an unbounded proof. Unbounded proof would mean that the proof is globally valid, and that has no time interval restrictions. Because of this, IPC is used when the property has to hold for the inputs within a range, meaning it is better to guarantee correctness in contrast to BMC.

The difference that enables IPC to deliver an unbounded proof is the starting state of the proof. In IPC, the starting state is an arbitrary starting state, rather than the reset state of the system (Nguyen et al., 2008). Thus, because all possible values are considered for the starting state, this can also include unreachable states of the system.

# 2.5 The OneSpin tool

The tool used in this experiment to implement the UPEC method is called OneSpin 360. OneSpin is a formal verification tool for digital integrated circuits and systems. It is used to verify that a design follows the specification and to ensure functional correctness. The verification platform thus helps developers with eliminating bugs and errors early on in the process by thoroughly analyzing the RTL (OneSpin Solutions, n.d). Below are explanations of how the formal verification subjects mentioned in the rest of this thesis are used within the OneSpin tool. The concepts themselves might not be OneSpin-specific, but still, they relate to how the tool has been used for these experiments.

## 2.5.1 Property Checking

As previously mentioned, formal verification is using tools to analyze all possible design behaviors, instead of looking at results for just some specific input values (Seligman et al., 2015a). Property checking in OneSpin is done by specifying the behavior of a module in a formal language and then checking the design against this behavior. A successful check results in a 'hold', while a 'fail' would generate a counterexample that displays a situation that violates the property (Siemens, 2023b). In OneSpin, the design behavior can be specified using SVA, the design intent is captured in properties and assertions, and the behavior of the system can be modeled by using constraints.

## 2.5.2 Black-boxing

Black-boxing is a technique used within formal verification, in order to simplify complex logic. This can be used to represent parts of the system as a blacked-out box, which could simplify any proofs run on the system, and thus also reduce the time spent analyzing it. Black-boxing results in logic being ignored during the verification because a replacement with no internal logic or implementation details is made in order to simplify the design. The actual internal logic is abstracted away. Signals connected to the black-boxed components inputs are treated as primary outputs of the system, while signals connected to the outputs are seen as primary inputs to the system (Siemens, 2023a). As a result, the proofing process time is shortened, as the tool can thus deal with a simplified design.

In OneSpin, this is implemented using a 'black-box' compile option, which then declares the module in question as a blacked-out box, and the tool then treats the module as such.

## 2.5.3 Counterexamples

A counterexample is generated by the OneSpin formal verification tool, as a way to show that a property fails, or that it cannot be satisfied. As previously stated, this allows the user to investigate what is the root cause of the property's fail, and how to fix this issue in the design. The counterexample provided by OneSpin shows what input values are the root cause of the property failure, as well as a waveform that shows the design behavior which contradicts the assertion. This also shows values of all other relevant signals in the DUT that help demonstrate why the proof failed (Siemens, 2023a).

#### 2.5.4 Hold\_bounded(n) result and unreachable counterexamples

A 'hold\_bounded(n)' result would indicate that the assertion tested holds up until a certain point, but no longer. The 'n' represents the specified depth (Siemens, 2023a). This generates a counterexample, which shows behavior indicating what has been violated. However, the tool cannot guarantee that the counterexample provided is reachable.

An unreachable counterexample depicts unrealistic system behavior, meaning that it cannot occur in reality.

Thus, a 'hold\_bounded' result is similar to a 'fail', in that the property cannot be proven beyond the point reached during the proof. However, because the counterexample might not show realistic behavior, manual inspection is required to see whether this is the case or not. If the counterexample is unreachable, the issues with the design can be fixed with inspection and correction of any erroneous constraints.

#### 2.5.5 Vacuous result

The result can also be 'vacuous'. This means that the property, its constraints, and the design is contradictory, and thus, it cannot be proven to either fail or hold. This often happens if the left hand side of the implication operator is contradictory. (Siemens, 2023b).

One such simplified contradiction can be seen in Listing 4. Here, the assertion tries to verify that the property 'vacuous\_ex\_property' is true, but the property itself is contradictory. It states that at the positive edge of the clock, the signal 'sig\_X' should both be set and not set, which cannot happen. The right side of the implication operator states that 'sig\_Y' should be set in the next positive edge of the clock. Because the left side is contradictory, this property would give a vacuous result.

#### 2.5.6 Approvers and disprovers

By default, OneSpin uses an automatic mode when checking assertions to get the best possible proof results. This automatic mode then combines several proof algorithms. However, in some instances, it can be useful to disable this automatic mode and thus also some proof engines. This could for example be if some proof engines do not help the overall result. In this case, the proof time might be enhanced if the proof engines are disabled.

Approvers, or IPC solvers, in OneSpin, is a feature that can be used to control the strategies used in checking assertions. When using only the approvers, which is the case when running an

```

vacuous_ex_property;

@(posedge clk) (sig_X && !sig_X) |=> sig_Y;

endproperty

```

assert property(vacuous\_ex\_property);

Listing 4: Example of a property that would give a vacuous result

IPC proof, a 'hold' can be outputted, but these cannot result in a 'fail', as they are only able to prove an assertion.

When IPC solvers are used, the proof is started in an arbitrary state, which might not be reachable from reset. The reason it might not be reachable is that the starting state itself could violate the property (Siemens, 2023b). Instead of a 'fail', a 'hold\_bounded(n)' result can therefore be outputted. This will create a counterexample, which will point toward the violation. However, the counterexample has to be manually inspected to determine whether it is reachable or not.

One can also choose which approvers one wishes to run, as there are differences between the approvers. Some are better for assertions that depend only on a few signals, while some are also able to disprove an assertion (Siemens, 2023b).

Another proof engine type is the BMC disprovers, which also can be used instead of using the automatic mode. These cannot prove an assertion, and can thus only result in a 'fail' or a 'hold\_bounded(n)'.

Because this proof engine type makes use of BMC, they will start the property from a known state, often reset. This guarantees that the counterexample provided whenever a 'fail' is outputted is a reachable counterexample (Siemens, 2023b). A 'hold\_bounded(n)' result in this case, however, would rather guarantee that the counterexample provided is unreachable. This would therefore show unrealistic system behavior, instead.

## 2.5.7 Timing Diagram Assertion Library

The Timing Diagram Assertion Library (Tidal) is a language extension made by OneSpin. It is a library of SVA definitions for modeling operations based on generalized timing diagrams. Properties expressed in Tidal are treated as an assertion by the OneSpin tool (Siemens, 2023b).

#### During\_0(T1, O1, T2, O2, SE)

The during\_o function is a concept in Tidal that states that the state expression, SE, should hold in the interval from the beginning T1 + O1 to the ending, T2 + O2 (Siemens, 2023b).

# 2.6 Scalability

#### Definition

According to Bondi (2000), scalability refers to a system's capacity to adapt and deal with an increasing number of elements or objects, to be able to effectively manage expanding volumes of work, and/or to handle enlargement.

Scalability is then the ability a system or a method has to continue to function as expected whenever its size or volume is altered. If one attempts to apply a method to a system of a larger scale, this also means that the method has to do more work. Scalability thus means that the system or method should be able to function as intended despite having to deal with an increasing amount of work.

The term scalability may vary from system to system, as it could include scalability in terms of size, data traffic, and more.

#### Limitations

The ability to scale onto a new system could be limited by the size of the new system one tries to apply the method to. As a system becomes larger, and hence also more complex, this also results in a lot more work for the system. Thus, the ability of a system or method to scale depends on whether it has enough resources to deal with this additional workload. An unscalable system would refer to a system in which the additional cost of managing this size increase is too large, or where the system is not able to deal with the growth at all (Bondi, 2000).

## 2.7 The two systems

#### 2.7.1 Pulpissimo

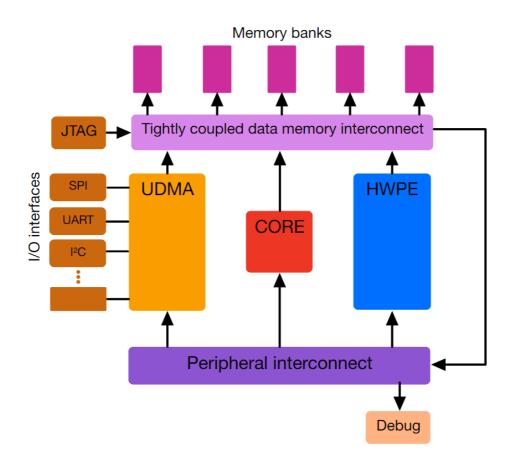

PULPissimo (Schiavone et al., 2018) is an open-source SoC platform that is part of the "Parallel Ultra Low Power (PULP) platform", which is a collaboration between ETH Zurich and the University of Bologna (The Parallel Ultra Low Power platform, n.d). Their aim is, according to The Parallel Ultra Low Power platform (2022), to develop a hardware and software platform that is scalable as well as open. Additionally, they want to meet the demands of current IoT applications, which require flexible processing of data streams.

The PULPissimo SoC is a single-core platform, designed to be very energy-efficient. The architecture includes for instance support for HWPE, which are hardware accelerators that share memory with the core. PULPissimo also supports input/output (I/O) interfaces, some of these are for instance Universal Asynchronous Receiver-transmitter (UART) and Inter-Integrated Circuit (I2C). Both of these are different communication protocols used to transmit data between devices.

The Serial Peripheral Interface (SPI) is also a communication protocol with a master-slave architecture, where the master initiates communication, and the slaves respond to the master's requests (Trivedi et al., 2018).

The architecture of the system can be seen in Figure 2.1, where the most central subsystems for this experiment, along with some Input/Output interfaces, are included. The interconnects are named to avoid any confusion regarding these blocks.

Figure 2.1: PULPissimo architecture, inspired by The Parallel Ultra Low Power platform (n.d)

The uDMA is a subsystem that communicates with the peripherals, such as the SPI and UART, autonomously. It can access memory and thus transfer data from the peripheral to memory or vice versa, without having to go through the processor (Sarangi, 2021, p. 587).

The 'debug' module seen in Figure 2.1 is the subsystem used for debugging during the development of the system.

One can choose to use either the Ibex core or the CV32E40P core, both of which are based on the RISC-V ISA. Both of the cores are also open-source.

#### CV32E40P core

The CV32E40P is a small, in-order core with a 4-stage pipeline. It is designed for low power consumption, which makes it suitable for many different types of embedded systems, such as the PULPissimo platform. The core was previously known as the RI5CY, and was maintained

by the PULP platform team until February 2020, when it was contributed to OpenHW Group (OpenHWGroup, n.d).

#### **Ibex Core**

The Ibex core was initially developed by the PULP team at ETH Zurich, and is now maintained by the lowRISC team, a non-profit company based in Cambridge (lowRISC team, n.d,a). It is a 32-bit CPU core that is highly parameterizable and suitable for embedded control applications (lowRISC team, n.d,b). It is also an in-order core with 2 pipeline stages. It was initially designed to target ultra-low-power and ultra-low-area constraints (The Parallel Ultra Low Power platform, n.d).

#### 2.7.2 nRF54L15

The nRF54L15 is an ultra-low-power SoC with a rich set of peripherals, which provides a range of analog and digital functionality, and advanced security features (Nordic Semiconductor, n.d,). This SoC is a product designed by Nordic Semiconductor, with an Arm Cortex-M33 processor. The processor features a floating-point unit for carrying out operations on floating-point numbers, as well as a digital signal processing extension, which offers signal processing for e.g. voice, audio, and machine learning applications (Arm Developer, n.d,a).

Further, the system has multiple power domains to provide low-power operation. This SoC is thus composed of three domains. The first is the radio domain, which contains the short-range radio and its supporting units. The second is the low-power domain, designed for ultra-low-power operating subsystems. The last one is the peripheral domain, which then contains most of the peripherals (Nordic Semiconductor, n.d,).

nRF54L15 also features Arm TrustZone technology and supporting units to ensure system protection and key management. This enables hardware-enforced separation, which thus reduces the potential for attack by isolating confidential information and critical security firmware from the rest of the application (Arm Developer, n.d,b).

# 3

# Unique Program Execution Checking

The purpose of this chapter is to give insight into the theory behind the UPEC methodology and to look into the intent behind it. The chapter also explains the UPEC-SoC extension to the methodology, which makes it possible to consider peripherals in a system as well. The templates and the tutorial provided by the UPEC team are also introduced.

The last section of this chapter has the intention of helping visualize what the UPEC method and the UPEC-SoC method actually look like in practice. This is to help establish a logical connection between the theoretical statements of the UPEC methods and the actual property as it would be presented in SVA. This is based on experiences gained during the experiments, the usage of the templates provided, and the general theoretic understanding of the methods.

The UPEC-SoC method is built on the same premises as the regular UPEC method. However, it has a few more considerations to be able to consider peripherals and not just the processor core. Therefore, section 3.2 will go on to explain the UPEC-SoC method, to clarify how the method extends onto SoCs as well.

Any further notion of 'the UPEC method' beyond this chapter will regard these two as one methodology. If there is any need to specify which methodology is referred to, this will be done using either 'the regular UPEC method' or 'the UPEC-SoC method', for the remaining chapters.

# 3.1 The Unique Program Execution Checking method

In attacks making use of microarchitectural side channels, non-trusted user processes do not have the privileges needed to directly read confidential data within a system. However, if there are any observable or measurable differences from a user's point of view, whenever an unprivileged user runs a program, these differences can be misused. An unprivileged user would in this case refer to a user that should not have access to this confidential information.

If the adversary is able to somehow measure the difference in any way, and then work out a way to find the secret based on the difference, the adversary could imaginably be able to manipulate the system and get hold of the secret data.

As stated in Fadiheh et al. (2019), confidentiality in hardware/software systems is the requirement that non-trusted user processes are not able to read confidential data. Therefore, there should be no observable traces of the secret. These traces can be manifested in side effects such as differences in value, timing differences, voltage level changes, and more.

Fadiheh et al. (2019) first described the UPEC method. This approach was introduced as a way to detect hidden side channels. A large motivation behind this methodology is that there seemingly is no need for prior knowledge about previous security exploits (Müller et al., 2021). Therefore, this methodology could really be beneficial for discovering vulnerabilities in systems under development.

The general intent behind the UPEC methodology is to check whether a system could contain any vulnerabilities that could be misused to get hold of secret, or confidential, information. The method thus attempts to test whether the secret information in the system can affect the system's operation in any observable way. If that is the case, then there might be observable traces of confidential information that can be picked up and maliciously exploited. Determining what information should be seen as secret can be done based on the security requirements of the system (Fadiheh, 2022).

The idea behind protecting this confidential data is that a system should behave uniquely, based on the confidential data within. This means that the values assigned to the set of architectural state variables should be independent of the confidential information (Fadiheh, 2022). The system should rather behave predictably, such that there are no user-observable behavior differences due to the secret.

Therefore, if the system executes uniquely in regard to the secret, this secret data remains confidential. This concept is called Unique Program Execution.