Daniel Eduardo Guarecuco Aguiar

# Multi-dimensional exploration of the Minimum Energy Point for RISC-V subsystem in 22 nm FDSOI

Master's thesis in Embedded Computing Systems Supervisor: Snorre Aunet Co-supervisor: Torbjørn Ness June 2023

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Daniel Eduardo Guarecuco Aguiar

# Multi-dimensional exploration of the Minimum Energy Point for RISC-V subsystem in 22 nm FDSOI

Master's thesis in Embedded Computing Systems Supervisor: Snorre Aunet Co-supervisor: Torbjørn Ness June 2023

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

# ABSTRACT

Battery operated devices are highly constraint in energy budget, there is a need for energy-efficient designs. Designing circuits to operate in the Minimum Energy Point (MEP) yields great energy savings, by at least 20%, by reducing supply voltage and operating frequency. The MEP is in the near or sub-threshold region, such that the circuit becomes very sensitive to PVT variations.

This thesis proposes a methodology to study and locate the MEP and its relationship with supply voltage, threshold voltage, channel length, body biasing, temperature and process variations, for a RISC-V Ibex CPU synthesized with standard cell libraries characterized for higher voltages with a commercially available 22 nm FDSOI technology. A critical path replica is converted into a ring oscillator for running SPICE simulations. The simulations are used to estimate the MEP of the CPU.

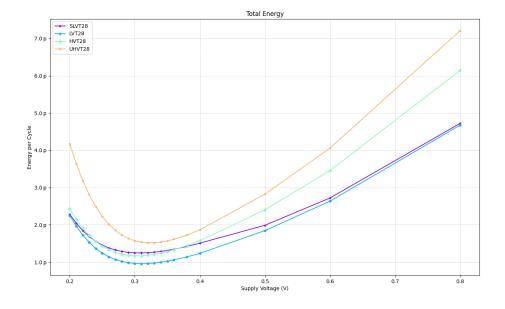

Results show that HVT and UHVT libraries are unfit for operating at the MEP due to a huge gap between slow and fast corners. It is shown that SLVT provides the best timing closure. The selection of threshold voltages becomes the most important parameter, adjustments can be made later by selecting a proper channel length and body-biasing voltages.

# PREFACE

This thesis is the final part of my double-degree in the European Master in Embedded Computing Systems (EMECS or MSECS) at the Department of Electronic Systems, at the Norwegian University of Science and Technology in Trondheim, and the Department of Control and Computer Engineering at the Politecnico Di Torino in Italy.

First and foremost, I am immensely grateful to my academic supervisor, Snorre Aunet, to all the great people at Nordic Semiconductor: Torbjørn Ness, Anders Vinje, and Frode Pedersen, for their invaluable guidance, expertise, and continuous support throughout the entire research process. Their insightful feedback shown on every weekly meeting have played a pivotal role in shaping the direction of this thesis.

Likewise, I am indebted to the EMECS program for the amazing and enriching experience I had in these two beautiful countries. Both universities with a lot to offer in and outside the classrooms. A shout-out to all the faculty members, and fellow students who have been part of this journey.

# CONTENTS

|          | Abs             | stract                                       | i    |  |  |  |  |  |  |  |  |

|----------|-----------------|----------------------------------------------|------|--|--|--|--|--|--|--|--|

|          | Pre             | face                                         | ii   |  |  |  |  |  |  |  |  |

|          | Con             | ntents                                       | vi   |  |  |  |  |  |  |  |  |

|          | List of Figures |                                              |      |  |  |  |  |  |  |  |  |

|          | List            | of Tables                                    | viii |  |  |  |  |  |  |  |  |

|          | Abbreviations   |                                              |      |  |  |  |  |  |  |  |  |

| 1        | Intr            | oduction                                     | 1    |  |  |  |  |  |  |  |  |

|          | 1.1 Objectives  |                                              |      |  |  |  |  |  |  |  |  |

|          | 1.2             | Organization                                 | 2    |  |  |  |  |  |  |  |  |

| <b>2</b> | Theory          |                                              |      |  |  |  |  |  |  |  |  |

|          | 2.1             | Power and energy                             | 3    |  |  |  |  |  |  |  |  |

|          |                 | 2.1.1 Sources of power dissipation           | 4    |  |  |  |  |  |  |  |  |

|          | 2.2             | Dynamic Voltage and Frequency Scaling (DVFS) | 6    |  |  |  |  |  |  |  |  |

|          | 2.3             | Process, Voltage and Temperature variations  | 7    |  |  |  |  |  |  |  |  |

|   | 2.4                  | FDSOI                                          | 8  |  |  |  |  |  |  |  |

|---|----------------------|------------------------------------------------|----|--|--|--|--|--|--|--|

|   | 2.5                  | Ring oscillator                                | 9  |  |  |  |  |  |  |  |

|   | 2.6                  | Previous work                                  | 10 |  |  |  |  |  |  |  |

| 3 | Met                  | thods                                          | 13 |  |  |  |  |  |  |  |

|   | 3.1                  | List of tools                                  | 13 |  |  |  |  |  |  |  |

|   | 3.2                  | The RTL design: Ibex RISC-V Core               | 14 |  |  |  |  |  |  |  |

|   |                      | 3.2.1 Building the software                    | 15 |  |  |  |  |  |  |  |

|   |                      | 3.2.2 RTL simulation                           | 15 |  |  |  |  |  |  |  |

|   | 3.3                  | The synthesis                                  | 16 |  |  |  |  |  |  |  |

|   | 3.4                  | Power estimation                               | 17 |  |  |  |  |  |  |  |

|   | 3.5                  | Building a ring oscillator                     | 18 |  |  |  |  |  |  |  |

|   |                      | 3.5.1 Analog simulation of RO                  | 20 |  |  |  |  |  |  |  |

|   | 3.6                  | Estimating MEP from RO                         | 23 |  |  |  |  |  |  |  |

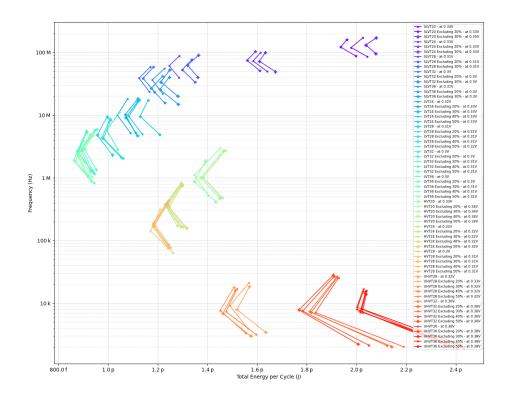

|   |                      | 3.6.1 Excluding worst performing cells         | 25 |  |  |  |  |  |  |  |

|   |                      | 3.6.2 Scaling the leakage power                | 27 |  |  |  |  |  |  |  |

|   | 3.7                  | Estimating MEP body-biasing corners            | 27 |  |  |  |  |  |  |  |

| 4 | $\operatorname{Res}$ | ults                                           | 31 |  |  |  |  |  |  |  |

|   | 4.1                  | RTL simulation                                 |    |  |  |  |  |  |  |  |

|   | 4.2                  | Synthesis and power estimation                 | 32 |  |  |  |  |  |  |  |

|   | 4.3                  | The testbench                                  | 34 |  |  |  |  |  |  |  |

|   | 4.4                  | MEP by sweeping supply voltage                 | 37 |  |  |  |  |  |  |  |

|   |                      | 4.4.1 MEP excluding worst performing cells     | 42 |  |  |  |  |  |  |  |

|   | 4.5                  | MEP by sweeping supply voltage and temperature | 42 |  |  |  |  |  |  |  |

|   |                 | 4.5.1 Scaling leakage power                                        | 47 |  |  |  |  |  |  |  |  |  |

|---|-----------------|--------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

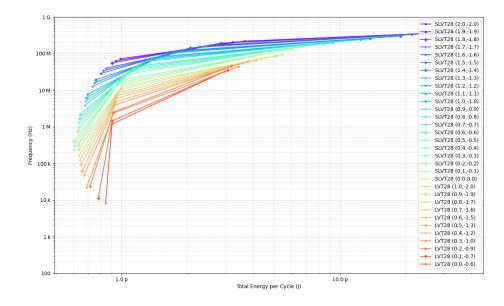

|   | 4.6             | MEP by sweeping supply voltage, temperature and body biasing       | 48 |  |  |  |  |  |  |  |  |  |

|   |                 | 4.6.1 SLVT                                                         | 49 |  |  |  |  |  |  |  |  |  |

|   |                 | 4.6.2 LVT                                                          | 52 |  |  |  |  |  |  |  |  |  |

|   |                 | 4.6.3 Adaptive Body-Biasing                                        | 56 |  |  |  |  |  |  |  |  |  |

| 5 | Discussion      |                                                                    |    |  |  |  |  |  |  |  |  |  |

|   | 5.1             | MEP and voltage scaling                                            |    |  |  |  |  |  |  |  |  |  |

|   | 5.2             | MEP and temperature                                                | 60 |  |  |  |  |  |  |  |  |  |

|   | 5.3             | MEP and FBB                                                        | 61 |  |  |  |  |  |  |  |  |  |

| 6 | Cor             | Conclusions                                                        |    |  |  |  |  |  |  |  |  |  |

|   | 6.1 Future work |                                                                    |    |  |  |  |  |  |  |  |  |  |

|   | References      |                                                                    |    |  |  |  |  |  |  |  |  |  |

|   | Appendices:     |                                                                    |    |  |  |  |  |  |  |  |  |  |

|   | A - Reports     |                                                                    |    |  |  |  |  |  |  |  |  |  |

|   | .1              | Critical path netlist                                              | 70 |  |  |  |  |  |  |  |  |  |

|   | .2              | Not annotated switching activity report                            | 70 |  |  |  |  |  |  |  |  |  |

|   | .3              | Data extracted from ring oscillator with open-loop: input to VDD . | 72 |  |  |  |  |  |  |  |  |  |

|   | .4              | Data extracted from ring oscillator with closed-loop               | 73 |  |  |  |  |  |  |  |  |  |

|   | в-              | Scripts                                                            | 74 |  |  |  |  |  |  |  |  |  |

|   | .5              | Main script                                                        | 74 |  |  |  |  |  |  |  |  |  |

|   | .6              | Synthesis script                                                   | 76 |  |  |  |  |  |  |  |  |  |

|   | .7              | Power estimation script                                            | 77 |  |  |  |  |  |  |  |  |  |

| .8  | Build Ocean script          | 78 |

|-----|-----------------------------|----|

| .9  | Build testbench script      | 80 |

| .10 | Extract timing from liberty | 83 |

| .11 | Verilog-A Counter           | 86 |

# LIST OF FIGURES

| 2.1.1 Dynamic power dissipated by an Inverter                                              | 5  |

|--------------------------------------------------------------------------------------------|----|

| 2.1.2 Static power dissipated by an Inverter                                               | 6  |

| 2.4.1 Bulk and FSDOI CMOS transistors cross-section                                        | 8  |

| 2.5.1 Schematic of a ring oscillator                                                       | 9  |

| 3.0.1 Minimum Energy Point exploration flow                                                | 14 |

| 3.5.1 Diagram of a testbench for ring oscillator                                           | 18 |

| 3.7.1 Testbench for simulating basic gates with body bias                                  | 29 |

| 4.1.1 Simulation traces captured in FSDB file                                              | 32 |

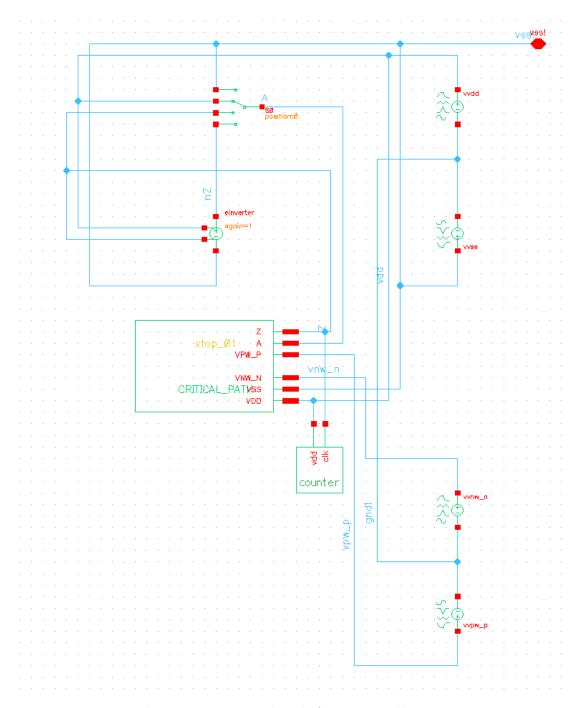

| 4.3.1 Testbench for ring oscillator                                                        | 35 |

| 4.3.2 Critical path replica subcircuit                                                     | 36 |

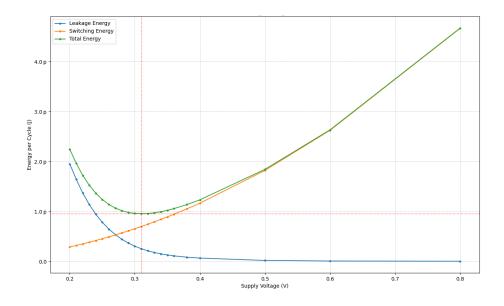

| 4.4.1 MEP for a 22 nm FDSOI process, TT, LVT, 28 nm at 25°C                                | 38 |

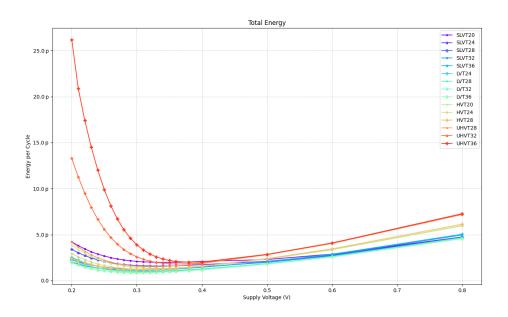

| 4.4.2 Total Energy for SLVT, LVT, HVT and UHVT 28 nm, TT at 25°C $$                        | 39 |

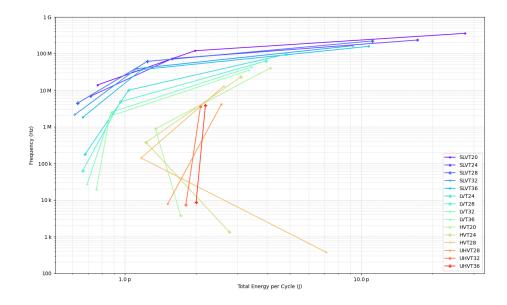

| 4.4.3 Total Energy for all VT and all channel length at TT, 25°C                           | 40 |

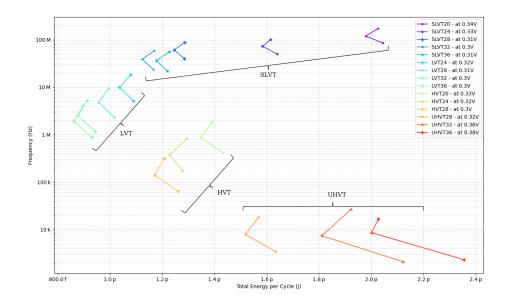

| 4.4.4 MEP for all VT and channel length, TT at 25°C $\ldots$                               | 41 |

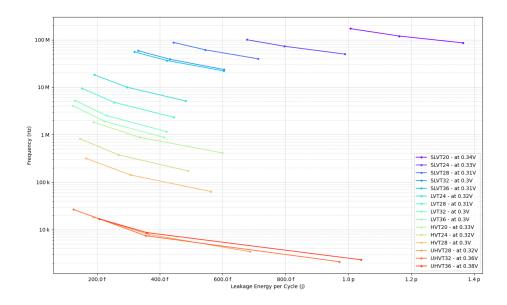

| 4.4.5 Leakage at MEP for all VT and channel length, TT at 25°C $\ \ldots$ .                | 41 |

| 4.4.6 MEP for all VT and channel length excluding worst cells, TT at 25 $^\circ\mathrm{C}$ | 42 |

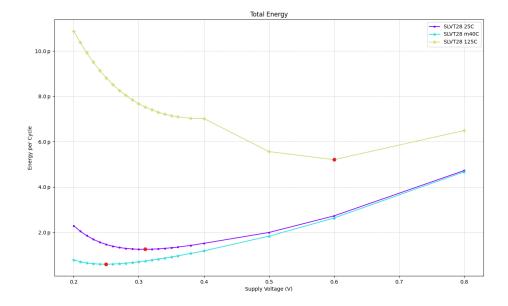

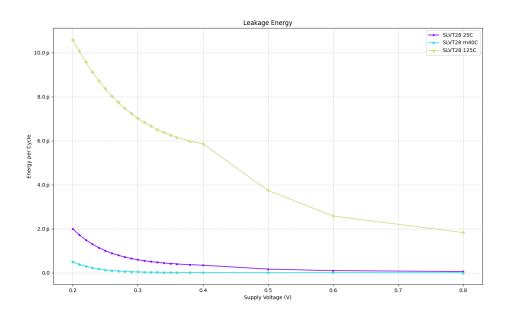

| 4.5.1  | Total energy for SLVT28 at -40, 25 and 125°C $\ldots$                                                     | 43 |

|--------|-----------------------------------------------------------------------------------------------------------|----|

| 4.5.2  | Leakage energy for SLVT28 at -40, 25 and 125°C. $\ldots$                                                  | 44 |

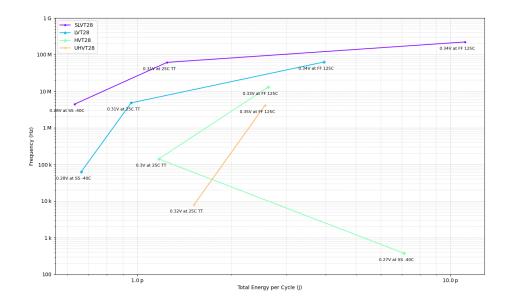

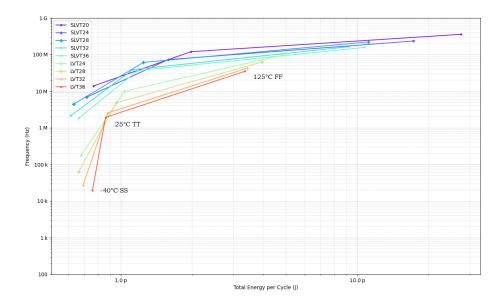

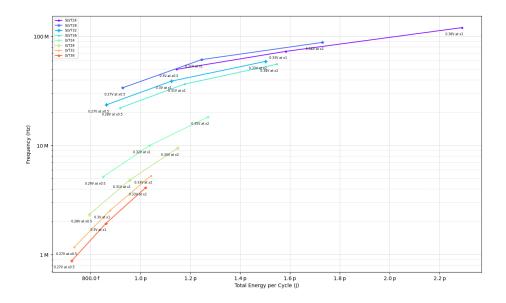

| 4.5.3  | MEP for SLVT, LVT, HVT, UHVT 28 nm at SS, TT, FF, -40, 25, $125^{\circ}$ C                                | 45 |

| 4.5.4  | MEP for SLVT and LVT all channel length at SS, TT, FF, -40, 25, $125^{\circ}$ C                           | 46 |

| 4.5.5  | MEP for all VT and all channel length at SS, TT, FF, -40, 25, 125°C                                       | 47 |

| 4.5.6  | MEP for x0.5, x1 and x2 leakage                                                                           | 48 |

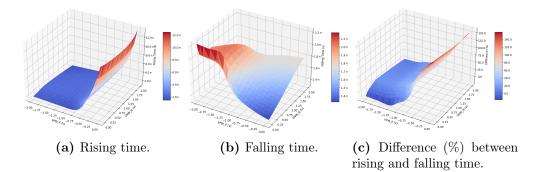

| 4.6.1  | INVX010: Sweeping biasing voltages for SLVT, 28 nm, at the slow condition                                 | 49 |

|        | NAND3X010: Sweeping biasing voltages for SLVT, 28 nm, at the slow condition                               | 49 |

|        | NOR3X010: Sweeping biasing voltages for SLVT, 28 nm, at the slow condition                                | 50 |

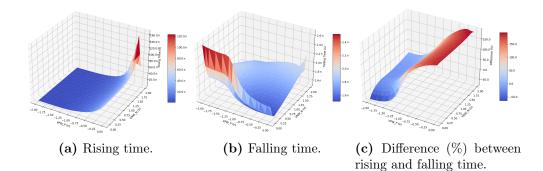

| 4.6.4  | SLVT28 INV, NAND, NOR: Skew between rising and falling time $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ . | 50 |

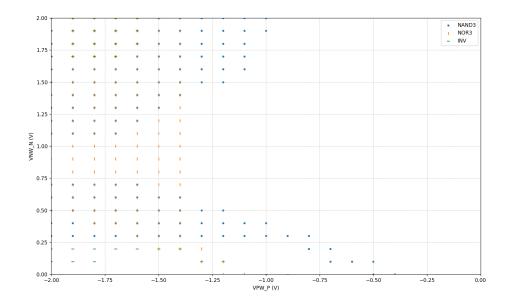

| 4.6.5  | SLVT28 superposed skew results                                                                            | 51 |

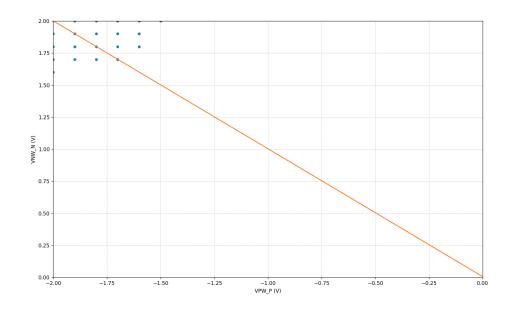

| 4.6.6  | SLVT28 skew intersection                                                                                  | 51 |

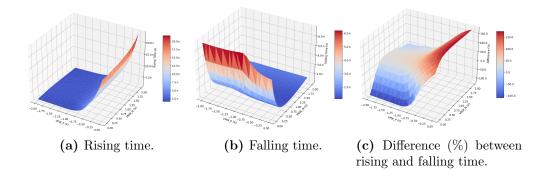

|        | INVX010: Sweeping biasing voltages for LVT, 28 nm, at the slow condition                                  | 52 |

|        | NAND3X010: Sweeping biasing voltages for LVT, 28 nm, at the slow condition                                | 53 |

| 4.6.9  | NOR3X010: Sweeping biasing voltages for LVT, 28 nm, at the slow condition                                 | 53 |

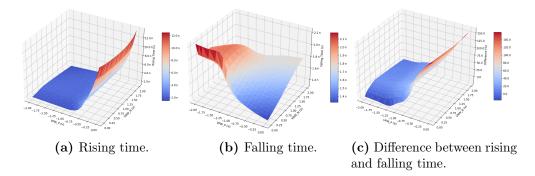

| 4.6.1  | $\mathbbm{LVT28}$ INV, NAND, NOR: Skew between rising and falling time                                    | 53 |

| 4.6.1  | LVT28 superposed skew results                                                                             | 54 |

| 4.6.12 | $2\!\!MEP$ for SLVT28 and LVT28 with different fixed body-bias $\ldots$ .                                 | 55 |

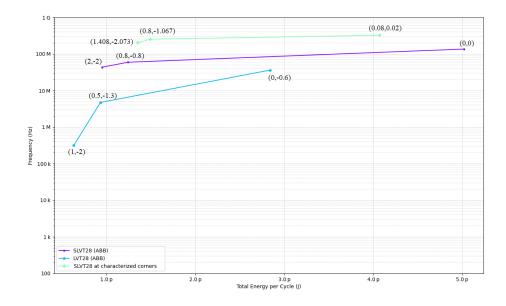

| 4.6.1  | 3MEP for SLVT28 and LVT28 using Adaptive Body-Bias                                                        | 57 |

# LIST OF TABLES

| 3.5.1 Simulation corners for SLVT and LVT on typical conditions                         | 22 |

|-----------------------------------------------------------------------------------------|----|

| 3.5.2 Simulation corners for HVT and UHVT on typical conditions                         | 23 |

| 3.5.3 Simulation corners for SLVT and LVT on SS, TT and FF conditions.                  | 24 |

| 3.6.1 Timing ratio between typical and worst case for a NAND3 example.                  | 26 |

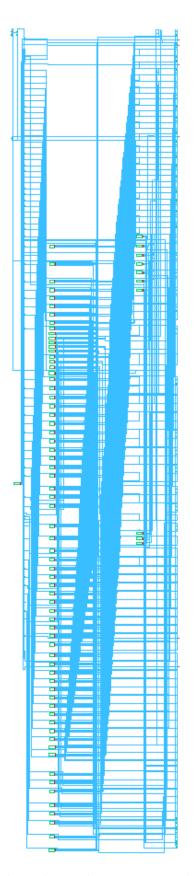

| 4.2.1 Cell comparison between Ibex Core and Critical Path                               | 34 |

| 4.4.1 Energy and frequency comparison at different supply voltages for LVT28            | 38 |

| 4.5.1 MEP conditions for all VT for 28 nm                                               | 45 |

| 4.5.2 MEP conditions for SLVT and LVT for all channel length                            | 46 |

| 4.5.3 PVT variations around MEP for all VT and all channel length with fixed body-bias. | 47 |

| 4.6.1 SLVT28 biasing points                                                             | 52 |

| 4.6.2 LVT28 biasing points.                                                             | 54 |

| 4.6.3 PVT variations around MEP with FBB for SLVT and LVT28 $\ .$                       | 56 |

| $4.6.4~\mathrm{PVT}$ variations around MEP with ABB for SLVT28 and LVT28                | 57 |

| .3.1 Data from ring oscillator in open-loop: LVT28, TT, 25°C, input to                  |    |

| .4.1 | Data from | ring | oscillator | in | $\operatorname{clos}$ | sed-loop: | LVT28, | TT, $2$ | 5°C, i | nput |    |

|------|-----------|------|------------|----|-----------------------|-----------|--------|---------|--------|------|----|

|      | to !Z     |      |            |    |                       |           |        |         |        |      | 73 |

# ABBREVIATIONS

List of all abbreviations in alphabetic order:

- **ABB** Adaptive Body-Bias

- CMOS Complementary Metal–Oxide–Semiconductor

- **DUT** Design Under Test

- **FBB** Forward Body-Bias

- FDSOI Fully Depleted Silicon-On-Insulator

- **FF** Fast-Fast

- HVT High Threshold Voltage

- **LVT** Low Threshold Voltage

- MEP Minimum Energy Point

- NTNU Norwegian University of Science and Technology

- **PVT** Process, Voltage and Temperature

- **RBB** Reverse Body-Bias

- **RO** Ring Oscillator

- **SOTB** Silicon on Thin-BOX

- **SLVT** Super-Low Threshold Voltage

- SS Slow-Slow

- **TT** Typical-Typical

- UHVT Ultra-High Threshold Voltage

- VT Threshold Voltage

#### CHAPTER

### ONE

# INTRODUCTION

In recent years, the field of embedded systems has experienced rapid development and has become an integral part of our daily lives. These are specialized computer systems designed to perform specific tasks in larger systems or devices [1]. They are found in many applications, including consumer electronics (such as smartphones, tablets, and smartwatches), automotive systems, medical devices, industrial control systems, and Internet of Things (IoT) devices. As the demand for these applications continues to grow, so does the need for efficient power utilization.

Most microprocessors ever produced go into the field of embedded systems [1]. It has been estimated that there are about 16 billion mobile devices (phones and tables) for the year 2023 [2],[3]. Other report forecasts 15 billion connected IoT devices for this year [4]. It is difficult to pinpoint the exact number of embedded systems currently available due to factors such as the variety of applications and industries they serve. In addition, the definition of an embedded system can vary depending scope of the classification.

One of the key challenges for embedded system designers is power consumption. These systems are typically powered by batteries or other limited power sources, as energy harvesting technologies. Their power requirements have a direct impact on their functionality, reliability, and lifespan. In addition, many embedded systems are deployed in remote or inaccessible locations, making it difficult or expensive to replace or frequently recharge their power supplies. Therefore, optimizing power consumption is extremely important to ensure sustainable systems.

To solve these power consumption challenges, various methods have been developed and implemented. These methods aim to reduce the energy consumption at various levels, including hardware design, software optimization, and circuit level. From an architectural perspective, RISC processors are increasingly used in this domain due to their low power consumption and computing power. For low power requirements, RISC is most suited that CISC architectures [5]. A promising development in this field is the RISC-V CPU architecture. Which provides an open-source instruction set architecture (ISA) that is simple, flexible, modular and extensible [6].

Meanwhile, from a circuit-level perspective, voltage scaling is a known method to significantly reduce power and energy consumption, because of its square relationship with supply voltage [7]. There is an optimum supply voltage that yields the most energy-efficient operation, called the Minimum Energy Point (MEP), which is located in the sub-threshold region, and it is depend on the activity factor and threshold variations [8]. This region is ideal for applications where low energy is the primary focus instead of performance.

### 1.1 Objectives

The aim of the thesis is to further research voltage scaling techniques in the near and sub-threshold regions to find the Minimum Energy Point of a RISC-V CPU subsystem. Many parameters are taken into considerations, such as the impact of different threshold voltages, different transistors' channel length, as well as process and temperature variations. The design is synthesised in a commercially available 22 nm FDSOI technology with *Synopsys Design Compiler*. Analog simulations are run with *Cadence Virtuoso* in order to vary PVT conditions.

# 1.2 Organization

The report is structured into four main chapters: theory, methods, results and discussion. The theory chapter provides relevant basic theory that is important to the thesis. The methods describes the techniques and tools used to generate the data and results. The results extracted from the methods section are later described. Finally, the discussion chapter serves as a platform for analysis and comparison of the results with the theory.

#### CHAPTER

### TWO

### THEORY

This chapter gives an introduction to the theory supporting this study and some terms used in later chapters. First, it is important to understand how power is consumed in digital circuits and its relationship with energy. Later a common power management technique is introduced. Finally, a summary of what has been done in the field of Minimum Energy Point is given.

## 2.1 Power and energy

To fully understand the concept behind MEP it is important to have some basic background knowledge in how energy is utilized in digital CMOS circuits, so that low power optimizations can be targeted.

In an electric circuit, *power* P is the rate at which energy is transferred from the power source (e.g., battery) to an electrical element [9]. The power consumed at a given time is given by the product of the current through and the voltage across such element [7], see Equation 2.1.

$$P(t) = I(t)V(t) \tag{2.1}$$

The *energy* E consumed over a time interval is given by the accumulated power [7], see Equation 2.2.

$$E = \int_0^t P(t) dt \tag{2.2}$$

In a digital circuit, if the average power is evaluated in a clock period, the previous expression can be simplified as Equation 2.3, or 2.4 if the frequency is used.

$$E = P_{avg} * T_{clk} \tag{2.3}$$

$$E = \frac{P_{avg}}{f_{clk}} \tag{2.4}$$

#### 2.1.1 Sources of power dissipation

It is of particular interest to study the sources of power dissipation, which for CMOS technology can be divided mainly in two categories: the *dynamic* and *static* power.

The dynamic power refers to the power consumed by a transistor when switching states. Its dissipation is due mainly to the charging and discharging of load capacitances, this is also know as *switching power*. There is a second component to the dynamic power consumption, the *short-circuit* power, which is due to a direct short-circuit path between VDD and GND through the NMOS and PMOS transistors as they are both partially active. Since the short-circuit contribution is typically very small compared to the switching power, it can often be neglected. So that the dynamic power can be expressed as the contribution of the switching power, described by Equation 2.5 [7], [10].

$$P_{dynamic} \approx P_{switching} = \alpha C f_{clk} V_{DD}^2 \tag{2.5}$$

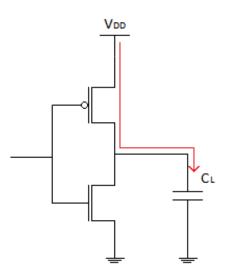

Where  $\alpha$  refers to the activity factor, or the probability that a circuit node transitions from low to high. The term *C* represents the loading capacitance. In this study, the terms dynamic power and switching power might be use interchangeably. Figure 2.1.1 illustrates how the switching energy is consumed in an inverter.

Figure 2.1.1: Dynamic power dissipated by an Inverter.

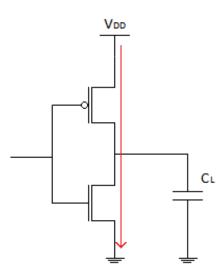

The static power is the power consumed by the circuit irrespective of the circuit state, even if it is not switching. This power loss is due to the non-ideal conditions of real transistors, which do not behave completely as ON/FF switches. The static power has multiple contributors, but the dominant source in modern CMOS technology is the *subthreshold leakage*. The static power is characterized by equation 2.6 and 2.7 [11]. This leakage is caused by a current flowing through a transistor that is meant to be OFF, but it is not due to reduced threshold voltages [12]. In this study, the terms static power and leakage power might be use interchangeably.

$$P_{static} \approx P_{subth} = I_{subth} V_{DD} \tag{2.6}$$

$$I_{subth} = \mu_N C_{ox} \frac{W_N}{L_N} V_t^2 e^{\frac{V_{GS} - V_{th}}{nV_t}} (1 - e^{-\frac{V_{DS}}{V_t}})$$

(2.7)

Where  $\mu_N$  is the electron carrier mobility,  $C_{ox}$  is the gate capacitance per unit area,  $W_N$  is the channel width,  $L_N$  is the channel length,  $V_t$  is the thermal voltage,  $V_{th}$  is the threshold voltage and n is the inverse slope of the subthreshold current [11]. Figure 2.1.2 shows how this type of energy is dissipated in an inverter.

Figure 2.1.2: Static power dissipated by an Inverter.

Putting together the two main sources of power dissipation, Equations 2.8 and 2.9 are obtained.

$$P_{total} = P_{dynamic} + P_{static} \tag{2.8}$$

$$P_{total} = \alpha C f_{clk} V_{DD}^2 + I_{leakage} V_{DD} \tag{2.9}$$

In terms of energy:

$$E_{total} = E_{switching} + E_{leakage} \tag{2.10}$$

$$E_{total} = \alpha C V_{DD}^2 + \frac{I_{leakage} V_{DD}}{f}$$

(2.11)

# 2.2 Dynamic Voltage and Frequency Scaling (DVFS)

According to [13], there are two successful methods for reducing the dynamic power, which becomes evident from Equation 2.5: activity ( $\alpha$ ) reduction and supply voltage (VDD) reduction. Due to the quadratic relationship between power and supply voltage, reducing this term can lead to significant power savings. There are two approaches to achieving supply voltage reduction while maintaining performance: static and dynamic methods.

In the *static supply voltage reduction* method, multiple supply voltages are utilized withing the same circuit. The higher supply voltage is employed for performance-critical logic that requires higher speeds but consumes more power, and low supply voltages are used for non-critical paths, with lower speeds but dissipating less power.

Alternatively, in *dynamic supply voltage scaling*, the logic chip is designed to operate at its maximum performance level when supplied with the highest voltage. However, when the performance demand is low, the chip can be operated at a lower voltage, resulting in reduced performance but substantial power reduction.

This second method is often called *Dynamic Voltage and Frequency Scaling* (DVFS), as the frequency often must scale down along with the supply voltage in order to guarantee correct operation in synchronous systems [10]. Evidence supports the effectiveness of this technique, for instance, the study carried by [10] on a 9-processor JPEG application, using 1.3 V and 0.8 V for voltage scaling, achieved a reduction of 48% energy consumption, while only diminishing performance by 8%, with an additional 12% area overhead for the DVFS circuit.

As voltage and frequency are both reduced, it can be seen from Equation 2.11 an opposing trend between the switching and leakage component of the energy. The switching energy term is always decreasing by a square relationship on VDD, while the leakage term is increasing due to slower operation times. At low supply voltages, leakage energy takes dominance. Their balance define the MEP location.

Implementing a DVFS systems in a general-purpose microprocessor involves three essential components: 1) An intelligent operating system capable of dynamically adjusting the processor speed. 2) A regulation loop that generates the minimum required voltage for the desired speed. 3) A microprocessor designed to function across a wide range of voltages. Software control is necessary as hardware alone may not be able to differentiate between computationally intensive tasks and non-speed-critical tasks. The supply voltage is regulated through a frequency-voltage feedback loop, controlled by dedicated ring oscillator, which is commonly used as a critical path replica. All chips within the system operate at the same clock frequency and supply voltage given by the ring oscillator [14].

## 2.3 Process, Voltage and Temperature variations

By looking at the leakage current in the sub-threshold regime (Equation 2.7), it can be seen that it is dependent on the threshold voltage, supply voltage and temperature (PVT). Meaning that changes in any of these parameters will reflect a variation in the drain current. According to [15], circuits are more sensitive to operating conditions in this region. Energy and performance are highly impacted due to process variations, operating temperatures and environment conditions.

The study also shows that an increased temperature improves speed, at the expense of increased energy dissipation. The effect is due to an reduced threshold voltage and an increased mobility at higher temperatures [8]. Temperature has

a much greater impact in the sub-threshold region than in the strong inversion region.

Moreover, due to manufacturing processes, transistors will show a random variation on the device length and width, that deviates the threshold voltage of each device [16]. It has been studied [17] that the standard deviation of the threshold voltage follows an inverse relationship with the square root of the transistor area. Meaning that variation spreads are higher as the device dimensions are reduced. From the same equation, in the sub-threshold regime, the threshold voltage has exponential effects in the drain current.

The stated above shows how difficult it might be to operate with low supply voltages in the sub-threshold region.

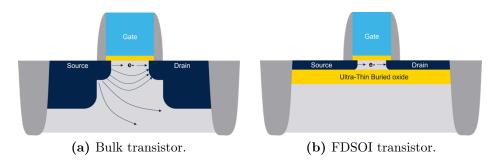

#### 2.4 FDSOI

FDSOI is a planar process technology that provides an alternative solution to overcome some of the limitations of bulk CMOS technology at reduced silicon geometries, it stands for *Fully Depleted Silicon on Insulator*. The FDSOI process has two distinct features. First, an ultra-thin buried oxide layer is placed on the top of the base silicon. Second, a very thin silicon layer on top creates the transistor channel. As the transistor channel layer is very thin, no channel doping is required, which makes the transistor fully depleted [18].

FDSOI technology exhibits significantly improved electrostatic characteristics of transistors compared to conventional bulk technology. The incorporation of a buried oxide layer serves to decrease the parasitic capacitance between the source and the drain. Moreover, it effectively confines the electron flow from the source to the drain, resulting in a remarkable reduction in leakage currents that impair performance [18]. Figure 2.4.1 shows the cross-section of both technologies.

Figure 2.4.1: Bulk (a) and FSDOI (b) CMOS transistors cross-section. Illustration from STMicroelectronics [18].

In this technology, the transistors possess four effective terminals: source, drain, gate, and body, which refers to the volume beneath the conduction channel.

In FDSOI, by applying a voltage bias to the body terminal, the transistor's threshold voltage can be effectively manipulated , controlling on the fly the threshold voltage by software [19].

This boody-bias can be employed in two directions: forward body-bias (FBB) and reverse body-bias (RBB). In FBB, the PMOS body terminal is driven to a lower voltage than the source supply (VDD), while the NMOS body terminal is driven to a higher voltage than the source supply voltage (typically ground). This configuration lowers the device threshold voltage, thus increasing performance. Conversely, in RBB, the PMOS body terminal is driven to a higher voltage than VDD, while the NMOS body terminal is driven to a lower voltage than the supply (often a negative voltage). This increases the threshold voltage with reduced leakage [19].

In summary, the body-bias technique has different impacts on the MOS transistor's fundamental characteristics. Forward body-bias (FBB) is aimed at enhancing performance by increasing mobility and reducing the threshold voltage (VT). On the other hand, reverse body-bias (RBB) is suitable for mitigating leakage current by increasing VT and improving the sub-threshold slope [19].

### 2.5 Ring oscillator

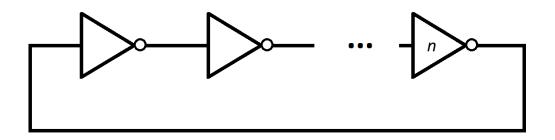

A ring oscillator is a digital oscillator created by connecting an odd number (n) of inverters in a closed-loop cascade [20]. When each inverter has the same propagation delay (Ti), the oscillation frequency can be determined using Equation 2.12, as illustrated in Figure 2.5.1.

$$F_{CLK} = \frac{1}{n * T_i} \tag{2.12}$$

Figure 2.5.1: Schematic of a ring oscillator.

These oscillators are highly desirable due to their ease of design using CMOS

technology. They can achieve oscillations at low voltages, offer electrical tuning, and provide a wide range of tuning options [11]. Additionally, by adjusting the supply voltage, a Voltage-Controlled Oscillator (VCO) can be obtained, allowing an increase or decrease of the propagation delay in each gate. One common application is incorporating them into a dynamic voltage scaling controller to regulate the operating frequency based on the core's performance [7].

## 2.6 Previous work

Studying low-power and low-energy techniques is not new. Minimum Energy Point around the sub-threshold region has been researched before, both by mathematical models, simulations and physical implementations.

In the study carried by [15], an optimal pair of VDD-Vth is explored with simulations of 11-stage NAND ring oscillators with BSIM3 models (Berkeley Short channel Insulated gate field effect transistor Model). It shows the effects of activity factor and operating conditions, concluding that operating at the optimal point can lead to an order of magnitude in energy savings.

Likewise, [16] studied the MEP in a 11-stage NAND ring oscillator with variable activity factor. Later extending the simulations to CMOS SRAMs, showing that the leakage energy increases and the dynamic energy reduces in a quadratic manner as the supply voltage is reduced. Finally locating the MEP to be around 300 mV.

The MEP has been studied [21] for a 32-bit adder and 16-bit multiplier circuits in 65 nm Silicon on Thin-BOX (SOTB) and bulk devices. The circuits were implemented on chip using only 2-input gates. The results reveal that minimum energy of SOTB is up to 49% smaller than bulk devices and that the MEP is proportional to the temperature. The supply voltage for a minimum energy operation increases linearly with temperature.

Finite impulse response (FIR) filters have been simulated and tested on chip to examine the MEP in sub-threshold circuits, showing the dependence on technology, design, temperature, duty cycle and workload. Variation in these parameters require an adjustment of hundred of millivolts in the supply voltage, demonstrating the need for a MEP tracking mechanism. Moreover, the study confirms that CMOS standard cells libraries are fit for sub-threshold operations [8].

According to [22], some algorithms have been developed previously to estimate the MEP at run time, however they are time-consuming and not fit for real-time operations. They proposed a real-time tracking algorithm based in predefined MEP curves characterized at Slow-Slow (SS), Typical-Typical (TT), and Fast-Fast (FF) conditions generated for a given chip during the boot phase. It was tested with a 50-stage inverter chain designed with 55 nm deeply depleted channel (DDC) process. It demonstrates that this model can quickly track the MEP even with wide PVT variations.

Finally, the *Minimum Energy Point Exploration in a CPU Subsystem* specialization project [23], carried in the fall semester 2022 at NTNU, also under Nordic Semiconductor supervision is the precursor of the current thesis. The study was limited to a single VT flavor (LVT) with a 24 nm channel length in a 22 nm FD-SOI process. The results were obtained at 25°C, with a typical transistor model and the body biasing recommended by the foundry.

This project provided a great opportunity for laying the foundations of the current work, as much of the initial setup and debugging of new tools happened during that time. Therefore, this specialization project enabled to extend the scope of this thesis and explore various conditions that yield better estimations.

#### CHAPTER

### THREE

### METHODS

The current thesis was conducted under the guidance of Nordic Semiconductor, located in Trondheim, Norway, during the spring semester 2023. It is the continuation of the previous study, *Minimum Energy Point Exploration in a CPU Subsystem*, carried in the fall semester 2022 [23].

This chapter presents the methodology and tools required to replicate the study, so that it can be expanded to different designs and technologies. Although there are many different tools, both licensed and freeware, the ones selected are those widely used both by the industry and by Nordic Semiconductor.

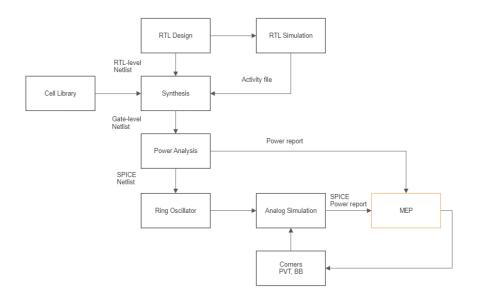

The flow used to extract the MEP of a RISC-V CPU is illustrated in Figure 3.0.1, every step is described in detail in the following sections. An overview of the methodology is as follows: The RTL design is simulated to extract the switching activity. The design goes under a synthesis process taking the selected standard cell library and the activity file as inputs. A gate-level netlist is obtained, from which a power estimation is generated and the critical path extracted. The critical path is used to build a ring oscillator that is simulated at the circuit-level sweeping through different PVT corners. From the analog simulation results and the original power report, the MEP for the selected conditions can be estimated. The worst-condition of the MEP is used to generated valid biasing points that can be feedback to the analog simulation to obtain better results through adaptive body-biasing techniques.

#### 3.1 List of tools

• Mentor QuestaSim 10.7c\_3.

Figure 3.0.1: Minimum Energy Point exploration flow.

- Synopsys Verdi 2021.09-sp2-2

- Synopsys Design Compiler 2020.09.

- Synopsys PrimePower 2019.12-SP5.

- Cadence Virtuoso ICADVM20.1

- Python 3.6.8 and 3.11.1

# 3.2 The RTL design: Ibex RISC-V Core

The very first step when studying the Minimum Energy Point is to have a design that can benefit from this technique. In particular, processors can profit greatly from Dynamic Voltage and Frequency Scaling (DVFS) and from threshold voltage scaling [22].

The choice of the Ibex RISC-V Core for the MEP exploration was based on several factors. It is based on a reduced instruction set computer (RISC) architecture, which simplifies the processor design. These type of architecture is incredible popular. According to RISC-V International, there are more than 10 billion RISC-V cores in the market, and tens of thousands of engineers working on RISC-V initiatives globally. They have seen more than 26% membership growth year-over-year, with over 3,180 members across 70 countries [24].

The Ibex Core is an open-source project targeted for embedded applications and has been thoroughly tested. It contains all the necessary modules for a minimum working CPU subsystem and offers integration with various simulation and synthesis tools. Additionally, it provides a framework for building and simulating designs, along with extensive documentation [25]. According to the Ibex group [25], the Ibex Core is a 32-bit production quality CPU based on the RISC-V architecture. It is implemented in SystemVerilog and maintained by lowRISC. The developers state that this core is specifically designed for embedded control applications. It has undergone extensive verification and supports various RISC-V extensions such as Integer, Embedded, Integer Multiplication and Division, Compressed, and Bit Manipulation extensions.

The project repository provides a *Simple System*, which integrates the Ibex Core with a basic system for simulations. The Simple System includes the following components:

- Ibex Core.

- Single memory for instructions and data.

- Basic peripheral for writing ASCII output to a file and halting the simulation.

- Basic timer peripheral capable of generating interrupts.

- Software framework for program development.

The Ibex Core RTL source files are actively under review and development by the community in a public repository. Many changes have been pushed since the beginning of this thesis. The CPU design used in this study was released in October 14th, 2022.

#### 3.2.1 Building the software

To test the capabilities of the Simple System, a *hello\_test.c* file is also provided. This file contains instructions for printing strings to a log file based on a periodic timer. The source file was compiled using the developers' provided Make executable. The resulting binary was then dumped into a Verilog Memory file (vmem) following the memory organization of the Simple System. This allows the instructions to be fetched by the Ibex core.

The Simple System binary was built using FuseSoc, a package manager and set of build tools for HDL [26]. FuseSoc allows the passing of parameters to build the final RTL design. For this study, the following parameters were used: RV32MFast (fast multiply extension), RV32BNone (no bit manipulation extension), RegfileFF (register file based on flip-flops), and the path to the memory file (vmem) containing the software code. These parameters are the standard recommendations according to the Ibex documentation for a simple system.

#### 3.2.2 RTL simulation

Once a design has been selected for the study, the next step in the MEP exploration process is to extract the switching activity through RTL simulations. According to the Synopsys PrimePower user guide [27], three main components are required to obtain an accurate power estimate from a design:

- Gate-level netlist describing the design.

- Power characterization of cells in a standard library.

- RTL simulation traces.

The gate-level netlist is obtained after synthesis, and the power characterization is already available in the library. However, the RTL simulation traces need to be extracted at this stage to provide the switching activity of the design under a specific workload defined by the firmware running on the core.

To extract the RTL simulation traces, the Simple System design, with the software loaded into the instruction memory, was simulated using *Mentor QuestaSim*  $10.7c_3$ . The simulation was executed using the make run instruction provided by the Ibex framework. The Makefile takes care of loading all source RTL files in the correct order using TCL scripts.

The primary focus at this stage is the extraction of the switching activity. As a result, all signals were stored in a Fast Signal Database (FSDB) during the simulation, allowing their utilization in the subsequent estimation phase. The clock period specified in the testbench was continuously fine-tuned within the exploration loop to achieve an optimal value for each corner. It is crucial for the clock speed used during synthesis to match the simulated clock in order to obtain the most accurate estimation. Failing to do so could potentially impact the toggle rates [28].

### 3.3 The synthesis

In accordance with a standard synthesis flow [29], the Ibex Simple System underwent synthesis using a 22 nm FDSOI library in *Synopsys Design Compiler 2020.09*. It was synthesized with different transistor flavors and different channel length: SLVT (20 to 36 nm), LVT (24 to 36 nm), HVT (20 to 28 nm) and UHVT (28 to 36 nm). The synthesis process was carried out through TCL scripting (refer to Appendix .6). The flow for synthesis is outlined below:

First, a 22 nm FDSOI 8-track standard cell library was selected for the synthesis process. The available libraries are listed below.

- 1. SLVT : in 20, 24, 28, 32, 36 nm characterized at 0.4V.

- 2. LVT: in 24, 28, 32, 36 nm characterized at 0.4V.

- 3. HVT: in 20, 24, 28 nm characterized at 0.8V.

- 4. UHVT: in 28, 32, 36 nm characterized at 0.8V.

Additionally, the RTL source files were loaded in the same hierarchical order as done during simulation. All files related to the testbench are excluded from the synthesis.

To ensure accurate power analysis, the switching activity needed to be reported in a Switching Activity Interchange Format (SAIF) file. This involved associating the design objects with their corresponding gate-level netlist elements. In other words, mapping RTL names to their gate-level counterparts. During synthesis, the switching activity was included in the FSDB file, and a name mapping database was created. The FSDB file was then converted into a SAIF file using the fsdb2saif command provided by *Synopsys Verdi 2021.09-SP2-2*.

A clock constraint was set, and its value was determined through a manual iterative loop. The loop continued until the critical path achieved a slack value of zero, or slightly negative. So that it is operating at its maximum speed. During this loop, new RTL simulations are obtained with the corresponding clock value (section 3.2.2), so that all clocks match.

The synthesized gate-level netlist, the Synopsys Design Constraint (SDC) file and the name mapping database were exported to be consumed in the following step.

### 3.4 Power estimation

An average power analysis was performed using a TCL script (refer to Appendix .7) in *PrimePower 2019.12-SP5* on the gate-level netlist generated by Synopsys Design Compiler in the previous step. To enhance accuracy, the analysis utilized the SDC file (constraints), SAIF file (containing switching activity), and an RTL-to-gate mapping file.

It is crucial for the power estimation to be reliable that close to 100% of the switching activity is properly annotated. This verification can be carried out using the **report switching activity** -list not annotated command to identify any unannotated switching activity.

A power report is generated for the Ibex Simple System. The report includes information about dynamic power (reported by Synopsys as *Net Switching* and *Cell Internal*), static power (*Cell Leakage*), and the total power consumption. The energy per cycle can be obtained by multiplying by the clock frequency used as a synthesis constraint. The report is only generated at typical corner characterized by the library (0.4 V/0.8 V, 25°C, Typical-Typical). There is no way of obtaining the MEP from this report. However, it will serve as a reference for extrapolating the power corners from a ring oscillator, for those corners not characterized in the library.

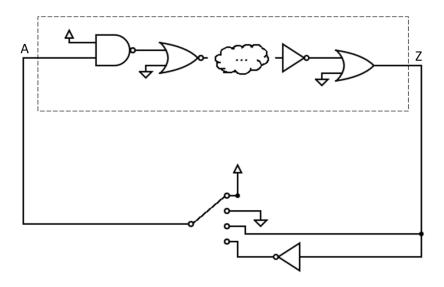

Figure 3.5.1: Diagram of a testbench for ring oscillator.

## 3.5 Building a ring oscillator

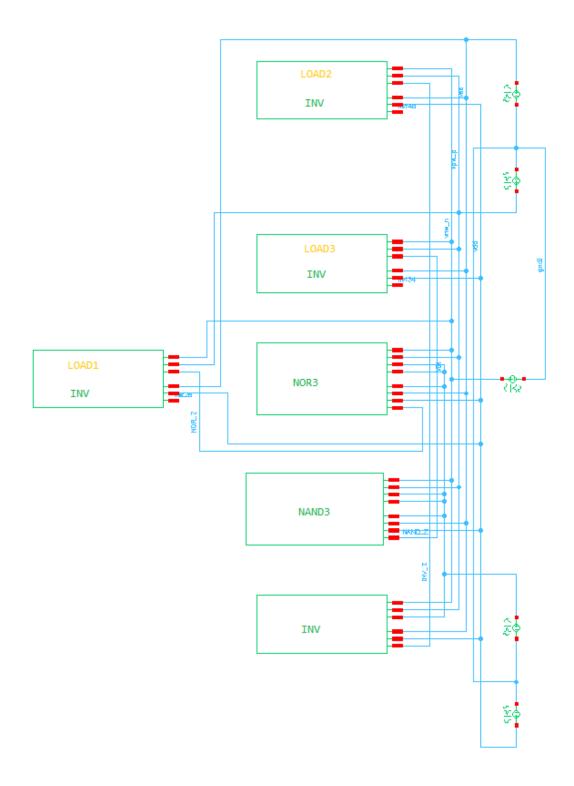

The power estimation conducted in the previous section 3.4 is limited to the characterized corners of the library. Specifically, the Typical-Typical (TT) process corner offers supply voltages of 0.4 V, 0.5 V, 0.6 V, and 0.8 V. Power estimation below 0.4 V cannot be performed using PrimePower, because the tool can only properly estimate the power consumption for the library corners, defined through liberty files. These files establish timing and power characteristics at a defined voltage for every cell in the library. These values are unknown for supply voltages not defined by the foundry. Instead, an analog simulation can be executed on the same transistor model with a lower supply voltage (or different VT flavor, temperature, or body biasing).

Due to the complexity and time-consuming task of running a SPICE simulation of the entire Ibex Core, only the critical path is simulated, as it is considered a representative sample. But also because this is the path that has the least slack and the one that requires the highest speeds. Using a replica of the critical path as a ring oscillator is a very common practice to regulate the speed and supply voltage of the main circuit [7], [22], [30].

The critical path is dumped into a SPICE netlist via the write\_spice\_deck command provided by Synopsys PrimePower. The netlist includes the cells in the path, resistors, ground capacitors, and coupling capacitors [27]. The circuit described by the netlist is converted into a ring oscillator by fixing the inputs that do not belong to the critical path either to VDD or VSS, such that the main input of the critical path can be observed at the output. Figure 3.5.1 illustrates this idea.

Using Python scripting (refer to Appendix .9), the exported SPICE netlist was modified to adhere to the Cadence Virtuoso simulator syntax. Additionally,

#### CHAPTER 3. METHODS

the initial and final sequential elements in the path were removed since only the combinational logic is of interest for building a ring oscillator. For each cell in the critical path there are individual voltage sources (VDD, VSS, VPW\_P, VNW\_N), they were removed, and respective pins were connected together and set as output ports of the critical path subcircuit. This reduces circuit complexity and allows values to be changed through a design variable in a testbench. A testbench circuit was created by instantiating the critical path subcircuit, a four-pole single-throw switch, all power supplies, and an ideal inverter (derived from a voltage-controlled voltage source).

After the critical path netlist has been parsed and cleaned it is converted into a SPICE subcircuit (SUBCKT), named *CRITICAL\_PATH*, which makes the ring oscillator circuit. A proper testbench is created, instantiating the subcircuit, the voltages sources and the 4-input switch. The testbench netlist is described in Listing 3.1.

#### Listing 3.1: SPICE testbench

```

.include netlist_critical_path.spi

vvdd vdd 0 vdd

.global vss

vvss vss 0 0

.temp 25

vvnw_n vnw_n 0 vnw_n

vvpw_p vpw_p 0 vpw_p

xtop_01 vdd vss vnw_n vpw_p A Z CRITICAL_PATH

* Input A is connected to a sp4tswitch. Inputs are VSS, VDD, Z or !Z

* Switch is controlled via sw_pos variable

einverter nZ vss vdd Z 1

simulator lang=spectre

S0 (A vss vdd Z nZ) sp4tswitch paramTyp=string tranPosition_str=sw_pos model=switch

simulator lang=spice

.end

```

The four-pole single-throw switch is connected in the following manner, shown also in Figure 3.5.1:

- Input 1 is connected to VDD.

- Input 2 is connected to VSS.

- Input 3 is connected to Z (output of ring oscillator).

- Input 4 is connected to !Z (inverted output of ring oscillator).

- Output 1 is connected to A (input of ring oscillator).

It can be decided which switch configuration to use at simulation time by means of a design variable. Configurations 1 and 2 will not make the circuit oscillate due to their static behavior, therefore this will yield the static power information. Either configuration 3 or 4 generates an oscillatory response on the circuit. If the ring oscillator has an odd number of inverter-like gates, then configuration 3 makes the circuit oscillate. In the case when the number o inverter-like gates is odd, an additional inverter is needed to make the circuit oscillate, in this case, configuration 4 is needed. The number of inverter-like gates in the netlist can be counted by studying the type of cells and their inputs-outputs paths, but it is very complex operations since there are near 1000 cells per library. Instead, it was decided that it is much easier to simulate for both possible conditions, and take the results of the oscillatory case.

#### 3.5.1 Analog simulation of RO

The testbench and critical path netlists from the previous section, and the transistor models are imported into *Cadence Virtuoso ICADVM20.1* from command line by using Spice In. It creates a schematic of the circuit that can later be simulated. The import command is [31]:

```

spiceIn -netlistFile netlist_testbench.spi -outputLib $TESTBENCH

→ -language SPICE -refLibList "cmos22fdsoi analogLib" -devMapFile

```

```

{\scriptstyle \hookrightarrow } \quad \text{devMapping.file}

```

Where *netlist\_testbench.spi* is the netlist described in Listing 3.1, which is instantiating the critical path by means of the .include directive. Output files are located in the directory pointed by \$TESTBENCH, and the devMapping file contains the device mapping information (such as resistor = res).

All SPICE simulations were performed using OCEAN scripts. The graphical user interface (GUI) was only used for the initial setup and understating how the tool works, everything was moved later to OCEAN scripting because of the amount of simulations and corners needed. This also allows greater automation during the exploration flow. See Appendix .8 for the script file.

The Open Command Environment for Analysis (OCEAN) is the scripting language used by Cadence Virtuoso Analog Design Environment to set up, simulate and analyze circuit data from command line without starting the GUI. Script files and simulations were design according to the recommended instructions [32], [33]. Initially, a basic simulation can be set up through the GUI and the configurations exported into an OCEAN file, that works as a baseline for designing more complex simulations.

The simulation time must be enough to accommodate a few cycles on the slowest corner. But because there is a huge difference in speed between the slowest and fastest corner, this time cannot be a fixed value, or it would be unfeasible to get results in a timely manner. For instance, ten cycles in the slowest corner could mean one million cycles in the fastest corner (five orders of magnitude greater) for a fixed stop time, creating huge amount of data with a big impact on computing resources. An optimization is therefore required.

The problem is that the frequency of oscillation is not know beforehand and

#### CHAPTER 3. METHODS

cannot be calculated until the simulation has finished and the simulation time cannot be defined until the oscillation frequency is known, in other words, a *chicken or egg* dilemma is faced. To circumvent this problem, a big enough fixed simulation time is used, and a counter written in Verilog-A (refer to Appendix .11) is instantiated so that the current analysis can be stopped dynamically once a given number of cycles have been obtained. The transient simulation will then continue with the following corner. The finish\_current\_analysis(0) command achieves the desire behavior.

Once the testbench, critical path, cell and transistor models are imported into Virtuoso, OCEAN scripts are used to simulate the circuit in all four possible switch cases: 1) connected to VDD, 2) connected to VSS, 3) connected to Z, 4) connected to !Z. All simulation parameters are described in the script, such as: supply voltage, temperature, transistor model, biasing voltages. The simulations can be started from the command line with the command:

#### virtuoso -nograph -restore script.ocn

The most important results are extracted using the script with the following directives:

• The frequency of oscillation is measured as the frequency of the voltage signal Z, after removing the first half of the simulation. This ensures that any transitory behavior is discarded.

frequency(clip(VT(\\"/Z\\") (lastVal(VT(\\"/Z\\")) / 2)  $\rightarrow$  lastVal(VT(\\"/Z\\"))))

• The power consumed by the circuit is equal to the average of the current signal through the VDD port, times the voltage value of VDD. First half of the simulation is also discarded  $(P = I_{DD} * V_{DD})$ .

average(clip((VAR(\\"vdd\\") \* IT(\\"/xtop\_01/VDD\\"))  $\rightarrow$  (lastVal(VT(\\"/Z\\")) / 2) lastVal(VT(\\"/Z\\"))))

• The duty cycle is given by the time it takes the voltage signal Z to cross half VDD on both edges.

dutyCycle(VT(\\"/Z\\") ?mode \\"user\\" ?threshold → (VAR(\\"vdd\\") / 2) ?xName \\"time\\" ?outputType → \\"average\\")

All data is dumped into CSV files automatically once the simulations are finished. Columns represent the simulated corner and rows contain the results of the previous expressions (frequency, power, duty cycle).

| Р  | V    | $T(^{\circ}C)$ | VNW_N(V) | VPW_P(V) |

|----|------|----------------|----------|----------|

| TT | 0.20 | 25             | 0.8      | -1.067   |

| TT | 0.21 | 25             | 0.8      | -1.067   |

| TT | 0.22 | 25             | 0.8      | -1.067   |

| TT | 0.23 | 25             | 0.8      | -1.067   |

| TT | 0.24 | 25             | 0.8      | -1.067   |

| TT | 0.25 | 25             | 0.8      | -1.067   |

| TT | 0.26 | 25             | 0.8      | -1.067   |

| TT | 0.27 | 25             | 0.8      | -1.067   |

| TT | 0.28 | 25             | 0.8      | -1.067   |

| TT | 0.29 | 25             | 0.8      | -1.067   |

| TT | 0.30 | 25             | 0.8      | -1.067   |

| TT | 0.31 | 25             | 0.8      | -1.067   |

| TT | 0.32 | 25             | 0.8      | -1.067   |

| TT | 0.33 | 25             | 0.8      | -1.067   |

| TT | 0.34 | 25             | 0.8      | -1.067   |

| TT | 0.35 | 25             | 0.8      | -1.067   |

| TT | 0.36 | 25             | 0.8      | -1.067   |

| TT | 0.38 | 25             | 0.8      | -1.067   |

| TT | 0.40 | 25             | 0.8      | -1.067   |

| TT | 0.50 | 25             | 0.542    | -0.632   |

| TT | 0.60 | 25             | 0.346    | -0.210   |

| TT | 0.80 | 25             | -0.024   | 0.020    |

Table 3.5.1:

Simulation corners for SLVT and LVT on typical conditions.

#### 3.5.1.1 Simulation corners

The following tables show all the parameters that were set for the analog simulations. PVT refers to Process (SS, TT, FF), Voltage (supply voltage) and Temperature. VNW\_N and VPW\_P refers to the biasing voltages, used for forward body-biasing (FBB). Reverse body-bias (RBB) is not studied in this thesis.

Table 3.5.1 contains the corners used to extract the MEP with SLVT and LVT libraries at typical conditions and fixed body biasing. For voltages 0.4, 0.5, 0.6 and 0.8 V, the biasing voltages used are the ones recommended by the foundry. Under 0.4 V the libraries are undefined, and it was decided to replicate the same values used for 0.4 V. In the case of HVT and UHVT libraries, FBB is not supported, so their biasing voltages are always zero, this is illustrated in Table 3.5.2. This is the first approximation on studying the MEP: only typical conditions and fixed body-biasing, so that supply voltage, threshold voltage and channel length are studied. In this way 22 corners are studied per VT and channel length, yielding a total of 330 corners.

The study is extended to different PVT conditions (slow and cold, slow and hot, fast and cold, fast and hot) with fixed body-bias. The corners for SLVT and LVT are shown in Table 3.5.3. Since HVT and UHVT do not support FBB, the corners are the same as Table 3.5.3 but with zero bias voltages. Now the exploration is expanded to 110 corners per VT and channel length, giving a total of 1650 corners studied.

| Р  | V    | $T(^{\circ}C)$ | $VNW_N(V)$ | $VPW_P(V)$ |

|----|------|----------------|------------|------------|

| TT | 0.20 | 25             | 0          | 0          |

| TT | 0.21 | 25             | 0          | 0          |

| TT | 0.22 | 25             | 0          | 0          |

| TT | 0.23 | 25             | 0          | 0          |

| TT | 0.24 | 25             | 0          | 0          |

| TT | 0.25 | 25             | 0          | 0          |

| TT | 0.26 | 25             | 0          | 0          |

| TT | 0.27 | 25             | 0          | 0          |

| TT | 0.28 | 25             | 0          | 0          |

| TT | 0.29 | 25             | 0          | 0          |

| TT | 0.30 | 25             | 0          | 0          |

| TT | 0.31 | 25             | 0          | 0          |

| TT | 0.32 | 25             | 0          | 0          |

| TT | 0.33 | 25             | 0          | 0          |

| TT | 0.34 | 25             | 0          | 0          |

| TT | 0.35 | 25             | 0          | 0          |

| TT | 0.36 | 25             | 0          | 0          |

| TT | 0.38 | 25             | 0          | 0          |

| TT | 0.40 | 25             | 0          | 0          |

| TT | 0.50 | 25             | 0          | 0          |

| TT | 0.60 | 25             | 0          | 0          |

| TT | 0.80 | 25             | 0          | 0          |

Table 3.5.2: Simulation corners for HVT and UHVT on typical conditions.

To further expand the study, different body-bias voltages are used, this is explained in section 3.7.

# 3.6 Estimating MEP from RO

Four CSV files are obtained from the simulation ran for the ring oscillator, described in the previous section, one for each switch case. They yield the following results: 1) static power on high input, 2) static power on low input, 3) total power and frequency, 4) total power and frequency (either 3. or 4. have valid data depending on the amount of inverters in the path).

The static power consumed by the ring oscillator is calculated as the average between the static power when input is high and when input is low. This is the best approach as it takes into consideration both equally possible cases. The dynamic power, due to switching state of transistors, can be computed as the subtraction between the total power and the average static power.

The energy per cycle is obtained by dividing the total power, dynamic power, and static power by the frequency of oscillation of the ring oscillator for each corner. By locating the lowest total energy consumption, the MEP is obtained for the RO. However, the focus of this study lies on finding the MEP of the original design, the Ibex core.

### CHAPTER 3. METHODS

| Р             | V              | T(°C)            | VNW N(V) | VPW P(V) | Р             | V            | T(°C)            | VNW N(V) | VPW_P(V) |

|---------------|----------------|------------------|----------|----------|---------------|--------------|------------------|----------|----------|

| SS            | 0.20           | -40              | 0.8      | -1.067   | SS            | 0.31         | -40              | 0.8      | -1.067   |

| SS            | 0.20           | 125              | 0.8      | -1.067   | SS            | 0.31         | 125              | 0.8      | -1.067   |

| TT            | 0.20           | 25               | 0.8      | -1.067   | TT            | 0.31         | 25               | 0.8      | -1.067   |

| FF            | 0.20           | -40              | 0.8      | -1.067   | FF            | 0.31         | -40              | 0.8      | -1.067   |

| FF            | 0.20           | 125              | 0.8      | -1.067   | FF            | 0.31         | 125              | 0.8      | -1.067   |

| SS            | 0.20           | -40              | 0.8      | -1.067   | SS            | 0.32         | -40              | 0.8      | -1.067   |

| SS            | 0.21           | 125              | 0.8      | -1.067   | SS            | 0.32         | 125              | 0.8      | -1.067   |

| TT            | 0.21<br>0.21   | 25               | 0.8      | -1.067   | TT            | 0.32         | 25               | 0.8      | -1.067   |

| FF            | 0.21<br>0.21   | -40              | 0.8      | -1.067   | FF            | 0.32         | -40              | 0.8      | -1.067   |

| FF            | 0.21<br>0.21   | 125              | 0.8      | -1.067   | FF            | 0.32         | 125              | 0.8      | -1.067   |

| SS            | 0.21<br>0.22   | -40              | 0.8      | -1.067   | SS            | 0.32<br>0.33 | -40              | 0.8      | -1.067   |

| SS            | 0.22<br>0.22   | 125              | 0.8      | -1.067   | SS            | 0.33         | 125              | 0.8      | -1.067   |

| TT            | $0.22 \\ 0.22$ | $\frac{125}{25}$ | 0.8      | -1.067   | TT            | 0.33         | $\frac{125}{25}$ | 0.8      | -1.067   |

| FF            | $0.22 \\ 0.22$ | -40              | 0.8      | -1.067   | FF            | 0.33         | -40              | 0.8      | -1.067   |

| FF            | $0.22 \\ 0.22$ | 125              | 0.8      |          | FF            | 0.33         | 125              |          |          |

|               |                |                  |          | -1.067   |               |              |                  | 0.8      | -1.067   |

| SS            | 0.23           | -40              | 0.8      | -1.067   | SS            | 0.34         | -40              | 0.8      | -1.067   |

| SS            | 0.23           | 125              | 0.8      | -1.067   | SS            | 0.34         | 125              | 0.8      | -1.067   |

| TT            | 0.23           | 25               | 0.8      | -1.067   | TT            | 0.34         | 25               | 0.8      | -1.067   |

| FF            | 0.23           | -40              | 0.8      | -1.067   | FF            | 0.34         | -40              | 0.8      | -1.067   |

| FF            | 0.23           | 125              | 0.8      | -1.067   | FF            | 0.34         | 125              | 0.8      | -1.067   |

| SS            | 0.24           | -40              | 0.8      | -1.067   | SS            | 0.35         | -40              | 0.8      | -1.067   |

| SS            | 0.24           | 125              | 0.8      | -1.067   | SS            | 0.35         | 125              | 0.8      | -1.067   |

| TT            | 0.24           | 25               | 0.8      | -1.067   | TT            | 0.35         | 25               | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.24           | -40              | 0.8      | -1.067   | FF            | 0.35         | -40              | 0.8      | -1.067   |

| FF            | 0.24           | 125              | 0.8      | -1.067   | FF            | 0.35         | 125              | 0.8      | -1.067   |

| SS            | 0.25           | -40              | 0.8      | -1.067   | SS            | 0.36         | -40              | 0.8      | -1.067   |

| SS            | 0.25           | 125              | 0.8      | -1.067   | SS            | 0.36         | 125              | 0.8      | -1.067   |

| TT            | 0.25           | 25               | 0.8      | -1.067   | TT            | 0.36         | 25               | 0.8      | -1.067   |

| FF            | 0.25           | -40              | 0.8      | -1.067   | FF            | 0.36         | -40              | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.25           | 125              | 0.8      | -1.067   | FF            | 0.36         | 125              | 0.8      | -1.067   |

| $\mathbf{SS}$ | 0.26           | -40              | 0.8      | -1.067   | SS            | 0.38         | -40              | 0.8      | -1.067   |

| $\mathbf{SS}$ | 0.26           | 125              | 0.8      | -1.067   | SS            | 0.38         | 125              | 0.8      | -1.067   |

| TT            | 0.26           | 25               | 0.8      | -1.067   | TT            | 0.38         | 25               | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.26           | -40              | 0.8      | -1.067   | FF            | 0.38         | -40              | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.26           | 125              | 0.8      | -1.067   | FF            | 0.38         | 125              | 0.8      | -1.067   |

| SS            | 0.27           | -40              | 0.8      | -1.067   | SS            | 0.40         | -40              | 0.8      | -1.067   |

| SS            | 0.27           | 125              | 0.8      | -1.067   | SS            | 0.40         | 125              | 0.8      | -1.067   |

| TT            | 0.27           | 25               | 0.8      | -1.067   | TT            | 0.40         | 25               | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.27           | -40              | 0.8      | -1.067   | FF            | 0.40         | -40              | 0.8      | -1.067   |

| $\mathbf{FF}$ | 0.27           | 125              | 0.8      | -1.067   | FF            | 0.40         | 125              | 0.8      | -1.067   |

| $\mathbf{SS}$ | 0.28           | -40              | 0.8      | -1.067   | SS            | 0.50         | -40              | 0.542    | -0.632   |

| SS            | 0.28           | 125              | 0.8      | -1.067   | SS            | 0.50         | 125              | 0.542    | -0.632   |

| TT            | 0.28           | 25               | 0.8      | -1.067   | TT            | 0.50         | 25               | 0.542    | -0.632   |

| $\mathbf{FF}$ | 0.28           | -40              | 0.8      | -1.067   | FF            | 0.50         | -40              | 0.542    | -0.632   |

| $\mathbf{FF}$ | 0.28           | 125              | 0.8      | -1.067   | FF            | 0.50         | 125              | 0.542    | -0.632   |

| SS            | 0.29           | -40              | 0.8      | -1.067   | SS            | 0.60         | -40              | 0.346    | -0.210   |

| SS            | 0.29           | 125              | 0.8      | -1.067   | SS            | 0.60         | 125              | 0.346    | -0.210   |

| TT            | 0.29           | 25               | 0.8      | -1.067   | TT            | 0.60         | 25               | 0.346    | -0.210   |

| $\mathbf{FF}$ | 0.29           | -40              | 0.8      | -1.067   | $\mathbf{FF}$ | 0.60         | -40              | 0.346    | -0.210   |

| $\mathbf{FF}$ | 0.29           | 125              | 0.8      | -1.067   | $\mathbf{FF}$ | 0.60         | 125              | 0.346    | -0.210   |

| SS            | 0.30           | -40              | 0.8      | -1.067   | SS            | 0.80         | -40              | -0.024   | 0.020    |

| $\mathbf{SS}$ | 0.30           | 125              | 0.8      | -1.067   | SS            | 0.80         | 125              | -0.024   | 0.020    |

| TT            | 0.30           | 25               | 0.8      | -1.067   | TT            | 0.80         | 25               | -0.024   | 0.020    |

| $\mathbf{FF}$ | 0.30           | -40              | 0.8      | -1.067   | FF            | 0.80         | -40              | -0.024   | 0.020    |

| $\mathbf{FF}$ | 0.30           | 125              | 0.8      | -1.067   | FF            | 0.80         | 125              | -0.024   | 0.020    |

|               |                |                  | 0.0      |          |               |              |                  | 5.021    | 0.0-0    |

**Table 3.5.3:** Simulation corners for SLVT and LVT on SS, TT and FF conditions.

By utilizing the power report generated by PrimePower for the TT corner, the energy per cycle of the Ibex core can be calculated by multiplying it by the clock period. Subsequently, the ratio of leakage energy between the ibex core and the ring oscillator can be determined at the typical corner (TT, 25°C, 0.4 V for SLVT and LVT, 0.8 V for HVT and UHVT). Since the critical path (RO) is only a subcircuit of the entire design, this ratio is expressing how much bigger is the core compared to the critical path. Although the ratio is only calculated at a single corner point, it will be considered a fixed value since it is expected that the ibex core scales in the same magnitude as the ring oscillator. Therefore this ratio is used for extrapolating the leakage energy at all corners.

In that sense, the static energy of the core at a given supply voltage equals that of the critical path times the leakage ratio:

$$E_{static}(V_{DD}) = E_{staticCP}(V_{DD}) * Ratio$$

The switching energy at any supply voltage is computed mathematically considering it has a square relationship with VDD, using as a baseline the energy obtained from the PrimePower report. In this case a ratio between the ibex core and ring oscillator is not used, because the RO has a 100% toggle rate, which is not true for the original circuit.

For SLVT and LVT:

$$E_{dynamic}(V_{DD}) = \frac{E_{dynamic(0.4V)}}{(0.4V)^2} * V_{DD}^2$$

For HVT and UHVT:

$$E_{dynamic}(V_{DD}) = \frac{E_{dynamic(0.8V)}}{(0.8V)^2} * V_{DD}^2$$

Finally, the total energy represents the contribution of the previous two components.

$$E_{total}(V_{DD}) = E_{dynamic}(V_{DD}) + E_{static}(V_{DD})$$

The Minimum Energy Point is located at the global minimum of the  $E_{total}$  signal as the supply voltage scales down.

#### 3.6.1 Excluding worst performing cells

Standard libraries contain hundreds of cells, somewhere between 400 and 1000 cells in the libraries used on this study. Typically, synthesis tools pick the best cells for a given design such that it meets the deadlines and constraints, and is still power-efficient. Nonetheless, this is only optimized at the corner where the

| Combination | Timing Typical Case | Timing Worst Case | Ratio | Worst ratio |

|-------------|---------------------|-------------------|-------|-------------|

| A->Z        | 1                   | 3                 | 3     | 3           |

| B->Z        | 1                   | 2                 | 2     | -           |

| C-> $Z$     | 1                   | 2                 | 2     | -           |

Table 3.6.1: Timing ratio between typical and worst case for a NAND3 example.

library is characterized, for instance, typical case, 0.4 V, 25°C. It is possible that cells do not scale equally as the supply voltage is lowered and closest to the MEP. It means that there are good performing cell at typical corner, that behave poorly at low voltages. Being able to exclude these cells opens another degree of freedom in the MEP exploration domain.

In order to tell which cells can be excluded, a ranking of all available cells is needed. This is obtained by looking at the timing information on the library file in the typical-case, 0.4 V at  $25^{\circ}$ C (0.8 V at  $25^{\circ}$ C for HVT and UHVT), and the same information on the library file in the worst-case, 0.36 V at  $-40^{\circ}$ C (0.72 V at  $-40^{\circ}$ C for HVT and UHVT). The ratio between both measurements represents the scaling factor. The cells with the biggest scaling factor are those that scale poorly from the typical to worst-case condition.

A python script is used for such task (refer to Appendix .10). It goes through the entire library file and extracts the average between rise and fall time for all input-output combinations for every cell, on both typical and worst case conditions. Then, for every cell and every matching pair of input-output combinations, the ratio is calculated, but only the worst is taken.

For instance, table 3.6.1 illustrates this with a NAND3 example. The average timing from A to Z at typical conditions is 1, and for the worst condition is 3, so that the ratio between worst and typical is also 3. Therefore the A to Z combination has the worst ratio of the three possible cases, this value is taken to build a weighted ranking. For the ranking, the cells are evaluated against all other cells, and not against cells with similar logic function. For instance, a NAND3 is not compared against a NAND2 and NAND3 with different driving strength to choose the best, but compared globally with all other cells. Excluding only high fan-in cells was not studied here.

Once a ranking is obtained in a CSV format, a TCL script can be generated containing cell that are meant to be excluded from the synthesis. For this purpose, Synopsys provides the command set\_dont\_use. It means that the tools will not used any of the cells listed. The command can be used in the following way:

```

set sdc_version 2.1

set_dont_use [get_lib_cells */NAND3X010]

set_dont_use [get_lib_cells */NOR3X010]

```

To avoid running into synthesis errors due to lack of compatible library cells,

not able to find replacements for registers, all D-Flip-Flops are in a "do not touch" list. Meaning that these type of cells are always allowed to be used by the tool.

#### 3.6.2 Scaling the leakage power

It results of interest to study how the MEP shifts as the leakage power of a given circuit changes but the switching power remains the same. For instance, if peripherals are added or removed, the leakage power will undoubtedly change as long as they are a powered-up, but the switching power will remain the same if they are not in used. Since this is a very real case, it becomes important to understand where the MEP lies and how to optimise for it.

The flow is exactly the same as described in previous sections. Since the switching activity remains unchanged, there is no need to rerun the entire process. However, the leakage power obtained from section 3.5.1 can be scaled by any factor. For this thesis, it was studied at 0.5 and 2 times the leakage.

# 3.7 Estimating MEP body-biasing corners

Different MEP can be obtained for different biasing-body pair values (VNW\_N and VPW\_P), as body-biasing techniques allow to dynamically change the transistor's VT, making them faster or slower, and with greater or less leakage. SLVT and LVT technologies allow only Forward Body-Biasing (FBB), in the following rage, VNW\_N: 0 to 2 V, VPW\_P: -2 to 0 V. That is, applying a positive voltage to the NMOS transistors, and a negative voltage on PMOS transistors. UHVT and HVT support only RBB, but it is not explored in this thesis.

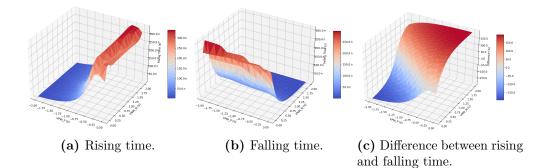

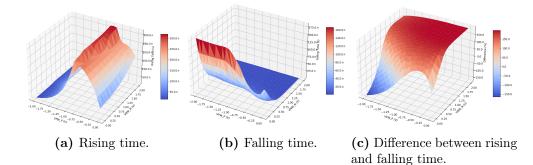

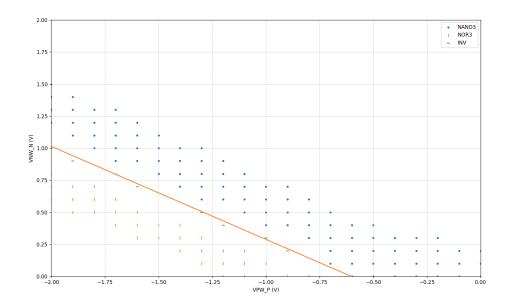

There are infinite values in the range described before, and only a subset of them are considered valid. To limit the scope, the valid range of biasing points that can be applied to the circuit are those that give a near-symmetric response in rising and falling times of the basic gates NAND3, NOR3 and INV at the slow corner. The threshold for deciding whether the points are allowed or not is extracted from the liberty file.