# Sindre Jacobsen Faeroe

# Fine-grained Multithreading for Deterministic Concurrency in Safety-Critical Systems

Master thesis for the degree Master of Science in Embedded Systems

Trondheim, June 2022

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

### $\mathbf{NTNU}$

Norwegian University of Science and Technology

Master thesis for the degree of Master of Science in Embedded Systems

Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

© 2022 Sindre Jacobsen Faeroe

## Abstract

Integrating multiple tasks of differing criticality levels onto a single hardware platform, known as a mixed-criticality system, has become a growing research topic in real-time embedded systems. The correctness of these systems depends not only on the software's functionality but also on the timing behavior. Therefore, the underlying hardware platform must provide both spatial and temporal isolation guarantees and predictability to have high confidence in the timing behavior of the software. Unfortunately, even though existing hardware consisting of multiple single-core, multi-core, or multithreaded processors supports hardware-based isolation, they do not manage to exploit the hardware resources available on the platform entirely. Under-utilizing hardware resources can, as a result, cause a decrease in the overall throughput for a set of tasks.

This report presents a microarchitecture intended for mixed-criticality systems that allow exchanging hardware-based isolation between tasks to increase hardware resource utilization and vice versa. The microarchitecture has been designed and simulated in Simulink, a model-based design tool that enables fast feedback on design requirements and decisions. The design incorporates cycle-by-cycle hardware thread interleaving, also known as fine-grained multithreading, to increase the resource utilization of the platform. Additionally, a configurable hardware thread scheduler and timing instructions have been added to the microarchitecture to enable the programmer to make compromises between hardware-based isolation, predictable timing behavior, and overall instruction throughput.

# Preface

The work presented in this thesis was carried out in the Department of Electronic Systems, Faculty of Information Technology and Electrical Engineering at the Norwegian University of Science and Technology (NTNU). The Master Thesis was supervised by Professor Per Gunnar Kjeldsberg (NTNU) and former co-worker at UBIQ Aerospace, Shibarchi Majumder, Ph.D. (Nordic Semiconductor). I am thankful for their well-informed insight while working on the project. In addition, they provided me with exceptional guidance and motivation throughout this process.

I am grateful to my friends and co-workers for their vast support. They have given me inspiration and exceptional advice through their work and study experiences.

Finally, I would also like to thank my family, my father, mother, and brother, for encouraging me to pursue a Master's degree. I am also grateful for my lovely girlfriend's support during the course of the year. Her limitless patience through long evenings of work and the affection that she offers me have kept me motivated during my Master's Thesis at NTNU.

# Contents

| A             | bstra            | ct                                         | v    |

|---------------|------------------|--------------------------------------------|------|

| Pı            | refac            |                                            | vii  |

| $\mathbf{Li}$ | $\mathbf{st}$ of | abbreviations                              | xvii |

| 1             | Intr             | oduction                                   | 1    |

|               | 1.1              | Introduction and motivation                | 1    |

|               | 1.2              | Objectives                                 |      |

|               | 1.3              | Contributions                              |      |

|               | 1.4              | Thesis Structure                           | 4    |

| 2             | Bac              | kground and Related Work                   | 5    |

|               | 2.1              | Mixed-Criticality Systems                  | 5    |

|               | 2.2              | Timing Instructions                        | 7    |

|               | 2.3              | Hardware Multithreading Techniques         | 9    |

|               | 2.4              | Model-Based Engineering                    | 11   |

|               | 2.5              | RISC-V                                     | 13   |

|               |                  | 2.5.1 RV32I Base Integer Instruction Set   | 13   |

|               |                  | 2.5.2 Control and Status Registers         | 14   |

|               |                  | 2.5.3 Machine-level Timer Registers        | 15   |

|               | 2.6              | Previous Work                              | 16   |

|               |                  | 2.6.1 Single-operation RISC-V Architecture | 16   |

|               |                  | 2.6.2 FlexPRET                             | 16   |

| 3             | The              | Microarchitecture Design                   | 19   |

|               | 3.1              | Architecture                               | 19   |

|               |                  | 3.1.1 5-Stage RISC-V Pipeline              | 19   |

|               |                  | 3.1.2 Control Unit                         | 23   |

|               |                  | 3.1.3 Memory Unit                          | 29   |

|               | 3.2              | Hardware Thread Scheduler                  | 31   |

|               |                  | 3.2.1 Hardware Thread Scheduling CSRs      | 32   |

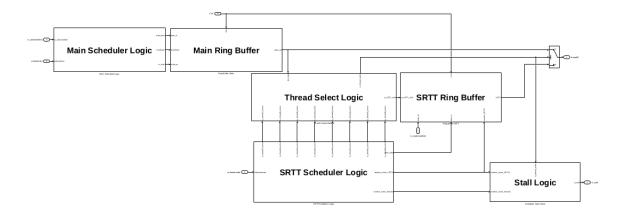

|               |                  | 3.2.2 Main Scheduler                       | 32   |

|               |                  | 3.2.3 SRTT Scheduler                       | 35   |

|               |                  | 3.2.4 Thread Select Logic                  | 38   |

|               |                  | 3.2.5 Stall Unit                           | 39   |

|               |                  | 3.2.6 Hardware Thread Scheduler Example    |      |

|               | 3.3              | Timer Unit                                 |      |

|               |                  | 3.3.1 Timing Instruction Set               |      |

|               |                  | 3.3.2 Memory Mapped Timer Registers        | 43   |

|               | 3.4              | Assembler for the Microarchitecture        | 46   |

| x | C | 0. | N' | II | IN | VТ | $^{\circ}S$ | , |

|---|---|----|----|----|----|----|-------------|---|

|   |   |    |    |    |    |    |             |   |

| 4        | System Analysis                   | 49         |

|----------|-----------------------------------|------------|

|          | 4.1 System Configurations         | 49         |

|          | 4.1.1 System Execution Time       | 49         |

|          | 4.1.2 System Response             | 56         |

|          | 4.2 Coarse-grained Multithreading | 62         |

|          | Conclusion and Future Work        | 65         |

| <b>A</b> | Code                              | 69         |

| A        | A.1 Python code                   | <b>6</b> 9 |

|          | A.2 Assembly code                 | 77         |

|          | A.2 Assembly code                 | 11         |

| Bi       | ibliography                       | 81         |

# List of Tables

| 4.1 | The slots configuration for the single-threaded system                          | 50 |

|-----|---------------------------------------------------------------------------------|----|

|     | The mode configuration for the single-threaded system                           |    |

|     | Real-time constraints of the tasks                                              |    |

| 4.4 | The slots configuration for the multi-threaded system using only soft real-time |    |

|     | threads (SRTT)                                                                  | 52 |

| 4.5 | The mode configuration for the multi-threaded system using only soft real-time  |    |

|     | threads (SRTT)                                                                  | 53 |

| 4.6 | The mode configuration for the multi-threaded system using only hard real-      |    |

|     | time threads (HRTT)                                                             | 54 |

# List of Figures

| 2.1  | Mixed Criticality Systems Application Integration         |

|------|-----------------------------------------------------------|

| 2.2  | DO-178C Design Assurance Levels                           |

| 2.3  | Coarse-grained Multithreading                             |

| 2.4  | Fine-grained Multithreading                               |

| 2.5  | RV32I instruction type formats                            |

| 2.6  | I-type operation instruction formats                      |

| 2.7  | RV32I 5-stage pipeline                                    |

| 2.8  | Slot CSR                                                  |

| 2.9  | Mode CSR                                                  |

| 3.1  | High-Level Model of Microarchitecture                     |

| 3.2  | Control Unit Simulink Design                              |

| 3.3  | CSR Models                                                |

| 3.4  | Branch Data Hazards in Schedule                           |

| 3.5  | Timer Compare First Solution                              |

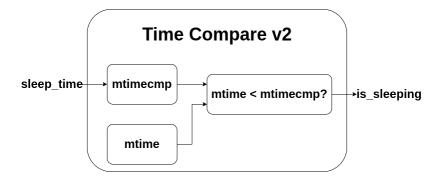

| 3.6  | Timer Compare Second Solution                             |

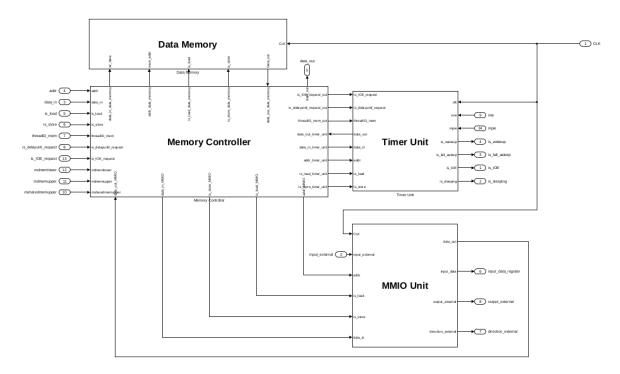

| 3.7  | Memory Unit Simulink Design                               |

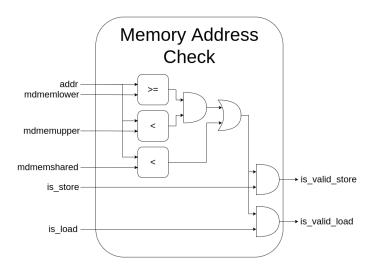

| 3.8  | Memory Address Check                                      |

| 3.9  | Hardware Thread Scheduler Simulink Design                 |

|      | Thread Scheduler Configuration Example                    |

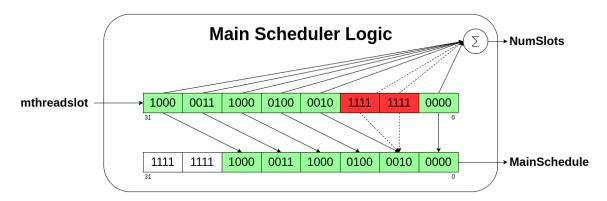

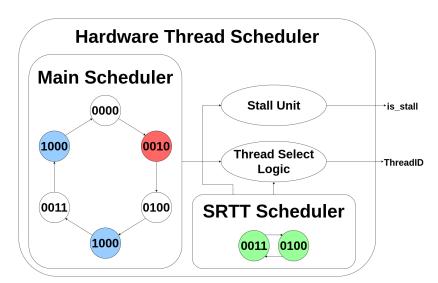

|      | Main Scheduler Logic Example                              |

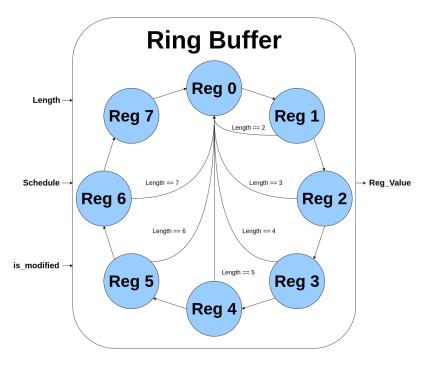

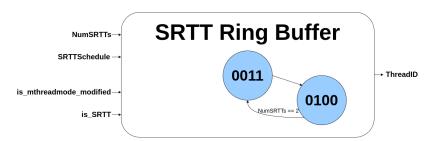

| 3.12 | Simple Ring Buffer Model                                  |

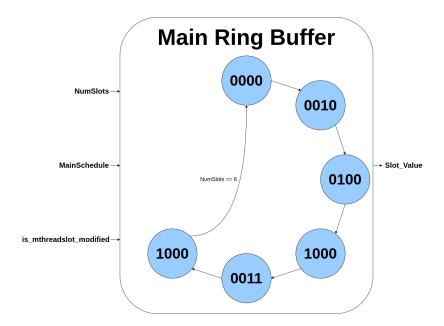

| 3.13 | Main Ring Buffer Example                                  |

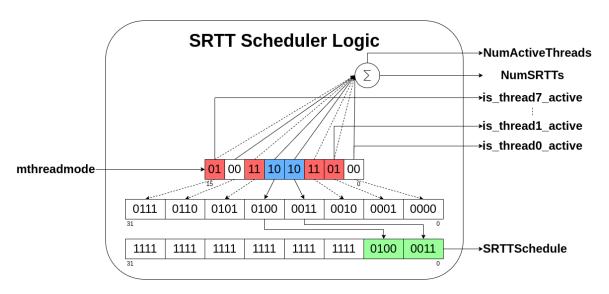

| 3.14 | SRTT Scheduler Logic Example                              |

|      | SRTT Ring Buffer Example                                  |

| 3.16 | Thread Select Logic                                       |

|      | Stall Unit                                                |

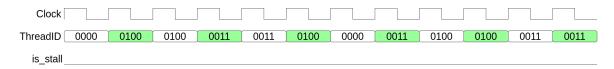

|      | Hardware Thread Scheduler Example                         |

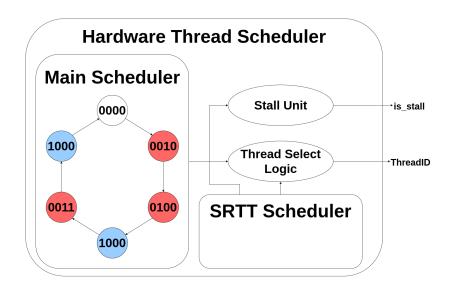

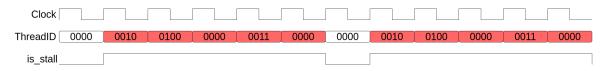

|      | Timing Diagram of Hardware Thread Scheduler               |

|      | Hardware Thread Scheduler Example with Stall              |

|      | Timing Diagram of Hardware Thread Scheduler with Stall 41 |

|      | Timing Instruction Set                                    |

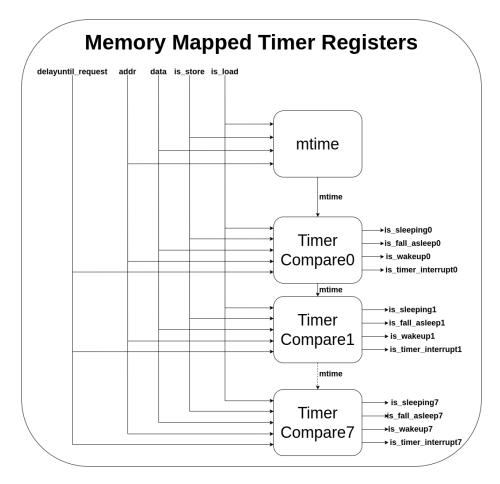

|      | Memory Mapped Timer Registers                             |

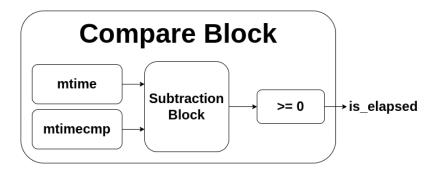

|      | Compare Block                                             |

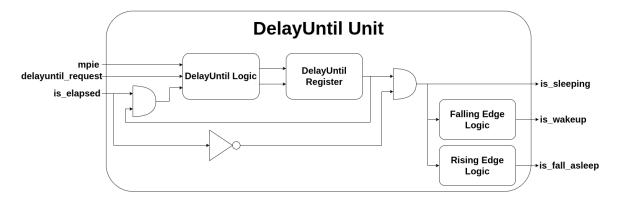

| 3.25 | Delay Until Unit                                          |

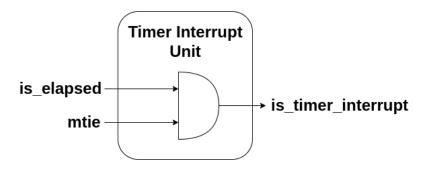

| 3.26 | Timer Interrupt Unit                                      |

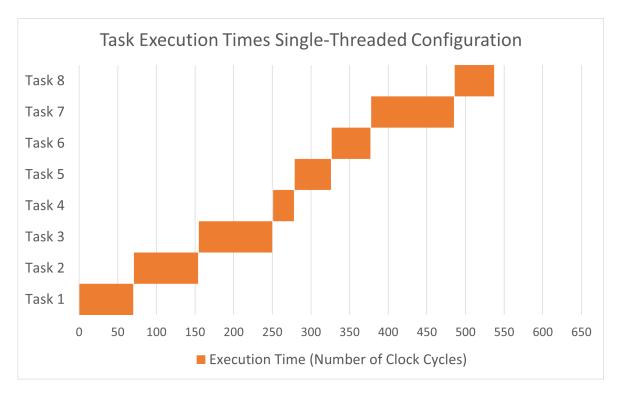

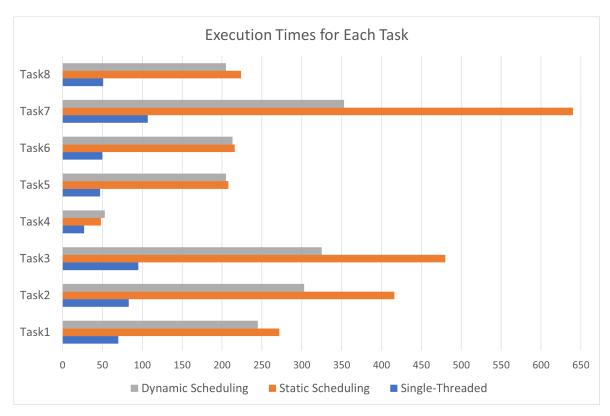

| 4.1  | Execution times for single threaded configuration         |

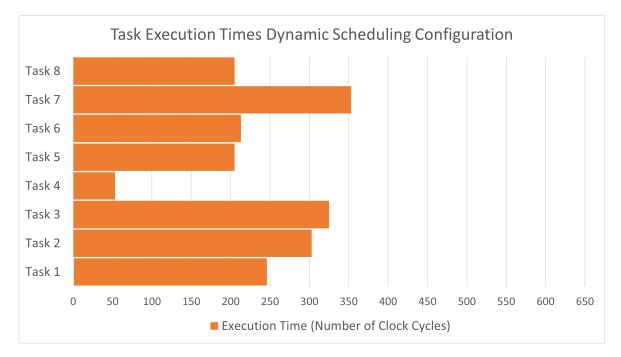

| 4.2  | Execution times for multi-threaded SRTT configuration     |

xiv LIST OF FIGURES

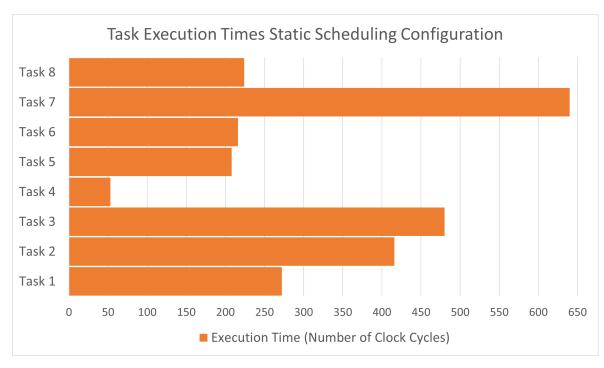

| 4.3  | Execution times for multi-threaded HRTT configuration        |

|------|--------------------------------------------------------------|

| 4.4  | Execution times for multiple tasks                           |

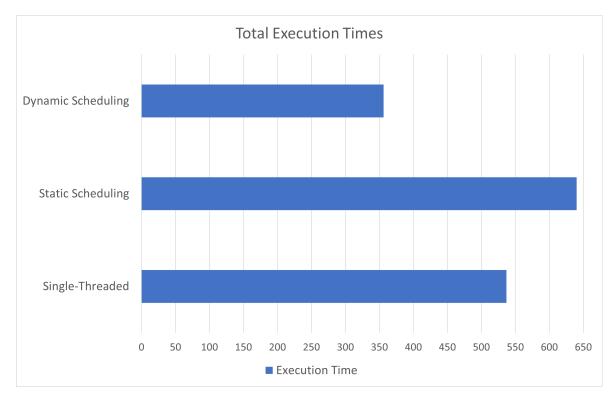

| 4.5  | Total execution times                                        |

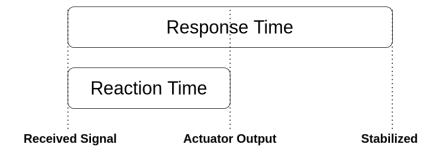

| 4.6  | Model of Response and Reaction Times                         |

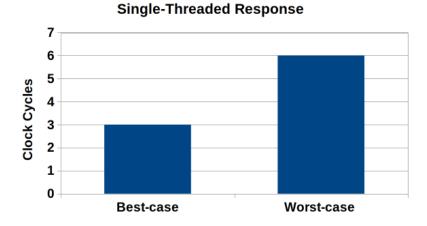

| 4.7  | Response Time Analysis SingleThreaded                        |

| 4.8  | Response Time Assembly Instructions                          |

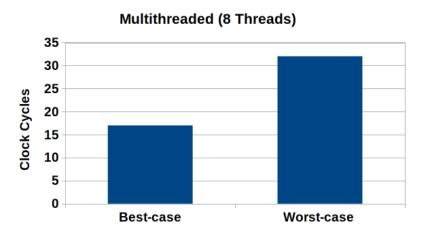

| 4.9  | Response Time Analysis Multithreaded 8 threads 6             |

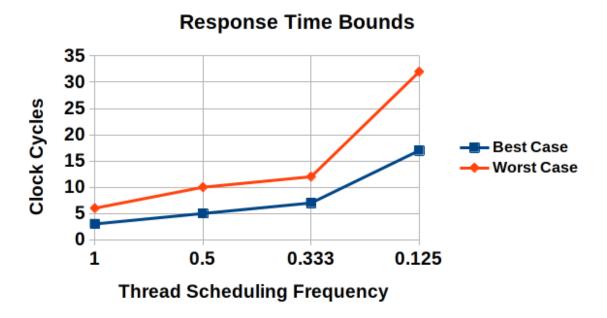

| 4.10 | Response time as a function of thread scheduling frequency 6 |

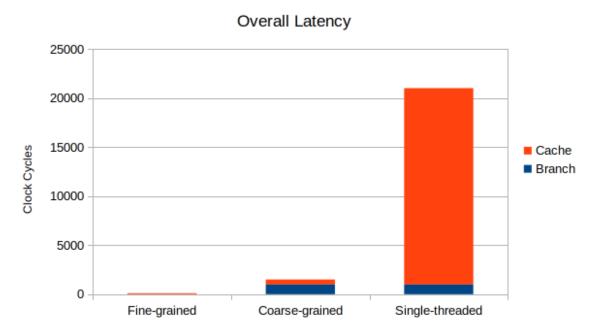

| 4.11 | Overall Latency                                              |

# Source code

| 2.1 | timingcontrol.a             | 8  |

|-----|-----------------------------|----|

| 2.2 | timingcontrolcase2.a        | 8  |

| 3.1 | branchthread.a              | 22 |

| 3.2 | timinginstructions.a        | 43 |

| 3.3 | assemblerbefore.a           | 47 |

| 3.4 | assemblerafter.a            | 47 |

| 4.1 | singlethreadedconfig.a      | 50 |

| 4.2 | fibonacci.a                 | 51 |

| 4.3 | srttconfig.a                | 52 |

| 4.4 | srttmain.a                  | 53 |

| 4.5 | hrttconfig.a                | 55 |

| 4.6 | responsetimetask.a          | 58 |

| A.1 | RiscvAssembler.py           | 69 |

| A.2 | DataHazardsSingleThreaded.a | 77 |

| A.3 | DataHazardsMultiThreaded.a  | 78 |

# List of abbreviations

CSR Control and Status Register

**DAL** Design Assurance Level

FPGA Field-Programmable Gate Array

**GPS** Global Positioning System

**HDL** Hardware Description Language

**HRTT** Hard Real-Time Thread

I/O Input/Output

IPC Inter-Process Communication

ISA Instruction Set Architecture

LSB Least Significant Bit

MBD Model-Based Design

MBE Model-Based Engineering

MCS Mixed-Criticality System

MMIO Memory Mapped Input/Output

MSB Most Significant Bit

PC Program Counter

PLL Phase-Locked Loop

PMP Physical Memory Protection

$\mathbf{RF}$  Register File

RTC Real-Time Clock

RTL Register-Transfer Level

RTOS Real Time Operating System

**SRTT** Soft Real-Time Thread

VGA Video Graphics Array

${f VHDL}$  Very high-speed integrated circuit Hardware Description Language

**WCET** Worst-Case Execution Time

# Chapter 1

## Introduction

## 1.1 Introduction and motivation

A real-time system is a computer system that must react to events in the given environment within a predetermined period, called a deadline [1, 2]. Consequently, the system's behavioral correctness depends not only on a calculation's logical correctness but also on the moment in which the system produced these results [3, 4]. In contrast to a general-purpose system, where the objective is to have fast computation to minimize the average response time of a given set of tasks, the goal of a real-time system is to meet the timing requirement of each task. The significance of an average-case execution time is minor for the real-time system behavior if several tasks are executed with different timing constraints. For example, consider the following quote made by Howard Marks:

Never forget the 6-foot-tall man who drowned crossing the stream that was 5 feet deep on average.

As the quote implies, even though the average depth was less than the height of the man, it could still be deeper in various places. Similarly, although the average-case performance of the system is less than the timing constraints placed on the system, a specific task execution may still be too slow to meet its timing constraint. Hence, a real-time system should have a predictable timing behavior rather than having a fast average-case performance.

In a real-time embedded system, a software task is assigned a criticality level based on how important it is to finish the task within a specified deadline. The tasks required to meet their respective deadlines to avoid catastrophic consequences are hard real-time tasks. On the other hand, a task is referred to as a soft real-time task if the system will still function correctly even though the deadlines are occasionally missed [5]. For example, an autonomous drone contains several real-time tasks that must keep up with external changes affecting the drone [6]. The obstacle avoidance and the global positioning system (GPS) tasks are among these tasks. If the obstacle avoidance task cannot react quickly enough to external changes, it can result in the drone crashing into an object, potentially destroying the drone and objects, and can lead to injury. Meanwhile, a late transmission from the GPS task reduces the reliability of the GPS location of the drone, meaning that the received location lags behind the actual location of the drone. Thus, the obstacle avoidance task must have a high criticality level as the task must finish within a given deadline. On the other hand, the GPS task can have a lower criticality level as missing a deadline is tolerable.

Real-time systems traditionally located multiple tasks with different criticality levels on separate hardware platforms to prevent unwelcome interference between tasks [7]. However,

having respective hardware platforms results in excessive resource consumption. For example, a drone with multiple tasks of different criticality levels would require numerous hardware platforms. As a result, the drone would be costly and energy inefficient due to the extra components needed to isolate the tasks. The drone would additionally be large and heavy due to the number of components required and the increased battery size due to the energy usage. Therefore, a solution integrates multiple components of more than one distinct criticality level onto a shared hardware platform. This integration method is an increasingly popular approach to designing real-time embedded systems, known as a mixed-criticality system [8].

With the integration of multiple criticality levels onto the same hardware platform, two interference issues arise; spatial and temporal interference. Temporal interference is the ability of a group of tasks on the same hardware platform to interfere with each other's time constraints [9]. This type of interference can cause a highly critical task to miss its deadline due to a lower criticality task obstructing the predicted timing schedule of the highly critical task. Spatial interference is the ability of a group of tasks on the same hardware platform to alter each other's code or private data [10]. Spatial interference can cause a highly critical task to have corrupted data due to the lower criticality task modifying the private data of the highly critical task, resulting in either incorrect or delayed task execution.

For a mixed-criticality system to be certifiable, there is a need for each task of varying criticality levels to meet their timing constraints to different levels of assurance. For example, the RTCA DO-178C avionics standard categorizes the criticality levels into five levels of assurance, ranging from A to E [11]. The worst-case execution time (WCET) used for analysis and certification is usually a conservative upper bound that exceeds the actual WCET of the system [12, 13]. Having tight bounds on the WCETs of the tasks is thus desirable, where it is preferable to have the WCET values as close as possible to the actual WCET. Furthermore, by maintaining sound spatial and temporal isolation, each independent task can avoid being negatively influenced by other tasks, resulting in predictable task execution. This predictable execution due to sound task isolation further leads to tight bounds on the WCET [14].

Because of the inefficient hardware resource utilization of hardware-based isolation using one processor per task, substantial research on software scheduling of mixed-criticality systems has been carried out over the past two decades [15, 16, 17]. In particular, research into real-time operating systems (RTOS) provided a method to enable software-based isolation while drastically reducing hardware costs. However, the RTOS must be certified, where overheads such as task switch latency, preemption time, and inter-process communication (IPC) must be considered [18, 19]. This overhead results in timing requirements in milliseconds, which is not precise enough for some applications. For example, applications that use software to replace functionality implemented initially in hardware or that interact with various hardware devices demand precision-timed input/output (I/O) with timing accuracy and precision on the order of nanoseconds which is at clock cycle granularity for processors [20].

## 1.2 Objectives

Instead of having a hardware platform for each application, it is possible to implement a processor where each task is deployed on separate computational components, such as cores in a multicore processor or hardware threads in a multithreaded processor. However, allocating a core to each task can result in the hardware resources being vastly underutilized because a less computationally heavy task can occupy an entire core. Meanwhile, a multithreaded processor allows multiple hardware threads to share a pipeline, resulting in fewer hardware resources for each computational component. Thus, having each task allocated a hardware thread enables better hardware resource utilization when multiple tasks are executing on the same

processor. However, many multithreaded processors do not have hardware thread scheduling mechanisms that manage to preserve hardware-based temporal isolation between tasks. Thus, a thread scheduling mechanism that manages to keep the hardware-based temporal isolation while utilizing the hardware resources better must be explored.

A typical processor can contain several components leading to a context-dependent execution time, such as memory, caches, pipelines, and branch prediction. This context-dependency leads to the execution time of individual instructions and memory accesses depending on the execution history [21]. For example, dynamic branch prediction allows the program to have insight into the execution history to avoid flushing pipeline stages when a branch is taken. However, there are instances where the information received from the execution history is not enough to make an assumption based on branch outcomes. Because the branch prediction is dynamic, it is challenging to foresee until the program run-time how the execution of instructions will behave exactly. The outcomes of the dynamic branch predictions may mainly vary when external influences coming from sensors are presented to the system, resulting in less predictable instruction latencies. Because the instruction's execution time depends mainly on the execution history, the processor lacks fine-grained predictability. As a result, the architectural features such as complex branch prediction and multilevel cache used to optimize the average-case performance reduce the coarse-grained predictability of the processor and make the WCET analysis cumbersome [14].

Fine-grained multithreading is a technique used in recent processor designs where instructions from different hardware threads are interleaved every clock cycle in the pipeline. This technique can enable hardware-based temporal and spatial isolation between tasks by allowing each task running on a hardware thread to use the pipeline for one clock cycle periodically. As a result, several tasks can run on the same mixed-criticality system without interfering with each other's timing constraints. Furthermore, the performance penalty caused by removing dynamic branch prediction and caches can be significantly reduced because of the concurrent execution of tasks provided by fine-grained multithreading. By removing the dependency on execution history, the fine-grained predictability of the processor can be maintained, and the WCET analysis becomes less demanding. However, even though fine-grained multithreading enables hardware-based isolation and predictable timing behavior, it cannot fully utilize the processor unless all threads are constantly running.

## 1.3 Contributions

This report presents a fine-grained multithreaded microarchitecture designed in Simulink that provides a means for each hardware thread to select between predictability and hardware-based isolation or increased instruction throughput. A hardware thread focusing on predictability will simplify the verification and certification of the safety-critical tasks. Additionally, the hardware-based isolation of the hardware thread allows the task to meet its timing constraints accurately. In comparison, having the hardware thread focusing on increased instruction throughput allows the less critical tasks to maintain good hardware resource utilization.

The designed microarchitecture contains a hardware thread scheduler and timing instructions inspired by the theory provided by the FlexPRET research paper [14]. Like the research paper, the microarchitecture contains a hardware-thread scheduler that uses two active round-robin schedulers to decide the hardware thread schedule. However, the microarchitecture utilizes a unique design to implement configurable round-robin schedulers of variable sizes. These configurable schedulers use CSRs to configure the hardware schedule, allowing the software to adjust the content and length of the thread schedule. The designed

microarchitecture also introduces a unique implementation of the four timing instructions presented by FlexPRET. The timer unit presented in this microarchitecture incorporates memory-mapped timer registers that expand on the mtime and mtimecmp registers described in the RISC-V documentation. Here, in addition to providing the original real-time timer interrupt functionality, the timer instructions give direct control over the thread schedule with fine-granularity resolution. Thus, the timer instructions allow the timing behavior of a task with hard real-time execution requirements to be specified in software while reallocating spare hardware resources to tasks with soft real-time execution requirements.

By designing the microarchitecture in Simulink, it was possible to continuously test and verify the design decisions made from start to finish. This design process made it possible to spot bugs early in the design process, thus drastically reducing the number of mistakes made. Additionally, the understanding received from previous research theory was used to inspire some of the design requirements during the design process. By using Simulink to test and verify the design, these design requirements could be adjusted or discarded based on the understanding and results provided by the simulations. As a result, a custom microarchitecture molded by inspiration from previous theory was achieved.

## 1.4 Thesis Structure

This thesis presents a fine-grained multithreaded microarchitecture incorporating a configurable hardware thread scheduler aimed at mixed-criticality and safety-critical systems. Any essential background information and prior work in the field that is necessary to explain the design decisions and reasoning is described in Chapter 2. Further, some of the design choices made throughout the microarchitecture design are discussed in Chapter 3. Additionally, some design issues and other enhancements or modifications are explained here. Chapter 4 will configure the hardware thread schedule of the microarchitecture in several ways to perform analyses on the execution times, response times, and its ability to hide instruction latencies. These results are then used to reason why specific threads provide high predictability, making them better for higher criticality tasks, while other threads are better for low criticality tasks prioritizing high instruction throughput. Finally, Chapter 5 will conclude the work done during this master thesis and discuss any problems that would be interesting in future works.

# Chapter 2

# Background and Related Work

## 2.1 Mixed-Criticality Systems

In Real-time systems, temporal correctness is just as important as logical correctness [3, 4]. A real-time system is required to respond to stimuli from its given environment within time intervals decided by that particular environment. The moment in time that a result must be available is called the deadline [1, 2]. The timing constraints of a real-time system are usually represented by how it enforces the deadlines placed on executing tasks. A deadline is classified as soft if the result of a task still has some value after the deadline has elapsed; otherwise, the deadline is firm.

In some cases, however, the result of a missed firm deadline can have severe consequences such as destruction of property or loss of life [22]. These deadlines are hard. Any real-time system classifies a system with at least one hard deadline as a hard or safety-critical real-time system. The system is a soft real-time system when there are no hard deadlines. For a hard real-time system to achieve functional correctness, all tasks with hard deadlines must meet their assigned deadlines. If such a task fails to meet its deadline, the executed task is considered a failure, and the system did not function as intended. Sometimes, failure in a hard real-time system could lead to catastrophic ramifications. In contrast, a soft real-time system has more relaxed constraints on its tasks. In these types of systems, it may be acceptable for a task to finish its execution after its deadline. However, the usefulness of the results in a soft real-time system decreases gradually with an increase in delay.

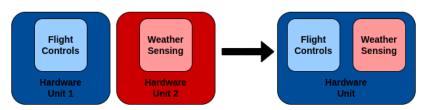

A safety-critical system can consist of functionalities with different levels of criticality. Criticality is used as a label to specify the level of assurance against failure needed for a system [11]. For example, a weather drone can contain flight control and weather sensing applications. If a failure within the functionality of the flight control application occurs, it could lead to the drone's destruction and possibly cause injury. As a result, the flight control application must be considered highly critical to avoid such circumstances. In comparison, the weather sensing application is of a lower criticality, where the drone could experience a failure by being unable to gather data for the weather station. This failure will only be perceived as an inconvenience for the weather station as it will at most require the drone to return to the weather station to fix the issue. Suppose both of these applications have separate physical hardware units on the drone. In that case, there is isolation between the functionality of both applications, meaning that the low-criticality task will not affect the high-criticality one. This isolation provides high safety guarantees and simplifies the certification process by limiting it to only the critical functions [22]. However, having a physical hardware unit for each application on the drone will result in inefficient resource utilization, an increase in costs and size, and a heavy drone with a significant amount of energy consumption. Alternatively, as illustrated in Figure 2.1, it is possible to integrate the applications on the same hardware unit to reduce the drone's cost, weight, size, and energy consumption. This integration will require the applications on the hardware unit to be assigned individual criticality levels to avoid having the drone prioritize gathering data the same way as the flight controls. Because of the mentioned advantages, integrating multiple applications with different levels of criticality onto a common hardware platform, known as a Mixed-Criticality System (MCS), is a growing trend in the design of real-time and embedded systems [23, 8].

Figure 2.1: Applications of different criticality levels can be located on separate hardware units to achieve isolation between applications. Integrating these applications onto a shared hardware unit reduces the hardware's cost, weight, size, and energy consumption.

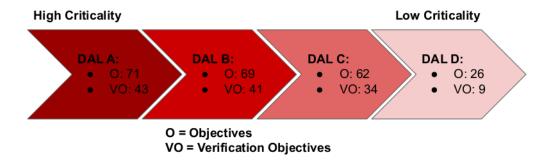

To allow a safety-critical system to be implemented and deployed, it must be certified due to the risks that could occur during system failures. To become certified, a third party known as the Certification Authority must perform a certification process to verify that the safety-critical system is safe. The certification standard usually used in the avionic systems' certification process is the RTCA DO-178C standard [11]. The RTCA DO-178C standard defines five Design Assurance Levels (DAL), categorized by their criticality from the highest criticality level (DAL-A) to the lowest (DAL-E) [17]. Because of the consequences of a failure or malfunction in an application of higher criticality levels, it is clear that the higher the DAL, the more activities, and objectives must be performed and met. In total, DO-178C includes 71 objectives, where 43 of these are related to verification. Therefore, for an application to pass with a DAL-A assurance, all 71 objectives must be met, as seen in Figure 2.2. In comparison, a DAL-E assurance does not require any objectives to be met because there are no consequences to the safety of the aircraft if a failure should occur. Thus, the flight control application would be regarded with a DAL-A assurance for the drone example above. In contrast, the weather sensing application could be as low as DAL-E.

Figure 2.2: The number of objectives and verification objects required in each DAL decreases from left to right [11]. Notice how DAL-E is not on the scale due to not requiring any objectives to be met.

A vital characteristic of any real-time system is that it behaves predictably. This char-

acteristic means the system can perform all applications correctly (functional predictability) and within a given timing bound (timing predictability). A significant concern when integrating multiple applications on the same hardware is the partitioning of the system [8]. Unfortunately, by combining various applications onto the same hardware, the tasks from one application will share compute resources with tasks from other applications. This sharing of resources increases the interference between the tasks regardless of the criticality level [24]. This interference means testing and verification must also account for the interference's timing behavior when determining the system's functional correctness. Introducing spatial and temporal isolation in the system can prevent independent tasks from affecting each other's behavior [20]. Spatial isolation is responsible for protecting a task's state that is stored in various forms of memory, while temporal isolation protects the timing behavior of a task [7]. When complete isolation is introduced, each task can be tested and verified for correctness by itself and still have identical behavior when integrated into the system. As a result, an isolated task will have better timing predictability, which will provide tighter bounds on the worst-case execution time (WCET) analysis [21]. These WCET bounds resulting from the WCET analysis determine the timing partitions that a scheduling tool or system designer must reserve for executing each task [12, 13]. Thus, as a consequence of having tighter bounds on the WCET of a system, fewer system resources will be required to maintain guarantees in the system behavior [16].

## 2.2 Timing Instructions

Real-time systems assign deadlines and periods to tasks. To meet every deadline and know when the real-time system should perform the task, the system requires a sense of time. An instruction that specifies the minimum amount of execution time for a section of code was introduced by Ip and Edwards [25]. A deadline instruction was implemented that forces the program to pause its execution while a timer register decrements. The pause lasts until the specified timer register reaches zero. Once the timer is zero, it is reloaded with the source value of the deadline instruction, and the program continues to the following instruction. This deadline instruction provided a software solution for specifying a lower execution time-bound on specific program code segments. Finally, they demonstrated the deadline instruction by showing how a video controller could be implemented in software and hardware. They concluded that an application that would usually only be possible in hardware is now much easier to write and debug in software, where they wrote roughly four times as many lines of code in VHDL compared to assembly.

Lickly et al. added this deadline instruction to their fine-grained multithreaded processor [26]. In addition, they included a replaying mechanism to the deadline instruction that allowed a particular thread to be stalled without stalling the entire pipeline. Each thread has twelve deadline registers, where eight of these count instruction cycles while the other four count at a different frequency specified by a phase-locked loop (PLL). Because the architecture uses a 6-stage pipeline, the instruction cycle is six clock cycles, as this is the time it takes an instruction to pass through the pipeline. Finally, they illustrated that the architecture could use the deadline instruction to meet VGA real-time constraints using a video game example with three main tasks running on separate threads.

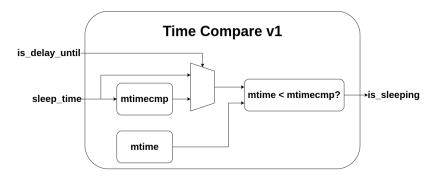

To provide temporal isolation in a multiprocessing architecture, Bui et al. identified four timing control cases that are desirable to have at an ISA level [27]:

1 - Executing a code segment takes a specified minimum amount of time [25].

- 2 Execute a code segment and branch afterward if the code segment exceeds the specified execution time limit.

- 3 Execute a code segment and branch immediately if the code segment exceeds the specified execution time limit.

- 4 Finish a code segment within a maximum execution time.

The first three capabilities can be added to a given ISA relatively simply, where the following four pseudo-instructions, proposed in previous work, can express this [20]:

- **get\_time:** Loads the current time of a timer register into a destination register.

- delay\_until: Stall the program execution until the value in the timer register exceeds

the value in the provided register.

- interrupt\_on\_expire: Interrupt program execution when the value in the timer register exceeds the value in the provided register.

- deactivate\_interrupt: Disables the interrupt\_on\_expire operation that is already in progress.

Consider a weather sensing drone that reads a sensor and adds up to 1000 samples to an average before transmitting the value to the weather station, shown in Listing 2.1. The sensor task uses the interrupt\_on\_expire and deactivate\_interrupt to achieve case 3 mentioned above. Here, the sensor task is allocated 1 ms of time, interrupting the task's execution if it exceeds the time limit. To ensure that the task uses a specific amount of time, the delay\_until task is added to achieve case 1, where the task will stall until 1 ms has elapsed since the retrieval of the current time.

Listing 2.1: timingcontrol.a

```

1 addi x6, x0, 1000

//Set loop limit

read_sensor:

2

get_time x1

//Get current time

3

addi x1, x1 1000000

//Calculate time 1 ms in future

addi x2, x0 0

//Set iterator to 0

5

addi x5, x0 0

//Set sensor sum register to 0

6

interrupt_on_expire x1 //Set a timer interrupt to trigger in 1 ms

7

poll_input:

8

1w \times 4, 0 (\times 3)

//Read sensor

9

addi x2, x2, 1

//Increment iterator

10

... Add to Average Calculation Code ...

11

blt x2, x6, poll_input //Branch if less than loop limit

13 output_average:

deactivate_interrupt

//Deactivate interrupt

14

15

sw x5, 4(x3)

//Write sensor average

//Stall until 1 ms from current time

delay_until x1

16

```

To achieve case 2, a comparison between two get\_time instructions can be performed. By reading the timer before and after some code segment, the program can see whether the code segment's duration lasted too long, where the program will branch to deadline\_miss if more than 1 ms elapsed.

Listing 2.2: timingcontrolcase2.a

```

1 get_time x1

2 addi x1, x1, 1000000

3 ... Code ...

4 get_time x2

5 bgt x2, x1, deadline_miss

```

Implementing the mentioned pseudo-instructions in hardware is relatively simple, where many possible alternative implementations exist [20]. The timing control cases' general idea is to stall, branch, or interrupt program execution due to a timer comparison. As a result, increased predictability in the timing behavior of a task can be achieved, where the timing instructions can allocate a specific amount of time to a task.

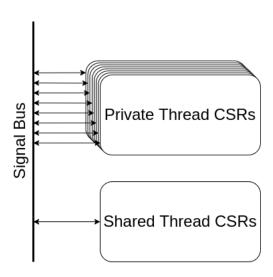

## 2.3 Hardware Multithreading Techniques

Hardware multithreading is a popular method used to improve the utilization of processor resources by integrating multiple hardware threads into the same processor core [28]. A hardware thread is logically equivalent to a processor, where each hardware thread has individual state registers, such as a register file (RF), a program counter (PC), and control and status registers (CSR) [29]. However, a hardware thread shares a pipeline and frequently the same memory space as other hardware threads within the same processor. By sharing the same or parts of the same memory space, the hardware threads can effortlessly access the data of other hardware threads, thus enabling data sharing [30].

In an operating system with multiple software threads, a software thread switch would spend many clock cycles storing the state of the software thread before fetching the state of a different software thread. As a result, having multiple software tasks allocated a certain amount of computing time will add significant latency to the overall execution time due to the context switching performed in software. In comparison, by having a software task allocated to a hardware thread in a multithreaded processor, the processor can perform hardware thread switching at clock cycle granularity, thus removing the latency due to the storing and retrieving of the task state.

In addition to removing the latency caused by context switching, hardware multithreading has an additional latency-related benefit. In a single-threaded processor, branching and cache miss results in short and long stalls in the task execution, respectively. Short stalls refer to a delay in executing a task of a few clock cycles, while a long stall can be many hundreds of clock cycles. Because of the poor hardware resource utilization caused by these stalls, much research is being performed on branch and cache prediction mechanisms to hide the added delay to the program execution [31, 32, 33]. In addition to these prediction mechanisms, it was discovered that an inherent benefit of hardware-based multithreading is that it can be used to hide these delays in program execution by switching to a different thread instead of stalling.

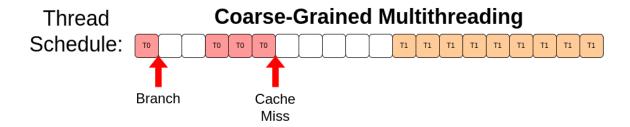

Coarse-grained multithreading, or block interleaving, is a hardware multithreading technique introduced to hide long stalls [30]. For example, the thread schedule of a coarse-grained multithreaded processor with five pipeline stages can be seen in Figure 2.3. When the coarse-grained technique notices a more prolonged stall such as a cache miss, it performs a thread switch [29]. This thread switch allows a different thread to execute while the thread that was stalled fetches the required data from a higher level cache, such as the L3 cache. However, when the thread has managed to retrieve the necessary data from the L3 cache, it must either wait until the other thread gives away the compute resources, or the thread has to preempt the thread currently occupying the pipeline. As a result, the thread that was stalled may have significant latency added to its task execution.

Figure 2.3: An example thread schedule using the coarse-grained multithreaded technique. The technique manages to hide most of the latency caused by cache miss, but is incapable of hiding the branch latency.

As can be seen in Figure 2.3, the program execution latency in a coarse-grained multithreaded processor caused by the cache miss is five clock cycles compared to the hundreds of clock cycles latency present in a single-threaded processor without cache prediction. The five-clock cycle delay is because the pipeline must be emptied of instructions from the previous thread and filled with instructions from the new thread. Thus, the number of clock cycles delayed depends on the number of pipeline stages in the processor architecture. Because of this pipeline delay, the coarse-grained multithreaded technique does not benefit from switching on shorter stalls. If the coarse-grained multithreaded processor example performs thread switching on branch stalls, the latency introduced to the pipeline will be three clock cycles longer than if it did not perform any thread switching. As a result, coarse-grained multithreading is used to hide a large portion of the latency caused by longer stalls such as cache misses. In contrast, it cannot conceal branch latencies without a branch prediction mechanism.

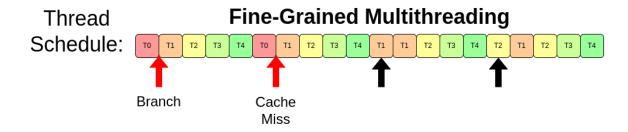

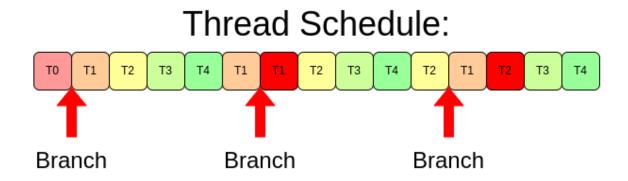

Fine-grained multithreading, or cycle-by-cycle interleaving, is another hardware multithreading technique introduced to hide long and short stalls [30]. For example, the thread schedule of a fine-grained multithreaded processor with five pipeline stages and five hardware threads can be seen in Figure 2.4. The fine-grained multithreaded technique performs thread switching at the clock cycle granularity. The thread scheduler usually switches between available hardware threads each clock cycle in a round-robin fashion [29, 34]. This scheduling method means that if there are as many threads as pipeline stages, the next instruction from any particular thread is, in principle, fed to the pipeline once the previous instruction is completed. Thus, the need for data forwarding is eliminated, and any data hazards that would otherwise cause a flush of the pipeline stages are avoided. As a result, the fine-grained multithreaded technique can avoid short stalls by having other threads use the pipeline stages that would otherwise be flushed. This avoidance can be seen in Figure 2.4, where the branch operation performed by thread0 does not lead to a stall because thread1 and thread2 are using the thread cycles where a pipeline flush would otherwise have occurred.

An example thread schedule using the coarse-grained multithreaded technique. The technique manages to hide most of the latency caused by cache miss, but is incapable of hiding the branch latency.

In addition to hiding shorter stalls by performing hardware thread interleaving every clock cycle, the fine-grained multithreaded technique can hide longer stalls, as seen in Figure 2.4. Here, thread0 notices a cache miss where the thread scheduler is notified of this occurrence. While thread0 fetches the required data from the L3 cache, the hardware thread scheduling technique will decide how the unused cycles are allocated. For example, PTARM is a fine-grained multithreaded processor that uses fixed round-robin scheduling, alternating between

Figure 2.4: An example thread schedule using the fine-grained multithreaded technique. The technique manages to hide the cache latency, except the cycle causing the cache miss. Here, other threads are using the spare cycles while Thread0 is stalling. Additionally, the technique manages to hide branch latency by scheduling other threads during the cycles that can be flushed due to a branch.

all hardware threads regardless of the thread status [35]. Because the scheduler does not care about the thread status, the thread cycles will be left unused until the thread stops stalling. Furthermore, if other threads result in cache misses, those cycles will also be left unused.

On the other hand, XMOS is a fine-grained multithreaded processor that uses active round-robin scheduling, alternating between all hardware threads ready to execute [36]. This scheduling method can be seen in Figure 2.4, where thread1 and thread2 use the cycles initially allocated to thread0. The disadvantage of this technique is that it can introduce some latency due to branch stalls, where two adjacent thread cycles can potentially be assigned to the same thread. For example, the figure shows thread1 being adjacent to another thread1 cycle and thread2 having a single thread cycle between another thread2 cycle. If the first thread cycle, in either case, performs a branch, the other cycle will result in a stall. Thus, there is a potential for some branch latency in the active round-robin scheduling method. However, active round-robin scheduling can allocate most unused cycles to other threads, resulting in better hardware resource utilization than fixed round-robin scheduling.

Although the fine-grained multithreaded technique is capable of hiding both short and long stalls, there is a trade-off that must be made. Because the method is performing cycle-by-cycle interleaving, where the scheduler will interleave several threads, the frequency of any specific thread will be reduced. For example, using the fine-grained processor above running at 100MHz clock frequency, each thread will execute at 20MHz. As a result, the frequency of each thread is inverse proportional to the number of actively scheduled threads. However, even though each thread is executing slower, concurrent thread execution results in a total throughput equivalent to that of a single-threaded processor when disregarding stall latency. In comparison, the coarse-grained technique has a similar thread-specific throughput as the single-threaded processor. For example, with a 100MHz frequency coarse-grained multithreaded processor, a single thread will execute at 100MHz due to the seemingly sequential behavior of the thread scheduling method. Finally, the overall throughput of the coarse-grained technique is equivalent to the fine-grained approach when disregarding stall latency.

## 2.4 Model-Based Engineering

Model-based design (MBD) is an effective and efficient method for understanding various systems, such as those found in microcontrollers and processors. MBD helps reduce the complexities that arise during the development of a system through visual prototyping and

continuous testing and validation of system characteristics [37, 38]. By continuously testing and validating the system throughout the design process, spotting bugs and areas in the design or requirements that need modification is made easy. This continuous checking enables rapid prototyping by fast feedback on requirements and design decisions that result in an overall reduction of development risks [39, 40]. Furthermore, traditional design processes usually handle the design information in a text-based approach that can lead to misinterpretations and be challenging to understand. Standard document-based procedures can also be more time-consuming and prone to errors due to the code and data being created manually in a text-based form. These reasons are essential when designing large and complex systems, such as satellites, aircraft, and automobile systems, where mistakes in the system can lead to catastrophic failure. With a model-based approach, it is possible to break a complex system into smaller digital models. These models are then verified to reduce the number of defects injected due to a lack of overview and validation of design decisions in a traditional document-based approach. These designed models do not necessarily need to represent the system perfectly. However, they serve as a method to supply the designer with valuable knowledge and feedback on the devised system sooner and more cost-effectively than system implementation alone.

Because of its ability to reduce development time, resolve design problems early, and provide less ambiguous system documentation, Model-Based Engineering (MBE) is an expanding field in multiple industries, including the automotive and aerospace industries [41, 42]. Amongst the many areas within these industries, MBE can also be used to accelerate FPGA development [43]. In a traditional FPGA design process, a systems engineer produces a high-level computer simulation of the system to be designed [44]. Further, the designer communicates with a hardware developer that will write the code for the model to be implemented on an FPGA. The hardware developer must understand the simulated system's logic before engaging in the HDL design. MBE significantly speeds up the design and verification process by allowing the hardware developer and systems engineer to cooperate using functional models of the design specifications. These are executable models and are easier for designers coming from different fields of expertise to interpret similarly. Consequently, the hardware developer does not need to spend the same amount of time trying to decipher the simulated design and can directly start the process of implementation and verification on an FPGA.

Simulink is an effective MBE tool that can further accelerate FPGA development using the available HDL Coder add-on. The tool can generate HDL code from the model by having the designer create an HDL-compatible Simulink Model [45, 46]. Thus, it is possible to design functional models that can be continuously tested and verified throughout the entire design process and later used to generate HDL code. Furthermore, Simulink provides methods for reusing reference models in design verification and performing FPGA-based debug and verification [47, 48]. This debug and verification method allows the RTL code to be verified against the reference model through simulation and on an FPGA. As a result, less time is spent correcting design mistakes, reducing the total development time considerably.

Moreover, as the generated HDL code has been designed and verified on an FPGA, Simulink also provides the capability to integrate the model into a more extensive system and perform Hardware-in-the-loop (HIL) simulation [49]. This simulation will allow the design to be further tested by providing the design implemented on an FPGA with various stimuli. These stimuli are then handled by the FPGA, which further outputs signals relative to the stimuli. The simulation then provides new stimuli dependent on the output signals retrieved from the FPGA. As a result, the algorithms implemented on the FPGA can be verified in an environment that simulates the real world, allowing critical systems to be tested in detail to ensure that no errors are possible.

2.5. RISC-V 13

### 2.5 RISC-V

RISC-V is a non-profit organization with billions of chips on the market and a large and growing community [50]. This organization provides the community with an open-source Instruction Set Architecture (ISA). An ISA is a computer model that defines how the processor is controlled by software, allowing developers to understand better what the instruction set can do, allowing for more efficient code to be written [51, 30]. Because RISC-V's ISA is open-source and the growing community, there is a myriad of resources available related to custom microarchitecture design based on this ISA [52, 53, 54]. RISC-V has a collection of available extensions that can be added to the baseline ISA, making it possible for designers to pick between various functionality options to add to their design, reducing the amount of custom functionality required.

## 2.5.1 RV32I Base Integer Instruction Set

The 32-bit base integer instruction set, also known as RV32I, is one of the most straightforward architectures available in the RISC-V extension libraries. The RV32I is an ISA designed to reduce the required hardware with minimal implementation while forming a compiler target able to support modern operating system environments [55]. RV32I contains 40 unique instructions that can be used to emulate all of the ISA extensions available except for the atomic-instruction extension, which requires additional hardware [56]. Creating a hardware implementation using this ISA, including the machine-mode privileged architecture, would require the addition of the 6 CSR instructions mentioned in Section 2.5.2.

RV32I also has several types of instructions. Namely, R-type, I-type, S-type, B-type, U-type, and J-type, shown in Figure 2.5. These instructions have their unique purpose, where, e.g., B-type instructions are branch instructions and I-type instructions are register-immediate operations [55]. First, the operation code stored in the seven least-significant bits (LSB), called opcode, is checked to determine which type of instruction is being executed. Then, based on the instruction type that has been established, it is possible to extract the instruction fields. As can be seen in the figure, most fields come from the same set of bits regardless of the instruction type. The immediate field, however, is constructed of different bits depending on the kind of instruction.

| 31 30 25                  | 24 21      | 20 19 | 9 15   | 14 12  | 2 11 8                      | 7       | 6 0    |        |

|---------------------------|------------|-------|--------|--------|-----------------------------|---------|--------|--------|

| funct7                    | rs2        |       | rs1    | funct3 | ro                          | l       | opcode | R-type |

|                           |            |       |        |        |                             |         |        |        |

| imm[1                     | 1:0]       |       | rs1    | funct3 | ro                          | l       | opcode | I-type |

|                           |            |       |        |        |                             |         |        |        |

| imm[11:5]                 | rs2        |       | rs1    | funct3 | imm                         | [4:0]   | opcode | S-type |

|                           |            |       |        |        |                             |         |        |        |

| $[imm[12] \mid imm[10:5]$ | rs2        |       | rs1    | funct3 | $\mid \text{imm}[4:1] \mid$ | imm[11] | opcode | B-type |

|                           |            |       |        |        |                             |         |        |        |

|                           | imm[31:12] | 2]    |        |        | ro                          | l       | opcode | U-type |

|                           |            |       |        |        |                             |         |        |        |

| [imm[20]] $[imm[1]$       | 0:1] im    | m[11] | imm[1] | 9:12]  | ro                          | l       | opcode | J-type |

Figure 2.5: The types of instructions available in the RV32I ISA.

Figure 2.6 shows the instruction encoding formats for several of the math operations that the RV32I architecture is capable of performing. The term I-type means that the instruction is of Immediate-type. These instructions only use one source register, rs1, whereas the other

value, imm[11:0], is derived from the instruction. The 3 bits in the middle of the 32-bit instruction format are the functional bits, which specify which operation is to be performed. These bits are used along with the opcode in the 7 LSBs to select the instruction operation. Once the operation has been performed on these two values, the result is placed in the destination register, rd.

| imm[11:0] | rs1 | 0 0 0 | $_{ m rd}$       | ( | ) ( | ) 1 | 0  | 0 | 1 | 1 | I-type | addi  | rd,rs1,imm |

|-----------|-----|-------|------------------|---|-----|-----|----|---|---|---|--------|-------|------------|

| imm[11:0] | rs1 | 0 1 0 | $_{ m rd}$       | ( | ) ( | ) 1 | 0  | 0 | 1 | 1 | I-type | slti  | rd,rs1,imm |

| imm[11:0] | rs1 | 0 1 1 | $^{\mathrm{rd}}$ | ( | ) ( | ) 1 | 0  | 0 | 1 | 1 | I-type | sltiu | rd,rs1,imm |

| imm[11:0] | rs1 | 1 0 0 | $_{ m rd}$       | ( | ) ( | ) 1 | 0  | 0 | 1 | 1 | I-type | xori  | rd,rs1,imm |

| imm[11:0] | rs1 | 1 1 0 | $_{ m rd}$       | ( | ) ( | ) 1 | 0  | 0 | 1 | 1 | I-type | ori   | rd,rs1,imm |

| imm[11:0] | rs1 | 1 1 1 | rd .             | ( | ) ( | ) 1 | .0 | 0 | 1 | 1 | I-type | andi  | rd,rs1,imm |

Figure 2.6: Example instruction formats for various I-type operations.

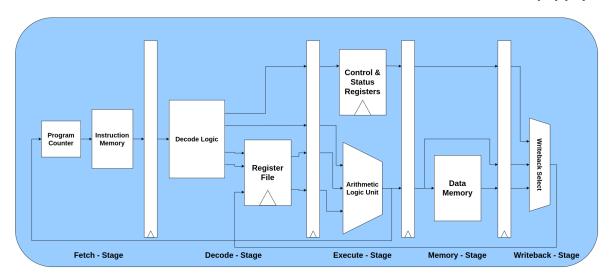

The instructions of RV32I are of the same lengths and can be fetched in a single cycle. Because of this, it is beneficial to divide the microarchitecture into pipeline stages [57]. Thus, a reduced clock time and throughput improvement can be achieved, where multiple instructions are overlapped in execution [58]. An example of a pipelined RV32I is the 5-stage pipeline, shown in Figure 2.7. This pipelined microarchitecture contains the fetch, decode, execute, memory access, and write-back stages, performed in the respective order [59] [60].

Figure 2.7: An example of a 5-stage pipeline containing the stages fetch, decode, execute, memory access, and write back, separated by a register.

#### 2.5.2 Control and Status Registers

To perform any control and status register (CSR) operations, RISC-V defines specific CSR instructions to read or write a CSR, known as Zicsr [61]. There are six available CSR instructions within Zicsr, where three (CSRRW, CSRRS, and CSRRC) use a source register. The other three instructions (CSRRWI, CSRRSI, and CSRRCI) use a 5-bit zero-extended immediate value to read/write a CSR. These instructions within the standard RISC-V ISA have a 12-bit encoding space set aside for up to 4096 CSR. The 2 MSB of this encoding space indicates whether the register is read/write or read-only. The following two bits encode the lowest privilege level that can access the CSR. This CSR address convention constrains the mapping of CSRs into the address space but makes the hardware easier to check for errors

2.5. RISC-V

and provides a larger CSR space [61]. The highest privilege mode available in a RISC-V system is the machine mode. This mode is used for low-level access to the hardware platform and is the first mode entered at a hardware reset. The machine mode additionally allows the implementation of features that would otherwise be implemented in hardware directly but is either too difficult or expensive to realize [62].

The machine-level ISA contains a list of several important CSRs that were added to the designed microarchitecture, described in Chapter 3, to allow certain features to be added [63]. For example, embedded systems rely heavily on handling asynchronous events, known as interrupts, which are designed to be managed by the processor [64]. Therefore, within the machine-level ISA, there are several CSRs described that are used to configure interrupts. These CSRs are part of the CSRs referred to as trap setup and trap handling CSRs, which are used to manage interrupts and exceptions. The term trap refers to the synchronous transfer of control to a trap handler caused by either an interrupt or an exception. The term exception refers to unusual conditions associated with the instruction in the currently running thread that can occur during run-time, such as illegal instructions and instruction address misalignment.

The CSRs required as a bare minimum to handle interrupts are the mstatus, mie, and mtvec trap setup CSRs and the mepc, mcause, and mip trap handling CSRs [64]. By having these CSRs, a RISC-V architecture can enter and exit the interrupt handler, although it will lack certain features that are not within the scope of this report. In addition to the CSRs necessary to handle traps, the mhartid CSR is essential in a multithreaded system. The mhartid is a read-only register that holds an integer value corresponding to the ID of the hardware thread that is running some code. Due to the occasional call for startup configuration, e.g., a system reset, one of the threads must have a thread ID of 0. Additionally, the magnitude of the largest thread ID used in the system should be as low as possible for higher efficiency.

#### 2.5.3 Machine-level Timer Registers

The machine-level timer register, mtime, is a memory-mapped register that provides the RISC-V architecture with a real-time counter [65]. This timer register is required to increment at a constant frequency, and the architecture must have a mechanism that determines the time base of the counter. Once mtime reaches the maximum value, the register will overflow, and the register will wrap around. In both 32-bit (RV32) and 64-bit (RV64) RISC-V systems, the mtime register is 64 bits.

In addition to the mtime register, another register known as mtimecmp is defined [65]. This register is a 64-bit memory-mapped timer compare register, which in combination with mtime, is used for timer interrupts. Whenever mtime contains a value greater than or equal to the value in mtimecmp, a timer interrupt becomes pending [64]. This interrupt will remain pending until the value of mtimecmp becomes greater than mtime, which typically results from writing mtimecmp. To allow a timer interrupt to occur, the timer interrupt bit, MTIE, must be set in the mie register. Otherwise, the architecture will not be able to treat the pending interrupt.

An accurate real-time clock (RTC) is relatively expensive and must be able to run even when the rest of the system is powered down [65]. As a result, the RTC is usually shared between threads in the same system, and accessing the RTC may result in the penalty of a voltage-level-shifter and clock-domain crossing. Thus, it is more natural to have the mtime register exposed as a memory-mapped register rather than a CSR. Finally, although the mtime register is shared between threads, having at least one mtimecmp register for each thread is typical, allowing the thread to perform timer interrupts.

### 2.6 Previous Work

### 2.6.1 Single-operation RISC-V Architecture

The single-operation RISC-V architecture was implemented in Simulink during the specialization project, TFE4590, last semester at the Norwegian University of Science and Technology (NTNU) [66]. This project aimed to implement a microarchitecture with a 5-stage pipeline capable of performing the addi operation from the RISC-V's base integer instruction set (RV32I) using a custom-made design methodology. The first step of this methodology was to design the functionality of each stage using Matlab scripts, followed by the design of the microarchitecture in Simulink. The third step of the methodology was to implement the microarchitecture in Verilog, where the knowledge from the Simulink design reduced errors during code writing. Finally, the last step was to use the Simulink model (step 2) as a golden reference model to test the Verilog code implemented on an FPGA. The idea of the specialization project was to develop a proper design methodology that could be used to design a fine-grained multithreaded microarchitecture. However, the time required to implement the fine-grained multithreaded microarchitecture, including the testing, resulted in only step 2 being considered. It should be noted, however, that the single instruction microarchitecture used in the previous semester was further used in this project as the baseline. However, the entire 5-stage pipeline was redesigned due to a better understanding of Simulink, resulting in better model-based testing and more readable models.

#### 2.6.2 FlexPRET

FlexPRET is a fine-grained multithreaded RISC-V processor that allows thread-level hardware-based isolation and predictability to be traded for instruction throughput [14]. The processor enables an arbitrary interleaving of threads controlled by a unique hardware thread scheduler. This scheduler allows for a flexible thread schedule where threads can either be characterized by isolation and predictability or efficient processor utilization. FlexPRET also utilizes timing instructions that enable direct control over timing in nanoseconds resolution, as mentioned in Section 2.2.

As described in Section 2.3, a fine-grained multithreaded system performs clock-by-clock thread interleaving. To achieve such fine-granularity hardware thread switching, some mechanism is required to decide which thread should be selected for each clock cycle. In the FlexPRET processor, the unit responsible for this is the hardware thread scheduler, a configurable scheduler capable of scheduling anywhere between 0 and 8 threads in a round-robin fashion.

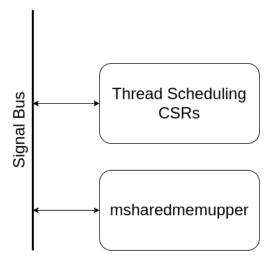

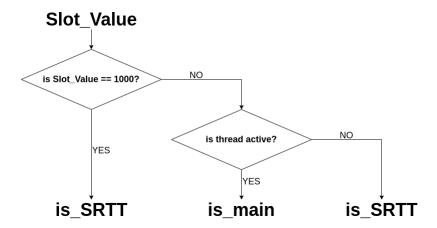

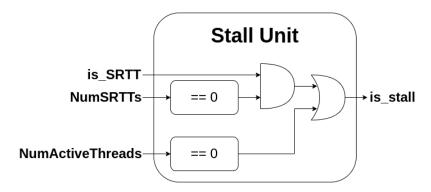

Unlike most multithreaded systems, the hardware thread scheduler presented in Flex-PRET classifies the threads as either hard real-time threads (HRTTs) or soft real-time threads (SRTTs). An HRTT is a thread that can only use the thread cycles allocated to that specific thread, meaning that the thread is locked to a slot in the repeating sequence. If the thread is not assigned any slots in the sequence, then the thread will stay inactive. In contrast, if a thread is configured as an SRTT, then the thread can have specific thread cycles allocated like an HRTT in addition to using any spare thread cycles available. This means that if unused slots are in the repeating sequence in the hardware thread scheduler, an SRTT can use these cycles. The hardware thread scheduler utilizes two active round-robin schedulers for the threads; one that schedules both HRTT and SRTT for fixed slots in the sequence and one that schedules SRTTs for spare cycles.

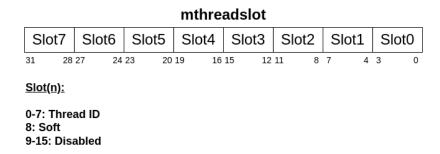

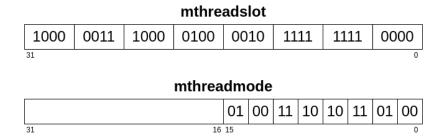

To configure the hardware thread scheduler, FlexPRET implemented two configuration registers: mthreadmode and mthreadslot. The mthreadslot register, shown in Figure 2.8,

is responsible for selecting the repeating thread sequence that is delivered from the thread scheduler to the fetch stage of the pipeline. The register is divided into eight 4-bit registers, called slots. As the name implies, a slot is a placeholder for a thread ID in the repeating sequence. Each of these slots can have a value from 0 to 15, specifying which thread should have priority for that slot in the sequence. For example, the values 0 to 7 indicate specific thread IDs, meaning that if slot0 contains the value 4, then thread 4 is prioritized for the zeroth slot in the repeating sequence. The meaning of prioritized in this case is that if the thread is awake, it has priority for that slot. However, if the thread is asleep, other threads, namely SRTTs, can use this slot until the prioritized thread wakes up again. Thus, each slot value specifies the thread ID with priority and not whether the slot is private to a specific thread ID. When the value eight is allocated to a slot, it means that the slot is soft. Any SRTTs can use this particular slot in the repeating sequence. A soft slot functions the same way as a slot containing the value of a thread ID that is sleeping. Finally, it should be possible to disable a slot in the sequence when a repeating sequence of length 8 is undesirable. To disable a slot in the sequence, any other values, 9 to 15, can be stored in the slot the programmer wants to disable.

Figure 2.8: The slot CSR of the hardware thread scheduler. Each slot can either contain a thread ID (0-7), a soft thread value (8), or be inactive (9-15).

The mthreadmode register, shown in Figure 2.9, is responsible for selecting whether a hardware thread should be an HRTT or SRTT and whether the thread is awake or asleep. The register only uses the lower 16 bits of the 32-bit register, where the used bits are divided into eight 2-bit registers, called mode registers. Each mode register has a thread ID, where mode0 relates to thread0. Compared to the slots CSR, the mode registers allocates 1 bit to select the mode of the thread and the other to choose the state. The mode register's least significant bit (LSB) is used to determine the thread's state; when the bit is 0, it means that the thread is awake, while a bit value of 1 means sleeping. The most significant bit (MSB) of the mode register selects the thread's mode; when the bit is 0, the thread is configured as an HRTT, while a bit value of 1 means that the thread is configured as an SRTT.

## mthreadmode

T7 T6 T5 T4 T3 T2 T1 T0

31 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

<u>T(n):</u>

00: Hard Active (HA) 01: Hard Sleeping (HZ) 10: Soft Active (SA) 11: Soft Sleeping (SZ)

Figure 2.9: The mode CSR of the hardware thread scheduler. This CSR configures each thread as either hard or soft real-time threads and whether the thread is awake or asleep.

# Chapter 3

# The Microarchitecture Design

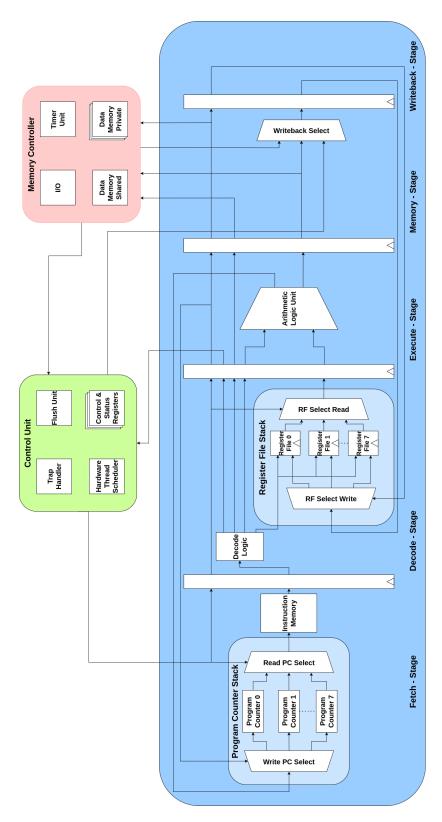

The architecture presented in Section 3.1 consists of a 32-bit RISC-V microarchitecture with five pipeline stages and uses vectored interrupts. Because the design is made in Simulink and has not been converted to HDL code, the critical paths of the system are unknown, meaning that the microarchitecture cannot provide any specific frequency at the time of this writing. Next, Section 3.2 presents the microarchitecture's reconfigurable software-controlled hardware thread scheduler. A dynamic scheduler allows the software to freely adjust the schedule and mode of the hardware threads whenever required. These hardware threads can be configured as hard real-time threads (HRTT) or soft real-time threads (SRTT). Classifying these hardware threads as either HRTTs or SRTTs makes it possible to tailor each thread's predictability, isolation, and throughput. However, changing one of these parameters may cause the other parameters to deteriorate. It is then necessary to select these levels with care. The microarchitecture contains a timing extension that improves the overall throughput of the program, presented in Section 3.3, and makes it possible to add real-time constraints. This extension contains a few timing instructions that allow the program to implement real-time functionality. Finally, Section 3.4 presents a custom assembler designed for this microarchitecture that understands instructions from the base integer RISC-V ISA, the Zicsr extension instructions, and the custom timing instructions.

### 3.1 Architecture

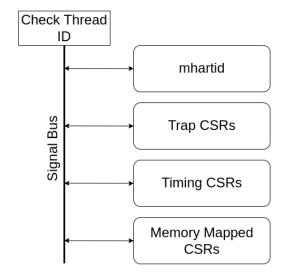

The microarchitecture consists of three primary modules: The 5-stage RISC-V pipeline, the memory unit, and the control unit, as shown in Figure 3.1.

#### 3.1.1 5-Stage RISC-V Pipeline

The pipeline is based on a typical 5-stage RISC-V pipeline containing the stages: fetch, decode, execute, memory, and write-back, as seen in Figure 3.1. To enable the microarchitecture to use fine-grained multithreading, additional state components, such as register files and program counters, must be integrated into the pipeline to allow multiple threads to run on the same microarchitecture. The following paragraphs detail the modifications done to each pipeline.

The pipeline must be expanded with additional program counters in the fetch stage to allow multithreading in the microarchitecture. These program counters enable each thread to point to different locations in the instruction memory. Hence, pointing to separate memory regions allows each thread to perform separate software tasks. Thus, eight program counters were added to the fetch stage, making it possible to schedule eight hardware threads. As a

Figure 3.1: A high-level model of the microarchitecture. The design consists of three main parts: a 5-stage RISC-V pipeline, Control Unit, and a Memory Unit, colored in blue, green, and red, respectively.

result, eight distinct software tasks can execute concurrently in the microarchitecture while maintaining hardware-based isolation between the tasks. However, a mechanism must be available to select which program counter to forward and increment. Selection between hardware threads is achievable using a multiplexer to choose which program counter should access the instruction memory. Additionally, the signal used to select the program counter also increments the program counter. Furthermore, the pipeline must know which program counter to update when performing operations such as branching. This update is achievable by adding a demultiplexer to the input to write the branch value to the correct program counter.

The multiplexer and demultiplexer used respectively for reading and writing utilize a thread ID that identifies the program counter to access. As can be seen in Figure 3.1, the multiplexer receives the thread ID from the hardware thread scheduler. In comparison, the demultiplexer receives the thread ID from the execute stage since this is the stage responsible for deciding any jumps in the instruction memory. Thus, the thread ID from the hardware thread scheduler must be forwarded to the other stages to make the pipeline aware of the thread ID residing in each stage. This awareness allows the stages to identify which thread is occupying the stage, thus limiting access to the state components with identical thread ID.

As mentioned previously, each thread must be supplied with a register file. Thus, to equip the microarchitecture with eight threads, the decode stage must contain eight register files, where each register file is private to a thread. By having a private register file, a hardware thread can maintain its state when the pipeline is shared with other hardware threads. However, although the decode stage contains eight register files, a mechanism similar to the program counters must be added to select the correct register file for a thread. As a result, a multiplexer and demultiplexer select port is added to the output and input, respectively. Compared to the program counter, the multiplexer uses the thread ID from the pipeline register between the fetch and decode stages. Since the write-back stage writes the register file, the demultiplexer uses the thread ID from this stage to select the corresponding register file.