# System integration of image processing and further developing of CCSDS and integration of RS422

Armin Bahadoran

Fakultet for informasjonsteknologi og elektroteknikk Institutt for elektroniske systemer

#### Abstract

When sending data onboard a satellite, the data transmission rate between modules is an issue. This thesis describes how to incorporate a UART data transmission function into a Zynq-based System on Chip. The Zynq is a System on Chip that connects a processor with programmable logic. The data is sent via the processing system, although the programmable logic uses a UART device. The functionality will be to use interrupts to transport data from the OPU to the PC. To ensure proper operation, tests were carried out using stimuli from the processing system and monitored using a protocol analyzer.

#### Summary

When hyperspectral pictures are collected and compressed, they must be stored in the satellite's storage device, i.e. the payload controller, which also serves as a router between the payload and the satellite bus. In order to communicate between its Onboard Processing Unit and the Payload Controller, the HYPSO-1 satellite, which is presently in orbit, uses the CAN standard. This method works fine, however data transmission takes some time. The NTNU Small Satellite Team has concluded that in parallel with the CAN interface, a UART coupled to an RS-422 with a baud rate close to 3 Mbps is preferable. Implementing an AXI UART 16550 peripheral to transport data from the memory to the Payload Controller is the method which is decided. This is accomplished by transferring serially with the peripheral the compressed HSI data from the Cube DMA, which is kept in a data buffer. The latency of the UART functionality is reduced by utilizing interrupts. The data is delivered from the device's transmit line to the RS-422, which is further linked to the Payload Controller. After integration and testing, the UART operated as intended, with data being successfully transferred and received between two devices. To complete the project, the UART driver must be made compatible with embedded Linux so that it can function with the other Onboard Processing Unit programs.

## Preface

This report is written by Armin Bahadoran as the end of the 2 year master programme named Electronic Systems Design with the specialization in Design of Digital Circuits. This master's project was published by the NTNU Small Satellite Team, a group working on satellite related activities.

The NSSL is now working on HYPSO-2, a nanosatellite with a payload that includes a hyperspectral imager (HSI) camera and also a software defined radio (SDR). On the satellite, there was no UART device at the start of this project.

The goal of this research is to show how compressed hyperspectral imaging (HSI) data may be transmitted and received using the UART, which has been implemented into the onboard processing unit.

## Acknowledgements

First and foremost, I'd like to thank my thesis adviser, Dr. Milica Orlandic of NTNU's Department of Electronic Systems. I want to thank her for all of her help and advice during the endeavor. She continuously let me do my own work on this project, but she pointed me in the appropriate path when she believed I needed it.

I'd also want to thank all of the NSSL members. During the pandemic, the ability to borrow lab equipment was incredibly useful. Also, for the sake of motivation, the members' advice and sympathy when times were rough were highly helpful. The team also allowed me to experience numerous work methodologies, which will be highly beneficial when I begin to work.

Finally, I want to express my sincerest appreciation to my parents and friends (in particular, an exchange student who was always there for me when things became difficult) for their unwavering support and encouragement during my years of study and the process of researching and writing my thesis. When circumstances were bad, you always found a way to keep me motivated. This achievement would not have been achievable without their assistance.

## Contents

| 1        | Intr        | roduction 1                                                                                                           |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------|

|          | 1.1         | HYPSO Mission                                                                                                         |

|          | 1.2         | Issue                                                                                                                 |

|          | 1.3         | Goal                                                                                                                  |

|          |             | 1.3.1 Thesis structure $\ldots \ldots 5$ |

| <b>2</b> | Sne         | cialization Project 6                                                                                                 |

| -        | 2.1         | Verification of Design   6                                                                                            |

|          | 2.1         | 2.1.1 Integrated Logic Analyzer (ILA)                                                                                 |

|          |             | 2.1.2 Virtual Input/Output (VIO)                                                                                      |

|          |             | 2.1.2       Virtual input/Output (VIO)       7         2.1.3       Results from the design       7                    |

|          |             |                                                                                                                       |

| 3        |             | kground 9                                                                                                             |

|          | 3.1         | Hyperspectral Imaging                                                                                                 |

|          | 3.2         | HYPSO 6U Nanosatellite bus M6P                                                                                        |

|          | 3.3         | HSI as a Remote Sensing Tool                                                                                          |

|          | 3.4         | Remote Sensing Techniques                                                                                             |

|          | 3.5         | Payload                                                                                                               |

|          |             | 3.5.1 Onboard processing unit                                                                                         |

|          | 3.6         | RS-422                                                                                                                |

|          | 3.7         | Field Programmable Gate Array    17                                                                                   |

|          |             | 3.7.1 UltraZed EV SoM $\ldots$ 17                                                                                     |

|          |             | 3.7.2 Zynq-7000                                                                                                       |

|          |             | 3.7.3 Board Support Package                                                                                           |

|          | 3.8         | Tools                                                                                                                 |

|          |             | 3.8.1 Vivado Design Suite                                                                                             |

|          |             | 3.8.2 Vitis                                                                                                           |

|          |             | 3.8.3 PetaLinux                                                                                                       |

|          | 3.9         | Operating Systems                                                                                                     |

|          |             | 3.9.1 Embedded Linux                                                                                                  |

|          |             | 3.9.2 Cube DMA                                                                                                        |

| 4        | Imr         | blementation 29                                                                                                       |

| т        | <b>4</b> .1 | Overview         25           29         29                                                                           |

|          | 4.2         | System Analysis         29                                                                                            |

|          | 4.4         | 4.2.1 Equipment                                                                                                       |

|          |             | 4.2.1 Equipment                                                                                                       |

|          |             | 4.2.2 AXI UARI 10550 V2.0                                                                                             |

|          | 4.9         | 8                                                                                                                     |

|          | 4.3         | Creating the Base Hardware                                                                                            |

|              |              | 4.3.1 Desired Functionality                                                                                     |

|--------------|--------------|-----------------------------------------------------------------------------------------------------------------|

|              |              | 4.3.2 Integration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 38$                    |

|              | 4.4          | Software Development 42                                                                                         |

|              |              | 4.4.1 Bare-metal configuration                                                                                  |

|              |              | 4.4.2 Xilinx Libraries                                                                                          |

|              |              | 4.4.3 UART550 Hello World                                                                                       |

|              |              | 4.4.4 Interrupts                                                                                                |

| <b>5</b>     | Test         | ing 54                                                                                                          |

| 0            | 5.1          | Overview $\ldots \ldots 54$ |

|              | $5.1 \\ 5.2$ | Procedure for testing                                                                                           |

|              | 0.2          | 5.2.1 Verifying Interrupt Service Routines                                                                      |

|              |              | 5.2.1 Verifying interrupt service routines                                                                      |

|              |              | 5.2.2 Increasing the baud rate                                                                                  |

| 6            | Dise         | sussion 57                                                                                                      |

|              | 6.1          | AXI UART 16550 instead of AXI UART Lite                                                                         |

|              | 6.2          | Implementing UART Feature                                                                                       |

|              | 6.3          | Coronavirus Disease                                                                                             |

|              | 6.4          | Development of Hardware 57                                                                                      |

| 7            | Cor          | clusion 59                                                                                                      |

|              | 7.1          | Result                                                                                                          |

|              | 7.2          | Learning                                                                                                        |

| Δ            | Zed          | Board Tcl Script 64                                                                                             |

| 11           |              | -                                                                                                               |

| В            | Bar          | e-Metal Source Code 75                                                                                          |

|              | B.1          | Simple Transmit/Receive Design                                                                                  |

|              | B.2          | Interrupt Design                                                                                                |

| $\mathbf{C}$ | Spe          | cialization Project VHDL Code 89                                                                                |

|              | C.1          | Transmitter (tUART) $\ldots$ 89                                                                                 |

|              | C.2          | Testbench Transmitter (tb_tUART)                                                                                |

|              | C.3          | Receiver (rUART)                                                                                                |

|              | C.4          | Testbench Receiver (tb_rUART)                                                                                   |

# List of Figures

| $     1.1 \\     1.2 \\     1.3 \\     1.4 \\     1.5   $ | Comparison between M6P and Sentinel-3A                                                                                                              | $     \begin{array}{c}       1 \\       3 \\       4 \\       5     \end{array} $ |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 2.1<br>2.2                                                | Test connection between transmitter design and IPs from Xilinx<br>ILA waveform <i>data_out</i> result from sending character 'A' to the transmitter | 6<br>7                                                                            |

| 3.1<br>3.2<br>3.3<br>3.4                                  | From RGB to hyperspectral [4]                                                                                                                       | 9<br>10<br>11                                                                     |

| 3.5<br>3.6                                                | room to the right, based on the illustration from [7]                                                                                               | 11<br>12<br>12                                                                    |

| $3.7 \\ 3.8$                                              | Sample ordering of HSI cube [10]                                                                                                                    | $12 \\ 13 \\ 14 \\ 15$                                                            |

| 3.9<br>3.10                                               | diagram from $[13]$                                                                                                                                 | 15<br>15                                                                          |

| 3.12                                                      | 3D rendering of HSI BoB V3 [14]                                                                                                                     | 16<br>17<br>18                                                                    |

| $3.14 \\ 3.15$                                            | ZedBoard Development Kit [17]                                                                                                                       | 19<br>19                                                                          |

| 3.17                                                      | SD Card Boot Device Jumper Setting                                                                                                                  | 20<br>21<br>24                                                                    |

| $3.19 \\ 3.20$                                            | Linux Operating System Architecture [20]                                                                                                            | 26                                                                                |

| 3.22                                                      | BSQ order block-wise streaming of HSI cube [21]Cube DMA Core [21]Unpacker example [21]                                                              | 26<br>27<br>27                                                                    |

| $4.1 \\ 4.2 \\ 4.3$                                       | Zynq-7000 Block Diagram                                                                                                                             | 30<br>31<br>32                                                                    |

|                                                           |                                                                                                                                                     |                                                                                   |

| 4.4  | CP2102 USB to UART Bridge                                             | 33 |

|------|-----------------------------------------------------------------------|----|

| 4.5  | Block diagram visualization of the design                             | 34 |

| 4.6  | ZYNQ7 Processing System                                               | 34 |

| 4.7  | Integrated Logic Analyzer IP                                          | 35 |

| 4.8  | AXI UART16550 Configuration                                           | 35 |

| 4.9  | AXI UART16550 Prototyping Design                                      | 36 |

| 4.10 | The connection between the Processing System and the Programmable     |    |

|      | Logic on the Zynq-7000 SoC                                            | 36 |

| 4.11 | The connection between the two UARTs                                  | 37 |

| 4.12 | Address of AXI UART16550 IP                                           | 37 |

| 4.13 | Baseline architecture before implementation of AXI UART 16550         | 38 |

| 4.14 | Baseline architecture after implementation of AXI UART 16550 $\ldots$ | 39 |

| 4.15 | Vivado Result Window Area with Tcl Console highlighted                | 39 |

| 4.16 | Interrupt flow for the design                                         | 49 |

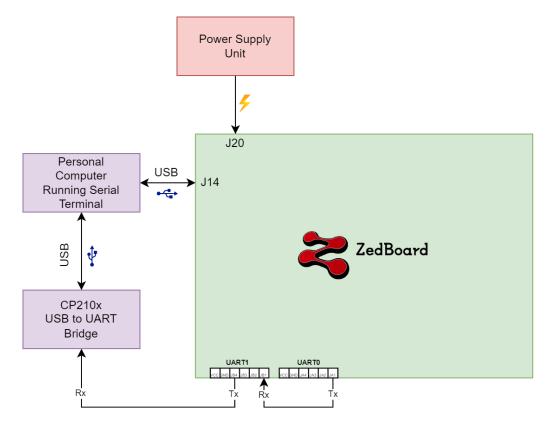

| 5.1  | Block diagram showing connection with ZedBoard                        | 54 |

| -    |                                                                       | -  |

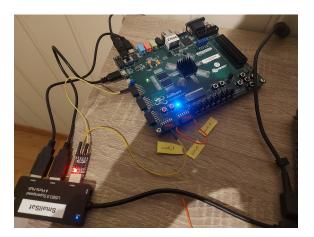

| 5.2  | Physical connection between UART modules and USB-UART bridge          | 55 |

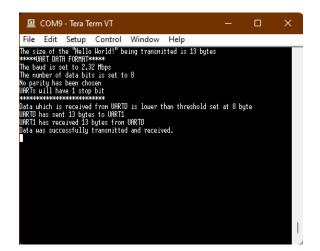

| 5.3  | Serial Terminal Result after Executing Interrupt Application          | 55 |

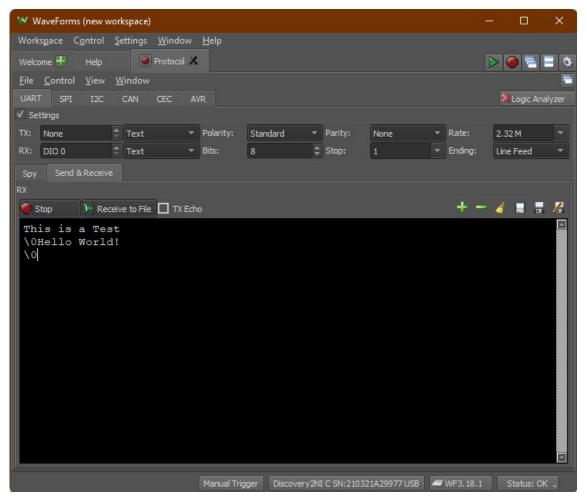

| 5.4  | Receive result from UART1                                             | 56 |

|      |                                                                       |    |

# List of Tables

| 3.1 | Zynq UltraScale+ MPSoC: EV Device Feature Summary [24] | 16 |

|-----|--------------------------------------------------------|----|

| 3.2 | Processing System Boot Mode Selections [25]            | 20 |

## Abbreviations

**LEO** Low Earth Orbit **HYPSO** Hyperspectral Smallsat for Ocean Observation **FPGA** Field-Programmable Gate Array **OPU** OnBoard Processing Unit **PLL** Phase Locked Loop **DDR** Double Data Rate **PS** Processing System **PL** Programmable Logic **UAV** Unmanned Aerial Vehicle **RISC** Reduced Instruction Set Computer **CISC** Complex Instruction Set Computer **RTOS** Real-Time Operating System **CSP** Cubesat Space Protocol **POSIX** Portable Operating System Interface MIO Multiplexed I/O **MPSoC** Multiprocessor System on a Chip **UHF** Ultra High Frequency **KDD** Kernel Device Driver **BSP** Board Support Package **USB** Universal Serial Bus **ESL** Electronic System Level **DMA** Direct Memory Access **UART** Universal Asynchronous Receiver-Transmitter **CCSDS** Consultative Committee for Space Data Systems **NASA** National Aeronautics and Space Administration **BIP** Band Interleaved by Pixel **BSQ** Band Sequential **MM2S** Memory Map to Stream **S2MM** Stream to Memory Map **NTNU** Norwegian University of Science and Technology **SDR** Software Defined Radio **NSSL** NTNU Small Satellite Lab **ROM** Payload Controller **FSBL** First Stage Bootloader **U-Boot** Second Stage Boot Loader FIFO First-In, First-Out **OCM** On-Chip Memory **RTL** Receive Trigger Level **CPU** Central Processing Unit

**RS-422** Recommended Standard 422 **HSI** Hyperspectral Imaging **RGB** Red Green Blue FC Flight Computer **PC** Payload Controller **BoB** Breakout Board **EPS** Electronic Power System **CAN** Controller Area Network SoM System on Memory **ILA** Integrated Logic Analyzer **VIO** Virtual Input/Output **OS** Operating System **ISR** Interrupt Service Routine **AXI** Advanced eXtensible Interface **CLK** Clock **IP** Intellectual Property **PMOD** Peripheral Module Tcl Tool Command Language  $\mathbf{Tx}$  Transmit **Rx** Receive SoC System on Chip **IRQ** Interrupt Request **GIC** General Interrupt Controller

# Chapter 1 Introduction

Thousands of artificial satellites orbit Earth. These satellites have various different purposes, some do collect pictures of the planet to help meteorologists predict the weather and track hurricanes. Some take pictures of other planets, the sun, black holes, dark matter, or faraway galaxies. These pictures assist scientists in better understanding the solar system and universe [26]. The bird's eye view that satellites have allowed for a large collection of data, more quickly than what instruments on the ground would achieve. One of the most important factors with satellites projects is the cost of the launch. NASA's space shuttle had a cost of about \$1.5 billion to launch 27,500 kg to Low Earth Orbit (LEO). Today SpaceX's Falcon 9 announce a cost of \$62 million to launch 22,800 kg to LEO [27]. Small satellites have revolutionized access to space by dramatically reducing the cost of launching and operating a satellite while in space. This has allowed for new opportunities for universities, the commercial sector, and national space agencies [28]. Still, there do exist issues being limited hardware access, shorter lifespan due to rapid orbital decay, and lower transmitter output signal than traditional satellites.

(a) 6U nanosatellite bus M6P (1 - 10 kg) [5] (b) ESA Sentinel-3A (> 500 kg) [29]

Figure 1.1: Comparison between M6P and Sentinel-3A

## 1.1 HYPSO Mission

At the Norwegian University of Science and Technology (NTNU) an organization named NTNU Small Satellite Lab (NSSL) consisting of bachelor-, graduate students, PhDs, and Ph.D. students have created a goal to create a small satellite to be sent to space for observing oceanographic phenomena. The mission is named Hyperspectral Smallsat for Ocean Observation (HYPSO) with the main objective to observe the ocean through a hyperspectral camera. The camera allows for the capture of a vast number of contiguous spectral bands across the electromagnetic spectrum. This is used to be able to discover harmful algae bloom in the Norwegian Sea in order to avoid fish die-off. The launch of the satellite will be in the year 2024. The satellite will be equipped with a hyperspectral- and an RGB camera. By the usage of hyperspectral imaging (HSI), it's possible to investigate bands of light frequencies and focus on designated colors [30].

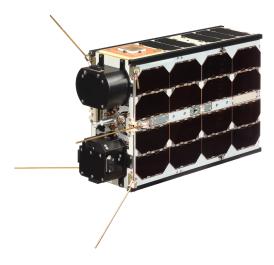

The HYPSO project's satellite will be a CubeSat. The CubeSat's size is measured in cubes, i.e. **Us**, where 1U is 10 cm x 10 cm x 10 cm [31]. The satellite for this project will be 6U provided by NanoAvionics LLC (Limited Liability Company), with dimensions of 340.5 mm x 226.3 mm x 100 mm (LxWxH) [32].

Onboard the satellite, there are effectively two missions going on: the SDRmission (Software Defined Radio) and the HSI-mission (Hyper Spectral Imager). The SDR mission's long-term purpose is to develop Arctic communication infrastructure to enable data retrieval from various sensor nodes and robotic agents [32]. This project is about the HSI- mission, also known as the HYPSO (HYPer-spectral Smallsat for Ocean Observation). The mission will conduct ocean observations, especially gathering hyperspectral data from the ocean's surface with a hyperspectral image and sending the data to Earth [30].

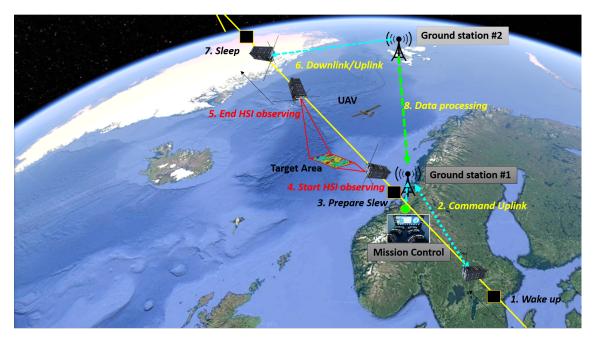

The Figure 1.2 on the next page shows the HYPSO mission's operational concept as well as the stages of a satellite fly-by over the Norwegian Sea. When the satellite is not in use, it goes into sleep mode. When it wakes up, it contacts the ground station located in Trondheim to receive orders, afterwards it gathers hyperspectral images of the ocean and connects to a ground station located in Svalbard to relay the data. It may take many fly-bys before all of the data is relayed, and several ground stations might be employed as data receiving stations. An unmanned aerial vehicle (UAV) travels over the same region as the satellite to gather reference photos that may be utilized to improve algal identification and atmospheric correction algorithms.

Figure 1.2: Different stages of the mission process HYPSO-1 [1]

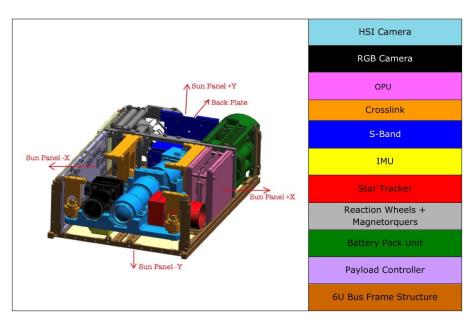

The satellite shown in Figure 1.3 will include a star tracker and a Red, Green, Blue (RGB) camera which does point at the direction of the Earth, which are used to assist in determining the spacecraft's orientation, while the orientation of the satellite is controlled by reaction wheels and magnetorquers. The mission data from the HSI is to be processed by the OPU (Onboard Processing Unit).

Figure 1.3: HYPSO-1 CubeSat architecture, inspired from [2]

Be aware that Figure 1.3 does show the CubeSat architecture of the HYPSO-1 system, and not the HYPSO-2. This does not include the SDR module, which is to be integrated into HYPSO-2 beside the OPU module.

## 1.2 Issue

One main problem with hyperspectral images is that they can be up to 140 megabytes [33]. As a result, the transfer time between the different modules onboard the satellite is extensive. Thus the need to reduce the file size is essential. This is done through the usage of a compression algorithm for high-speed computation. In order to achieve this, the team has decided to use a Multiprocessor System on a Chip (MP-SoC) with a Field-Programmable Gate Array (FPGA) built inside. The HYPSO-2 mission will be using a Xilinx Zynq UltraScale+ MPSoC for the onboard processing unit (OPU) instead of the previous board which was the PicoZed 7030 using Zynq-7000 All Programmable System on Chip.

(a) UltraZed-EV SOM Top View [11]

(b) PicoZed 7030 SOM Front View [34]

Figure 1.4: Different Processing Boards

Implementing the compression algorithm on the satellite it will allow for faster download time. From this issue, a group named the Consultative Committee for Space Data Systems has been able to develop the standard CCSDS-123 for compression of hyperspectral images. A previous member of the small satellite team implemented the CCSDS123 onto the FPGA for his master thesis to be used on the OPU in the HYPSO satellite [21]. This thesis will take into use what has already been developed, by integrating the technical standard Recommended Standard (RS-422) into the system.

## 1.3 Goal

In HYPSO-1's system architecture, the spacecraft does its data transfer through the Controller Area Network (CAN) serial communication protocol. The specialization project done in the previous semester was an introduction to the work to be done in this master thesis. The work consisted of creating a UART protocol from scratch [35]. This project was not integrated into the OPU-system being that it does not interface with the processing system, still, it is a good document to read to become familiar with the protocol itself, making this paper more understandable. The goal of this project is to implement the AXI UART 16550 v2.0 Intellectual Property [22] into the OPU to allow for faster data transfer between the OPU and Payload Controller (PC).

Figure 1.5: HYPSO-2 Satellite Architecture [3]

#### 1.3.1 Thesis structure

The prototyping, implementation, integration, and testing of UART capabilities within the Onboard Processing Unit will be covered in this paper.

- Chapter 1 Introduction

- Chapter 2 Specialization Project

- Chapter 3 Background

- Chapter 4 Implementation

- Chapter 5 Testing

- Chapter 5 Discussion

- Chapter 6 Conclusion

The first part consisting of the first 3 chapters will introduce the problem, the current satellite system, and relevant theory. The outcomes of the implementation, integration, and testing solutions will be presented in the second section. The last section will go through discussion and conclude whether or not the problem has been solved.

# Chapter 2 Specialization Project

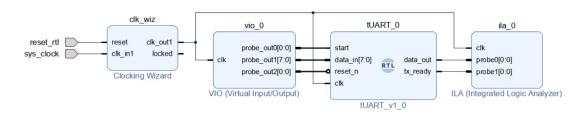

For the specialization project, the task was to implement and integrate a UART communication protocol to the OPU system on the Zynq UltraScale+ MPSoC EV. The RTL code was fully written in VHDL, the goal of the module was to be able to transmit and also receive data from the external source Payload Controller through an RS-422 standard. The baud rate was expected to be between 3 and 4 Mbps. Both the transmitter and receiver hardware design can be found in Appendix C.1 and Appendix C.3 respectively as well as their test benches C.2 and C.4.

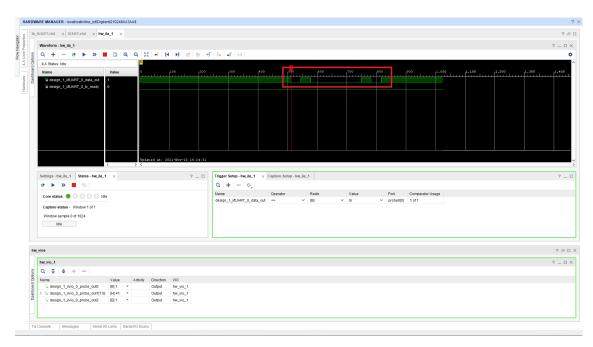

Both the transmitter and the receiver part of the design were tested in the Vivado simulation window, and also on the Xilinx Zynq-7000 All Programmable (AP) SoC mounted on the ZedBoard development kit on hardware i.e. sending data from the personal computer to the Zynq-7000 in real-time through the usage of the Xilinx VIO (Virtual Input/Output) IP [36] also using the Xilinx ILA (Integrated Logic Analyzer) IP [37] to examine the wave diagram.

## 2.1 Verification of Design

As previously stated, the hardware verification of the design was performed in Vivado's IP Integrator window, using both ILA and VIO IPs to test both the transmitter and receiver functionality of the UART design.

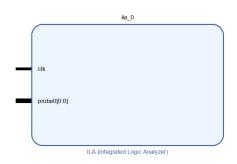

Figure 2.1: Test connection between transmitter design and IPs from Xilinx

## 2.1.1 Integrated Logic Analyzer (ILA)

The Integrated Logic Analyzer (ILA) IP core is a logic analyzer core that may be used to monitor a design's internal signals. Many sophisticated capabilities of current logic analyzers, such as boolean trigger equations and edge transition triggers, are included in the ILA core [37].

### 2.1.2 Virtual Input/Output (VIO)

The LogiCORE IP Virtual Input/Output (VIO) core is a programmable core that can monitor and control internal FPGA signals in real-time. To interact with the FPGA design, the number and width of the input and output ports may be customized [36].

#### 2.1.3 Results from the design

For the verification of the design, there was made a test bench which gave the transmitter module information about sending the ASCII information "A L G" in the form of a hex value which is 0x41, 0x4C, 0x47 respectively. This converted to binary is the following:

- A  $\rightarrow$  0100 0001

- L  $\rightarrow$  0100 1100

- $G \rightarrow 0100 \ 0111$

Sending the signal 'A' onto the chip i.e. 0x41 the output data should become 0100 0001. This is confirmed by observing the ILA waveform as can be seen in Figure 2.2

Figure 2.2: ILA waveform  $data_out$  result from sending character 'A' to the transmitter

The same test procedure was done to the receiver part of the project with a satisfactory result. Being that the design is purely hardware and not interconnecting with software it was decided to not integrate this into the OPU design. Still, the design of the UART has allowed for an easier understanding of the protocol, please do look into "Exploration and implementation of communication protocols for satellite payload systems" [38] and "UART Design Document HYPSO-RP-003" [35] for more detail.

# Chapter 3 Background

The goal of this chapter is to present the current satellite system while also providing essential background material such as hyperspectral imaging to assist the reader comprehend the methods used. How the AXI UART 16550 v2.0 LogiCORE IP works, the satellite platform itself and also the recent replacement of the PicoZed, UltraZed-EV SOM. Also the Linux kernel, drivers and memory in Linux is described. Also included is the FPGA accelerator that was previously constructed by students as part of the HYPSO project.

## 3.1 Hyperspectral Imaging

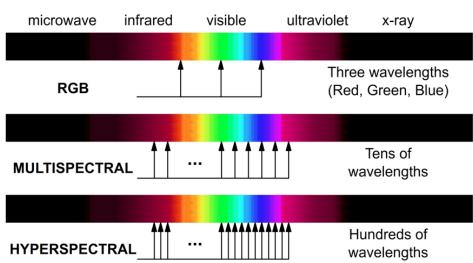

Hyperspectral imaging makes use of data from hundreds of wavelengths across the electromagnetic spectrum, whereas a standard RGB camera, collects single frames with information about red-green-blue. It is designed to determine the spectrum of each pixel in an image of a scene in order to detect objects, identify materials, or identify processes.

#### **ELECTROMAGNETIC SPECTRUM**

Figure 3.1: From RGB to hyperspectral [4]

## 3.2 HYPSO 6U Nanosatellite bus M6P

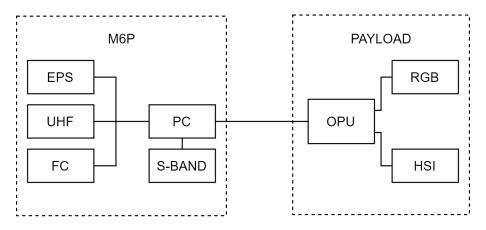

The HYPSO nanosatellite is a sophisticated assembly of parts and software from multiple student projects in collaboration with NanoAvionics. NanoAvionics develops nanosatellite casings that integrate features such as a Flight Computer (FC), a Payload Controller (PC), and intercommunication.

NSSL is developing a payload that will be integrated into the nanosatellite. The Figure 3.2 depicts the NanoAvionics satellite shell. The CSP (Cubesat Space Protocol) protocol is used by all systems and subsystems.

Figure 3.2: The 6U nanosatellite bus M6P [5]

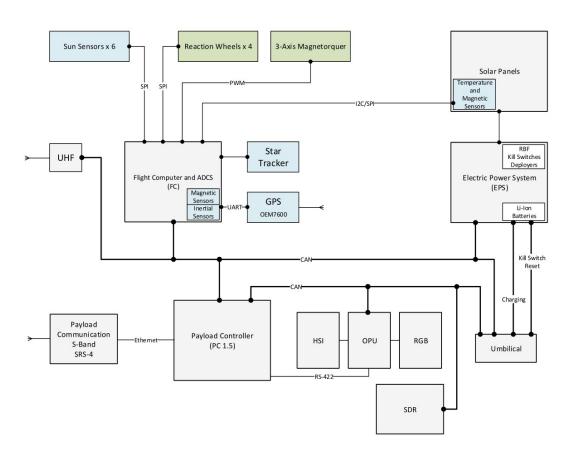

The implementation of CSP is written in C and has been adapted to Free Real-Time Operating System (RTOS), Portable Operating System Interface (POSIX), and pthreads-based operating systems like Linux [39]. CSP has a service-oriented network structure divided into two segments: ground and space. The space segment is represented in Figure 1.5, while the ground segment is represented by the ground station interacting with the satellite. A CSP node is operated on each module in the network, and each node can execute several services, as well as receive different commands and data. CSP packets can be used to communicate freely across the modules.

CSP packets are packed and transferred between segments through the CAN bus or networks equipped with the Ultra High Frequency (UHF) module. The platform is equipped with two CAN busses, one for payloads and the other for satellite operation systems. The PC (Payload Controller) distributes CSP packets across CAN buses and buffers mission data from payloads before sending it to the S-band, which then transfers data to the ground station. The FC (Flight Computer) is in charge of logging telemetry data as well as attitude determination and control [40]. The satellite is powered by the EPS (Electrical Power System). The power source is Lithium-Ion batteries, which are charged by solar panels.

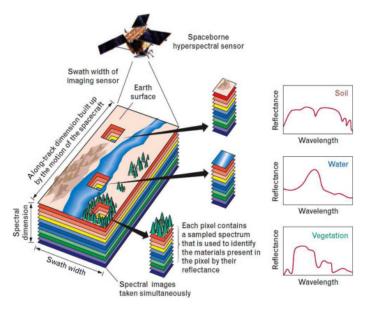

## 3.3 HSI as a Remote Sensing Tool

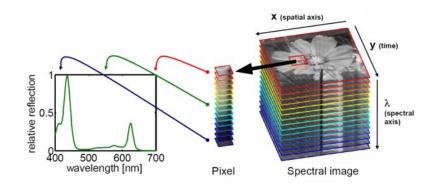

A hyperspectral sensor collects information as a set of images. A spectral band, also known as a wavelength range, corresponds to each image in the electromagnetic spectrum. These images are then combined into a three-dimensional (x, y,  $\lambda$ ) hyperspectral data cube for processing and analysis, where x and y represent two spatial dimensions of the scene, and  $\lambda$  represents the spectral dimension [41].

Figure 3.3: HSI concept in the remote sensing applicative context [6]

Through the use of spectral information, objects and materials can be detected with a much higher degree of precision than with a conventional red-green-blue (RGB) camera.

## 3.4 Remote Sensing Techniques

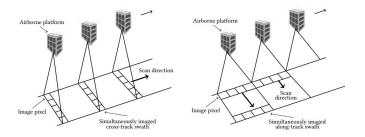

The HSI-cube can be obtained using different techniques. The push-broom and whiskbroom scanning methods are the two most common methods for pointing, as shown in Figure 3.4.

Figure 3.4: The different scanning techniques. Pushbroom on the left and whiskbroom to the right, based on the illustration from [7]

In order to accomplish its mission, HYPSO uses push-broom scanning. The image to the left in Figure 3.4 shows the camera scanning a line of light as it points

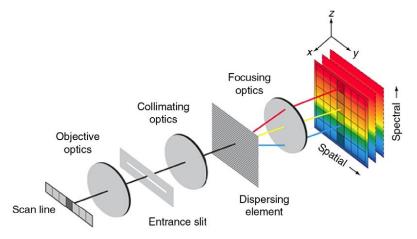

downwards. Using this line of light, the light is dispersed into several bands, thus creating a frame as shown in Figure 3.5. These frames end up being placed on top of each other, resulting in the HSI cube shown in Figure 3.6.

Figure 3.5: Optical chain of a common push-broom imaging spectrometer [8].

Figure 3.6: Hyperspectral datacube [9]

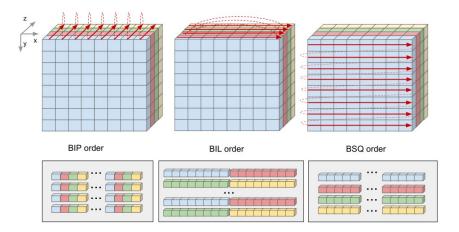

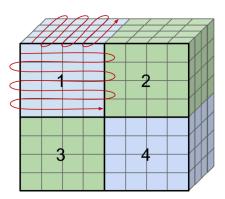

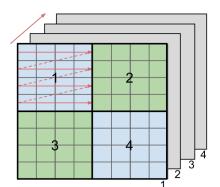

There are three types of ways to store hyperspectral images. Band Interleaved by Line (BIL), Band Interleaved by Pixel (BIP), and Band Sequential (BSQ) as presented in Figure 3.7

Figure 3.7: Sample ordering of HSI cube [10]

BIL sequentially stores pixels from the 'x' spatial direction for each band in each row, while the 'y' spatial direction represents the rows. The 'y' spatial direction likewise represents the rows in BIP, but inside the rows, all the bands for one pixel in the 'x' spatial direction are positioned sequentially, followed by the same for the following pixel. BSQ differs from the other two in that it represents all of the pixels in the 'x' spatial direction from one band in the columns. The 'y' spatial direction is displayed in successive rows for one band, followed by the next band [10].

## 3.5 Payload

The payload is comprised of the HSI, RGB cameras, and OPU.

- 1. **Hyperspectral camera** The HSI camera can be located in the center of the nanosatellite. It is easily identified by its size and slanted inclination as shown in Figure 1.3.

- 2. **RGB camera** The RGB camera is positioned on the left side of the HSI camera see Figure 1.3. Its function will be to capture the same region as the HSI camera in order to augment the hyperspectral image.

### 3.5.1 Onboard processing unit

#### Overview

The OPU system will ideally consist of a Zynq UltraScale+ MPSoC EV and a Breakout Board (BoB) connected together thus referred to as UltraBoB.

Figure 3.8: UltraZed-EV SOM Angle View [11]

This module collects and processes data from sensors mounted onboard the payload, primarily the hyperspectral imaging sensor and RGB camera. Most of the modules on the spacecraft are off-the-shelf products prepared by the Aviation & Aerospace industry NanoAvionics, except for the payload consisting of the OPU, HSI, and RGB cameras. These modules are the interest area for the other work fields in the HYPSO research project.

The HYPSO-1 architecture mostly used Controller Area Network (CAN) communication between its modules using the CubeSatProtocol (CSP) both for transmitting instruction data between the modules, and also to transmit payload data.

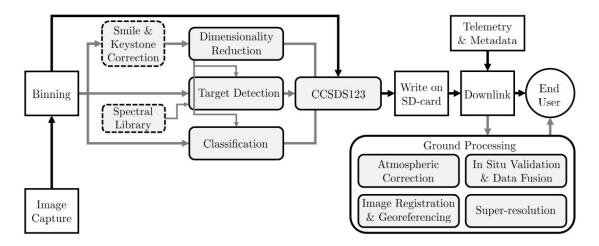

Figure 3.9: HYPSO-1 Onboard image processing pipelines [12]

The suggested onboard image processing pipelines are depicted as a block diagram, shown in Figure 3.9. The hyperspectral pictures are taken, binned, processed at a predetermined level, saved on an SD card, and downlinked together with telemetry and metadata. Depending on the data product selected, additional ground-based processing and fine-tuning might be performed before dissemination to end users. The black lines represent the simplest onboard processing pipeline, while the gray arrows provide alternate paths for customised data products [12].

The HYPSO-2 system is designed to optimize system performance by integrating Ethernet communication and adding RS-422 serial communication between OPU and PC see Figure 1.5, which will be the major focus of this thesis.

Figure 3.10: Relations between the subsystems of the HYPSO-2 satellite. Adapted diagram from [13]

The OPU is powered by the Electronic Power System (EPS), which may be managed via the Payload Controller (PC), allowing for power reset if the OPU ceases to react.

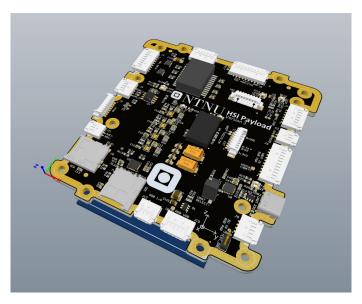

#### Printed Circuit Board - UltraBoB

The UltraBoB will consist of an UltraZed-EV SoM and the BoB to interface mechanically, electrically, and thermally between the M6P satellite platform and payload instruments and UltraZed-EV SoM. The UltraZed-EV is manufactured by Avnet and consists of a Xilinx XCZU7EV-1FBVB900 commonly referred to as Zynq UltraScale+ MPSoC a Dual QSPI Flash 64MB, 8GB, x8 eMMC Flash, 4GB DDR4 SDRAM PS (Processing System) and 1GB DDR4 SDRAM PL (Programmable Logic), USB (Universal Serial Bus) 2.0 and Gigabit Ethernet PHY (Physical Layer) interface controller [24].

| Model   | IOBs  | LUTs   | ${ m FF}$ | BRAMs | URAM | DSPs |

|---------|-------|--------|-----------|-------|------|------|

| XCZU7EV | 28800 | 230400 | 12720     | 312   | 96   | 1728 |

Table 3.1: Zynq UltraScale+ MPSoC: EV Device Feature Summary [24]

Interface connections, SD-Card readers, voltage regulators, and logic level shifters are all part of the BoB (Break out Board). The team's PCB engineer's 3D depiction of the BoB V3 may be seen in Figure 3.11.

Figure 3.11: 3D rendering of HSI BoB V3 [14]

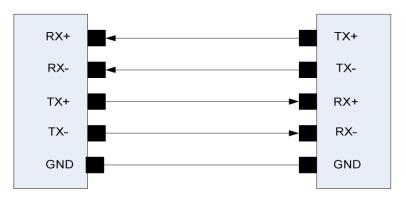

## 3.6 RS-422

The Electronic Industries Alliance developed RS-422, a technical standard that describes the electrical properties of a digital signaling circuit. Data transmission speeds of up to 10 Mbit/s are possible with RS-422 systems [42]. The RS-422 standard defines differential signaling, with each data line coupled with its own return line. The mark and spacing are determined by the voltage differential between these two lines. The advantage of employing a differential signal over a single ended signal is that it is more noise resistant, allowing for longer cable lengths. The signals have a voltage range of +/-2.0V [15].

Figure 3.12: Typical RS-422 Interconnect [15]

## 3.7 Field Programmable Gate Array

A Field Programmable Gate Array (FPGA) is an integrated circuit with programmable logic blocks. This enables low-level programming of a chip after it has been manufactured. Unlike a CPU, the FPGA's power rests in its capacity to do many distinct particular jobs simultaneously. A bitstream file may be used to simply update the logic of the FPGA. As a result of its flexibility to be reconfigured while in use, FP-GAs are a popular choice for sectors such as aerospace and nanosatellites. FPGA logic may be designed using Hardware Description Languages (HDLs) such as Verilog and VHDL [43].

## 3.7.1 UltraZed EV SoM

The UltraZed is a System on Module (SoM) based on Xilinx's Zynq UltraScale+Multiprocessor System on a Chip (MPSoC). As seen in Figure 3.8.

The MPSoC utilizes four ARM Cortex-A53 CPUs in conjunction with a Field Programmable Gate Array (FPGA). The ARM processors employ the Reduced Instruction Set Computer (RISC) architecture, which, as the name indicates, is less complex than the Complex Instruction Set Computer (CISC). It reduces the number of instructions required per job while increasing the number of cycles required for each instruction. It is designed to be more efficient by employing fewer instruction sets and simpler instructions, resulting in reduced energy consumption [44].

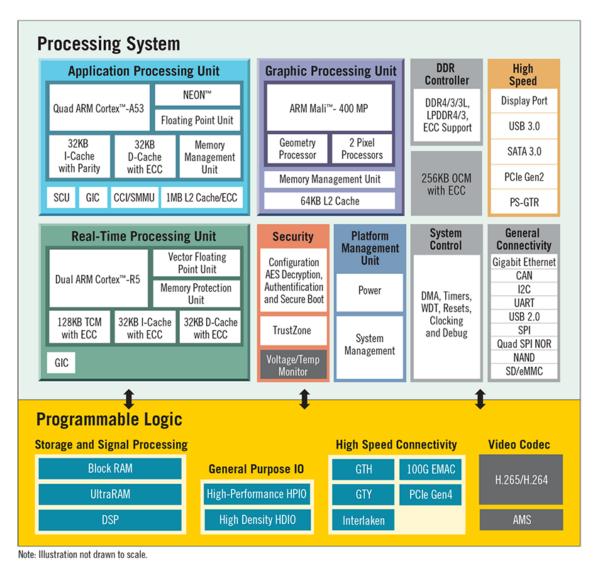

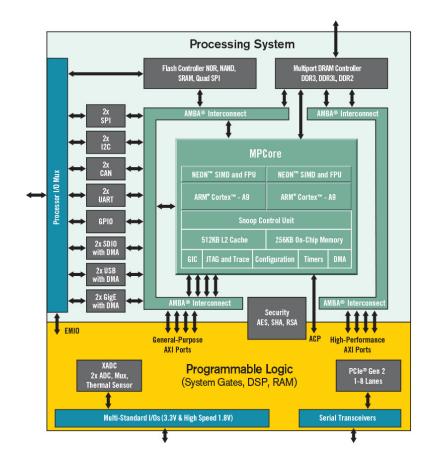

The Zynq MPSoC's advantage stems from its utilization of both CPUs and an FPGA. The FPGA enables specialized low-level programming and parallel data processing. The Zynq UltraScale+ MPSoC is divided into two major components: the Programmable Logic (PL) and the Processing System (PS). The PL denotes the FPGA setup and connectivity with the PS. The PS denotes the software that runs on the processors [45]. Based on the work to be completed in this thesis, both the PL and PS are dependent on each other for the UltraZed to function accordingly. The Figure 3.13 depicts how these components interact.

Figure 3.13: Zynq UltraScale+ EV Block Diagram [16]

The Vivado Design Suite [46] is used for the development and setup of the PL in this project. The PS is coded in programming languages like C. It is powered by an Embedded Linux OS created with PetaLinux [47].

### 3.7.2 Zynq-7000

The ZedBoard equipped with the Zynq-7000 was utilized instead of the UltraZed-EV during development. This is due to COVID-19's influence on electronic supply chains, which has resulted in a longer manufacturing lead time. If an UltraZed-EV board fails, consumers may have to wait multiple months before getting a replacement. This is detailed in further detail in subsection 4.2.1.

Figure 3.14: ZedBoard Development Kit [17]

#### Starting up Zynq

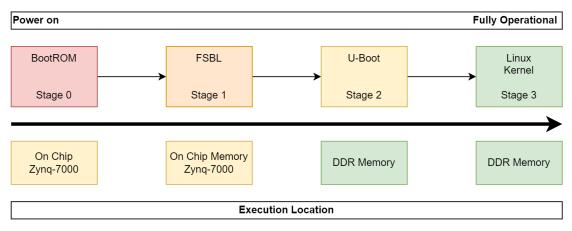

The Zynq features on-chip memory (OCM), which is used for booting. The memory is split into two parts: Read-only memory (ROM) and Random-access memory (RAM), having 128 KB and 256 KB of memory, respectively [19]. The steps of the booting procedure are depicted in Figure 3.15.

Figure 3.15: Zynq-7000 Boot Sequence [18]

The first stage begins when the chip receives a power-on signal, which occurs when the board's power switch is turned on or when the system reboots. The first thing this step does is read the boot mode signals to determine where the boot source should be loaded from, which can be JTAG, QSPI, flash, or SD card [19].

|               | MIO[6]       | MIO[5]       | MIO[4]       | MIO[3]       | MIO[2]       |  |  |

|---------------|--------------|--------------|--------------|--------------|--------------|--|--|

| Xilinx TRM→   | Boot_Mode[4] | Boot_Mode[0] | Boot_Mode[2] | Boot_Mode[1] | Boot_Mode[3] |  |  |

|               |              |              |              |              |              |  |  |

| Cascaded      |              |              |              |              | 0            |  |  |

| JTAG          |              |              |              |              | 0            |  |  |

| Independent   |              |              |              |              | 1            |  |  |

| JTAĠ          |              |              |              |              | I            |  |  |

|               |              | Boot D       | evices       |              |              |  |  |

| JTAG          |              | 0            | 0            | 0            |              |  |  |

| Quad-SPI      |              | 1            | 0            | 0            |              |  |  |

| SD Card       |              | 1            | 1            | 0            |              |  |  |

| PLL Mode      |              |              |              |              |              |  |  |

| PLL Used      | 0            |              |              |              |              |  |  |

| PLL           | 1            |              |              |              |              |  |  |

| Bypassed      | I            |              |              |              |              |  |  |

| Bank Voltages |              |              |              |              |              |  |  |

|               | MIO Bank 500 |              | 3.3V         |              |              |  |  |

|               | MIO Bank 501 |              | 1.8V         |              |              |  |  |

Table 3.2: Processing System Boot Mode Selections [25]

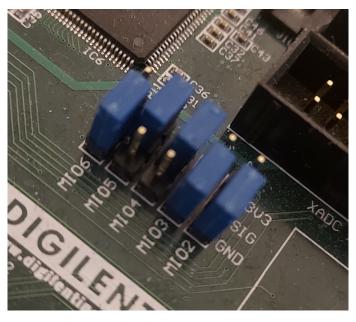

Jumpers on pin MIO2 to MIO6 on the board can be used to set different boot mode signals. Once the boot mode has been selected, the boot ROM will read the boot header, verify the image, and load the FSBL image from the selected interface to the OCM using the configuration settings [19].

Figure 3.16: SD Card Boot Device Jumper Setting

The function of the First-Stage Boot Loader (FSBL) is the following: load the Linux U-Boot image and execute from non-volatile memory to DDR, initialize the clock phase-locked loop (PLL), initialize the DDR controller, configure the Multiplexed I/O (MIO) and also configures the FPGA with the hardware bitstream (if it exists) [48]. If any user applications are present, the U-boot will run them. The kernel image is then loaded into memory as a compressed image of the Operating System (OS) and decompressed. In addition, the kernel includes a device tree and a ram disk file. The kernel checks the device tree to see what hardware is available, and the ram disk aids in the loading of the root file system [49].

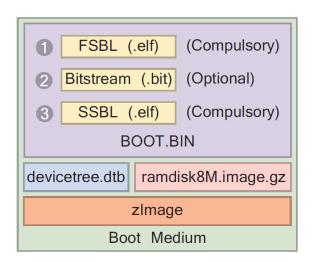

The files necessary for the Linux boot procedure are shown in Figure 3.17. The Zynq boot image file named **BOOT.bin**. It consists of two mandatory files, the FSBL and the SSBL (U-boot) produced by bootgen [48], as well as an optional FPGA bitstream file. The FSBL and SSBL files contain the final stages of the bootloader, which is used to load Linux on the device, as their names imply. The bitstream is the configuration file for the Zynq-7000 AP device's programmable logic. Lastly, the device tree, ramdisk, and compressed Linux kernel are added to an image file known as **image.ub**

Figure 3.17: Required files for Zynq Linux boot process [19]

## 3.7.3 Board Support Package

A domain or board support package (BSP) is a collection of software drivers and, if desired, the operating system on which the application is built. It's the support code for a certain hardware platform or board that aids in basic startup and allows software programs to operate on top of it. One may use the domain to run numerous apps. A domain is associated with a single platform processor [50].

## 3.8 Tools

Developing embedded systems necessitates the use of software to design and program the various layers of the system. Three separate tools are utilized in this project:

- 1. Vivado Design Suite (Hardware Development)

- 2. Vitis (Software Development)

- 3. PetaLinux (Deploying Embedded Linux)

## 3.8.1 Vivado Design Suite

Vivado, which was announced in April 2012 [51], is an integrated design environment (IDE) with system-to-IC level capabilities built on a single scalable data model and a common debug environment. Vivado comprises electronic system level (ESL) design tools for synthesizing and testing C-based algorithmic IP; standards-based packaging of both algorithmic and RTL IP for reuse; standards-based IP stitching and system integration of all types of system building blocks; and block and system verification [52].

#### IP Integrator

The Vivado IP integrator tool allows the user to develop sophisticated system designs on a design canvas by instantiating and interconnecting IP from the Vivado IP catalog. Designs may be created interactively using the IP integrator canvas GUI or automatically via a Tcl programming interface [53].

#### Tcl Programming Language

Tcl has commands for reading and writing files to the local file system. This allows the user to build folders dynamically, launch FPGA design projects, add files to projects, and perform synthesis and implementation. Tcl can also be used to implement new design techniques or to work around current challenges, such as inserting and removing design objects or changing attributes as needed [54].

#### Developing Hardware Files

Vivado will produce hardware files after the design is complete. These are two files: a bitstream (.bit) and a hardware design file (.xsa). These two files may then be utilized in software development tools like Vitis and embedded Linux systems like PetaLinux. The bitstream describes an FPGA's logic, whereas the hardware definition file provides information on the various IPs, such as addresses and settings.

## 3.8.2 Vitis

Vitis is a Xilinx embedded programming IDE that integrates with the open-source software Eclipse [55]. The software provides the user with a high-level coding GUI, allowing them to write in either C or C++ if object-oriented programming (OOP) is preferred. Vitis makes use of hardware files provided by the Vivado Design Suite. Everything needed to design and deploy on a Xilinx board is included in the program.

### 3.8.3 PetaLinux

PetaLinux is a toolchain that includes everything needed to modify, produce, and deploy Embedded Linux solutions on Xilinx processing systems. It also allows users to customize the boot loader, Linux kernel, or Linux applications. The OPU's operating system is an Embedded Linux OS created with the Xilinx tool Petalinux [47].

# 3.9 Operating Systems

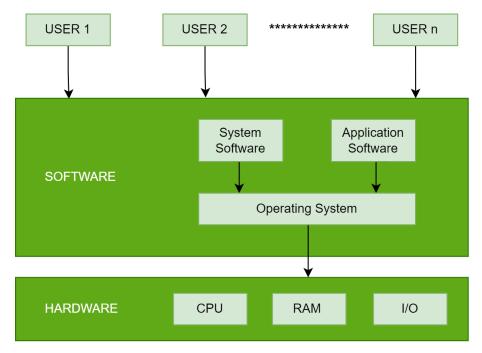

An operating system is a program that governs the execution of applications and serves as an interface between the computer user and the computer hardware [56].

All of the software and hardware on a computer are managed by the operating system (OS). It handles input and output, as well as regulates peripheral devices.

Several computer applications are usually operating at the same time, and they all require access to the computer's central processing unit (CPU), memory, and storage. All of this is coordinated by the operating system to ensure that each software receives the resources it requires.

Figure 3.18: Overview of an Operating System

Open source Linux-based operating systems are a common choice for embedded systems. In comparison to commercial operating systems, open-source operating systems are more configurable and adaptable.

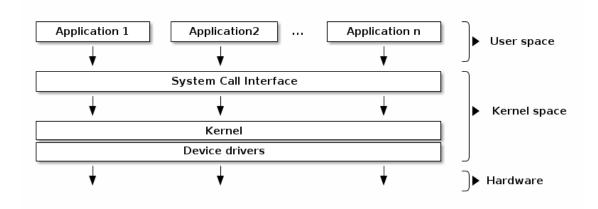

The Linux kernel is the core of the Linux operating system. The kernel has access to all of the associated resources and distributes them as the user applications request [43].

# 3.9.1 Embedded Linux

The OPU's operating system is an Embedded Linux OS created with the Xilinx tool Petalinux as mentioned in subsection 3.8.3. The OS on the OPU is designed to operate on Xilinx processors and perform certain tasks with limited features. It is accessed via a command line, where the user may browse a file system using commands. Memory in Linux is divided into two halves shown in Figure 3.19 user space and kernel space where in user space the user applications are executed and in kernel space kernel code is being executed. Usually, the kernel space has complete access to hardware and system resources, whereas user space has limited access to some of the kernel functions through system calls [49].

Figure 3.19: Linux Operating System Architecture [20]

#### Kernel Device Drivers

In Linux, some system functions are only accessed through the kernel space. In order to access these, the Linux developer can use the Kernel Device Drivers (KDD). It is possible to develop a custom kernel driver in the event of missing functionality, which means there is no supported kernel driver for a certain task. These are known as loadable kernel modules (LKMs), and they are written in C-code in the same way as user applications are. The LKM differs from executables in that it utilizes kernel libraries and is built in a different way [43].

#### Startup and Exit of LKM

Another difference between the LKM and an executable is the method they're developed. A *main()* function is used by an executable to run the program. However, an LKM utilizes two functions: *init* and *exit*. Upon loading the LKM the *init* function starts. Initializing, creating devices, allocating memory, and setting up hardware are all common tasks in this function. Whenever the LKM is unloaded, the exit function is called. Unloading an LKM is uncommon because it disables hardware and removes devices [43].

#### Virtual Memory

The concept of virtual memory is that the program sees a block of memory of a specific size. This memory can be used by the program in any way it sees fit. The memory block is virtual in the sense that it is made up of many pieces. Some of it may be stored in the computer's main memory, while others may be stored on a disk.

# 3.9.2 Cube DMA

The Cube DMA core is an FPGA core that specializes in Direct Memory Access (DMA) of cube data, and it employs two standard approaches for arranging picture data for multiband images.

- **BIP** Band Interleaved by Pixel

- **BSQ** Band Sequential

The Cube DMA is made to read bit-depths that aren't byte multiples and aren't stored with padding. It is possible to read a cube block-by-block, which implies that if the accelerator requires data to be streamed in blocks, one block is streamed completely before the next. The only restriction is that the block sizes must be multiples of two [21].

As mentioned in the Remote Sensing Techniques section 3.4 Figure 3.26 illustrates the method in which BIP and BSQ cubes are streamed from memory using a four-block cube. The order in which the pixels are read is shown by the red lines. The spatial dimensions of width and height are spatial, whereas the spectral dimension is depth.

Figure 3.20: BIP order block-wise streaming of HSI cube [21]

Figure 3.21: BSQ order block-wise streaming of HSI cube [21]

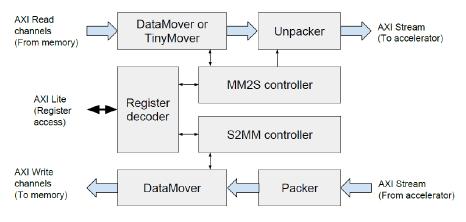

Figure 3.22 shows a block diagram of the Cube DMA. It is made up of two separate channels: Memory Map to Stream (MM2S) and Stream to Memory Map (S2MM). The MM2S gets data from memory and streams it into an accelerator, whereas the S2MM works in the same manner just the opposite. Both channels are configured using a common register interface.

Figure 3.22: Cube DMA Core [21]

The S2MM channel has three components: a packer, a datamover, and a controller. The packer gets data from the accelerator and converts it to the proper word size before sending it to the datamover. The datamover then writes the data to memory in a sequential manner via the AXI bus.

Similarly the MM2S channel also consists of three parts: datamover/tinymover, unpacker, and controller. The datamover/tinymover is in charge of reading from memory directly over the AXI bus. The datamover is a Xilinx IP [57] used for BIP transfers in this architecture, whereas the tinymover is developed by the Cube DMA core designer and used for BSQ transfers.

The unpacker receives the lines fetched from memory through the datamover or tinymover depending on whether it is a BIP- or BSQ transfer. The unpacker aligns the data and adjusts the word sizes. Figure 3.23 depicts the shifting and placement of a 64-bit word of unaligned 12-bit data from memory into four 12-bit sample words. Figure 3.28 shows how a 64-bit word of unaligned 12-bit data from memory is shifted and placed into words containing four 12-bit samples.

Figure 3.23: Unpacker example [21]

During the transfer, the controller handles the datamover and unpacker, as well as providing a control stream that an accelerator may require. The control stream contains information such as whether a sample is the final pixel in a block, whether it is in the last column, and if it is in the last row [21].

# Chapter 4 Implementation

# 4.1 Overview

There were various working phases involved in completing this project. First, it was necessary to study how the present system operates, particularly the aspects pertaining to data transfer functions. Then it was necessary to identify and design solutions to the technological challenges. Learning a new series of tools, Linux OS, and also programming languages, as well as strengthening partially known programming knowledge, were all part of the process. Interactions with the other developers and participants in the HYPSO project were also required to ensure that the product is properly integrated with the rest of the system.

# 4.2 System Analysis

This project required a considerable amount of research. The research began with the goal of better understanding the present system and learning how a Zynq-7000 SoC operates. Various tutorials and forums/servers were utilized to master the tools Vivado and Vitis, as well as the hardware design flow. The following web resources were really informative:

- Edaboard.com

- Reconfigurable Embedded Systems with Xilinx Zynq APSoC

- Udemy FPGA Courses

Reading theses from past HYPSO students helped with the comprehension of the OPU system.

# 4.2.1 Equipment

In addition to the equipment stated in the preceding chapter, the research and prototyping included the use of measurement devices and a prototype board other than the UltraZed board. The following equipment was used:

- ZedBoard Development kit using the Zynq-7000 All Programmable SoC.

- $\bullet$  Analog Discovery 2 USB oscilloscope, logic analyzer, and multi-function instrument

#### **COVID-19** Impact on Electronics Supply Chain

The worldwide supply chain has been greatly impacted by the COVID-19 outbreak. Multiple nationwide lockdowns continue to stall or even halt the movement of raw materials and completed goods, causing manufacturers to suffer [58].

As a result, it was determined that electronics experiments should be carried out on the ZedBoard rather than the UltraZed. This is due to the fact that SmallSatLab has more ZedBoards than UltraZeds. If something goes wrong with the board and causes it to malfunction, it is preferable that it happen to the ZedBoard rather than the UltraZed. The Zynq-7000 and Zynq UltraScale+ MPSoC families share portions of the same architecture, making design compatibility simple.

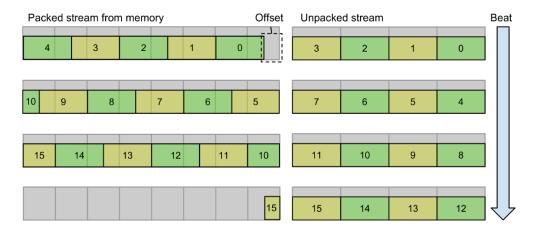

Figure 4.1: Zynq-7000 Block Diagram

# 4.2.2 AXI UART 16550 v2.0

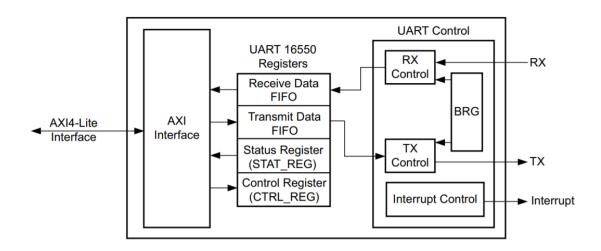

The AXI UART 16550 core is capable to perform parallel-to-serial conversion on characters received from the AXI master. The AXI UART 16550 is capable of transmitting and receiving 8, 7, 6, or 5-bit characters, with 2 or 1 stop bits and odd, even, or no parity. The AXI UART 16550 can transmit and receive independently, making it full-duplex [22]. The internal registers in the core keep track of its status in the specified state. Receiver, transmitter, and modem control interruptions can all be signaled which is explained in more detail in subsection 4.4.4

Figure 4.2: The AXI UART 16550 core's top-level block diagram [22]

#### FIFOs

The First-In, First-Out (FIFO) buffer is intended to increase communication performance; however, if it is configured wrong, communication performance may suffer. The AXI UART16550 is equipped with separate, 16-character-length transmit and receive FIFOs, as shown in Figure 4.2. The software can be used to enable or disable FIFOs which is mentioned further in the paper section regarding the setup of the UART instances 4.4.4.

With a wide receive FIFO, such as the one found in the 16550, the CPU can read all of the data for each receive interrupt at once, saving CPU resources by not having to read data continuously or also known as polling [23].

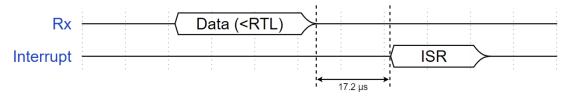

A Receive Trigger Level (RTL) can be specified in the receive FIFO, indicating that the UART will send an interrupt if the quantity of received data surpasses a certain threshold. The AXI UART 16550 supports the following FIFO trigger levels: 1, 4, 8 and 14 bytes of data [22].

It's worth noting that the highest threshold is 14 bytes rather than the FIFO's maximum capacity of 16 bytes. This is to avoid overflow [23].

More about this functionality, and how it is used is explained in subsection 4.4.4 When selecting a high FIFO threshold, keep in mind the following question: when will the UART produce an interrupt if the quantity of data received hasn't met the RTL? The UART receive timeout becomes important at this point. If the data received falls short of the RTL, the UART will wait the time required to send four bytes before issuing an interrupt [23].

Consider the scenario below as an illustration of how long this 4 byte may be. The following configuration has been chosen:

- 2.32 Mbps baud rate

- 8 data bits

- No parity bit

- 1 start bit

- 1 stop bit

Each byte requires the transmission of a start bit, eight data bits, and one stop bit, for a total of ten bits, as follows:

4 bytes time = 4 bytes \* 10 bits/byte \*

$$\frac{1}{2.32 \ Mbps} \approx 17.2\mu s$$

(4.1)

The threshold should be set such that these timeout interruptions don't happen frequently, as they cause latency, as shown in the image below.

Figure 4.3: Latency Caused by FIFO Timeout [23]

#### Receiving - Throughput or Latency?

When adding a serial communication protocol to a system, the developer needs to determine whether latency or throughput is more crucial. Keep in mind that the OPU will communicate with the PC via both the CAN and UART protocols, see Figure 1.5. As a result, an RTL value of 8 bytes is preferred, this makes sure to give equal weight to throughput and latency to the receiving end.

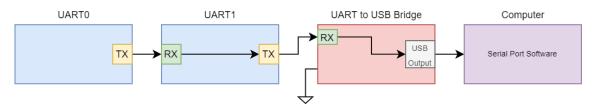

# 4.2.3 Silicon Labs CP2102 USB to UART Bridge

In order to verify that indeed the data does get transmitted between two devices there is to be used a device between the computer and the FPGA to do the translation from the UART signal to USB. For this task, it has been chosen to use the Silicon Labs CP2102 [59].

Figure 4.4: CP2102 USB to UART Bridge

#### 4.3Creating the Base Hardware

In order to be configuring the AXI UART16550 IP to be doing different operations, it needs to have a hardware architecture connecting the programmable logic to the Zyng processing system so that data can be transferred between the sections. The Vivado Design Suite is used to connect the hardware. After the architecture has been realized the bitstream and hardware design file generation will take action and afterward the work is to be done in the software development kit Vitis IDE [60] taking in the usage of the ARM Cortex-A9 CPU [61]

#### 4.3.1**Desired Functionality**

It is desired to create a design that will ensure that both data transmission and data reception are tested. For this, two UART modules will be utilized, one for data transmission and the other for data received before transmitting the same data to the computer to test if the received data matches the one sent. For a better understanding, see the diagram below.

Figure 4.5: Block diagram visualization of the design

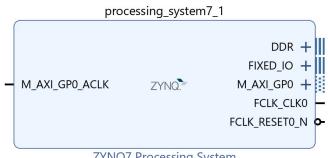

#### **ZYNQ7** Processing System IP

The software interface that wraps around the Zyng-7000 Processing System is known as the Zynq-7000 Processing System IP. The Zynq-7000 series is built on a systemon-chip (SoC) integrated processing system (PS) and a Programmable Logic (PL) unit.

The Processing System IP Wrapper connects the PS and the PL logic [62].

Figure 4.6: ZYNQ7 Processing System

#### Integrated Logic Analyzer

As mentioned in section 2.1.1 the Integrated Logic Analyzer Figure 4.7 is a logic analyzer core that can be used to monitor a design's internal signals. This IP was very important when prototyping. Being that it allowed to monitor the signals on the Zynq in real-time directly through Vivado. It came to a high value when working with implementing interrupt signals to the UART modules as it made it possible to set triggers for once the interrupt signals occur. Allowing the hardware design to be debugged, see prototyping design Figure 4.10.

Figure 4.7: Integrated Logic Analyzer IP

#### AXI UART16550 IP

This IP will take care of the communication to the external world. The IP can take clock signals ranging from 25 MHz to 300 MHz. The higher value of the AXI CLK (Advanced eXtensible Interface Clock) the higher baud rate it is possible to achieve but there is also a drawback of doing so as the energy level will end up increasing. Also, the IP will not be using any external clock, neither for the baud rate nor the external receiver thus both checklists are not checked shown in Figure 4.8. The maximum AXI CLK frequency will be 250 MHz. This is the highest clock frequency (FCLK\_CLK0) that the processing system can provide to the programmable logic, see the port to the right in Figure 4.6.

| Show disabled ports | Component Name axi_uart16550                                                                     |       |                            |  |  |

|---------------------|--------------------------------------------------------------------------------------------------|-------|----------------------------|--|--|

|                     | AXI CLK Frequency                                                                                | 100.0 | [25.0 - 300.0] [25-300]MHz |  |  |

|                     | UART Mode   16550 16450 Use External CLK for BAU External CLK Frequency Enable External Receiver | 25    | [1-150]MHz                 |  |  |

|                     | <                                                                                                |       | >>>>                       |  |  |

Figure 4.8: AXI UART16550 Configuration

#### Making Connections

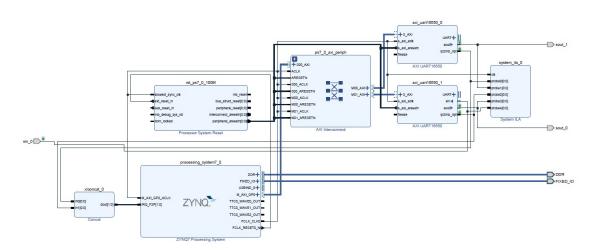

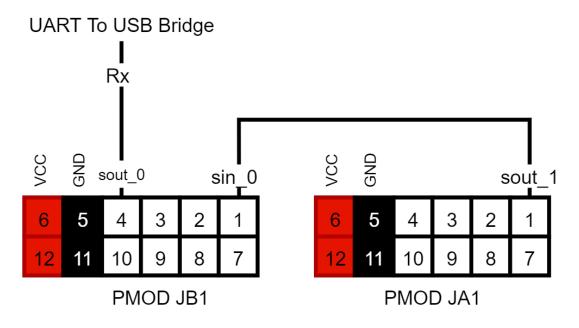

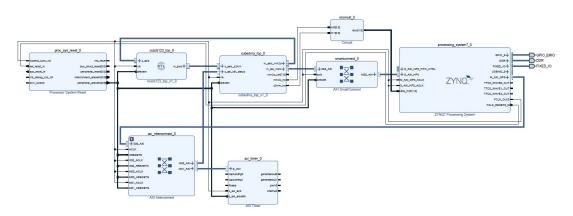

Following the implementation of the ZYNQ7 processing system IP, Integrated Logic Analyzer as well as two AXI UART16550 IP blocks. Block automation is carried out to ensure that the necessary connections are established between the two IPs and the processing system. The transmission UART module is connected to the JA1 peripheral module (PMOD), while the receiver/verification UART is connected to the JB1 PMOD. After completing the block design, the following result is obtained.

Figure 4.9: AXI UART16550 Prototyping Design

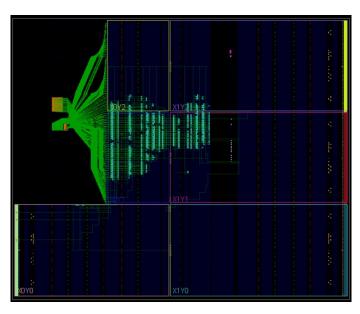

The following Zynq device diagram is obtained after placing and routing the design. The bright orange portion in the top left is the hardened Processing System, which contains the memory controllers and ARM processor cores, while the boxes indicate distinct design sections of the Programmable Logic.

Figure 4.10: The connection between the Processing System and the Programmable Logic on the Zynq-7000 SoC

The links between the PMODs are formed in the following manner:

Figure 4.11: The connection between the two UARTs

Again, by performing block automation, both connections between the multiple IPs are formed, and the AXI UART 16550s are automatically allocated memory addresses. The tools assigned addresses to the additional peripherals automatically, making them compatible with the Zynq device. This address is saved in the hardware design file and will be exported to Vitis later. The addresses can be found by opening the *Address Editor* tab as seen in Figure 4.12

| Diagram × Address Editor × Address Map × uart_back_2_back.xdc ×                             |               |               |                     |       |                     |  |  |  |

|---------------------------------------------------------------------------------------------|---------------|---------------|---------------------|-------|---------------------|--|--|--|

| Q     ★     ♦     ↓     ✓ Assigned (2)     ✓ Unassigned (0)     ✓ Excluded (0)     Hide All |               |               |                     |       |                     |  |  |  |

| Name                                                                                        | ^ 1 Interface | Slave Segment | Master Base Address | Range | Master High Address |  |  |  |

| と は Network 0                                                                               |               |               |                     |       |                     |  |  |  |

| ✓ ♥ /processing_system7_0                                                                   |               |               |                     |       |                     |  |  |  |

| ✓ ☑ /processing_system7_0/Data (32 address bits : 0x40000000 [ 1G ])                        |               |               |                     |       |                     |  |  |  |

| /axi_uart16550_0/S_AXI                                                                      |               | Reg           | 0x43c0_0000 🖉       | 64K 👻 | 0x43C0_FFFF         |  |  |  |

| /axi_uart16550_1/S_AXI                                                                      |               | Reg           | 0x43C1_0000 🖉       | 64K 👻 | 0x43C1_FFFF         |  |  |  |

Figure 4.12: Address of AXI UART16550 IP

When dealing with bare-metal programming, Vitis IDE will automatically establish these addresses, but when using PetaLinux, the addresses must be entered in order to be utilized in the source code.

#### Bitstream Generation and Hardware Export

Following the completion of the preceding procedures, the bitstream will be formed, and the hardware platform will be exported for use in software-related tasks.

# 4.3.2 Integration

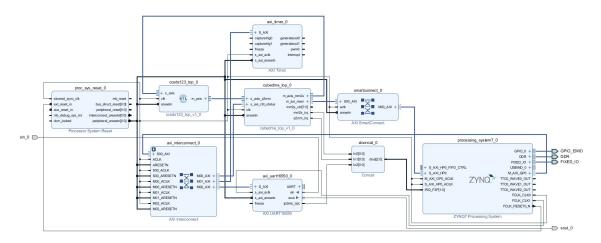

This section will go through how the UART implementation fits into the overall system. This means integrating the AXI UART 16550 into the present system's block architecture and wiring it to it. The modifications to the OPU block design are registered in the ZedBoard's main Tcl (Tool Command Language) script.

#### Architecture of today's hardware

Obtaining the most recent version of the current block design from the OPU-system repository on GitHub was the first step toward modifying it. The script includes all of the commands required to construct the entire HYPSO OPU system.

Figure 4.13: Baseline architecture before implementation of AXI UART 16550

The block design before the AXI UART 16550 is implemented is shown in the diagram above Figure 4.13. Several IPs related to compression and cube construction are included in the block design as well as the timestamping functionality.

#### Integration of the AXI UART 16550

The AXI UART 16550 was added in almost the same way as the programmable logic implementation was described in Section 4.3. The difference in setting up and integrating the AXI UART16550 IP was that connection automation was not being used. Instead, connections between the IP and the rest of the system were done manually to record the Tool Command Language (Tcl) commands that were printed so that they could be added to the system's Tcl-script, automating the OPU design project. The Figure 4.14 shows how the design ended up looking after integrating the AXI UART 16550.

Figure 4.14: Baseline architecture after implementation of AXI UART 16550

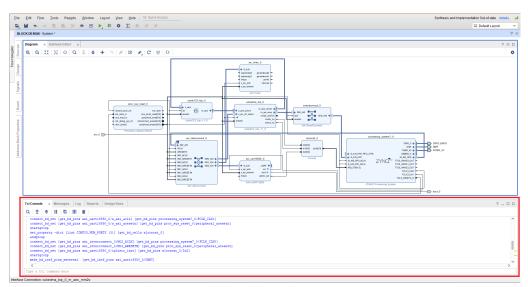

#### TCL Script

Having the hardware architecture design ready for the OPU system, *ZedBoard.tcl* file was to be modified. As mentioned in subsection 4.3.2 the preparation and making of connections between the IPs was done manually and the commands were recorded from the Tcl script seen in Figure 4.15. These commands were saved to a text document which later was added to the main Tcl file.

Figure 4.15: Vivado Result Window Area with Tcl Console highlighted

The code below is extracted from the ZedBoard.tcl script and changed for presenting purposes in this report. The full code can be found in Appendix A.

The first modification to the main block design was, of course, the addition of the AXI UART 16550 IP.

Since the AXI UART16550 IP is being controlled by the processing system, the AXI Interconnect IP had to add another master interface so that it could connect to the slave interface of the UART IP.

The requirement for the UART from the HYPSO team is to be able to achieve a baud rate as close to 3 Mbps as possible. Therefore the clock frequency which is provided to the UART IP is chosen as high as the processing system is capable of. Being that the PL Fabric Clock  $FCLK_CLK0$  is already been set to 100 MHz another component  $FCLK_CLK1$  has been added to the Zynq Processing System generating a clock frequency of 250 MHz.

```

# Enabling Second Clock for PL

set_property -dict [list CONFIG.PCW_EN_CLK1_PORT {1}] [get_bd_cells

→ processing_system7_0]

set_property -dict [list CONFIG.PCW_FPGA1_PERIPHERAL_FREQMHZ {250}

→ CONFIG.PCW_EN_CLK1_PORT {1}] [get_bd_cells processing_system7_0]

```

The AXI UART16550 will also implement interrupt functionality. Therefore the Concat IP needs to have 3 input ports

Lastly, connect the ports of the UART IP to the necessary ports.

```

# For the AXI UART16550

connect_bd_intf_net [get_bd_intf_pins axi_uart16550_0/S_AXI]

-boundary_type upper [get_bd_intf_pins

axi_interconnect_0/M02_AXI]

connect_bd_net [get_bd_pins axi_uart16550_0/s_axi_aclk] [get_bd_pins

processing_system7_0/FCLK_CLK1]

connect_bd_net [get_bd_pins axi_uart16550_0/s_axi_aresetn]

[get_bd_pins proc_sys_reset_0/peripheral_aresetn]

connect_bd_net [get_bd_pins axi_uart16550_0/ip2intc_irpt]

[get_bd_pins xlconcat_0/In2]

connect_bd_net [get_bd_pins axi_interconnect_0/M02_ACLK] [get_bd_pins

processing_system7_0/FCLK_CLK1]

connect_bd_net [get_bd_pins axi_interconnect_0/M02_ARESETN]

j [get_bd_pins proc_sys_reset_0/peripheral_aresetn]

```

When assigning the address the range was set to 64K by default. This was reduced to 4K because the UART does not require anything more than that. The offset value was set to 0x43C1 0000, which was also the case with the automated configuration. When accessing the UART registers in the C source code, this address will be utilized.

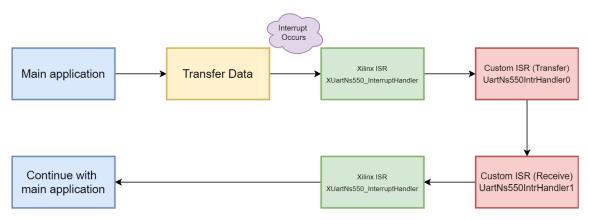

# 4.4 Software Development

When it came to programming the Processing System, there were two basic approaches. Xilinx Vitis was used to program the PS at the start of the project. The software developed there is bare-metal, meaning it does not run an operating system. This was utilized in the prototype and implementation of the project. For further information, see section 4.4.1. After being satisfied with the UART functionality it had to become compatible with the rest of the OPU system running Embedded Linux.

# 4.4.1 Bare-metal configuration