Rikke Solbjørg

# Evaluating Code Overlays on the Oberon System Using RISC-V

Master's thesis in Computer Science Supervisor: Michael Engel July 2021

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

Master's thesis

Rikke Solbjørg

# Evaluating Code Overlays on the Oberon System Using RISC-V

Master's thesis in Computer Science Supervisor: Michael Engel July 2021

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

## Abstract

Code overlays are a versatile technique to reduce the memory footprint of programs, by allowing parts of the program to be loaded from secondary storage into memory as they are needed. While it is an old technique, it has been seeing renewed interest in the context of embedded RISC-V systems without memory management units.

This thesis evaluates automatically generated code overlays on RISC-V in the context of an operating system, Project Oberon 2013. A prototype for an overlay system on the Oberon system is developed, and along with it several different strategies, including one that incorporates Oberon's heap allocation and garbage collection mechanisms.

The thesis concludes by evaluating the benefits and drawbacks of the presented strategies in the context of Pareto optimality. It finds that while one strategy is able to minimise the memory footprint substantially, it can only do this at the cost of considerable performance degradation. Another strategy, utilising the system heap, is able to strike a balance between performance and minimising the memory footprint of the system's code.

## Sammendrag

Code overlays er en teknikk for å redusere minnet brukt av programkode ved å laste deler av programmet fra sekundærminnet til primærminnet etter behov. Til tross for å være en gammel teknikk har det nylig vekt interesse til bruk i enkle RISC-V-systemer som mangler minnehåndterere (MMU).

Denne masteroppgaven vurderer bruken av automatisk genererte code overlays til RISC-V, under operativsystemet Project Oberon 2013. En prototype av et slikt overlay-system utvikles, samt diverse strategier. En av disse strategiene inkorporerer operativsystemets innebygde systemer for heap allocation og garbage collection.

Masteroppgaven konkluderer ved å vurdere strategiene opp mot hverandre ved bruk av Pareto-optimalitet. Denne analysen viser at dog én strategi evner å merkverdig redusere systemets totale minnebruk, klarer den kun dette ved en drastisk påvirkning på systemets totale ytelse. En annen strategi, som bruker systemets heap, finner en mer ønskelig balanse mellom minnebruk og ytelse.

## Acknowledgements

Writing a master's thesis is a long and difficult process, even moreso after a year of living with a pandemic. These last six months have been both amazing and stressful, and I couldn't have done it without the help of all the people around me.

I owe many thanks to my advisor, Michael Engel, for supporting me with insights, papers, and lots of support when I needed it. Thank you for helping me with this project, for reminding me of the purpose of my work, for believing that I could pull through even when I was stuck, and for providing your ideas as well as building on the weird ideas of my own.

Thanks to all my friends for being there, and for listening to me talk about operating systems, memory layouts, heap allocation and garbage collection over and over these last few months. Perhaps especially those of you who don't know the first thing about computers.

Thank you to my family for supporting me during a long and difficult project, for making me relax when I most needed it, and for several supply drops of snacks. Thanks also go to my dad, Ole Kristen Solbjørg, for proofreading my final draft.

I would also like to thank my partner, Martine, for being a great support through the ups and downs of writing the thesis, for brewing countless mugs of coffee — and for reminding me to go for a walk now and then after working long hours and late nights.

Rikke Solbjørg Trondheim, July 2021

# Contents

| Ab  | strac | <b>t</b>   | iii                                                                                                                                      |

|-----|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Sa  | mme   | ndrag .    | · · · · · · · · · · · · · · · · · · ·                                                                                                    |

| Ac  | know  | ledgen     | nents                                                                                                                                    |

| Co  | ntent | t <b>s</b> | ix                                                                                                                                       |

| Fig | gures |            | xiii                                                                                                                                     |

| Ta  | bles  |            | XV                                                                                                                                       |

| Co  | de Li | stings .   |                                                                                                                                          |

| 1   | Intro | oductio    | $n \ldots \ldots$ |

| 2   | Back  | ground     | 1 3                                                                                                                                      |

|     | 2.1   | RISC-V     | 7                                                                                                                                        |

|     | 2.2   | Project    | t Oberon                                                                                                                                 |

|     |       | 2.2.1      | History and goals of Oberon                                                                                                              |

|     |       | 2.2.2      | The Oberon language                                                                                                                      |

|     |       | 2.2.3      | The Oberon compiler         7                                                                                                            |

|     |       | 2.2.4      | The Oberon system         8                                                                                                              |

|     | 2.3   | Overla     | ys 14                                                                                                                                    |

|     |       | 2.3.1      | An overview of overlays $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 14$                                                            |

|     |       | 2.3.2      | Automatic overlays 17                                                                                                                    |

|     | 2.4   | Multi-o    | bjective optimisation and Pareto optimality                                                                                              |

| 3   | Desi  | gn         |                                                                                                                                          |

|     | 3.1   | A desig    | gn overview                                                                                                                              |

|     |       | 3.1.1      | Mechanism 23                                                                                                                             |

|     |       | 3.1.2      | Strategy 24                                                                                                                              |

|     | 3.2   | The ov     | rerlay mechanism                                                                                                                         |

|     |       | 3.2.1      | Overlay tokens                                                                                                                           |

|     |       | 3.2.2      | Overlay manager                                                                                                                          |

|     |       | 3.2.3      | Indirect procedure calls                                                                                                                 |

|     | 3.3   | Linking    | g code and generating overlays                                                                                                           |

|     | 3.4   | Improv     | ving performance of transfer from memory to disk 30                                                                                      |

|     | 3.5   | Positio    | n-independent code 33                                                                                                                    |

|     |       | 3.5.1      | Table of Contents         33                                                                                                             |

|     |       | 3.5.2      | Position-independence using the overlay manager 34                                                                                       |

|     | 3.6   |            | g overlays in memory                                                                                                                     |

|     |       | 3.6.1      | A code buffer                                                                                                                            |

|   |     |         | An overlay heap                                      |    |    | 35 |

|---|-----|---------|------------------------------------------------------|----|----|----|

|   | 3.7 | Garba   | ge collection                                        | •• | •• | 38 |

|   |     | 3.7.1   | 8F                                                   |    |    | 38 |

|   |     |         | Using garbage collection to free overlays            |    |    | 41 |

|   | 3.8 |         | le-granularity overlays                              |    |    | 41 |

|   | 3.9 | Functi  | on-granularity overlays                              |    |    | 43 |

|   |     | 3.9.1   |                                                      |    |    | 43 |

|   |     |         | An automatic overlay tree strategy on the heap       |    |    | 44 |

| 4 | Met |         | ду                                                   |    |    | 47 |

|   | 4.1 |         | g environment                                        |    |    | 47 |

|   |     |         | RISC-V emulator                                      |    |    | 47 |

|   |     | 4.1.2   |                                                      |    |    | 47 |

|   |     | 4.1.3   | Gathering data on instructions run                   |    |    | 48 |

|   |     | 4.1.4   | 5 6                                                  |    |    | 48 |

|   | 4.2 |         | tions of the testing environment                     |    |    | 48 |

|   |     | 4.2.1   | Disk write/read performance                          |    |    | 48 |

|   |     | 4.2.2   | Memory performance                                   |    |    | 49 |

|   |     | 4.2.3   | Cycles spent                                         |    |    | 49 |

|   | 4.3 |         | ethodology and experiments                           |    |    | 49 |

|   |     | 4.3.1   | Code size                                            |    |    | 50 |

|   |     | 4.3.2   | Data transfer between disk to memory                 |    |    | 50 |

|   |     | 4.3.3   | Dynamic memory allocation                            |    |    | 51 |

|   |     | 4.3.4   | Testbenches                                          |    |    | 51 |

|   |     | 4.3.5   | Booting                                              |    |    |    |

| 5 |     |         | d Discussion                                         |    |    |    |

|   | 5.1 |         | er of data from disk to memory                       |    |    |    |

|   | 5.2 |         | on-independent code                                  |    |    | 57 |

|   | 5.3 | •       | nic memory management                                |    |    |    |

|   | 5.4 |         | le-granularity strategies                            |    |    |    |

|   | 5.5 |         | on-granularity strategies                            |    |    | 61 |

|   |     | 5.5.1   | Code buffer results                                  |    |    |    |

|   |     | 5.5.2   | System heap results                                  |    |    |    |

|   | 5.6 |         | ng                                                   |    |    | 67 |

| 6 |     |         | and Future Work                                      |    |    | 71 |

|   | 6.1 |         | tions of overlays using SD cards                     |    |    | 71 |

|   | 6.2 | -       | fragmentation                                        |    |    | 72 |

|   | 6.3 |         | optimality                                           |    |    | 73 |

|   | 6.4 |         | ework                                                |    |    | 75 |

|   |     | 6.4.1   | Testing on hardware                                  |    |    | 76 |

|   |     | 6.4.2   | A dynamic Least Recently Used strategy on the heap . |    |    | 76 |

|   |     | 6.4.3   | Sophisticated overlay strategies                     |    |    | 76 |

|   |     | 6.4.4   | Identifying hot code                                 |    |    | 77 |

|   |     | 6.4.5   | Towards an Oberon Microkernel                        |    |    | 77 |

| 7 | Con | clusion | ι                                                    | •• | •• | 79 |

х

#### Contents

| Bil | bliography                                                          | 81 |

|-----|---------------------------------------------------------------------|----|

| Α   | Test programs and data                                              | 85 |

|     | A.1 Data transfer from disk to memory                               | 86 |

|     | A.2 Test programs                                                   | 87 |

| В   | Project Report: Porting the Oberon system to the RISC-V instruction |    |

|     | set architecture                                                    | 91 |

# Figures

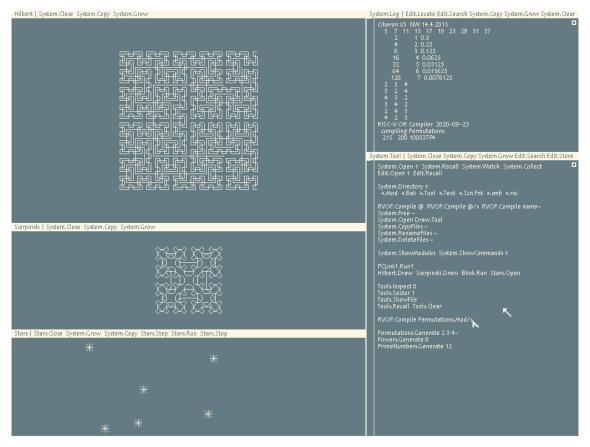

| 2.1 | A screenshot of the Oberon system (here running on RISC-V). Taken                                                                                                                                                  |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | from our previous project performing this port, included in Ap-                                                                                                                                                    |    |

|     | pendix B                                                                                                                                                                                                           | 5  |

| 2.2 | Memory layout of the Oberon system.                                                                                                                                                                                | 8  |

| 2.3 | The booting process of the Oberon system.                                                                                                                                                                          | 11 |

| 2.4 | The structure of every allocated block on the Oberon system heap, based on a figure in [2]                                                                                                                         | 11 |

| 2.5 | An example of an overlay tree                                                                                                                                                                                      | 15 |

| 2.6 | The relationship between the Pareto optimal front, the approxim-<br>ate Pareto optimal front, and dominated solutions. Adapted from a                                                                              | 10 |

|     | figure in [19]                                                                                                                                                                                                     | 18 |

| 3.1 | The modified inner core of the Oberon system, when code overlay support is added.                                                                                                                                  | 22 |

| 3.2 | The overarching design that will be detailed in Chapter 3                                                                                                                                                          | 22 |

| 3.3 | Memory layout of the Oberon system when using a code buffer<br>strategy. The size of the boxes represents approximate relative use<br>in memory.                                                                   | 42 |

| 3.4 | Memory layout of the Oberon system, modified to support function-<br>granularity overlays on the heap.                                                                                                             | 44 |

| 4.1 | The Oberon system, when fully booted according to the methodo-<br>logy presented in Section 4.3.5.                                                                                                                 | 54 |

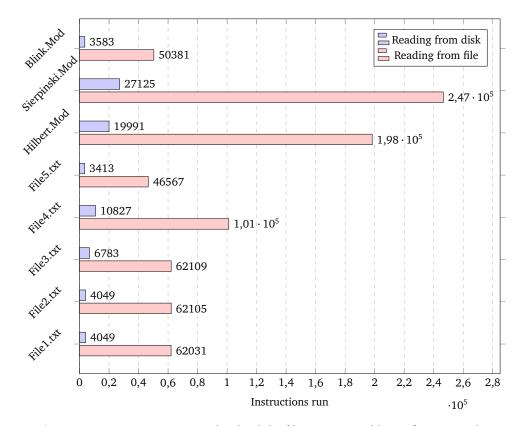

| 5.1 | Instructions required to load the files given in Table 4.1 from sec-<br>ondary storage into memory, when loading through the file system<br>or directly from disk. Fewer instructions indicate better performance. | 56 |

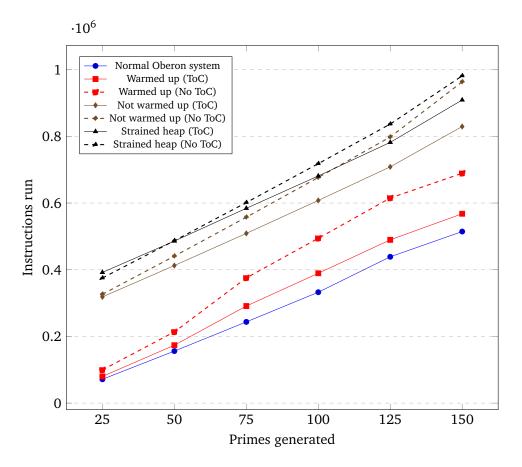

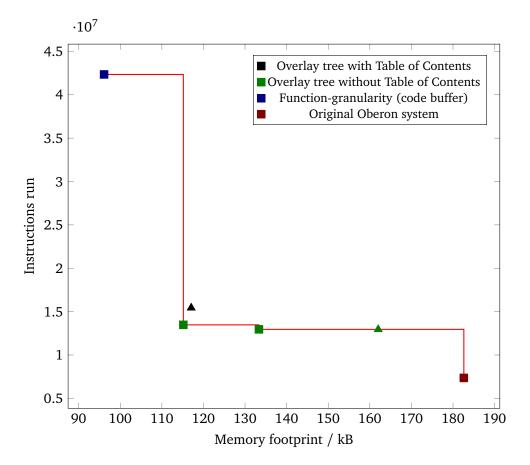

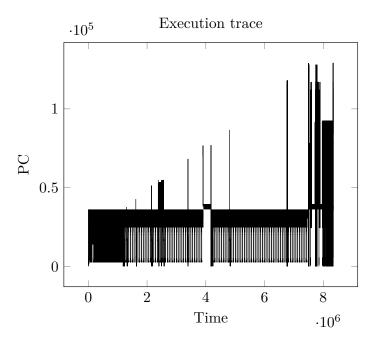

| 5.2 | The performance of PrimeNumbers.Generate given different setups, using an overlay tree strategy.                                                                                                                   | 66 |

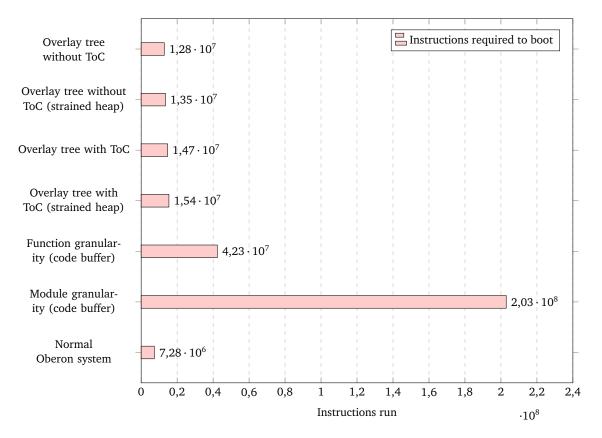

| 5.3 | Instructions required to boot a full Oberon system, given the differ-<br>ent strategies presented in this thesis, as well as whether the heap                                                                      |    |

|     | is strained. ToC is short for Table of Contents.                                                                                                                                                                   | 68 |

xiv

# **Tables**

| The sizes of files on which read performance was tested              | 51                                                                        |

|----------------------------------------------------------------------|---------------------------------------------------------------------------|

| 6 6 6                                                                |                                                                           |

| 1 0                                                                  | 53                                                                        |

| A table containing details regarding the Hilbert.Draw program        | 53                                                                        |

| Overhead in code required to support position independence using     |                                                                           |

|                                                                      | 57                                                                        |

| Minimum heap size required for different workloads depending on      |                                                                           |

| whether stack marking is included.                                   | 58                                                                        |

| Performance of module-granularity overlays, using a code buffer,     |                                                                           |

| compared to a normal Oberon system.                                  | 60                                                                        |

| Performance of function-granularity overlays using a code buffer,    |                                                                           |

| compared to a normal Oberon system.                                  | 61                                                                        |

| Results of experiments run with a heap-based strategy, using the     |                                                                           |

| overlay manager for position-independent code                        | 63                                                                        |

| Results on experiments run with a heap-based strategy, using the     |                                                                           |

| Table of Contents for position-independent code.                     | 65                                                                        |

| The minimal heap used for the <i>strained heap</i> testbenches       | 65                                                                        |

| Minimum amount of memory required to boot. The Overlays column       |                                                                           |

| contains information on overhead used by the overlay system, i.e.    |                                                                           |

| the overlay table and overlay region. Note that memory required to   |                                                                           |

| include the bitmapped display, 98304B, is not included in the total. |                                                                           |

| Sizes are given in bytes.                                            | 67                                                                        |

|                                                                      | A table containing details regarding the PrimeNumbers.Generate<br>program |

# **Code Listings**

| 2.1                | Simple example of an addition procedure in Oberon                        | 7                    |

|--------------------|--------------------------------------------------------------------------|----------------------|

| 3.1                | Initial implementation of an overlay manager.                            | 26                   |

| 3.2                | Optimised version of the overlay manager                                 | 27                   |

| 3.3                | RISC-V assembly for handling an indirect function call. Labels have      |                      |

|                    | been added for readability.                                              | 28                   |

| 3.4                | Code for copying an overlay from disk to memory using the file           |                      |

|                    | system                                                                   | 31                   |

| 3.5                | Code for efficiently getting data from disk to memory                    | 32                   |

| 3.6                | Oberon code for moving a code segment from secondary storage to          |                      |

|                    | memory                                                                   | 33                   |

| 3.7                | Procedure to allocate a 32B block. If there is an entry in the 32B       |                      |

|                    | free-list, that is used; if not, a 64B block is allocated, and the first |                      |

|                    | half is returned while the second half is added to the 32B free-list     | 36                   |

| 3.8                | Code marking potential references to objects on the heap currently       |                      |

|                    | living on the stack.                                                     | 39                   |

|                    |                                                                          |                      |

| 3.9                | The record containing information of overlays given a module-granula     | rity                 |

|                    | strategy.                                                                | rity<br>42           |

|                    | strategy                                                                 | 42                   |

| 3.10               | strategy                                                                 | 42<br>43             |

|                    | strategy                                                                 | 42                   |

| 3.10               | strategy                                                                 | 42<br>43             |

| 3.10<br>5.1        | strategy                                                                 | 42<br>43             |

| 3.10<br>5.1        | strategy                                                                 | 42<br>43             |

| 3.10<br>5.1        | strategy                                                                 | 42<br>43<br>59       |

| 3.10<br>5.1<br>A.1 | strategy                                                                 | 42<br>43<br>59       |

| 3.10<br>5.1<br>A.1 | strategy                                                                 | 42<br>43<br>59       |

| 3.10<br>5.1<br>A.1 | strategy                                                                 | 42<br>43<br>59<br>87 |

| 3.10<br>5.1<br>A.1 | strategy                                                                 | 42<br>43<br>59       |

| 3.10<br>5.1<br>A.1 | strategy                                                                 | 42<br>43<br>59<br>87 |

# Chapter 1

### Introduction

RISC-V is a quickly growing alternative to other instruction set architectures, such as x86 and ARM; it stands out as a completely free ISA. However, there is still much to be explored when it comes to RISC-V, as it is still rather new. In an effort to begin exploring the possibilities of RISC-V, we previously undertook a project to port Project Oberon 2013 to RISC-V [1]. This thesis builds on that project, further exploring the possibilities available in running the Oberon system on RISC-V.

The Oberon system, along with its corresponding programming language and compiler, was first developed by Niklaus Wirth and Jürg Gutknecht between 1986 and 1989 [2]. In Niklaus Wirth's well-known article A Plea for Lean Software, it is given as an example of software that is small, simple, and easy to understand [3], as a potential counter to a version of Parkinson's Law which states that "software expands to fill the available memory". Furthermore, Wirth's newest iteration of the system, Project Oberon 2013, is published as free and open-source software, making it easy to access and research<sup>1</sup>.

In this thesis, code overlays will be explored as a way to further minimise the memory footprint of the Oberon system. Overlays became less of a necessity with the increased adoption of virtual memory. A memory management unit (MMU) can offer the illusion of an infinite amount of virtual memory mapped onto a restricted amount of physical memory, supplanting the need for overlaying techniques.

However, requiring an MMU increases the complexity of hardware, which is undesirable for very simple embedded systems. There has recently been increased interest in using overlays on embedded RISC-V systems, and a task group has been created to that end [4]. RISC-V's modularity and extensibility makes it particularly useful for embedded/IoT applications, as a device can be very simple and still be compliant with the specification. With this in mind, a RISC-V implementation with a minimal amount of extensions, use of only machine-mode, and no MMU, is now a hardware platform with real-world application.

<sup>&</sup>lt;sup>1</sup>The entirety of the Oberon system can be found on Prof. Wirth's website, https://people.inf. ethz.ch/wirth/ProjectOberon/.

A website with additional resources can be found at http://projectoberon.com.

To our knowledge, implementing code overlays on Project Oberon has not been attempted before. This is despite the fact that Project Oberon is an operating system designed with a single, physical address space in mind, with the goal to be as minimal as possible [2][3]; code overlays would minimise it further. In addition, as mentioned, RISC-V is seeing renewed interest in code overlays in general. Therefore, implementing code overlays on the Oberon system under RISC-V is a goal worth pursuing.

Thus, the overarching research goal of the thesis is to **evaluate whether code overlays are a tenable strategy for reducing the memory footprint of the Oberon system**. For it to be a tenable strategy, it must be able to reduce the memory footprint while exhibiting acceptable performance. To that end, the thesis will explore different strategies for implementing code overlays in the Oberon system, and evaluate whether any of them either fulfil this goal or have the potential to fulfil this goal. In addition, we also hope that in using an operating system that has not been widely researched in quite some time, novel insights will reveal themselves.

Additionally, while it would be possible to manually create overlays based on careful analysis of the operating system, this is a difficult task for several reasons, biggest of all being that it is error-prone in a regular application [5][6], let alone an entire operating system [7]. Furthermore, automatic overlays will allow any program to run on top of the developed overlay system without programmer intervention. Therefore, automatic generation of code overlays will be pursued.

The thesis is laid out as follows. Chapter 1 has introduced the overarching goals for the project. Chapter 2 introduces concepts regarding RISC-V, Oberon, memory management, and code overlays, that will be important to the rest of the thesis. Then, Chapter 3 will cover how the goals presented above were reached, as well as the decision-making process behind certain choices. Chapter 4 covers the ways in which data was gathered, limitations faced regarding what data could be gathered, and the specific experiments that are run. Chapter 5 presents results on the data that was gathered and discusses them. Chapter 6 evaluates the presented strategies, and proposes future avenues to further develop the concepts presented in this thesis, before the thesis is concluded in Chapter 7.

### Chapter 2

# Background

In the following chapter, background information useful for understanding the rest of the thesis is presented. In Section 2.1, basic information on the RISC-V instruction set architecture — the one used in this thesis — is given. Section 2.2 gives an introduction to Project Oberon, its distinctive characteristics, as well as the process of porting it to the RISC-V instruction set architecture, which was completed in a previous project. Finally, Section 2.3 covers prior work and important details to note on code overlays, both in general and in the context of operating systems in particular.

Note that parts of this background section are adapted from the one given in our previous project report on porting the Oberon system to RISC-V [1], which can be found in Appendix B.

#### 2.1 RISC-V

RISC-V is a rather new instruction set architecture, the goal of which is to become completely universal [8]. In other words, it should be able to accommodate all possible cores that desire to implement it, whether they are in-order or out-of-order; as well as all technologies a core can be fabricated with, whether it's on an FPGA or ASIC.

It is unique for many reasons, and not all of them will be recounted here. Of particular importance to this project, RISC-V is an example of a RISC (reduced instruction-set computing) design, meaning it favours combining multiple simple instructions to do something complex, as opposed to performing the complex instruction in hardware. This is as opposed to a CISC (complex instruction-set computing) design, wherein the processor understands many more instructions that can perform very specific operations.

Another important aspect is that it is a *modular* ISA [8]. It offers a basic set of instructions that every RISC-V processor is guaranteed to implement, and then a set of extensions that a processor can choose to implement depending on what it targets. For instance, a small implementation might use RV32I; the RV signifies that it's RISC-V, *32* signifies a 32-bit processor, and *I* signifies the most basic extension, which includes only instructions essentially deemed necessary, 47 in total. Other extensions can be added on top of this: for instance, instructions for multiplication and division are defined in the *M* extension. An implementation that also includes these instructions would be a RV32IM processor. There are many other extensions, such as F and D for single- and double-precision floating point respectively.

Choices regarding what parts of the RISC-V ISA to support were done in our previous project porting the Oberon system to RISC-V[1], detailed in Appendix B. These choices will be reiterated for the convenience of the reader. A RV32IM architecture was targeted, as it is a reasonable architecture for embedded applications, including the kinds of constraints under which Oberon performs well. As mentioned, that means basic instructions, as well as multiplication and division instructions. Notably, it also means that floating-point operations are not supported by hardware. Another feature offered by RISC-V is various modes that signify different levels of privilege. It offers three: machine-mode, supervisor-mode, and user-mode [9]. While many modern operating systems require different privilege levels, this is not necessary for the Oberon system. As such, a system using only machine-mode was targeted, often ideal for simple embedded systems [9].

#### 2.2 Project Oberon

This section will go over several aspects of Project Oberon that are useful to have a basic understanding of for the rest of this thesis. Section 2.2.1 covers the history of Oberon, and more importantly the goals it strives to achieve. Section 2.2.2 will explain some basic aspects of the Oberon programming language, which the entire Oberon system is programmed in; Section 2.2.3 will cover specifics regarding the Oberon compiler, which will see several modifications throughout the thesis; and finally, Section 2.2.4 will cover the construction of the Oberon system itself, particularly the aspects relevant to this thesis.

#### 2.2.1 History and goals of Oberon

The Oberon system was first designed in 1986–1989 by Niklaus Wirth and Jürg Gutknecht, then as a complete workstation for use both in academia and industry, on which they also wrote a book describing the inner workings of the entire system [2][3]. The goal of this textbook is to make the system easily understandable to any single person who takes the time to study it. As mentioned in Chapter 1, it was used as an example of a lean software system in [3], where it is cited as a simple, minimal, yet complete system, something that could only be done by focusing on the essentials. It was later picked up again by Wirth in 2013, to update the system and provide an accompanying textbook equivalent to the previous — as the old textbook was based on a machine that is no longer available, the Ceres, using a processor that is also no longer available, the NS32032 [2].

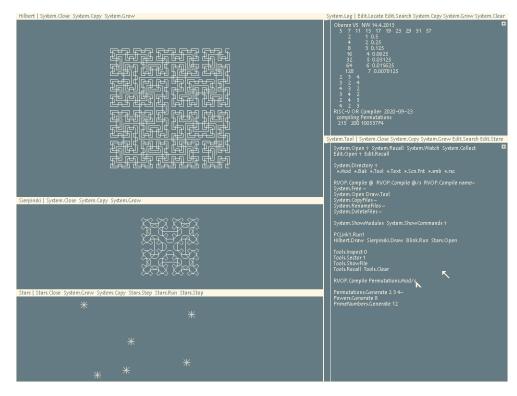

**Figure 2.1:** A screenshot of the Oberon system (here running on RISC-V). Taken from our previous project performing this port, included in Appendix B.

A particularly notable addition in the 2013 version is the design of a custom RISC processor, to replace the NS32032. Both the processor and the ISA were called RISC-5 (not to be confused with RISC-V), and they were designed with the goal of being very simple, such that the hardware can also be studied and understood.

For the remainder of the thesis, it will be useful to understand the goals of the Oberon system, as presented in [3] and [2]. The primary goal "was to show that software can be developed with a fraction of the memory capacity and processor capacity usually required, without sacrificing flexibility, functionality, or user convenience" [3], while the secondary goal "was to design a system that could be studied and explained in detail, a system suitable as a software-design case study that could be penetrated top-down and whose design decisions could be stated explicitly" [3]. These stated goals remain the guiding principles of Project Oberon 2013 — its largest changes to previous versions are by far found in the compiler, and not in the system itself [2].

Finally, as an example of what the Oberon system looks like, the reader may find Figure 2.1 interesting. This figure in particular is of the ported RISC-V system, but it should look no different from a RISC-5 Oberon system (apart from a differently named compiler).

#### 2.2.2 The Oberon language

The Oberon language is a successor to previous languages in the Wirth family of languages, such as Pascal and Modula. Its design sensibility is quite similar, but it has a more stripped back set of features, with the goal of making it "as simple as possible, but no simpler" [10]. It is meant to be general-purpose, while satisfying enough criteria to be used as a systems programming language. A few features of the programming language, namely those particularly relevant to this thesis, will be explained in this section. The full report of the most recent revision of the language can be found at [10].

Firstly, Oberon programs are split into units that can be separately compiled, i.e. modules. A module is a collection of constants, types, global variables, and procedures [10], and a module can import other modules (so long as the dependency graph does not become circular). Furthermore, as long as a dependent module's exported types/procedures have not changed, recompilation of a module does not necessitate recompilation of dependencies. This is to allow easy extensibility without forcing unnecessary recompilation of every imported module. The programmer chooses which parts of the module to export for use by other modules, e.g. from its types and procedures.

Another important feature of the Oberon language is that it is strongly typed. It offers a set of basic types (such as BOOLEAN, CHAR, INTEGER), the potential to create arrays, pointers, and types describing specific procedure signatures, as well as the potential for the programmer to create new types, known as record types (which are quite similar to structs in C). A consequence of this strong typing is that, unlike a language like C, pointers are also strongly typed: pointers *must* point to a specific record.

However, as it is meant to work as a systems programming language, the Oberon language also specifies the existence of the pseudo-module SYSTEM. This module contains procedures that allow for e.g. breaking the rules of the language, as well as procedures that are implementation-dependent, both in terms of the compiler and the underlying computer. An example of a procedure that breaks the rules of the language is SYSTEM.VAL, which allows for converting one type to another (i.e. casting). An example of a procedure that is specific to the machine in question, on the RISC-5 system, is SYSTEM.H, which reads the auxiliary register H on the RISC-5 processor, containing the upper 32 bits of the previous multiplication operation or the remainder of the previous division operation (depending on which was last performed) [11].

Finally, a word on terminology. Although the term "function" commonly encompasses any callable unit in modern computer science, the Oberon language and documentation makes a consistent distinction between a function, which returns a value, and a procedure, which does not return a value. As such, when discussing particulars written in the Oberon language, this thesis will make the same distinction.

#### 2.2.3 The Oberon compiler

Several characteristics of the Oberon compiler are particularly noteworthy for this project. The characteristics described here were present in the original RISC-5 compiler as written by Niklaus Wirth, and are also in the RISC-V port.

Firstly, the Oberon compiler is a single-pass compiler. Information contained later in the program cannot be used by earlier parts; for instance, a procedure declared later in the program cannot be called by an earlier procedure except by means of an indirect function call. It also performs no optimisations: it contains no abstract syntax tree or intermediary representation, instead emitting machine code on a per-statement basis. This has ramifications for precisely how performant a compiled Oberon program can be. For example, take the following procedure:

Code listing 2.1: Simple example of an addition procedure in Oberon.

```

1 PROCEDURE Add(a, b: INTEGER): INTEGER;

2 VAR c: INTEGER;

3 BEGIN

4 c := a + b;

5 RETURN c

6 END Add;

```

An optimising compiler could turn this procedure into two instructions, adding the two registers containing the values of variables a, b together and depositing the result in the register holding the return value, then jumping back to the caller. It could even be inlined, turning it into a single instruction.

The Oberon compiler, however, will scan the program one line at a time, and perform no analysis of the program to cut intermediate steps that are unnecessary. In this example, it will first increase the size of the stack to accommodate the variables, push the parameters onto the stack, pop them from the stack, add them together into a new register, push that register back onto the stack in the location reserved for variable c, then pop that off the stack into the register reserved for the return value before jumping back to the caller.

In other words, Oberon programs are often less performant than what one is used to in modern compilers. This is in large part because Wirth's metric for the quality of the compiler was not the performance of all compiled programs, but rather the *speed of self-compilation*, a metric either invented or popularised by Wirth [12]. In other words, the compiler is its own benchmark, and the only improvements allowed to enter the compiler are those that increase the speed at which the compiler compiles itself. This results in a very fast compiler, though at the cost that it does not employ many optimisations.

As this thesis will not focus on compiler optimisations, these design decisions have been left as-is; however, they do have implications for how performant it is possible to make programs that are built using the Oberon compiler.

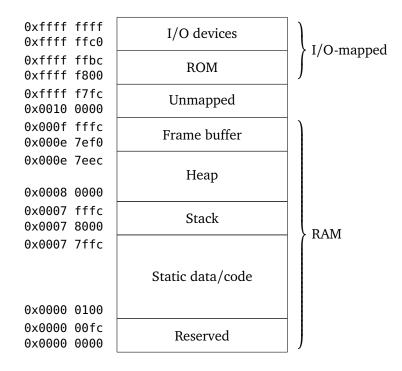

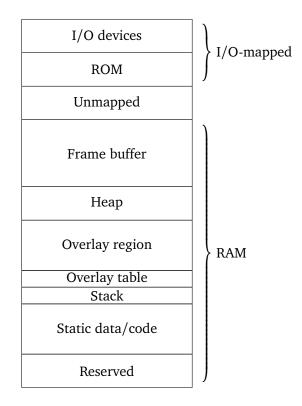

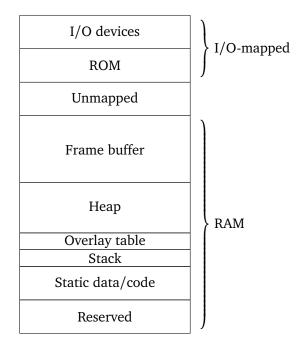

Figure 2.2: Memory layout of the Oberon system.

#### 2.2.4 The Oberon system

The Oberon system has some unique characteristics that will be of particular interest in this thesis, which will be discussed in the following section, giving a detailed description of specific parts of the Oberon system. The memory layout of the Oberon system will be explained in some detail, as understanding it is of particular importance when trying to improve the memory footprint of the entire system. This is followed by an explanation of Oberon's dynamic linking loader, which will see some significant modifications in the prototype presented in this thesis. This is followed by an overview of the process of booting the Oberon system. Then, an interesting feature of the system is briefly explained, namely the built-in heap allocator and its corresponding garbage collector, responsible for deallocation. Finally, a brief explanation of the process of porting the Oberon system to RISC-V is given.

#### The Oberon memory layout

An understanding of the Oberon memory layout, depicted in Figure 2.2, will be useful, as several modifications to it will be described later in the thesis. The Oberon system's memory layout is split into three sections: static data/code, the stack, and the heap. Additionally, the upper areas of memory are used for the bit-mapped display and I/O.

The "Reserved" area is used for the trap handler as well as the module table. The module table is a table of pointers into the static data/code section, which is the largest region of memory in the system. This is where the linking loader places modules, allocating space for static data, type signatures, and any module code. It effectively functions like a first-fit heap: if a module is removed, it is considered a hole in the list of modules, and upon allocating space for a new module, it looks through the list for any holes large enough, placing it at the end of the list of modules if no appropriate holes are found.

Next, although the stack is given with a definite size here of 32kB (as the system does specify a theoretical "size" of the stack), there is no canary mechanism or similar in the Oberon system to detect a stack overflow, and in practice, few Oberon systems are demanding enough to cause one. (Maliciously breaking the system with a stack overflow is also trivial, but security is given little consideration in the Oberon system in general.)

The heap is the second largest portion of the system, at approximately 425kB. As in other systems, the heap is used for dynamic data allocation.

Finally, the frame buffer section of memory is bit-mapped onto the display. As Oberon only uses monochrome colours, one bit for each pixel suffices. The display is by default assumed to be 1024x768, so it follows that this memory region must occupy at least 98304B. (In the system it occupies 98576B, as there is some unused memory between the heap and the display buffer; this unused memory is not necessary for the system to function.) This part is not considered for improvement in this project; one could trivially lower the required memory for the frame buffer by lowering the resolution, e.g. by lowering it to 800x600 it would only require 60000B. Different hardware to handle displaying pixels in a more memory-efficient manner could also be employed, but again, that would be outside the scope of this thesis.

As the sizes of the section for static data and code, the stack, and the heap are all variable, they can be tweaked to different sizes depending on the needs of the system.

#### The dynamic linking loader

As supporting code overlays requires loading already linked code from secondary storage to main memory, it will be useful to have an understanding of how Oberon links modules, especially as Oberon does *not* link modules right after compilation (i.e. statically), but rather in runtime. To support increased extensibility and to avoid large statically linked binaries, the Oberon system uses a dynamic linker and loader [2]; similar advantages of dynamic linking are noted in [13]. The dynamic linker only links an Oberon module right before it is to be loaded into the system, using information only available at runtime, such as other modules' positions in the module table, the exact locations of dependencies in memory, etc., to do so. As Wirth notes in [2], to do so requires the linker to be fast, and therefore quite simple.

The linking loader first reads the header of the module to gather information needed for linking, and then reads the unlinked code into memory. The linker works by traversing linked lists stored in instructions in the code, with the tail of each linked list provided in the header of the module, performing fixups — i.e. changing the instruction to correctly reference the location of external dependencies — on every instruction in each linked list. One such tail points to the location of the last instruction in code that needs a fixup, which contains both enough information to correctly identify how to fixup the instruction, as well as a pointer to the next instruction that needs a fixup. When it finishes traversing every list, the module is done being linked, and as the module was already loaded into memory prior to being linked, this doubles as the module being successfully loaded. Note that in no part of this stage is the linked code written back to secondary storage — the code is only linked in memory, and if the module is unloaded and needs to be loaded anew, the linking process will have to be repeated.

#### Booting the Oberon system

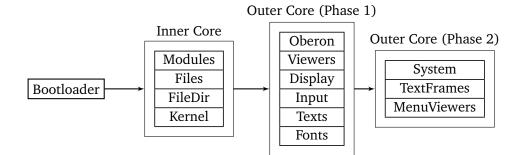

Booting the Oberon system occurs in multiple phases, and will necessarily interact with the code overlay system presented later in the thesis. Therefore, an understanding of how the Oberon system builds its different layers on top of one another in the process of booting will be helpful. A more detailed description can be found in [2], but it will be quickly recounted here.

Booting Oberon occurs in three phases: loading the inner core, then loading the outer core in two steps; which modules are involved in which stage of the booting process can be seen in Figure 2.3. The bootloader, responsible for loading the inner core, is present in the ROM; the processor knows to begin the booting process by reading instructions from it. Once the inner core has been loaded by the bootloader, the bootloader jumps to the entry point for initialising the inner core, transferring execution from the ROM to main memory. Note that, while the inner core is responsible for linking and loading the outer core, it cannot link itself; it has to have been linked beforehand, which is done in the process of installing the operating system on a new workstation.

Once execution has been transferred to the inner core, it loads what has in Figure 2.3 been termed *Phase 1*, which is responsible for loading most of the UI, as well as the driver for the keyboard and mouse. It is also responsible for the module **Oberon**, which contains the core loop that governs the operating system, as well as procedures for calling other modules via user input. Once *Phase 1* has been loaded, it immediately begins loading *Phase 2*, which builds on top of *Phase 1*, before entering the previously mentioned loop. At that point, the system is fully booted.

#### Heap allocation and garbage collection

The Oberon system has both a heap allocation system as well as a garbage collector built into its kernel. These will both play a role in this thesis, so an introduction

Figure 2.3: The booting process of the Oberon system.

**Figure 2.4:** The structure of every allocated block on the Oberon system heap, based on a figure in [2].

to how they work is warranted.

The heap, in short, uses free-lists segregated by block size. To avoid fragmentation, the heap is composed of four lists of free blocks at different levels of granularity: 256B, 128B, 64B, and 32B. Allocation of, for instance, a 32B block is done by allocating a 64B block, marking the first 32B as allocated, and marking the other 32B as free in the 32B free-list. The same goes for every granularity, up to the 256B list, which allocates as many 256B blocks as are needed for the size of the data structure being allocated. By the taxonomy of dynamic storage allocators presented in [14], the Oberon heap allocator uses a system of segregated fits using strict size classes with rounding.

To mark whether a block in the heap is free, as well as to denote the size of the block, two words are reserved as a prefix to every block. If the block is allocated, the first word is a pointer to a field in memory that holds the size of the block; if it is freed, the first word is the size of the free block. The second word is used to mark whether the block is allocated in Oberon's mark-scan garbage collection scheme. Thus, for every allocated block, an extra 8B is required, as can be seen in Figure 2.4.

Oberon also includes a built-in garbage collector, which is installed as a task that runs every second (provided the system is not occupied running another process). This task is located in the **Oberon** module, which calls procedures in the kernel to perform the different phases of garbage collection. As Oberon employs a mark-scan (also known as mark-sweep) garbage collector [2], there are two phases, marking and scanning, both of which will be explained below.

The mark phase occurs first, and consists of iterating through a list of *roots*. A root is a known pointer, which may point to a data structure that contains other

pointers. Thus, the task of the mark phase is to iterate through this list of roots, mark the pointers in that list, and also search through the data structures pointed to by these roots for additional pointers that must be marked. Although this phase is implemented as an iterative procedure to avoid stressing the stack [2], the actual algorithm is recursive in nature, as it must mark every found data structure starting from each root using a tree traversal algorithm. As Oberon only runs garbage collection when no other process is running, the list of roots is limited to pointers located in the static data section of every module, of which a separate list is kept for each module, precisely to make the process of traversing this list simple.

The second phase is the scan phase. The scan phase linearly traverses the heap, starting from the base of the heap. It scans the prefix of each block on the heap, retrieves its size from that prefix, and uses that size to jump to the next block. While scanning, it keeps track of the *mark* located in each block's prefix. If the mark is 0, it is *unmarked*, i.e. it was not found in the previous mark phase, meaning it will be be collected by adding it to the free-list and setting its mark to -1. Adjacent unmarked blocks are merged. If the scan phase reaches a marked block, meaning it should not be collected, it is skipped, and its mark is set back to 0 such that it has to be marked again the next time garbage collection runs. If the scan phase reaches a block marked as -1, i.e. free, it is skipped entirely. (Any negative mark will be treated the same way, but the system only uses -1.)

When both phases are complete, the heap has been garbage collected, and the routine is completed.

#### Porting the Oberon system to RISC-V

The process of porting Oberon to RISC-V is detailed in [1], which is also in this document in Appendix B. A brief explanation of the process follows, as it was essential to allowing this project, and it illustrates several key aspects of the Oberon system.

The porting effort began by setting up an environment in which the Oberon system can both be built and tested. The building system was based on Project Norebo, by Peter de Wachter<sup>1</sup>. Project Norebo is based on a headless version of Oberon that runs on a RISC-5 emulator, with some facilities allowing it to interact with the shell (for printing text) as well as the underlying file system (to read/write files). Using this, Oberon programs such as the compiler can be run; this can then compile the RISC-V compiler, thus setting up a cross compiler running on RISC-5 that emits RISC-V code. The testing was handled by extending an emulator of the Oberon system, also by Peter de Wachter<sup>2</sup>, to support RISC-V instead of RISC-5<sup>3</sup>.

<sup>&</sup>lt;sup>1</sup>Project Norebo can be found here: https://github.com/pdewacht/project-norebo

<sup>&</sup>lt;sup>2</sup>The RISC-5 emulator can be found here: https://github.com/pdewacht/oberon-risc-emu/ <sup>3</sup>Our extended RISC-V emulator can be found here: https://github.com/solbjorg/ oberon-riscv-emu

Next, as the built-in Oberon compiler only supported the special-purpose RISC-5 ISA, it needed to be rewritten to support RISC-V. We discovered partway through the process that an in-progress version of such a port existed, courtesy of Samuel A. Falvo II<sup>4</sup>, which we built the rest of the project on top of. Though that version was mostly working in that it had been converted to emit RISC-V code, there were a fair few bugs to be ironed out (as is to be expected when testing a compiler). After a considerable amount of effort, the RISC-V compiler reached a state of being fully self-compiling.

Besides porting the compiler, some other parts of the Oberon system necessarily also had to be changed to support RISC-V, though not as many as one would expect in porting an operating system. This is in large part due to the simplicity of the system, as detailed in Section 2.2.1. In particular, the minimal hardware requirements of Oberon made porting it quite effortless once the compiler was fully functioning — as mentioned in Section 2.1, floating-point instructions are not required to run the Oberon system, and in addition, interrupts are not required either. Furthermore, the bootloader of the Oberon system is also written in Oberon, by signalling to the compiler that the module in question should be compiled as bare-metal code, and not as an Oberon module meant to be loaded into the Oberon runtime. Thus, while the compiler had to be changed somewhat to support compiling bare-metal code for RISC-V, the bootloader itself could remain completely untouched. Similarly, the kernel required some minimal changes, while the file system and the outer core of the Oberon system required no changes at all.

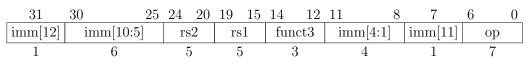

One more aspect of the system had to be updated, namely the linking loader. The linking loader, as explained in Section 2.2.4, is responsible for fixing dependencies and loading a module into the Oberon system. Fixing these dependencies proved to be significantly more complex in RISC-V than in RISC-5, due to more complex instruction encodings, though not prohibitively so.

A few things are worth noting about differences between the RISC-5 and RISC-V versions of the Oberon system, however. Firstly, code generated for RISC-V is generally somewhat larger than code generated for RISC-5. It is also in some cases slower and in some cases faster than RISC-5 code, due to different strengths inherent to the two ISAs. Secondly, while the static data sections of the RISC-5 Oberon system are practically restricted to 64kB due to compiler limitations [1], static data sections of the RISC-V Oberon system are restricted to 2kB (due to the load instruction's signed 12-bit offset). In practice this does not have a large effect on the system, except that the sector map in the kernel is stored on the heap instead of static data, and other programs must be rewritten to use the heap if their static data exceeds 2kB. Finally, as mentioned, the linker is more complex.

To summarise, once the compiler, certain aspects of the kernel, and the linking loader were ported, the entire Oberon system worked in just the way one would expect it to. This speaks to a strength of the Oberon system: as all of it is written in the Oberon language, rather than e.g. having parts written in assembly code, it

<sup>&</sup>lt;sup>4</sup>His RISC-V compiler can be found here: https://github.com/sam-falvo/project-norebo

is rather easy to port. It is fully featured, aside from some of the extra hardware features that were dropped (i.e. interrupts and floating-point), and very stable<sup>5</sup>.

#### 2.3 Overlays

Code overlays are an old technique in computer programming. By splitting a larger program into smaller independent segments, and *overlaying* them on top of one another, the technique allows a large program to fit into much smaller memory. Overlaying in particular means that two different segments can occupy the same area of memory, depending on when either is needed.

As code overlays are the main focus of this thesis, this section provides some background on code overlays and different ways they are used, as well as relevant related work. Section 2.3.1 will go over the basic structure of code overlays, including the units of which they are composed as well as how they are used in the context of a program. Section 2.3.2 will motivate the use of an automatic approach, rather than a manual one, as well as detail an approach to automatically overlaying an operating system kernel.

#### 2.3.1 An overview of overlays

There are three parts of the technique that immediately must be cleared up: Firstly, what are the smaller segments of the program? Secondly, how are the contents of these segments decided upon? And thirdly, how are these smaller segments overlaid on top of one another? All three of these questions will be given more attention in the rest of the thesis, but an introductory explanation is given here.

#### Granularity

The first question, what comprises the specific smaller segments that are put together in overlays, is a question of granularity. Different overlay schemes will decide on different levels of granularity depending on the use case in question. For instance, an early example of an automatic overlay generation scheme from IBM [5] uses *modules* as its level of granularity. Modules are here understood as individual files containing several functions. Function-level granularity is also very commonly used [7][15], where an overlay is composed of one or several functions. Another possibility is a sub-function granularity, which splits functions where necessary to improve the memory footprints of large functions [15]. Finally, although not found much in more recent years, another example of a type of granularity was found in the GIER ALGOL compiler from 1965 [16]. An early version of an automatic overlay scheme, it generated what can be thought of as prototypical automatic overlays by linearly segmenting the program into smaller parts comprising a set amount of words. These pieces were automatically swapped into memory; efficient use of this scheme would have to avoid e.g. placing a loop in

<sup>&</sup>lt;sup>5</sup>Our RISC-V port can be found here: https://github.com/solbjorg/oberon-riscv

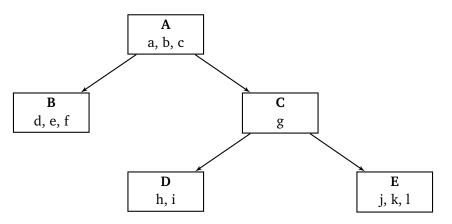

Figure 2.5: An example of an overlay tree.

between two segments, as that would cause it to repeatedly load each segment as the loop iterates [17].

#### Contents of an overlay

The contents of an overlay are determined both by the granularity of the overlays as well as the specific behaviour of the program. Commonly, it has been the programmer's task to determine which code segments can be overlaid on top of one another, manually creating an overlay tree [13][5]. An example of such an overlay tree can be seen in Figure 2.5. The overlays are named **A**, **B**, **C**, ..., and are composed of code segments *a*, *b*, *c*, ..., of which the segments' sizes determine how many can fit into a single overlay. In this example, overlay **A** is the root of the overlay tree, and must always be resident in memory, such that overlays below it in the tree are able to return to it after finishing execution. Overlays **B** and **C** can be overlaid, as there is no edge between them; the same goes for overlays **D** and **E**. The longest path in this overlay tree is from **A** to **C** to **D** and **E**, where if code in overlay **E** is executing then **A** and **C** must also be resident in memory. If the overlay tree is manually generated, then the programmer must be careful to overlay things in such a way that a tree requiring a minimal amount of memory, while having decent performance, is generated.

A useful way of determining which code segments should be in memory simultaneously is interference, a measure of how many times code segments call one another [6]. If code segments that frequently call one another are placed in the same region of memory, such that the calling code segment will repeatedly have to be replaced with the called code segment (and vice versa for returning), performance will suffer. Interference thus captures an important relationship when considering strategies for code overlays, as a high amount of interference will lead to a large amount of time spent loading code segments into main memory, something that should be minimised as much as possible for acceptable performance.

#### **Overlaying mechanism**

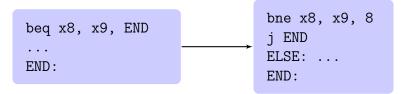

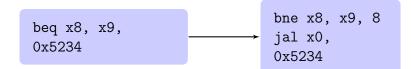

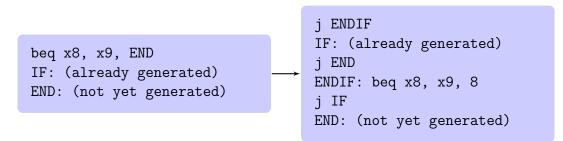

After the code segments to be overlaid on top of one another have been determined, a missing piece is still how the program actually loads code segments from disk to memory as they are needed. This is usually done by the overlay manager (OVM), which has the responsibility of intercepting jumps to code that is currently not loaded, and loading the necessary code segments [13][18]. Such interception requires some cooperation from the linker, which has the responsibility of generating overlays and fixing up code such that it cooperates with the overlay manager. A basic overlay manager would work in the following way, where A and B are code segments of any granularity:

- 1. A needs to jump to a location in B

- 2. A calls the overlay manager, which checks if B is loaded into memory

- a. If B is loaded into memory, then the overlay manager branches to B, passing along the parameters from A (if there are any)

- b. If B is **not** loaded into memory, then the overlay manager calls a code segment loader that loads B, then branches to B, passing along the parameters from A (if there are any)

- 3. B executes

- 4. B returns to A, which must still be in memory

There are, however, a few points worth considering that potentially add to the complexity of an overlay manager.

Firstly, for reasonable performance, item 2*a* needs to be efficient, as every call to overlaid code has to perform this check.

Secondly, in items 2a and 2b, parameters are passed through the overlay manager to the code segment being called. The exact mechanism for doing this will necessarily be dependent on the calling convention in use. To give a simplified example, if parameters are entirely passed on the stack, the overlay manager can quite easily transparently forward the procedure call by modifying the stack pointer. If parameters are passed entirely using registers, then the overlay manager must ensure that the registers have the correct parameters loaded before calling B. Whatever solution is used will be complicated by the overlay manager having to call other procedures in the case of 2b, as it must then make sure to efficiently save and restore parameters as needed.

Thirdly, in item 4, it is necessitated that A is still in memory, as otherwise, if A is not in memory and has been rewritten, it will return to where A branched to B, which may now be data or a different code segment, likely causing the program to crash. This is what gave rise to the tree approach of laying out code segments that can be overlaid. An alternative is to intercept returns as well, and perform a similar series of steps as given above. If this is done, any code segment can be overlaid with any other [7][6].

#### 2.3.2 Automatic overlays

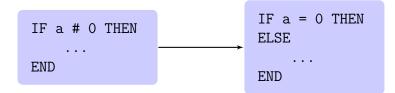

Cytron, et al. mention a few motivations for automating the generation of overlays in [5], and although the paper was written in 1986, these considerations are still relevant today [6]. To summarise, automatically generated overlay structures are desirable because, not only does it save the programmer from having to redesign the overlay tree following small changes in code, but it also greatly reduces the chance of programmer error. Programmer error can mean simply not finding an ideal overlay structure through manual inspection — as they can be quite complex — but also outright mistakes that will lead to a broken program, e.g. if two codependent code segments are overlaid on top of one another (assuming a tree structure as described in Section 2.3.1).

The decision to use automatic overlays was made in a similar project to this thesis, where automatic overlays were used to reduce the memory footprint of the Linux kernel for embedded applications [7]. Their strategy in particular relied on generating overlays after linking through static analysis of the kernel's control flow graph, to find ideal clusters of code. The strategy required a certain amount of kernel code to always be resident in memory, such as trap/interrupt handlers, memory management, etc. All other code could be overlaid, using a separate code buffer that held one code overlay at a time; if a new overlay was needed, the calling overlay was evicted to make room for the new one. This will, in the rest of the thesis, be referred to as a *code buffer* strategy.

To improve performance, certain parts of the kernel that constituted hot code, i.e. code that saw very frequent use, was not overlaid. A separate variable  $\gamma$  is used to determine how much code should be allowed to always stay resident in memory, rather than be overlaid. Their study sees performance improve by an order of magnitude by placing hot code in resident memory, as it no longer has to be loaded into memory every time it is needed [7].

Another thing of note is that some particular difficulties with overlaying operating systems (and kernels) are given. However, most of them do not apply to the Oberon system: for instance, handwritten assembly code is given as an example of code that is difficult to analyse, but that does not exist in the Oberon system. Similarly, Oberon's lack of interrupts (at least in the RISC-V version [1]) simplifies a great deal, as the situation wherein overlaid code is interrupted does not have to be considered.

## 2.4 Multi-objective optimisation and Pareto optimality

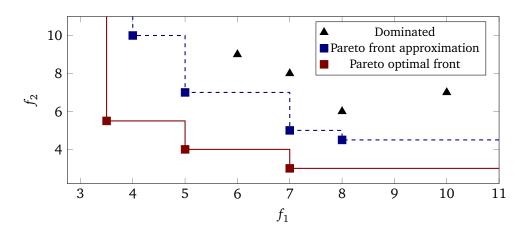

In evaluating different strategies of overlaying code, there are many different objectives one can optimise for. Examples of these are worst-case execution time (WCET), average-case execution time (ACET), minimising interference, memory footprint, and code size. Furthermore, many such objectives directly conflict, such that optimising for one will worsen the other, such as code size and performance; loop unrolling, for instance, improves performance at the expense of increased

**Figure 2.6:** The relationship between the Pareto optimal front, the approximate Pareto optimal front, and dominated solutions. Adapted from a figure in [19].

code size. In comparing different overlay strategies, a basic understanding of how one can evaluate their success at optimising for a combination of opposed objectives will be useful. The most relevant objectives to this thesis will be performance and memory footprint.

In [19], multi-objective optimisation is done in the context of real-time embedded systems, within which there are many objectives to optimise for. A similar approach will be used to evaluate different strategies for code overlays, based on identifying approximate Pareto efficient solutions, as well as identifying solutions that are dominated by other solutions. As such, a quick explanation of Pareto dominance, Pareto optimal solutions, the Pareto front, and the approximate Pareto front will be given.

Let a vector in this context be composed of every objective towards which one can optimise; the optimisation in this case will assume that objectives should be as minimised as possible. (If they are to be maximised, multiplying the objective by -1 suffices [19].) A vector u dominates vector v if u is partially less than v, i.e. at least one of its objectives are smaller without any other objectives being higher [20]. A solution is *Pareto optimal* if no other solution dominates it [20].

However, proving Pareto optimality is computationally infeasible for many problems, and as such the goal in this thesis is instead to identify solutions that are approximately Pareto optimal [19]. While we cannot prove whether a given solution is Pareto optimal, we *can* assess whether other solutions are dominated by it. In so doing, a set of potentially desirable solutions are given (depending on which objective one wishes to optimise for), while undesirable solutions are discarded. An example scenario showing the relationship between the Pareto optimal front, the approximate Pareto optimal front, and dominated solutions for two objective functions is depicted in Figure 2.6; squares indicate (approximate) Pareto optimal solutions, and triangles indicate dominated solutions. Finally, note that even if a solution is Pareto optimal, it might have unacceptable characteristics: a solution that optimises entirely for one objective function at the expense of all others may be Pareto optimal, without being desirable; ideally, a good solution should be within acceptable bounds for all objective functions [19].

# **Chapter 3**

# Design

In order to support code overlays in the Oberon system, many separate pieces had to be designed and developed.

This chapter begins with an overview of the designed system in Section 3.1. The rest of the chapter is split into two parts. The first part covers the *mechanism* supporting overlays, including compiler support; loading, linking, and creating overlays; and the overlay manager. The second part concerns the different *strategies* for what constitutes an overlay, as well as when an overlay should be loaded into and out of memory. This part also explains aspects that needed to be developed to support the given strategies.

The first part, concerning the mechanism, proceeds as follows. First of all, the overlay mechanism itself, which is responsible for branching from one overlay to another, and loading the new overlay if necessary, is presented in Section 3.2; the process of linking and generating overlays is presented in Section 3.3. Ways to efficiently load code from secondary storage to memory also had to be developed; these are presented in Section 3.4. Finally, a strategy for position-independent code, which avoids every procedure call having to go through the overlay manager, is developed in Section 3.5.

This is followed by an explanation of the different strategies for creating overlays and placing them in memory, and the development thereof. Section 3.6 presents the two strategies by which overlays are placed in memory, one which allows only one overlay to be loaded at a time and another which allows multiple; to support the second method, changes were made to the Oberon garbage collector, presented in Section 3.7. Finally, concrete strategies for creating overlays and placing them are presented in Sections 3.8 and 3.9, which detail module-granularity and function-granularity overlays respectively.

# 3.1 A design overview

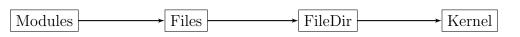

This chapter will detail the design and implementation of the many disparate parts that, put together, make up the overlay system developed in this thesis. To aid the

| Modules  |

|----------|

| Overlays |

| Files    |

| FileDir  |

| Kernel   |

**Figure 3.1:** The modified inner core of the Oberon system, when code overlay support is added.

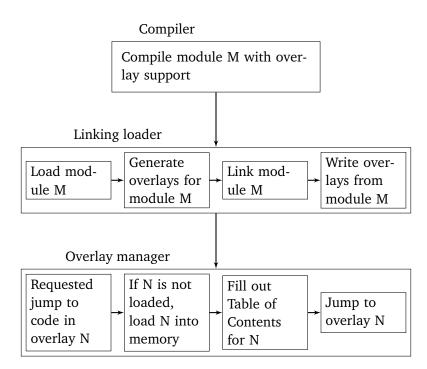

Figure 3.2: The overarching design that will be detailed in Chapter 3.

reader's understanding, this section will give an overview of what each part of the system is doing, and how they fit together.

As noted in Section 2.2.4, booting the Oberon system consists of several phases, starting with the *inner core*, which is responsible for loading the *outer core*. This inner core consists of the kernel, the file system, and the dynamic linking loader. We will be overlaying the outer core, as well as anything loaded on top of it; therefore, the inner core must be changed to support this. This is done by adding a new module, **Overlays**, which is responsible for both the creation and the management of overlays. The new layout of the inner core can be seen in Figure 3.1. As shown, it is placed just below **Modules**, which contains the linking loader. This is because the linker must use the overlay system to correctly link code.

Figure 3.2 shows the overarching design of the system that will be explained in detail in this chapter. It consists of three parts, namely the compiler, the linking

#### Chapter 3: Design

loader, and the overlay system. The overlay system itself is the most significant addition.

Firstly, several changes were made to the compiler, to add information in the header regarding the locations of procedures as well as to correctly handle jumps to overlaid code segments. Additional changes were also made to support position-independent code, such that code can be placed anywhere in memory. Secondly, changes had to be made to the dynamic linking loader. As it is dynamic, the creation of overlays cannot be done before runtime without changing the funda-mental design of the linker, as overlays have to be made out of linked code. Thirdly, the overlay system itself had to be built. This is responsible for loading, evicting, and branching to overlaid code. All these aspects will be briefly described here, before they are given a more detailed explanation in their respective sections.

We will in this section first pay attention to the *mechanism* by which overlays are created, loaded, and branched to, followed by an overview of the *strategy* that governs what constitutes an overlay, and when they should be loaded into and out of memory. These explanations are purposefully left somewhat superficial; the details of each part are given in the rest of this chapter.

#### 3.1.1 Mechanism