Martin Rebne Farstad

# Understanding the Key Performance Trends of Optimized Iterative Stencil Loop Kernels on High-End GPUs

Master's thesis in Computer Science Supervisor: Magnus Jahre June 2021

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

Martin Rebne Farstad

# Understanding the Key Performance Trends of Optimized Iterative Stencil Loop Kernels on High-End GPUs

Master's thesis in Computer Science Supervisor: Magnus Jahre June 2021

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Computer Science

# **Problem Description**

Iterative Stencil Loops (ISLs) are the performance bottleneck of many problems within computational science, and the objective of this thesis is to better understand the key performance trends of ISLs on high-end GPUs. The student is hence expected to conduct an extensive performance analysis of highly optimized ISL kernels and thereby identify and explain key performance trends. Meeting this objective will require significant implementation work. First, the student should implement ISL kernels for both 2D and 3D problem domains. Second, they should investigate the performance impact of commonly used optimizations such as using shared memory, thread coarsening, and autotuning. Third, the student should identify numerous stencil types from a wide range of ISL applications and explore to what extent performance trends are stencil-dependent. If time permits, the student should investigate how the implemented code scales on tightly-coupled multi-GPU systems such as the NVIDIA DGX-2.

# Abstract

Iterative Stencil Loops (ISLs) are the main computational kernel of many applications within computational science. This thesis explores the key performance trends of ISLs on high-end GPUs through an extensive performance analysis of individual and combinations of optimizations. The optimizations include utilizing shared memory, thread coarsening, and autotuning thread block dimensions for optimizing Reverse Time Migration stencils in 2D and 3D domains. We benchmark our ISL application on two modern GPU architectures: Pascal (P100) and Volta (V100), observing up to 20.3x (12.7x) and 6.07x (3.34x) increased performance for Volta's shared memory kernel over Pascal's baseline kernel in 2D (3D) for 128 MiB and 8 GiB domains, respectively. We crucially find that device memory write (local memory) throughput bottlenecks our 2D (3D) kernels on Volta and suggests that cache utilization composes the performance bottleneck for Pascal. Our optimizations improve the kernels' performance over the architectures' respective baseline kernels by up to 1.47x (1.36x) on Volta and 3.64x (1.44x) on Pascal in 2D (3D) by improving the bottlenecks. Finally, we extend our optimization approach by utilizing up to 16 V100 GPUs. Our multi-GPU scheme achieves near-linear performance scaling by offloading the workload onto more devices, increasing performance over single-GPU by up to 14.8x.

### Sammendrag

Iterative stensil-løkker (ISL) er hovedberegningskjernen til mange applikasjoner innen beregningsvitenskap. Denne masteroppgaven utforsker de viktigste ytelsestrendene for ISL-applikasjoner ved hjelp av spesielt kraftige grafikkprosessorer ved å gjennomføre en omfattende ytselsesanalyse av individuelle og kombinasjoner av optimaliseringer. Optimaliseringene inkluderer bruk av delt minne, trådforgrovning og autotuning av trådblokkdimensjoner for å optimalisere "Reverse Time Migration"-stensiler for to- og tredimensjonale domener. Vi evaluerer applikasjonen vår på to moderne arkitekturer: Pascal (P100) og Volta (V100), og observerer ytelsesforbedringer på opp til 20.3x (12.7x) og 6.07x (3.34x) for Volta's kjerne med delt minne i forhold til Pascal's enkleste kjerne for todimensjonale (tredimensjonale) domener med domenestørrelser henholdsvis på 128 MiB og 8 GiB. Vi oppdager at skrivehastigheten til hovedminnet (lokalt minne) er en flaskehals for applikasjonen vår med to (tre) dimensjoner på Volta og indikerer at hurtigminne utgjør flaskehalsen for Pascal. Optimaliseringene våre forbedrer kjerneytelsen i forhold til arkitekturenes respektive enkleste kjerner med opp til 1.47x (1.36x) på Volta og 3.64x (1.44x) på Pascal for todimensjonale (tredimensjonale) domener ved å forbedre flaskehalsene. Videre utvider vi optimaliseringsmetoden vår til å anvende opp til 16 V100 grafikkprosessorer. Ved å fordele arbeidsmengden mellom grafikkprosessorerene klarer vi å oppnå tilnærmet lineær ytelsesskalering som øker ytelsen i forhold til én grafikkprosessor med opp til 14.8x.

# Preface

The thesis builds upon our previous work [1] for the specialization project performed in Fall 2020 for the TDT4501 course. The project applied the Jacobi method to approximate the numerical solution of Laplace's equation in 2D by iteratively calculating a five-point stencil. The project utilized shared memory, grid synchronization through Cooperative Groups, autotuned thread block dimensions, multiple GPUs (up to four V100 GPUs in a different system), and a technique to prevent unnecessary inter-GPU synchronization. However, we configured the baseline thread block dimensions naively and did not optimize occupancy. Crucially, the previous implementation was considerably more superficial, and the analysis was shallow and gave limited insights.

Our previous project's weaknesses motivated our decision to significantly extend our implementation, perform a more comprehensive performance analysis, and locate the performance bottlenecks. This thesis is an extensive extension of the previous work that includes optimizations that improve performance significantly for different stencils in 2D and 3D. Additionally, introducing 3D presents significant implementation complexities and different application behavior. This thesis also generalizes the concept of stencil computations from a specific iterative method to ISLs in general, targeting a broader audience.

As our previous work implemented the Jacobi method on GPUs, certain parts of the background material are relevant for this thesis. However, we do not expect the reader to have read our previous work, so we base certain parts of our background material on our previous work to include all overlapping aspects. This adaptation is standard practice at NTNU, and we presently present which parts of our background our thesis bases on and to which degree it overlaps with our previous work:

- Section 1.1 bases certain parts of the GPU architecture theory on our previous work.

- Section 2.2 bases certain parts of the execution model and thread synchronization theory on our previous work.

- Section 2.6 bases most parts on our previous work.

# Contents

| Pr  | obler  | m Description                            | iii          |

|-----|--------|------------------------------------------|--------------|

| Ab  | ostrac | zt                                       | $\mathbf{v}$ |

| Sa  | mme    | endrag                                   | vii          |

| Pr  | eface  | 9                                        | ix           |

| Co  | onten  | ts                                       | xi           |

| Fig | gures  | 3                                        | iii          |

| Та  | bles   |                                          | xv           |

| Co  | ode Li | istings                                  | vii          |

| 1   | Intr   | oduction                                 | 1            |

|     | 1.1    | Motivation                               | 1            |

|     | 1.2    | Assignment Interpretation                | 3            |

|     | 1.3    | Contributions                            | 3            |

|     | 1.4    | Outline                                  | 4            |

| 2   | Bacl   | kground                                  | 5            |

|     | 2.1    | Iterative Stencil Loops                  | 5            |

|     |        | 2.1.1 Stencil Patterns                   | 5            |

|     |        | 2.1.2 Spatial and Temporal Blocking      | 7            |

|     | 2.2    | General-Purpose GPU Computing Using CUDA | 8            |

|     |        | 2.2.1 Execution Model                    | 8            |

|     |        | 2.2.2 Thread Synchronization             | 10           |

|     | 2.3    | The GPU Memory Architecture              | 10           |

|     |        | 2.3.1 Registers                          | 10           |

|     |        | 2.3.2 Shared Memory                      | 11           |

|     |        | 2.3.3 Unified Cache                      | 12           |

|     |        | 2.3.4 High Bandwidth Memory              | 13           |

|     | 2.4    | Desirable GPU Characteristics            | 14           |

|     |        | 0                                        | 14           |

|     |        | 2.4.2 Effective Resource Utilization     | 15           |

|     |        | 2.4.3 Avoiding Branch Divergence         | 16           |

|     | 2.5    | Single-GPU Optimization Approaches       | 16           |

|     |        | 2.5.1 Thread Coarsening                  | 16           |

|     |        |                                          | 18           |

|     | 2.6    | Utilizing Multiple GPUs                  | 19           |

|     |        | 2.6.1 Domain Partitioning                | 19           |

|     |        |                                          | 20           |

|     |      | 2.6.3  | Handling Inter-GPU Communication             | 21 |

|-----|------|--------|----------------------------------------------|----|

| 3   | Imp  | lement | ing Optimized ISL Kernels                    | 23 |

|     | 3.1  | ISL Ke | rnels                                        | 24 |

|     |      | 3.1.1  | The Baseline Kernel                          | 24 |

|     |      | 3.1.2  | Coarsening the Baseline Kernel               | 26 |

|     | 3.2  | Shared | d Memory ISL Kernels                         | 26 |

|     |      | 3.2.1  | The Hybrid Shared Memory Kernel              | 26 |

|     |      | 3.2.2  | Coarsening the Hybrid Shared Memory Kernel   | 29 |

|     |      | 3.2.3  | The Padded Shared Memory Kernel              | 31 |

|     |      | 3.2.4  | Coarsening the Padded Shared Memory Kernel   | 35 |

|     | 3.3  | Launcl | hing ISL Kernels                             | 36 |

|     |      | 3.3.1  | Allocating Resources                         | 36 |

|     |      | 3.3.2  | Kernel Configuration                         | 38 |

|     |      | 3.3.3  | Launching Single-GPU Kernels                 | 40 |

|     |      | 3.3.4  | Launching Multi-GPU Kernels                  | 41 |

| 4   | Exp  | erimen | tal Setup                                    | 43 |

|     | 4.1  | Hardw  | <i>r</i> are Setup                           | 43 |

|     | 4.2  | Measu  | rements                                      | 44 |

|     |      | 4.2.1  | Kernel Timing                                | 44 |

|     |      | 4.2.2  | Metric Collection                            | 45 |

|     |      | 4.2.3  | Reporting Measurements                       | 45 |

|     | 4.3  | Execut | tion Configurations                          | 47 |

|     |      | 4.3.1  | Stencils                                     | 47 |

|     |      | 4.3.2  | Stencil Configurations                       | 48 |

| 5   | Rest |        |                                              | 49 |

|     | 5.1  | Optim  | izing ISL Kernels on the Volta Architecture  | 49 |

|     |      | 5.1.1  | 5                                            | 49 |

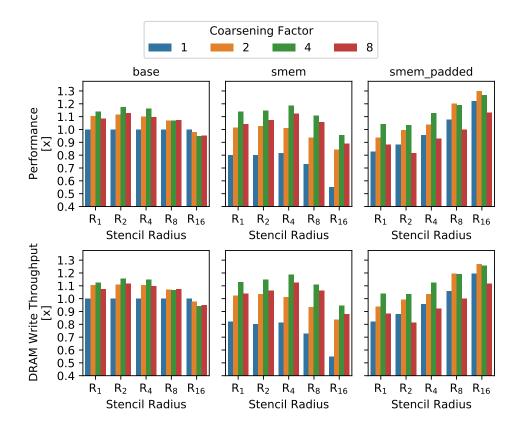

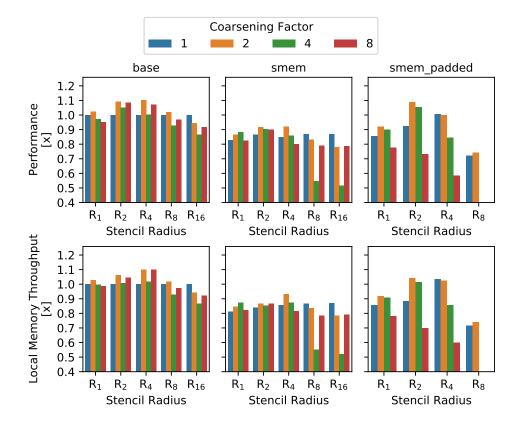

|     |      | 5.1.2  | Thread Coarsening                            | 52 |

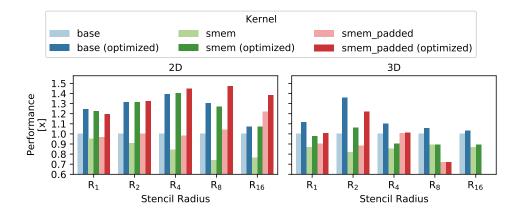

|     |      | 5.1.3  | Autotuning                                   | 55 |

|     | 5.2  | -      | izing ISL Kernels on the Pascal Architecture | 58 |

|     |      | 5.2.1  | Shared Memory                                | 58 |

|     |      | 5.2.2  | Thread Coarsening                            | 60 |

|     | 5.3  |        | GPU                                          | 62 |

| 6   |      |        | and Future Work                              | 65 |

|     | 6.1  |        | ision                                        | 65 |

|     | 6.2  |        | e Work                                       | 65 |

|     |      | 6.2.1  | Spatial and Temporal Blocking                | 65 |

|     |      | 6.2.2  | Stencil Patterns                             | 66 |

|     |      | 6.2.3  | Iteration Patterns                           | 66 |

|     |      | 6.2.4  | Case Studies                                 | 67 |

|     |      | 6.2.5  | Autotuning                                   | 67 |

|     |      | 6.2.6  | Improving Inter-GPU Communication            | 67 |

| Bil |      |        |                                              | 69 |

| Α   | Auto | otuned | Thread Block Dimensions                      | 75 |

# Figures

| 1.1                                                                                                                | An example distribution of a multi-core CPU vs. a many-core GPU .                                                                                                                                                                                                                | 2                                    |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol> | Calculating a Jacobi iteration of an RTM stencil in 2D and 3D<br>Spatial blocking in 3D                                                                                                                                                                                          | 6<br>9<br>13<br>14<br>16<br>18<br>20 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                             | Shared memory layouts for the smem kernel in 2D and 3D Shared memory layouts for the smem_coarsened in 2D and 3D Increasing shared memory reuse through thread coarsening Shared memory layout for the smem_padded kernel for 2D and 3D Visualizing smem_padded's prefetch stage | 27<br>29<br>31<br>32<br>32<br>36     |

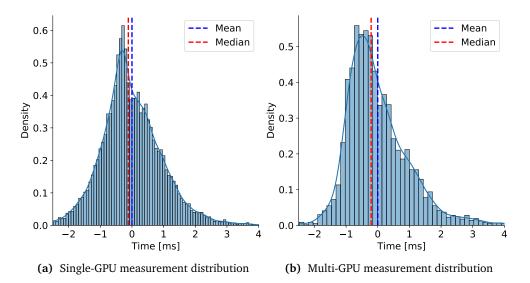

| 4.1<br>4.2                                                                                                         | Single-GPU and multi-GPU measurement distribution                                                                                                                                                                                                                                | 46<br>47                             |

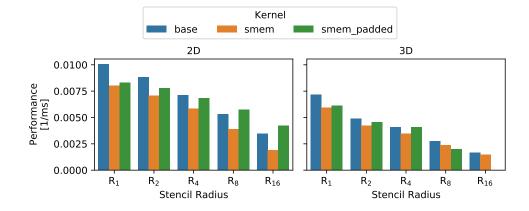

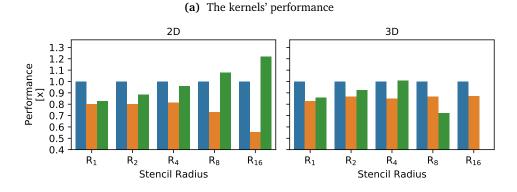

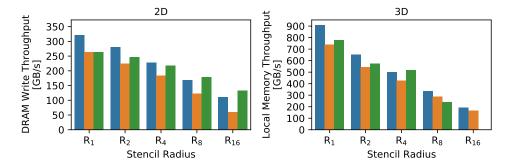

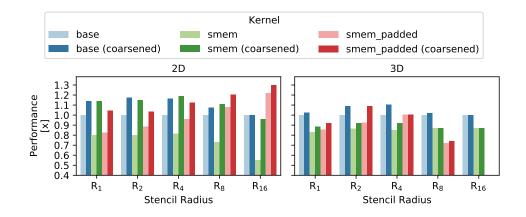

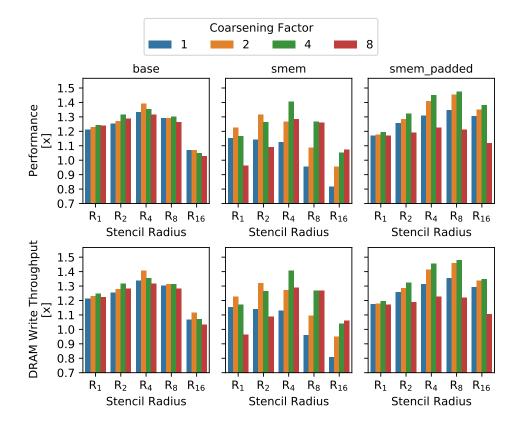

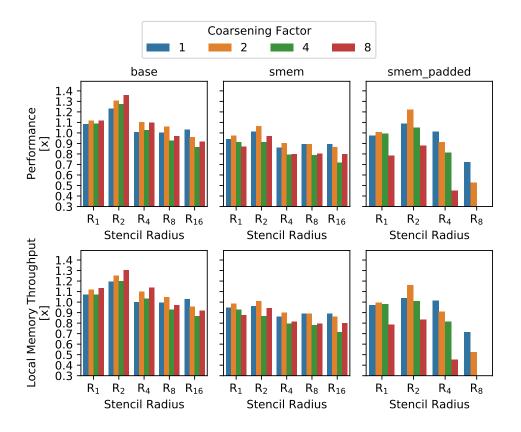

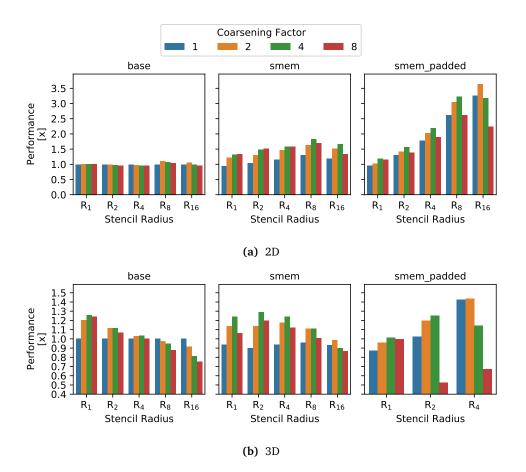

| 5.1<br>5.2<br>5.3                                                                                                  | Kernel performance and metrics on Volta                                                                                                                                                                                                                                          | 50<br>51<br>52                       |

| 5.4<br>5.5                                                                                                         | Coarsened kernels with heuristic thread block dimensions in 2D Coarsened kernels with heuristic thread block dimensions in 3D                                                                                                                                                    | 53<br>54                             |

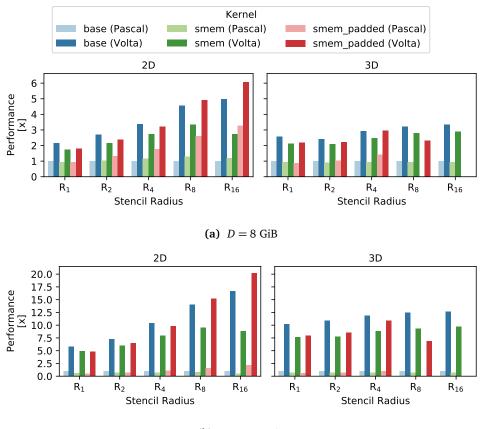

| 5.6<br>5.7<br>5.8                                                                                                  | Uncoarsened kernels (heuristic) vs. coarsened kernels (autotuned)<br>Coarsened kernels with autotuned thread block dimensions in 2D .<br>Coarsened kernels with autotuned thread block dimensions in 3D .                                                                        | 55<br>56<br>57                       |

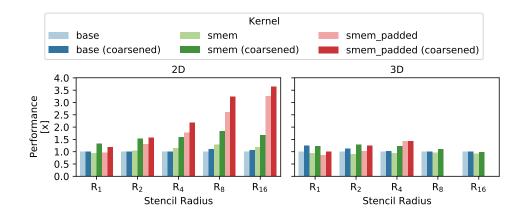

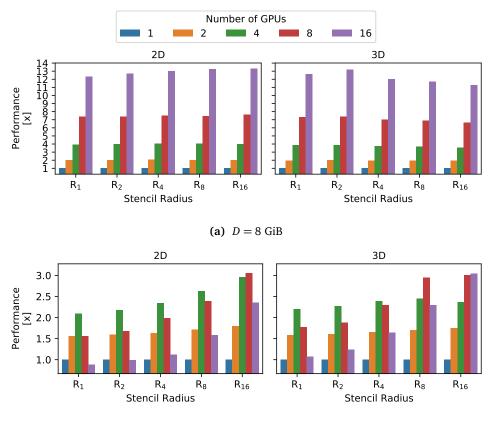

| 5.9                                                                                                                | Comparing uncoarsened kernels (heuristic): Volta vs. Pascal<br>Uncoarsened vs. coarsened kernels (heuristic) on Pascal                                                                                                                                                           | 59<br>60                             |

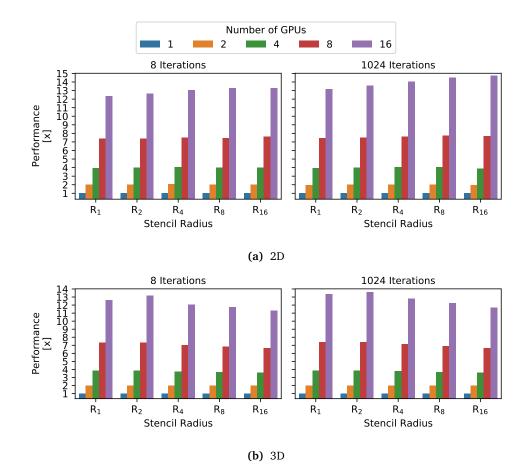

| 5.11                                                                                                               | Coarsened kernels (heuristic) in 2D and 3D on Pascal                                                                                                                                                                                                                             | 61<br>63                             |

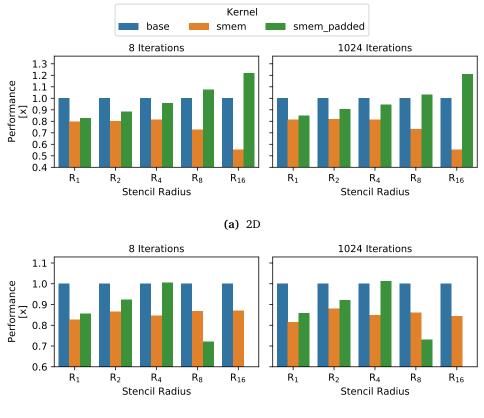

|                                                                                                                    | Comparing stencil iterations on multi-GPU: 8 vs. 1024                                                                                                                                                                                                                            | 64                                   |

# **Tables**

| Constants frequently used in our ISL application                                                                       |  |

|------------------------------------------------------------------------------------------------------------------------|--|

| DGX-2 vs. Idun cluster node                                                                                            |  |

| Autotuned 2D TB dimensions (blockDim.x, blockDim.y)<br>Autotuned 3D TB dimensions (blockDim.x, blockDim.y, blockDim.z) |  |

# **Code Listings**

| 3.1  | The base kernel                                                | 25 |

|------|----------------------------------------------------------------|----|

| 3.2  | The base stencil                                               | 25 |

| 3.3  | Global memory stencil accumulators                             | 25 |

| 3.4  | The base_coarsened kernel                                      | 26 |

| 3.5  | The smem kernel                                                | 27 |

| 3.6  | The smem stencil                                               | 28 |

| 3.7  | Hybrid global/shared memory stencil accumulators               | 28 |

| 3.8  | The smem_coarsened kernel                                      | 30 |

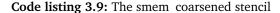

| 3.9  | The smem_coarsened stencil                                     | 30 |

| 3.10 | The smem_padded kernel                                         | 33 |

| 3.11 | The smem_padded stencil                                        | 33 |

| 3.12 | Prefetching values into shared memory for smem_padded          | 34 |

| 3.13 | Prefetch functions                                             | 34 |

| 3.14 | The smem_padded_coarsened kernel                               | 35 |

| 3.15 | Allocating GPU memory in parallel                              | 37 |

| 3.16 | Transferring memory between host and GPUs in parallel          | 37 |

| 3.17 | Maximizing dynamic shared memory allocation size               | 39 |

| 3.18 | Distributing threads between the thread block dimensions       | 39 |

| 3.19 | Configuring shared memory allocation size                      | 39 |

| 3.20 | Launching single-GPU kernels                                   | 40 |

| 3.21 | Utility function for configuring shared memory allocation size | 40 |

| 3.22 | Transferring ghost zone elements between neighboring GPUs      | 41 |

| 3.23 | Launching multi-GPU kernels                                    | 42 |

### Chapter 1

# Introduction

### 1.1 Motivation

ISLs are the key computational kernel within a range of compute-intensive applications, including image processing, data mining, weather- and climate modeling, as well as physical simulations such as seismic or fluid simulations [2, 3]. ISLs are among the most important computational kernels of contemporary and future applications, residing within the category of structured grids [4]. In a multidimensional discretized grid, the method computes each element as a function of its neighbors. The number of neighbors calculated depends on the number of dimensions at hand and the stencil's size. This technique often simulates a time-step (e.g., Conway's Game of Life [5]) that can converge to a solution (e.g., iterative methods [6]). Initially, ISLs were studied widely for CPU applications [7–10]. ISLs often compose large parts of applications' total execution time (up to 100% for SPEC 2017's Lattice Boltzmann Method [3, 11]), motivating the interest for offloading such computations onto high-performant accelerators [12].

Although initially proposed as a hardware-accelerator for computing specialized graphics computations in parallel [13, p. 8], Graphics Processing Units (GPUs) extended their domain onto general-purpose computing by realizing high performance through a highly parallel execution model by extensive latency hiding. Utilizing the vast amount of threads for parallelism, GPUs became the de facto hardware accelerator for compute-intensive applications within High-Performance Computing. Meanwhile, energy-constrained environments make offloading stencil computations onto FPGAs also widely recognized [3, 14, 15]. Utilizing GPUs as accelerators for processing ISLs has been studied extensively in the last decade [2, 16–18]. ISLs' widespread importance sparks the need for efficient GPU implementations. However, as we will show later, the applications' performance depends on the underlying GPU architecture. Therefore, this thesis studies ISLs on two GPU architectures: Pascal and Volta.

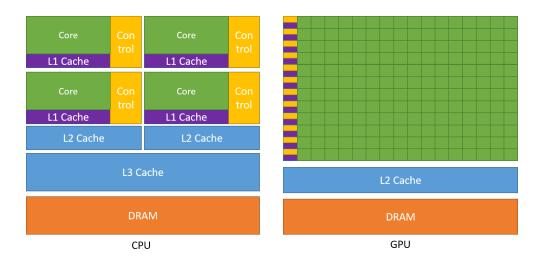

As presented in Figure 1.1, the GPU differentiates itself from the CPU by allocating more on-chip area for execution units as a trade-off for cache and control flow logic like branch predictors and prefetchers. The GPU's programming model

**Figure 1.1:** The figure displays an example distribution of a multi-core CPU vs. a many-core GPU. More transistors are devoted to computation in GPUs. From [19, p. 2]. Reprinted with permission from Nvidia.

does not require such resources to find runtime parallelism because this is the programmer's task. The GPU architectures emphasize high throughput through many lower-frequency cores compared to the CPU's few high-frequency cores. As a result, the GPU programming model's weak spot is high latency, making applications with limited parallelism better suited for CPUs than GPUs.

The GPUs employ an array of Streaming Multiprocessors (SMs) to achieve extensive hardware parallelism [13, p. 68]. Each row in Figure 1.1's simplified GPU architecture layout represents an SM comprising an L1/unified cache, control units, and numerous execution units. GPUs also achieve significant parallelism by employing fast context switches and lightweight threads [13, p. 90]. The ISLs' grid-structured problem domains map elegantly to the many-core GPU architectures. The cores' incredible parallelism composes a powerful tool to solve ISLs.

The Compute Unified Device Architecture (CUDA) [19] serves as the primary platform for Nvidia GPUs currently dominating the market, which we focus on in this work. CUDA enables implementing ISLs on GPUs at a relatively low abstraction level but enables the programmer more detailed optimizations to prevent redundant memory requests to the device memory (e.g., shared memory or register caching [20]) or increase the number of in-flight memory requests (e.g., thread coarsening [21, 22]). Furthermore, optimizing ISLs require significant attention to memory access patterns to avoid redundant accesses to the device memory [13, p. 158]. Moreover, using automatic code generation tools to aid optimization is possible [12, 23]. However, modern GPU architectures improve ISLs' performance inconspicuously for the programmer, making naive implementations highly competitive [24]. Therefore, we wish to investigate the performance gap between naive and more advanced implementations for contemporary architectures.

Modern domain workloads for ISLs rapidly exceed the capacity of a single

GPU, motivating the need to offload computation onto more GPUs. Distributing workload between multiple GPUs is an excellent optimization for improving performance. Additionally, multi-GPU also improves performance tremendously for moderate domain sizes, offering a great optimization to combine with one or more single-GPU optimizations. However, the addition of numerous GPUs comes at a cost. Operating multiple devices requires creating GPU contexts associated with each device. Furthermore, the GPUs' asynchronous execution implies a need for proper synchronization to ensure program correctness. The synchronization implies an overhead to the application and requires synchronization through the host or between the devices themselves. Finally, we need to make sure our multi-GPU scheme is scalable by making the application's source code handle an arbitrary number of GPUs. Scalable multi-GPU applications can potentially increase performance linearly with the number of GPUs added.

### 1.2 Assignment Interpretation

The problem description states that our main objective is to better understand the key performance trends of ISLs on high-end GPUs through an extensive performance analysis of highly optimized ISL kernels. To state our interpretation of the problem description, we define the following tasks:

- T1 Implement an ISL application in 2D and 3D and explain the key performance impacts of moving from 2D to 3D.

- T2 Optimize the ISL application's kernels through utilizing shared memory, thread coarsening, and autotuning. Identify and explain the optimizations' key performance-enhancing factor by localizing the application's performance bottlenecks on high-end GPUs.

- T3 Include numerous stencils from multiple ISL applications and explain to which extent the performance trends depend on the stencil type.

- T4 Compare the ISL application's performance on different high-end GPUs to learn whether our results are architecture-dependent.

- T5 Implement a scalable multi-GPU scheme by distributing the workload between more GPUs and analyze its scaling capabilities.

### 1.3 Contributions

We describe our contributions by highlighting their objective task in parentheses. This thesis implements an ISL application in 2D and 3D (T1) and contributes a thorough analysis into utilizing a combination of shared memory, thread coarsening, and autotuned TB dimensions (T2) for optimizing Reverse Time Migration (RTM) stencils (T3). Our analysis finds that introducing shared memory achieves the most stencil-dependent performance improvements (T3). Furthermore, we propose a simplistic but powerful scheme for choosing thread block (TB) dimensions heuristically. The approach maximizes occupancy, ensures correct execution,

and provides a baseline to compare against autotuned TB dimensions. Moreover, we investigate the optimizations' key performance trends on two modern GPU architectures: Pascal and Volta, emphasizing the incredible performance improvements achieved by upgrading from Pascal to Volta (T4).

Introducing shared memory kernels improves performance over the architectures' respective baseline kernels by up to 1.22x (1.01x) in 2D (3D) on Volta and 3.27x (1.43x) on Pascal for an 8 GiB domain. Applying thread coarsening improves the kernels' performance over the architectures' respective baseline kernels by up to 1.30x (1.10x) on Volta and 3.64x (1.44x) on Pascal in 2D (3D) for an 8 GiB domain. Autotuning the coarsened kernels' TB dimensions improves performance over the baseline kernel by up to 1.47x (1.36x) on Volta. Comparing Volta's kernels to Pascal's baseline kernel exhibits an incredible 20.3x (12.7x) performance improvement for a 128 MiB domain and 6.07x (3.34x) for an 8 GiB domain in 2D (3D).

Our analysis crucially finds that DRAM write (local memory) throughput bottlenecks our 2D (3D) application on Volta (T2), indicating that moving from 2D to 3D introduces significant register spilling (T1). Unfortunately, we do not have permission to profile our application on Pascal. However, utilizing shared memory has a significant impact on Pascal, indicating that cache utilization composes the performance bottleneck for Pascal instead of DRAM throughput (T2).

Finally, we further improve the performance by partitioning the workload between multiple GPUs (T5), keeping the domain sizes equal to the single-GPU analysis. Consequently, the analysis focuses on strong scaling instead of weak scaling, enabling a more direct comparison of multi-GPU against single-GPU optimizations. Furthermore, the implementation utilizes strip partitioning in 2D and 3D to distribute the workload between devices, enlarging the partitions with ghost zones to ensure correct execution. Our multi-GPU scheme's performance improvements closely resemble the number of GPUs utilized for most executions (T5), increasing performance over single-GPU by up to 14.8x.

### 1.4 Outline

- Chapter 2 introduces the theoretical concepts required to understand the presented implementation and refers to related work.

- Chapter 3 presents and explains the approach for implementing the optimized ISL application and presents the source code.

- Chapter 4 presents the experimental setup for benchmarking the optimized ISL application.

- Chapter 5 presents measurements and analyses our optimized ISL application.

- Chapter 6 concludes our contributions and presents future work for improving the presented implementation.

- Appendix A presents the autotuned TB dimensions generated for our kernels on a single GPU.

### Chapter 2

# Background

The following chapter introduces ISLs and describes multiple stencil patterns commonly used within scientific applications. Subsequently, we propose the motivation for using general-purpose GPU (GPGPU) computing to accelerate our ISL application and describe multiple approaches for optimizing the implementation.

### 2.1 Iterative Stencil Loops

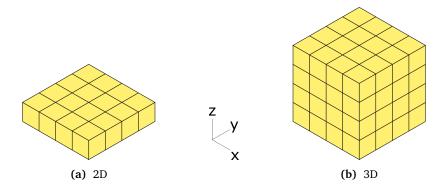

ISLs represent a significant number of compute-intensive applications within High-Performance Computing [3]. ISLs traverse grids and iteratively update cell values based upon their neighboring cells multiplied by a set of coefficients. For every iteration, input cells are read from one buffer and updated in the other before swapping buffers to prepare for the next iteration. The discretized domains range from one to three dimensions, representing a line (1D), plane (2D), or cube (3D). Higher dimensions require calculating more neighboring cells, increasing the GPU's workload. The distance to neighboring elements within the linear memory layout increases along with introduced dimensions, constituting offsets of a line (plane) in 2D (3D) for accessing a value along the last dimension. Additionally, increasing the number of dimensions decreases each domain dimension's size due to limited GPU memory size.

#### 2.1.1 Stencil Patterns

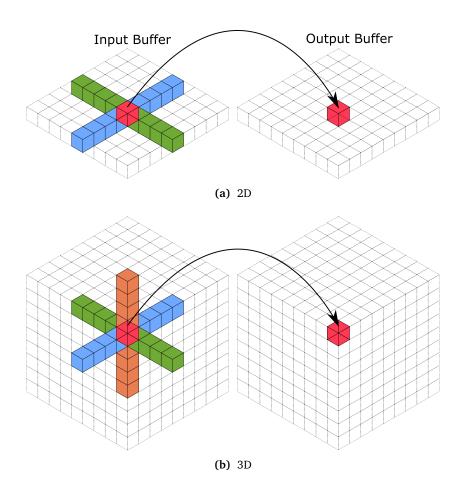

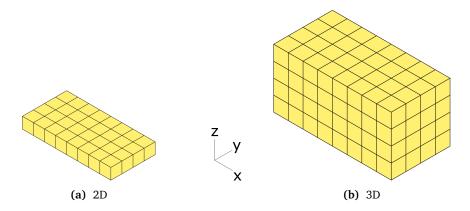

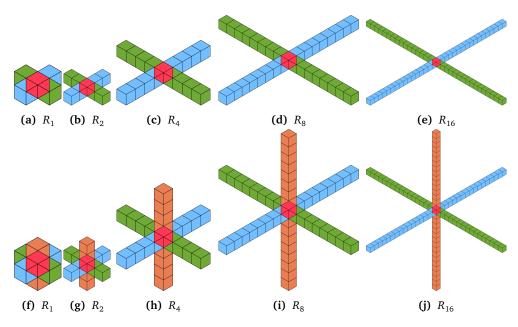

Different stencil patterns exist as a result of the characteristics of widely different underlying methods. The vast number of patterns emerges as the number of underlying methods is extensive. Koraei et al. [3] used three stencil patterns to analyze ISLs on FPGAs: Jacobi, Gauss-Seidel, and RTM. In 2D (3D), their Jacobi pattern featured a 3x3(x3) square (cube), while Gauss-Seidel formed an X-shaped pattern within the same shape. Their RTM pattern featured a cross-shaped pattern within a 5x5(x5) square (cube). This thesis focuses on RTM patterns only, although we analyze the pattern differently; we utilize the same shape, although

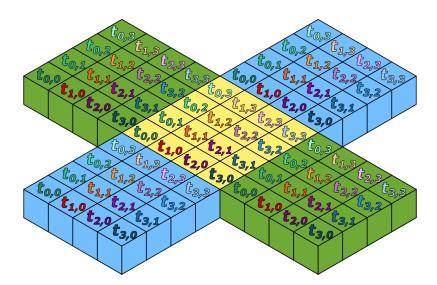

**Figure 2.1:** Calculating a Jacobi iteration of the RTM stencil pattern in 2D and 3D. The green, blue, and brown elements represent the stencil's radius-sized neighborhood within the X-, Y-, and Z-dimension, respectively. The red element represents the value written to the output buffer.

we study more RTM stencil sizes, observing the stencils' impact on GPU resource usage.

We define the stencil's size as the stencil's *radius* and define it as the number of neighboring elements along each dimension from the center. Additionally, we denote a given stencil with stencil radius r by  $R_r$ . Our ISL application uses an input and output buffer for computing the stencil (Jacobi iterations [25, p. 12]). Figures 2.1a and 2.1b display the RTM stencil,  $R_4$ , in 2D and 3D, respectively. The figures compute a Jacobi iteration using the center and neighboring values from the input buffer and write an updated center value to the output buffer. The figures' colors emphasize the stencil's properties: green, blue, and brown elements represent the neighbors read from the input buffer along the X-, Y-, and Z-dimension, respectively. The red element represents the value written to the output buffer. This procedure is repeated for all elements within the input buffer's domain and represents a single ISL iteration.

#### 2.1.2 Spatial and Temporal Blocking

ISLs show considerable spatial locality utilizable by the GPU architecture's caches. Spatial blocking utilizes the caches more efficiently by processing subsets of the domain that fit well into the caches. This technique reduces the pressure on slower memory accesses, further increasing the performance. Temporal blocking reuse input data within the cache before writing to the output buffer. Spatial blocking and temporal blocking is prevalent for optimizing ISLs on CPUs [8, 26–28], GPUs [2, 12, 16, 29, 30], and FPGAs [15, 31, 32].

Spatial blocking provides limited reuse opportunities by reusing each grid point only a few times, depending on the stencil pattern. In general, spatial blocking is insufficient to transform memory-bound kernels into compute-bound [16]. Temporal blocking applies in combination with spatial blocking by calculating subsequent iterations within the spatial block before fully computing the first iteration for the whole domain [15].

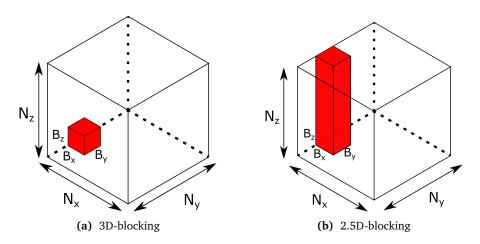

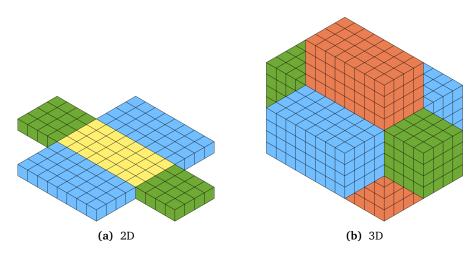

Figure 2.2a visualizes the 3D-blocking algorithm, a commonly used technique for dividing the input into overlapping axis-aligned three-dimensional blocks [16]. The scheme maps effortlessly onto TBs, with each thread handling a single element within the block. The argument is similar for 2D-blocking in 2D. Unfortunately, memory bandwidth essentially limits the scheme's performance. However, the technique imposes fewer requirements on the cache capacity compared to more sophisticated approaches. Therefore, this thesis implements 3D-blocking to ensure compatibility with an arbitrary domain size and proposes more sophisticated blocking algorithms as future work.

Nguyen et al. [16] presented a 3.5D-blocking algorithm for ISLs on CPUs and GPUs that combined 2.5D-spatial and 1D-temporal blocking using on-chip memory. Figure 2.2b visualizes their 2.5D-blocking algorithm, which utilizes the fact that every Z-value required grid values within a stencil radius' range in Z-direction to be resident within the cache. The approach performs blocking through the XY plane and *streaming* through the third dimension. The authors argued that streaming removes bandwidth requirements from the Z-direction by preventing the same elements from being loaded multiple times, leading to substantial performance improvements by achieving near-optimal memory bandwidth utilization. However, this approach requires the cache capacity to include the blocked data.

The authors further argued that temporal blocking is the only way to reduce bandwidth further after implementing 2.5D blocking and provided thread-level and data-level parallel algorithms to utilize computing resources fully. Furthermore, the authors argued that their 3.5D blocking scheme made the ISL application compute-bound, increasing performance significantly by removing the memory bandwidth dependency. Moreover, the authors argue that 4D blocking (3D-spatial + 1D-temporal) improves performance by reducing bandwidth through temporal reuse but emphasize that it introduces significant overhead compared to their 3.5D approach.

Figure 2.2: Spatial blocking in 3D. Based on [16].

### 2.2 General-Purpose GPU Computing Using CUDA

#### 2.2.1 Execution Model

CUDA is a parallel computing platform developed by Nvidia containing a programming model extending multiple programming languages, including the C programming language [19, p. 2]. The programming model enables programmers to write kernels, essentially data-parallel functions using CUDA runtime libraries for procedure calls and GPU device manipulation [19, p. 15]. CUDA utilizes the Single Instruction Multiple Threads (SIMT) architecture to manage and execute groups of 32 threads called warps. The architecture differs from the well-known Single Instruction Multiple Data (SIMD) architecture by allowing multiple threads in the same warp to execute independently, having a private instruction counter, register state, and local memory space [13, p. 68-69]. The independent execution enables multiple threads to issue equal instructions to arbitrary data rather than a single thread issuing vector instructions across many data elements [33].

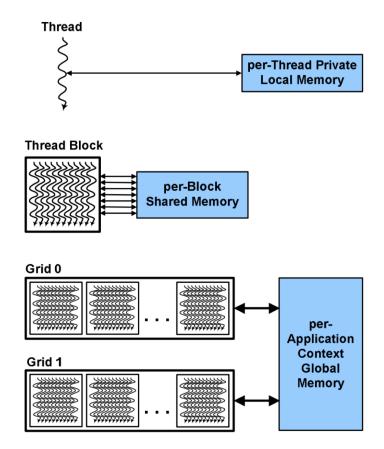

From the programmer's perspective, threads organize into TBs with per-thread private registers and access to per-block shared memory. The TBs compose an execution grid with access to a global memory space containing per-SM L1 and a global L2 cache [34, p. 6]. Figure 2.3 provides an overview of the execution model, where the programmer decides the TB dimensions and grid dimensions. When the GPU schedules TBs for execution to an SM, the warp scheduler dynamically groups 32 threads into warps and executes the warps in lockstep across available SMs. Three execution hierarchies exist from the hardware's perspective: Cooperative-Thread-Array (CTA), warp, and SIMD-lane [35]. Launching a kernel maps TBs and threads onto CTAs and SIMD-lanes, respectively. Warp-level execution remains transparent to the programmer unless the application utilizes warp-level primitives (e.g., via warp shuffle functions [19, p. 168]).

All active threads within a warp execute the same instruction on different

**Figure 2.3:** CUDA thread execution with per-thread local, per-block shared, and per-application global memory spaces. From [34, p. 6]. Reprinted with permission from Nvidia.

data elements. The coalescer combines the threads' memory requests into cache requests, quickly brought back into an SM's compute cores. If the request results in a cache miss, the system allocates one Miss Status Holding Register (MSHR) [36, 37, p. 2] and continues to search in the lower parts of the cache hierarchy. The warp scheduler schedules another warp if the active warp's request misses the last level cache, hiding the expensive memory operation's latency through Thread-Level Parallelism (TLP). However, the cache can maximally serve as many in-flight misses as the number of MSHRs, exposing the SMs to the total DRAM access latency should no MSHRs be available [38].

#### 2.2.2 Thread Synchronization

Simultaneous execution of a substantial number of concurrent threads requires synchronization to prevent *race conditions* [13, p. 97]. A race condition implies non-serialized access by concurrently executing threads to the same memory location, resulting in unknown access orders. GPUs provide thread synchronization at different granularities to battle this issue. Threads synchronize either explicitly through barriers or implicitly when exiting kernels. CUDA 9 introduced Cooperative Groups (CG) [39] to provide synchronization capabilities at multiple granularities, extending from warps to multiple grids. Previously, TB synchronization was the only available synchronization method. However, synchronizing threads at a granularity coarser than TBs using CG generally does not improve performance [40], explaining our choice for sticking with implicit synchronization.

Li et al. [35] emphasized that current technology trends favor allocating more lightweight CTAs for processing individual tasks more independently in favor of fewer heavily-loaded CTAs with significant intra-CTA data reuse. By reducing the number of threads per TB (CTA) to the warp size, the authors increased performance significantly by replacing inter-warp communication (e.g., via shared memory), cooperation, and synchronizations (e.g., via bar primitives [41, p. 218]) with more efficient intra-warp communication (e.g., via warp shuffle functions [19, p. 168]), cooperation (e.g., via warp vote functions [19, p. 165]) and synchronizations (SIMT lockstep execution) across the SIMD-lanes within a warp.

### 2.3 The GPU Memory Architecture

#### 2.3.1 Registers

Registers reside on the top of the memory hierarchy within GPUs. Each SM contains a register file partitioned among the active warps. Their scope is private to each thread and contains variables or arrays having compile-time-determined indices referring to it [13, p. 138]. The registers' lifetime is equal to that of a kernel, and the number of registers allocated by a kernel can severely limit a kernel's performance. Modern GPUs limit the number of registers per thread (block) to 255 (65536) [42]. The kernel spills registers over to *local memory* should the number of registers surpass the hardware limit. However, local memory resides within device memory, making accesses have high latency and low bandwidth. Local memory depends on memory coalescing in the same manner as global memory accesses with a layout organized as consecutive 32-bit words accessible by consecutive threads. Therefore, accesses coalesce as long as a warp's threads access the same relative address (e.g., same index in an array variable) [19, p. 118].

Warp-level primitives enable the use of registers as a high-end cache for stencil computations [20]. The warp-shuffle instructions enable threads to exchange values with other threads within the same warp. Pooling registers from a warp's threads creates a small cache with high performance. The number of registers per thread and the number of threads per warp limits the cache's size. The incredible register usage impacts the achieved occupancy but does not necessarily lead to worse performance [43]. Furthermore, register caching frees up shared memory usage, enabling using shared memory as a second-level cache [20] or creating more space for the L1 cache within the unified cache.

Falch and Elster [20] implemented register caching for a 1D 7-point and 2D 5-point stencil. As a single shuffle instruction could replace a shared memory load, store, and the in-between barrier, the authors argued that their implementation was best suited for applications reading and writing to shared memory. The authors argued that register caching indicated more redundant computation, more loads from global memory, and increased branch divergence than shared memory applications. Their work did not focus on optimizing ISLs particularly but instead evaluated register caching with a realistic ISL benchmark, showing promising results that increased performance up to 2.04x on a GTX 680 GPU.

#### 2.3.2 Shared Memory

Shared memory is essentially a software-managed L1 cache (scratchpad) with much higher bandwidth and lower latency than global memory. The cache is either stand-alone or combined with the L1 cache into a unified cache. Using shared memory can hide the performance impact of global memory bandwidth and latency [13, p. 204-206]. The programmable shared memory differentiates itself from the L1 cache by controlling what data to store and where. For the L1 cache, the hardware loads and evicts data automatically [13, p. 213]. Every warp within a TB shares the same shared memory region, indicating the need for TB synchronization after fetching data into shared memory to ensure program correctness. Subsequently, each warp can fetch data from shared memory stored by other warps within the same TB.

*Memory banks* are physically separate memory modules that handle a subset of the memory address space [44]. Equally-sized shared memory banks allow shared memory to simultaneously serve multiple memory requests if the requests map to different banks. The Volta architecture employs 32 4-byte banks per SM, offering a theoretical bandwidth of 13,800 GiB/s across 80 SMs [45]. However, bank conflicts can decrease shared memory bandwidth utilization. Bank conflicts occur when the addresses of multiple memory requests map to the same memory bank, requiring serialized access to serve the memory requests. The hardware splits the memory requests with bank conflicts into separate requests to perform conflict-free requests to the banks. This process can decrease shared memory throughput by a factor equal to the number of replayed memory bank accesses [19, p. 119]. However, it is crucial to note that the memory accesses must come from different threads within the same warp. Bank conflicts do not occur for threads in different warps or instructions arising from the same thread. This latter fact indicates that the stencil computation for RTM stencils can safely access elements along the Y-dimension, even though the offset between each element implies accessing the same memory bank. Therefore, bank conflicts are not a significant issue for RTM stencils.

The amount of shared memory available for each SM is reconfigurable, and utilizing more than 48 KiB of shared memory per TB is architecture-specific, explicitly requiring dynamic shared memory allocations [19, p. 343]. Dynamic shared memory implies an overhead compared to static allocations and requires passing the allocation's size as a parameter to the launched kernel. The TBs cannot allocate the entire region of an SM's shared memory as the system retains a small allocation for system use. Furthermore, if the available shared memory amount per CTA is lower than per SM, a single TB can not allocate the whole SM's available region by itself. Lastly, as the Volta architecture combines shared memory and L1 into a unified cache, where configuring more shared memory for the SM is a trade-off for less L1 cache space available.

#### 2.3.3 Unified Cache

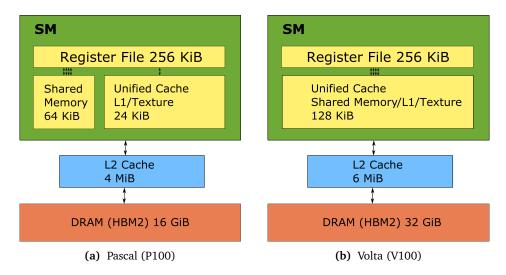

Figure 2.4 presents simplified memory hierarchy diagrams of the Pascal and Volta architectures, showing the architectures' different cache configurations. The Volta architecture provides a unified shared memory/L1/texture cache where up to 96 KiB of the 128 KiB L1 cache storage can be configured dynamically as programmable shared memory, whereas the Pascal architecture provides separate L1 and shared memory. This hardware feature has significant consequences for the performance benefit of utilizing shared memory in ISL applications on Volta vs. Pascal.

Choquette et al. [24] benchmarked a set of applications designed to use shared memory and remapped their design to utilize the L1 cache instead for both reads and writes. They argued that Volta's cache unification caused the L1 cache's performance characteristics to be much closer to the shared memory's characteristics. The authors estimated that their remapped applications exhibited 30% performance decreases on average on Pascal, while the performance decrease was only 7% on Volta. They further argued that "programmers will be able to get reasonably high performance without the additional effort of programming to shared memory."

Furthermore, Volta's L1 caches drastically outperform Pascal by increasing the total size by a factor of 7.7 from 1.3 MiB up to 10 MiB while increasing the L2

**Figure 2.4:** The figures present simplified memory hierarchy diagrams of the Pascal and Volta architectures. The main difference between the architectures lies in Pascal's separate shared memory and L1/texture cache versus Volta's unified shared memory/L1/texture cache. The diagrams simplify the layout by only presenting a single SM instead of replicating many SMs. Based on [13, p. 159]

cache from 4 MiB to 6 MiB. Volta's L1 cache also has four times the bandwidth of Pascal's L1 cache. Additionally, Volta introduces a *streaming* L1 cache [42], substantially increasing the number of possible cache-misses in flight with a large number of MSHRs, reducing the severe performance impact of divergent memory accesses [38] and also making thread coalescing more viable as an optimization by enabling more in-flight memory requests.

#### 2.3.4 High Bandwidth Memory

Both Pascal and Volta use the High Bandwidth Memory 2 (HBM2) memory system as their DRAM (device memory). The HBM2 memory system comprises memory stacks located on the same physical package as the GPU, providing substantial power and area savings compared to traditional GDDR5 memory designs [42]. Volta utilizes an improved HMB2 reaching up to 900 GB/s peak memory bandwidth, compared to 732 GB/s from Pascal's HBM2 system [46]. Volta's memory system also consists of an improved memory controller, which, when combined with the improved memory system, improves the theoretical memory bandwidth by 50% over Pascal, and Nvidia reports that the achieved bandwidth efficiency exceeds 95% bandwidth efficiency for specific workloads [46]. However, to fully utilize the HBM2's bandwidth over the GDDR5, more memory accesses must be kept in flight. In this thesis, we use thread coalescing to increase the number of in-flight memory requests. Furthermore, the advanced Volta system engages large numbers of SMs, increasing the number of concurrent threads and, thus, the inflight memory requests compared to previous architectures.

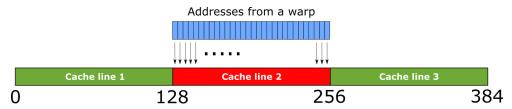

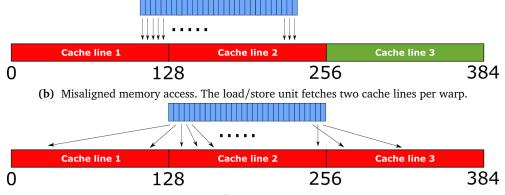

(a) Aligned and coalesced memory access. The memory coalescer coalesces the memory accesses into a single cache line request. The load/store unit serves all warps' requests by fetching a single cache line per warp.

(c) Uncoalesced memory access. The load/store unit fetches multiple cache lines per warp (up to 32 in the worst-case).

**Figure 2.5:** The following figures visualize memory access pattern characteristics. Figure 2.5a presents the ideal situation where fetching a single cache line is sufficient to satisfy a warp's memory requests. Figure 2.5b displays misaligned accesses' unfortunate consequence of requesting twice the number of cache lines required. Figure 2.5c presents the most severe situation fetching up to 32 cache lines per warp compared to Figure 2.5a's single cache line request per warp. Based on [13, p. 161-162].

### 2.4 Desirable GPU Characteristics

#### 2.4.1 Aligned and Coalesced Memory Accesses

Memory bandwidth bottlenecks most GPU applications, making maximizing bandwidth efficiency crucial [13, p. 158]. Figure 2.5 presents three memory access patterns: coalesced, misaligned, and divergent, where divergent and misaligned memory access patterns decrease performance significantly. The GPU's L1 (L2) cache consists of 128-byte (32-byte) cache lines. Ideally, a memory request's first address should be an even multiple of the cache granularity to prevent fetching an extra cache line [13, p. 162]. As the cache-line sizes differ, the consequences for divergent L1 loads are more severe than for divergent L2 loads. Therefore, our following example focus on divergent L1 access patterns.

For the L1 cache, using 4-byte floats (single-precision) enables an ideal situation where the coalescer can combine 32 memory loads of a warp into a single cache request. This situation requires the loads' offsets to be contiguous within the 128-byte segment to ensure maximum efficiency. However, strided offsets incur large overheads for the memory system. The worst-case scenario occurs for 128-byte offsets, where the threads' loads request 32 different cache lines (4096 bytes) to satisfy a single warp's memory requests for 32 4-byte elements (128 bytes), reaching a meager 3.125% efficiency. Additionally, the requests allocate 32 MSHRs compared to a single MSHR in the coalesced example, and the enormous amount of memory requests essentially flood the GPU's Network-on-Chip and DRAM systems [38].

Vast domains incur large offsets for RTM's cross-shaped stencil in the Ydirection (2D) or Z-direction (3D). The last dimension offset for 3D (plane) quickly outgrows 2D's offset (line), decreasing the probability that the requested cache lines reside within the caches. As a result, the memory system allocates more MSHRs and saturates the NoC and DRAM systems more substantially in 3D than 2D to satisfy the memory requests, causing severe issues for maintaining TLP.

The streaming executing model of the GPU implies that applications can be memory-bound or compute-bound [47]. If compute-bound, the performance scales linearly with the number of occupied SMs, and if memory-bound, performance is strongly correlated with memory bandwidth. ISL applications are famously memory-bound [31], but reducing the memory-boundedness is possible through temporal blocking [15].

#### 2.4.2 Effective Resource Utilization

*Occupancy* is a metric expressing the ratio of active warps per SM to the total number of hardware warp-slots per SM [35]. The metric focuses exclusively on the number of concurrent warps per SM and is, therefore, not the only goal for performance optimization [13, p.97]. Cheng et al. [13, p. 100] provide an excellent example showing that higher occupancy does not always mean higher performance. The authors show that increasing occupancy at the expense of decreasing other vital metrics, such as the efficiency of global memory loads, can decrease performance. For memory-bound applications, the consequences of decreasing memory efficiency can be fatal. Therefore, the programmer must be aware of the metrics' trade-offs. The metrics can be studied using the performance analysis tools Nvidia Visual Profiler (NVP) [48] or Nvidia Nsight Compute [49].

Each SM contains a finite set of registers and shared memory partitioned between the SM's executing warps. Additionally, the SMs have an upper bound on the number of warps eligible for simultaneous execution, causing the number of threads per block to decide how many blocks the GPU can execute simultaneously. Occupancy decreases if either resource is exhausted, making it crucial to adhere to these restrictions for optimizing the kernel's achieved occupancy. Therefore, manipulating the TB dimensions can expose sufficient parallelism to saturate the system resources. The CUDA Occupancy Calculator [50] is an excellent tool to guide the developer on how to handle these resources effectively.

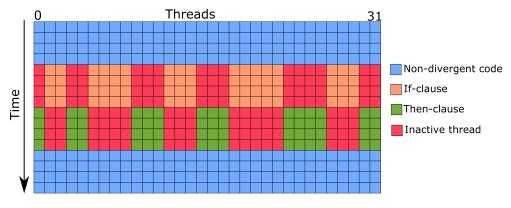

**Figure 2.6:** The figure displays threads' behavior when branch divergence occurs. The warp's threads remain active when executing non-divergent code. If a warp's threads take different paths when reaching a conditional branch, the warp executes each path serially, deactivating threads that do not follow the current execution path. Based on [13, p. 83].

#### 2.4.3 Avoiding Branch Divergence

Warps execute single instructions at a time, realizing total efficiency only when all threads within the warp do not have divergent execution paths [19, p. 107]. Each execution path still executes if the path of threads within a warp diverges on a conditional branch. However, the scheduler disables the threads not following the executed path. Figure 2.6 presents a situation where branch divergence occurs. Branch divergence occurs within warps only and is therefore independent of the execution behavior of other warps. Traditionally, warps have had a single execution state shared by all threads. The Volta architecture introduced per-thread execution states, thus allowing independent thread scheduling, although the execution model remains SIMT. The feature improves the divergence and reconvergence of threads within warps by making them more flexible and efficient [35]. However, branch divergence does not disappear with the added feature as the hardware still restricts the execution to only a single instruction at a time [51].

### 2.5 Single-GPU Optimization Approaches

#### 2.5.1 Thread Coarsening

Decomposing a problem into a set of fine-grained tasks distributed between the GPU's threads inevitably introduce overheads from different sources varying by the algorithm or method implemented. The implemented kernel might map unfavorably to the underlying hardware, causing poor compute resource utilization. Finer-grained decompositions incur inefficiencies by scheduling and communication overhead and needing to recalculate light operations in many threads, e.g., address offsets for memory requests [22].

Loop unrolling is an optimization technique utilized by the preprocessor to increase the code size and register pressure as a trade-off for increased concurrency and data reuse [52]. The technique reduces the total number of branches and loop maintenance instructions for loops by duplicating the loop body instructions multiple times. Lack of branch prediction mechanisms makes branching expensive for GPU applications, indicating the available optimization potential. Additionally, the technique creates more independent instructions to schedule, enabling more inflight operations to provide higher instruction and memory bandwidth efficiency [13, p. 114]. Utilizing the GPU's exceptionally lightweight warp scheduling enables the opportunity to hide latency by scheduling new warps when others stall for arithmetic instructions or memory operations. Therefore, more in-flight operations help the system hide more instruction and memory latency [13, p. 115]. The compiler provides automatic loop unrolling for loops of limited size with known loop conditions [19, p. 208].

Thread coarsening [21, 22] takes advantage of loop unrolling by merging code usually executed by separate threads into a single thread. The procedure effectively de-parallelizes a program, making threads more coarse-grained by increasing each thread's workload. The coarsening factor describes the factor by which we increase the amount of work per thread. Thread coarsening gets similar performance benefits as loop unrolling, combined with potentially improving problem decomposition. At some point, the reduced number of threads will limit parallelism and decrease performance. Furthermore, increasing the coarsening factor increases resource consumption (e.g., registers, shared memory), eventually reducing occupancy. Additionally, some kernels increase pressure on the caches with an increasing coarsening factor [21]. The performance trade-off motivates the search for an ideal coarsening factor or deciding that no coarsening should be applied at all. Exploring the coarsening factor can be explored manually [53, 54] or automatically through either autotuning [55] or machine-learning [56]. This thesis explores the ideal coarsening factor manually through benchmarking.

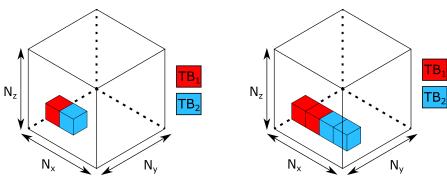

Two thread coarsening strategies remain dominant: thread- and block-level coarsening [21]. The former combines the threads' workload within a TB, while the latter merges multiple TBs' workload into one. Figure 2.7 visualizes the block-level coarsening approach utilized to optimize our ISL application. These approaches have different impacts on memory access patterns as each coarsening strategy imposes different memory access strides. Magni et al. [53] studied thread-level and Unkule et al. [55] explored block-level coarsening. Stawinoga and Field [21] scrutinized both strategies, concluding that block-level outperformed thread-level coarsening due to practical issues when deciding the memory stride for each thread, arguing that poor striding breaks memory coalescing. They further emphasize that block-level coarsening has no issues regarding memory coalescing. Furthermore, by utilizing a conservative approach for electing kernels for coarsening, the authors either increased or kept performance flat in most cases. The authors' conclusions motivate our inclination for focusing on block-level coarsening only.

(a) The figure presents two neighboring TBs executing without thread coarsening.

(b) The figure displays the effect of coarsening each TB with CF = 2.

**Figure 2.7:** The figures present block-level thread coarsening, which combines multiple blocks' workload into one TB. The coarsening factor, *CF*, decides how many blocks to merge. Figures 2.7a and 2.7b presents an example without (CF = 1) and with (CF = 2) thread coarsening. Furthermore, doubling the coarsening factor halves the number of scheduled TBs.

The coarsening strategy also impacts TB synchronization performance. As fewer threads (thread-level coarsening) or blocks (block-level coarsening) participate in the block-level synchronization barriers, performance increases for barrier-sensitive applications. Furthermore, Stawinoga and Field [21] observed that both strategies have a similar effect on barrier performance. Liu et al. [57] highlighted the importance of reducing cycles spent in barriers for barrier-sensitive applications as the number of cycles proliferates even though barriers employ lightweight hardware support. Therefore, coarsening impacts the per-formance of the kernels within this thesis that employ TB synchronizations (i.e., the kernels utilizing shared memory).

#### 2.5.2 Optimizing Thread Block Dimensions

Section 2.4.2 emphasized the TB dimensions' importance for effectively using GPU resources and exposing sufficient parallelism. Choosing TB dimensions using the CUDA occupancy calculator is often suboptimal, as maximizing occupancy does not necessarily produce the best performance. However, testing all available TB dimension combinations is extremely difficult as the number of possible configurations is massive.

An autotuning framework enables TB dimension exploration either by bruteforce or more sophisticated approaches using search algorithms. However, imposing restrictions on the parameters prevent complete domain exploration. Cheng et al. [13, p. 96] proposed guidelines for choosing grid and block sizes, emphasizing the importance of keeping the innermost dimension a multiple of the warp size to keep all threads within each warp active. Additionally, keeping the number of TBs much greater than the number of SMs generally improves parallelism. Spencer [58] proposed the Flamingo autotuning framework, providing bruteforce parameter exploration, enabling TB dimension and thread coarsening factor optimization. The author designed the framework to be very general-purpose, making few assumptions on user interaction, making it remarkably simple. This thesis utilizes Flamingo to optimize the TB dimensions for each thread coarsening factor, exploring more ideal configurations for improved resource consumption.

## 2.6 Utilizing Multiple GPUs

#### 2.6.1 Domain Partitioning

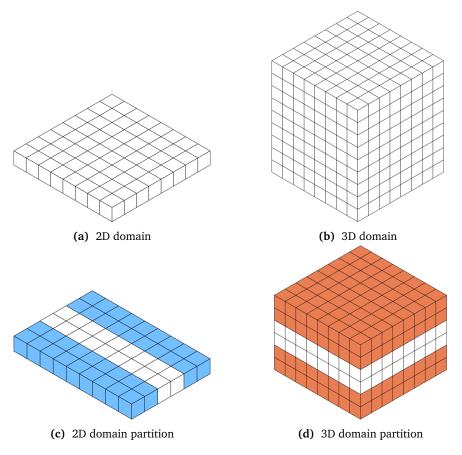

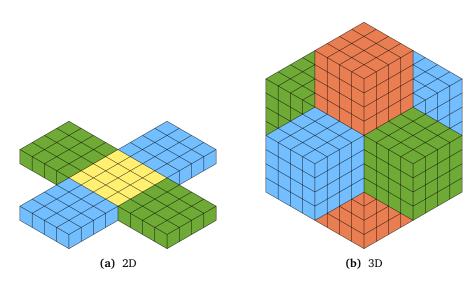

Extracting the computation power added by utilizing multiple GPUs requires problem domain partitioning between the GPUs. Spampinato [59] contributed an investigation of multi-GPU data partitioning in 2D and the communication pattern required for each iteration in his scheme's iterative method. He specified the prevailing domains of both strip and block partitioning. If we assume a 2D (3D) square (cube) domain with equal dimension sizes, strip partitioning subdivides the grid along the y-axis (z-axis) into horizontal strips (planes). In comparison, block partitioning partitions the domain evenly into smaller squares (cubes). Assuming a system containing 4 GPUs, Spampinato argued that strip partitioning reduces communications by half for the GPUs having partitions with only a single neighbor. In comparison, block partitioning incurs the same number of communications for every GPU but needs to transfer fewer bytes per communication.

With differing communication requirements, data partitioning proposes a trade-off between latency and bandwidth. The optimal structure depends on the system architecture and the application at hand. Spampinato [59] refers to Wilkinson and Allen [60], stating that strip partitioning is better for high-latency communication systems, while block partitioning is better for low-latency communication. However, Spampinato concluded that this model was too general and not suited for multi-GPU systems because it does not include the incredible number of architectural hardware details necessary to provide an accurate model. Furthermore, the author's results showed that strip partitioning outperformed block partitioning for its setup containing 4 GPUs. Therefore, we choose to utilize strip partitioning in our multi-GPU scheme.

Another option not pursued in this thesis is to use frameworks for automatic problem domain partitioning onto multiple GPUs. Ben-Nun et al. [61] proposed a multi-GPU framework called MAPS-Multi, providing a programming abstraction that automatically allocates and distributes the workload among multiple GPUs and optimizes applications for the given architectures. The framework is also capable of providing memory transfers implicitly if required by the application. A host- and device-level API provides this abstraction and includes off-the-shelf functionality for various architectures containing an arbitrary number of GPUs. The API significantly reduces code length and achieves near-linear performance scaling by adding more devices for various applications.

**Figure 2.8:** The figure shows an example of strip partitioning in 2D and 3D for multi-GPU. Figures 2.8a and 2.8b display simplified grid layouts by setting each dimension to 8 elements. Figures 2.8c and 2.8d show each GPUs partition including their ghost zones when we utilize 4 GPUs in 2D and 3D, respectively.

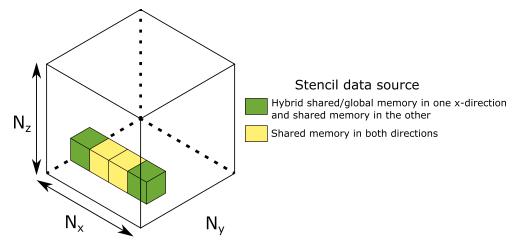

#### 2.6.2 Ghost Zones

Partitioning domains between multiple GPUs introduces a problem where stencil calculations along the boundary require elements residing in other devices' memory. A naive solution for ISL applications is communicating the required elements when necessary, but this approach implies a significant communication and synchronization overhead. Therefore, we augment the partitions to include *ghost zones* [2], essentially overlapping neighboring partitions causing redundant computations.

Figure 2.8 visualizes a strip partitioning of an 8x8(x8) domain between 4 GPUs in 2D (3D), including ghost zones applicable for computing the  $R_2$  stencil. The figure's domains are superficially small for illustrational purposes. Partitioning the 2D (3D) domain between 4 GPUs creates an 8x2 (8x8x2) domain for each GPU shown in Figure 2.8c (Figure 2.8d), significantly reducing the workload per GPU. Figures 2.8c and 2.8d enlarge the second and third dimensions with additional

ghost zone elements visualized with blue and brown cells, respectively.

Reducing inter-GPU communication is possible by increasing the computational workload by enlarging the partitions' ghost zones. Spampinato [59] argued that increasing the ghost zone's depth by a given size, *n*, reduces the communication factor by the same value. Thus, each iteration shrinks the ghost zone by one row (plane) for 2D (3D) until the number of iterations equals *n*. The author further argued that the optimal ghost zone size depends on the application and architecture and is a trade-off between the system's latency and transmission time. Therefore, it is beneficial as long as the new transmission overhead does not exceed the previous overhead. However, the concept belonged originally to compute clusters. At maximum, the author increased performance only by 1.1x for his setup using 4 GPUs. Our previous work [1] implemented a similar communication reduction scheme using the same number of GPUs but showed no significant performance improvements.

#### 2.6.3 Handling Inter-GPU Communication

CUDA streams are sequences of operations executed in the order they are issued and can also provide a valuable mechanism for overlapping communication with computation [13, p. 268]. Our multi-GPU implementation utilizes a single stream per GPU to handle communications, enabling direct memory transfers between the devices asynchronously. Using multiple streams can significantly improve communication performance in some applications by overlapping communication with neighboring GPUs.

As device context switches are independent, host multi-threading allows parallel kernel launches, removing the single-threaded overhead imposed by switching GPU contexts and launching the kernel. Also, it prevents the main thread from stalling, as would be the case for only using a single thread. Preventing stalls can be significant in real-world applications where the thread needs to attend other tasks [62]. As a result, multi-threading provides improved task-parallelism for the CPU, resulting in increased system performance.

Sourouri et al. [62] provided an efficient inter-GPU communication scheme, utilizing multiple OpenMP [63] threads with multiple streams to overlap communication with computation. The additional streams facilitated inter-GPU communication, using two streams per neighboring device, each responsible for either the sending or receiving part of the communication. The authors emphasized the importance of utilizing lightweight OpenMP threads instead of MPI [64] processes to maximize performance. As a result, a device can simultaneously communicate with both neighbors, reducing the communication stages into a single stage, effectively doubling communication performance. The authors provided an example requiring half the original number of communications to emphasize the benefit of utilizing multiple streams. The authors also studied using either PCIe or GPU-Direct but did not look into the effects of having the novel NVLink, NVSwitch, or NV-SLI interconnects. The main drawback of older multi-GPU implementations is the need to stage memory transfers through the host, a requirement imposed by PCIe interconnects, requiring twice the number of memory transfers as direct communication between the devices on a single node. However, modern multi-GPU systems use different NVLink, NVSwitch, or NVI-SLI versions, providing alternatives to the typical PCIe interconnect. This project applies direct P2P communication between the devices through an NVSwitch system on a single compute node.

Li et al. [65] studied numerous interconnect topologies in multi-GPU systems, contributing a thorough investigation into the execution behavior altered by the interconnects. The authors measured latency, bandwidth and studied the emerging performance factors of employing different topologies. The authors made a crucial observation by discovering that some modern GPU interconnects (e.g., NVLink) showed non-uniform memory access effects that increased latency, although previously claiming transparency. However, the NVSwitch interconnect utilized in this thesis showed no such deficiencies.

## Chapter 3

# Implementing Optimized ISL Kernels

The following chapter presents and discusses our ISL application by introducing multiple kernels. The kernels calculate the RTM stencil for equal inputs, whose workload can reside within both L1 or shared memory. We present the kernels' source code in 3D as it is more sophisticated than 2D, although the 2D-equivalent is similar. However, we visualize the shared memory layout of both 2D and 3D kernels. The kernels correctly execute on different architectures where L1 and shared memory do not necessarily reside within the same unified cache. Furthermore, we coarsen the kernels' threads to increase the workload per thread. Table 3.1 summarizes preprocessor macros used throughout the following sections' code listings. Crucially, this chapter presents essential parts of the source code only. However, the complete source code is available on Github<sup>1</sup>.

| <sup>1</sup> see https:/ | /github. | <pre>com/mrfarstad/thesis</pre> |

|--------------------------|----------|---------------------------------|

|--------------------------|----------|---------------------------------|

| Variable         | Description                                |

|------------------|--------------------------------------------|

| DIMENSIONS       | Specifies 2D or 3D kernels and domains     |

| NX, NY, NZ       | Problem domain dimensions                  |

| RADIUS           | The stencil radius                         |

| STENCIL_COEFF    | The stencil calculation's coefficient      |

| ITERATIONS       | The number of stencil iterations           |

| BYTES_PER_GPU    | Domain partition size per GPU in bytes     |

| COARSEN_X        | The coarsening factor (in the X-direction) |

| GHOST_ZONE       | Number of elements per ghost zone          |

| GHOST_ZONE_BYTES | Ghost zone size in bytes                   |

| GHOST_ZONE_DEPTH | Number of rows (planes) per ghost zone     |

| NGPUS            | Number of GPUs utilized                    |

Table 3.1: Constants frequently used in our ISL application

Table 3.2: Kernels used in our ISL application

| Kernel                           | Description                                    |

|----------------------------------|------------------------------------------------|

| base                             | Baseline RTM kernel using global memory only.  |

| <pre>base_coarsened</pre>        | Extends base. Handles CF elements per thread.  |

| smem                             | Extends base by adding TB sized shared memory. |

| <pre>smem_coarsened</pre>        | Extends smem by multiplying the shared memory  |

|                                  | allocation by CF. Handles CF elements per      |

|                                  | thread.                                        |

| <pre>smem_padded</pre>           | Extends smem by padding the shared memory al-  |

|                                  | location by the stencil radius.                |

| <pre>smem_padded_coarsened</pre> | Extends smem_coarsened by padding the shared   |

|                                  | memory allocation. Handles CF elements per     |

|                                  | thread.                                        |

### 3.1 ISL Kernels

Table 3.2 presents the kernels representing a combination of various shared memory implementations and thread coarsening. We greatly simplify our discussions throughout the subsequent sections by introducing some abbreviations, denoting the coarsening factor for a given kernel by *CF* and the TB dimensions as  $B_x$ ,  $B_y$ ,  $B_z$ .

#### 3.1.1 The Baseline Kernel

Code listing 3.1 presents the base kernel providing the most straightforward ISL implementation without any further optimizations. Lines 7 to 11 calculate the threads' index within the domain (i.e., the global index). Line 12 checks if the computed indices fit within the domain dimensions minus (or plus) an offset equal to the stencil radius. Line 13 computes the stencil by calling a function that fetches all the elements needed for the stencil calculation directly from global memory. Code listing 3.2 presents this stencil function as a series of accumulations, summing the values of all neighbors in each direction of the stencil. Lines 5 to 11 present the functions used to perform this accumulation, consisting of function calls where all functions essentially call the function defined in Code listing 3.3 with different parameters depending on the accumulation direction.

The global memory is cached, providing excellent reuse capabilities if the cache capacity can include a TB's workload. The stencil includes the stencil's center, meaning that the elements in the X-direction are contiguous. Finally, the kernel multiplies the sum of the neighboring elements with a predefined constant and subtracts the stencil's center element. We choose to define the constants using a preprocessor macro. If the stencil requires different constants, then loading the values into constant memory maintains satisfactory performance.

```

Code listing 3.1: The base kernel

```

```

_global__ void base_3d(

float* __restrict__ d_in,

float* __restrict__ d_out,

1

2

3

4

unsigned int kstart,

unsigned int kend)

5

6

{

7

unsigned int i, j, k, idx;

8

i = threadIdx.x + blockIdx.x*blockDim.x;

j = threadIdx.y + blockIdx.y*blockDim.y;

9

10

k = threadIdx.z + blockIdx.z*blockDim.z;

idx = i + j*NX + k*NX*NY;

11

if (check_stencil_border_3d(i, j, k, kstart, kend))

12

stencil(d_in, d_out, idx);

13

14

}

```

Code listing 3.2: The base stencil

```

1

device

host

inline void stencil(

float *in, float *out, unsigned int idx)

2

3

{

4

float sum = 0.0f;

accumulate_global_i_prev(&sum, in, idx);

5

accumulate global i next(&sum, in, idx);

6

7

accumulate_global_j_prev(&sum, in, idx);

accumulate_global_j_next(&sum, in, idx);

8

#if DIMENSIONS>2

9

10

accumulate_global_k_prev(&sum, in, idx);

11

accumulate_global_k_next(&sum, in, idx);

12

#endif

13

out[idx] = sum / STENCIL_COEFF - in[idx];

}

14

```

Code listing 3.3: Global memory stencil accumulators

```

1

device__

host__

inline

2

void accumulate_prev(float *sum, float *in, unsigned int idx, int offset)

3

4

#pragma unroll

for (unsigned int d=RADIUS; d>=1; d--)

5

*sum += in[idx-d*offset];

6

}

7

8

9

_device__ _host__ _inline_

void accumulate_next(float *u, float *in, unsigned int idx, int offset)

10

11

{

#pragma unroll

12

13

for (unsigned int d=1; d<=RADIUS; d++)</pre>

*sum += in[idx+d*offset];

14

15

}

```

Code listing 3.4: The base coarsened kernel

```

_global__ void base_coarsened_3d(

1