Peter Uran

## Design of an FPGA-based Data Acquisition System for a Shore-based Maritime Radar Network

Master's thesis in Electronic Systems Design and Innovation Supervisor: Egil Eide Co-supervisor: Zolve AS July 2021

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Peter Uran

## Design of an FPGA-based Data Acquisition System for a Shore-based Maritime Radar Network

Master's thesis in Electronic Systems Design and Innovation Supervisor: Egil Eide Co-supervisor: Zolve AS July 2021

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Abstract

A shore-based network of maritime radars is to be developed by NTNU and Sintef as part of the Ocean Lab Node 2 infrastructure. The purpose of the network is to track both autonomous and traditional vessels in the Trondheim fjord and contribute to a shared situational awareness. This report presents a system architecture for the remote radar sites, based on sampling the radar data on-site and transmitting the data via the emerging 5G network in Trondheim to minimize the cost of infrastructure. A data acquisition system is developed based on the Analog Devices AD-FMCDAQ2 ADC and an iWave Intel Arria10 SoC/FPGA FMC+ Development Kit. A Simrad Halo 20+ pulse compression radar is currently considered for the system. The radar waveforms are measured and revealed to transmit both pulses and chirps with varying center frequencies and bandwidths. The sweep bandwidth is measured to a maximum of 30 MHz, which is expected to result in 1.0 Gbit/s of uplink data. The data acquisition system is shown to successfully perform IQ demodulation, clock domain crossing and pulse compression in simulation. Pulse compression is achieved by dynamically creating a matched filter from the transmitted chirp to account for the alternating center frequency and bandwidth of the chirp. The required filter length was not achieved due to over-utilization of the FPGA multipliers, to which multiple solutions are discussed. A driver issue prevented the testing of the dechirping in hardware. The project also makes successful use of a continuous integration workflow for simulating the FPGA design with the VUnit test framework and the open source GHDL simulator. It is also demonstrated how VUnit can be used to verify the signal processing chain by generating and validating simulation data in Python, rather than pure VHDL.

## Sammendrag

Et landbasert nettverk av maritime radarer skal utvikles av NTNU og Sintef som en del av Ocean Lab Node 2-infrastrukturen. Hensikten med nettverket er å spore både autonome og tradisjonelle fartøy i Trondheimsfjorden for å bidra til en delt situasjonsbevissthet. Denne rapporten presenterer en systemarkitektur for eksterne radarsteder, basert på sampling av radardata på stedet og opplasting via det nye 5G-nettverket i Trondheim for å minimere infrastrukturkostnadene. Et datainnsamlingssystem er utviklet basert på Analog Devices AD-FMCDAQ2 ADC og et iWave Intel Arria10 SoC / FPGA FMC+ utviklingskort. En Simrad Halo 20+ pulskompresjonsradar er tiltenkt for systemet som del av prosjektet. Radarbølgeformene måles og viser seg å overføre både pulser og chirps med varierende senterfrekvenser og båndbredde. Båndbredden for en chirp måles til maksimalt 30 MHz, som forventes å resultere i 1.0 Gbit/s opplinkingsdata. Datainnsamlingssystemet er vist å utføre IQ-demodulering, klokkedomenekryssing og pulskompresjon i simulering. Pulskompresjon oppnås ved dynamisk å lage et matchet filter fra den overførte chirp-en for å ta hensyn til den alternerende senterfrekvensen og båndbredden til chirpen. Den nødvendige filterlengden ble ikke oppnådd på grunn av overutnyttelse av FPGA-multiplikatorene, som flere løsninger blir diskutert til. Et driverproblem forhindret testing av *dechirping* i maskinvare. Prosjektet bruker også *continuous integration* for å simulere FPGA-design med VUnit-testrammeverket og GHDLsimulatoren med åpen kildekode. Det er også demonstrert hvordan VUnit kan brukes til å verifisere signalbehandlingskjeden ved å generere og validere simuleringsdata i Python, fremfor bruk av ren VHDL.

## Acknowledgements

First and foremost I want to thank my colleagues in Zolve for their support. While the FPGA-world is fascinating, it is certainly not traveled alone. I appreciate all the experience and advice you have been sharing with me the last year. One should also not underestimate the value of engineers discussing problems by the coffe machine. There are few other companies with such a joyous and nurturing culture as Zolve, which is deeply appreciated. I very much look forward to start working full time in Zolve this autumn.

I also want to thank my supervisor Egil Eide for sharing his expertise and giving valuable feedback throughout the project. As both an outstanding source of radar as well as humor, our meetings have been something to look forward to. While your are an entrepreneur with many ambitious projects, I hope you continue to spend time on educating the next generation of engineers. Your lectures were much appreciated.

Last but not least, a special thanks goes to Lars Lundheim for taking it upon himself to transform the way we teach electronics to university students. You have been a good source of motivation and knowledge even years after I had you as a lecturer. Elsys would never have existed without you, and I hope you continue to teach for years to come.

# Abbreviations

| Abbreviation         | Definition                                                                        |

|----------------------|-----------------------------------------------------------------------------------|

| BFM                  | Bus Functional Module. Software model applying stimuli to a bus under simulation. |

| COTS                 | Commercially available off-the-shelf                                              |

| DSP slice            | Special logic block providing arithmetic for large numbers                        |

| DUT                  | Device Under Test                                                                 |

| Entity               | VHDL language construct defining a module, its ports and content                  |

| Fabric               | Reconfigurable logic part of the FPGA silicon                                     |

| FIFO                 | First In, First-Out. Simple memory structure                                      |

| FMC HPC              | FPGA Mezzanine Card High Pin Count. Also called FMC+                              |

| FMC LPC              | FPGA Mezzanine Card Low Pin Count. Often denoted as only FMC                      |

| FPGA                 | Field-programmable gate array                                                     |

| GNSS                 | Global Navigation Satellite System                                                |

| GNSSDO               | GNSS Disciplined Oscillator                                                       |

| HPS                  | Hard Processor System                                                             |

| IP Core              | Intellectual Property core. Ready-to-use entity designed by vendor or third party |

| Logic block          | Basic FPGA building block providing reconfigurable logic                          |

| LUT                  | Lookup table                                                                      |

| Process              | VHDL language construct providing sequential execution of code                    |

| PPS / 1PPS           | (1) Pulse Per Second                                                              |

| Quartus              | Intel/Altera Quartus Prime FPGA design tool                                       |

| m R/W                | Read/Write                                                                        |

| $\operatorname{SoC}$ | System on Chip. Term describing a FPGA with a HPS                                 |

| UDP                  | User Datagram Protocol                                                            |

| UVVM                 | Universal VHDL Verification Methodology                                           |

| VHDL                 | VHSIC-HDL, Very High Speed Integrated Circuit Hardware Description Language       |

# Contents

| 1        | Intr              | roduction                               | 1          |  |  |  |  |  |  |  |  |  |

|----------|-------------------|-----------------------------------------|------------|--|--|--|--|--|--|--|--|--|

| <b>2</b> | Rad               | dar characteristics 3                   |            |  |  |  |  |  |  |  |  |  |

|          | 2.1               | Radar background                        | 3          |  |  |  |  |  |  |  |  |  |

|          | 2.2               | Simrad Halo 20+ Radar                   | 4          |  |  |  |  |  |  |  |  |  |

|          | 2.3               | Waveform characteristics                | 6          |  |  |  |  |  |  |  |  |  |

|          | -                 | 2.3.1 Measurement setup                 | 6          |  |  |  |  |  |  |  |  |  |

|          |                   | 2.3.2 Measurement results               | 7          |  |  |  |  |  |  |  |  |  |

|          |                   | 2.3.3 Measurement discussion            | 9          |  |  |  |  |  |  |  |  |  |

| 3        | Syst              | tem architecture                        | 11         |  |  |  |  |  |  |  |  |  |

| 0        | 3.1               |                                         | 11         |  |  |  |  |  |  |  |  |  |

|          | 3.2               |                                         | 12         |  |  |  |  |  |  |  |  |  |

|          | 3.3               |                                         | 13         |  |  |  |  |  |  |  |  |  |

|          | 3.4               | -                                       | 13         |  |  |  |  |  |  |  |  |  |

|          | 3.5               | 8                                       | $15 \\ 15$ |  |  |  |  |  |  |  |  |  |

|          | 0.0               | 1                                       | $15 \\ 15$ |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 17         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 17         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 18         |  |  |  |  |  |  |  |  |  |

|          |                   | 3.5.4 Bill of materials (BOM)           | 10         |  |  |  |  |  |  |  |  |  |

| 4        | Imp               |                                         | 19         |  |  |  |  |  |  |  |  |  |

|          | 4.1               |                                         | 19         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 19         |  |  |  |  |  |  |  |  |  |

|          |                   | 0                                       | 19         |  |  |  |  |  |  |  |  |  |

|          |                   | 2 0 0                                   | 21         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.1.4 Pitfalls and other considerations | 21         |  |  |  |  |  |  |  |  |  |

|          | 4.2               | User top overview                       | 24         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.2.1 Comms module                      | 25         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.2.2 Address decoder                   | 27         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.2.3 About module                      | 27         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.2.4 Debug module                      | 27         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.2.5 1PPS module                       | 28         |  |  |  |  |  |  |  |  |  |

|          | 4.3               | DSP core                                | 28         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.3.1 Clock domain crossing             | 29         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 30         |  |  |  |  |  |  |  |  |  |

|          |                   | 4.3.3 Decimation                        | 32         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 35         |  |  |  |  |  |  |  |  |  |

| 5        | Des               | sign verification                       | 39         |  |  |  |  |  |  |  |  |  |

| 0        | 5.1               | -                                       | 39         |  |  |  |  |  |  |  |  |  |

|          | 0.1               |                                         | 39         |  |  |  |  |  |  |  |  |  |

|          |                   |                                         | 40         |  |  |  |  |  |  |  |  |  |

|          | 5.2               | v                                       | 41         |  |  |  |  |  |  |  |  |  |

|          | $\frac{5.2}{5.3}$ |                                         | 41<br>41   |  |  |  |  |  |  |  |  |  |

|          |                   |                                         |            |  |  |  |  |  |  |  |  |  |

|          | 5.4               | DSP core testbench                      | 42         |  |  |  |  |  |  |  |  |  |

|    |                         | 5.4.1    | Simulation results                                | 44 |  |  |  |  |  |

|----|-------------------------|----------|---------------------------------------------------|----|--|--|--|--|--|

|    | 5.5                     | Physic   | al test                                           | 45 |  |  |  |  |  |

|    |                         | 5.5.1    | Test setup                                        | 45 |  |  |  |  |  |

|    |                         | 5.5.2    | Register access test                              | 46 |  |  |  |  |  |

|    |                         | 5.5.3    | Dechirping test                                   | 47 |  |  |  |  |  |

| 6  | Disc                    | cussion  | L                                                 | 48 |  |  |  |  |  |

|    | 6.1                     | Evalua   | ation                                             | 48 |  |  |  |  |  |

|    |                         | 6.1.1    | Radar selection                                   | 48 |  |  |  |  |  |

|    |                         | 6.1.2    | Hardware selection                                | 48 |  |  |  |  |  |

|    |                         | 6.1.3    | Verification toolchain and continuous integration | 48 |  |  |  |  |  |

|    |                         | 6.1.4    | Physical test                                     | 49 |  |  |  |  |  |

|    |                         | 6.1.5    | Data rates                                        | 49 |  |  |  |  |  |

|    | 6.2                     | Future   | e work                                            | 49 |  |  |  |  |  |

|    |                         | 6.2.1    | Timing analysis and timing violations             | 49 |  |  |  |  |  |

|    |                         | 6.2.2    | DSP block optimization                            | 49 |  |  |  |  |  |

|    |                         | 6.2.3    | HPS driver                                        | 50 |  |  |  |  |  |

|    |                         | 6.2.4    | More processing on the FPGA                       | 50 |  |  |  |  |  |

|    |                         | 6.2.5    | Build tools                                       | 51 |  |  |  |  |  |

|    |                         | 6.2.6    | Python model                                      | 51 |  |  |  |  |  |

| 7  | Con                     | clusio   | n                                                 | 52 |  |  |  |  |  |

| •  | 001                     | ierubier |                                                   | 01 |  |  |  |  |  |

| Bi | bliog                   | raphy    |                                                   | 53 |  |  |  |  |  |

| Α  | Ava                     | lon M    | M slave process                                   | 55 |  |  |  |  |  |

| в  | IQ I                    | Demod    | lulator Sample Sorter                             | 56 |  |  |  |  |  |

| С  | C VUnit run file        |          |                                                   |    |  |  |  |  |  |

| U  | v UI                    | unt nun  |                                                   | 57 |  |  |  |  |  |

| D  | D Python UART interface |          |                                                   |    |  |  |  |  |  |

## Chapter 1

## Introduction

In 2016, The Norwegian Coastal Administration authorized the Trondheim Fjord as the first testbed for autonomous vessels in the world [2]. These vessels are also known as Maritime Autonomous Surface Ships (MASS). Since then, the fjord has been a prime target for innovation in the transport, fishing and aquaculture industries through the emergence of autonomous vessels [31]. This includes the NTNU research vessel MilliAmpere [34] and its recent commercialization through ZeaBuz [3]. The new autonomous vessels need to co-exist with and safely navigate traditional crafts and recreative vessels, as well as sporting crafts such as sailboats and kayaks. This is imperative to sustain a safe environment, establish trust and preserve the various and diverse interests of all the different groups using the fjord.

As part of the effort to sustain safe transport on the fjord, NTNU and SINTEF wish to develop a radar network to track both autonomous and non-autonomous vessels. The radar network is to be part of the Ocean Lab Node 2 infrastructure [35]. The objective of this infrastructure is to help detect small craft and objects, assist navigation in confined waters and automatic operation in ports, as well as contribute to a shared situational awareness for the vessels. Furthermore, the information can be used in control rooms to monitor the traffic and quickly react to emerging situations. The radar network will also be useful to gather more information for further research on autonomous vessels.

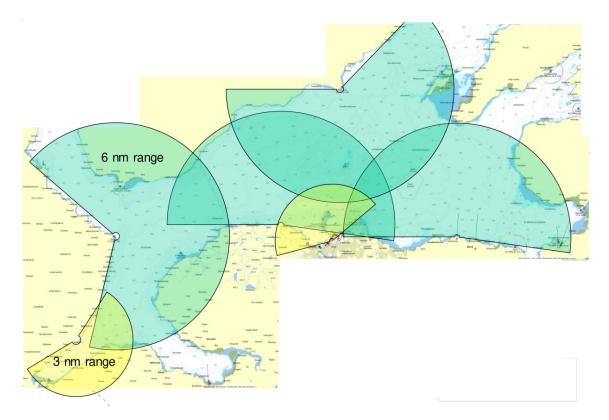

The radar network will consist of several shore based radars stationed at remote sites around the fjord, as shown in Figure 1.1. A data acquisition system on site shall be used to sample and process the radar data. Each site will transmit the raw radar data to a central processing hub using the emerging 5G mobile broadband network in Trondheim [5]. Observing the objects from multiple angles allows for better coverage and high reliability of detection, as well as reduction of sea clutter [19].

Existing solutions, such as the Vessel Traffic System (VTS), are mostly based on professional personnel supervising and hailing vessels to regulate traffic and ensure safe passage. Autonomous vessels pose a challenge as they cannot be contacted as conventional piloted vessels. At the same time, they provide both the potential to resolve situations themselves as well as do it faster and more accurately than human personnel could achieve. This requires an accurate shared awareness between the autonomous vessels. Other research projects are also addressing this problem, albeit with slightly different solutions. The University of Florence develop a similar system, albeit based on AIS and shared data from ship-borne radars [37]. Kongsberg Maritime AS also develop several systems for situational awareness based on radar, cameras and AIS [28].

A secondary objective of the project is to offer users of recreative vessels with a real-time map of the various vessels in the fjord. This service is dubbed "Augmented AIS". This service is largely targeted at small recreational vessels with onboard radar. These vessels are susceptive to tilting during wind and high waves, potentially blinding the radar. The Augmented AIS, therefore, has a comparative advantage to the on-board radar, in addition to avoiding the investment of a radar. There should be less than a one-second delay from the radar detecting a vessel to the end-user being updated.

Figure 1.1: Overview image of the fjord showing potential radar sites and coverage [19].

The scope of this project is to explore a possible system architecture and its validity for the projects remote site systems. A proof of concept for the on-site data acquisition system is to be developed, in addition to the hardware selection for this system.

## Chapter 2

## **Radar characteristics**

This chapter presents the Simrad Halo 20+ pulse compression radar currently considered for the project. Measurements to characterize the radar waveforms are also presented, as well as some background material for radar systems.

## 2.1 Radar background

The following section aims to provide a short introduction to radar systems and important terms therein, such as IQ samples, complex signals and pulse compression.

### Radar system introduction

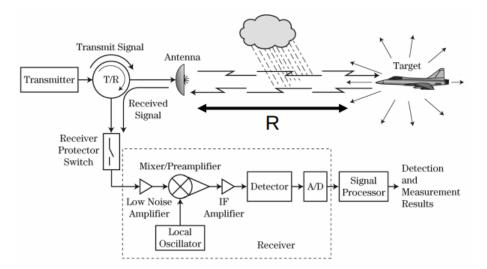

A typical radar transmitter and receiver is shown in Figure 2.1. An oscillator generates a radio frequency (RF) signal which is transmitted by an antenna. The resulting radio wave will propagate until it hits a target. This will cause a fraction of the energy to be transmitted back to the radar. The received signal will be very weak and must first be amplified before it is mixed down to an intermediate frequency (IF). It this stage, a detector can be used to determine whether a target is present or not. Alternatively, the radar signal can be sampled by an analog to digital converter (ADC) as Figure 2.1 suggest. This allows more complicated signal processing to be performed digitally using a signal processor.

Figure 2.1: Typical radar system showing the major elements of the transmit (TX) and receive (RX) processes [33].

#### IQ samples and complex signals

When sampling radar signals it is often desired to measure phase changes between transmit and receive. This is referred to as a coherent receiver and is useful for measuring Doppler shifts [33]. Coherent sampling is achieved by sampling the signal twice with a 90° phase difference in between. These are called the in-phase (I) and in quadrature (Q) samples, respectively, which together make up an IQ-sample. The signal can then be represented as a complex-valued signal, where the I-channel is real and the Q-channel is imaginary. For instance,  $x_{IQ}(t)$  is a complex signal represented by its I- and Q-components,

$$x_{IQ}(t) = x_I(t) + j \cdot x_Q(t),$$

(2.1)

where j is the imaginary unit.

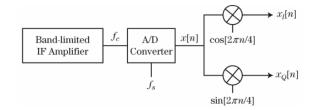

Figure 2.2 illustrates this concept in practice, where a real-valued signal x[n] is split into an I- and Q-channel after being sampled by an ADC. This is done by multiplying the sampled signal with a sine and cosine function, which are separated by a 90° phase offset. Note that the IF signal is band-limited to avoid aliasing.

Figure 2.2: Figure illustrating how an IQ-signal is constructed after sampling an IF signal [33].

#### **Pulse compression**

A basic pulse radar is based on transmitting short duration pulses to detect targets. The radar can transmit more energy by transmitting longer pulses, which increases the signal strength and improves the signal-to-noise ratio (SNR). Longer pulses will however also decrease the radar's ability to distinguish between targets that are very close. This is called the radars range resolution and is given by

$$\Delta R = c_0 \frac{\tau}{2},\tag{2.2}$$

where  $c_0$  is the speed of light and  $\tau$  is the pulse length in seconds. Because the of the inverse relationship between resolution and pulse length, a pulse radar must trade between SNR and range resolution.

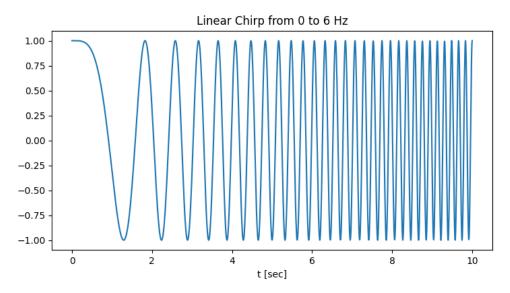

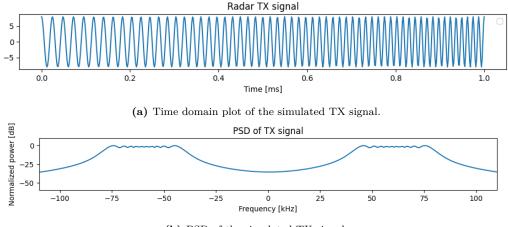

This tradeoff can be overcome by using a chirp radar to decouple the pulse length and range resolution. A chirp radar transmits *chirps*, which are frequency modulated signals that increase or decrease in frequency. One such chirp is shown in Figure 2.3, which clearly shows the increasing frequency from 0 Hz to 6 Hz. A radar can create a chirp by modulating the frequency of a sine wave. By using knowledge of the modulation and frequency change, the radar can demodulate the reflected chirp back to a simple pulse. This technique is called pulse compression, which yields a narrow bandwidth pulse to resolve close targets without decreasing the radars SNR.

## 2.2 Simrad Halo 20+ Radar

A Simrad Halo 20+ Pulse Compression radar is currently considered for the project. While the exact radar to be used in the system is yet to be determined, the Halo 20+ serves as a reference radar for initial development. It can therefore be used to extract design specifications and constraints. Since this is a commercial product, its implementation details and internal workings are largely unknown. Some key specifications are however available from the manual [4], given in Table 2.1.

Frequency and bandwidth specifications are of special interest for sampling the radar signal. Table 2.1 states that the radar operates in the X-band with a center frequency between 9.4 GHz

Figure 2.3: Example of a chirp signal increasing in frequency.

Table 2.1: Key radar specifications taken from the Simrad Halo 20+ Radar manual [4].

| Range                      | 36         | NM      |                                     |

|----------------------------|------------|---------|-------------------------------------|

| Rotation speed             | 20-60      | RPM     | Dependent on mode and display (MFD) |

| Frequency                  | 9.4 - 9.5  | GHz     | X-band                              |

| Transmitter peak power     | 25         | W       |                                     |

| Polarization               | Horizontal |         |                                     |

| Minimum range              | 6          | m       |                                     |

| Sweep repetition frequency | 700-2400   | Hz      | Mode dependent                      |

| Pulse length               | 0.04-64    | us      | $\pm 10\%$                          |

| Sweep bandwidth            | 48         | MHz     | Max                                 |

| Horizontal beamwidth       | 4.9        | degrees | TX and RX                           |

| Noise figure               | 5          | dB      | max                                 |

and 9.5 GHz. The radar sweeps over a maximum of 48 MHz, which dictates the sampling frequency. Another Simrad Halo model additionally lists its intermediate frequency (IF) stage as  $f_{IF} = 70$  MHz [4]. It can be assumed that this is equal to, or at least close to, the IF frequency of the Halo 20+.

#### Time of flight

The radar's two way time of flight (TOF) is also of interest to determine how long the delay is between a transmitted and received signal. Figure 1.1 suggests that a radars in this aplication should be operated with a range of 6 nautical miles, or 11 km. The time of flight t is then given by

$$t = \frac{2 \cdot R}{c_0} = \frac{2 \cdot 11.1 \,\mathrm{km}}{3 \cdot 10^8 \,\mathrm{m/s}} = 74.1 \,\mathrm{\mu s},\tag{2.3}$$

#### Antenna position

It is necessary to know the antenna position to discern where the radar targets are. While the time of flight determines the distance to the target, the position of the antenna determines the direction of the target. The radar does not explicitly state which communication protocol is used to communicate with the antenna rotator. It is however likely that it is based on NMEA 2000, as the radar already uses this to communicate with external systems [4]. Other common antenna rotator interfaces include RS232 or CAN-bus, or simply as a pulsed signal.

## 2.3 Waveform characteristics

This section presents the waveform characteristics of the Simrad Halo 20+ radar acquired by measuring the radar signal. The measurements are important to gain further insight into the functionality of the radar, as well as narrowing down constraints regarding bandwidth and pulse lengths. The measurement setup is also presented, along with a brief discussion of the measurement results.

### 2.3.1 Measurement setup

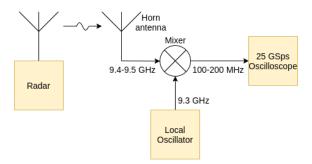

Both time domain and frequency domain representations of the radar waveforms are of interest for further examination. Table 2.1 lists the radar frequency between 9.4 GHz and 9.5 GHz, with a max sweeps bandwidth of 48 MHz. In order to measure the waveform with good resolution, it should be mixed down to the order of a few 100 MHz using a mixer and a local oscillator (LO) before being measured with an oscilloscope. The proposed measurement setup is shown in Figure 2.4.

Figure 2.4: Block diagram of the measurement setup for determining the radar waveforms.

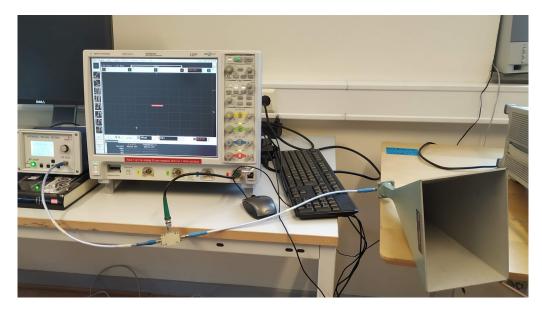

The measurement setup is shown in Figure 2.5. An AnaPico APSIN20G (100 kHz-20 GHz) was used as a local oscillator and set to 9.3 GHz. Considering the frequency and bandwidth of the signal, a signal between 100 and 200 MHz was left after mixing with the local oscillator output. The signal was sampled using an Agilent MSO9254A (2.5 GHz, 25 GSaps) set to 4 GSps. This yields an oversampling rate of at least 20, giving good resolution. The radar was set to different range settings and the data was exported from the oscilloscope to create a spectrogram for each setting. To avoid fading due to the rotating antenna, the radar was put on its side as shown in Figure 2.6. The results are shown in table Table 2.2.

Figure 2.5: Image showing the radar measurement setup with a local oscillator, mixer signal analyzer and a horn antenna.

Figure 2.6: Image showing the radar being put on its side to avoid fading due to the rotating antenna.

### 2.3.2 Measurement results

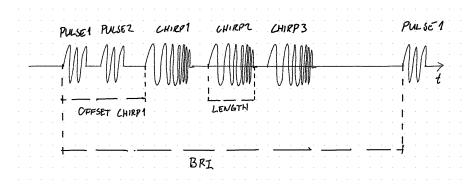

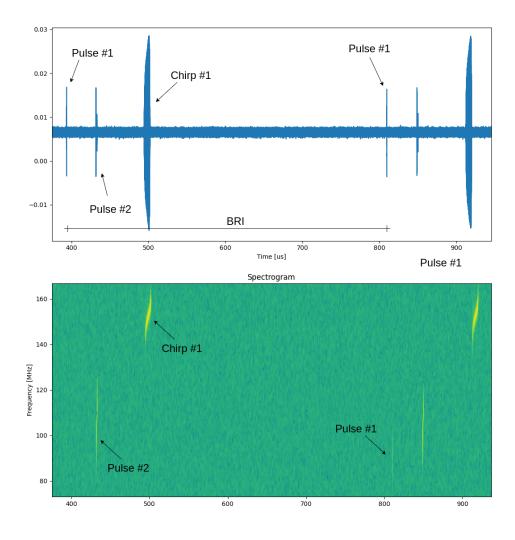

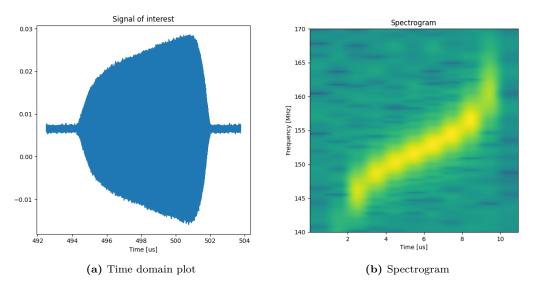

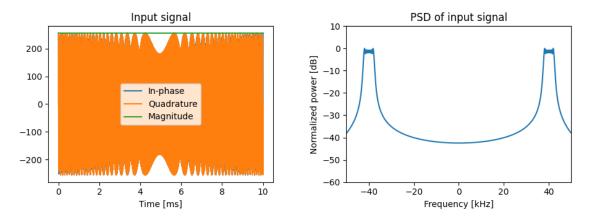

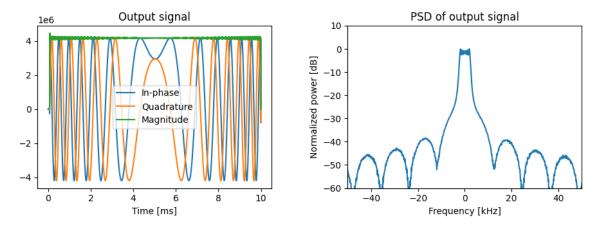

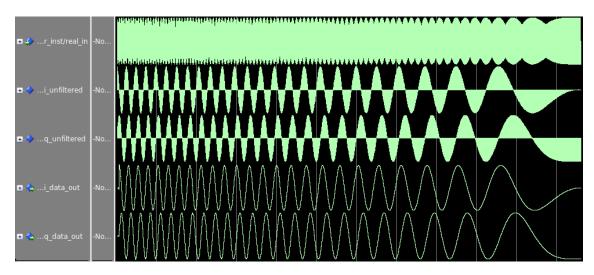

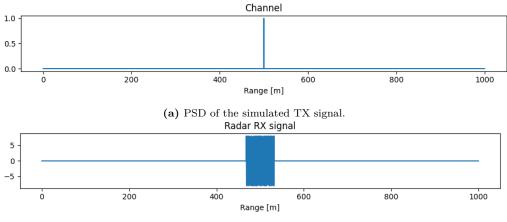

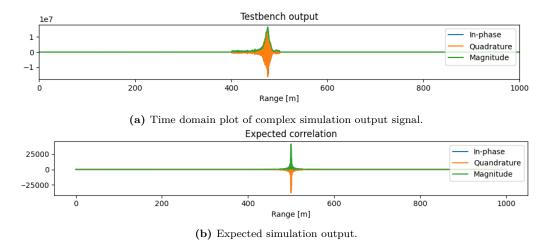

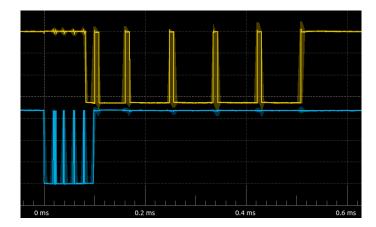

Table 2.2 shows the measurement results for various range settings of the radar. The radar emits bursts consisting of up two pulses followed by up to three chirps, as shown in Figure 2.7. The exact number of pulses and chirps depends on the radar setting. The time between two bursts is denoted the Burst Repetition Interval, while the offset denotes the time since the first pulse in a burst. Two such bursts are shown in Figure 2.8 for the 0.75 NM setting, consisting of two pulses and a single chirp. Figure 2.9 shows the time domain and spectrogram plots of a single chirp, showing how the chirp increases in frequency.

Figure 2.7: Illustration of a radar burst containing two pulses and three chirps. Examples of offset and length, along with burst repetition interval (BRI), are annotated.

The table indicates that the radar emits a single pulse for range settings below 1 NM and two for ranges above that. Likewise, the radar will emit up to three pulses for the longest range. Pulse and chirp center frequencies are listed after downmixing for readability. The true frequencies lie 9.3 GHz above the listed frequencies.

It can be noted that the pulses are of constant frequency and the length independent of the range. The varying frequency of the first pulse is likely attributed to measurement error.

|                  | Burst desc | Burst description                          |             |          |            |             |          |          |                                            |             |

|------------------|------------|--------------------------------------------|-------------|----------|------------|-------------|----------|----------|--------------------------------------------|-------------|

| Radar Range (NM) | Pulse #1   |                                            |             | Pulse #2 |            |             | Chirp #1 |          |                                            |             |

|                  | f1 (MHz)   | $\operatorname{Length}(\operatorname{us})$ | Offset (us) | f2 (MHz) | Length(us) | Offset (us) | fc (MHz) | BW (MHz) | $\operatorname{Length}(\operatorname{us})$ | Offset (us) |

| 0.125            | 100        | 0.1                                        | 0           |          |            |             |          |          |                                            |             |

| 0.25             | 90         | 0.1                                        | 0           |          |            |             | 105      | 30       | 1.75                                       | 38          |

| 0.5              | 90         | 0.1                                        | 0           |          |            |             | 105      | 30       | 1.76                                       | 38          |

| 0.75             | 100        | 0.1                                        | 0           |          |            |             | 110      | 30       | 1.5                                        | 38          |

| 3.00             | 90         | 0.1                                        |             | 110      | 2          |             | 150      | 20       | 10                                         |             |

| 6.00             | 80         | 0.1                                        | 0           | 110      | 2          | 40          | 150      | 12       | 8                                          | 102         |

| 12.00            | 90         | 0.1                                        | 0           | 110      | 2          | 38          | 150      | 15       | 16                                         | 100         |

Table 2.2: Radar waveforms for the Simrad Halo 20+ radar. Not all burst repetition intervals (BRI) could be calculated using the measurements.

|       | Chirp #2 |          |            |             | Chirp #3 |          |                                            |             | BRI (us)  | Remarks                     |

|-------|----------|----------|------------|-------------|----------|----------|--------------------------------------------|-------------|-----------|-----------------------------|

|       | fc (MHz) | BW (MHz) | Length(us) | Offset (us) | fc (MHz) | BW (MHz) | $\operatorname{Length}(\operatorname{us})$ | Offset (us) | Diti (us) | itemarks                    |

| 0.125 |          |          |            |             |          |          |                                            |             |           | Single pulse only           |

| 0.25  |          |          |            |             |          |          |                                            |             |           | Single pulse and chirp      |

| 0.5   |          |          |            |             |          |          |                                            |             |           | Single pulse and chirp      |

| 0.75  | 150      | 20       | 8          | 39          |          |          |                                            |             | 415       | Single pulse and two chirps |

| 3.00  | 130      | 10       | 16         |             |          |          |                                            |             |           | Two pulses and two chirps   |

| 6.00  | 133      | 8        | 15         | 182         | 18       | 4        | 30                                         | 300         | 965       | Two pulses and three chirps |

| 12.00 | 135      | 20       | 15         | 185         | 19       | 4        | 60                                         | 300         | 1020      | Two pulses and three chirps |

Figure 2.8: Time domain and spectrogram plots of two bursts for the 0.75 NM setting. Two pulses and one chirp can be seen for each burst.

### 2.3.3 Measurement discussion

The length of the pulses and chirps increases with the range, likely to improve the SNR for long distances. Pulse #2 is 20 times longer than Pulse #1 and only used for the longer ranges. The pulses seem to have a fixed length. Chirp #1 however increases its length for longer ranges, which is also true for Chirp #2. Chirp #3 is only used for ranges above 6 NM and goes up to 60 µs.

It was not possible to measure the burst repetition interval for all settings. The three measurements that were made indicate that the BRI increases with range. The BRI can however be used to give some indications of the radar time budget. It can be seen that the BRI is some ten times longer than the TOF for the various ranges. For instance, for the 12 NM range the BRI is 1020 µs compared to a TOF of only 148 µs. This is likely to add guard time in case the radar signal bounces of a strong reflector beyond the intended range, which would look like a large vessel on a short-range to the radar. The large BRI can also indicate that the radar uses some time to transfer or process the incoming data.

As shown in Table 2.2, the radar switches frequencies for the chirps. This is likely done to solve

Figure 2.9: Time domain and spectrogram plots of a single chirp for the 0.75 NM setting.

some ambiguity functions or make the radar more resistant to interference. Table 2.2 further reveals that the radar only performs up-chirps. That is, the chirps only increase in frequency. There are no down-chirps that decrease in frequency, which is a common way to resolve the ambiguity function for pulse compression systems [33].

Furthermore, the radar transmits one or two pulses before transmitting the chirps. This may have been done to trigger radar beacons which may not work with chirps. The fact that it switches between transmitting one or two pulses depending on the setting, along with the radar lacking down-chirps, suggests that the pulses may be used to solve the radar ambiguity function by creating estimates of position and velocity.

Figure 2.9 also suggests that the chirp may be non-linear, as seen by the rapid changes in frequency near the edges of the chirp. Non-linear chirps are a technique used by radars to suppress sidelobes [33]. New measurements must be performed to confirm the non-linearity of the chirp.

## Chapter 3

## System architecture

This chapter presents the initial project specifications. Estimates for required sampling frequencies and data rates are presented, based on measurements of radar waveforms from a reference radar. The proposed system architecture is presented, along with hardware selection and a proposed FPGA fabric design.

## 3.1 System specification

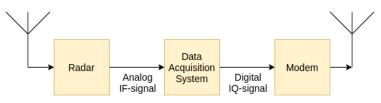

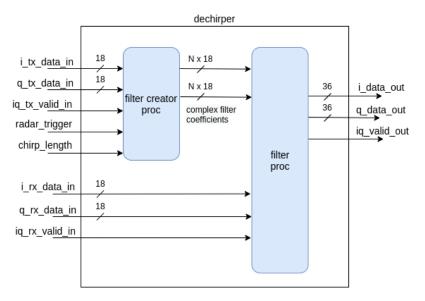

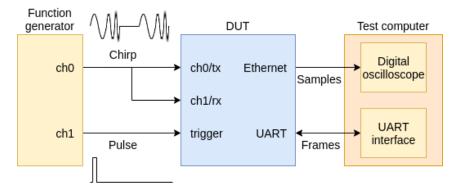

The remote site system shall sample and transmit a stream of IQ-samples from the various radar sites to a central processing hub. The data shall be sampled at the radars IF stage using a data acquisition system, as shown in Figure 3.1. As the reference radar is a pulse compression radar, the data acquisition system must also perform dechirping of the received signal, as explained i Section 2.1. Due to the function of the pulses being currently unknown, only the chirps will be considered at this time. The transfer of data shall be done via a mobile broadband connection to avoid the need for cables. 5G should preferably be used due to strategic partnerships with Telia Norge AS during the roll out of their new infrastructure in Trondheim. As the radar network is part of a safety-related system, there should be emphasis on minimizing latency as well. It is desired that the overall system provides less that a one second delay between receiving the radar data to broadcasting the radar tracks to subscribing systems.

Figure 3.1: Overview of the system.

As the sites are remote, the system shall also have some debug and configuration options that can be accessed remotely.

Since the project is at an early development stage, commercially available off-the-shelf (COTS) parts are preferred to create a minimum viable product (MVP).

The following list summarizes the requirements set for the system at this stage:

- Sample an intermediate frequency (IF) radar signal at 70 MHz.

- Perform dechirping on the reflected radar signal.

- Precisely timestamp IQ-samples for correlation with the data from other sites.

- Transmit data from site to the central processing hub via mobile broadband.

- Offer remote access and debug capabilities for each site.

- Hardware should be COTS

The specs presume a stream of IQ-data are to be transmitted from the radar site. It is therefore assumed that no further processing than the dechirping is desired on-site at this point.

## 3.2 System proposal

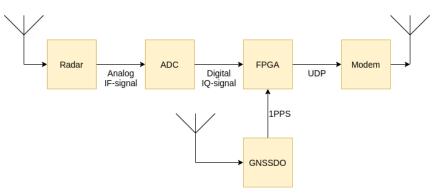

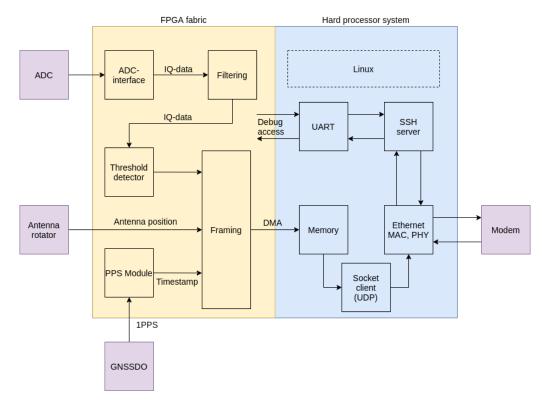

The proposed system for the remote site data acquisition is shown in Figure 3.2.

The data acquisition system is split into an ADC (Analog to Digital Converter) and FPGA (Field-Programmable Gate Array). The analog radar waveform is sampled by an ADC at the radar IF-stage. Both the transmitted and received signals are sampled in order to perform the dechirping, as discussed in Section 3.3. The digitized waveforms are transmitted to an FPGA for processing. An FPGA is chosen as it is well suited for fast, deterministic signal processing at the order of a few 100 MHz. In addition, FPGAs add flexibility due to being re-programmable, so the design can be updated and expanded as needed in the future. The FPGA can also be used to do signal conditioning and preprocessing before it is sent to the central processing hub, to ease the computational load and latency constraints of the latter.

A modem is used to transfer the data to the central processing hub. The User Datagram Protocol (UDP) is preferred for the uplink of data due to its simplicity and low latency. It is also well suited for streaming data in real time systems, as UDP is an unreliable protocol that will drop lost packets rather than request a time consuming re-transmission.

The FPGA must know the exact time of arrival of the radar waveforms. This is necessary to compare data from different sites. While a operating system or processor with a network stack can request the current time trough an internet connection, sub-second precision must be provided trough the use of a GPS (Global Positioning System) disciplined oscillator (GPSDO). The GPSDO uses the accurate clocks in the GPS system as a time source and provides a pulse per second (PPS or 1PPS) signal.

The antenna position must also be transmitted along with the radar data, so the direction of the radar targets can be known. This will however not be considered at this point, due to the radar antenna interface being unknown.

Figure 3.2: Proposed system architecture.

## **3.3** Proposed FPGA architecture

Figure 3.3 shows the proposed FPGA architecture. SoC (System on Chip) FPGAs, such as the proposed solution, contain a Hard Processing System (HPS) in addition to the usual programmable fabric. The HPS consists of a microprocessor, which can run a Linux-based operating system or be programmed bare metal. In either case, the HPS can be used to implement functionality that is better suited for software, such as using a network stack. The namesake programmable fabric of the FPGA consists of generic logic units, which the compiler uses to implement behaviour specified by a hardware description language (HDL), such as VHDL (Very High Speed Integrated Circuit Hardware Description Language). The fabric additionally contains RAM blocks and special DSP blocks with multipliers for signal processing.

An ADC interface in the FPGA fabric provides a stream of IQ-samples from the ADC. Desired signal processing is performed on the IQ-samples, including dechirping of the radar signal. This is proceeded by a threshold detector to remove the samples between the received signals, in order to reduce the amount of data. The processed IQ-samples is given to a framer, which packs the IQ-data with metadata such as the antenna position and a timestamp from the GNSSDO.

While using Ethernet PHY is possible directly from the FPGA fabric, the use of a MAC-layer (Media Access Control layer) and the rest of the network stack is inherently a software job. Therefore the transfer of the data to the modem should be handled by a HPS rather than the FPGA fabric. The same applies to providing an UDP/IP stack and handling socket traffic to transfer the data to the central processing hub. FPGAs not including an HPS can still initialize a processor in the fabric through the use of an IP core. These are however inherently slower, as they typically use a fabric oscillator at only hundreds of MHz, rather than some GHz. A HPS also works out of the box, requires no extra licenses and can be used to program the FPGA fabric of necessary.

The frames with IQ-samples, antenna position and timestamps are transferred from the FPGA fabric to the HPS via direct memory access (DMA). DMA lets the FPGA fabric directly access the system memory without interrupting the processor, while the processor is busy transferring the frames to the modem via Ethernet and UDP.

The use of a HPS also allows the system to run a Linux-based operating system. As the modem provides the system with an Internet connection, the system can be reached through an SSH (Secure Shell) session for debugging and configuration. As Figure 3.3 indicates, the SSH session can access the FPGA fabric via UART or similar interconnects. Furthermore, the FPGA fabric can also be completely reprogrammed by the HPS if necessary or fall back to a safe version of the firmware if a critical error is detected [15].

## 3.4 Data rate calculation and link budget

While the Nyquist theorem states that it is theoretically sufficient to sample the radar signal at its Nyquist rate, oversampling the signal increases design flexibility at an early stage in the project. This makes it possible to change the radar, which may also change the signals bandwidth and enter frequency. Furthermore, oversampling has the added benefit of enabling averaging of samples to reduce white noise and therefore increase the effective number of bits (ENOB). For instance, for each additional bit of resolution, the signal must be oversampled by a factor of four [27]. To maximize the design flexibility, using an oversampling factor of four is suggested.

The required ADC resolution is not quantitatively known, as this would require knowledge of the receiver noise level and clutter-to-noise-ratio (CNR), amongst others [33]. As a general rule of thumb, the effective number of bits for an ADC is usually one to three bits less than listed due to the SNR of the device. Qualitatively, this places the ADC in the 12-14 bit range. Opting for a higher number of bits early on also makes for a more flexible option for early development.

The reference radar is according to Section 2.2 stated to use an IF stage of 70 MHz and a chirp bandwidth of 48 MHz. Examining the radar measurements in Table 2.2 show that the bandwidth is at most 30 MHz, but that the center frequencies vary. To find the necessary sampling rate for the ADC, the highest frequency component of the IF signal must be known. Examining the measurements, chirp #1 is revealed to have the highest frequency component at 160 MHz for the longest ranges. However, these measurements are taken at an IF frequency of 100 MHz. Considering

Figure 3.3: Overview over fabric design.

the chirp at an center frequency of 70 MHz yields a highest frequency component of 130 MHz. The data rate calculations for sampling the radar IF signal are thus given in Table 3.1.

| Parameter                             | Value               |

|---------------------------------------|---------------------|

| Highest frequency component $f_{max}$ | $130\mathrm{MHz}$   |

| Nyquist rate $2f_{max}$               | $260\mathrm{MHz}$   |

| Oversampled 4 times                   | $1040\mathrm{MHz}$  |

| ADC resolution                        | $14\mathrm{bit}$    |

| Data rate at Nyquist rate $r_{IF}$    | $3.64\mathrm{Gb/s}$ |

| With oversampling $r_{IF,4}$          | $14.6{ m Gb/s}$     |

Table 3.1: Sample rate and data rate estimates for the IF signal.

The calculations in Table 3.1 reveals that the ADC must at least be able to sample at 260 MHz to satisfy the Nyquist requirement, but up towards 1.0 GHz to add flexibility. This requires the ADC interface to be able to transmit between 3.64 Gb/s and 14.6 Gb/s for a 14 bit resolution.

The data rate requirements for transmitting the radar data to the processing hub varies from the data rate requirements of the ADC, as shown in Table 3.2. Here it is assumed that the varying center frequencies can be ignored by moving the various chirp bandwidths down to complex baseband with digital down conversion (DDC). It is further assumed that the signal is reduced to its Nyquist rate to minimize the data rate. As the listed and measured sweep bandwidth differ, an estimate is given for both. The data rate can be further reduced by neglecting the samples between the bursts, rather than continuously streaming the incoming samples. The burst itself constitutes at most 30% of the burst repetition interval, seen at the 12 NM range setting in Table 2.2. Therefore the data rate can potentially be reduced by 70%. More could be removed if the pulses and chirps were isolated.

Table 3.2 shows that the remote site must be able to continuously transmit at least 0.84 Gb/s or 1.34 Gb/s, depending on which estimate is used. If only the bursts are transmitted, this can be reduced all the way down to 0.25 Gb/s for the slightly smaller measured sweep bandwidth. To allow for some overhead and add flexibility, the target uplink rate should be increased towards 1.0 Gb/s, which is a factor of four above the minimum specified.

|                                | Listed              | Measured            |

|--------------------------------|---------------------|---------------------|

| Bandwidth B                    | 48 MHz              | 30 MHz              |

| Nyquist rate $2B$              | $96\mathrm{MHz}$    | $60\mathrm{MHz}$    |

| ADC resolution                 | $14\mathrm{bit}$    | $14\mathrm{bit}$    |

| Data rate at baseband $r_{cb}$ | $1.34\mathrm{Gb/s}$ | $0.84\mathrm{Gb/s}$ |

| $r_{cb}$ with 30 % duty cycle  | $0.40\mathrm{Gb/s}$ | $0.25{ m Gb/s}$     |

Table 3.2: Data rate estimates for the complex baseband signal for both the listed and measured sweep bandwidth.

## 3.5 Hardware requirements and selection

This section summarizes the hardware requirements set by the design requirements and proposed design. A selection is made and a bill of materials (BOM) is presented at the end.

## 3.5.1 ADC and FPGA

The ADC and FPGA should be part of a development kit to shorten development time. As such, the selection of these two components are closely related and presented together here. In general, it is desired that both components are part of a development kit and easy to interface with each other. Preferably, they should be part of an evaluation kit consisting of an FPGA and ADC to start development faster. This kit should include the minimum source code to get the ADC and FPGA to work together.

#### **ADC** requirements

Sampling rate and data transfer requirements are taken from Section 3.4. The ADC must be part of a development kit or similar that can be readily used, rather than an integrated circuit (IC). It must also employ high-speed interfaces that are easily combined with FPGAs.

The ADC should also provide digital downconversion (DDC) and support complex signals as output to avoid the need to implement it on the FPGA.

To summarize, the ADC requirements are:

- Sampling IF signals at 1 GSps

- Resolution of 12-14 bits

- Support transfer of up to  $15\,\mathrm{Gb/s}$  of sampled data

- Part of a development kit

- Easy to interface with FPGA

- Should support digital downconversion (DDC)

#### **FPGA** requirements

The FPGA is responsible for interfacing with the ADC at high data rates, do real-time signal processing on the digitized IF signal and transmit the data to the processing hub. It also provides a flexible development platform which can be reprogrammed to respond to changing requirements and designs. The FPGA should preferable be part of a development kit with lots of exposed IO, such as PMOD, GPIO, UART/USB-connections for debug, LEDs and various buttons.

Section 3.4 suggests that a Gigabit Ethernet connection is required due to the high data rates. As mentioned in Section 3.3, the FPGA must provide an Ethernet MAC layer which requires a HPS. Thus a SoC FPGA is desired. The FPGA should also be sufficiently large to accommodate future signal processing logic. By experience a mix-range FPGA with around 100.000 logic elements and above a hundred DSP blocks should suffice. These requirements stem from mid-range Cyclone V FPGA the commonly used for such signal processing [9].

To summarize, the FPGA requirements are:

- SoC FPGA

- Gigabit Ethernet connector

- At least 100 000 logic elements

- Above 100 DSP blocks

- High-speed interface for ADC

- Varied IO interfaces such as UART, PMOD, LEDs and buttons

#### ADC and FPGA selection

Arrow Electronics was chosen as the hardware supplier for the data acquisition system as they are the official vendor for both Intel FPGA and Analog Devices in Norway. They offer both recommendations, advice and support for these products.

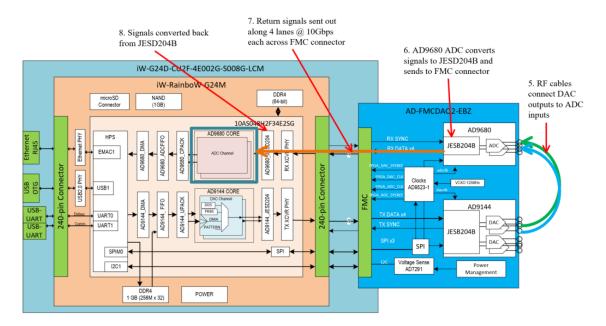

**iWave's Intel Arria10 SoC/FPGA FMC+ Development Kit** (IW-G24D-CU2F-4E002G-S008G-LCM) was recommended by Arrow as a FPGA board for this project. It is part of a reference design for the AD-FMCDAQ2 offered by Analog Devices and Arrow Electronics shown in Figure 3.4. This means that the hardware combination of FPGA and ADC is verified to work, as well as the accompanying HDL. It is also one of the few FPGA boards currently available with an FMC (FPGA Mezzanine Card) HPC (High Pin Count) connector.

(a) iWave Arria 10 SoC Development Board(b) AD-FMCDAQ2 [16][22].

Figure 3.4: Pictures of the selected FPGA and ADC for the project.

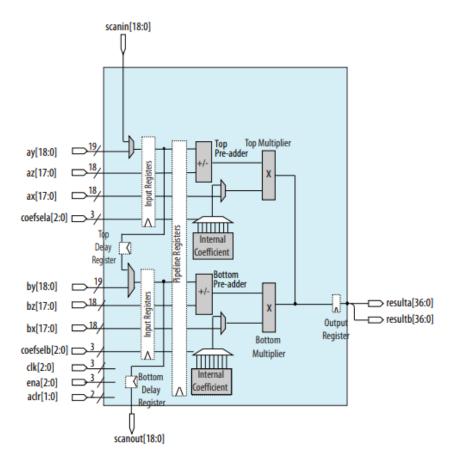

The Analog Devices AD-FMCDAQ2-EBZ is a combined ADC and DAQ extension card. It is based on the AD9680 ADC with 14 bit resolution and 1.0 GSPS sampling rate. The card uses a FMC HPC connector and performs data transfer to the FPGA via a JESD204B data interface. It has four FMC lanes running at 10 Gbit/s for the two ADC-channels, which covers the data rate requirement [16]. The ADC can be further configured via SPI (Serial Peripheral Interface) to enable digital down-conversion and signal decimation. Timestamping of the sampled data is also supported for aligning samples from multiple chips [17]. The samples are timestamped relative to a reference signal. This can be considered for the future, if latency between the FPGA and ADC proves to be a problem. While the DAQ is not needed, it can be useful for testing the system by generating test signals. [21].

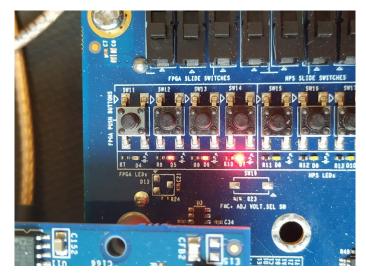

The iWave systems development kit consists of an Intel Arria 10 SX480 SoC/FPGA system-on-amodule (SOM) and a carrier card containing a FMC HPC (also called FMC+) connector and a Gigabit Ethernet Port. The on-board FMC connector matches the data rate of the ADC, being able to receive a total of 40 Gbit/s of data. This more than covers the data rate requirement from section Section 3.4. The FPGA has 480k logic elements and a speed grade of -2. It features 2736 DSP blocks that can handle 18x19 bit fixed-point multiplication at 438 MHz [12]. The board also contains PCIe lane connectors, USB Blaster-II interface, Pmod connectors, as well as various LEDs, push buttons and switches [22]. The development kit from Arrow was deemed as very good as it more than satisfies the requirements. This combined with the reference design and free support on both FPGA and ADC led to the development kit being selected for the project.

### 3.5.2 Modem

The modem is responsible to upload the radar data from the remote site. It must do so according to the data rate calculations in Section 3.4. Although a partnership with Telia Norway AS provides early access to the 5G network in Trondheim, the choice will be further elaborated here along with a modem selection.

To satisfy the criteria of up to 1.0 Gbit/s mobile broadband with a high data rate must be used. While the standards are numerous and telecommunication company claims vary, the 3GPP Releases and ITU standards give a good overview. The 3GPP Release 15, which specifies the initial release of 5G, has a target uplink rate of 50 Mbit/s according to the ITU.[1] This number serves as an indicator of the mean data rate, described as the "user experienced data rate" taking protocol overhead and environment variations into account. It should also be noted that this applies only to the eMBB (enhanced Mobile Broadband) part of 5G.

Telia on the other hand only specifies a maximum data rate of at least four times that of their 4G+ networks [5]. This accounts to a maximum data rate of 140 Mbit/s. The maximum data rate is however not suitable to calculate mean operating conditions. It is also not specified weather this is the maximum data rate that can be achieved under the right operating conditions, or the max that can be served in the duration of a short burst of data. Therefore the ITU performance requirements likely give a better and more balanced indication of the data rates.

The Celerway Arctus is a high-end, ruggedized and 5G-ready modem which has been previously tested in the related MilliAmpere project [6]. It has the required gigabit Ethernet interface for the FPGA. The modem itself supports above 1 Gbit/s uplink with load balancing by using six SIM card slots. Using the ITU and Telia data rate estimates, this amounts to between 300 Mbit/s and 840 Mbit/s. The minimum data rate of 0.25 Gbit/s lies somewhere slightly below the presumed mean estimate by ITU, but this leaves little design overhead. It is therefore suggested that measurements must be done to verify the data rate. Furthermore, more signal processing should be applied to decrease the required data rate further.

No further alternatives were found for modems at the time of writing, likely due to the relatively new technology. Teltronika, another modem producer, does not have any 5G ready hardware at the time of writing but expects to release a comparable modem that can be considered in the future [18].

## 3.5.3 GNSSDO

A GNSSDO (Global Navigation Satellite Systems Disciplined Oscillator) is required for creating accurate timestamps for the radar data. The GNSSDO must have a 1PPS output to help the FPGA determine the exact UTC time. Furthermore, the accuracy of that pulse directly affects the range accuracy of the radar. A 10 ns delay in the system will cause a  $c \cdot 10 \text{ ns}/2 = 1.5 \text{ m}$  error in range. Therefore the jitter of the 1PPS signal should be low, but for the development phase some tens of nanoseconds will be sufficient.

As the radar network is a key part of the Ocean Lab Node2 infrastructure, it should also be resistant to jamming and have a high holdover capability should a loss of signal occur. The latter is achieved by featuring the GNSSDO with an extremely stable oscillator. This lets the GNSSDO function with very low frequency drift over an extended time period without being disciplined by GNSS until the signal can be reacquired.

The requirements for a GNSSDO are summarized as follows:

- 1PPS output

- Jitter at only tens of nanoseconds

- Should have holdover capability

- Should be jamming resilient

Furuno supplies high-end GNSSDOs, but for the early development stage the Digilent PMOS GPS suffices as a proof of concept. The PMOS interface is a good fit for the iWave development board as well. It should be noted that the listed jitter of only 10 ns seems a bit low compared to the industrialized Furuno alternatives.

## 3.5.4 Bill of materials (BOM)

A selection of components is presented in the BOM (bill of materials) in Table 3.3. For the initial development, only the iWave, AD-FMCDAQ2 and PMOD GPS module have been acquired.

| Name                                  | Price (NOK, exc. VAT) | Vendor                         |

|---------------------------------------|-----------------------|--------------------------------|

| iWave Intel Arria10 SoC/FPGA FMC+     | 19800                 | Arrow Electronics [22]         |

| AD-FMCDAQ2-EBZ                        | 13600                 | Arrow Electronics              |

| Celerway Arctus                       | 0                     | Borrowed. Price not incquired. |

| Digilent GPS Expansion Module 410-237 | 340                   | RS Components [7]              |

| Sum:                                  | 33740                 |                                |

## Chapter 4

## Implementation

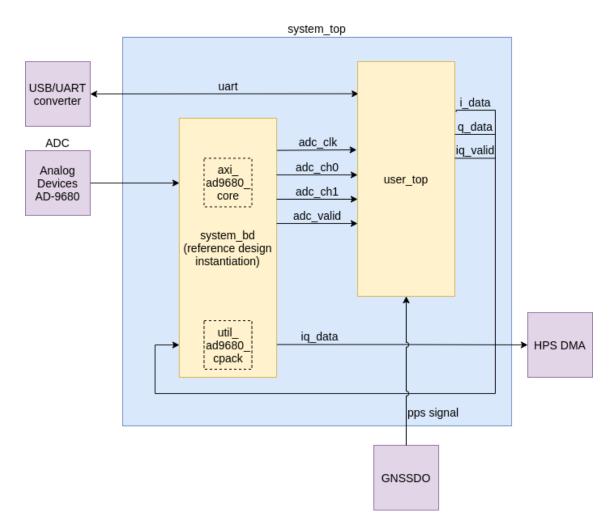

The following chapter presents an overview of the reference design and how it is altered for the project. It is shown how signals of interest are exported from the **system\_bd** entity, which contains the reference design. The new **user\_top** entity is introduced to contain the application specific logic, also called the user logic. Furthermore, each module in the user top is presented and documented.

The entire codebase, including the modified reference design, can be found at https://gitlab.com/peteruran/ntnu-coastal-radar.

## 4.1 Reference design

The reference design is provided by Arrow Electronics and Analog Devices for the evaluation kit containing the iWave Arria 10 SoC board and the AD-FMCDAQ2. It consists of HDL which can be found at GitHub under https://github.com/ArrowElectronics/hdl.git. The reference design also provides a Linux image for the HPS and a software oscilloscope to test the ADC. The following section presents an overview of the design, as well as a manual on how to build and modify it.

## 4.1.1 Overview of the reference design HDL

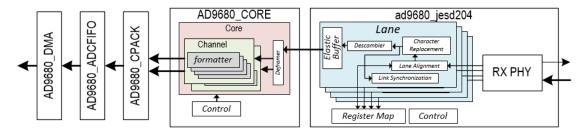

The reference design provided by Arrow Electronics is shown in Figure 4.1. The RX path in the fabric is emphasized in Figure 4.2. The figures show that the sampled data is transmitted over FMC to the FPGA, where it is received in the AD9680\_JESD204 entity. This entity handles the implementation of the JESD204B protocol, including deserialization of the serial data and synchronization of the four serial channels. The AD9680\_CORE entity deframes the data and provides two 64-bit buses for ADC channels ch0 and ch1, as well as a valid signal for each stream.

The samples are then transferred to the HPS via direct memory access (DMA). The DMA is configured to use a 128 bit bus. As such, the AD9680\_CPACK entity will combine the ch0 and ch1 samples to a single 128-bit vector, which is buffered up in the AD9680\_FIFO before being transferred to the HPS domain with DMA.

The data is further streamed from the HPS via Ethernet using a *libiio* daemon running on a Linux core on the HPS. *libiio* is a protocol developed by Analog Devices for streaming sensor data in an industrial setting [20].

It should also be noted that transferring 14-bit samples using 64-bit signals is under-optimized, especially in regards to the DMA. However, altering the DMA is dependent on the HPS implementation, which is out of scope at this time. Keeping the larger bus also adds flexibility at this point.

### 4.1.2 Building the reference design

The Arrow Electronics reference design requires the Intel Quartus Prime Standard version 18.0 software, which can be downloaded from https://fpgasoftware.intel.com/18.0/?edition=

Figure 4.1: Overview over the reference design provided by Arrow Electronics, showing a loopback configuration. [20]

Figure 4.2: The RX path in the FPGA fabric.

standard&platform=linux. The build script will look for Quartus in the system path. The build script will fail if it detects that another version of Quartus is being used.

A floating license can be checked out from the Department for Electronic Systems license server 1716@europa.iet.ntnu.no while being connected to Eduroam. This also works while being connected to Eduroam via the NTNU VPN server (vpn.ntnu.no). Note that the free Quartus Lite version is not sufficient, as does not include support for Arria10 devices.

To build the reference design, first clone the Arrow Electronics HDL repository from Github.

```

git clone https://github.com/ArrowElectronics/hdl.git

cd hdl

```

The repository contains HDL (hardware description language) for various Analog Devices daughter boards and accompanying carrier boards. The latter include both Intel and some Xilinx boards. Checkout the correct branch for the iWave carrier board.

```

1 git checkout R18.0_IW_CC_2.0

```

To build the HDL, use **make** and target the **daq2** project for the **iwg24d**. The latter is a short form for the iWave board.

```

1 make daq2.iwg24d

```

12

The build process can take a significant amount of time to complete, taking up to several hours. The Makefile will run several Tcl-scripts to setup and configure dependencies for the project. The completed project folder will contain a Quartus project file to configure and synthesize the design, a Quartus Qsys (also known as Platform Designer in new versions of Quartus) file to configure peripherals and interconnects. The **system\_bd/system\_top.v** file contains the design's top level entity **system\_bd**.

### 4.1.3 Modifying the reference design

There are several ways to alter the reference design to include the user logic. One can either

- modify the HDL files directly,

- create a new Qsys component for the user logic and connect it using Qsys,

- or export the system\_bd signals of interest and manually instantiate and connect the user top.

While modifying the HDL files directly is most straightforward and requires less use of the tools, doing so puts the design changes at risk of being overwritten should the Platform Designer be used to regenerate the HDL wrappers. While creating a new Qsys component mostly consists of selecting the desired HDL source files in the tool, it creates an unnecessary hard dependency on using Qsys to build the design. A decision is made to divide and conquer by exporting the signals of interest from Qsys and manually instantiate an entity for the user logic. This leaves the responsibility of generating the reference design to Qsys, while the designer keeps full control of the changes in the user logic. This also has the added benefit of being able to keep the altered reference design and user top in separate git repositories. This is an advantage as the latter can be updated and simulated independently, in addition to increasing the portability of the design. The altered reference design only is needed for the compilation.

To contain the user logic, a new entity must be inserted into the design. As it contains the user logic and provides a new top-level abstraction created by the user, it shall be called the *user top*. Figure 4.3 shows how the user top is inserted into the reference design by exporting signals of interest from system\_bd. The user top must use valid-handshaking on its input and output interfaces to match the proceeding and succeeding entities in the signal processing chain. This is a simple bus protocol enforcing the use of a separate valid signal to indicate whether the data in the associated data bus is valid or not [23].

The design is altered by first opening the **system\_bd.qsys** file in Qsys. This will open a large list of Qsys components with ports and interconnects. As it is desired to insert the **user\_top** entity between the **axi\_ad9680\_core** and **util\_ad9680\_cpack** entities, the **adc\_ch\_0** and **adc\_ch\_1** must be exported, along with the **adc\_valid** and **adc\_clock** signals. The Qsys components with their ports are shown in Figure 4.4 and Figure 4.5. Exporting the signals is done by clicking the "Export" tab in Qsys for both entities. This will break the connection between the entities and instead expose the signals as ports in the **system\_bd** entity. These ports can then be connected to the **user\_top** instance in the **system\_top.v** file.

After exporting the desired signals the HDL must be regenerated. The Qsys generated entity is called **system\_bd** and is manually instantiated in **system\_top.v** as part of the reference design. The port map of the **system\_bd** instance in **system\_top.v** must be manually updated to reflect the changes done in Qsys. When this is done, the **user\_top** entity can be instantiated beside **system\_bd** in **system\_top.v**. The user should ensure that the **adc\_clock** signal is routed to the **user\_top** along with the data to keep everything in the same clock domain.

### 4.1.4 Pitfalls and other considerations

This section lists some important considerations to successfully set up the project, as well as some pitfalls.

### VHDL vs Verilog wrappers

Qsys has an option to generate the HDL wrappers in either Verilog or VHDL. Generating the system\_bd entity in VHDL resulted in numerous syntax errors. While the **user\_top** entity is written in VHDL, it can easily be instantiated in Verilog as Quartus provides multi-language

Figure 4.3: Overview of the system top entity, illustrating how the system\_bd and user\_top entities are connected.

support. This has the added benefit of not needing to translate the **system\_top.v** to VHDL, as that is a manually created file supplied as part of the reference design.

### Generation of the QIP file

When exiting Qsys, the user is prompted to generate a QIP (Quartus Prime IP) file to store the file paths for all the IP cores. This file must NOT be added to the project, as it is automatically generated and used by **system\_qsys.tcl**. Adding the QIP file will cause it to interfere with the **system\_qsys.tcl** script and break the synthesis chain.

#### Adding VHDL 2008 support

Quartus Standard only has limited support for the 2008 version of the VHDL standard, compared to Quartus Pro which has full support. While this edition of the standard has few changes for synthesizable code and targets mainly simulation, it brings support for useful constructs such as unconstrained elements in arrays. VHDL 2008 support must be enabled by opening the .qpf (Quartus Project file) file and adding the following line:

set\_global\_assignment -name VHDL\_INPUT\_VERSION VHDL\_2008

#### Changing the IP regeneration policy

Quartus will automatically regenerate the whole design, including the Qsys components, when the project is compileded. Since the Qsys components are mostly unchanging and that all frequent

#### CHAPTER 4. IMPLEMENTATION

| 6             | ∃ axi_ad9680_core | axi_ad9680            |                    |                            |

|---------------|-------------------|-----------------------|--------------------|----------------------------|

| $\rightarrow$ | s_axi_clock       | Clock Input           | Double-click to    | sys_clk                    |

| $\rightarrow$ | s_axi_reset       | Reset Input           | Double-click to    | [s_axi_clock]              |

| $\rightarrow$ | s_axi             | AXI4Lite Slave        | Double-click to    | [s_axi_clock]              |

| $\rightarrow$ | if_rx_clk         | Clock Input           | Double-click to    | ad9680_jesd204_link_clk    |

|               | if_rx_sof         | Conduit               | Double-click to    |                            |

| $\rightarrow$ | if_rx_data        | Avalon Streaming Sink | Double-click to    | [if_rx_clk]                |

|               | if_adc_clk        | Clock Output          | axi ad9680 core if | axi_ad9680_core_if_adc_clk |

| 0-0-          | adc_ch_0          | Conduit               | axi_ad9680_core_a  | [if_rx_clk]                |

| <u>~</u> ~    | adc_ch_1          | Conduit               | axi_ad9680_core_a  | [if_rx_clk]                |

|               | if adc dovf       | Conduit               | Double-click to    |                            |

Figure 4.4: The entry for the ad9680\_core entity in Qsys, showing the ports, clocks and protocols. Note the exported signals in the right hand side.

|                     | 🗉 util_ad9680_cpack | util_cpack  |                   |                         |

|---------------------|---------------------|-------------|-------------------|-------------------------|

| $\rightarrow$       | if_adc_clk          | Clock Input | Double-click to   | ad9680_jesd204_link_clk |

| $\rightarrow$       | if_adc_rst          | Reset Input | Double-click to   | [if_adc_clk]            |

|                     | if_adc_valid        | Conduit     | Double-click to   |                         |

| ¢                   | if_adc_sync         | Conduit     | Double-click to   |                         |

|                     | if_adc_data         | Conduit     | Double-click to   |                         |

| $\rightarrow \sim$  | adc_ch_0            | Conduit     | util_ad9680_cpack | [if_adc_clk]            |

| $\diamond \diamond$ | adc_ch_l            | Conduit     | util_ad9680_cpack | [if_adc_clk]            |

|                     |                     |             |                   |                         |

Figure 4.5: The entry for the ad9680\_cpack entity in Qsys, packing the ADC ch0 and ch1 into a signle signal.

design updates happen in the user\_top, Quartus' IP regeneration policy can be changed to only generate IP cores once. This change removes much of the projects compilation time. This setting is found under the Assignments pane > Settings > IP Settings > IP Regeneration Policy and is set to "Never regenerate design files for IP cores".

### Removal of the DAC code

Compiling the reference design shows multiple setup time violations related to the JESD204 interface of the now unused AD9144 DAC (Digital to Analog Converter). This indicates that the routing algorithm struggles to route the signals in a way ensuring they arrive on time. To fix these, all AD9144 components are removed in Qsys as they played no integral part of the application specific design either way. This has the added benefit of speeding up compilation time, save FPGA resources and relax routing constraints. The removed components are the avl\_ad9144\_fifo, ad9144\_jesd204, axi\_ad9144\_core, util\_ad9144\_unpack and axi\_ad9144\_dma.

#### Bitstream generation and programming

As the design contains a HPS, the Intel design guidelines discourage programming the FPGA directly with Quartus [13] as this can crash the Linux drivers using the FPGA-HPS interconnect. A restart of the HPS will also cause it to reprogram the FPGA with the bitstream present on the SD card.

To create a new bitstream for the HPS to use when programming the FPGA, the quartus\_cpf utility can be used to generate a RBF file (Raw Binary File). This must then be placed on the boot-partition of the SD card in the iWave Arria 10 card.

To generate the RBF file, run:

```

1

```

```

quartus_cpf -c -o bitstream_compression=on daq2_iwg24d.sof

socfpga.rbf

```

## 4.2 User top overview

The user top entity contains the application specific design to be inserted into the reference design. This partitioning makes it easier to focus on the core design, as well as increasing the portability. It also makes it simpler and faster to simulate part of the design rather than the system in its entirety.

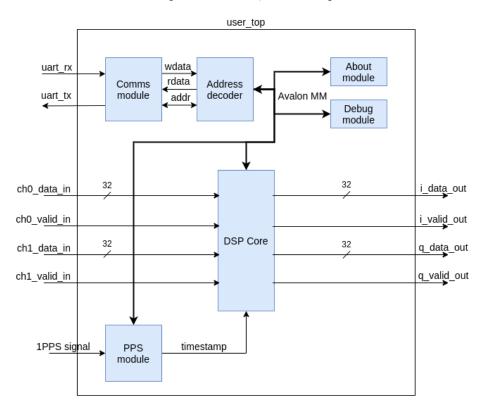

The user top consists of several debug and convenience modules. The comms module implements a UART interface to the FPGA fabric that can be connected to either the HPS or external ports. Together with the address decoder it makes up a system for register access, where registers can be read and written to. The UART interface and register access are together referred to as the debug interface. This is convenient to provide an entrypoint to inspect the internal workings of the FPGA, as well as adjusting settings in runtime rather than compile time. The address decoder acts as a bridge between the comms module and the various modules. It uses an Avalon MM interface covered in Table 4.3 to access the module registers.

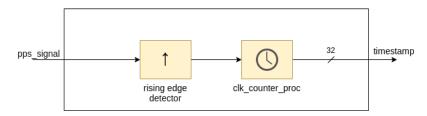

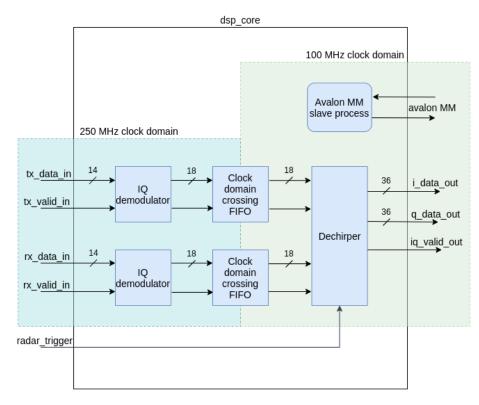

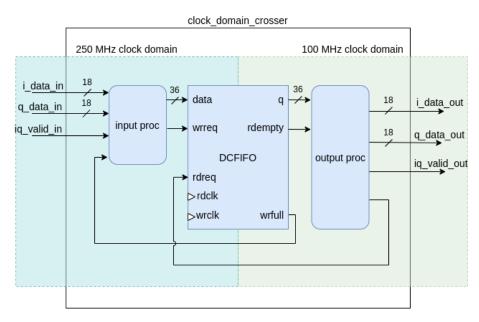

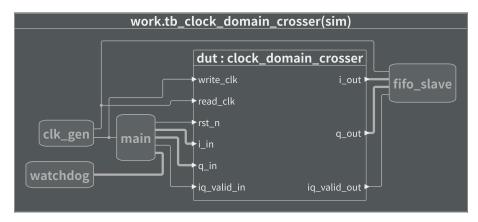

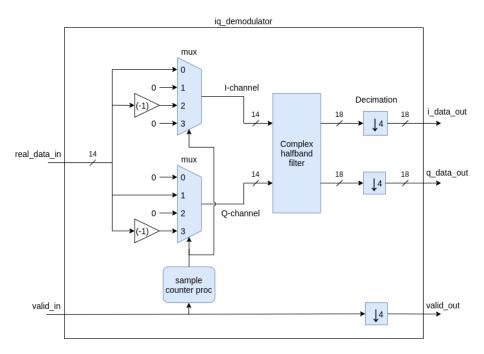

All signal processing is performed inside the DSP Core to provide another abstraction level in the design. It uses a simple valid interface to receive and transmit samples and receives accurate timestamps from the PPS module. The DSP core is covered in Section 4.3.

This section presents the various modules in the user top, along with their testbenches. Testcases and simulation results for the user top and DSP core are presented in Section 5.1. The simulator and test framework selection is also presented there, with an explanation of VUnit.

Figure 4.6: Overview of the user\_top entity.

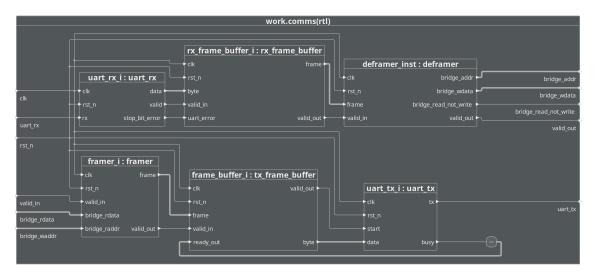

### 4.2.1 Comms module

The comms module is responsible for providing access to the FPGA fabric via UART. It is part of the chain of modules enabling read and write access to FPGA registers together with the address decoder. An overview of the module is shown in Figure 4.7. The UART configuration is shown in Table 4.1.

| Baud rate | Data bits | Stop bits | Parity | Flow control | Bit order             |

|-----------|-----------|-----------|--------|--------------|-----------------------|

| 115200    | 8         | 1         | None   | None         | Least significant bit |

Figure 4.7: Overview over the comms module, showing both the TX- and RX-chain.

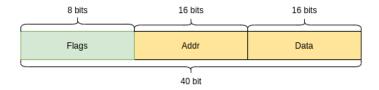

Communication is based on frames, containing a header followed by an address and data. The frame is shown in Figure 4.8, consisting of header, address and data fields. The frame is used for both transmit (TX) and receive (RX). The frame header contains flags for specifying write and read, in addition to other system status and error flags. The header flags are listed in Table 4.2. More bits can be reserved in the future for transmitting various status and error flags, such as an unknown address error.

Table 4.2: Table of flags in the frame header.

| Bit number | Flag           | Purpose                                              |

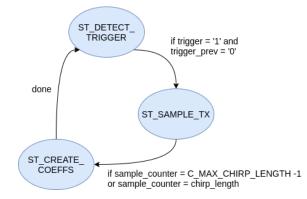

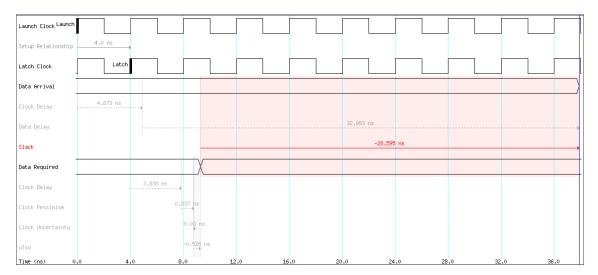

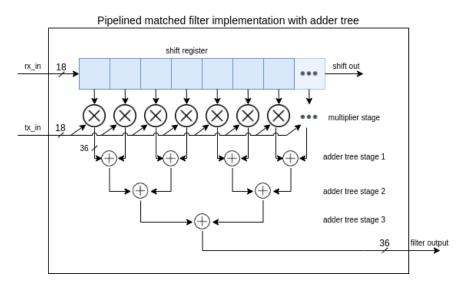

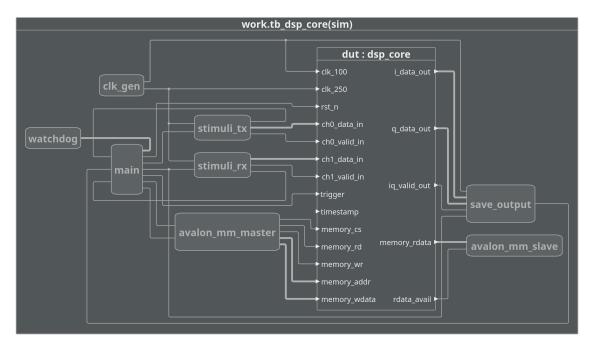

|------------|----------------|------------------------------------------------------|