# Phase-Tracking Robust-Synchronization-Loop for Grid-Connected Converters

Mohammad Amin, Senior Member, IEEE,

Abstract—This paper presents a novel phase-tracking robustsynchronization-loop (RSL) to track the phase and frequency of the grid voltage. A detailed analytical model of the proposed RSL algorithm is presented. Further, a state-space small-signal model is developed, including the dynamics of a grid-connected converter and its controller. From the small-signal analysis, it is shown that the eigenvalues associated with the states of the RSL remain in the left half-plane even for a very weak grid condition with a grid impedance of 1.0 pu, thus, it provides better stability property with the grid-connected converters. In order to show the effectiveness of the proposed RSL, simulation results are provided for different scenarios of the grid conditions such as voltage and frequency disturbance, unbalance grid condition and grid faults. Further, the performance of the RSL algorithm is tested by experiment in lab. The results show that the proposed method effectively tracks the phase and frequency of the grid voltage and maintains the good synchronism of the converters during different disturbances.

*Index Terms*—Robust-synchronization-loop, grid-connected converter, synchronization, converter controller, phase-tracking-loop.

#### I. INTRODUCTION

T HE power electronics converters is increasingly used in modern power systems for integrating distributed generation (DG) based on renewable energy sources (RES) [1]–[3]. These power electronic converters are controlled using different techniques such as the standard vector control, model predictive control, [4]–[6] and more recently artificial intelligence-based control such as artificial neural network, fuzzy logic control [7]. Regardless of the control strategy employed in these DG converters, a synchronization unit is required in the controller in order to synchronize the terminal voltage of the converters to the grid before connecting them to the grid [8]–[10]. The synchronization enables the converters to connect effectively to the grid without a harmful transient overcurrent during the connection.

The synchronization of grid-connected converters is usually accomplished by detecting the phase of the grid voltage using a phase-locked-loop (PLL) [11]. The PLL is first introduced in 1930s for the synchronous reception of radio signals [12]. It is now widely used in the modern power system, to estimate the phase, frequency and amplitude of the fundamental voltage, to measure the harmonics, inter-harmonics, power quality indices, in machine drives, power electronics-based renewable energy integration, high voltage dc (HVDC) transmission system, and flexible ac transmission system (FACTS). The PLLs present a proper performance under a balance voltage condition and a strong grid condition, however, the performance of PLLs degrades significantly under an unbalanced and distorted condition of the grid voltage, load unbalances, as well as measurement scaling error and dc offset, produces periodic disturbances. In order to improve the issues, several advanced PLLs have been proposed, for example, a moving average filter with the synchronous reference frame (SRF) PLL improves the disturbance rejection capability [13]; the dual a SRF filtering-based PLL (DSRF-PLL) improves the performance for imbalance voltage [14]; the delayed signal cancellation (DSC) improves the frequency variation performance [15]; the adaptive PLLs provides a dynamically change PLL bandwidth to achieve a fast-tracking performance for large phase jump [16]. The other advanced PLLs that exist in the literature are Type-N PLL and Quasi Type-N PLLs [17]. More details about the recent advancement on the PLL can be found in the following review paper [11]. Even though the advanced PLLs improve the performance of one targeted matrices while degrading the others, for example, the MAF improves disturbance rejection capability while degrading the dynamic performance; the DSC increases the computational effort and the implementation complexity. Moreover, PLLs are inherently non-linear, difficult and time-consuming tuning the PLLs to achieve satisfactory performance and introduce an instability problem with the grid-connected converters, especially a weak grid condition (a high impedance grid) [18], [19].

Frequency-locked-loop (FLL) is often used for the synchronization of grid-connected converters [20]. The main difference between the PLL and FLL is that PLL is implemented in SRF (dq-frame) while the FLL is in the  $\alpha\beta$ -frame [21]. The PLL has reached a mature stage of development in power and energy applications, contrary the FLL is not a mature technique yet, however, from the functional point of view, both FLLs and PLLs are equivalent and are nonlinear negativefeedback control systems [11], [21]. This equivalence implies that FLLs have similar issues as the PLLs. Further development of the FLLs allows the designer to mitigate the issues, for example, in order to tackle the dc offset, two additional integrator can be realized [22]; to improve performance for imbalance voltage and harmonics, a parallel configuration of two or more first-order complex band-pass filter can be used [23]. More details about the recent advancement of the FLLs can be found in the following review papers [21], [24].

The power exchange between the grid and the converters can be used to realize the synchronization mechanism of a gridconnected converter which utilizes the internal synchronization

Manuscript received August xx, 2021 and revised September xx, 2021; accepted October xx, 2021.

Mohammad Amin is with the Department of Electric Power Engineering at the Norwegian University of Science and Technology, Trondheim, 7491, Norway, e-mail: mohammad.amin@ntnu.no

mechanism of an ac system in a similar way as the operation of a synchronous generator (SG) [25]–[27]. This type of synchronization technique is known as power-synchronizationloop (PSL) [27]. A PLL is no longer required during the normal operation of the grid-connected converter, however, in some situations like the converter is in blocked stage, it needs a PLL to provide the initial synchronization signal to the converter controller before connection. During a severe ac-system fault, the PSL synchronization switches to the PLL synchronization mode to limit the current flowing into the converter semiconductor devices. This adds complexity to the overall control system and will impact its stability. Furthermore, control algorithms for converters have been developed where the synchronization can be performed without a dedicated synchronization unit like PLL [28], [29]. Those controllers mimic the synchronization mechanism of an SG and provide the grid voltage and frequency support. The performance of these controllers is very satisfactory during a normal operation of the grid. The main concern of these controllers is the limited capability of regulating current during faults as these controllers do not have an internal current control-loop.

This paper presents a new phase-tracking-loop, so-called Robust-Synchronization-Loop (RSL) for the grid-connected DG converters to track the phase and frequency of the grid voltage. The main difference between the PLL and proposed RSL is that in a PLL, the q-axis voltage is forced to be zero by a PI/PID controller to get the phase of the voltage, while in the proposed RSL, the estimated phase angle makes the q-axis voltage to zero without using a PI/PID controller. A detailed analytical model of the proposed RSL algorithm is presented. Further, a state-space small-signal model is developed which includes the dynamics of a grid-connected converter and its controller. The analytical small-signal model is also verified by comparing it with a simulation model. From the small-signal analysis, it is shown that the eigenvalues associated with the states of the RSL remain in the left half-plane even for a very weak grid condition with a grid impedance of 1.0 pu, thus, it provides better stability property with the grid-connected DG converters. Simulation and experimental results are provided to show the effectiveness of the proposed RSL. The results show that the proposed method effectively tracks the phase and frequency of the grid voltage and maintains the good synchronism of the DG converters.

The concept of the proposed RSL has been introduced in the author's conference version of the paper [30]. The new contribution compared to the conference paper comprises the following: (i) a detailed theoretical analysis, including the small-signal modeling and stability analysis, (ii) the performance comparison with the standard PLL, and (iii) experimental verification of the proposed RSL for a grid-connected converter. The rest of the paper is organized in the following. Section II presents the development of the proposed RSL synchronization mechanism. Section III presents the statespace model development and parameter tuning of the RSL. Section IV presents the small-signal model development for the grid-connected converter and the small-signal analysis of the system. Simulation and experimental results are presented

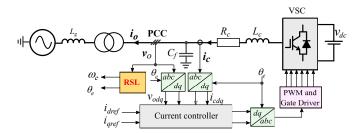

Fig. 1. A grid-connected DG converter and its controller with an RSL.

in section V. Finally, this paper is concluded in Section VI.

## II. THE PROPOSED ROBUST-SYNCHRONIZATION-LOOP

Fig. 1 shows a grid-connected converter. The dc-side can be connected to a RES, such as solar PV, battery energy storage, wind power generator. In this work, a dc-voltage source has been considered here. Before enabling the pulse-width-modulation (PWM) of the converter switches, the converter voltage must be synchronized with the point of common coupling (PCC) voltage  $v_o$  in order to avoid a transient overcurrent. The synchronization unit is used to serve that purpose.

The RSL generates a voltage, e internally in the digital signal processor, which is synchronized with  $v_o$  to track the frequency and phase of the PCC voltage. Initially, it is assumed that e is not synchronized with  $v_o$ , thus, the magnitude and phase of e are not the same as  $v_o$ . As these two voltages are not synchronized, there will be a voltage error,  $v_{err} = e - v_o$ . The PCC voltage is available in the digital controller through voltage sensors. If a virtual impedance is introduced in between the RSL and PCC voltage, a virtual current  $i_v$  flows through this virtual impedance due to this voltage error. Thus, the virtual current can be given by

$$\mathbf{i_{vabc}} = \frac{\mathbf{e_{abc}} - \mathbf{v_{oabc}}}{sL_v + R_v} \tag{1}$$

where the bold font is used to represent the voltage in the matrix form for the three-phase system, as  $\mathbf{e_{abc}} = [e_a \ e_b \ e_c ]^T$ ,  $\mathbf{v_{oabc}} = [v_{oa} \ v_{ob} \ v_{oc} ]^T$  and  $\mathbf{i_{vabc}} = [i_{va} \ i_{vb} \ i_{vb} ]^T$ ;  $L_v$  and  $R_v$  are virtual inductor and resistor. The power due to this virtual current can be given by

$$\begin{bmatrix} P_v \\ Q_v \end{bmatrix} = \begin{bmatrix} \sin \theta_v & -\cos \theta_v \\ \cos \theta_v & \sin \theta_v \end{bmatrix} \begin{bmatrix} \frac{3EV_o}{Z_v} \sin \delta \\ \frac{3E^2}{Z_v} - \frac{3EV_o}{Z_v} \cos \delta \end{bmatrix}$$

(2)

where E and  $V_o$  are the RMS value of e and  $v_o$ , respectively;  $\theta_e$  and  $\theta_o$  are their corresponding phase angle and  $\delta = (\theta_e - \theta_o)$ ;  $Z_v$  and  $\theta_v$  are the magnitude and angle of the virtual impedance.

The purpose of implementing RSL is to estimate the phase of the PCC voltage to synchronize the converter voltage to the grid. The synchronization is achieved when the estimated RSL voltage e becomes equal to the PCC voltage  $v_o$ , i.e.,

$$E = V_o \text{ and } \theta_e = \theta_o. \tag{3}$$

The active and reactive power in (2) becomes zero, regardless of the virtual impedance type when  $E = V_o$  and  $\theta_e = \theta_o$ , i.e.

when synchronization is achieved. Contrary, synchronization can be achieved by regulating the active and reactive power to zero.

The virtual impedance is selected to be dominantly inductive which gives  $\theta_v \approx \pi/2$ . Thus, the active and reactive power can be rewritten by

$$\begin{bmatrix} P_v \\ Q_v \end{bmatrix} = \begin{bmatrix} \frac{3EV_o}{Z_v} \sin \delta \\ \frac{3(E-V_o \cos \delta)}{Z_v} E \end{bmatrix}.$$

(4)

The active and reactive power in (4) give a positive correlation between the active power with the frequency and the reactive power with the voltage which can be expressed as

$$P_v \sim \delta$$

and  $Q_v \sim E$ . (5)

The frequency of the PCC voltage can be given by

$$\omega_o = \omega_s + \Delta \omega_s \tag{6}$$

where  $\omega_s$  is the system fundamental frequency and  $\Delta \omega_s$  is the frequency deviation from the fundamental frequency. This frequency deviation is resulting from the active power deviation which can be expressed as

$$\Delta\omega_s = -k_p \Delta P \tag{7}$$

where  $k_p$  is a droop gain or a positive gain and  $\Delta P$  is the power deviation that causes fundamental frequency deviation.

As it is assumed, initially, the RSL generated voltage is not synchronized, it results in a phase difference,  $\delta$  and the frequency difference,  $\Delta \omega_e$ . Thus, the frequency of the RSL voltage can be expressed as

$$\omega_e = \omega_o + \Delta \omega_e \tag{8}$$

and the phase difference between the PCC and the RSL voltages can be expressed by

$$\delta = \int \Delta \omega_e dt. \tag{9}$$

An integral controller is introduced to compensate this phase error of the estimated voltage by regulating active power as

$$\delta = k_p \int \left( P^* - P_{v2} \right) dt. \tag{10}$$

where  $P^*$  is the reference active power and  $P_{v2}$  is the virtual active power introduced by the phase difference between the PCC voltage,  $v_o$  and RSL internally generated voltage, e. Hence, the estimated frequency of the RSL can be written by

$$\omega_e = \omega_s - k_p \Delta P + k_p \left( P^* - P_{v2} \right). \tag{11}$$

When the synchronization is achieved,  $\delta$  becomes zero. It can be achieved by setting the reference power,  $P^*$  to 0 in (10). Thus, the estimated frequency and phase of the RSL can be given by

$$\omega_e = \omega_s - k_p P_v \tag{12}$$

$$\theta_e = \int \omega_e dt. \tag{13}$$

where  $P_v = \Delta P + P_{v2}$ .

$\underbrace{v_{oabc}}_{e_{abc}} \underbrace{v_{err}}_{e_{abc}} \underbrace{1}_{v_{abc}} \underbrace{i_{val}}_{i_{vq}} \underbrace{i_{vq}}_{i_{vq}} \underbrace{i_{vq}}_{e_{d}} \underbrace{i_{vq}}_{i_{vq}} \underbrace{i_{vq}}_{e_{d}} \underbrace{$

Fig. 2. Proposed phase-tracking robust-synchronization-loop.

Another condition in (3) for achieving the synchronization is having the equal magnitude of the estimated RSL voltage and the PCC voltage. This can be achieved by setting

$$E = V_o \tag{14}$$

which is available in the digital controller through voltage transducer and after applying Clarke transformation as

$$V_o = \sqrt{v_{o\alpha}^2 + v_{o\beta}^2} / \sqrt{2}.$$

(15)

The RSL generates voltage  $e_{abc}$  in the stationary abc-frame, and produces the phase angle that keeps the q-axis voltage to zero. Hence, the magnitude of the d- and q-axis voltage is given by

$$e_d = \sqrt{2E} \text{ and } e_q = 0. \tag{16}$$

Thus, the RSL voltage can be given in the *abc*-frame by

$$\mathbf{e_{abc}} = \mathbf{T_{dq}}(\theta_e) \begin{bmatrix} e_d \\ e_q \end{bmatrix}$$

(17)

where

$$\mathbf{\Gamma_{dq}}(\theta_e) = \begin{bmatrix} \cos \theta_e & -\sin \theta_e \\ \cos(\theta_e - \frac{2\pi}{3}) & -\sin(\theta_e - \frac{2\pi}{3}) \\ \cos(\theta_e + \frac{2\pi}{3}) & -\sin(\theta_e + \frac{2\pi}{3}) \end{bmatrix}.$$

This RSL generated voltage is used to obtain the virtual current in (1). The virtual current can be expressed in dq-frame as

$$\begin{bmatrix} i_{vd} \\ i_{vq} \end{bmatrix} = \mathbf{T}_{\mathbf{dq}}^{-1}(\theta_e) \mathbf{i}_{\mathbf{vabc}}.$$

(18)

Since the q-axis component of the estimated voltage is directly set to zero, the virtual active power can be given by

$$P_v = \frac{3}{2} e_d i_{vd}.$$

(19)

Hence the RSL is proposed as

$$\frac{d\theta_e}{dt} = \omega_s - k_p P_v \tag{20}$$

$$e_d = \sqrt{2}E = \sqrt{v_{o\alpha}^2 + v_{o\beta}^2}$$

and  $e_q = 0.$  (21)

The proposed RSL is shown in Fig. 2, where the virtual impedance structure forms into a virtual admittance structure. The virtual admittance structure emulates the output impedance without leading to difficulties in hardware implementation. Note that a low pass filter is often necessary to remove the high-frequency component from the power.

## III. DYNAMIC REPRESENTATION AND PARAMETER TUNING OF THE RSL

## A. State-space modeling of the RSL

The virtual current in (1) can be presented by differential equation as

$$L_v \frac{d\boldsymbol{i_{vabc}}}{dt} = \boldsymbol{e_{abc}} - \boldsymbol{v_{oabc}} - R_v \boldsymbol{i_{vabc}}.$$

(22)

Since the small-signal analysis cannot be directly applied to the *abc*-stationary frame, the modeling and analysis of the system will be presented in a SRF. The transformation of the three-phase quantity from the stationary reference frame to the SRF is based on the amplitude-invariant Park transformation, thus, the dynamic equation of the virtual current can be given in the dq-frame as

$$\frac{di_{vd}}{dt} = \frac{e_d}{I} - \frac{v_{od}}{I} - \frac{R_v i_{vd}}{I} + \omega_e i_{vq}$$

(23)

$$\frac{di}{dv} = \frac{L_v}{L_v} = \frac{L_v}{L_v} = \frac{L_v}{L_v}$$

$$\frac{di_{vq}}{dv} = \frac{e_q}{L_v} - \frac{v_{oq}}{L_v} - \frac{R_v i_{vq}}{L_v} - \omega_e i_{vd}.$$

(24)

$$\frac{1}{dt} = \frac{1}{L_v} - \frac{1}{L_v} - \frac{1}{L_v} - \omega_e \imath_{vd}.$$

(24)

A low pass filter (LPF) is introduced to remove the high-frequency component from the virtual active power. With the LPF, (20) can be rewritten as

$$\frac{d\theta_e}{dt} = \omega_s - k_p P_{vf} \tag{25}$$

where

$$P_{vf} = \frac{\omega_{lf}}{s + \omega_{lf}} P_v. \tag{26}$$

$P_{vf}$  is the filtered virtual active power and  $\omega_{lf}$  is the cut-off frequency of the low pass filter. The LPF can be presented in the state-space form as

$$\frac{dP_{vf}}{dt} = \omega_{lf} \left( P_v - P_{vf} \right). \tag{27}$$

The dynamic performance of the RSL can now be described by (23), (24), (25) and (27) which is presented in the state-space form through a 4th order non-linear model.

#### B. Parameter tuning

The phase tracking speed of the RSL depends upon the design of the parameters. As shown in Fig. 2,  $L_v$ ,  $R_v$  and  $k_p$  need to be selected to achieve the desired performance for the grid-connected converter. The open-loop transfer function can be used to find the value of  $L_v$ ,  $R_v$  and  $k_p$ . The RSL is a nonlinear negative feedback control system like the other synchronization units [11], [21], therefore obtaining the control-loop transfer function needs a lot of effort for the designing the parameters. The step of obtaining the transfer function has been described in the following.

In order to derive the transfer function, a relationship between the phase and dq-voltage is obtained. Applying Clarkeand Park-transformation, the dq-frame PCC voltage can be given by [11]

$$v_d = \sqrt{2} V_o \cos\left(\Delta \theta_o - \Delta \theta_e\right) \tag{28}$$

$$v_q = \sqrt{2V_o} \sin\left(\Delta\theta_o - \Delta\theta_e\right). \tag{29}$$

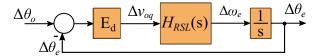

Fig. 3. Small-signal linearized model of the robust-synchronization-loop.

The RSL tracks the phase of the PCC voltage, i.e.,  $\Delta \theta_o = \Delta \theta_e$  which gives

$$v_d \approx E_d$$

(30)

$$v_q \approx E_d \left( \Delta \theta_o - \Delta \theta_e \right) \tag{31}$$

wher  $E_d = \sqrt{2}V_o$ .

(

As can be seen in (31),  $v_q$  contains the phase information which will be used to derive the open-loop and closed-loop transfer function of the RSL.

In the RSL implementation, the virtual active power given in (19) is realized to obtain the phase information. Since the phase information in (31) is obtained in terms of the q-axis voltage, it needs to find a relation between the q-axis voltage and the virtual active power. It can be started with the virtual currents. The dynamic equation of virtual current in the dqframe has been given by (23) and (24). Applying Laplace transform, the dynamic equation of the virtual current can be rewritten in the small-signal form as

$$(sL_v + R_v)\Delta i_{vd} = \Delta e_d - \Delta v_{od} + \omega_e L_v \Delta i_{vq}$$

(32)

$$sL_v + R_v)\Delta i_{vq} = -\Delta v_{oq} - \omega_e L_v \Delta i_{vd}$$

(33)

Again, the voltage magnitude in (21) can also be obtained from the dq-frame voltage as

$$e_d = \sqrt{v_{od}^2 + v_{oq}^2} \tag{34}$$

which in the small-signal form gives

$$\Delta e_d = \frac{V_{od}}{\sqrt{V_{od}^2 + V_{oq}^2}} \Delta v_{od} + \frac{V_{oq}}{\sqrt{V_{od}^2 + V_{oq}^2}} \Delta v_{oq}$$

(35)

where capital letter is used to represent the steady-state values. At steady-state,  $V_{oq} = 0$ , which gives

$$\Delta e_d = \Delta v_{od}.\tag{36}$$

Inserting (36) into (32), solving for  $i_{vd}$ , the relation between the *d*-axis virtual current and *q*-axis voltage can be given by

$$\Delta i_{vd} = -\frac{\omega_e}{L_v} \frac{1}{s^2 + 2s\frac{R_v}{L_v} + \frac{R_v^2}{L_v^2} + \omega_e^2} \Delta v_{oq}.$$

(37)

Inserting this relation in (19) and combine with (12), it can be obtained

$$\Delta \omega_{e} = \frac{3E_{d}k_{p}\omega_{e}}{2L_{v}} \frac{1}{\left(s^{2} + 2s\frac{R_{v}}{L_{v}} + \frac{R_{v}^{2}}{L_{v}^{2}} + \omega_{e}^{2}\right)} \Delta v_{oq}$$

The small-signal model of the RSL is depicted in Fig. 3 where  $H_{RSL}(s)$  is defined

$$H_{RSL}(s) = \frac{3E_d k_p \omega_e}{2L_v} \frac{1}{\left(s^2 + 2s\frac{R_v}{L_v} + \frac{R_v^2}{L_v^2} + \omega_e^2\right)}$$

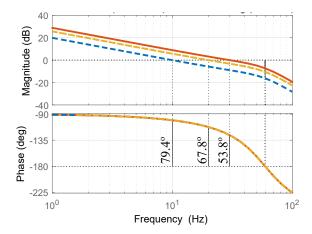

Fig. 4. Frequency response of the open-loop transfer function.

The open-loop transfer function of the RSL can now be given by

$$T_{RSL-OL}(s) = \frac{3E_d^2 k_p \omega_e}{2L_v} \frac{1}{s \left(s^2 + 2s \frac{R_v}{L_v} + \frac{R_v^2}{L_v^2} + \omega_e^2\right)}.$$

(38)

Eqn. (38) indicates that a higher value of  $k_p$  provides fast tracking performance while reduces the noise reduction capability as it increases the bandwidth of open-loop transfer function. A higher value of the virtual impedance ratio,  $\frac{R_v}{L_v}$  provides a better stability property. Therefore, the selection of the virtual impedance and  $k_p$  is a trade-off between the response time and the stability of the synchronization loop.

The magnitude of the open-loop gain of (38) at the crossover frequency  $\omega_c$  is unity. Thus, according to (38), it can be written:

$$|T_{RSL-OL}(j\omega_c)| = 1 \tag{39}$$

which gives

$$k_{p} = \frac{2L_{v}}{3E_{d}^{2}\omega_{s}}\sqrt{\left(2\omega_{c}^{2}\frac{R_{v}}{L_{v}}\right)^{2} + \omega_{c}^{2}\left(\left(\frac{R_{v}^{2}}{L_{v}^{2}} + \omega_{s}^{2}\right) - \omega_{c}^{2}\right)^{2}}.$$

(40)

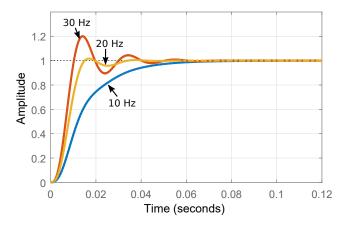

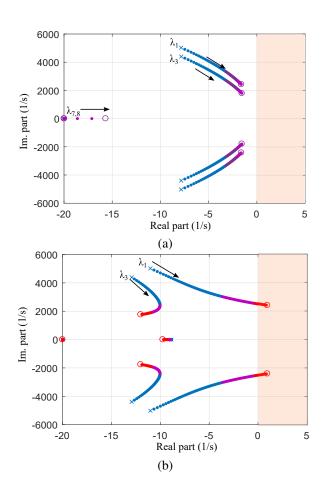

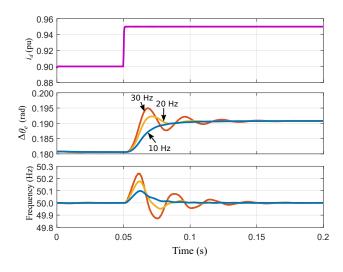

It is straightforward selecting the value of the virtual inductor and resistor based on the converter parameters. The parameter of the test converter setup is given in Table I. An example of the control tuning is presented here, where  $L_v = 0.25$ mH, i.e., 50% of the converter inductance and the resistance,  $R_v = 0.05 \Omega$  are used.  $k_p$  can be calculated by setting the crossover frequency  $\omega_c$ . The bode plot of the open-loop transfer function is shown in Fig. 4 for  $\omega_c$  of  $2\pi 10$ ,  $2\pi 20$ and  $2\pi 30$  rad/s. As can be seen, the open-loop frequency responses have a phase margin of  $79.4^{\circ}$ ,  $67.8^{\circ}$  and  $53.8^{\circ}$  at 10, 20 and 30 Hz, respectively which ensure the stability of the synchronization-loop. In order to further investigate the performance, the location of the closed-loop poles and step responses have been studied. The closed-loop transfer function of the RSL can be given by

$$T_{RSL-CL}(s) = \frac{\frac{3E_d^2 k_p \omega_s}{2L_v}}{s^3 + 2\frac{R_v}{L_v} s^2 + \left(\frac{R_v^2}{L_v^2} + \omega_s^2\right) s + \frac{3E_d^2 k_p \omega_s}{2L_v}}{2L_v}.$$

(41)

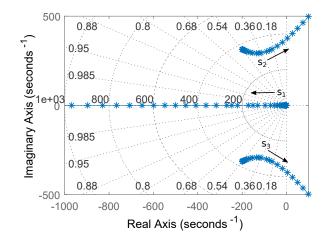

Fig. 5. Root-lucas plot of the closed-loop transfer function.

Fig. 6. Step response of the closed-loop transfer function.

The root-lucas of the closed-loop system is shown in Fig. 5. The closed-loop transfer function shows that RSL has three poles in the form of  $s_1 = -\alpha_1, s_{2,3} = -\alpha_2 \pm j\omega_d$ . As shown in Fig. 5, the pole  $s_1$  always stays in the left half-plane while the left or right half-plane location of  $s_{2,3}$  depends on the parameter. Moreover, the performance of the RSL depends on the location of the poles. The dominant pole determines the performance of the RSL. If  $s_1$  is the dominant pole, then performance will be over-damped otherwise it will be under-damped response. The step response of the closedloop system for the three crossover frequencies are shown in Fig. 6 where it is over-damped response for  $f_c = 10$ Hz with  $s_1 = -75.4, s_{2,3} = -162.3 \pm j296.5$  as  $s_1$  is the dominant pole, while it is under-damped response for 20 Hz with  $s_1 = -167.3, s_{2,3} = -116.4 \pm j293.6$  and 30 Hz with  $s_1 = -240.1, s_{2,3} = -79.9 \pm j306.5$  as  $s_{2,3}$  is the dominant pole. In order to further verify this theoretical analysis, the simulation results are presented for these three designs in Section V-A1 (see Fig. 12), which proves the accuracy of the theoretical design. The 30 Hz design has an overshoot of 20%, however, 10 Hz and 20 Hz designs ensure the robustness and stability of the closed-loop RSL, therefore, both designs can be implemented.

TABLE I

PARAMETERS OF THE CONVERTER SYSTEM.

| Parameters                     | Values                    | Parameters | Values          |

|--------------------------------|---------------------------|------------|-----------------|

| Rated line voltage (RMS), Vo   | $100\sqrt{\frac{3}{2}}$ V | $C_f$      | $50\mu\text{F}$ |

| Rated dc voltage, $V_{dc}$     | 300 V                     | $L_c$      | 0.5 mH          |

| Rated frequency, $f$           | 50 Hz                     | $L_v$      | 0.25 mH         |

| Converter filter inductance, L | 0.2 mH                    | $R_v$      | $0.05\Omega$    |

#### IV. SMALL-SIGNAL MODELING AND STABILITY ANALYSIS

# A. State-space modeling of the converter and its controller

The electrical circuit of a converter for analytical modeling is shown in Fig. 1 where  $L_c$  and  $R_c$  are the total series inductance and resistance between the converter and PCC,  $C_f$  is the filter capacitance connected at PCC and  $R_g$  and  $L_g$  are the grid resistance and inductance including the series resistance and inductance of the transformer. The dynamic equations of the converter current, the capacitor voltage and the grid current can be given in the dq-frame by

$$\frac{d\boldsymbol{i_{cdq}}}{dt} = \frac{\boldsymbol{v_{cdq}}}{L_c} - \frac{\boldsymbol{v_{odq}}}{L_c} - \left(\frac{R_c}{L_c} + j\omega_g\right)\boldsymbol{i_{cdq}} \quad (42)$$

$$\frac{d\boldsymbol{v_{odq}}}{dt} = \frac{\boldsymbol{i_{cdq}}}{C_f} - \frac{\boldsymbol{i_{odq}}}{C_f} - j\omega_g \boldsymbol{v_{odq}}$$

(43)

$$\frac{d\boldsymbol{i_{odq}}}{dt} = \frac{\boldsymbol{v_{odq}}}{L_g} - \frac{\boldsymbol{v_{gdq}}}{L_g} - \left(\frac{R_g}{L_g} + j\omega_g\right)\boldsymbol{i_{odq}}$$

(44)

where, for example, converter current  $i_{cdq} = i_{cd} + ji_{cq}$ .

The current controller is assumed to be a widely used SRF-PI controller with the decoupling term and feed-forward term. If the delay introduced by the PWM switching is neglected, the output voltage reference obtained from the current controller can be given by

$$v_{cd} = k_{pc} \left( i_{d,ref} - i_{cd} \right) + k_{ic} \gamma_{id} + v_{od} - \omega_e L_c i_{cq}$$

(45)

$$v_{cq} = k_{pc} \left( i_{q,ref} - i_{cq} \right) + k_{ic} \gamma_{iq} + v_{oq} + \omega_e L_c i_{cd} \qquad (46)$$

where  $i_{d,ref}$  and  $i_{q,ref}$  are the d- and q-axis current reference;  $k_{pc}$  and  $k_{ic}$  are the proportional and integral gain of the current controller;  $\gamma_{id} = \int (i_{d,ref} - i_{cd}) dt$  and  $\gamma_{iq} = \int (i_{q,ref} - i_{cq}) dt$  are two auxiliary variables introduced to represent the integral part of the current controller and can be written in the state-space form as

$$\frac{d\gamma_{id}}{dt} = i_{d,ref} - i_{cd} \tag{47}$$

$$\frac{d\gamma_{iq}}{dt} = i_{q,ref} - i_{cq}.$$

(48)

#### B. Small-signal modeling of the system, including RSL

The small-signal model of the system is developed based on the state-space model developed in subsections III-A and IV-A. The system is presented in state-space form through a 12th-order nonlinear model by

$$\frac{dx(t)}{dt} = f(x(t), u(t)) \tag{49}$$

$$y(t) = g(x(t), u(t))$$

(50)

TABLE II

EIGENVALUES AND MAIN PARTICIPATING STATES.

| Oscillation                    | Eigenvalues,                           | Associated                     |

|--------------------------------|----------------------------------------|--------------------------------|

| Mode                           | $\lambda = \sigma \pm j\omega$         | states                         |

| $\lambda_{1,2}, \lambda_{3,4}$ | $-7.85 \pm j4399.1, -7.85 \pm j5027.4$ | $v_{od}, v_{oq}i_{od}, i_{od}$ |

| $\lambda_{5,6}$                | -5000.0, -5000.0                       | $i_{cd}, i_{cq}$               |

| $\lambda_{7,8}$                | -20, -20                               | $\gamma_{id}, \gamma_{iq}$     |

| $\lambda_{9,10}$               | $-175.5 \pm j248.9$                    | $i_{vd}, i_{vq}$               |

| $\lambda_{11}$                 | -123.1                                 | $\theta_e$                     |

| $\lambda_{12}$                 | -426.6                                 | $P_{vf}$                       |

where x(t) and u(t) are the state vector and the input vector, respectively and given by

$$\begin{aligned} x(t) &= [v_{od} \ v_{oq} \ i_{cd} \ i_{cq} \ \gamma_{id} \ \gamma_{iq} \ i_{od} \ i_{oq} \ i_{vd} \ i_{vq} \ \theta_e \ P_{vf}] \\ u(t) &= [i_{d,ref} \ i_{q,ref} \ v_{gd} \ v_{gq} \ \omega_g] \,. \end{aligned}$$

The non-linearity of the model prevents the direct application of classical linear analysis techniques. Therefore, a smallsignal representation is derived for a steady-state operating point as given by

$$\frac{d\tilde{x}}{dt} \simeq A\tilde{x} + B\tilde{u} \tag{51}$$

$$\tilde{y} \simeq C\tilde{x} + D\tilde{u} \tag{52}$$

where, for example,  $A = \Delta_x f$  and  $\Delta_x f$  denotes the Jacobean matrix of f with respect to x. This small-signal model will be used for small-signal analysis and time-domain simulation verification.

## C. Small-signal stability analysis

1) Eigenvalue analysis: The small-signal stability analysis is investigated for the analytical small-signal state-space (ASS) model developed in (51) and the eigenvalues are calculated analytically. The resulting eigenvalues are presented in Table II. The system has 12 eigenvalues, among which 3 pairs are complex conjugates. Further, the participation factor analysis is carried out to identify the contribution of the states and the resulting associated states with the eigenvalues are shown in Table II. The first two pairs of eigenvalues,  $\lambda_{1,2} = -7.85 \pm$  $j4399.1, \lambda_{3,4} = -7.85 \pm j5027.4$  are associated with the state of the filter capacitor voltage and grid current with an oscillation frequency of 700 Hz and 800 Hz, respectively. The eigenvalues associated with the converter inductor current and current controller are a negative real value, thus, the oscillation frequency is zero. Four eigenvalues are related to the RSL from which one pair of the complex conjugate is associated with the current of the virtual inductor. This complex eigenvalue is well damped. The other two eigenvalues associated with the RSL integrator and filter are with negative real value which indicates that the frequency tracking performance will be well damped.

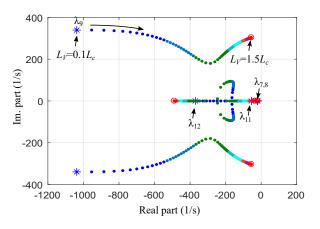

2) Impact of virtual impedance on the stability of the RSL: The performance and stability of the RSL depends on the design of the virtual impedance, therefore, a discussion is presented on the design principles of  $L_v$  and  $R_v$ , by presenting a trajectory of eigenvalue for a change of the virtual inductor. Fig. 7 shows the trajectory of the eigenvalues for a change of

Fig. 7. Trajectory of eigenvalues for a change of grid virtual inductor,  $L_v$  from  $0.10 L_c\,$  to  $1.50 L_c.$

the virtual inductor,  $L_v$ . As presented in Section III.B,  $L_v$  is chosen to be 50% of the inverter series inductor  $L_c$ . Here the trajectory is presented for change  $L_v$  from 10 % to 150 % of  $L_c$ , while  $R_v$  is kept constant. As can be seen, the higher value of  $L_v$ , the eigenvalue,  $\lambda_{9,10}$  associated with the state of virtual current,  $i_v$  is moving towards the right side of the eigenvalue plot. This means a higher value of the virtual inductor, the lower the damping part of the eigenvalue  $\lambda_{9,10}$ . In order to have sufficient damping of the eigenvalue  $\lambda_{9,10}$ , the virtual inductor should be small.  $\lambda_{11}$  and  $\lambda_{12}$  are two real-modes. It is noticed that if the virtual impedance ratio,  $\frac{R_v}{2\pi 50L_v}$  is kept larger than 1,  $\lambda_{11}$  and  $\lambda_{12}$  become oscillatory, on the other hand, the larger is the ratio, the better the damping is. In the design, the virtual impedance ratio,  $\frac{R_v}{2\pi 50L_v}$  is 0.64. It is also worth mentioning that the frequency and phase tracking speed depends on the RSL control-loop bandwidth. To have a fast-tracking speed, the crossover frequency  $\omega_c$  in (40) can be selected higher depending on the inner-loop control bandwidth.

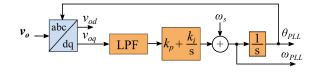

3) A comparison with standard second-order PLL: As the synchronization loop bring instability problem for a weak grid condition, the small-signal analysis is carried out for varying the grid impedance from 0.2 pu to 1.0 pu and the trajectory of the eigenvalues is shown in Fig. 8(a). As can be seen, the eigenvalues associated with the voltage of the filter capacitor, the current of the grid inductor and the current controller are moving towards the right direction, however, they are still in the left half-plane even for 1.0 pu value of the grid inductor, i.e., a very weak grid condition and stay stable. For a comparison with the PLL, a small-signal model of the system with the PLL is developed. The widely-used SRF PLL with a first-order low-pass filter as shown in Fig. 9 is used for comparison. The open-loop transfer function of the PLL can be given by [11]

$$T_{PLL-OL}(s) = \sqrt{2}V_o\left(k_p + \frac{k_i}{s}\right)\frac{1}{s}$$

(53)

and, the closed-loop transfer function of the PLL can be given by

$$T_{PLL-CL}(s) = \frac{2\zeta\omega_n s + \omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(54)

Fig. 8. Trajectory of eigenvalues for a change of grid impedance from 0.2 pu to 1.0 pu: (a) RSL and (b) PLL.

Fig. 9. Standard PLL with a first-order low-pass filter.

where  $\zeta = \frac{k_p}{2} \sqrt{\frac{\sqrt{2}V_o}{k_i}}$  and  $\omega_n = \sqrt{\sqrt{2}V_o k_i}$ . The PLL is tuned such that the open-loop gain has a

sufficient phase margin, i.e., >  $45^{\circ}$  while the bandwidth is sufficient phase margin, i.e., >  $45^{\circ}$  while the bandwidth is sufficient enough to track the phase and frequency, and also rejects the high-frequency noise and operate stably in a weak grid condition. A detailed discussion on tuning the PLL can be found in [31]. The damping factor  $\zeta$  is set to 0.707 to have the maximum flatness on the closed-loop frequency response and  $\omega_n$  is set to achieve desired bandwidth of the PLL. Here,  $\omega_n$  is set such that PLL has the same bandwidth as the RSL.  $\omega_n = 2\pi 6.5$  gives  $k_p = 0.5778$  and  $k_i = 16.68$  for which the open-loop gain has a phase margin of  $65.5^{\circ}$  at 10.1 Hz. Now the bandwidth of the PLL is the same as  $f_c = 10$  Hz design of the RSL, which will be used for comparison. The detailed small-signal state-space modeling of the PLL has not been described due to the page limit, however, it can be found in [32]. The trajectory of the eigenvalues for the same grid

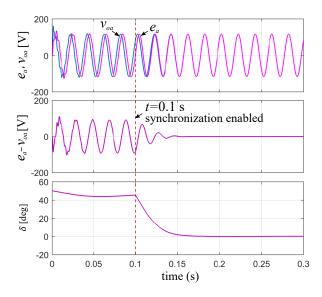

Fig. 10. Phase-A voltage of the PCC  $v_{oa}$  and RSL  $e_a$ , voltage difference,  $v_{err} = e_a - v_{oa}$  and phase difference  $\delta = \theta_e - \theta_o$ : (i) simulation started at t = 0.s, (ii) RSL is activated at t = 0.1 s.

impedance variation is shown in Fig. 8(b). As can be seen, one pair of complex conjugate eigenvalues associated with the current of the grid inductor and the voltage of the filter capacitor moved to the right half-plane when the grid inductor is higher than 0.9 pu. By comparing the two trajectory plots in Fig. 8, the RSL shows a better immune from instability for a very weak grid condition.

# V. VALIDATION OF THE PROPOSED RSL WITH A GRID-CONNECTED CONVERTER

In order to verify the effectiveness of the proposed RSL, simulation and experimental results are presented for a gridconnected converter. The converter is shown in Fig. 1 and the parameters of the system are given in Table I. The dc-side of the converter is connected to a dc source. The widely used standard vector control is adopted to control the converter as presented in IV-A.

#### A. Simulation result

The converter system has been implemented in MAT-LAB/Simulink association with the SimPower block-set with a detailed switching model of the converter and a sampling frequency of 10 kHz. Fig. 10 shows the synchronization process of the RSL with a grid-connected converter. The top plot of Fig. 10 shows the phase-A voltage of the PCC, voa and RSL,  $e_a$ ; the middle plot shows the difference between these two voltages, i.e.,  $v_{err} = e_a - v_{oa}$  and the bottom plot shows the phase difference  $\delta = \theta_e - \theta_o$  of these two voltages. As shown in Fig. 10, it has a phase difference between the RSL and PCC voltage is around  $42^{\circ}$  and a voltage difference with a peak value of around 90V. The simulation is started at t = 0 s and the tracking-loop of the RSL is activated at t = 0.1 s to start the synchronization. Within a few cycles, the RSL voltage is synchronized with the grid. The RSL is able to track the phase of the grid voltage and the phase difference

Fig. 11. Simulation result: (a) three-phase voltage,  $v_o$  and output current  $i_o$  and (b) the d- and q-axis voltage and current of the converter.

$\delta$  becomes zero. Since the RSL tracks the phase of the grid voltage, the PWM of the converter can be enabled at any time to turn on the converter for grid connection.

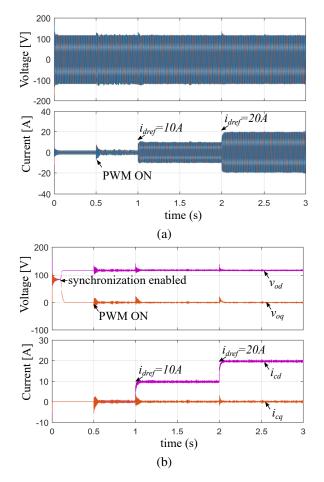

Fig. 11 shows the complete simulation of the grid-connected converter. The simulation is started at t = 0 s. The first 0.3 s of the simulation is presented in Fig. 10 where the tracking-loop of the RSL is activated at t = 0.1 s. The PWM of the converter is enabled at t = 0.5 s after the synchronization is achieved. Since the synchronization is achieved, the grid connection is very smooth and there is no transient over-current.

Fig. 11(a) shows the three-phase instantaneous voltages and currents. Initially, the current reference is set to zero, i.e.,  $i_{d,ref} = i_{q,ref} = 0$  A. At t = 1 s, the d-axis current reference is to 10 A. The current controller follows the reference smoothly. At t = 2 s, another current step is applied. The controller quickly catches the reference and the system operates smoothly as expected. Fig. 11(b) shows the d- and q-axis voltage and current of the converter. As can be seen, before enabling the RSL, the d- and q-axis voltage are not a pure dc component, however, when the RSL is enabled to perform synchronization, the d- and q-axis voltage becomes dc components where the d-axis voltage has a magnitude with a peak value of the voltage and the magnitude of the q-axis voltage is zero as it is set  $e_q = 0$  in (21). The d- and q-axis current components are also pure dc components as expected.

Fig. 12. Performance comparison for three different crossover frequencies.

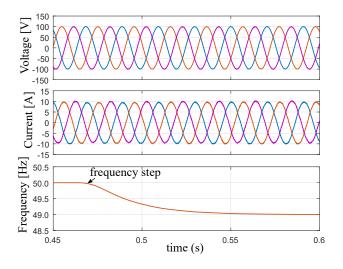

Fig. 13. Simulation result for a step change of frequency: (i) three-phase instantaneous voltage,  $v_o$ , (ii) converter current  $i_c$  and (iii) frequency of the RSL.

1) Impact of the control-loop bandwidth : As presented in section III-B,  $k_p$  in (40) is calculated for three crossover frequencies and the step responses of the closed-loop system is presented in Fig. 6 for these three designs. In order to further verify these responses, simulation results are presented in Fig. 12. As can be seen, the simulation results have the same response to the change of the *d*-axis current reference from 0.90 pu to 0.95 pu as the step responses shown in Fig. 6. The 30Hz and 20Hz designs have under-damped responses, and the 10Hz design gives over-damped response. Both 20Hz and 10Hz design are a good choice, however, only 10Hz design is used for the simulation and experimental results presented below.

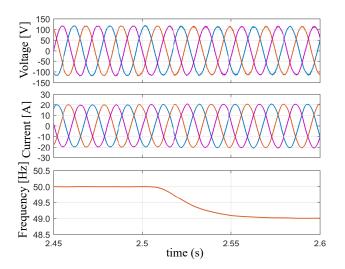

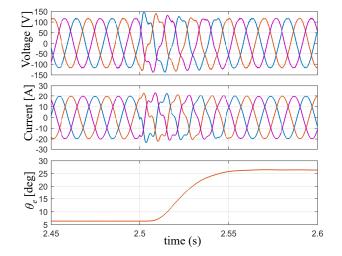

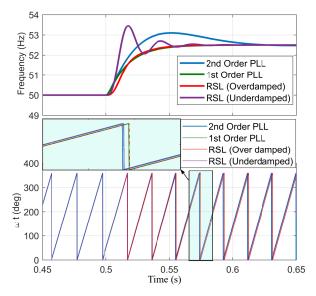

2) Frequency and Phase Jump: The frequency tracking performance is tested by changing the frequency of the grid voltage and the simulation result is shown in Fig. 13. The bottom plot of Fig. 13 shows the RSL frequency. The

Fig. 14. A 20° phase jump of the grid voltage.

Fig. 15. Unbalanced and distorted grid voltage.

frequency of the grid voltage is reduced to 49 Hz at 2.5 s. As can be seen, the RSL follows the grid frequency. The frequency tracking performance is very fast and robust without any low/high frequency oscillation and overshoot. The instantaneous voltages and currents of the converter are also shown in Fig. 13. During the frequency change, the converter follows the reference current of the controller without any harmful transient.

The performance of the RSL has been tested for a phase jump of the grid voltage and the simulation result is shown in Fig. 14. A phase jump of  $20^{\circ}$  is applied in the grid voltage at 2.5 s. As can be seen in Fig. 14, RSL tracks the phase jump within two cycles and follow the grid voltage. Initially, the phase of the PCC voltage is  $6.3^{\circ}$ . When the phase drift occurs, the phase becomes  $26.3^{\circ}$  within two cycles i.e.,  $20^{\circ}$  increased.

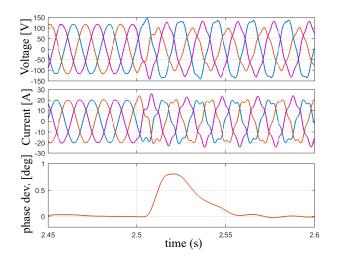

3) Unbalanced and distorted Grid Voltage: The next simulation is carried out for an unbalance and distorted grid voltage. The unbalanced and distorted grid voltage is created by injecting a 20% of negative sequence component at the fundamental frequency and a 5% 5th harmonic positive sequence

Fig. 16. 50% symmetrical voltage sag.

Fig. 17. Comparison with PLL for a step change of the converter current.

component. The instantaneous value of the voltages, currents and phase deviation are shown in Fig. 15. The transient phase error is around  $0.8^{\circ}$ , which eventually becomes zero in steady-state. The phase difference is insignificant and does not have any significant impact on the steady-state operation of the converter.

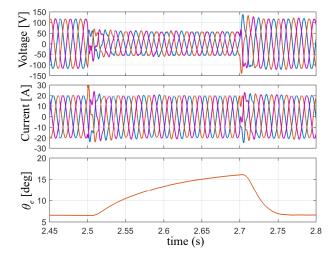

4) Voltage Sag: The performance of the RSL has been tested for symmetrical voltage sag and the simulation result is shown in Fig. 16. A 50% symmetrical grid voltage sag is applied at 2.5 s. The instantaneous value of the voltages, currents and phase are shown in Fig. 16. As can be seen, the phase of the voltage is increasing during the voltage sag. When the grid fault is cleared at 2.7 s, the phase returns to it's prefault value within two cycles. RSL has not lost synchronization during this large disturbance.

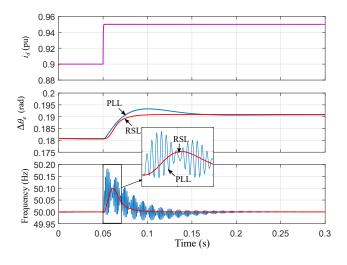

## B. Performance comparison with PLL

The performance of the RSL has been compared with a PLL as shown in Fig. 17. Here an average model of the converter is used so visualize the comparison by removing the high-

Fig. 18. Performance of the PLL under input frequency deviation from the fundamental frequency.

frequency oscillation caused by the PWM switching. As shown in the top plot of Fig. 17, the initial d-axis current is 0.90 pu. At 0.05 s, the d-axis current reference is set to 0.95 pu and the current of the converter immediately follows the reference. The middle plot shows the phase difference between the voltages of the grid and PCC. The initial phase difference for 0.90 pu current is 0.1808 rad, while it is 0.1909 rad for 0.95 pu of current. The phase tracking response of the RSL is well damped while it is under-damped with a small-overshoot for the PLL. If the phase margin of the loop is reduced, then it becomes under-damped with oscillatory behavior for the PLL, while it is well-damped for the RSL. The bottom plot of Fig. 17 shows the frequency obtained from the RSL and PLL. A first-order low pass filter with a cut-off frequency 500-rad/s is used with both the RSL and PLL. As can be seen, the frequency tracking performance of the RSL is smooth, while the PLL frequency has oscillation with frequency of 700 Hz ( $\approx 4399$  rad/s) and 800 Hz ( $\approx 5027$  rad/s). By looking at the eigenvalues in Table II, these two frequencies corresponding to the states of the grid impedance current and the filter capacitor voltages, which are reflecting on the PLL frequency while the proposed RSL effectively suppresses those oscillations.

The performance of the RSL has been investigated for the scenario when the input frequency deviated from the fundamental frequency and the results have been compared with first-order and second-order PLL as shown in Fig. 18. The results have been presented for two designs of the RSL, i.e., (i) under-damped ( $f_c = 10$  Hz) and (ii) over-damped ( $f_c = 30$ Hz) response of the RSL. As can be seen, phase  $\omega t$  is the same as the first-order PLL when the RSL response is designed to be over-damped. However, phase  $\omega t$  is the same as the secondorder PLL for the under-damped response of the RSL. These phase differences do not have any significant impact on the converter operation.

As shown in Fig. 8, the PLL is more prone to instability in

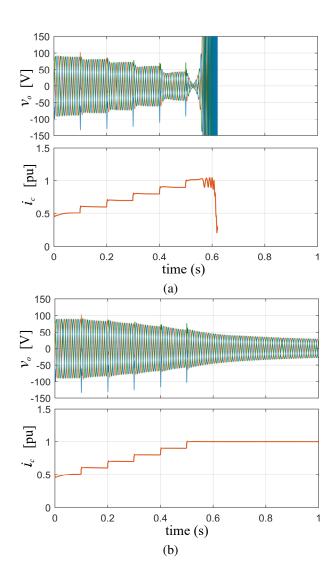

Fig. 19. Comparison with PLL in a weak grid condition: (a) PLL performance and (b) RSL performance.

weak grid condition than RSL. A simulation is carried out to see the performance as it is noticed in the eigenvalue analysis. The grid impedance is set to 1 pu. The simulation results are shown in Fig. 19. The current reference is set to 0.5 pu initially which has been increased to 1 pu with a step of 0.1 pu as shown in Fig. 19. As can be seen, the system becomes unstable with PLL synchronization, while it is stable with RSL and the voltage magnitude is reduced significantly as there is no voltage support function implemented in the control.

The voltage magnitude dependency on the control-loop frequency response is the root cause of instability for the PLL under a weak grid (high impedance) condition [33]. From the PLL transfer function in (53) and (54), it can be noted that the magnitude of input voltage has a significant influence on synchronization-loop stability. The PLL will always be stable under a strong grid as the PCC voltage is unaffected by the power injected by the converter. However, the PCC voltage will change a lot with the variation of injected power under a weak grid condition, which causes the instability with the PLL synchronized converter. The transfer functions of the

Fig. 20. Experimental setup used in this work.

Fig. 21. Experimental result for a step change of current reference: (i) threephase instantaneous voltage,  $v_o$ , (ii) converter current  $i_c$ , (iii) d- and q-axis current of the converter and (iv) frequency of the RSL.

RSL in (38) and (41) show that the stability of the controlloop depends on the  $R_v$  and  $L_v$  rather than the PCC voltage magnitude. The PCC voltage magnitude influences the gain of the RSL transfer function. Therefore, the RSL shows a better immune from instability for a weak grid condition.

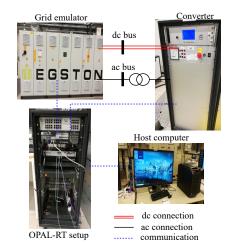

## C. Experimental result

In order to further verify the effectiveness of the proposed RSL, experiments have been conducted for the system presented in the simulation. The parameters of the experiment are

Fig. 22. Experimental result for a step change of frequency.

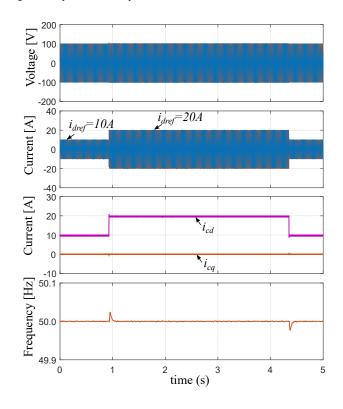

the same as the simulation given in Table I. Fig. 20 shows a picture of the experimental setup. A two-level converter is used in the experiment. Both the ac-side and dc-side are connected to a grid emulator. The current controller of the converter is implemented in the local FFGA-core in the converter and RSL is implemented in the OPAL-RT system. The converter and the grid emulator are controlled by OPAL-RT and they are connected by optical fiber communication. Two experimental results are presented here. Fig. 21 shows the three-phase instantaneous voltages and currents, the d- and q-axis current and the frequency of the RSL. After the synchronization is achieved, the PWM of the converter is turned on and the d-axis current reference is set to 10 A. A current step is applied and the controller follows the current reference. The RSL works satisfactorily.

The frequency tracking performance is also tested in the experiment by changing the frequency of the grid voltage and the experimental result is shown in Fig. 22. The frequency of the grid voltage is reduced to 49 Hz. As can be seen, the RSL follows the grid frequency. It shows that RSL follows the frequency of the grid in 3 cycles. The frequency tracking performance is very fast and robust without any low/high frequency oscillation and overshoot.

#### VI. CONCLUSION

This paper presents a new phase-tracking robustsynchronization-loop for the grid-connected DG converters. Analytical modeling, as well as a method for tuning the parameters, is presented. A small-signal stability analysis is presented and it is shown that the eigenvalues associated with the RSL always stay in the left half-plane, which indicates that the RSL will always be stable itself. The performance of the RSL has also been compared with widely used PLL and the RSL shows a better immune than a PLL from instability for a very weak grid condition. Simulation and experimental results are provided to show the effectiveness of the proposed method in tacking the phase and frequency of the grid. The result shows that the proposed method effectively tracks the phase and frequency of the grid voltage and maintains the synchronism of the converters during different disturbances.

## ACKNOWLEDGMENTS

The author would like to thank Dr. Salvatore D'Arco from SINTEF Energy Research, Norway for supporting in the experimental work.

#### REFERENCES

- F. Blaabjerg, M. Liserre, and K. Ma, "Power electronics converters for wind turbine systems," IEEE Trans. Ind. Appl., vol. 48, no. 2, pp. 708–719, March 2012.

- [2] F. Katiraei and J. R. Aguero, "Solar pv integration challenges," IEEE Power Energy Mag., vol. 9, no. 3, pp. 62–71, May 2011.

- [3] Q.-C. Zhong, "Power-electronics-enabled autonomous power systems: Architecture and technical routes," IEEE Transactions on Industrial Electronics, vol. 64, no. 7, pp. 5907–5918, 2017.

- [4] X. Li, H. Zhang, M. B. Shadmand, and R. S. Balog, "Model predictive control of a voltage-source inverter with seamless transition between islanded and grid-connected operations," IEEE Trans. Ind. Electron., vol. 64, no. 10, pp. 7906–7918, Oct 2017.

- [5] F. Freijedo, J. Doval-Gandoy, O. Lopez, P. Fernandez-Comesana, and C. Martinez-Penalver, "A signal-processing adaptive algorithm for selective current harmonic cancellation in active power filters," IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 2829–2840, Aug. 2009.

- [6] H. Ye, J. Wang, Y. Ge, J. Li, and Z. Li, "Robust integration of highlevel dispatchable renewables in power system operation," IEEE Trans. Sustain. Energy, vol. 8, no. 2, pp. 826–835, April 2017.

- [7] S. Zhao, F. Blaabjerg, and H. Wang, "An overview of artificial intelligence applications for power electronics," IEEE Trans. Power Electron., vol. 36, no. 4, pp. 4633–4658, 2021.

- [8] C. da Silva, R. Pereira, L. da Silva, G. Lambert-Torres, B. Bose, and S. Ahn, "A digital PLL scheme for three-phase system using modified synchronous reference frame," IEEE Trans. Ind. Electron., vol. 57, no. 11, pp. 3814–3821, Nov. 2010.

- [9] I. Carugati, P. Donato, S. Maestri, D. Carrica, and M. Benedetti, "Frequency adaptive PLL for polluted single-phase grids," IEEE Trans. Power Electron., vol. 27, no. 5, pp. 2396–2404, May 2012.

- [10] D. Jovcic, "Phase locked loop system for FACTS," IEEE Trans. Power Syst., vol. 18, no. 3, pp. 1116–1124, Aug. 2003.

- [11] S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Three-phase plls: A review of recent advances," IEEE Trans. Power Electron., vol. 32, no. 3, pp. 1894–1907, 2017.

- [12] H. de Bellescize, La réception synchrone. E. Chiron, 1932.

- [13] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: Performance analysis and design guidelines," IEEE Trans. Power Electron., vol. 29, no. 6, pp. 2750–2763, 2014.

- [14] P. Xiao, K. A. Corzine, and G. K. Venayagamoorthy, "Multiple reference frame-based control of three-phase pwm boost rectifiers under unbalanced and distorted input conditions," IEEE Trans. Power Electron., vol. 23, no. 4, pp. 2006–2017, 2008.

- [15] S. Golestan, M. Ramezani, J. M. Guerrero, and M. Monfared, "dq-frame cascaded delayed signal cancellation- based pll: Analysis, design, and comparison with moving average filter-based pll," IEEE Trans. Power Electron., vol. 30, no. 3, pp. 1618–1632, 2015.

- [16] P. Kanjiya, V. Khadkikar, and M. S. El Moursi, "Adaptive low-pass filter based dc offset removal technique for three-phase plls," IEEE Trans. Ind. Electron., vol. 65, no. 11, pp. 9025–9029, 2018.

- [17] Y. Li, D. Wang, W. Han, S. Tan, and X. Guo, "Performance improvement of quasi-type-1 pll by using a complex notch filter," IEEE Access, vol. 4, pp. 6272–6282, 2016.

- [18] B. Wen, D. Dong, D. Boroyevich, R. Burgos, P. Mattavelli, and Z. Shen, "Impedance-based analysis of grid-synchronization stability for threephase paralleled converters," IEEE Trans. Power Electron., vol. 31, no. 1, pp. 26–38, Jan 2016.

- [19] D. Dong, B. Wen, D. Boroyevich, P. Mattavelli, and Y. Xue, "Analysis of phase-locked loop low-frequency stability in three-phase grid-connected power converters considering impedance interactions," IEEE Trans. Ind. Electron., vol. 62, no. 1, pp. 310–321, Jan. 2015.

- [20] J. Rocabert, G. M. S. Azevedo, A. Luna, J. M. Guerrero, J. I. Candela, and P. Rodröčæguez, "Intelligent connection agent for three-phase gridconnected microgrids," IEEE Trans. Power Electron., vol. 26, no. 10, pp. 2993–3005, Oct 2011.

- [21] S. Golestan, J. M. Guerrero, J. C. Vasquez, A. M. Abusorrah, and Y. Al-Turki, "A study on three-phase fils," IEEE Trans. Power Electron., vol. 34, no. 1, pp. 213–224, 2019.

- [22] A. J. Wang, B. Y. Ma, and C. X. Meng, "A frequency-locked loop technology of three-phase grid-connected inverter based on improved reduced order generalized integrator," in in Proc. IEEE 10th Conf. Ind. Electron. Appl., 2015, pp. 730–735.

- [23] W. Li, X. Ruan, C. Bao, D. Pan, and X. Wang, "Grid synchronization systems of three-phase grid-connected power converters: A complexvector-filter perspective," IEEE Trans. Ind. Electron., vol. 61, no. 4, pp. 1855–1870, 2014.

- [24] S. Golestan, J. M. Guerrero, F. Musavi, and J. C. Vasquez, "Singlephase frequency-locked loops: A comprehensive review," IEEE Trans. Power Electron., vol. 34, no. 12, pp. 11791–11812, 2019.

- [25] W. Zhang, A. M. Cantarellas, J. Rocabert, A. Luna, and P. Rodriguez, "Synchronous power controller with flexible droop characteristics for renewable power generation systems," IEEE Trans. Sustain. Energy, vol. 7, no. 4, pp. 1572–1582, Oct 2016.

- [26] O. Mo, S. D'Arco, and J. A. Suul, "Evaluation of virtual synchronous machines with dynamic or quasi-stationary machine models," IEEE Trans. Ind. Electron., vol. 64, no. 7, pp. 5952–5962, July 2017.

- [27] L. Zhang, L. Harnefors, and H.-P. Nee, "Power-synchronization control of grid-connected voltage-source converters," IEEE Trans. Power Syst., vol. 25, no. 2, pp. 809–820, May 2010.

- [28] Q.-C. Zhong, P.-L. Nguyen, Z. Ma, and W. Sheng, "Self-synchronised synchronverters: Inverters without a dedicated synchronisation unit," IEEE Trans. Power Electron., vol. 29, no. 2, pp. 617–630, Feb. 2014.

- [29] Q.-C. Zhong, W. L. Ming, and Y. Zeng, "Self-synchronized universal droop controller," IEEE Access, vol. 4, pp. 7145–7153, Oct. 2016.

- [30] M. Amin, "A robust-synchronization-loop for grid-connected distributed generation converters," in IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, 2020, pp. 3648–3653.

- [31] F. D. Freijedo, J. Doval-Gandoy, O. Lopez, and E. Acha, "Tuning of phase-locked loops for power converters under distorted utility conditions," vol. 45, no. 6, pp. 2039–2047, 2009.

- [32] M. Amin, J. A. Suul, S. D'Arco, E. Tedeschi, and M. Molinas, "Impact of state-space modelling fidelity on the small-signal dynamics of VSC-HVDC systems," in 11th IET International Conference on AC and DC Power Transmission, Feb 2015, pp. 1–11.

- [33] C. Wu, X. Xiong, M. G. Taul, and F. Blaabjerg, "Enhancing transient stability of pll-synchronized converters by introducing voltage normalization control," IEEE J. Emerg. Sel. Topics Circuits Syst., vol. 11, no. 1, pp. 69–78, 2021.

**Mohammad Amin (M'11-SM'20)** received the B.Sc. degree in electrical and electronic engineering from Chittagong University of Engineering and Technology, Bangladesh, in 2008, the M.Sc. degree in electric power engineering from Chalmers University of Technology, Sweden, in 2011 and the Ph.D. degree in engineering cybernetics from Norwegian University of Science and Technology, Norway, in 2017.

From 2008 to 2013, he was with the Department of Electrical and Electronic Engineering, Interna-

tional Islamic University Chittagong, Bangladesh. In 2015, he was a Ph.D. Visiting Scholar with the Wind Power Research Center, Shanghai Jiao Tong University, Shanghai, China. From 2017 to 2019, he was a Senior Research Associate with the Department of Electrical and Computer Engineering, Illinois Institute of Technology, Chicago, IL, USA. Currently, Dr. Amin is an Associate Professor with the Department of Electric Power Engineering at Norwegian University of Science and Technology. He is the recepient of the 2018 IEEE JESTPE First Prize Paper Award from IEEE Power Electronics Society and The 2020 Premium Award for best paper in IET Generation, Transmission & Distributio. His research interest include on power electronics application to power system, application of artificial intelligence in power electronics system, robust integration of wind and solar energy, high voltage direct current (HVDC) transmission, microgrid, smart grids, and robust control theory for power electronics system.