Erling Rennemo Jellum David Christoph Metz

# Evaluating FIFO-based Instruction Scheduling Techniques using FPGAs

Master's thesis in MTTK Supervisor: Magnus Själander, Sverre Hendseth June 2020

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

Master's thesis

Erling Rennemo Jellum David Christoph Metz

# Evaluating FIFO-based Instruction Scheduling Techniques using FPGAs

Master's thesis in MTTK Supervisor: Magnus Själander, Sverre Hendseth June 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

# Contents

| Co  | ontents                                           | <br>i    |

|-----|---------------------------------------------------|----------|

| Lis | st of Figures                                     | <br>v    |

| Lis | st of Tables                                      | <br>vi   |

| Ac  | cknowledgments                                    | <br>vii  |

| Ab  | bstract                                           | <br>viii |

| 1   | Introduction                                      | <br>1    |

|     |                                                   |          |

| Ι   | Iterative Backwards Dependency Analysis           | 3        |

| 2   | Background                                        | <br>4    |

|     | 2.1 Program Slices                                | 4        |

|     | 2.2 Dependency Analysis                           |          |

|     | 2.3 Hashing                                       |          |

|     | 2.3.1 Entropy                                     | <br>5    |

|     | 2.4 Memories                                      |          |

|     | 2.5 Caches                                        | <br>7    |

|     | 2.6 Iterative Backwards Dependency Analysis       | <br>8    |

| 3   | IBDA implementations                              | 10       |

|     | 3.1 Perfect IBDA                                  | <br>10   |

|     | 3.2 Original IBDA                                 | <br>10   |

|     | 3.2.1 RDT                                         | <br>10   |

|     | 3.2.2 IST                                         | <br>11   |

|     | 3.3 Single Write IBDA                             | <br>11   |

|     | 3.4 Fuzzy IBDA                                    | <br>12   |

|     | 3.4.1 Hash Functions                              | <br>15   |

|     | 3.4.2 Naive Hash                                  | <br>15   |

|     | 3.4.3 Random Binary Matrix Hash                   | <br>15   |

|     | 3.5 Bloom IBDA                                    | <br>17   |

| 4   | Methodology                                       | <br>21   |

|     | 4.1 Spike                                         | <br>21   |

|     | 4.1.1 Pseudo Entropy                              | <br>21   |

|     | 4.2 Load Slice Core                               | <br>22   |

|     | 4.3 FPGA-based Application Performance Evaluation | <br>22   |

|     | 4.4 FPGA-based Area Analysis                      |          |

|   | 4.5 | IBDA Parameters                                 |

|---|-----|-------------------------------------------------|

| 5 |     | lts & Discussion                                |

|   | 5.1 | Application Performance                         |

|   | 5.2 | Implementation Sizes                            |

|   |     | 5.2.1 Single Write IBDA                         |

|   |     | 5.2.2 Going Fuzzy                               |

|   |     | 5.2.3 Bloom IBDA                                |

|   | 5.3 | Precise IBDA                                    |

|   |     | 5.3.1 Address Space Switches                    |

|   |     | 5.3.2 Speculative Execution                     |

|   |     | 5.3.3 Moving the RDT                            |

| 6 | Con | lusion                                          |

|   |     |                                                 |

|   |     | O have d Instruction O had align                |

| Π |     | O-based Instruction Scheduling 31               |

| 7 |     | ground                                          |

|   | 7.1 | Instruction Scheduling                          |

|   |     | 7.1.1 In-Order Scheduling                       |

|   |     | 7.1.2 Out-of-Order Scheduling                   |

|   | 7.2 | Computer Architecture Research Tools            |

|   |     | 7.2.1 Architectural Simulators                  |

|   |     | 7.2.2 RISC-V Instruction Set Architecture       |

|   |     | 7.2.3 Chisel                                    |

|   |     | 7.2.4 The Berkeley Out-of-Order Machine    36   |

|   |     | 7.2.5 Rocket                                    |

|   |     | 7.2.6         Chipyard SoC Generator         38 |

|   | 7.3 | Novel Scheduling Techniques                     |

|   |     | 7.3.1 Load Slice Core                           |

|   |     | 7.3.2 Delay and Bypass         39               |

|   |     | 7.3.3 CASINO                                    |

| 8 |     | ementation                                      |

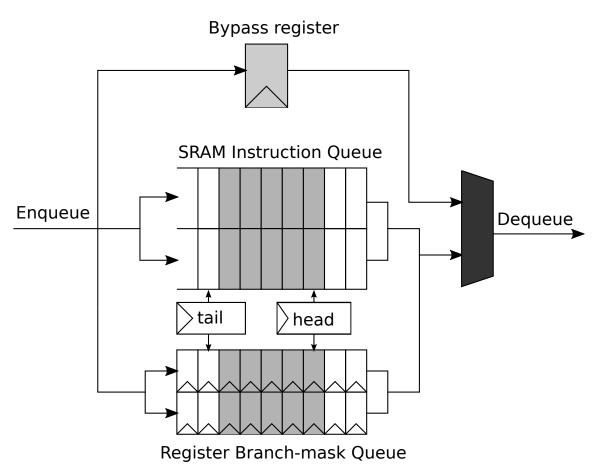

|   | 8.1 | Cheap Queue         42                          |

|   |     | 8.1.1 Shifting Register Based Queue             |

|   |     | 8.1.2 Single SRAM Queue                         |

|   |     | 8.1.3 Multi SRAM Queue                          |

|   |     | 8.1.4 Head Registers                            |

|   | 8.2 | Berkeley Out-of-Order Machine    45             |

|   |     | 8.2.1 Issue Unit                                |

|   | 8.3 | In-Order BOOM                                   |

|   |     | 8.3.1 Unified Dual-Issue                        |

|    |      | 8.3.2 Queue based In-Order                | 49 |

|----|------|-------------------------------------------|----|

|    | 8.4  | Load Slice Core                           | 50 |

|    |      | 8.4.1 Dispatcher                          | 50 |

|    |      | 8.4.2 Issue Unit                          | 52 |

|    | 8.5  | Delay and Bypass                          | 52 |

|    |      | 8.5.1 Dispatcher                          | 52 |

|    |      | 8.5.2 Issue Unit                          | 52 |

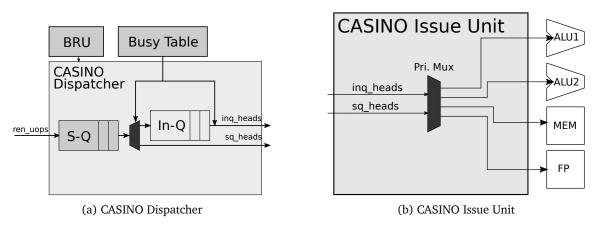

|    | 8.6  | CASINO                                    | 53 |

|    |      | 8.6.1 Dispatcher                          | 53 |

|    |      | 8.6.2 Issue Unit                          | 55 |

| 9  | Met  | hodology                                  | 56 |

|    | 9.1  | Size & Power Evaluation                   | 56 |

|    |      | 9.1.1 FPGA Resources                      | 56 |

|    |      | 9.1.2 Synthesis Flow                      | 56 |

|    |      | 9.1.3 Vivado Power Estimation             | 57 |

|    | 9.2  | Application Performance Evaluation        | 59 |

|    |      | 9.2.1 Target Hardware                     | 59 |

|    |      | 9.2.2 System-on-Chip                      | 59 |

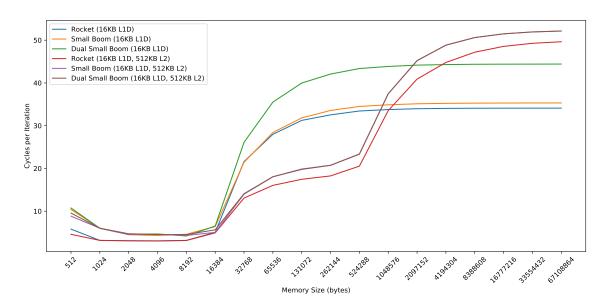

|    |      | 9.2.3 Memory Subsystem Analysis           | 59 |

|    |      | 9.2.4 Performance Counters                | 61 |

|    |      | 9.2.5 Proxy Kernel                        | 62 |

|    |      | 9.2.6 Linux                               | 62 |

|    |      | 9.2.7 SPEC 2006                           | 64 |

|    | 9.3  | Core Configuration Parameters             | 66 |

| 10 | Resu | ults                                      | 68 |

|    | 10.1 | Size Overhead from BOOM                   | 68 |

|    |      | 10.1.1 Configuration                      | 68 |

|    |      | 10.1.2 Sizes                              | 69 |

|    |      | 10.1.3 Summary                            | 73 |

|    | 10.2 | Queue Sizes                               | 73 |

|    | 10.3 | Core Sizes                                | 74 |

|    |      | 10.3.1 LUTs and Flip-Flops                | 74 |

|    |      | 10.3.2 Memories                           | 76 |

|    | 10.4 | Critical Path                             | 76 |

|    | 10.5 | Application Performance                   | 79 |

| 11 | Disc | sussion                                   | 81 |

|    | 11.1 | Implementing Instruction Queues in Chisel | 81 |

|    |      |                                           | 81 |

|    |      | 11.2.1 Overheads of InO Implementation    | 81 |

|    |      | 11.2.2 LSC                                | 82 |

| 11.2.3 DnB                                   | 82 |

|----------------------------------------------|----|

| 11.2.4 CASINO                                | 83 |

| 11.3 Energy and Area-normalized Performance  | 84 |

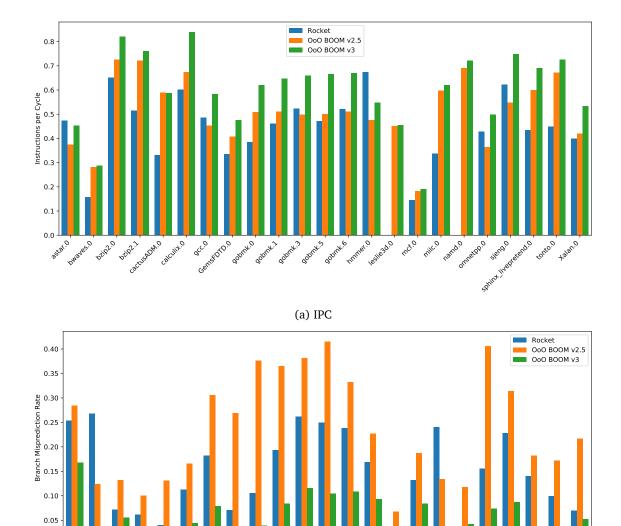

| 11.4 Release of BOOM v3                      | 85 |

| <b>12 Future Work</b>                        | 86 |

| <b>13 Conclusion</b>                         | 87 |

| Bibliography                                 | 88 |

| A Manual: Running RISC-V SoCs on a Zynq FPGA | 95 |

| A.1 Installation                             | 95 |

| A.1.1 Vivado                                 | 95 |

| A.1.2 Chipyard                               | 96 |

| A.1.3 Fpga-zynq                              | 96 |

| A.1.4 Zynq Board                             | 97 |

| A.2 Running Applications                     | 99 |

# List of Figures

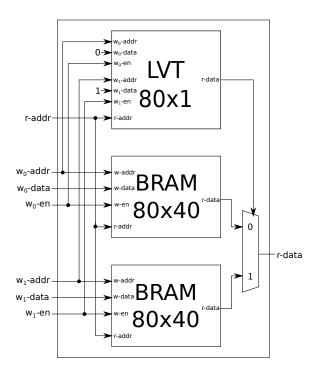

| 1  | Memory with two write ports and one read ports using LVT                            | 6  |

|----|-------------------------------------------------------------------------------------|----|

| 2  | IBDA embedded in the Load Slice Core. Adapted from [1]                              | 9  |

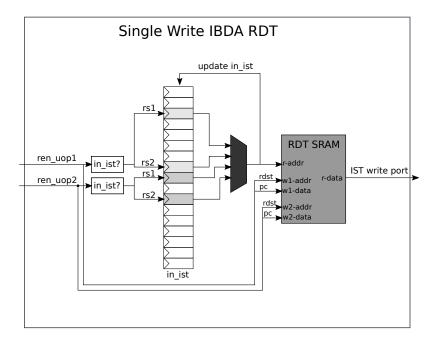

| 3  | Single Write IBDA RDT with one write port to the IST                                | 12 |

| 5  | Average pseudo-entropy for each PC-bit running SPEC CPU2006                         | 14 |

| 6  | Load slice extraction normalized to Perfect IBDA for Original IBDA and Fully Asso-  |    |

|    | ciative implementation running SPEC CPU2006                                         | 15 |

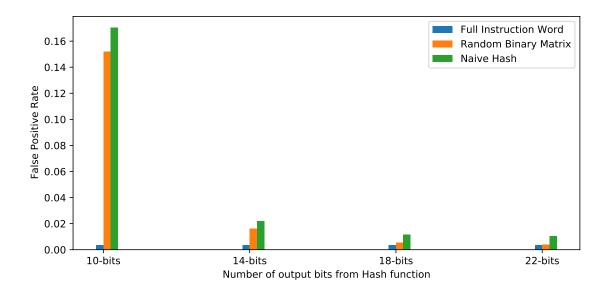

| 7  | Average false positive rate for Fuzzy IBDA running SPEC CPU2006 with different      |    |

|    | hash functions                                                                      | 16 |

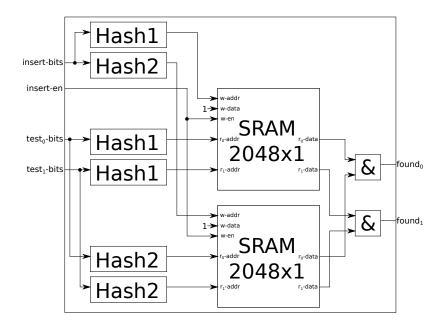

| 8  | Partitioned Bloom filter with one insert and two membership test ports. Flush logic |    |

|    | not shown.                                                                          | 17 |

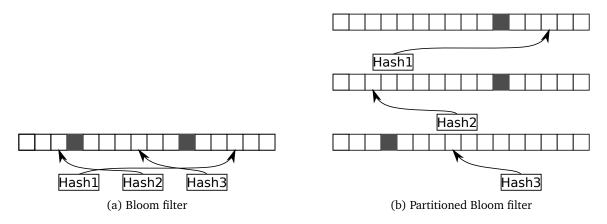

| 9  | Comparing a conventional Bloom filter to a Partitioned Bloom filter                 | 18 |

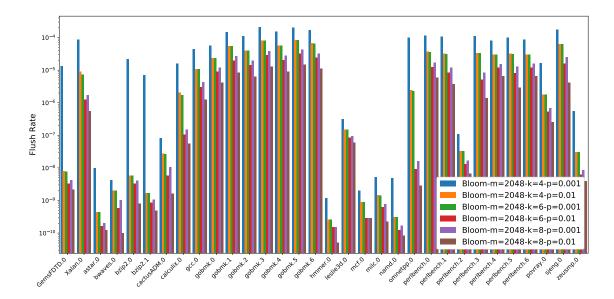

| 10 | Flush rate for different implementations of Bloom IBDA running SPEC CPU2006         | 19 |

| 11 | Comparing load slice extraction normalized to Perfect IBDA for Fuzzy, Baseline and  |    |

|    | Single Write IBDA running SPEC CPU2006                                              | 20 |

| 12 | Performance of the Load Slice Core using different IBDA implementations running     |    |

|    | SPEC CPU2006                                                                        | 25 |

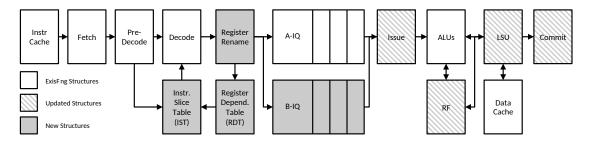

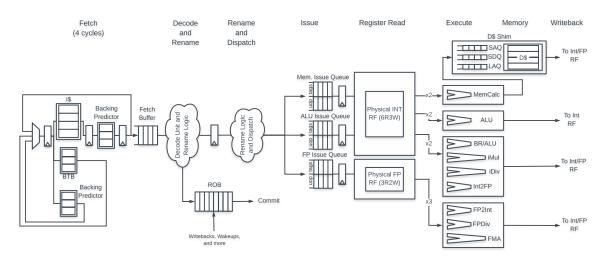

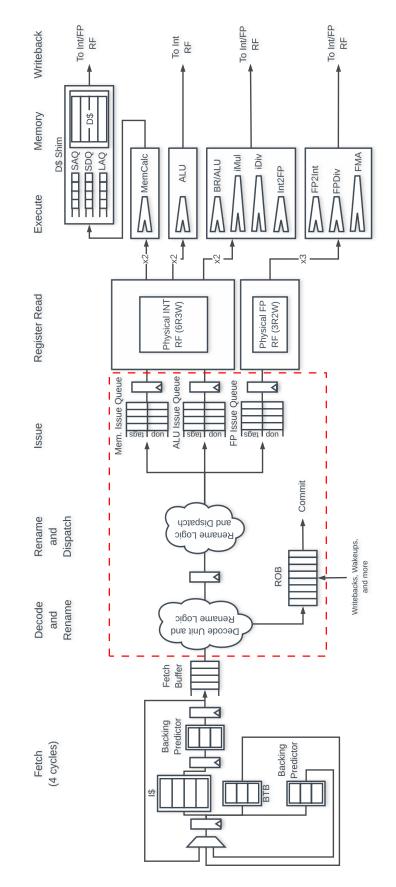

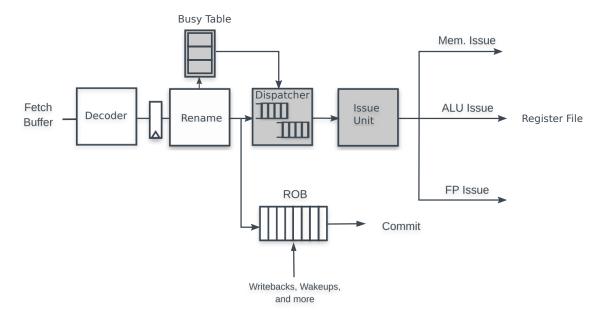

| 13 | A high-level view of BOOMs pipeline. Adapted from [2]                               | 36 |

| 14 | Overview of the Multi SRAM-Based Queue                                              | 44 |

| 15 | BOOM pipeline with area of interest marked in red. Adapted from the RISCV-BOOM      |    |

|    | documentation [2]                                                                   | 46 |

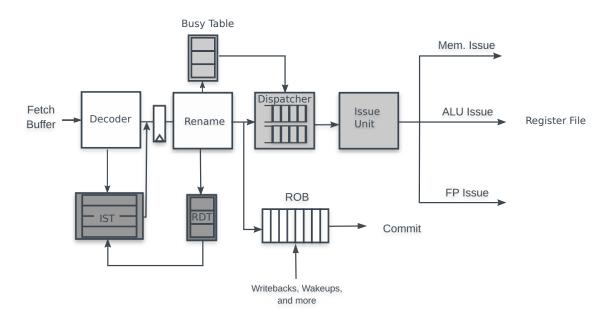

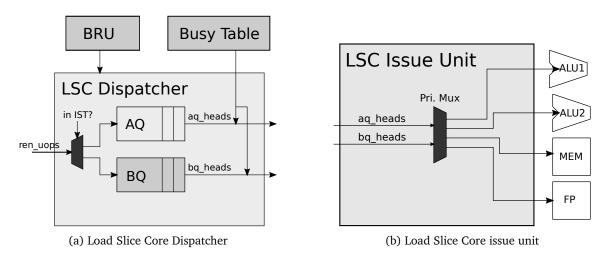

| 16 | High-level view of Load Slice Core and Delay and Bypass instruction scheduling      | 50 |

| 17 | Load Slice Core instruction scheduling                                              | 51 |

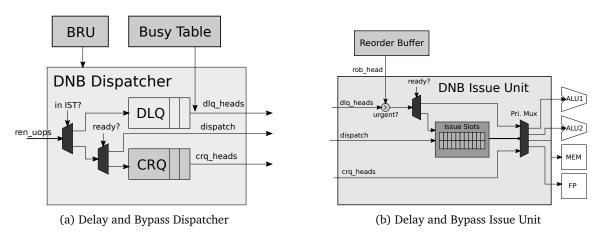

| 18 | Delay and Bypass instruction scheduling                                             | 53 |

| 19 | High-level view of CASINO instruction scheduling                                    | 54 |

| 20 | CASINO instruction scheduling                                                       | 54 |

| 21 | Memory hierarchy latency of Rocket and BOOM for different working set sizes         | 60 |

| 22 | Performance comparison of BOOM v2.5, BOOM v3 and Rocket cores                       | 63 |

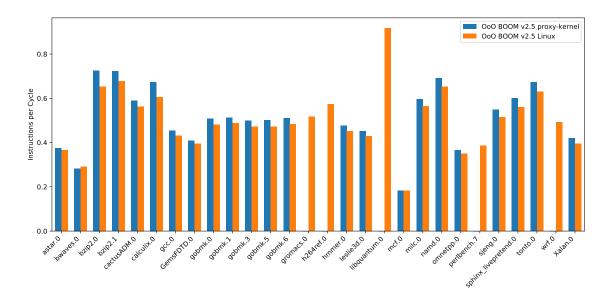

| 23 | Performance of BOOM v2.5 running SPEC CPU2006 using Linux and RISC-V Proxy          |    |

|    | Kernel                                                                              | 64 |

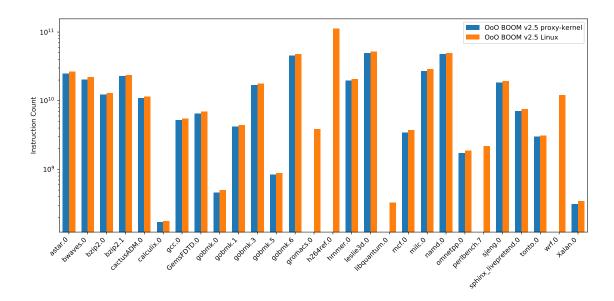

| 24 | Instruction count for BOOM v2.5 running SPEC CPU2006 using RISC-V Proxy Kernel      |    |

|    | and Linux                                                                           | 65 |

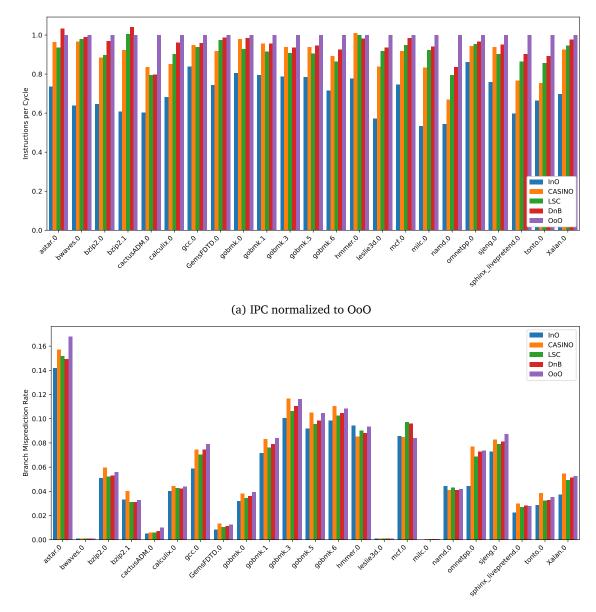

| 25 | Performance comparison of the different cores excluding fesvr call cycles           | 80 |

# List of Tables

| 1  | IBDA parameters                                                                        | 23 |

|----|----------------------------------------------------------------------------------------|----|

| 2  | LUTs (left) and flip-flops (right) for different IBDA implementations                  | 26 |

| 3  | LUTRAM usage (left) and BRAM usage (right) for different IBDA implementations          | 26 |

| 4  | Unrealistic power utilization estimation of dual-issue stall-on-use BOOM (InO), CASINO | ,  |

|    | Load Slice Core (LSC), Delay and Bypas (DnB), 2-wide BOOM (OoO) in W.                  | 58 |

| 5  | Single issue in-order BOOM (SInO) and Rocket configuration parameters                  | 66 |

| 6  | Configuration parameters for dual-issue stall-on-use BOOM (InO), CASINO, Load          |    |

|    | Slice Core (LSC), Delay and Bypass (DnB) and BOOM (OoO)                                | 67 |

| 7  | Sizes of the SInO BOOM (left) and Rocket (right) cores                                 | 70 |

| 8  | LUT (left), flip-flop (center) and BRAM (right) utilization of different queues with   |    |

|    | 16 entries                                                                             | 74 |

| 9  | LUT (left) and flip-flop (right) utilization of different cores                        | 77 |

| 10 | LUTRAM (left) and BRAM (right) utilization of different cores                          | 78 |

# Acknowledgments

We would like to thank the following persons for their help during the work with our master thesis. First and foremost we want to thank our main supervisor, Magnus Själander, for his excellent feedback and for guiding us in the right direction. We are also thankful for the opportunity to pursue a topic of our choosing. We also would like to thank Rakesh Kumar, for sharing his work and giving us valuable feedback. We would also like to thank Erling's supervisor at ITK, Sverre Hendseth, for supporting us in doing a cross-departmental thesis.

Finally, we would like to extend our thanks to Christopher Celio, Jerry Zhao and the rest of the BOOM team at UC Berkeley. Their work with developing BOOM is fantastic, and they were always very helpful and responsive to inquiries.

D.M. & E.J.

# Abstract

The performance advantage of out-of-order processors stems from their ability to extract more instruction-level parallelism (ILP) and memory-level parallelism (MLP) than in-order cores. This is largely the benefit of the dynamic out-of-order schedules they create. The downside of out-of-order scheduling is that it comes at high energy and die-area cost. We evaluate three recently proposed FIFO-based scheduling techniques found in Load Slice Core (LSC), Delay and Bypass (DnB), and CASINO. They all promise a large part of the performance gain of out-of-order scheduling, but at a much lower cost.

DnB and LSC focus on extracting MLP by iteratively building load slices and giving them precedence in the execution order. The dependency analysis technique they employ is called Iterative Backward Dependency Analysis (IBDA). We evaluate implementability, performance, and area of the proposed IBDA as well as proposing three improved implementations of IBDA that require less area and power while providing essentially the same performance. DnB, LSC, and CASINO, the third technique, are all based around the idea of replacing the expensive, content addressable issue queue with cheaper FIFOs.

We implement all these techniques based on BOOM, an open-source, RTL implementation of an out-of-order RISC-V core. We synthesize our designs and evaluate them on a Xilinx ZC707 FPGA. By instantiating our cores as part of a system on chip, we are also able to boot Linux on them.

Our evaluation, using parts of the SPEC CPU2006 benchmark suite, confirms the claims that these techniques come close to the performance of a fully-fledged out-of-order core. LSC and CASINO do this while consuming noticeably fewer resources. DnB comes closest to the performance of out-of-order cores, but it fails to show area-benefits in our implementation. Additionally, we provide insights into the overheads that the BOOM core has over its smaller sibling, the in-order processor Rocket.

As this form of implementation is much closer to real silicon tapeouts than simulators, it forces us to consider and analyze implementation specifics that can be ignored in high-level simulation. This provides insights into the implementability of the different techniques.

Our work provides a big step towards providing accurate measurements, instead of estimates, of performance, power, and area usage for LSC, DnB, and CASINO.

# 1 Introduction

In 1974 Robert Dennard, an IBM researcher, saw that by reducing the size of a transistor, it was possible to reduce its switching voltage, increase the switching frequency and still keep the power consumption per square mm constant [3]. This was later referred to as Dennard Scaling. It meant that, as transistors kept getting smaller, the operating voltage could be decreased, and the operating frequency could be increased, without using more power. For each technology node, a bigger processor that still wouldn't consume more power, or take up more valuable die area, could be designed. Computer architects could optimize solely for instruction-level-parallelism without being too concerned about area or power consumption [4]. This has led to complex and power-inefficient super-scalar out-of-order designs, some of which have instruction windows of over 200 instructions [5]. What Dennard scaling ignores is the constant leakage current and threshold voltage which contributes to the power density in the transistor and doesn't scale down with the size. As the leakage current starts to dominate, power consumption per transistor no longer scales down with smaller transistors. This means that while more transistors are available, their power consumption per square millimeter rises [6].

This has created the so-called Power Wall [7] which not only limits the clock frequency of desktop processors to around 4 GHz, but also makes reducing the power consumption of mobile processors more challenging. Today energy-efficiency is the key evaluation metric for computer architects [4].

The rise of the Internet of Things creates a need for very low-power processors that still offer enough performance to perform meaningful tasks. These systems are connected to the internet and often run full operating systems like Linux. In order to keep up with the rising demand for compute of more and more advanced cryptographic standards, these systems should offer a high amount of performance for their power envelope. This is important as it keeps these systems from becoming obsolete or insecure quickly. Furthermore, some applications only become possible if processors with sufficient performance in a small power envelope are available.

This has led to a series of innovative designs trying to maximize the performance per watt and performance per square millimeter of processors. Central to some of these designs are novel approaches to instruction scheduling. To reduce power and area they try to harness as much of the performance gains of out-of-order cores as possible, while keeping the cheap and simple structures of in-order cores.

This report is split into two parts. In the first part we look at Iterative Backwards Dependency Analysis (IBDA), a promising hardware technique that builds program slices. IBDA is a key enabling technique in several promising architectures, including the Load Slice Core [1], Delay and Bypass [8] and Freeway [9]. We introduce Single Write IBDA, Fuzzy IBDA and Bloom IBDA, three

optimizations that greatly reduce the original IBDAs area and power consumption.

In the second part we present our implementation of, and evaluate, three promising, recently proposed instruction-scheduling techniques that aim to extract *some* instruction-level parallelism, but without needing all the expensive structures of conventional out-of-order designs. The techniques share the core idea of replacing expensive issue queues with cheap FIFOs. We, therefore, explore different designs for these FIFOs. The *Load Slice Core* [1] adds a bypass instruction queue to a stall-on-use in-order processor, to let memory slices bypass the rest of the instruction stream and executed early. *Delay and Bypass* [8], keeps the expensive out-of-order structures but tries to reduce their sizes at minimal performance loss. *CASINO* [10] adds a simple instruction queue to a stall-on-use in-order processor and lets instructions execute early if they are ready.

We implemented these techniques based on the most recent version of the BOOM core, BOOM v3 [11], an open-source core written in the hardware description language Chisel [12]. Furthermore, we evaluate them on an FPGA, integrated in the Chipyard [13] system on chip platform. Our evaluation includes size estimates based on FPGA synthesis, application performance under both Linux and a lightweight micro-kernel. To gauge the overhead an implementation based on BOOM incurs, we compare a simplified in-order version of BOOM to Rocket [14]. We also report on difficulties and caveats encountered during the implementation of these microarchitectures.

# Part I

# Iterative Backwards Dependency Analysis

# 2 Background

This chapter will introduce the main concepts underlying IBDA, Single Write IBDA, Fuzzy IBDA and Bloom IBDA. The sections Program Slices and Dependency Analysis lay the theoretical groundwork for dependency analysis in general. Sections Cashes and Memories give a foundation for understanding how different design choices for the IST affect how it is synthesized. Hashing introduces concepts used by Fuzzy IBDA which sacrifices precision for reduced area. Lastly we will introduce IBDA, as it was described by Carlson et al. [1].

#### 2.1 Program Slices

IBDA builds on the concept of program slices [15]. A program slice is a series of dependent instructions which leads up to, or away from, a *criterion*. A criterion is an event, typically performancedegrading, which can occur at a point in the program if certain prerequisite are fulfilled. This can for instance be a branch misprediction, or a cache miss.

A slice can be broken up into four components. The *value sub-slice* consists of instructions that manipulate the input operands of the criterion. The *address sub-slice* consists of instructions that calculate the memory addresses, either for the criterion itself, when it's a store or a load, or for the value sub-slice. The *existence sub-slice* consists of branches that determine whether the criterion instruction will be executed at all. Lastly, the *control flow sub-slice* consists of branches, that decide which of multiple paths to the criterion the program will take.

Instructions are recognized as part of a sub-slice, if there is a chain of dependencies from it to the criterion. Dependencies come in two flavors. *Data dependencies* occur when the input operand of an instruction is the output of another. *Control dependencies* exist between an instruction and a branch, if the branch decides whether the instruction will execute or not. Furthermore, a data dependency is an *address dependency*, if the data contributes to the calculation of a memory address.

A slice architecture is one that is centered around extracting and diverting slices leading up to certain criteria. Examples of slice architectures are the Decoupled Access/Execute Architecture [16], Load Slice Core [1], Delay and Bypass [8], and Branch Slice Core [17].

## 2.2 Dependency Analysis

There are several techniques for detecting slices. The simplest option, from a hardware perspective, is to let the compiler do the analysis [18]. The disadvantage of this approach is that it is not backwards compatible. A proposed hardware solution is to store the N latest committed instructions with their dependencies in a FIFO buffer, called the *Slicer*, and, upon detecting a criterion, traversing the Slicer and extracting the PCs of the slice [19]. The slices are stored in a cache indexed by the PC of the lead instruction. This sets the maximum number of instructions to be stored within a single

slice cache entry as the limit to the maximum slice length. The depth of the Slicer, N, sets the limit for how far into the past a slice can be computed.

# 2.3 Hashing

This section describes the basics of hash functions and entropy. Hashing is an operation h(x) = y, mapping an arbitrary sized input x, called a key, to a fixed length output y, the hash, typically of a smaller length [20] Since y is of a fixed length and x can be of arbitrary length, there will be multiple inputs  $x_1, x_2$  which map to the same output.  $h(x_1) = h(x_2)$ . Such a scenario is called a collision. An ideal implementation of h(x) is cheap to compute and distributes the keys uniformly among the output values, thus minimizing collisions. This means, an ideal implementation is very dependent on the set of input keys it will receive.

#### 2.3.1 Entropy

Entropy is a measure of randomness or unpredictability. Given a set X, consisting of n-bit symbols, the entropy H(X) of the set is the average number of bits per symbol needed to encode all symbols in X [21] Mathematically entropy can be expressed as

$$H(X) = -\sum_{i=1}^{n} P(x_i) \log_2 P(x_i)$$

(2.1)

Where P(X) is the probability distribution for the symbols in X.

If the symbols in X are uniformly distributed, i.e. it is equally likely to draw any symbol from that set, the set would have  $log_2n$  bits of entropy, where n is the number of unique symbols. However, if the distribution is not uniform, but rather skewed towards some value, there would be less entropy because there is less randomness. Consider for instance the set  $X_1 = \{a, b, c, d\}$ . With a uniform probability distribution, i.e.  $P(X_1) = \{0.25, 0.25, 0.25, 0.25\}$ . The entropy for  $X_1$  is  $H(X_1) = 2$ . However, consider the set  $X_2$  which also contains only four different types of symbols, but has a nonuniform probability distribution  $P(X_2) = \{0.7, 0.1, 0.1, 0.1\}$ . The entropy is in this case  $H(X_2) =$ 1.86. It is lower because it is a set with a lower degree of randomness. An efficient hash function h(x) will retain as much as possibly of the entropy of the input keys and spread it to the output bits.

# 2.4 Memories

Regular SRAMs use shared bit lines for reading and writing. This means they can perform one read or write during each cycle. Adding the ability to read and write in the same cycle generally doubles the area of a single SRAM cell. Since the size of an SRAM is largely dominated by the cells, the total size effectively doubles. Additional ports can be added by using additional bit lines. As this increases the fan-out of the cells, the transistors need to drive a higher load and their sizes might need to be increased. [22]

While it is possible to customize the SRAMs and add additional ports when targeting ASICs, the limits of resources within FPGAs can not be altered. The Xilinx Zynq FPGAs we use for evaluation provide SRAM blocks with synchronous reads called BRAMs. These 18 Kbits large blocks can be

Figure 1: Memory with two write ports and one read ports using LVT

configured to different widths and sizes. Each BRAM provides two ports that can both either read or write (true dual port). [23]

The other type of SRAM available in Zynq FPGAs is called Distributed RAM. Up to a quarter of the SRAM-based look-up tables (LUTs) that are used to implement combinational logic can be re-purposed as Distributed RAMs. Distributed RAMs support both synchronous and asynchronous reads, and consist of up to 4 LUTs. They provide one primary port that can both read and write, as well as up to 3 additional read-only ports. Depending on the port configuration their size ranges from 32x1 to 256x1 with options for 32x6 and 64x3. [24]

Multiple BRAMs can be combined to emulate an SRAM with more ports. To emulate a singlewrite-multiple-read SRAM, multiple BRAMs can be used without requiring external logic, by writing the same data to one port of all BRAMs and using the other ports as independent reads. Adding write ports is not possible without external logic. Different schemes that can be used to emulate such a memory on an FPGA were described by LaForest et al. [25]. The simplest but most expensive option is emulating the SRAM using registers and LUTs.

A more advanced scheme uses a Live Value Table (LVT). An example of a memory using the LVT is shown in Figure 1. Here BRAMs are used to store the data itself and a LVT, a small multi-ported structure implemented using LUTs and registers, to select the BRAM with the right data.

A general factor that has to be decided for SRAMs with multiple write ports is precedence. If

several ports write to the same address, the precedence decides which write will be stored. In our implementation higher ports have precedence over lower ones. When multiple instructions write data to an SRAM, the data from the latest instruction is used.

#### 2.5 Caches

Building hierarchical memories with caches is one of the main ideas underlying modern high performance computing [26]. In this section we will introduce the cache concepts needed to build efficient IBDA. We will look at caches from the perspective of their main use-case - storing a subset of main memory in a small and low-latency structure to decrease average memory latency.

The idea of the cache is to create a small and fast memory that stores important data. Caches in the memory hierarchy contain some subset of the full main memory. An address location can be quickly looked up and fetched if it resides in this kind of cache. If it is not present in the cache it can be fetched from main memory and kept in the cache for the next time the program wants to access it.

One of the main characteristics of a cache is its associativity. Associativity defines how much flexibility there is in choosing a cache entry for an address. A cache where an address can map to any location in the cache is said to be *fully associative*. To look up an address in such a cache all its entries must be read, because a match could be found anywhere. A cache where each address maps to a single entry is called *direct mapped*. In this case each address is mapped to one specific cache entry. A middle ground between fully associative and direct mapped is set associative. A set associative cache consists of m sets, each consisting of n ways, for a total of  $m \times n$  entries. Addresses are mapped to one of the m sets, but the placement within the set, i.e. in which way, is up to the cache. To look up an address in a set associative cache, all the ways of the set to which the address maps have to be read. A *n*-entry fully associative cache is equivalent of a *n*-entry *n*-way set associate cache. A *n*-entry directly mapped cache is equivalent of a *n*-entry 1-way set associative cache.Riot control agents are designed to cause irritation within seconds of exposure, making the exposed want to flee the scene. And indeed, toxicologists advise that getting away from the gas is the best and first thing to do to mediate the impact. To add an entry to a set associative cache with more than one way, a replacement policy deciding which entry to overwrite is needed. The standard replacement policy is Least Recently Used (LRU), which overwrites the entry which was least recently accessed. For a 2-way cache this can be implemented with a single bit per set. The cache only contains a small subset of the main memory and thus will have cache misses. Cache misses can be divided in three classes [27].

- 1. A *compulsory* cache-miss happens the very first time a program accesses an address and will always result in a cache miss.

- 2. A *capacity* cache-miss occur if the set of addresses that the program access, i.e. the working set, is bigger than the cache.

- 3. A *conflict* cache-miss occurs when an address has been evicted because the number of working set addresses that map to a cache set is greater than the number of ways.

## 2.6 Iterative Backwards Dependency Analysis

IBDA is a hardware technique for building program slices of data-dependent instructions. It is implemented using two structures. The *Register Dependency Table* (RDT) contains, for all physical registers, the PC of the instruction that last wrote to it. Another way to view it is that the RDT contains the producers of all the registers. When an instruction that is part of a program slice is entered into the RDT, the PC of the instructions that produced its source operands can be looked up. These PCs can be added to the *Instruction Slice Table* (IST), the second component of IBDA. The RDT also stores a bit indicating whether the producer of a register is already present in the IST, to avoid writing the same PC to the IST multiple times. [1]

The IST stores all the instructions which have been identified by the RDT as part of a program slice. Figure 2 shows an overview of how IBDA is placed in the Load Slice Core. Instructions are looked up in the IST during the decode stage and the RDT is updated during the rename stage. Instructions that are found in the IST are tagged as a part of a program slice. We call these *marked* instructions. When such a marked instruction is entered into the RDT, its source registers are looked up and the producers of the source registers are added to the IST. [1]

Consider the program in Listing 2.1. Let's assume that the criterion is a load, i.e. we are tracking load slices. Our loop is centered around instruction (1) which loads data. Instruction (2)-(6) are transforming the loaded data and writing it back to memory. Instructions (7) and (8) calculate the next load address, and are thus part of the load slice. At the beginning of the program the IST is empty. During the first iteration of the loop the IST will be updated with the *li a3, 0x800500c* instruction which is the producer of the first load address. But at the second iteration of the loop when we get to (1), the RDT will map (8) as the producer of 2. Thus (8) is added to the IST. Later in that same iteration when we get to (8), it will be present in the IST. So when (8) is entered into the RDT it is marked as part of a program slice and we will look up the producer of its only dependency *a2*. This is (7), so it is added to the IST. In the next iteration when we get to (7) we will look up its dependency, which is a1, and its producer, (1). Thus we have the whole program slice resulting in the load at (1), stored in the IST.

```

init:

li a0, 100 ; Loop iterator

li a2, 0x8000301c ; Intial load address

li a3, 0x8005000c ; Initial store address

j loop

loop:

(1) lw a1, O(a2) ; Load data from memory

(2) mul a4, a1, a5 ; Do arithmetic on data

(3) add a6, a4, a1

(4) div a7, a4, a6

(5) sw a6, O(a3); Store result in other memory location

(6) addi a3, 32 ; Calculate next store address

(7) mul a2, a1, 99 ; Calculate next load address

(8) addi a2, 32 ; Calculate next load address cont'd

(9) addi a0, -1 ; Decrement loop counter

(10) bnez a0, loop

```

Listing 2.1: Example of a loop to show how IBDA works

Figure 2: IBDA embedded in the Load Slice Core. Adapted from [1].

# 3 IBDA implementations

In this chapter we motivate and introduce our IBDA improvements. They were all implemented as part of our Load Slice Core (LSC) implementation, which is based on a 2-wide BOOM core [28]. LSC uses loads and stores as program slice criteria, and thus is tracking load slices [1]. LSC is discussed in greater detail in Part II of this report. The 2-wide LSC decodes and renames two instructions in parallel each cycle.

We are particularly interested how different design choices affect the number of read and write ports to the SRAMs, which will hold the RDT data and IST data. We motivate some of our design choices with simulation data from Spike, a high-level RISC-V simulator. This should not be confused with the cycle accurate simulation results presented in Section 10.5.

# 3.1 Perfect IBDA

Perfect IBDA is a theoretical implementation with a limitless fully associative cache as the IST. Perfect IBDA will still not be able to correctly identify all load slices, as it also needs to iteratively compute them. It is not synthesizable and is, unlike the others, only implemented in Spike. By implementing Perfect IBDA *together* with the other each of the other IBDA designs we can evaluate their performance normalized to the maximum achievable performance.

# 3.2 Original IBDA

The Original IBDA is a straightforward implementation as described by Carlson et al. [1]. The IST is a 128 entry, 2-way set associative cache indexed by the 40 bit PC of each instruction. The RDT has 80 entries, as many as there are physical registers in our core.

## 3.2.1 RDT

To support the dual write needed by a 2-wide core, we need two SRAM banks and an LVT to implement the the RDT. As each instruction that is looked up can have up to two dependencies, the RDT has a total of four read ports. Likewise, the RDT needs four output ports to write the dependencies to the IST. Since we are working with a 2-wide core we must also consider the scenario when the instructions added to the RDT are data-dependent. If the later instructions are consuming the result of the former, then that later instruction will do a lookup in the RDT entry that the former writes to. Writing and reading to the same address in the same cycle has undefined behavior for many SRAMs, including the BRAMs on out ZC706 [23]. Bypass registers are added to avoid this.

# 3.2.2 IST

When implementing a cache one of the design choices is how to compute the index. For the Original IBDA we compute it as PC[1 : 6] XOR PC[7 : 12]. The least significant bit is left out as it is always zero in RISC-V, as instructions are half-word aligned. The reason for the XOR operation is to increase the entropy of the least significant bit of the index. PC[1] is only used when using compressed instructions and thus there is a risk of having programs where there is no entropy in this bit.

The IST essentially does two things. The first is that it looks up instructions during decode to identify them as part of a program slice or not. As our design uses a 2-wide decode stage, this requires two read ports to each of the SRAMs which contain the different ways. The second is to write the PCs it receives from the RDT to its cache so that they later will be identified as part of a program slice. This naturally requires one write port per instruction that could be written, for a total of four.

# 3.3 Single Write IBDA

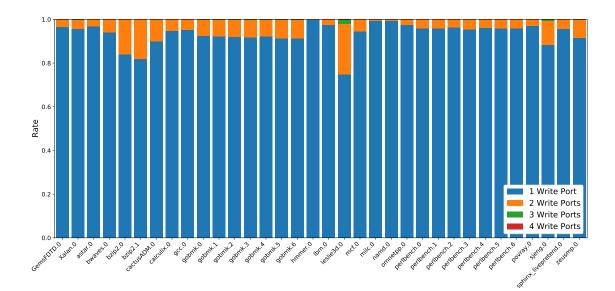

The Original IBDA has a major flaw. The IST needs four write ports from the RDT. As discussed in Section 2.4, implementing memories with multiple read and write ports is expensive. Figure 4a shows how often the different write ports where used for a 128 entry 2-way set associative design running SPEC. On average, 93% of the writes from RDT to IST only used one of the four write ports.

To solve this issue we propose Single Write IBDA. Single Write IBDA use the fact that the RDT already stores whether the producer of the physical registers are already present in the IST or not, to reduce the number of write ports from four to one. Figure 3 shows the overview of the RDT for a 2-wide core with only one write port to the IST. There are mainly two things happening. First, *ren\_uop1* and *ren\_uop2* update the RDT SRAM by writing their addresses, *pc*, to the position corresponding to their destination registers. *rdst*. This keeps the RDT updated with the addresses of all the producers of the registers. Then, we check whether *ren\_uop1* and *ren\_uop2* are marked *in\_ist*. This signal was updated by the IST the previous cycle. If *ren\_uop1* and *ren\_uop2* are marked as in the IST we proceed to check whether the producers of the source operands, *rs1* and *rs2* are already written to the IST. This is stored with flip-flops in the structure we call *in\_ist*. The source operands which are *not* already present in the IST are fed into a priority MUX which takes the first operand of the youngest micro-op available and forwards it to the read port of the RDT SRAM. In essence, we look up the producer of the first.

Consider the scenario where both *ren\_uop1* and *ren\_uop2* are marked as in the IST, and both have two operands with producers that are *not* marked as in the IST. In this scenario Original IBDA would use all four write ports to add all four producers to the IST. Single Write IBDA will only add the producer of the first *ren\_uop1* operand, i.e. the instruction that last wrote to rs1 or *ren\_uop1*. In the following iteration that first producer will be marked as in IST and we will write the second

Figure 3: Single Write IBDA RDT with one write port to the IST

producer, i.e. the instruction that last wrote rs2 of *ren\_uop1*. In essence Single Write IBDA doubles down on the iterative approach of IBDA by adding only one producer at a time to the IST.

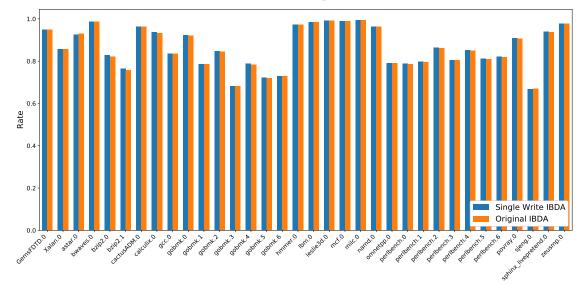

Figure 4b compares the load slice extraction rate of Single Write IBDA with one write port and Original IBDA with four write ports. Notice that reducing the number of write ports has a negligible effect on slice extraction.

#### 3.4 Fuzzy IBDA

Fuzzy IBDA is an optimization that reduces the size of the instruction tag that is stored in both the IST and RDT, at the cost of introducing false positive hits in the IST. This section motivates why a fuzzy approach could be better and shows the implementation details of a Fuzzy IBDA using the instruction bits as input.

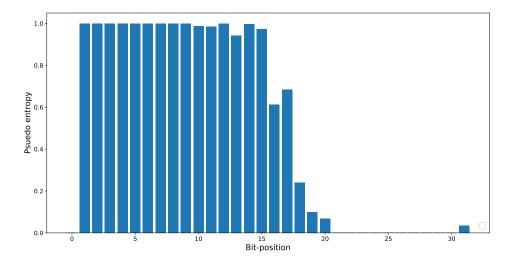

The Original IBDA uses the full PC of 40 bits to tag instructions. This provides a unique identifier for each instruction, however, it is unnecessarily big. Figure 5 shows the pseudo-entropy contained in each bit of the PC for a complete run of SPEC. Notice that only bit 1-17 have significant entropy.

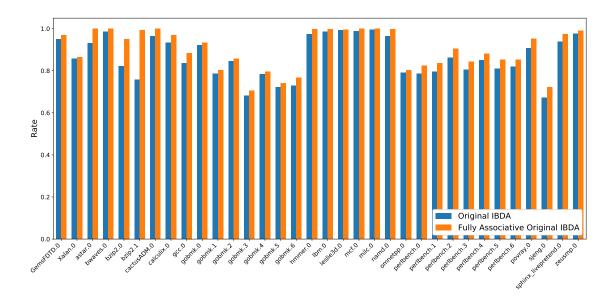

Another observation is that Original IBDAs performance is mainly limited by the IST. Figure 6 shows the load slice extraction for Original IBDA and Fully Associative Original IBDA, an implementation with a fully associative cache as the IST. Both are normalized to Perfect IBDA. The difference in load slice extraction is entirely due to the premature evictions of IST entries. The delta between Original IBDA and Perfect IBDA is composed of both capacity cache misses, i.e. because 128 entries are not enough to store the working set, and conflict misses, when multiple instructions map to the

# (a) Utilization of the four IST write ports for SPEC CPU2006

#### (b) Load Slice extraction normalized to Perfect IBDA for Single Write IBDA and Original IBDA

Figure 5: Average pseudo-entropy for each PC-bit running SPEC CPU2006

same set. The delta between Fully Associative Original IBDA and Perfect IBDA is only composed of capacity cache misses. This tells us that the main issue is the capacity misses. By reducing the instruction tags we can afford more entries in the IST and thus tackle the real issue of capacity misses.

There is also another BOOM-specific drawback of Original IBDA. BOOM does not forward the full PC beyond the frontend, where it is stored in the fetch target queue (FTQ). Only the 6 lower order bits, denoted *pc\_lob*, which give the address of the instruction within the cache block, are bundled with the micro-op. To work around this the full PC could be bundled with the micro-op and passed through the fetch buffer, decode and rename. Another option would be to add additional read ports to the FTQ for the IST and RDT. A third option that we now will explore in depth is to use a combination of pc\_lob and the instruction bits as a tag. The BOOM pipeline will be discussed in Section 7.2.4

Using the instruction bits as a tag introduces the possibility of false positive hits in the IST. This can happen if the program has two identical instructions located at two different addresses that share the *pc\_lob*. A false positive hit in the IST will trigger the extraction of a false slice leading up to a false criterion. Any hits in the IST which would not have occurred with Perfect IBDA are denoted as a false positive, i.e. correct hits on *false slices* are also counted. False slices will likely lead to eviction of true slices and thus degrade performance further.

Using a hash of the PC bits is also an option for micro architectures that have the PC available in the backend. The following discussion also applies to the this.

Figure 6: Load slice extraction normalized to Perfect IBDA for Original IBDA and Fully Associative implementation running SPEC CPU2006

# 3.4.1 Hash Functions

Our estimations show that for SPEC CPU2006 the instruction words contains around 11 bits for entropy. Combined with around 5 bits of entropy for *pc\_lob* we get a total 16 bits. There is therefore no point in using full 38 bits of instruction word and pc\_lob. A hash function is thus used to reduce number of bits in the tag.

#### 3.4.2 Naive Hash

Our first approach to a hash function is just be picking out the bits shown to have the highest entropy. We call this Naive Hash. Its main weakness is that is purely optimized for SPEC workloads and its thus not very flexible for new types of programs. Naive hash serves as a baseline for other hash implementations.

#### 3.4.3 Random Binary Matrix Hash

A more promising technique is that of a Random Binary Matrix Hash. It is inspired by the address mapping techniques using binary invertible matrices described by Jahre et al. [29].

For a hash function with n input bits and m output bits, a random matrix M with m rows and n columns is created. For an input x the hash h(x) is simply the matrix multiplication h(x) = Mx over the residue field of 2. Lets consider a simple example of a Random Binary Matrix Hash function that

Figure 7: Average false positive rate for Fuzzy IBDA running SPEC CPU2006 with different hash functions

maps a 4-bit input to a 3-bit output. Our hash function is then

$$h(x) = \begin{bmatrix} m_{11} & m_{12} & m_{13} & m_{14} \\ m_{21} & m_{22} & m_{23} & m_{24} \\ m_{31} & m_{32} & m_{33} & m_{34} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ x_4 \end{bmatrix} = \begin{bmatrix} m_{11}x_1 + m_{12}x_2 + m_{13}x_3 + m_{14}x_4 \\ m_{21}x_1 + m_{22}x_2 + m_{23}x_3 + m_{24}x_4 \\ m_{31}x_1 + m_{32}x_2 + m_{33}x_3 + m_{34}x_4 \end{bmatrix}$$

(3.1)

This can be implemented by XOR'ing together the columns of M corresponding to the set bits of x. The Random Binary Matrix Hash works by letting each input bit contribute to each output bit. A chained version of this type of hash was described by Augot et al. [30].

Figure 7 compares the false positive rate for Naive Hash and Random Binary Matrix Hash hashing  $pc\_lob$  and the instruction word. The values reported are the average for a run through SPEC. The same Binary Matrix was used for all programs. The false positive rate for a design using the full instruction word and  $pc\_lob$  is also added for comparison as "Full Instruction Word". By producing 14 bit hashes the Random Binary Matrix achieves close to the same performance as using the full Instruction Word and the  $pc\_lob$  which is 38 bits in total. At 18 bits the performance is almost identical.

A problem we encountered was that there is some variance in the performance of different random matrices. We solved this by running multiple smaller benchmarks until we found a seed for our random number generator that gave satisfactory performance.

Figure 8: Partitioned Bloom filter with one insert and two membership test ports. Flush logic not shown.

# 3.5 Bloom IBDA

The Bloom IBDA is a fuzzy implementation that uses a Bloom filter as the IST. A Bloom filter is an approximate set that can have false positives but not false negatives for membership tests [31]. It uses an array of m bits that is indexed by k different hash functions. When a value is added to the Bloom filter it is hashed using each of the hash functions, and the bits that the hashes correspond to are set to high in the array. To check if a value is in the Bloom filter it is again hashed. If the bits at the indices the hash point to are all high it is reported as part of the set. This can either be because it was added before or because there was a collision resulting in a false positive.

As more values get added to the Bloom filter, more bits get set, and the probability of a false positive rises. If *n* values have been added to the Bloom filter the probability of a false positive  $p \approx (1 - e^{-kn/m})^k$ . This means that a Bloom filter can only be used with reasonable confidence until a certain number of values has been added. The maximum value of *n*,  $n_{max}$ , depends on *m*, *k* and the acceptable rate of false positives,  $p_a$ .

A conventional Bloom filter requires k writes to the bit array, for each addition to the filter, and k reads for each membership check. As SRAMs using multiple read and write ports are expensive our implementation deviates from this scheme by using a separate bit array for each hash function. This structure is called a Partitioned Bloom filter [32]. It uses k m-bit arrays with one write and two read ports, to support one addition and two membership checks per cycle.

A schematic for k = 2, m = 2048 is shown in Figure 8 The probability of false positives changes

Figure 9: Comparing a conventional Bloom filter to a Partitioned Bloom filter

to  $p_{partitioned} \approx (1 - e^{-n/m})^k$ . An example of a Bloom filter membership test, with k = 3 and m = 16 is shown in Figure 9a. The gray entries represent the high bits from a previously added value. The arrows point to the hash function outputs of the membership test. This will result in a negative result.

The same example using the Partitioned Bloom filter is shown in Figure 9b. Notice that the conventional Bloom filter has a collision between Hash1 and Hash2 for the previously added value. The Partitioned Bloom filter avoids such collisions but requires k times more storage. This makes the conventional Bloom filter more attractive in software, where the target is to keep the memory footprint low, and the accesses for the different hash functions can happen sequentially. A hardware implementation of this would get prohibitively expensive for larger values of k. In hardware the Partitioned Bloom filter shines by requiring only memories with multiple read and one write port. Furthermore, the probability of a collision for given values of k and m is lower since collisions between different hash functions become irrelevant.

The disadvantage of Bloom filters is that there is no way of removing individual old and irrelevant entries. Because the probability of false positives grows as more values are added, the Bloom filter has to be flushed when  $n_{max}$  values have been added. In our current implementation it takes m cycles to flush the Bloom filter, so a high flush rate will degrade performance. If the SRAM arrays were partitioned into smaller banks this could be reduced by zeroing the banks in parallel. Figure 10 shows the flush rate for various implementations of Bloom IBDA. The flush rate reflects the  $n_{max}$  of that implementation and the load slice working set of the benchmark. Notice that for some benchmarks, like bzip, the load slice working set fits within Bloom filter for most of the benchmark, and the flush rate is close to zero.

Finally, Figure 11 compares the load slice extraction for Original IBDA, Single Write IBDA, Fuzzy IBDA and Bloom IBDA. Fuzzy IBDA uses the instruction word and the 6 least significant bits of the PC. Bloom IBDA uses 2048 bits, eight hash function and  $p_{partitioned} = 0.01$  The results are normalized to Perfect IBDA which has the maximum achievable load slice extraction for any IBDA.

Figure 10: Flush rate for different implementations of Bloom IBDA running SPEC CPU2006

based design. Clearly the inaccurate approach of Fuzzy IBDA and Bloom IBDA gets a higher load slice extraction. This is because they are more likely to identify any instruction as part of a load slice, leading to false positives. Some of these false positive hits will actually be part of a load slice.

The missing piece of information is how expensive those additional false positives are. This can be investigated by doing an RTL implementation of the different IBDA designs and running real workloads on it.

Figure 11: Comparing load slice extraction normalized to Perfect IBDA for Fuzzy, Baseline and Single Write IBDA running SPEC CPU2006

# 4 Methodology

# 4.1 Spike

To generate the false positive rates and load slice extraction rates reported in Chapter 3 we used Spike. Spike is an open-source RISC-V ISA simulator. It is a high-level behavioral simulator and does not model any low-level pipeline structures. This means it is not fitted to simulate the performance implications of false positive rate and load slice extraction rates. However, it was a great fit for rapid implementation and behavioral testing of the IBDA algorithm itself. Our fork of Spike is hosted on Github<sup>1</sup>.

# 4.1.1 Pseudo Entropy

To calculate the entropy of a set X probability distribution P(X) needs to be known. In many cases this is not available and heuristics have to be used instead. We wanted to calculate the entropy contained in each bit of the instruction word for RISC-V instruction set architecture (ISA). For an introduction to RISC-V please refer to Section 7.2.2. Using Spike we could simulate the whole benchmark and thus have access to the complete stream of instructions that constitutes these benchmarks. However, since it contains billions of instruction it would simply not be feasible to store the instruction word of each retired instruction. Instead, we use a 32x32 matrix of integers, E, to track how often each bit was high. When an instruction retires, all the 32 bits of its instruction word are looped over. When a high bit is found, all the integers in the corresponding matrix row, that match the high bits of the instruction word, are incremented. In other words, the diagonal of the matrix will contain the absolute number of times each instruction bit was found to be high. E(8, 8) has the count of how many times bit 8 of the instruction word was high. The other positions count how many times combinations two bits where high together. Thus E(1, 2) is how many times both bit 1 and bit 2 were high. This matrix is thus symmetric, as E(i, j) = E(j, i).

*E* will thus contain information about the probability of each bit being high and the conditional probability of it being high. Note that we only have a "one-level" conditional probability, i.e. given a single other observation.

Using Equation 2.1 we can calculate the matrix H that contains the entropy for each bit on the diagonal and the conditional entropy outside.

Our algorithm for calculating the pseudo entropy of all the bits based on the matrix H is given in Listing 4.1. What we essentially do is in each iteration pick the bit with the highest average conditional entropy, with respect to each individual bit that is already picked. Thus, we order the bits from high entropy to low, and we can sum up the entropy.

This is pseudo-entropy because each iteration we should have computed the conditional entropy

<sup>&</sup>lt;sup>1</sup>https://github.com/erlingrj/riscv-isa-sim/tree/ibda

based on all the bits in the  $PICKED_BITS$  array. However, we only can calculate the conditional entropy with respect to one at the time.

Listing 4.1: Pseudo entropy algorithm

```

H = {32x32} # H is a 32x32 bit matrix containing entropy and conditional entropy of all bits

A = \{1..32\} \# A contains all the bit positions

PICKED_BITS = {} # Contains our picked bit positions.

total_pseudo_entropy = 0

while len(A) > 0:

if len(RES) == 0: # First iteration

# Find element S with the highest "absolute entropy"

S = find_max(diagonal(H))

# Initialize the running total with that entropy

total_pseudo_entropy += H(S,S)

# Finally remove S from A and add to PICKED_BITS

A.remove(S)

PICKED BITS += S

else: # Rest of iterations

# First we find the bit with the highest average conditional entropy

# given the bits already present in PICKED_BITS

S = find_max_avg_conditional_entropy(H,PICKED_BITS)

# Then we add the average conditional entropy of that bit to the running total

total_pseudo_entropy += get_avg_conditional_entropy(S,PICKED_BITS)

# Lastly we remove the bit from A append it to the PICKED_BITS array

A.remove(S)

PICKED_BITS += S

```

# 4.2 Load Slice Core

We have implemented the different IBDA designs as part of our Load Slice Core implementation. It is a register-transfer level (RTL) design based on BOOM and explained in detail in Section 8.4. Our fork of BOOM which contains the Load Slice Core and all IBDA designs is hosted on Github<sup>2</sup>.

# 4.3 FPGA-based Application Performance Evaluation

For testing and verification we used the cycle accurate software simulator Verilator [33]. However, to get real performance numbers of our IBDA implementations we have synthesized our designs, as part of LSC, to a Xilinx Zynq ZC706 FPGA. This allowed us to run parts of the test data set of the SPEC2006 benchmarks, with LSC running at 50 MHz. Refer to Section 9.2 for a more detailed discussion on running core emulations on an FPGA and Appendix A for a step-by-step guide.

When reporting averages we use the harmonic mean.

<sup>&</sup>lt;sup>2</sup>https://github.com/EECS-NTNU/riscv-boom/tree/thesis-final

|                               | Baseline | Single Write IBDA | Fuzzy IBDA | Bloom IBDA |

|-------------------------------|----------|-------------------|------------|------------|

| IST Ways                      | 2        | 2                 | 2          | -          |

| IST Sets                      | 64       | 64                | 64         | -          |

| RDT->IST Write ports          | 4        | 1                 | 1          | 1          |

| IBDA Tag Size                 | 40       | 40                | 14         | 40         |

| Bloom hash functions          | -        | -                 | -          | 6          |

| Bloom collision rate          | -        | -                 | -          | 0.001      |

| Bloom IST entries             | -        | -                 | -          | 2048       |

| Seed for random hash matrices | -        | -                 | 1          | 1          |

Table 1: IBDA parameters

# 4.4 FPGA-based Area Analysis

To evaluate the area needed by each IBDA design we look at the resource utilization in the synthesized designs targeting FPGAs. Refer to Section 9.1.1 for a more detailed description of the resources available and the shortcomings of this method.

# 4.5 IBDA Parameters

Refer to Table 6 in Section 9.3 for the configuration parameters used in LSC for all the IBDA implementations. Table 1 shows the IBDA parameters used by the different different implementations.

# 5 Results & Discussion

In this section we will look at the results from synthesizing and simulating our RTL implementations of the various IBDA designs. First we will look at the performance when running SPEC CPU2006 on an FPGA prototype of the Load Slice Core with the different implementations of IBDA. Then we will take a detailed look into area and resource usage of the different implementations.

# 5.1 Application Performance

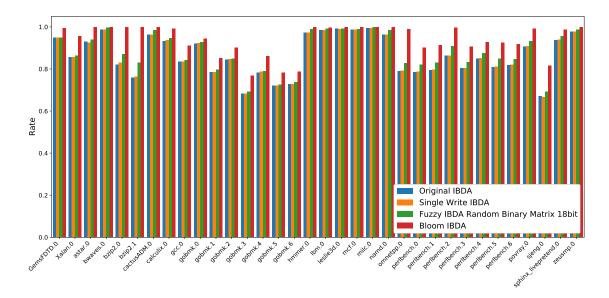

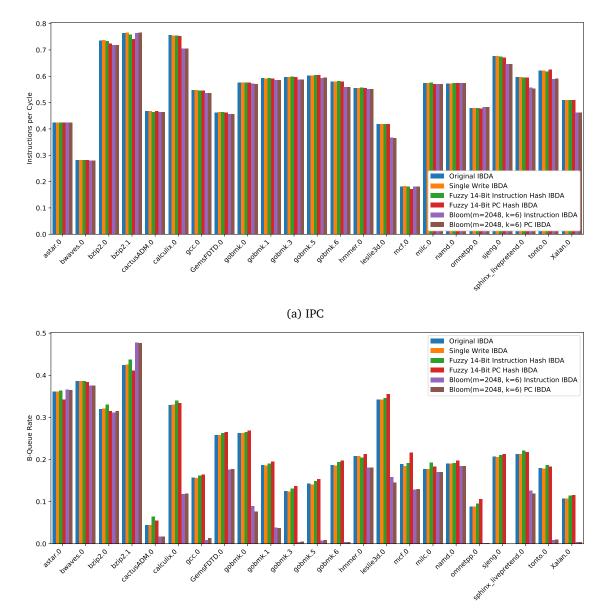

Figure 12a shows the instructions per cycle (IPC) for the different IBDA implementations normalized to the Original IBDA. Figure 12b shows the rate of instructions identified as part of load slices. Our first observation is that Single Write IBDA has on average 100.1 % of IPC and 99.8 % of the rate of instructions identified as load slices, compared to the Original IBDA. Single Write IBDA performs virtually identical to Original IBDA but at a significantly lower cost, as will be shown in Section 5.2 For Fuzzy IBDA we include both a configuration using the PC as input for the hash function and another using the instruction word and the six least significant bits of the PC. The instruction and PC version achieves on average 99.9 % and 98.9 % of the performance using Original IBDA. The *bzip* and *mcf* benchmarks are outliers where Fuzzy performs significantly worse. There will be some random matrices which performs worse than others, depending on the input data. We are unable to draw any conclusions regarding these outliers by looking at the load slice extraction rate.

For Bloom IBDA we observe varying performance and for *omnetpp* it actually outperforms Original IBDA. However, on average, the Bloom IBDA PC and instruction configurations gets 97.2 % and 97.3 % of the IPC of Original IBDA, respectively. The Bloom IBDA configurations both have a  $n_{max}$  of 778. This means that Bloom could work very well for programs with a working load slice set considerably less than Z if the false positives are not to frequent. With many false positives the Bloom IST will fill up and false program slices will be computed and added as well, which will further degrade performance.

In conclusion, Single Write is unquestionably a good optimization. If a design can allow false positive hits in the IST, Fuzzy IBDA will save a lot of space at the cost of only a slight performance drop.

## 5.2 Implementation Sizes

The percentages reported here are comparing only the IBDA components. Single Write IBDA sees a 75 % reduction of BRAM usage, a 55 % reduction of LUT usage, and a 47 % reduction of flip-flop usage, compared to the Original IBDA. Fuzzy IBDA has a 91 % reduction in BRAM usage, 57 % reduction LUT usage and 67 % flip-flop reduction compared to Original IBDA. Bloom IBDA shows an 42 % reduction in BRAM usage, 54 % reduction in LUT usage and a 75 % reduction in flip flop

(b) Load Slice Rate

Figure 12: Performance of the Load Slice Core using different IBDA implementations running SPEC CPU2006.

|       | Original IBDA |       | Single Write IBDA |       | Fuzzy IBDA |       | Bloom IBDA |       |

|-------|---------------|-------|-------------------|-------|------------|-------|------------|-------|

| IST   | 2944          | 556   | 614               | 276   | 498        | 118   | 679        | 25    |

| RDT   | 2096          | 354   | 1662              | 209   | 1717       | 184   | 1631       | 207   |

| IFU   | 6928          | 4968  | 6928              | 4968  | 6926       | 4968  | 6926       | 4968  |

| Total | 115395        | 54187 | 112404            | 53770 | 109903     | 53585 | 112419     | 53461 |

Table 2: LUTs (left) and flip-flops (right) for different IBDA implementations

|       | Original IBDA |    | Single W | rite IBDA | Fuzzy | IBDA | Bloom IBDA |    |

|-------|---------------|----|----------|-----------|-------|------|------------|----|

| IST   | 0             | 32 | 0        | 8         | 80    | 0    | 0          | 24 |

| RDT   | 0             | 16 | 0        | 4         | 0     | 4    | 0          | 4  |

| IFU   | 532           | 19 | 532      | 19        | 484   | 19   | 484        | 19 |

| Total | 1056          | 82 | 1056     | 46        | 1088  | 36   | 1008       | 50 |

Table 3: LUTRAM usage (left) and BRAM usage (right) for different IBDA implementations

usage compared to Original IBDA.

The rest of this section provides in-depth discussion and analysis of the area estimates summarized above. Table 2 and Table 3 report the resource usage of different IBDA implementation. The BRAM usage reported in Table 3 are the combined usage of RAMB36 and RAMB18.

## 5.2.1 Single Write IBDA

Starting with Table 3 we observe that Single Write IBDA only uses a quarter of the BRAMs for RDT and IST compared to the Original IBDA. This is as expected, as our implementation of multi-port SRAM duplicates the whole SRAM for each added write port and for each read port. The IST of Single Write IBDA uses eight BRAMs, that is two for each read port of each way of the IST. This is compared to the 32 BRAMs used for Original IBDA IST. A way has 64 entries of 40 bits for a total of 2560 bits. Each BRAM block can hold 18 Kbits. This gives a utilization of only 7,1% of each individual BRAM block. From Table 2 we observe that the IST of Single Write IBDA sees a reduction of 2330 LUTs and 280 flip-flops compared to Original IBDA. 256 of the flip-flops are saved in the LVTs which no longer must store 2 bits per entry. The LUT reduction is also due to the decrease of the number of BRAMs, which reduces the need for glue logic and number of compare operations for lookups.

Single Write IBDA's RDT uses four BRAMs, two for each duplicate RDT due to the two write ports. Each RDT has 80 entries of 40 bits which gives us a utilization of 8.9 % of the BRAM. The Original IBDA RDT has 16 BRAMs with the same utilization. The Single Write IBDA RDT shows a reduction of 434 LUTs and 145 flip-flops. Of the flip-flops 124 are saved in the LVT. The LUTs are saved by reducing the number of duplicate SRAMs and the needed glue logic.

Clearly, a reduction in the number of write-ports from RDT to IST leads to massive improvement in the area used by IBDA. Furthermore, power consumption will also decrease accordingly.

## 5.2.2 Going Fuzzy

Compared to Single Write IBDA, the instruction tags are reduced from 40 bits to 14 bits, and the additional FTQ ports are removed. However, looking at Table 3 we see that Fuzzy IBDA still uses 4 BRAMs for the RDT, which is the same as Single Write IBDA. What is not shown is that the utilization of each BRAM should be more than halved. For the IST, the synthesis tool has chosen to use LUTRAMs instead of BRAMs. This is because the utilization of each BRAM would have been so low. In total Fuzzy IBDA will use only 35 % of the BRAM that Single Write IBDA uses, which gives a total reduction of 91 % compared to Original IBDA. Fuzzy IST shows a reduction of 2446 LUTs and 438 flip-flops compared to Original IBDA. 128 of the flip-flops are saved because the valid bits can be removed, as it is already fuzzy. However, Fuzzy IST needs additional 28 flip-flops to implement synchronous reads from the LUTRAMs.

The reduction in LUTs is likely stemming from reduced width of the combinational operations. E.g. to do an IST look-up a compare operation between the look-up value, and the value found in the IST, has to be done. Such a comparison could be implemented as a tree of XOR gates, each implemented as a LUT. LUTs have at maximum six inputs, which means that each LUT can compare 3 bits of the value. Going from 40 bits to 14 bits would reduce the a straightforward compare implementation from 20 LUTs to 6 LUTs. The binary hash matrix is implemented as 125 LUTs.

For the RDT, Fuzzy IBDA sees a reduction of 70 LUTs and 25 flip-flops. The RDT contains two bypass register, so we would actually expect a twice as big reduction in flip-flops. The RDT also contains a copy of the binary hash matrix using 125 LUTs.

Fuzzy IBDA also sees a reduction of 48 LUTRAMs in the instruction fetch unit (IFU), compared to Original IBDA and Single Write IBDA. This is because Fuzzy IBDA uses the instruction bits rather than the PC. Original IBDA needs an additional read port to the FTQ which causes a duplication in the LUTRAMs used for it.

To conclude, Fuzzy IBDA contributes to a significant reduction in all structures used.

#### 5.2.3 Bloom IBDA

The Bloom IBDA represents an alternative fuzzy implementation. The main benefit being that the set associative cache can be replaced with a much simpler bit vector. Table 3 shows that the Bloom IST uses 24 BRAMs. It uses 6 hash functions each with a 2048-entry bit-vector. Since we have 2 read ports, one for each core-width, we need to duplicate that. In total Bloom IST stores 24576 bits, which is about a 40 % decrease compared to Original IBDA. Bloom IST has a reduction of 526 flip-flops compared to Original IST. This is largely due to the 64 flip-flops needed for the LRU and 128 flip-flops used for valid bits. In total Bloom IST needs 65 more LUTS than Single Write IBDA. The Bloom RDT stores the 38 bit input to its hash function, consisting of the instruction word and pc\_lob. This makes the BRAM, LUT and flip-flop usage of Bloom RDT more or less equal that of Single Write IBDA.

Bloom IBDA sees the same reduction in LUTRAMs used in the IFU as Fuzzy IBDA. This is also due to the removal of a read port to the FTQ.

In conclusion, for applications where the working set can be sufficiently large, using a Bloom

filter gets too costly compared to a set associative cache.

## 5.3 Precise IBDA

This section will discuss some scenarios where the Original IBDA is imprecise, i.e. can get false positive hits in the IST. A Precise IBDA is an implementation where no instructions are mistakenly identified as part of a program slice when they are not.

First we will look at what could happen after an address space switch, before we will look at how speculation can affect IBDA. We also discuss a potential solution to this problem, namely moving the RDT.

#### 5.3.1 Address Space Switches

If a processor uses virtual memory, two different processes can use the same virtual address range for their instructions. The physical address-range is different and translated by the translation lookaside buffer. If the IST is kept unchanged for an address space switch, the new process will potentially get false positives when looking up the addresses of its instructions and finding hits from completely different instructions using the same address, but added by a different process. In order to maintain correctness of IBDA we propose to flush the IST on context switches. This can be done by clearing the valid bits implemented as registers. The RDT typically does not require any flushing. If the register file (RF) is restored to the state of the previous time the process was executing by loading values from the stack, the RDT will be updated to reflect the new dependencies, which will all originate from the loads that restored the RF.

#### 5.3.2 Speculative Execution

Speculative execution can lead to the execution of unintended instruction sequences. Listing 5.1 shows a sequence of instructions that could cause this. The branch is always taken, so that the load depends on li a5, 5. If it is speculated as not being taken, a false dependency from the load to li a5, 10 will appear. This dependency is false in the sense that it never appears when executing the program. It could, however, also be marked as a dependency when static analysis tools are used.

Listing 5.1: Example of a program that could add instructions to the slice due to speculative execution

```

start:

li a0, 10

li a5, 10

beq a0, a5, branch

load:

lw a4, 0(a5)

j end

branch:

li a5, 5

j load

end:

```

To solve the issue of speculative IBDA, we must either roll back the state of the IST and RDT on a misspeculation, or we must hold off updating the RDT and IST until instructions are no longer speculative. Doing a rollback would be very costly and could require keeping duplicate ISTs and RDTs for checkpoints. On speculation, a new duplicate of the IST and RDT would be used. On a misspeculation a single cycle reset could be done, by starting off from the appropriate check point.

#### 5.3.3 Moving the RDT

Avoiding speculation altogether seems like a more attractive solution. This is easily achieved by moving the RDT lookup to the commit stage. Instructions only reach the commit stage once its guaranteed that they are in fact part of the program. Since there is no speculation, the logical register specifiers, of which there are only 32 in RISC-V, can be used. The main drawback is that there are potentially many cycles between the IST lookup and the RDT lookup. This can lead to duplicates in the IST in tight loops. Consider the first iteration through a tight loop with a load slice. None of the instructions will be in the IST and thus not be marked as part of the slice. If multiple iterations through the tight loop can fit in the instruction window there will be multiple copies of the same instruction, none marked as part of the slice. When the first instructions reach commit, they will update the RDT and be added to the IST. However, when the next iteration of the same instructions arrive they will also be marked as not present in the IBDA. So for Single Write IBDA to be compatible with moving the RDT it must implement a read-before-write policy in the IST.

# 6 Conclusion

In this part we have presented the first, to our knowledge, RTL implementation and in-depth evaluation of IBDA in terms of size and application performance. We also include three different optimizations for IBDA. Single Write IBDA, Fuzzy IBDA and Bloom IBDA. Our evaluation shows that Fuzzy IBDA will only use a fraction of the original area, while delivering almost the same performance. While Bloom IBDA is an interesting concept, it suffers from poor performance in some cases and has no size-benefit over Fuzzy IBDA.

# Part II

# **FIFO-based Instruction Scheduling**

# 7 Background

This chapter will introduce the fundamental concepts needed for creating register-transfer level (RTL) implementations of novel instruction scheduling techniques on a modern out-of-order core. We start by laying the theoretical framework for instruction scheduling by looking at in-order and out-of-order instruction scheduling. The additional modules needed to support out-of-order scheduling, e.g. the reorder buffer and Register Renaming, are also introduced. Then we look at the recent computer architecture research tools enabling the RTL implementation of these techniques. We introduce the RISC-V instruction set architecture (ISA), the hardware construction language Chisel, BOOM and Rocket, two cores written in Chisel, and the Chipyard system-on-chip (SoC) framework. Lastly, we introduce three novel instruction scheduling techniques found in the Load Slice Core, Delay and Bypass, and CASINO.

## 7.1 Instruction Scheduling

Instruction scheduling is one of the key techniques for extracting instruction-level parallelism (ILP) and memory-level parallelism (MLP) from a program. Since program binaries are expected to run on different microarchitectures sharing the same ISA, dynamic hardware scheduling is used in addition to static software scheduling. ILP is a measure of how many instructions of a program could be executed in parallel because they are independent. It is a measure of how many memory operations, i.e. loads and stores, can overlap. MLP is an important subset of ILP, since memory latency is one of the key limitations of computer performance [34].

#### 7.1.1 In-Order Scheduling

In-order scheduling is the simplest form of hardware scheduling and is also called static scheduling. A static scheduler does not rearrange the order of the instructions as specified in the binary. The programmer, or compiler, has complete control over the order in which the instructions propagate through the pipeline. Many hazards can be avoided if the details of the target pipeline architecture are known at compile-time. The main advantages of static instruction scheduling is its low hardware complexity.

The simplest in-order processors use static instruction scheduling. These kinds of processors have to wait until an instruction finishes execution for the next instruction to execute. If, for example, a cache miss happens, and a load has to go to the main memory, the whole pipeline stalls and no other instructions can execute. More advanced stall on use in-order processors provide higher performance while still being mostly in order. They achieve this by allowing the execution phases of instructions to overlap. In the example above other independent instructions can be issued by such a processor. A method that is commonly used for this is called scoreboarding. A scoreboard keeps track of instruction dependencies and issues instructions in-order, as soon as their dependencies are

met. It also ensures that instructions retire in the right order, even if their execution phases might end out of order. Furthermore, this approach allows issuing instructions to multiple execution units at the same time, leading to super scalar designs [35]. The pipeline has to stall if an instruction depends on another instruction that has not finished execution or targets a non-pipelined execution unit currently in use. Another source of conflicts are write-after-write dependencies between instructions with the same target register.

#### 7.1.2 Out-of-Order Scheduling