Mathilde Bergerskogen

## Design Considerations and Modeling of a VSC Assisted Resonant Current DC Circuit Breaker for MVDC Applications

Master's thesis in Energy and Environmental Engineering Supervisor: Dimosthenis Peftitsis June 2020

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Mathilde Bergerskogen

## Design Considerations and Modeling of a VSC Assisted Resonant Current DC Circuit Breaker for MVDC Applications

Master's thesis in Energy and Environmental Engineering Supervisor: Dimosthenis Peftitsis June 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

## **Preface and Acknowledgment**

This master's thesis completes my MSc degree in Energy and Environmental Engineering at the Norwegian University of Science and Technology (NTNU). It has been carried out at the Department of Electric Power Engineering during the spring semester of 2020. The thesis investigates the voltage source converter assisted resonant current circuit breaker (VARC-CB) for medium-voltage DC (MVDC) applications. The VARC-CB was found to be a particularly interesting and promising concept when studying different MVDC circuit breaker designs in my specialization project work [1] during the fall semester of 2019.

I would like to thank my supervisor, Associate Professor Dimosthenis Peftitsis, for providing guidance and valuable input throughout my work, and for pushing and motivating me. I would also like to express my gratitude to my co-supervisor, PhD Candidate Andreas Giannakis, for always being available for questions and discussion, for believing in my work, and for spending numerous of hours helping me with my simulation model. I am also grateful to Professor Kaveh Niayesh for showing interest in my project, and for providing me with insights into the area of vacuum interrupters.

I would like to thank my mom and brother for great support and patience, in particular during my final week of thesis writing. I would also like to thank my fellow students at NTNU, who have made my years in Trondheim unforgettable. A particular thanks goes to Mona Martinsen and Nina Lindholm for being fantastic flatmates during the special and challenging spring 2020 semester. Finally, a huge thanks goes to Sigrid Sollie Kornstad for great help with proofreading my thesis.

Mathilde Bergerskogen

Mathilde Bergerskogen Oslo, June 2020

## Abstract

Medium-voltage DC (MVDC) power grids offer many beneficial features compared to the medium-voltage AC (MVAC) counterpart, and are considered well-suited for a wide range of application areas. However, one of the main hindrances towards a widespread of MVDC power grids is associated with the handling of short-circuit (SC) faults. In particular, the lack of high-performance MVDC circuit breakers (CBs) is a key challenge. To address this barrier, the main purpose of this master's thesis is to investigate a particularly interesting and promising DC circuit breaker (DCCB) concept: the voltage source converter (VSC) assisted resonant current circuit breaker (VARC-CB). The VARC-CB is originally proposed for high-voltage DC (HVDC), however this thesis investigates the VARC-CB concept for MVDC applications.

The thesis studies and analyzes the MVDC VARC-CB in detail. A thorough theoretical foundation is given, exploring MVDC power grids and their SC fault protection. Furthermore, operating principles, features, and subcomponents of a variety of DCCB concepts suggested in literature are examined, with a special focus on the VARC-CB. This creates a basis for the subsequent in-depth analytical investigation of the MVDC VARC-CB. The analysis takes several design principles and component limitations into account, upon which a full set of design strategies are derived. Furthermore, a complete, parameterized Simulink<sup>®</sup> simulation model of the VARC-CB concept employed in an MVDC power grid is developed, where the component-level model of the MVDC VARC-CB is parameterized using the derived design equations. Through simulations, the analytical investigations, the proposed design strategies, and the developed simulation model are validated. Weaknesses and shortcomings of the analysis and modeling processes are pointed out and discussed, and possible revisions are proposed. In addition, suggestions of improvements in the MVDC VARC-CB design are made.

The main contributions of this thesis are a complete set of design strategies to be used when designing the parameters of the MVDC VARC-CB, a Simulink model of the VARC-CB employed in an MVDC grid, and suggestions of possible improvements in the MVDC VARC-CB design.

## Sammendrag

Mellomspente likestrømsnett (MVDC-nett) har mange fordeler sammenlignet med mellomspente vekselstrømsnett (MVAC-nett), og betraktes som velegnet til et bredt spekter av bruksområder. Håndteringen av kortslutningsfeil er imidlertid et av de viktigste hindrene for utbredelsen av MVDC-nett; spesielt er mangelen på MVDC-effektbrytere en fundamental utfordring. Hovedhensikten med denne masteroppgaven er å adressere denne barrieren ved å undersøke et spesielt interessant og lovende effektbryterkonsept: Spenningskildeomformerassistert resonansstrømeffektbryter (VARC-CB). Effektbryteren er opprinnelig foreslått for høyspente DC (HVDC)-applikasjoner, men denne avhandlingen utforsker VARC-CB-konseptet for MVDC-bruk.

Avhandlingen studerer og analyserer VARC-CB-konseptet for MVDC i detalj. Først legges et teoretisk fundament for oppgaven ved å utforske MVDC-nett og beskyttelsen mot kortslutningsfeil i disse. Videre utforskes et utvalg effektbryterkonsepter for MVDC fra litteraturen, inkludert konseptenes virkemåter, karakteristikker og delkomponenter, med et særlig fokus på VARC-bryteren. Dette danner grunnlaget for den påfølgende analytiske undersøkelsen av VARC-CB-konseptet for MVDC. I analysen utledes et fullstendig sett med designstrategier basert på etablerte designprinsipper og -begrensninger. Videre utvikles en komplett, parametrisert Simulink<sup>®</sup>-simuleringsmodell, hvor VARCbryteren opererer i et MVDC-nett. Effektbryterens komponentmodell er parametrisert ved å bruke de utledede designligningene. Deretter valideres den utførte analysen, de foreslåtte designstrategiene og den utviklede simuleringsmodellen gjennom simuleringer. Basert på resultatene blir svakheter og mangler ved analyse- og modelleringsprosessene påpekt og diskutert, og mulige revisjoner blir vurdert. Potensielle forbedringer av VARC-CB-konseptet blir også foreslått.

Masteroppgavens hovedbidrag er et komplett sett med designstrategier som kan brukes til å designe parameterne til VARC-effektbryteren for MVDC, en Simulink-modell av effektbryteren i et MVDC-nett, samt forslag til mulige forbedringer av VARC-CB-konseptet.

## Table of Contents

| Pr | eface                      | and Acknowledgment                                                                                                                                                                                                                   | i                            |

|----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Ab | ostrac                     | t                                                                                                                                                                                                                                    | ii                           |

| Sa | mmei                       | ndrag                                                                                                                                                                                                                                | iii                          |

| Ta | ble of                     | f Contents                                                                                                                                                                                                                           | vii                          |

| Li | st of T                    | Tables                                                                                                                                                                                                                               | viii                         |

| Li | st of H                    | Figures                                                                                                                                                                                                                              | xi                           |

| Ab | obrevi                     | iations                                                                                                                                                                                                                              | xii                          |

| 1  | Intro<br>1.1<br>1.2<br>1.3 | oduction         Background and Perspective         Objectives         Report Outline                                                                                                                                                | 1<br>1<br>2<br>3             |

| 2  | <b>Theo</b> 2.1 2.2        | MVDC Power Grids                                                                                                                                                                                                                     | <b>4</b><br>5<br>5<br>6<br>6 |

|    | 2.2                        | 2.2.1       Three Methods for DC Fault Interruption         2.2.2       Basic DCCB Operating Principles and Requirements         2.3.1       Conventional Mechanical AC Circuit Breakers         2.3.1.1       The Insulating Medium | 6<br>7<br>9<br>9<br>10       |

|    |                            | <ul><li>2.3.1.2 Arc Extinction and Current Interruption</li></ul>                                                                                                                                                                    | 10<br>12                     |

|   |     | 2.3.2    | Ultra-Fast Disconnectors                                   |

|---|-----|----------|------------------------------------------------------------|

|   | 2.4 | The M    | letal-Oxide Varistor                                       |

|   |     | 2.4.1    | Equivalent Circuit                                         |

|   |     | 2.4.2    | Metal-Oxide Varistor Applications                          |

|   | 2.5 |          | rcuit Breakers Presented in Literature                     |

|   |     | 2.5.1    | Mechanical DC Circuit Breakers                             |

|   |     | 2.5.2    | Solid-State DC Circuit Breakers                            |

|   |     | 2.5.3    | Hybrid DC Circuit Breakers                                 |

|   |     | 2.5.4    | Choice of DCCB Concept for Further Study                   |

| 3 | Ope | rating I | Principles of the MVDC VARC-CB 22                          |

| - | 3.1 |          | er Topology                                                |

|   | 3.2 |          | ting Principles and Timing Sequence                        |

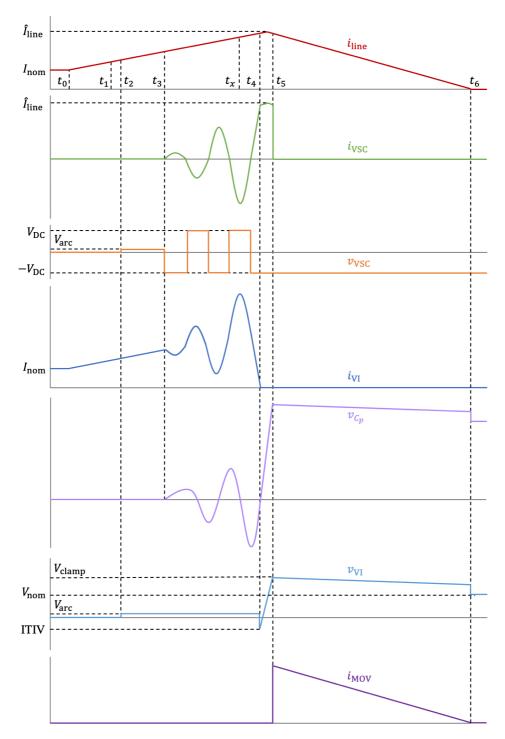

|   |     | 3.2.1    | Before $t_0$ : Steady State and Charging of the DC Link 25 |

|   |     | 3.2.2    | $t_0$ : Fault Inception                                    |

|   |     | 3.2.3    | $t_0-t_1$ : Relay Time                                     |

|   |     | 3.2.4    | $\mathbf{t_1}$ - $\mathbf{t_2}$ : VI Actuation Delay       |

|   |     | 3.2.5    | $t_2-t_3$ : VI Opening, VSC Not yet Activated              |

|   |     | 3.2.6    | $t_3-t_4$ : VSC Switching                                  |

|   |     | 3.2.7    | $t_4-t_5$ : Charging of $C_p$                              |

|   |     | 3.2.8    | $t_5-t_6$ : MOV Operation                                  |

|   |     | 3.2.9    | $t_6$ : Line Current Zero                                  |

|   |     |          |                                                            |

| 4 |     | •        | Investigation and Design of the MVDC VARC-CB 31            |

|   | 4.1 | -        | 1 Goals                                                    |

|   | 4.2 |          | 1 System                                                   |

|   | 4.3 | -        | 1 Strategies                                               |

|   |     | 4.3.1    | The Current-Limiting Inductor                              |

|   |     | 4.3.2    | The Voltage Source Converter                               |

|   |     |          | 4.3.2.1 The Switching/Resonance Frequency                  |

|   |     |          | 4.3.2.2 The Power Semiconductor Switches                   |

|   |     |          | 4.3.2.3 The DC Link                                        |

|   |     |          | 4.3.2.4 The Charging Circuit                               |

|   |     | 4.3.3    | The Metal-Oxide Varistor 39                                |

|   |     | 4.3.4    | The Vacuum Interrupter    41                               |

|   |     |          | 4.3.4.1 The Opening Time                                   |

|   |     |          | 4.3.4.2 The di/dt Capability                               |

|   |     |          | 4.3.4.3 The dv/dt Capability                               |

|   |     | 4.3.5    | Summary of the Design Strategies for the MVDC VARC-CB 49   |

| 5 | Mod | leling a | nd Parameterization of the MVDC VARC-CB 51                 |

|   | 5.1 |          | are Considerations                                         |

|   | 5.2 |          | ation Model                                                |

|   | 5.3 |          | Grid Modeling and Parameterization                         |

|   |     | 5.3.1    | Nominal Voltage, Current and Load                          |

|   |     | 5.3.2    | Range of Interruption Currents                             |

|   |     |          | -                                                          |

| Bi<br>A | мо                       | V Mode         | el Parameterization                                                                                                                                                                | 103                   |

|---------|--------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Bi      | -                        |                |                                                                                                                                                                                    |                       |

|         | bliogr                   | aphy           |                                                                                                                                                                                    | 94                    |

| 7       | <b>Con</b><br>7.1<br>7.2 | Conclu         | and Further Work         usion            vr Work                                                                                                                                  | <b>90</b><br>90<br>93 |

| _       | G                        | 6.4.5          | 6.4.4.2 Ensuring Favorable VI Interruption Conditions System Modeling and RRITIV Considerations                                                                                    | 85<br>87              |

|         |                          | 6.4.4          | Possible Improvement: Adjustment of VSC Triggering Instant $\dots$<br>6.4.4.1 Minimizing $t_{VSC,delay}$                                                                           | 84<br>84              |

|         |                          | 6.4.2<br>6.4.3 | 6.4.1.2 Number of Switching Operations in Case 1 and in Case 3<br>Estimated vs. Simulated $v_{DC}$ and $i_{VSC}$ Dynamics Possible Improvement: Auxiliary Passive Resonant Circuit | 78<br>80<br>81        |

|         |                          | 6.4.1          | Comparison of Results from the Three Simulation Cases 6.4.1.1 VI Interruption Conditions in Case 1 and in Case 2                                                                   | 76<br>77              |

|         | 6.4                      | Discus         | ssion                                                                                                                                                                              | 76                    |

|         | 6.3                      |                | B: Interrupting Reverse Fault Current                                                                                                                                              | 74                    |

|         | 6.2                      |                | 2: Interrupting Nominal Load Current                                                                                                                                               | 72                    |

| 6       | <b>Sim</b> u<br>6.1      |                | <b>Results and Discussion</b><br>: Interrupting a Terminal Fault                                                                                                                   | <b>66</b><br>67       |

|         | 5.9                      |                | ling and Parameterization of the Current-Limiting Inductor                                                                                                                         | 65                    |

|         |                          | 5.8.0<br>5.8.7 | Parameterization Overview                                                                                                                                                          | 65                    |

|         |                          | 5.8.5<br>5.8.6 | Switch Positions                                                                                                                                                                   | 63<br>63              |

|         |                          | 5.8.4          | Passive Resonant Circuit                                                                                                                                                           | 62                    |

|         |                          | 5.8.3          | Charging Circuit                                                                                                                                                                   | 61                    |

|         |                          | 5.8.2          | DC Link                                                                                                                                                                            | 61                    |

|         |                          | 5.8.1          | Switching Frequency                                                                                                                                                                | 61                    |

|         | 5.8                      |                | ing and Parameterization of the Current Injection Branch                                                                                                                           | 60                    |

|         | 5.7                      |                | Modeling and Parameterization                                                                                                                                                      | 60                    |

|         |                          | 5.6.4          | Overview of VI Parameterization                                                                                                                                                    | 59                    |

|         |                          | 5.6.3          | Current Chopping                                                                                                                                                                   | 59                    |

|         |                          | 5.6.2          | di/dt- and dv/dt Capabilities                                                                                                                                                      | 59                    |

|         | 5.0                      | 5.6.1          |                                                                                                                                                                                    | 58                    |

|         | 5.5<br>5.6               |                | Ing and Parameterization of the Energy Absorption Branchodeling and Parameterization                                                                                               | 54<br>56              |

|         | 5.4                      |                | Circuit Fault Modeling and Parameterization                                                                                                                                        | 54<br>54              |

|         |                          | 5.3.5          | Overview of Power Grid Parameters                                                                                                                                                  | 54                    |

|         |                          | 5.3.4          | Equivalent Stray Capacitance                                                                                                                                                       | 54                    |

|         |                          | 5.3.3          | DC Line                                                                                                                                                                            | 53                    |

| С | Final Model Parameterization       | 107 |

|---|------------------------------------|-----|

| D | Auxiliary Passive Resonant Circuit | 109 |

## List of Tables

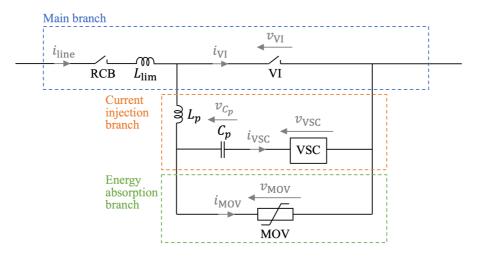

| 3.1 | Operation sequence of the VARC-CB during a typical fault current inter-<br>ruption process, as presented in Figure 3.3. | 25  |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Power grid parameter values for the system in Figure 5.1                                                                | 54  |

| 5.2 | MOV parameter values                                                                                                    | 56  |

| 5.3 | Values of the VI parameters and the timing aspects related to the VI                                                    | 59  |

| 5.4 | Parameter values related to the current injection branch                                                                | 65  |

| 6.1 | Key parameter values from case 1: Interrupting a terminal fault                                                         | 71  |

| 6.2 | Key parameter values from case 2: Interrupting nominal load current                                                     | 74  |

| 6.3 | Key parameter values from case 3: Interrupting reverse fault current                                                    | 76  |

| C.1 | Final parameterization of the simulation model.                                                                         | 107 |

## List of Figures

| 2.1<br>2.2 | Simplified DC system experiencing an SC fault                                                                                                      | 7  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | 2.1.                                                                                                                                               | 7  |

| 2.3        | Typical terminal voltage (blue) and arc current (red) waveforms of an                                                                              |    |

|            | ACCB around the moment of interruption.                                                                                                            | 11 |

| 2.4        | Illustrative curves showing the capability curve (black) of a theoretical ACCB, together with the TRV (blue) applied across the breaker terminals, |    |

|            | and a line representing the RRRV (orange).                                                                                                         | 12 |

| 2.5        | Typical static V-I characteristics of a high-pressure arc.                                                                                         | 13 |

| 2.6        | MOV: (a) Symbol, (b) Typical MOV V-I curve plotted on log-log scale                                                                                | 14 |

| 2.7        | Equivalent circuit of an MOV.                                                                                                                      | 15 |

| 2.8        | Mechanical DC circuit breaker with passive/active current injection.                                                                               | 16 |

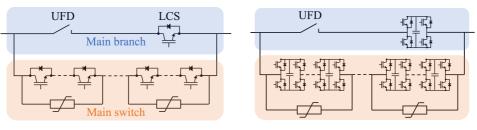

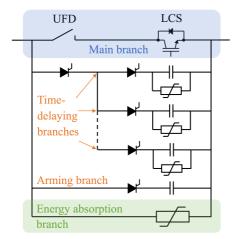

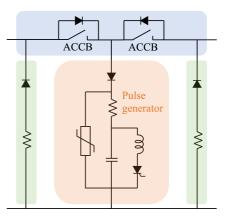

| 2.9        | Various HCB topologies suggested in literature.                                                                                                    | 19 |

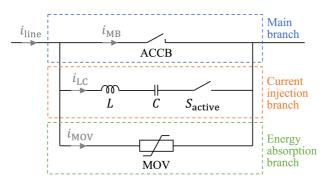

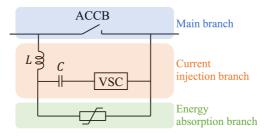

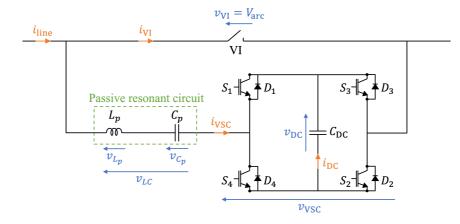

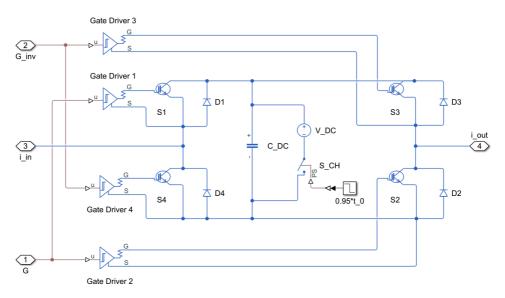

| 3.1        | Topology of the MVDC VARC-CB module.                                                                                                               | 23 |

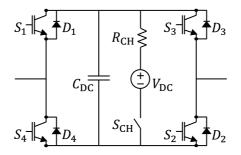

| 3.2        | Structure of the VSC in the VARC-CB topology.                                                                                                      | 23 |

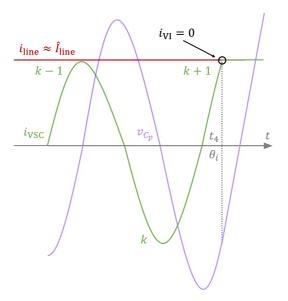

| 3.3        | Current and voltage waveforms illustrating the operation of the VARC-CB.                                                                           | 24 |

| 3.4        | The loop formed by the VI and the current injection branch                                                                                         | 27 |

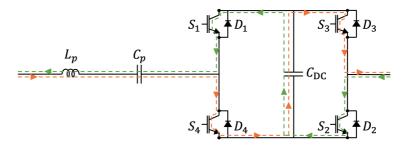

| 3.5        | Current flow in the current injection branch during VSC switching                                                                                  | 28 |

| 4.1        | Design system.                                                                                                                                     | 32 |

| 4.2<br>4.3 | Worst case scenario for the maximum $ v_{C_p} $ value prior to $t_4$ The course of the VI voltage (blue curve) immediately after $t_4$ during a    | 40 |

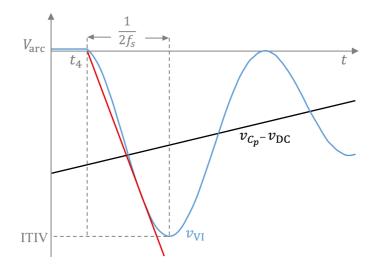

| 1.5        | terminal fault. The red line indicates the RRITIV.                                                                                                 | 47 |

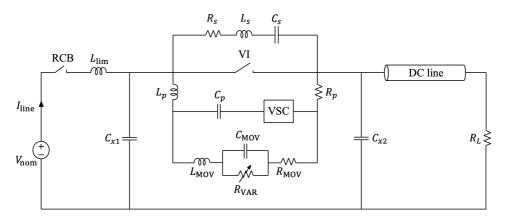

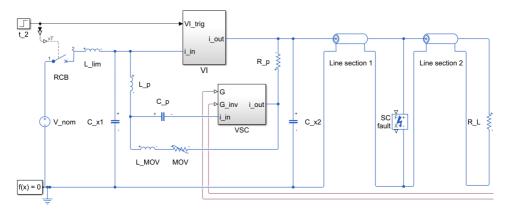

| 5.1        | Simulation model of the system.                                                                                                                    | 52 |

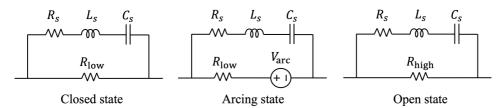

| 5.2        | Operating states of the electrical model of the VI                                                                                                 | 56 |

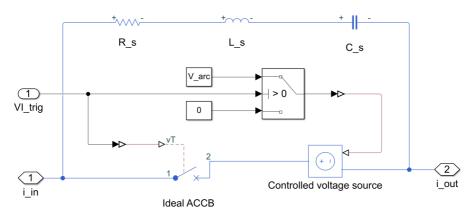

| 5.3        | Simulation model of the VI.                                                                                                                        | 57 |

| 5.4        | Simulation model of the VSC.                                                                                                                       | 60 |

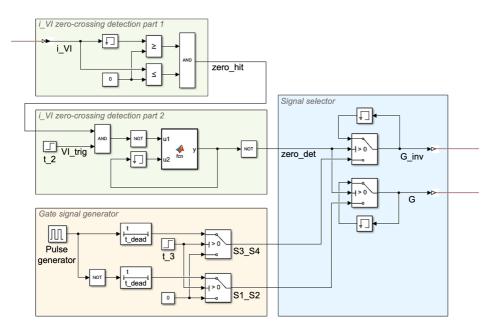

| 5.5        | Circuitry for generation and control of the gate signals provided to the VSC switches.                                                             | 64 |

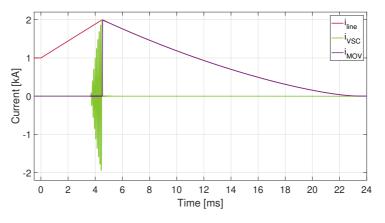

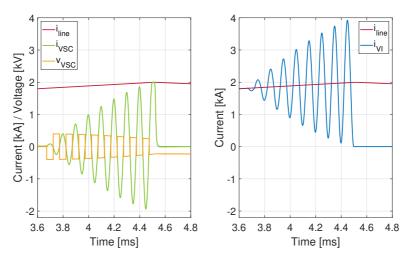

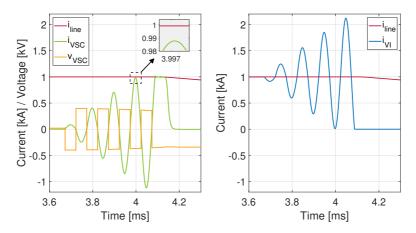

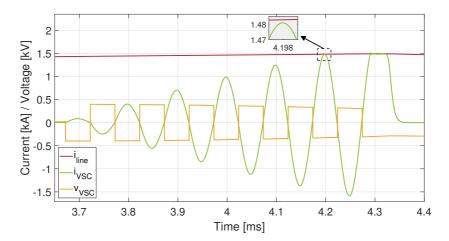

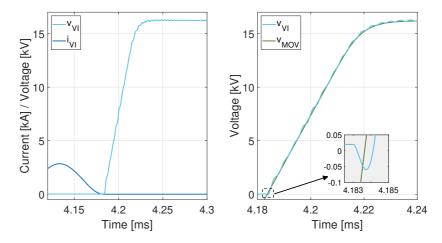

| 6.1         | Line, VSC, and MOV currents during a terminal fault                                                                                        | 67  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2         | Line current, VSC current, and VI voltage during a terminal fault                                                                          | 68  |

| 6.3         | Terminal fault. Left: Line current, VSC current, and VSC voltage. Right:                                                                   |     |

|             | Line and VI currents.                                                                                                                      | 68  |

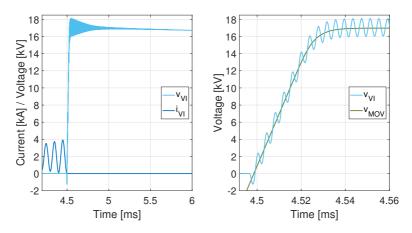

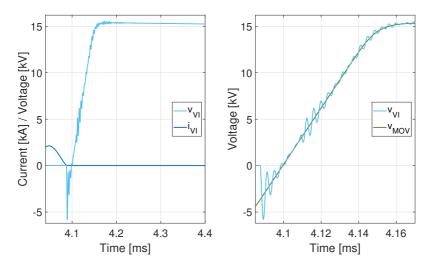

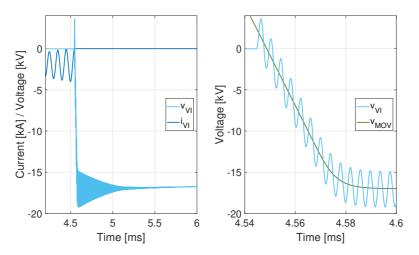

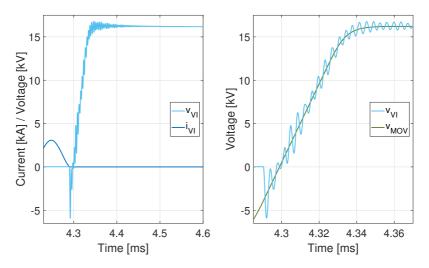

| 6.4         | Terminal fault. Left: VI voltage and current. Right: VI and MOV voltages.                                                                  | 69  |

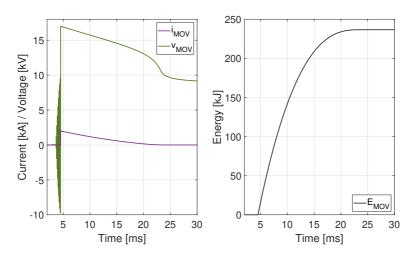

| 6.5         | Terminal fault. Left: MOV current and voltage. Right: Energy absorption                                                                    |     |

|             | of the MOV                                                                                                                                 | 70  |

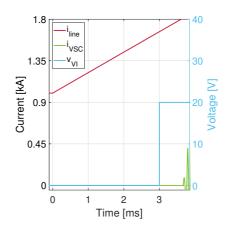

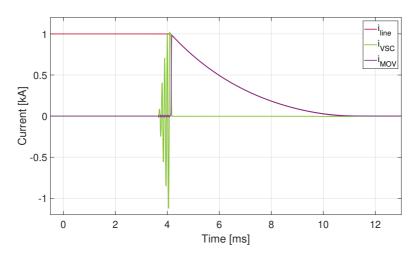

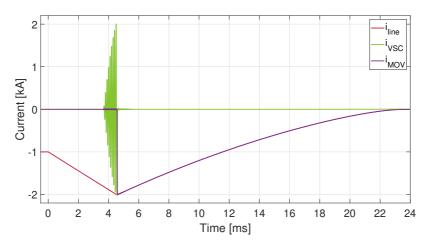

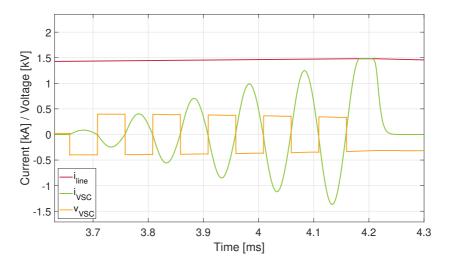

| 6.6         | Line, VSC, and MOV currents during interruption of nominal load current.                                                                   | 72  |

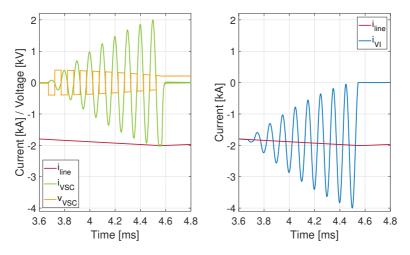

| 6.7         | Nominal load current interruption. Left: Line current, VSC current, and                                                                    |     |

|             | VSC voltage. Right: Line and VI currents.                                                                                                  | 72  |

| 6.8         | Nominal load current interruption. Left: VI voltage and current. Right:                                                                    |     |

|             | VI and MOV voltages.                                                                                                                       | 73  |

| 6.9         | Line, VSC, and MOV currents during a terminal fault with reverse fault                                                                     |     |

|             | current                                                                                                                                    | 74  |

| 6.10        | Terminal fault with reverse fault current. Left: Line current, VSC current,                                                                |     |

|             | and VSC voltage. Right: Line and VI currents.                                                                                              | 75  |

| 6.11        | Terminal fault with reverse fault current. Left: VI voltage and current.                                                                   |     |

|             | Right: VI and MOV voltages                                                                                                                 | 75  |

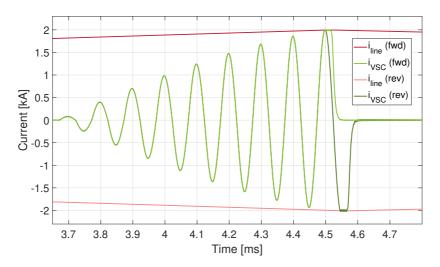

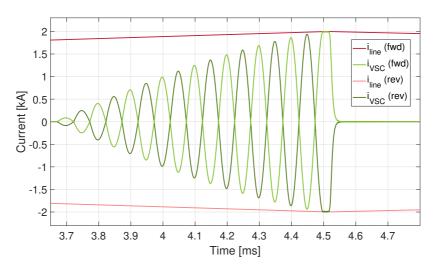

| 6.12        | Line currents and VSC currents from case 1 (fwd) and case 3 (rev)                                                                          | 78  |

|             | Line currents and VSC currents from case 1 (fwd) and case 3 (rev), with                                                                    |     |

|             | the case 3 simulation now using opposite gate signals compared to case 1.                                                                  | 79  |

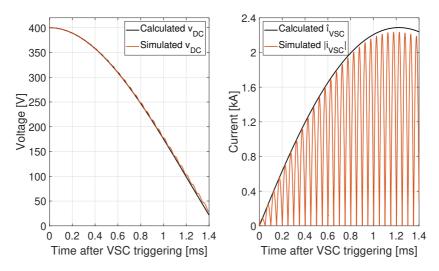

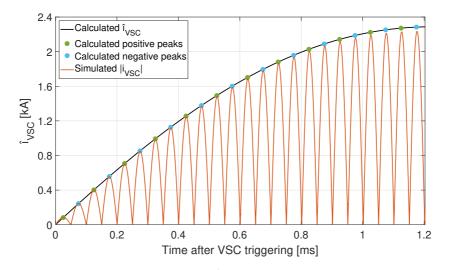

| 6.14        | Left: Calculated and simulated trajectories for $v_{DC}$ . Right: Calculated                                                               |     |

|             | trajectory for $\hat{i}_{VSC}$ , and simulated waveform of $ i_{VSC} $ .                                                                   | 80  |

| 6.15        | Line current, VSC current, and VSC voltage during mid-point fault with                                                                     |     |

|             | fault impedance 6.2 $\Omega$ .                                                                                                             | 83  |

| 6.16        | Mid-point fault with fault impedance 6.2 $\Omega$ . Left: VI voltage and VI cur-                                                           |     |

|             | rent. Right: VI and MOV voltages.                                                                                                          | 83  |

| 6.17        | Black: Calculated trajectory for $\hat{i}_{VSC}$ . Dots: Estimated peaks of $i_{VSC}$ .                                                    |     |

|             | Orange: Simulated $ i_{VSC} $ waveform.                                                                                                    | 85  |

| 6.18        | Results from simulation with adjusted $t_{VSC,delay}$ , simulating a mid-point                                                             |     |

|             | fault with fault impedance 6.2 $\Omega$ : Line current, VSC current, and VSC                                                               |     |

|             | voltage.                                                                                                                                   | 86  |

| 6.19        | Results from simulation with adjusted $t_{VSC,delay}$ , simulating a mid-point                                                             |     |

|             | fault with fault impedance 6.2 $\Omega$ . Left: VI voltage and VI current. Right:                                                          |     |

|             | VI and MOV voltages.                                                                                                                       | 87  |

|             |                                                                                                                                            |     |

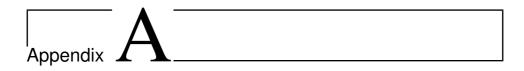

| A.1         | V-I characteristics of the BB series MOVs from Littelfuse                                                                                  | 103 |

| A.2         | Parameterization of the Varistor block representing the developed MOV                                                                      |     |

|             | module                                                                                                                                     | 104 |

|             |                                                                                                                                            |     |

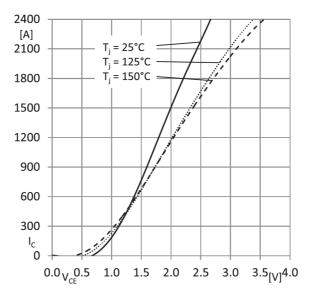

| <b>B</b> .1 | SEMIKRON SKM1200ML112TE4 IGBT1 output characteristics $I_C = f(V_C)$                                                                       | ·   |

|             | $V_{GE} = 15 \text{ V}, \dots \dots$ | 105 |

| B.2         | Parameterization of the N-Channel IGBT blocks representing the IGBTs                                                                       |     |

|             | of the VSC                                                                                                                                 | 106 |

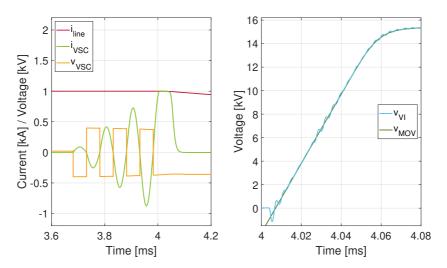

| D.1 | Simulating case 2 with the proposed auxiliary LC circuit of $Z_{LC}$ = 4.7 $\Omega$ . |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | Left: Line current, VSC current, and VSC voltage. Right: VI and MOV                   |     |

|     | voltages                                                                              | 109 |

## Abbreviations

| AC     | = | Alternating Current                                        |

|--------|---|------------------------------------------------------------|

| ACCB   | = | Alternating Current Circuit Breaker                        |

| BESS   | = | Battery Energy Storage System                              |

| BIGT   | = | Bi-Mode Insulated Gate Transistor                          |

| CB     | = | Circuit Breaker                                            |

| DC     | = | Direct Current                                             |

| DCCB   | = | Direct Current Circuit Breaker                             |

| DER    | = | Distributed Energy Resources                               |

| ESR    | = | Equivalent Series Resistance                               |

| EV     | = | Electric Vehicle                                           |

| FB-HCB | = | Full-Bridge Based Hybrid Circuit Breaker                   |

| HCB    | = | Hybrid Circuit Breaker                                     |

| HV     | = | High-Voltage                                               |

| HVDC   | = | High-Voltage Direct Current                                |

| IEEE   | = | Institute of Electrical and Electronics Engineers          |

| IGBT   | = | Insulated Gate Bipolar Transistor                          |

| IGCT   | = | Integrated Gate-Commutated Thyristor                       |

| ITIV   | = | Initial Transient Interruption Voltage                     |

| LCS    | = | Load Commutation Switch                                    |

| MCB    | = | Mechanical Circuit Breaker                                 |

| MOSFET | = | Metal-Oxide Semiconductor Field Effect Transistor          |

| MOV    | = | Metal-Oxide Varistor                                       |

| MS     | = | Mechanical Switch                                          |

| MV     | = | Medium-Voltage                                             |

| MVAC   | = | Medium-Voltage Alternating Current                         |

| MVDC   | = | Medium-Voltage Direct Current                              |

| NTNU   | = | Norwegian University of Science and Technology             |

| P-HCB  | = | Proactive Hybrid Circuit Breaker                           |

| PV     | = | Photovoltaic                                               |

| PG-HCB | = | Hybrid Circuit Breaker with Pulse Generator                |

| RCB    | = | Residual Current Breaker                                   |

| RRDS   | = | Rate of Rise of the Dielectric Strength                    |

| RRITIV | = | Rate of Rise of the Initial Transient Interruption Voltage |

| RRRV   | = | Rate of Rise of the Transient Recovery Voltage             |

| RRTIV  | = | Rate of Rise of the Transient Interruption Voltage         |

| SC     | = | Short-Circuit                                              |

| SCR    | = | Silicon-Controlled Rectifier                               |

| $SF_6$ | = | Sulfur Hexafluoride                                        |

| SSCB   | = | Solid-State Circuit Breaker                                |

|        |   |                                                            |

| TD-HCB<br>TIV<br>TRV<br>UFD<br>VARC-CB<br>VI<br>VSC<br>WBG |   | Transient Interruption Voltage<br>Transient Recovery Voltage<br>Ultra-Fast Mechanical Disconnector<br>Voltage Source Converter Assisted Resonant Current Circuit Breaker<br>Vacuum Interrupter<br>Voltage Source Converter |

|------------------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |   |                                                                                                                                                                                                                            |

| WBG                                                        | = |                                                                                                                                                                                                                            |

|                                                            |   |                                                                                                                                                                                                                            |

| ZCS                                                        | = | Zero Current Switching                                                                                                                                                                                                     |

| ZnO                                                        | = | Zinc Oxide                                                                                                                                                                                                                 |

## Chapter

## Introduction

#### **1.1 Background and Perspective**

Except for the final paragraph, this section is reused, with modifications, from the specialization project report [1].

The DC technology was originally declared the losing part in The War of Currents in the late 1800s, where Thomas Edison fought for DC on the one side, while Nikola Tesla and George Westinghouse defended AC on the other [2]. The tipping point was the invention of the AC transformer, enabling simple conversion between different AC voltage levels. This facilitated transmission of electrical power using AC with high voltages and low currents, hence minimizing losses. As corresponding DC conversion technology did not exist, AC was the most economical alternative for electrification. Since then, systems for electricity transmission and distribution worldwide have mainly been based on AC.

However, over the past decades, advancements in semiconductor devices and converter technologies have marginalized the main advantage of AC systems. Since the 1970s, DC conversion technologies have been maturing [3], making both AC/DC and DC/DC conversion increasingly cost-effective. Consequently, the ability to step voltages up and down is now not only reserved for AC systems, hence renewing the interest in employing DC in electrical power systems.

The attractiveness of DC is also increasing due to changes in how we produce and use electrical energy. A growing share of electrical power is generated by renewable energy sources and other distributed energy resources (DER), of which many are DC-sources by nature [4], such as photovoltaic (PV) systems and fuel cells. Battery energy storage systems (BESS), which also are DC operated, are penetrating the power grids. The number of loads and equipment powered by DC keeps growing, such as light-emitting diode lighting, data centers, DC motors and consumer electronics [2, 3]. In addition, DC power must be supplied for charging the increasing amount of electric vehicles (EVs) and electric ferries.

The interest in DC power systems also stems from their advantages compared to systems based on AC. Multiple benefits can be listed, such as higher efficiency, controllability and simplicity, as well as no need for reactive power compensation nor phase synchronization [5]. Especially for transferring bulk power over huge distances, high-voltage DC (HVDC) is the natural choice of technology, due to lower losses and cost [6].

HVDC is already a well-established technology, and medium-voltage DC (MVDC) grids are also gaining increased attention. Similar to HVDC, the MVDC technology offers several beneficial features over its AC counterpart, and MVDC grids are considered well-suited for a wide range of application areas [4].

MVDC power grids are, however, still at an early stage of development, and some hindrances and challenges remain [3, 5]. One crucial design barrier is associated with the handling of short-circuit (SC) faults. Robust protection methods against SC faults must be developed in order to enable MVDC grids with satisfactory reliability. In particular, high-performance MVDC circuit breakers (CBs) are a key enabling technology [5, 7]. Today, no CBs for MVDC are commercially available, which currently is an important showstopper for MVDC grids.

This master's thesis builds upon the work presented in the specialization project report [1], where a comprehensive literature overview of and a comparison of DC circuit breaker (DCCB) concepts suitable for MVDC are given. In this thesis, one of the more promising and interesting DCCB topologies examined in the specialization project has been selected for a more detailed study: the voltage source converter (VSC) assisted resonant current CB (VARC-CB). The VARC-CB is a topical, promising technology currently under development, with several prominent beneficial features. Through an analytical investigation of the breaker, design equations and constraints are derived. These constitute a complete set of design strategies, which can be used for designing the VARC-CB for MVDC applications. A Simulink<sup>®</sup> simulation model of the VARC-CB employed in a simplified MVDC grid is also developed, and the model is parameterized using the derived design strategies. The results from several simulation cases are presented. On this basis, the robustness of the developed strategies and models is evaluated, and possible improvements in the MVDC VARC-CB design are proposed.

#### 1.2 Objectives

The scope of this thesis is limited by the main objectives given in the following list:

- 1. Present and discuss the operating principles of the VARC-CB concept

- Analytically investigate the MVDC VARC-CB, taking design principles and design limitations into consideration

- 3. Propose a complete set of design strategies for the MVDC VARC-CB

- 4. Develop a simulation model, including a component-level model of the VARC-CB and a simplified MVDC grid model, by using the physical modeling provided by the Simscape<sup>TM</sup> toolbox within the Simulink<sup>®</sup> environment

- 5. Validate the performed analysis, the proposed design strategies, and the developed model through Simulink simulations

- 6. Suggest possible improvements in the MVDC VARC-CB design

#### **1.3 Report Outline**

The thesis is divided into seven chapters. Chapter 2 sets the theoretical foundation upon which the rest of the thesis will be based. An overview of the concept of MVDC power grids is presented, and the benefits, possible application areas, and remaining challenges of the MVDC technology are discussed. A special focus is given to the challenge of SC fault handling, and a theoretical background on DC fault interruption and DCCB requirements is given. Furthermore, basic theory of three components found in many suggested DCCB topologies – the conventional mechanical AC circuit breaker (ACCB), the ultra-fast disconnector (UFD), and the metal-oxide varistor (MOV) – is provided. Finally, an overview of MVDC CB concepts proposed in literature is presented. Particular attention is given to the hybrid circuit breakers (HCBs), as the VARC-CB falls into this category.

Chapter 3 goes into details on the operating principles of the MVDC VARC-CB. Typical current- and voltage waveforms during an interruption process are shown, and a typical timing sequence is presented and described.

In Chapter 4, the MVDC VARC-CB is analytically investigated, and its design is examined. A set of design goals and a design system are first defined. Thereafter follows an analysis of each subcomponent of the breaker topology, taking design considerations and limitations into account. On the basis of these analyses, a full set of design strategies for the MVDC VARC-CB are derived.

Chapter 5 presents a complete, parameterized Simulink simulation model of the VARC-CB concept employed in an MVDC power grid. The modeling and parameterization processes are described and discussed in detail.

Chapter 6 includes simulation results and a following discussion of these. Through three main simulation cases, the performance of the developed simulation model is verified, and the derived design strategies are validated. Weaknesses and shortcomings of the modeling and analyses performed are also pointed out. In addition, two suggestions for improvements in the MVDC VARC-CB design are made and discussed

Finally, Chapter 7 concludes the thesis. The main findings and results are summarized, and recommendations for further work on the VARC-CB concept are made.

# Chapter 2

## **Theoretical Background**

The aim of this chapter is to provide a theoretical background and framework for the rest of the thesis. The first two sections include text and figures which are reused, with modifications, from the specialization project report [1]. The very first section gives an overview of the concept of MVDC power grids, including the benefits, promising application areas, and remaining challenges of the MVDC technology. The second section focuses on the main challenge of handling DC faults, with particular attention paid to operating principles and requirements of DCCBs employed for DC fault interruption. Subsequently, sections three and four present the physics and characteristics of three components found in many suggested DCCB topologies: the conventional mechanical AC circuit breaker (ACCB), the ultra-fast disconnector (UFD), and the metal-oxide varistor (MOV). The final section summarizes some of the main findings from the specialization project work. It gives a comprehensive but condensed overview of the main DCCB concepts suggested in literature, including their basic operating principles, their most essential beneficial features, and their drawbacks/challenging aspects. Some of the text is reused, with modifications, from the specialization project report. The literature review has, however, been updated, to provide a more accurate presentation of the state of the art. Furthermore, all the figures have been redrawn in order to present clearer explanations. The very last subsection of the chapter narrows the scope down to the breaker concept investigated in this thesis, the VARC-CB, giving a brief reasoning for the choice of the DCCB concept.

#### 2.1 MVDC Power Grids

The term *MVDC power grid* refers to an interconnection of more than two power electronic converter stations using medium-voltage DC links [8]. The voltage range for MVDC is not yet standardized: [3] uses a range of 1.5–30 kV, [9] employs 10–70 kV, and the IEEE standard 1709-2010 for MVDC power systems on ships provides 1–35 kV [10]. Based on existing literature, the potential lower and upper limits for medium-voltage DC thus seems to be around 1 kV and 70 kV, respectively.

#### 2.1.1 Beneficial Features

When comparing MVDC and MVAC systems, several advantages of the former can be listed. The most important ones are the following:

- Losses. MVDC connections offer lower losses than MVAC connections of similar voltage level [11]. This is mainly due to the absence of skin and proximity effects in DC links, no electrical hysteresis nor dielectric losses, less corona losses, and the fact that only active power is transmitted [3]. Consequently, the power transfer capability for the same voltage level is higher when employing MVDC.

- **Reactive compensation.** As DC links neither produce nor absorb reactive power, the need for reactive power compensation, which is present in many AC systems, is eliminated [11].

- **Interconnection.** The ease of integrating multiple sources and loads is an essential advantage of MVDC systems. When connecting a power source or load to an MVAC grid, the phase, magnitude and frequency of its voltage must be synchronized with the grid voltage. On the other hand, integration of a source or load into an MVDC system only requires voltage control [12].

- **Controllability.** The use of power electronic converters, rather than conventional transformers employed in AC systems, enables dynamic control of the power flow through the DC links [13]. Consequently, MVDC systems provide a higher degree of controllability, and hence also flexibility, than MVAC systems [14].

- **Conversion steps.** In many application areas, MVDC requires fewer conversion stages between sources and loads. Due to this, MVDC can offer increased efficiency, increased reliability, and a smaller footprint [2].

- Size and weight. Compared to an MVAC grid, the accumulated size and weight of an MVDC power grid can in many cases be smaller. One of the main reason thereof is that the bulky 50 and 60 Hz AC transformers are eliminated [10]. In addition, the number of conversion steps is possibly lower. Furthermore, MVDC offers higher power capability for the same voltage level, as discussed earlier. Consequently, choosing MVDC links over MVAC links can diminish the required space, and hence reduce environmental impacts [11].

#### 2.1.2 Promising Application Areas

Many application areas for MVDC power grids have been suggested in literature. Some of the more promising are power systems on ships [15, 16], aircraft power systems [4, 17], and collector grids for solar- and wind farms [2, 18]. Distribution grids with many different sources and loads, and large penetrations of DER and BESS are another area of interest for MVDC employment [2, 4]. A more detailed investigation of how these application areas can benefit from the many advantageous features of MVDC grids can be found in [1].

#### 2.1.3 Challenges and Barriers

Despite the many benefits and promising application areas, some challenges remain before MVDC power grids can be widely deployed. The main barriers are listed below.

- **Standardization.** One important obstacle is the lack of standards, regulations and guidelines for MVDC grids [19]. The lack of an established voltage range, which was discussed in the beginning of the current section, is an example of this challenge. Some standards for specific applications exist, such as the IEEE Standard 1709-2010 for MVDC systems on ships [10]. However, application-independent regulations targeted at design and operation of MVDC power grids are nonexistent [5].

- **Cost.** When compared to the conventional 50 and 60 Hz transformers employed in AC systems, the less mature power electronic converters required for DC grids are more costly [20]. However, this price difference is rapidly decreasing due to developments in semiconductor devices and converter technologies [5].

- **Fault handling.** A significant challenge is developing proper protection schemes suitable for MVDC power grids [21]. In particular, handling SC faults is a main difficulty in the design and operation of MVDC systems. This challenge will be examined in further detail in Section 2.2.

- Equipment. Electrical infrastructure and equipment specifically designed for medium-voltage DC must be developed in order to establish MVDC grids. One example is the need for proper MVDC cables [22]. Another crucial challenge is the lack of high-performance DCCBs [16]. This is one of the main hindrances towards MVDC grid deployment today, and is considered a key enabling technology [7].

#### 2.2 Fault Handling in MVDC Power Grids

In any electrical power system, protection against faults is required in order to ensure reliable and safe system operation. This is also necessary for preventing damage to components and people. At the occurrence of a fault, a well-functioning protection scheme should be able to eliminate the fault, while limiting the impact on the healthy parts of the system. Two important steps in the elimination process are to detect and to locate the fault. These steps are, however, beyond the scope of this study. When the fault has been identified, the protection system must ensure fault interruption and isolate the faulted parts of the grid. The main emphasis of this section will be to present different methods for DC fault interruption, with a particular focus on DCCBs.

#### 2.2.1 Three Methods for DC Fault Interruption

There are three main approaches to provide DC fault interruption, each relying on different devices: ACCBs, converters with fault-blocking capabilities, or DCCBs. The first strategy has been a common way to clear DC faults in point-to-point HVDC transmission systems based on voltage source converters (VSCs), and is based on utilizing the ACCBs of the AC/DC converters at each end [4, 23]. This is an economical and simple solution, but not

optimal for multi-terminal DC grids, as it is slow and leads to an outage of the whole grid [24]. In the second approach, power converters with inherent fault interruption capabilities are employed. This approach may be well-suited in certain application areas, as it can be space- and weight-efficient [25]. However, it is a costly and relatively slow method, and it involves grid deenergization, just as the ACCB approach [26, 27]. The third strategy is to install DCCBs at all line ends, which, as opposed to the two prior strategies, provides selective grid protection [26]. Using DCCBs for DC fault clearance is the main area of interest in this thesis, and is explored in more detail below.

#### 2.2.2 Basic DCCB Operating Principles and Requirements

Developing CBs for DC fault clearance is not straightforward. DC fault interruption is a challenging task, imposing demanding requirements on the breaker design and operation. These challenges, and the resulting DCCB operation principles required, are examined in the following by means of an illustrative example.

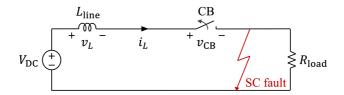

Figure 2.1 represents a simplified DC system experiencing a pole-to-pole SC fault. The system consists of a constant DC voltage source  $V_{DC}$ , a line inductance  $L_{line}$ , an ideal DCCB, and a resistive load  $R_{load}$ .  $v_L$  and  $i_L$  are, respectively, the voltage across and the current through the line inductance, while  $v_{CB}$  is the terminal voltage of the CB. Inspired by [28], the idealized waveforms in Figure 2.2 represent  $i_L$  and  $v_{CB}$  during the fault.

Figure 2.1: Simplified DC system experiencing an SC fault.

Figure 2.2: Fault current (red) and DCCB voltage (blue) during the SC fault in Figure 2.1.

The SC fault occurs at the time instant  $t_0$ , at which  $i_L$  starts to increase from its nominal value  $I_{\text{nom}}$ . At  $t_1$ ,  $v_{\text{CB}}$  rises above the nominal system voltage, the CB neutralizes the fault, and  $i_L$  starts to decrease from its peak value  $\hat{I}_L$  towards zero. The fault current reaches zero at  $t_2$ , at which the CB voltage drops to the nominal system voltage  $V_{\text{DC}}$ .

One of the main reasons that DC fault interruption is a demanding task is the absence of natural current zero-crossings in DC systems. Thus, unlike ACCBs, DCCBs must be capable of forcing the fault current to zero. This is normally done by the DCCB generating a counter-voltage with an amplitude exceeding the source voltage. Hence, the voltage across the line inductance becomes negative, resulting in a negative time derivative of the line current, as deduced from Equation (2.1). Consequently, the line current will decrease to zero. This phenomenon can be observed in the time interval  $t_1-t_2$  in Figure 2.2.

$$\frac{di_L}{dt} = \frac{V_{\rm DC} - v_{\rm CB}}{L_{\rm line}} \tag{2.1}$$

According to Equation (2.1), there will be an overvoltage induced across the circuit breaker during the decrease of the fault current. This overvoltage is referred to as the transient interruption voltage (TIV) [29], and is shown as  $V_{\text{TIV}}$  in Figure 2.2.  $V_{\text{TIV}}$  can be calculated by:

$$V_{\rm TIV} = V_{\rm DC} + L_{\rm line} \left| \frac{di_L}{dt} \right|$$

(2.2)

The DCCB must have sufficient voltage withstand capability to handle the TIV. From Equation 2.2, it is evident that a larger  $V_{\text{TIV}}$  value means a higher line current time derivative, as  $V_{\text{DC}}$  is constant. Consequently, an increase in  $V_{\text{TIV}}$  will result in the fault current decreasing more rapidly to zero. The downside is that this requires a larger voltage withstand capability for the DCCB.

Another challenging aspect of DC fault interruption is the handling of the magnetic energy stored in the DC system during the fault. In AC systems, the stored energy drops to zero at each zero crossing of the current. Consequently, an AC system is demagnetized periodically [30]. This is not the case for a DC system, as it lacks current zeros. Unlike an ACCB, a DCCB must thus include means for energy dissipation. For the system in Figure 2.1, the CB must be able to absorb the total energy  $W_{\text{total}}$  given by Equation (2.3) [29].

$$W_{\text{total}} = \frac{1}{2} L_{\text{line}} \hat{I}_L + \int_{t_1}^{t_2} V_{\text{DC}} i_L(t) dt$$

(2.3)

The first term on the right-hand side of Equation (2.3) is the magnetic energy stored in the line inductance during the fault. The second term is the energy fed into the network by the DC source during the fault current decrease between  $t_1$  and  $t_2$ . Both energy contributions must be dissipated by the DCCB, leading to energy stress on the breaker [29].

The low network inductance of DC grids is also contributing to the complexity of DC fault interruption. Normally, DC network inductances are considerably lower than those of AC grids. This is mainly due to the lack of transformer leakage inductances and the lower DC line/cable inductances [5]. A low network inductance gives a high rising rate of the fault current during  $t_0-t_1$  in Figure 2.2. To prevent the current from reaching

detrimentally high values, the CB must quickly neutralize the fault (stop the current from increasing). Preferably, the time from the trip order is received by the breaker until the fault is neutralized should be in the range of a few milliseconds for a DCCB operating in an MVDC grid [31]. In comparison, the corresponding time for conventional ACCBs operating in AC systems is typically in the range of several tens of milliseconds [32].

The final factor complicating the process of fault interruption in MVDC grids is the sensitivity of power electronic equipment. Power converters are essential building blocks of MVDC power grids, and the power electronic components employed in these converters are sensitive to overloads. They must therefore be protected against overcurrents [33]. This results in demanding requirements regarding the operating speed of DCCBs.

To summarize, a DCCB operating in an MVDC power grid is required to:

- 1. Neutralize the fault current within a few milliseconds from its trip order

- 2. Force the fault current down to zero

- 3. Dissipate the residual energy of the network

- 4. Withstand the transient interruption voltage (TIV)

In addition to these core requirements comes the desired features of a DCCB. Several features can be listed, and all of them may used as DCCB performance parameters. Inspired by the discussion on DCCBs in [4], some key features are low power losses, high reliability, low complexity, low cost, compact size, and low weight. The importance of each feature depends on the application area and the grid topology under consideration.

#### 2.3 Mechanical Switches

Several proposed DCCB designs include mechanical switches (MS) in their topologies. In these designs, one out of two MS types are normally used: some DCCBs employ a conventional mechanical ACCB, while others make use of an ultra-fast mechanical disconnector (UFD). In this section, the physical behavior and characteristics of the two MS types are examined, and their design and applications are briefly discussed.

#### 2.3.1 Conventional Mechanical AC Circuit Breakers

Conventional ACCBs are mechanical devices capable of initiating, carrying and interrupting the flow of current in an AC circuit under normal conditions and under specified abnormal conditions, such as those of an SC fault [34, 35]. The basic configuration of an ACCB consists of two metallic contacts, i.e. electrodes, placed in a container with an insulating medium [36]. One of the electrodes is fixed, whereas the other is movable. When the CB is in its closed state, the two electrodes are in galvanic contact, creating a very low-resistive path for the current. When the CB is to perform a current interruption, a driving mechanism separates the electrodes. This results in a conductive plasma, i.e. an electric arc, being formed in the contact gap. The current continues to flow through the arc, and will keep flowing as long as the arc is burning. Because of this, a prerequisite of the current interruption in ACCBs is that the electric arc must be extinguished [34].

#### 2.3.1.1 The Insulating Medium

The electrode separation and arc burning in an ACCB takes place in an insulating medium. This medium has two main tasks: the first is to ensure successful arc extinction, and the second is to provide insulation between the separated electrodes and between each electrode to earth [35]. A proper insulating medium should have high thermal and chemical stability, good arc-quenching properties, and high dielectric strength. Different mediums possess these characteristics, and the ones most commonly used in ACCBs are air, oil, sulfur hexafluoride (SF<sub>6</sub>) and vacuum. Previously, air and oil were the leading technologies for insulating mediums in ACCBs rated above 1000 V [34]. Today, vacuum and SF<sub>6</sub> are dominating, with vacuum CBs being the most widely deployed CB type for voltages up to 72.5 kV [36], whereas SF<sub>6</sub>-based ACCBs prevail at higher voltage levels [34].

#### 2.3.1.2 Arc Extinction and Current Interruption

The arc in the contact gap of an ACCB exists as long as it remains stable, which is satisfied when its energy input is able to compensate for its energy losses [37]. As the arc's energy input is given by the time integral of the product of arc voltage and arc current, the arc experiences unstable conditions if its current crosses zero. At such points the energy input will temporarily be zero, causing the arc to extinguish for a brief period [35, 36].

Due to the oscillatory behavior of an AC system, the current runs periodically through zero, causing arc extinction to occur naturally. This property of AC circuits is exploited in conventional ACCBs, which perform current interruption when the arc current passes through zero. The main task of the ACCB is therefore to prevent the arc from reigniting after it has extinguished at a current zero-crossing [34].

After the arc is extinguished, there is still a considerable amount of charge carriers present in the contact gap and the temperature is high. Hence, the gap still has some remaining electrical conductivity, and its voltage withstand capability is low [35]. At the same time, a voltage produced by the surrounding power system – the recovery voltage – starts to rise across the breaker contacts. If the free charge carriers in the contact gap are not rapidly removed, the applied recovery voltage will cause a dielectric breakdown in the gap, hence reigniting the arc. The core of preventing reignition is therefore to eliminate the remaining electrons and ions. This will recover the dielectric strength of the insulating medium in the gap, so it can withstand the applied recovery voltage.

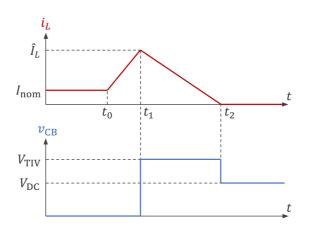

Figure 2.3 illustrates a typical recovery voltage waveform after a successful current interruption. An idealized arc current curve is also included. When the arc current is interrupted, the recovery voltage oscillates towards the power frequency system voltage in the course of a transient period, as seen in the figure. The breaker voltage during this period is called the transient recovery voltage (TRV).

Figure 2.3: Typical terminal voltage (blue) and arc current (red) waveforms of an ACCB around the moment of interruption.

The peak TRV value, together with the breaker's gap distance at arc current zero, affect whether a reignition is prevented or not. As the dielectric strength of the breaker increases with the distance between its electrodes, the gap distance is decisive for the maximum voltage withstand capability the gap can recover to [35]. Ergo, to achieve a successful current interruption, the gap length at the instant of arc extinction must correspond to a capability higher than the maximum value the TRV attains.

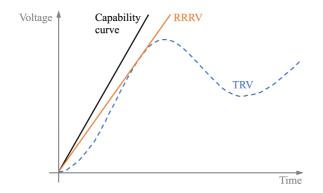

The rate of rise of the TRV (RRRV) and the rate of rise of dielectric strength (RRDS), i.e. the dv/dt capability of the breaker, are also factors playing important roles in the success or failure of the current interruption [38, 39]. Favorable interruption conditions in terms of RRRV and RRDS are illustrated in Figure 2.4, in which the arc current is assumed to cross zero at t = 0. The black line represents a typical capability curve of an ACCB, which has a slope of RRDS. The blue curve represents the course of a typical oscillatory TRV, and the orange line illustrates the RRRV. For the case displayed, RRRV < RRDS, hence the dv/dt capability of the ACCB is not exceeded. However, if the buildup of the dielectric strength was slower than the TRV rising rate, i.e. RRRV > RRDS, the TRV would at some point have surpassed the recovered voltage withstand capability. This would result in a dielectric reignition and an unsuccessful current interruption. For a successful interruption, it is therefore essential that the TRV is kept below the capability curve of the breaker, meaning the RRDS must be equal to or higher than the RRRV.

Figure 2.4: Illustrative curves showing the capability curve (black) of a theoretical ACCB, together with the TRV (blue) applied across the breaker terminals, and a line representing the RRRV (orange).

Another factor decisive for the successfulness of the current interruption is the current steepness, i.e. di/dt, at current zero [37]. A higher di/dt-value shortens the time available for the gap to start the recovery of its voltage withstand capability before the TRV is applied. Consequently, each ACCB has a maximum di/dt-limit, above which the breaker will not be able to quench the electric arc.

#### 2.3.1.3 Arc Characteristics and Arc Models

Usually, switching arcs in ACCBs are divided into two categories: high-pressure arcs and low-pressure arcs. The first category includes arcs existing at or above atmospheric pressure, which is the case in gas- and oil-based ACCBs. The latter comprises arcs formed at pressures below the atmospheric, which is the case in ACCBs using vacuum as the insulating medium [34, 37].

The high-pressure arc in gas- and oil-based ACCBs is created through ionization of the insulating medium between the breaker contacts. As the insulting medium is the source of plasma, the properties of a high-pressure arc is determined by the surrounding gas or oil [37]. In vacuum-based ACCBs, on the other hand, there is no ionizable medium present in the contact gap. Instead, the substance forming a vacuum arc is a metal vapor which is boiled off from the electrodes [40]. The characteristics of a vacuum arc are therefore solely determined by the electrode material [37].

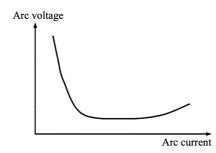

Figure 2.5 displays the typical shape of the V-I characteristic belonging to a *stationary* high-pressure arc [37]. It should be noted that ACCBs always deal with arcs which are *dynamic*, as the arc current and voltage vary with time. The characteristics and physical behavior of a dynamic arc are, however, rather complex. Therefore, a common simplifying assumption is that the arc behavior is static within a time interval. As can be seen in Figure 2.5, the static V-I characteristic is very nonlinear. At low current values, the voltage decreases with increasing current, i.e. the arc exhibits negative differential resistance. Then follows a current range in which the arc voltage is relatively constant. For this flat portion of the V-I curve, normal voltage values lie in the range of a few hundred volts to a few kilovolts. At high current values, the differential arc resistance turns positive; the arc voltage increases with the arc current.

Figure 2.5: Typical static V-I characteristics of a high-pressure arc, adapted from [37].

Many mathematical models have been developed for describing the V-I characteristics of high-pressure arcs. Two well-known, classic black box models are the ones of Cassie and of Mayr [37, 40]. Both models are founded on the premise of arc conductance being strongly affected by the energy stored in the arc. Several new, more advanced models have also been developed, using the Mayr and Cassie models as foundations.

The mentioned analytical models can, however, not be used for describing the behavior of arcs formed in vacuum-based ACCBs, as vacuum arcs show some important differences from high-pressure arcs [40]. One unique characteristic of vacuum arcs is that they have two modes in which they can exist: diffuse mode and constricted mode [37]. The transition from the diffuse to the constricted mode happens when the arc current exceeds a certain limit. This limit depends on the electrode material and geometry, but is typically in a range of 10–15 kA. The physical details of these arc modes will not be elaborated on. However, an important aspect to highlight is that the longer time the arc is in the diffuse mode prior to current zero, the greater the likelihood of a successful current interruption [34].

When in the diffuse mode, vacuum arcs have a V-I relationship quite different from the one shown in Figure 2.5. The diffuse vacuum arc voltage is fairly constant, and almost independent of the arc current magnitude [36, 37]. It is also considerably lower than the arc voltages observed for high-pressure switching arcs. Typically, the arc voltage is approximately 20–40 V, and it varies slightly with the electrode material used [34, 37]. When in the constricted mode, on the other hand, the vacuum arc appears quite similar to that of a high-pressure arc [40]. In this mode, the arc voltage varies intermittently, and has an average value significantly higher than in the diffuse mode [37].

Another special feature of vacuum arcs is a phenomenon called *current chopping*. It can, under certain conditions, occur in other ACCB types, but it is considered a typical vacuum CB phenomenon [37]. Current chopping occurs when the arc current approaches zero. When reaching a certain low current level, the arc abruptly collapses due to instability; the arc extinction occurs before the current has reached zero [41]. This is highly unwanted, as the abrupt current cut-off can cause overvoltages in the circuit [37]. Low chopping current levels are therefore desirable. This level is determined by the electrode material, and is typically in the range of 1–15 A for conventional vacuum ACCBs [34].

#### 2.3.2 Ultra-Fast Disconnectors

A disconnector is a mechanical device normally used to isolate a part of an electrical system from the rest [42, 43]. Disconnectors are capable of continuously carry rated current, and they can carry SC currents for a specified duration. They also have the ability of performing no-load switching, but in contrast to ACCBs, disconnectors are not designed for interrupting electric arcs of significant magnitude [42]. Consequently, disconnectors have very low current breaking capabilities compared to ACCBs [42, 43].

The basic construction and operating principles of a disconnector have many similarities to those of an ACCB. A disconnector has two metallic electrodes, of which one is fixed and the other is movable [44]. Under closed operation, the electrodes are in contact, providing a path for the current with very low resistance. At an opening signal, an actuator separates the electrodes, hence exposing the insulating medium in which the electrodes are placed (e.g. SF<sub>6</sub>, air or vacuum). The electrode distance is then increased until the contact gap has obtained a voltage withstand capability that meets the isolation requirement.

Just as for ACCBs, it is important that during opening, the voltage applied to the disconnector terminals does not at any point exceed the obtained voltage withstand capability of the contact gap. If this happens, it will cause a dielectric breakdown of the gap [45].

The disconnectors in DCCB designs in literature usually employ Thomson coil actuators. These actuators are based on electromagnetic repulsion forces, which results in very fast mechanical operation, hence the name *ultra-fast* disconnectors [46, 47]. The operating principles, modeling and design of a Thomson coil-based UFD can be found in [46].

#### 2.4 The Metal-Oxide Varistor

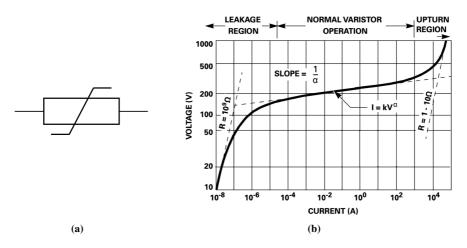

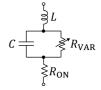

The metal-oxide variator (MOV) is a vital component in most DCCB designs. It is a variable resistor, and its circuit symbol is shown in Figure 2.6a. Figure 2.6b displays an example MOV V-I curve similar to that typically provided in MOV datasheets. Only one quadrant is shown, as the characteristic is symmetrical [48, 49].

Figure 2.6: (a) MOV symbol, (b) Typical MOV V-I curve, adapted from [49].