Sindre Bjørbekk Kongerød

# Modeling of SiC MOSFETs and Parameter Fitting Using a Genetic Algorithm

Master's thesis in Energy and Environmental Engineering Supervisor: Assoc. Prof. Dimosthenis Peftitsis June 2020

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Sindre Bjørbekk Kongerød

# Modeling of SiC MOSFETs and Parameter Fitting Using a Genetic Algorithm

Master's thesis in Energy and Environmental Engineering Supervisor: Assoc. Prof. Dimosthenis Peftitsis June 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

# Acknowledgement

In this segment I would like to acknowledge those who have helped me in my work. Associate Professor Dimosthenis Peftitsis and Ph.D Candidate Ole Christian Spro have been my supervisors and their guidance and support has been vital in my work. I thank Dimosthenis for his motivation and positivity, encouraging me in my work. Ole Christian has been my day-to-day supervisor and has helped me with difficulties I have had. His guidance has always challenged me to think and given me pointers which have helped me understand rather than simply giving me the easiest answer. This has helped me grow as a person. I thank Ole Christian for using many hours of his time to guide and motivate me in my work.

Furthermore, my appreciation also goes to Ph.D Candidate Daniel Alexander Philipps for discussing different topics with me and giving me feedback. This has helped me improve my work.

Lastly, I would like to thank my family and friends for believing in me and encouraging me. This helped me overcome difficult times and ultimately finish my studies!

# Abstrakt

Denne masteroppgaven demonstrerer bruken av en genetisk algoritme til å optimalisere parametere i simuleringsmodeller for å nøyaktig representere målte statiske egenskaper til en SiC MOSFET ved romtemperatur. Ulike SiC MOSFET modeller funnet i litteraturen er undersøkt og klassifisert. To modeller fra produsenter er valgt for optimaliseringsprosessen; en forbedret modell basert på Cree-modellen og modellen fra ROHM. En genetisk algoritme implementeres og brukes for å tilpasse de to modellene til eksperimentelle måledata. De statiske egenskapene - også kjent som IV-kurver eller IV-karakteristikk - for en kommersiell SiC MOSFET (C3M0075120D) ble målt ved bruk av en kommersiell curve tracer.

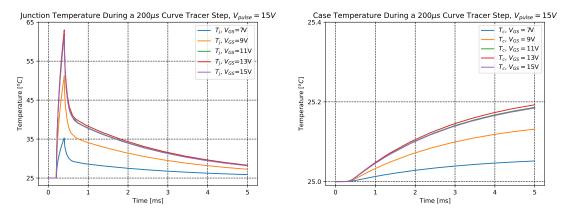

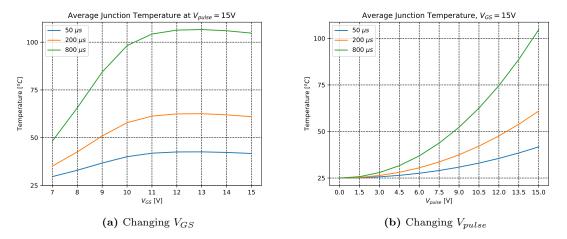

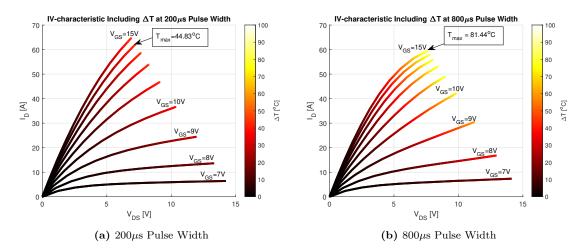

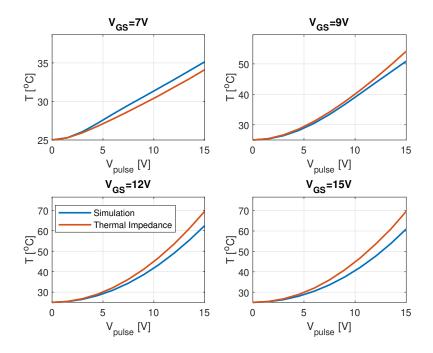

To metoder for å oppnå karakteristikkene ved bruk av curve traceren blir undersøkt og diskutert. Blant testinnstillingene på maskinen har det vist seg at pulsbredden til påført spenning eller strømpuls påvirker målingene sterkt. Den indre temperaturen i enheten som måles blir undersøkt gjennom simuleringer mens den påfører samme puls som den opplever under karakteriseringen. Ofte antas den indre temperaturen å være tilnærmet lik den ytre temperaturen for korte testpulser. Ved å bruke produsentens termiske modell av enheten, ble det funnet at den indre temperaturen øker til nærmere  $65^{\circ}$ C for flere av karakteriseringspunktene under en fullstendig curve tracer test. Følgelig er den indre temperaturen større enn den ytre temperaturen når målingene blir utført, og denne feilen kan overføres til modelleringen av den samme enheten. Disse termiske undersøkelsene blir verifisert ved termiske beregninger ved bruk av den termiske impedansen fra enhetens datablad.

I dette arbeidet blir temperaturøkningen under eksperimentell karakterisering tatt med i beregningen av optimaliseringsalgoritmen. Dette oppnås ved å sette den indre temperaturen til verdiene oppnådd fra termiske beregninger på hvert målepunkt i simuleringene. Den genetiske algoritmen justerer modellparametrene slik at de passer til måledataene. Begge modellene oppnår parameterverdier som gir en samlet tilpassing av måledataene. Imidlertid har ROHM-modellen bedre passform i alle kjøringene av algoritmen.

## Abstract

This master thesis demonstrates the use of a genetic algorithm to optimize parameters of simulation models to accurately represent the measured static characteristics of a SiC MOSFET at room temperature. Various models in the literature for simulating SiC MOSFETs are investigated and classified. Two models from device manufacturers are selected for the optimization process; an improved model based on the Cree model and the model from ROHM. A genetic algorithm is implemented and used to fit the two models to experimental measurement data. The static characteristics – also known as IV-curves – of a commercial SiC MOSFET (C3M0075120D) were measured using a commercial curve tracer.

Two methods for obtaining the characteristics when using the curve tracer are investigated and discussed. Among the test settings of the machine, the pulse width of the applied voltage or current pulse has been found to strongly influence the measurements. The junction temperature of the device-under-test is investigated through simulations while applying the same pulse as it experiences during characterization. Often, the junction temperature is assumed to be approximately equal to the case temperature for short test pulses. By using the manufacturer provided thermal model of the device, it is found that the junction temperature increases up to approximately 65°C for several of the characterization points during a complete curve tracer test. Hence, the junction temperature is greater than the case temperature when the measurements are taken, and this error can carry over to the modelling of that same device. These thermal investigations are verified by thermal calculations using the thermal impedance from device datasheet.

In this work, the temperature increase during experimental characterization is taken into account by the optimization algorithm. This is accomplished by setting the junction temperature to the values obtained from thermal calculations at each measurement point in the simulations. The genetic algorithm adjusts the model parameters to fit the measurement data. Both models obtain parameter values that provide an overall fit of the measurement data. However, the ROHM model is found to have better fit in all runs of the algorithm.

# Contents

|          | Ack                      | nowledgement                                            | i                  |  |

|----------|--------------------------|---------------------------------------------------------|--------------------|--|

|          | Abstrakt                 |                                                         |                    |  |

|          | Abstract                 |                                                         |                    |  |

|          | List                     | of Abbreviations                                        | vi                 |  |

| 1        | <b>Int</b><br>1.1<br>1.2 | oduction         Scope of the Thesis         Outline    | <b>1</b><br>1<br>1 |  |

| <b>2</b> | 2 Semiconductor Devices  |                                                         |                    |  |

|          | 2.1                      | The Physics of Semiconductor Devices                    | <b>2</b><br>2      |  |

|          |                          | 2.1.1 Doped Semiconductors                              | 3                  |  |

|          |                          | 2.1.2 Current Flow                                      | 4                  |  |

|          |                          | 2.1.3 pn-junction                                       | 5                  |  |

|          | 2.2                      | Semiconductor Device Structures and Characteristics     | 6                  |  |

|          |                          | 2.2.1 Bipolar Junction Transistor                       | 6                  |  |

|          |                          | 2.2.2 Metal-Oxide-Semiconductor Field-Effect Transistor | 7                  |  |

|          |                          | 2.2.3 Insulated Gate Bipolar Transistors                | 9                  |  |

|          |                          | 2.2.4 Capacitor Model of a MOSFET                       | 10                 |  |

|          |                          | 2.2.5 Transconductance and IV-Characteristics           | 11                 |  |

|          | 2.3                      | Switching Events of MOSFETs                             | 13                 |  |

|          |                          | 2.3.1 Turn-on Waveforms                                 | 13                 |  |

|          | 2.4                      | 2.3.2 Turn-off Waveforms                                | 15                 |  |

|          | 2.4                      | Si and SiC Comparison                                   | 16                 |  |

| 3        | Mo                       | leling of SiC MOSFETs                                   | 18                 |  |

|          | 3.1                      | What Makes a Good MOSFET Model?                         | 18                 |  |

|          | 3.2                      | SiC MOSFET Models                                       | 18                 |  |

|          |                          | 3.2.1 Established Models                                | 20                 |  |

|          |                          | 3.2.2 Charge-Based Model                                | 20                 |  |

|          |                          | 3.2.3 Non-segmented Model                               | 21                 |  |

|          |                          | 3.2.4 Electro-Thermal Model                             | 23                 |  |

|          |                          | 3.2.5 Curtice-Ettenberg Based Model                     | 24                 |  |

|          | 3.3                      | Manufacturer Models                                     | 26                 |  |

|          |                          | 3.3.1 Cree Wolfspeed: C3M0075120K SPICE Model           | 26                 |  |

|          |                          | 3.3.2 STMicroelectronics: SCT30N120_V3 SPICE Model      | 29                 |  |

|          |                          | 3.3.3 ROHM: SCT2080KE SPICE Model                       | 32                 |  |

|          | 3.4                      | Universal Model                                         | 35                 |  |

| <b>4</b>     | 4 Method of Data Extraction and Optimization 36 |    |  |  |  |  |

|--------------|-------------------------------------------------|----|--|--|--|--|

|              | 4.1 Curve Tracer                                | 36 |  |  |  |  |

|              | 4.1.1 Load Line                                 | 38 |  |  |  |  |

|              | 4.1.2 Comparison of Measurement Methods         | 39 |  |  |  |  |

|              | 4.2 Parameter Extraction and Optimization       | 46 |  |  |  |  |

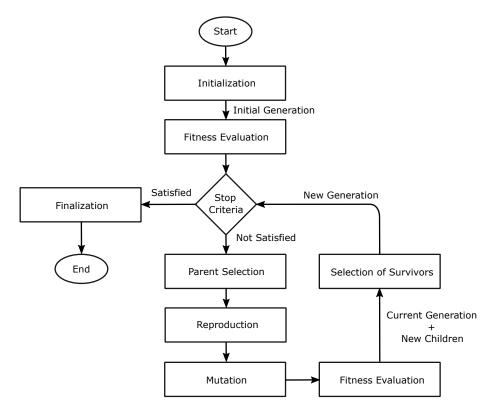

|              | 4.2.1 Evolutionary Algorithms                   | 46 |  |  |  |  |

|              | 4.2.2 Genetic Algorithm                         | 47 |  |  |  |  |

|              | 4.2.3 Implementation of the GA                  | 48 |  |  |  |  |

| 5            | Results                                         | 59 |  |  |  |  |

| 0            | 5.1 Fitting of IV-curves                        | 59 |  |  |  |  |

|              | 5.2 Evaluation of the Algorithm                 | 61 |  |  |  |  |

|              |                                                 |    |  |  |  |  |

| 6            | Conclusions                                     |    |  |  |  |  |

|              | 6.1 Further Work                                | 68 |  |  |  |  |

| Appendices 7 |                                                 |    |  |  |  |  |

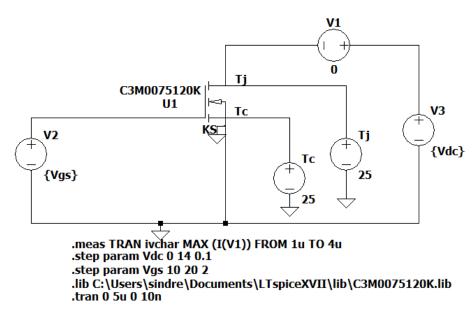

| A            | IV-characteristics Simulation Circuit           |    |  |  |  |  |

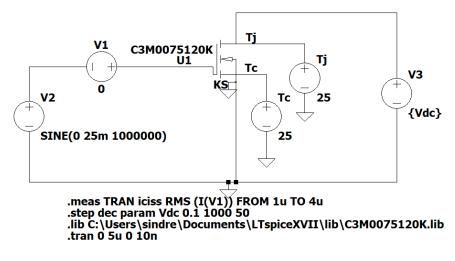

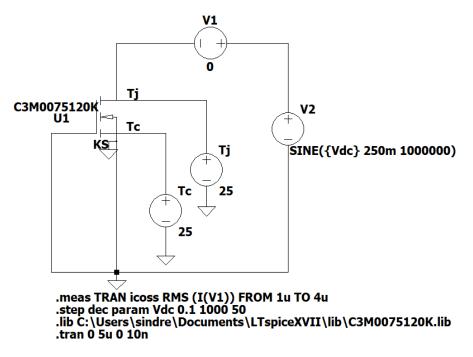

| в            | CV-characteristics Simulation Circuits          |    |  |  |  |  |

|              | B.1 Ciss Simulation Circuit                     | 71 |  |  |  |  |

|              | B.2 Coss Simulation Circuit                     | 72 |  |  |  |  |

|              | B.3 Crss Simulation Circuit                     | 72 |  |  |  |  |

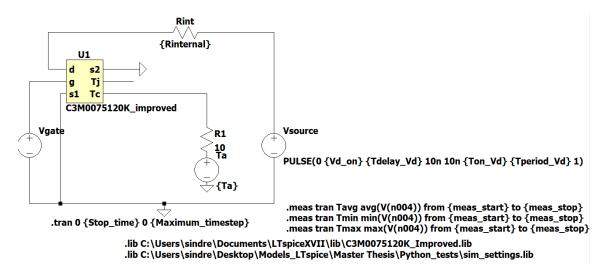

| $\mathbf{C}$ | Junction Temperature Simulation Circuit 7       |    |  |  |  |  |

| D            | Verification of Temperature Simulations         |    |  |  |  |  |

| $\mathbf{E}$ | E Setting Junction Temperature LTSpice          |    |  |  |  |  |

| R            | References                                      |    |  |  |  |  |

# List of Abbreviations

| $\mathbf{AC}$          | Alternating Current                                                                      |

|------------------------|------------------------------------------------------------------------------------------|

| ACO                    | Ant Colony Optimization                                                                  |

| BJT                    | Bipolar Junction Transistor                                                              |

| BSIM                   | Berkeley Short-channel IGFET Model                                                       |

| BVS                    | Behavioral Voltage Source                                                                |

| CMOS                   | Complementary Metal–Oxide–Semiconductor                                                  |

| СТ                     | Curve Tracer                                                                             |

| DC                     | Direct Current                                                                           |

| $\mathbf{E}\mathbf{A}$ | Evolutionary Algorithm                                                                   |

| EKV                    | Enz-Krummenacher-Vittoz                                                                  |

| FET                    | Field-Effect Transistor                                                                  |

| $\mathbf{GA}$          | Genetic Algorithm                                                                        |

| HV                     | High Voltage                                                                             |

| IGBT                   | Insulated-Gate Bipolar Transistor                                                        |

| JFET                   | Junction-Field-Effect Transistor                                                         |

| $\mathbf{LV}$          | Low Voltage                                                                              |

| MOSFET                 | $Metal \hbox{-} Oxide \hbox{-} Semoconductor\ Field \hbox{-} Effect \hbox{-} Transistor$ |

| NSGA                   | Non-dominated Sorting Genetic Algorithm                                                  |

| OOP                    | Object-Oriented Programming                                                              |

| PSO                    | Particle Swarm Optimization                                                              |

| $\mathbf{RC}$          | Resistor-Capacitor                                                                       |

| RMSE                   | Root Mean Square Error                                                                   |

| SPICE                  | Simulation Program with Integrated Circuit Emphasis                                      |

| VCCS                   | Voltage-Controlled Current Source                                                        |

| VCVS                   | Voltage-Controlled Voltage Source                                                        |

| WBG                    | Wide Bandgap                                                                             |

# 1 Introduction

Modeling of real systems and components is a major contributor to technological innovation and developments by abstracting ideas, systems or processes into a manageable and understandable set of rules or equations. This set of rules or equations can, in many cases, be used to solve or optimize problems, achieving desired outcomes. Models of real components are used in many design processes to find potential flaws of a system before implementing a prototype version. Furthermore, the use of simulation tools as part of a product design process is becoming increasingly important in the power electronic industry. By using simulated circuits, the design space can be explored in less time and at lower cost compared to prototype based design processes. Accurate circuit simulations can also be used in automated design and optimization processes to reduce workload of engineers or explore design spaces that are not directly accessible to design engineers. E.g. investigate operational parameters on junction temperature of a semiconductor component, which is otherwise impossible to measure in practice. Additionally, simulation tools can be used for troubleshooting circuits and converters that are not behaving as expected. Moreover, new power semiconductors made from wide band gap materials open new possibilities for designing power electronic converters, such as increased power density and efficiency at lower system costs. This is suitable for a wide range of applications like industry, marine applications and utilization of renewable energy. However, to fully explore the potential of wide band gap materials, advanced circuitry and accurate models may be required. Accurate models can be used in simulation of new power converters that takes advantage of the wide band gap materials.

#### 1.1 Scope of the Thesis

The thesis is written as part of the energy and environment master of technology program at NTNU. It is a continuation of a semester project from previous semester [1]. However, the focus has shifted from advanced gate drivers to modeling of SiC MOSFETs. The objectives are to present different MOSFET modeling approaches,  $I_D V_{DS}$ -characterization of MOSFETs and optimization of models using a genetic algorithm.  $I_D V_{DS}$ -characterizations using a curve tracer are performed to obtain measurement data that is used in the genetic algorithm. Changes on junction temperature during curve tracer measurements are investigated. The measurements are limited to one device (C3M0075120D), to a single case temperature (25°C) and static characteristics. Furthermore, the genetic algorithm is made in the Python programming language and simulations of certain models are performed in LTspice as part of the optimization process by the genetic algorithm.

#### 1.2 Outline

Firstly, theory of semiconductor devices is presented in section 2. Section 2 covers semiconductor physics and examples of different devices with focus on SiC MOSFETs. This will serve as a foundation to understanding certain elements of SiC MOSFET modeling. Secondly, different SiC MOSFET modeling approaches are presented in section 3. A range of different models found in the literature are presented and classified. Additionally, three manufacturer models are discussed and reviewed. Thirdly, section 4 covers the method of data extraction and optimization. The equipment will be introduced and two different methods of performing the characterization is discussed. Effects on the junction temperature during the measurements are investigated. Furthermore, the genetic algorithm will be explored in detail. Finally, results from several runs of the genetic algorithm are presented, discussed and concluded in section 5 and 6.

### 2 Semiconductor Devices

Semiconductor devices are widely used in electronics and communication technologies. These devices utilize the properties of semiconductor materials. Today, silicon (Si) is the dominating material used in semiconductor devices in power electronics. However, silicon based semiconductor devices are reaching their theoretical limit. Therefore, efforts in both research and development have targeted new and better semiconductor materials. This may allow the development of new components with characteristics better suited for various applications. Higher efficiency, higher switching frequency and higher operating temperature are the most important characteristics in the development of new power electronic devices. Throughout the following subsections, knowledge about semiconductors, the same concepts of carriers, doping and device structure are applicable to semiconductor devices based on other materials such as silicon carbide (SiC), which is the selected semiconductor material for this thesis.

#### 2.1 The Physics of Semiconductor Devices

The characteristics of semiconductor materials range between conductor and insulator materials. An electric field applied to a material will cause a current to flow if there are free charge carriers [2]. The density of free charge carriers varies greatly from material to material. Most metals have a large density, e.g. copper has a density in the order of  $10^{23}$  per cm<sup>3</sup>, while other materials such as quartz have densities less than  $10^3$  per cm<sup>3</sup>. Semiconductors have a density somewhere in between that of conductors and insulators ( $10^{8}$ - $10^{19}$  per cm<sup>3</sup>) [2]. The density in semiconductors can be changed by orders of magnitude by introducing impurities as will be discussed in section 2.1.1.

Silicon (Si) is the dominating semiconductor material. Si with atom number 14 in the periodic table, has four valence electrons. Valence electrons are the electrons located at the outer shell of an atom. These are the electrons that participate in the formation of a chemical bond and may be gained or lost. Due to having 4 valence electrons, Si atoms will lay in an array in a single crystal.

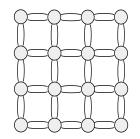

Figure 2.1: Silicon in array, taken from [2]

Each Si atom is bound to four other Si atoms by covalent electron bonds. Covalent binding means that the electrons are shared between the two atoms. These bonds may be broken by a process called thermal ionization. This means that the random thermal motion around the atom's equilibrium position may break the bonds. A free electron and a positive charge, called hole, is created when the bond is broken. Consequently, allowing the electron to move and recombine at another hole location or simply recombine at the same place. Figure 2.2 illustrates the process of thermal ionization; generation and movement of holes and free electrons in pure silicon material.

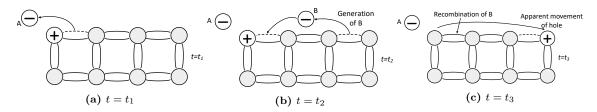

Figure 2.2: Process of thermal ionization and hole movement  $(t_1 < t_2 < t_3)$ , taken from [2]

At time  $t_1$  in figure 2.2a an electron, named A, breaks the bond and becomes a free electron inside the material. Some time later,  $t_2$ , another electron, named B, may be attracted to the positive charge and breaks free from its bond somewhere else in the material, illustrated by figure 2.2b. As electron B is attracted towards the positive hole generated by electron A earlier, it may take that place and become bound again at time  $t_3$ . Figure 2.2c shows the recombination of electron B and illustrates the apparent movement of the positive hole generated by thermal ionization of electron A. The process of thermal ionization will increase with temperature. Higher temperature means greater thermal motion, subsequently leading to higher chances of breaking the bonds. Regardless, pure Si will always generate an equal amount of free electrons and holes at any time as a result of thermal ionization.

#### 2.1.1 Doped Semiconductors

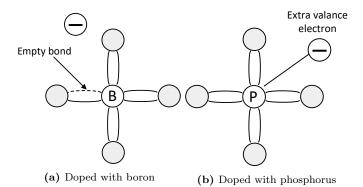

Adding atoms of other elements to the Si array may change the thermal equilibrium density of electrons. Boron (B) or phosphorus (P) can be introduced to create excess electrons or holes. Boron has 3 valence electrons. That means in Si doped with B, the B tends to accept a free electron and completes the last bond with Si, figure 2.3a. Hence, free electrons from thermal ionization get taken by B, leaving positive holes free to move in the material. This type of silicon doping is called p-type. In a p-type Si material there are more holes than electrons. In this case, holes are the majority carriers and electrons minority carriers.

Figure 2.3: Illustration of doped silicon material, taken from [2]

The opposite occurs when introducing phosphorus. P has 5 valence electrons, meaning that in the Si array there will be additional electrons not in bonds with the Si atoms, figure 2.3b. Furthermore, the P atom is easily ionized, subsequently releasing the fifth valence electron. This electron is donated to the Si array and creates more free electrons than holes. Hence, a negatively doped Si material, called n-type, results. In an n-type Si material the electrons are the majority carriers while the holes are the minority carriers.

#### 2.1.2 Current Flow

Two mechanisms control the movement of the free carriers; drift and diffusion. Drift happens when an electric field is applied to the material. In the presence of an electric field, free carriers are accelerated. Thus, moving them parallel to the field as shown in figure 2.4.

Figure 2.4: Free carrier movement when applied to an electric field [3]

Positive and negative carriers will move parallel to the field, but in opposite directions. The amount of drift current depends on the size of the electric field, the amount of free carriers and the mobility of the carriers in the material.

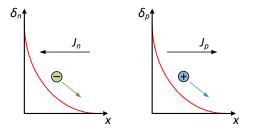

Diffusion on the other hand, is a result of spatial density variations of the free carriers. Figure 2.5 shows the cause of diffusion current.

Figure 2.5: Free carrier movement due to spatial density variations [3]

$\delta n$  and  $\delta p$  represent negative and positive free carrier density respectively. The x-axis represents different positions in the material. As the figure shows, when the spatial carrier density varies inside the material, a movement of carriers from the high density area to the lower density area within the material occurs. Thus, the diffusion current density will be the sum of the electron current density  $J_n$  and the hole current density  $J_p$ .

Different semiconductor devices capitalize on these effects differently. Some devices utilize the diffusion effect while others use the drift effect. For example, BJTs utilize the diffusion effect while MOSFETs are based on the drift effect.

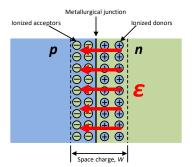

#### 2.1.3 pn-junction

A pn-junction is formed by doping one part of the semiconductor material n-type and doping the other side to a p-type. In a pn-junction there will be an inherent electric field at the border between the layers, called junction, as shown in figure 2.6.

Figure 2.6: Space charge in a pn-junction [3]

The field originates as a result of majority carriers on both sides diffusing over to the lower density side. On each side of the junction, a small region has received majority carriers from the other side. I.e. electrons from the n-type layer diffuse over to the p-type layer and holes from p-type layer diffuse over to the n-type layer. These two regions create a space charge, also called depletion layer. Furthermore, the generated electric field will set up a drift current, pushing the free carriers back to their respective layers. An equilibrium is reached when the diffusion current equals the drift current.

An external voltage source can change the generated field. When the applied voltage is positive on the p-region it will counter the space charge and the pn-junction is called forward biased. By increasing the applied voltage greater than that of the space charge, current will flow through the pn-junction. If the applied voltage is negative on the p-region, the space charge will increase. In such a state the pn-junction is said to be reverse biased. As a result, the pn-junction will block the majority of the current while in this state. However, a small current is still present, called leakage current. Leakage current is a result of minority carriers diffusing into and pushed across the field due to small variations in the minority densities which are caused by the applied voltage. In addition, a small contribution to the leakage current is made by thermal ionization occurring in the space charge. If the space charge region becomes too large as a result of increasing the applied voltage, the pn-junction will start to conduct. Electrons with high kinetic energy collides with atoms in the material and can break a covalent bond, creating another free electron and a hole. This process is called impact ionization [2]. Additionally, the newly freed electron may gain sufficient kinetic energy by the applied field to break other covalent bonds. Consequently, if this process cascades into a chain reaction, a large current is produced and will quickly destroy the device. The voltage level that makes this happen is called the breakdown voltage of the device. Pn-junctions enable more advanced semiconductor devices. Semiconductor devices are built up by several layers with various doping levels and types to achieve different properties.

#### 2.2 Semiconductor Device Structures and Characteristics

This subsection will briefly discuss bipolar junction transistors (BJT), metal-oxide-semiconductor field-effect transistors (MOSFET) and insulated bipolar gate transistors (IGBT). However, since the focus of this thesis is on MOSFET devices, more detailed explanations and figures are given for the MOSFET structure.

#### 2.2.1 Bipolar Junction Transistor

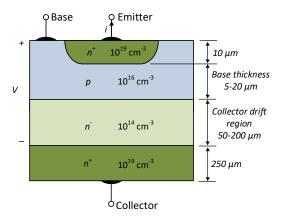

Bipolar junction transistors (BJT) have a four layer structure of alternating doping levels and types as shown in figure 2.7. The doping level and thickness of the layers have a significant effect on the characteristics of the device [2].

Figure 2.7: Structure of a BJT [3]

A BJT uses the diffusion effect for conducting current from collector to emitter. By injecting a constant base-emitter current, holes are introduced in the p-layer. This will introduce a change in the carrier densities in the layers, giving rise to a diffusion current from collector to emitter. In on-state, it requires a constant base-emitter current to be able to keep up the diffusion current. It takes some time to change the carrier densities in the materials, resulting in longer switching time. However, the conduction losses are low due to a small on-state resistance. In summary, the BJT is a current controlled device, where the base-emitter current is controlling the collector-emitter current flow.

#### 2.2.2 Metal-Oxide-Semiconductor Field-Effect Transistor

Metal-oxide-semiconductor field-effect transistors (MOSFETs) have a four layer structure of alternating doping levels and types. For example, an n-channel MOSFET has an  $n^+pn^-n^+$  structure as shown in figure 2.8.

Figure 2.8: MOSFET structure, taken from [3]

The end  $n^+$ -layers at source and drain are approximately the same in terms of doping level. The  $n^+$ -layer located at source is encapsulated in a p-type middle layer, often termed body [2]. The  $n^-$ -layer is called the drift region and has a lower doping level compared to the  $n^+$ -layers, hence the signs. This layer determines the breakdown voltage of the device. For a p-channel MOSFET the structure is the same with opposite doping profile, i.e.  $p^+np^-p^+$ .

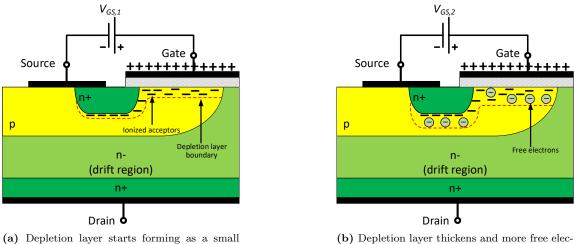

When a voltage is applied to the gate, the carriers in the semiconductor material will be affected by the field. Carriers will move and create a depletion layer at the boundary of gate-oxide and player. Figure 2.9 illustrates this process.

(a) Depletion layer starts forming as a small voltage is applied between gate and source,  $V_{GS} = V_{GS,1}$  [3]

(b) Depletion layer thickens and more free electrons are attracted as gate-source voltage increases,  $V_{GS} = V_{GS,2}$  [3]

Figure 2.9: Development of depletion layer as gate-source voltage increases,  $V_{GS,1} < V_{GS,2}$

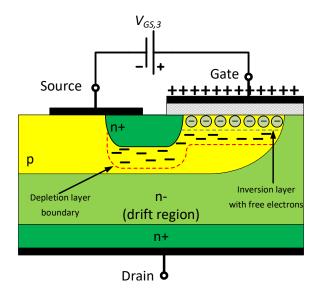

As a small positive gate-source voltage is applied, electrons will get attracted to the positive charge on the gate. Between the gate and the silicon material there is an oxide layer blocking the charge from passing through. Majority carriers in the p-layer (holes) will be repelled from the border between the gate and p-layer, figure 2.9a. I.e. electrons will occupy the holes and create negatively charged acceptors. Thus, a depletion layer is formed. When the gate-source voltage increases further, the depletion layer thickens to provide additional negative charge. In addition to repelling more holes, free electrons are also attracted to the depletion layer, figure 2.9b. Moreover, as this process continues, more free electrons are attracted and eventually the negative charge density becomes greater than the positive hole density in the p-layer. Consequently, a so called inversion layer forms at the border between the gate-oxide layer and p-layer. Since the electrons become the majority carriers in the inversion layer, the p-layer close to the border is effectively inverted to an n-layer, hence the name inversion layer. The voltage level at which point the inversion layer emerges is called the threshold voltage. Figure 2.10 illustrates the inversion layer.

Figure 2.10: Inversion layer has been created,  $V_{GS} = V_{GS,3}$  [3]

The inversion layer contains free electrons that are free to move, i.e. highly conducting. This opens a channel through the p-layer between the n-layers. Thus making it possible for the current to flow from drain to source.

After opening the channel, the gate voltage is increased further to enlarge the inversion layer, allowing higher current to pass through and making the on-state resistance of the MOSFET smaller. In conclusion, the MOSFET is a voltage controlled device, where the gate-source voltage controls the drain-source current flow.

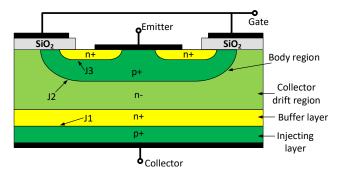

#### 2.2.3 Insulated Gate Bipolar Transistors

Insulated gate bipolar transistors (IGBTs) are a result of combining the best characteristics of both BJTs (low conduction losses) and MOSFETs (low switching losses). The IGBT consists of five alternating layers of different doping levels and types as shown in figure 2.11.

Figure 2.11: Structure of an IGBT [3]

The IGBT is structurally similar to that of the MOSFET shown earlier. It is designed as a

MOSFET with an injecting layer on its collector side. This layer provides conductivity modulation of the collector-drift region. This means that holes from the lower  $p^+$ -layer will get injected into the drift region, making the resistance in the drift region decrease. Consequently, the on-state resistance is decreased. The performance of an IGBT is therefore in between that of a MOSFET and a BJT. It is slower than a MOSFET because, as for the BJT, the injected charge carriers in the drift region must be removed before it is completely turned off. The IGBT is also a voltage controlled device.

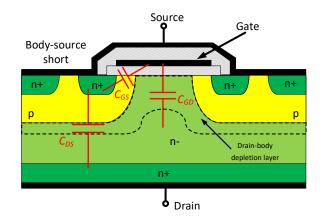

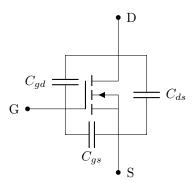

#### 2.2.4 Capacitor Model of a MOSFET

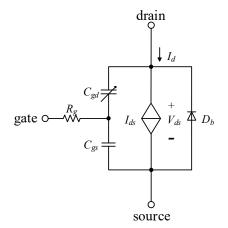

To describe the switching characteristics of MOSFETs, the capacitor model shown in figure 2.12 is commonly used.

Figure 2.12: Capacitor model of MOSFET

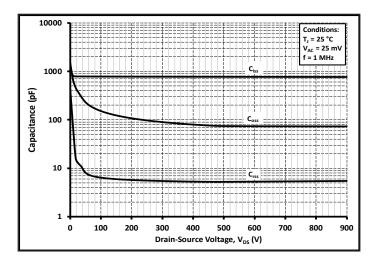

$C_{gd}$ ,  $C_{gs}$  and  $C_{ds}$  represent the internal parasitic capacitances of the MOSFET. They are dependent on the structure and material of the semiconductor device [2]. For the gate-source and gate-drain capacitances, the insulator material is an important factor. In addition to this, the depletion layer contributes to these capacitances. Hence, they are dependent on the voltage. Furthermore, the drain-source capacitance is dependent on the size of the drift region. Due to these effects, manufacturers present measurements of these capacitances in datasheets like in equation 2.1 and figure 2.13.

$$C_{iss} = C_{gs} + C_{gd}$$

$$C_{oss} = C_{ds} + C_{gd}$$

$$C_{rss} = C_{gd}$$

(2.1)

It is observed in figure 2.13 how the capacitances vary with the drain-source voltage.

Figure 2.13: MOSFET capacitances as function of drain-source voltage. Taken from C3M0065090D datasheet [4]

Modeling the switching waveform is challenging when considering the parasitic capacitors in the MOSFET since  $C_{gd}$  is dependent on the drain-source voltage as shown in figure 2.13. Advanced models are used to investigate the switching event in simulation environments such as SPICE based simulation software.

#### 2.2.5 Transconductance and IV-Characteristics

Devices such as MOSFETs, BJTs and IGBTs are three terminal devices where the input (gate signal) controls the output (drain-source or collector-emitter) current. As discussed in previous sections, the drain-source current of a MOSFET is dependent on the gate-source voltage. The relationship between the gate voltage magnitude and the resulting drain current is commonly presented in a transfer curve. In a transfer curve, the drain current is plotted as a function of gate-source voltage. As the gate-source voltage (input) increases, the drain current (output) increases. From the transfer curve, the threshold voltage can be found as the voltage where the current starts to increase from zero. The transconductance is the derivative of the transfer curve with respect to gate-source voltage and is defined in equation 2.2.

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \tag{2.2}$$

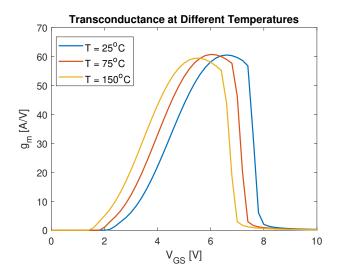

From this definition, transconductance is the ratio of how much change is seen on the output by a change on the input. Figure 2.14 shows the transconductance of a SiC MOSFET using the simulation model provided by the manufacturer. The figure also shows how the transconductance changes with temperature.

Figure 2.14: Transconductance at different temperatures from simulations using model for CPM3-0900-0010A provided by Wolfspeed

From the figure it is observed that as the temperature increases, the threshold voltage is reduced. Higher temperature will increase the thermal ionization in the material, creating more holes and free electrons. This means that the inversion layer will be established faster and the MOSFET starts to conduct earlier for higher temperatures compared to low temperatures. Consequently, this may have an impact on the design and driving of the MOSFET.

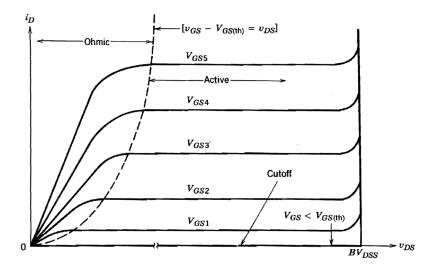

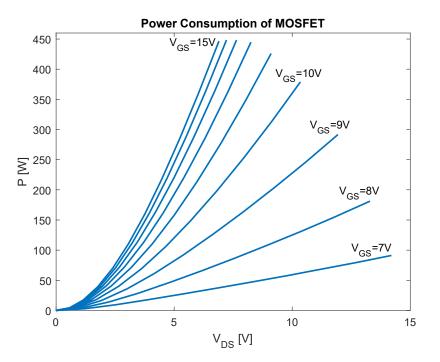

In figure 2.15,  $I_D$  is shown as a function of  $V_{DS}$  at different  $V_{GS}$  values for an n-channel MOSFET.

Figure 2.15:  $I_D V_{DS}$ -characteristics from [2],  $V_{GS5} > V_{GS4}$  etc.

Conventionally, the characteristics of a MOSFET have been divided into three regions; the cutoff, active and ohmic region [2]. When the gate-source voltage is below the threshold voltage, the MOSFET is in the cutoff region. No current is flowing through the device and it has a drain-source voltage equal to the applied voltage. In the active region, the drain current is only dependent of the gate-source voltage. A higher gate-source voltage allows for larger current through the MOSFET. The device consumes a lot of power in the active region because the drain-source voltage is approximately equal to the applied voltage. When the gate-source voltage is increased to a large value, the MOSFET will eventually enter the ohmic region. The power consumption is much lower in this region compared to the active region. The goal when switching a MOSFET is to move from the cutoff region into the ohmic region and vice versa.

#### 2.3 Switching Events of MOSFETs

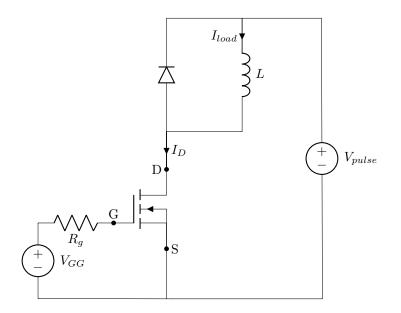

In this subsection, the turn-on and turn-off switching events of a MOSFET will be investigated. A simple resistor in series with the gate voltage source is connected to the gate of the MOSFET to explain the switching events. Thus, creating an RC-circuit from the gate to source loop. This RC-circuit will determine the shape of the gate-source voltage. Figure 2.16 shows the circuit used to explain the switching event.

Figure 2.16: Inductive switching circuit

#### 2.3.1 Turn-on Waveforms

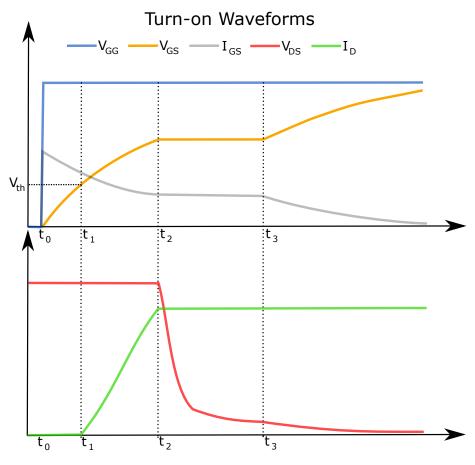

In order to turn-on a MOSFET, a voltage must be applied to the gate. This voltage depends on the type of MOSFET. An n-channel MOSFET will be used in this example. N-channel MOSFETs require positive applied gate voltage to charge the gate capacitors, turning the MOSFET on. Figure 2.17 shows the turn-on waveform divided into 4 time intervals.

Figure 2.17: Turn-on event

The first interval,  $t_0$  to  $t_1$ , is called the turn-on delay interval. Here, the gate-source voltage is charged from zero to the threshold voltage. During this interval, the depletion layer is changed by the applied gate voltage and the inversion layer is formed at  $t_1$ . In this interval, the MOSFET is not conducting, i.e. it is in the cutoff region of figure 2.15. At  $t_1$ , the threshold voltage of the MOSFET is reached. At this point, current starts flowing through the MOSFET. From  $t_1$  to  $t_2$ , the current through the MOSFET increases until it reaches the load current. The rate of change of the current is given by the transconductance curve and equation 2.2. The MOSFET is now in the active region. When the drain current reaches the load current, it is seen from the IV-characteristics that the gate-source voltage can not increase until the drain-source voltage has decreased significantly. Hence, the drain-source voltage will change.  $t_2$  to  $t_3$  represents the time interval of the voltage commutation. The drain voltage drops to the on-state voltage drop given by the IV-characteristics curve (zero in the ideal case). This time interval is also called the miller plateau. During the miller plateau, the capacitor between gate and drain will change and become larger, making dV/dt smaller for the last part of the voltage commutation. In this interval, most of the current goes through the gate-drain capacitor, keeping the gate-source voltage close to constant, hence the name miller "plateau". Once the miller plateau ends, the MOSFET has been moved along the constant  $V_{GS}$  lines in figure 2.15 into the ohmic region. Finally, the last stage of the waveform is from the end of the miller plateau to when the gate voltage has reached the reference voltage,  $V_{GG}$ , applied in the drive circuit. This last part reduces the on-state resistance of the MOSFET, decreasing the conduction losses.

#### 2.3.2 Turn-off Waveforms

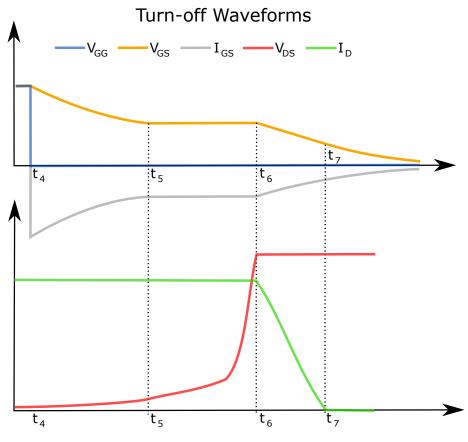

N-channel MOSFETs are turned off by reducing the gate voltage to zero or a negative value. Figure 2.18 shows the turn-off event. The turn-off event has the same intervals found in the turn-on event, though they happen in reverse order. I.e. the gate-source voltage goes from a high  $V_{GG}$  value to a low  $V_{GG}$  value.

Figure 2.18: Turn-off event

During turn-off, the gate capacitances are discharged by letting  $V_{GG}$  become zero or a negative value. This will create a negative current flowing from the gate capacitors through the gate resistor. The first time interval,  $t_4$  to  $t_5$  is termed the turn-off delay time. In this interval, the charge used to lower the on-state resistance is released. Thus, moving the MOSFET from the ohmic region back into the active region, increasing the on-state resistance during this interval. Once  $t_5$  is reached, the

voltage commutation interval begins. However, the gate-source voltage cannot decrease until the drain-source voltage has increased. Hence, the MOSFET is moved further into the active region. During this interval, the gate-drain capacitance will change and the effect of this is seen on the voltage rise of  $V_{DS}$ . Once  $V_{DS}$  has reached the supply voltage, the drain-source current will start to decrease.  $t_6$  to  $t_7$  is the current commutation interval. The rate of change will be determined by the transconductance curve and equation 2.2. At  $t_7$ ,  $I_D$  has decreased to zero and the MOSFET has been moved from the active region into the cutoff region. Consequently, the MOSFET is completely turned off.

#### 2.4 Si and SiC Comparison

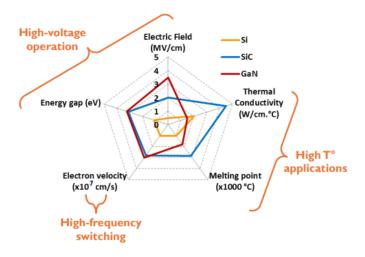

Wide band gap (WBG) materials have been emerging as the silicon technology is reaching its limits. These materials have characteristics that allow for higher efficiency, higher switching frequency and higher temperature operation. Silicon carbide (SiC) is one of the promising WBG materials [5]. Figure 2.19 shows a comparison of Si, SiC and gallium nitride (GaN).

Figure 2.19: GaN, SiC and Si comparison for different material properties [6]

As SiC and GaN have higher energy gap and higher breakdown electric field compared to Si, they can deliver the same voltage ratings with smaller drift region or higher doping levels. The drift region determines the breakdown voltage and is the dominating resistance for the conduction losses of a MOSFET. Hence, decreasing this region will reduce the drift resistance and subsequently lower the on-state resistance. According to [7], SiC can, in theory, reduce the resistance per unit area of the drift region to 1/300 compared to Si at the same breakdown voltage. Lower resistance per unit area for SiC allows for lower losses at the same ratings compared to Si. Besides, it allows for the same resistance at higher blocking voltages. For high blocking voltages, Si MOSFETs have high conduction losses. To combat this, IGBTs have an injection layer that can inject carriers in to the drift layer, allowing for higher blocking voltages while having low resistance. Hence, IGBTs have lower conduction losses and are more competitive for high power applications. However, SiC MOSFETs allow for higher blocking voltages at lower resistance compared to Si MOSFETs. This might make SiC MOSFETs able to compete with Si IGBTs. The advantage of a MOSFET structure is that the switching event is faster compared to an IGBT. IGBTs are bipolar devices and have longer switching times due to conductivity modulation. Carriers are injected into the drift layer, allowing lower on-state voltage. However, these carriers must be removed when turning off. As a consequence, there will be a so called tail-current at the end of an IGBT switching, lasting for some time after the collector-emitter voltage has increased. Tail-current makes the switching take longer and increases the switching losses. MOSFETs are unipolar devices and do not have a tail-current. Consequently, the switching losses in a MOSFET are lower compared to an IGBT. Subsequently, SiC MOSFETs can switch at higher frequency. Higher switching frequency reduces the size of the passive elements, which may allow the system to be denser. Additionally, SiC MOSFETs have an intrinsic body diode. This body diode may replace the requirement for separate diodes parallel to the switching device. Thus, it may reduce the size of modules and converters. Moreover, SiC has higher electron velocity compared to Si, enabling faster carrier movement within the material. This makes SiC based semiconductor devices able to switch faster, further strengthening the competetiveness of SiC MOSFETs.

Another characteristic of SiC is that it has much higher thermal conductivity and melting point compared to Si. Higher thermal conductivity and melting point allow for higher temperature operation. I.e. SiC can dissipate more heat and operate at higher temperatures. This is attractive for high power applications. Using SiC in place of Si might allow for denser and cheaper systems. E.g. fewer SiC devices may be needed compared to Si devices to do the same task, due to SiC's thermal properties. Furthermore, this might open new high frequency applications, since SiC can both switch faster and tolerate higher operating temperatures.

Due to all these characteristics of WBG materials, SiC MOSFETs might be able to replace Si IGBTs in many applications [8][9].

## 3 Modeling of SiC MOSFETs

Models of components are important when simulating systems. Simulations can be used to predict the response of the system, subsequently allowing the designer to find potential flaws or shortcomings in the design before implementing a prototype. Therefore, it is of great importance that the models used in simulations accurately represent the real components that will be used in the system. However, the model chosen for the simulations will often have certain limitations. There will be a compromise between fast simulation speed and accuracy of the model. A detailed and accurate model can be vastly time consuming to simulate, while a simple model described by a few equations will give fast results, but at a price of reduced accuracy. This section will give an introduction to modeling of SiC MOSFETs and present several models proposed in the literature and by different manufacturers. To begin with, section 3.1 will discuss some of the important aspects of MOSFET modeling.

### 3.1 What Makes a Good MOSFET Model?

The behavior of a MOSFET depends on the structure, design and the operating condition. Providing an accurate IV-characteristic is essential for the accuracy and reliability of the simulation. In connection to this, the transconductance should be accurate and smooth continuous in the operating range to avoid convergence issues. Furthermore, the model should have a well defined and efficient parameter extraction methodology. This will allow users to easily utilize measurements or values from a device to obtain a model. Moreover, temperature is an important factor in the modeling design of a device. In most cases, temperature will change the behavior of the device by a noticeable degree. E.g. the thermal ionization in the semiconductor material depends heavily on temperature. As a consequence of this, the inversion layer might be more easily created at higher temperatures, consequently lowering the threshold voltage of the device. In many applications, there will be some sort of temperature difference and thermal considerations are in several levels of the design process. Thus, the model should include temperature dependency and be well behaved for the temperature range of interest. Finally, computational efficiency is an important aspect of simulation models. In theory, a model could be described by all its physical and mathematical equations and relationships. However, solving such a detailed description would require a lot of computational power and time. Usually, when simulating a circuit, it is simulated over a wide range of possible operating points in order to evaluate the performance. Hence, the model should be fast and accurate. A compromise will often have to be made; either increasing accuracy at the cost of more simulation time or vice versa. Therefore, the model to be used in simulations should be chosen based on the level of the design process. E.g. to assess a new circuit design, thermal considerations may be neglected. Thus, allowing for a simpler model, which will give results faster. The thermal considerations come later in the design process and a more advanced model may be utilized then.

#### 3.2 SiC MOSFET Models

Models used in simulations may be chosen based on the level of the design process. Some models will be simple and fast, while others will be computationally expensive and highly accurate. SiC MOSFET modeling can be divided into five levels [10].

1. Behavioral Models:

Behavioral models are simple models that simulate the devices without considering the physical mechanisms of operation. Such models are usually implemented using mathematical fitting methods. As a result, behavioral models are fast to simulate at the cost of low accuracy.

2. Semi-physics-based Models:

Semi-physics-based models are partially based on the device physics. For example, some parts of the model are based in physics equations, while other parts are defined by mathematical fitting methods.

3. Physics-based Models:

Physics-based models use semiconductor physics. The electrical and thermal behavior will be obtained by solving equations based on semiconductor physics.

4. Semi-numerical Models:

When a physics-based model contains equations or relations that is solved by numerical methods, such as Fourier or Laplace, the model is said to be semi-numerical.

5. Numerical Models:

Numerical models are used when a complete and complex mathematical model of the system are to be used. The mathematical model is solved numerically due to its complexity, which makes it hard to find an analytical solution. These types of models require great detail of material properties and device geometry.

The list presents five different types of models. These are used to characterize the SiC MOS-FET models presented in the coming sub-sections. Generally, the computational complexity of the model types is in the order of the list; behavioral models are the fastest, while numerical models are the slowest. Numerical and semi-numerical models include many equations that require detailed information of device structure and material properties. That information might not be easily obtainable and is not shown in datasheets. As a result, many proposed models are usually behavioral, semi-physics-based or physics-based. Some manufacturers even provide their own models. Although the first three model types will be less accurate compared to numerical and semi-numerical, they can still provide the necessary results needed to evaluate a circuit or design. Physics-based models utilize equations based on semiconductor physics. However, certain constants used in these equations may have its own relations, and is based on material properties and device structure. This can make it hard to use the same model on other devices that may have slightly different structure and material properties. Behavioral models are based on fitting equations to measurement data of the devices. Models of this type may have excellent match to the measurement data or datasheet curves. However, the performance of the model can vary. There are many elements in a MOSFET model, such as IV-characteristics, CV-characteristics, breakdown, body diode and reverse recovery of body diode to mention a few. In modeling, there will be a trade-off between having accurate results and complexity of the model.

The following sub-sections will explore different MOSFET models. Firstly, established models for low voltage (LV) complementary metal-oxide-semiconductors (CMOS) will be briefly mentioned, followed by models proposed in the literature. Various models with and without temperature considerations will be presented. Additionally, some manufacturer models will be discussed. The models presented will be of the first three types; behavioral, semi-physics-based and physics-based.

#### 3.2.1 Established Models

For integrated circuits and LV CMOS technology, Berkeley short-channel IGFET model (BSIM) is the industry standard. It is a detailed and comprehensive model of a variety of effects related to MOSFET physics, including the sub-100nm regime. All the effects included in the model are described in its user manual [11], which is more than 170 pages long. BSIM requires a great number of parameters and detailed information about MOSFET structure and physical properties. This can introduce many challenges when extracting parameters from datasheets or measurements to model a new or pre-existing device where a simulation model is not provided by the manufacturer. BSIM can be classified as a numerical model. Other models are also well established, such as the Enz-Krummenacher-Vittoz (EKV) model. The EKV MOSFET model characterizes all modes of operation for a MOSFET and includes modeling of several physical effects [12, 13]. It is in principle formulated as a single expression, subsequently preserving continuity of derivatives in the model. Compared to BSIM, the number of parameters are reduced, making it easier to extract parameters and establish a model for the device. Moreover, other models based on curve fitting also exist. The Curtice-Ettenberg WBG FET model uses a certain expression for the drain current and uses data to fit the expression and obtain accurate static characteristics [14, 15].

#### 3.2.2 Charge-Based Model

The charge-based model proposed in [16] is a compact model able to predict the behavior of the device on the basis of a single equation. It can be classified as a physics-based model. The proposed model contains the intrinsic capacitances  $C_{GD}$ ,  $C_{GS}$  and  $C_{DS}$  and an  $R_{on}$  on drain. Parasitic elements and breakdown modeling are not included. The drain current is obtained through an analytical expression that represents the inversion charge density at the source and drain electrodes. Equation 3.1 shows the expression of the drain current as the difference between the forward current  $I_F$  and the reverse current  $I_R$ .

$$I_{DS} = I_F - I_R = \beta \int_{V_S}^{\infty} \frac{-Q_i}{C_{ox}} dV - \beta \int_{V_D}^{\infty} \frac{-Q_i}{C_{ox}} dV$$

(3.1)

where  $\beta$  is the transmission coefficient,  $C_{ox}$  the oxide capacitance per unit area and  $Q_i$  is the inversion charge. Furthermore, the model represents the parasitic capacitances as defined in [17]. Equation 3.2 shows the definition of the capacitances.

$$\begin{cases}

C_{GS} = C_m + C_{oxs} + \frac{1}{\frac{1}{C_{oxc}} + \frac{1}{C_c}} \\

C_{GD} = \frac{1}{\frac{1}{C_{oxd}} + \frac{1}{C_{gdj}}} \\

C_{DS} = C_{dsj}

\end{cases}$$

(3.2)

$C_m$ ,  $C_{oxs}$ ,  $C_{oxc}$  and  $C_{oxd}$  are related to the gate oxide layer and do not change with the applied voltage. However,  $C_c$ ,  $C_{gdj}$  and  $C_{dsj}$  originates from the depletion layer and depends on the gatesource voltage, gate-drain voltage and drain-source voltage respectively. By defining the draincurrent and the parasitic capacitances, the model may be able to accurately represent both static and dynamic behavior of the device. Although the model is very compact with few parameters, the equation describing the drain current can be difficult to compute directly and might require simplifications of the transition between the forward current and reverse current. Additionally, the model suffers from lack of thermal considerations. Hence, the model cannot be used in thermal analysis of the circuit design.

#### 3.2.3 Non-segmented Model

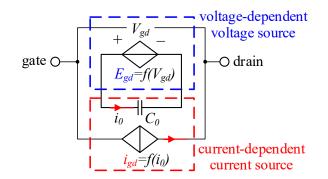

One way to solve convergence issues is to use non-segmented, smooth continuous equations to describe the static and dynamic characteristics of SiC MOSFETs [18]. In this cases it leads to a behavioral model. The equations used has no physical meaning. Figure 3.1 shows the model of a SiC MOSFET proposed in [18].

Figure 3.1: Non-segmented model proposed in [18]

The model includes a voltage-dependent current source  $I_{ds}$ , a gate-drain voltage-dependent capacitance  $C_{gd}$ , a gate-source constant capacitance  $C_{gs}$ , an internal gate resistance  $R_g$  and a body diode  $D_b$ . Parasitic elements and breakdown modelling are not included. The voltage-dependent current source describes static IV-characteristic of the SiC MOSFET. It is obtained as in equation 3.3,

$$I_{ds} = k \cdot \{1 + \tanh\left[a \cdot (V_{gs} + m) + b \cdot (V_{gs} + n)^2\right]\} \cdot \frac{p(V_{gs}) \cdot V_{ds}}{1 + q(V_{gs}) \cdot V_{ds}}$$

(3.3)

where k, a, b, m and n are parameters related to the transfer characteristic, while p and q are parameters related to the output characteristic. Furthermore, the gate-drain capacitance  $C_{gd}$  has strong non-linearity, and the equivalent current source shown in figure 3.2 is used to describe the voltage-dependent capacitance  $C_{gd}$ . Moreover, the non-linear characteristic of  $C_{gd}$  is realized by the constant capacitance  $C_0$ . Equation 3.4 and 3.5 represent the model for the nonlinear capacitance  $C_{gd}$ .

$$E_{gd} = f(V_{gd}) \tag{3.4}$$

$$i_0 = C_0 \frac{\mathrm{d}E_{gd}}{\mathrm{d}t} = C_0 \frac{\mathrm{d}E_{gd}}{\mathrm{d}V_{gd}} \cdot \frac{\mathrm{d}V_{gd}}{\mathrm{d}t}$$

(3.5)

Figure 3.2: Voltage-dependent capacitance model used in [18]

The current-dependent current source in the gate-drain capacitance model is given as in equation 3.6.

$$i_{gd} = f(i_0) = \frac{1}{C_0} i_0 = \frac{\mathrm{d}E_{gd}}{\mathrm{d}V_{gd}} \cdot \frac{\mathrm{d}V_{gd}}{\mathrm{d}t}$$

(3.6)

In a physical model,  $i_{gd}$  will be as in equation 3.7.

$$i_{gd} = C_{gd} \frac{\mathrm{d}V_{gd}}{\mathrm{d}t} \tag{3.7}$$

Combining equation 3.6 and 3.7 results in equation 3.8.

$$C_{gd} = \frac{\mathrm{d}E_{gd}}{\mathrm{d}V_{gd}} \tag{3.8}$$

An expression for  $C_{gd}$  is found through data extraction from the CV-characteristics in the datasheet of the chosen SiC MOSFET, followed by curve fitting. The results are shown in equations 3.9 and 3.10.

$$C_{gd} = s \cdot \frac{1}{1 + \exp\left\{\frac{h - V_{gd}}{f}\right\}} + r \tag{3.9}$$

$$E_{gd} = s \cdot f \cdot \ln\left[1 + \exp\left\{\frac{V_{gd} - h}{f}\right\}\right] + r \cdot V_{gd}$$

(3.10)

where s, h, f and r are parameters related to the C-V characteristics.

The internal resistance  $R_g$  and the gate-source capacitance  $C_{gs}$  are constant and are found in the datasheet. However, the body diode  $D_b$  uses an inherent diode model in PSpice, and the modeling of the drain-source capacitance  $C_{ds}$  is considered in the body diode.

The results show good agreement between the datasheet and the simulated curves. However, there is a noticable difference when it comes to the body diode curve.

This simple model will give fast simulation results with less convergence problems due to the continuous smooth equations describing the SiC MOSFET.

A similar approach has been used in [19], where a genetic algorithm iterates to fit the model parameters to the original data. The model is divided into a static and dynamic model. The static model represents the forward and reverse conduction characteristics of the SiC power MOSFET, whereas the dynamic part aims at reproducing the switching waveforms of the device. Furthermore, the parasitic inductances and resistances of the three pins of the device are included in the dynamic model. Additionally, the dynamic model includes a model for the internal body diode of the SiC MOSFET.

Nonetheless, the temperature will change the behavior of the SiC MOSFET and these effects are completely ignored in these models. Thus, they can only provide accurate results for simulations at the temperature used when extracting the data from the datasheet or from measurements. As temperature is an important aspect in the design of power electronic converters, more advanced models should be looked at.

#### 3.2.4 Electro-Thermal Model

As temperature is an important aspect of the design of power electronic converters, a model taking that into account is necessary. By introducing temperature dependency, the simulations can more accurately represent the usage of a real device in a circuit design.

A fast and accurate SiC MOSFET model is proposed in [20]. The model is based on 25 model equations. Many of these equations are temperature dependent, meaning that as the temperature changes, the characteristics of the SiC MOSFET will also change. In this model, the intrinsic capacitances  $C_{GD}$ ,  $C_{GS}$  and  $C_{DS}$ , an  $R_{DD}$  on drain, breakdown characteristics and an empirical description of the third quadrant operation are included. Thus, the model can be classified as a semi-physics-based model, since it has a mix of physics-based and behavioral equations. Parasitic elements are not included. The channel current is generated by a low current region and high current region. Equations 3.11 - 3.16 show the equations used for the MOSFET channel current.

$$I_{D\boldsymbol{x}} = \begin{cases} 10K_{P\boldsymbol{x}}[(V_{GS} - V_{T\boldsymbol{x}})V_{DSM} - \mathbf{P_{VFx}}^{y\boldsymbol{x}-1}V_{DSM}^{y\boldsymbol{x}}(V_{GS} - V_{T\boldsymbol{x}})^{2-y\boldsymbol{x}}] &, V_{DSM} \leq V_{DSS\boldsymbol{x}} \\ \frac{1}{2}K_{P\boldsymbol{x}}(V_{GS} - V_{T\boldsymbol{x}})^{2} &, V_{DSM} \geq V_{DSS\boldsymbol{x}} \end{cases}$$

(3.11)

$$V_{T\boldsymbol{x}} = \mathbf{V}_{\mathbf{T}\boldsymbol{x}\boldsymbol{0}} - \mathbf{V}_{\mathbf{T}\boldsymbol{x}\boldsymbol{1}}(T_M - 27) \tag{3.12}$$

$$V_{DSSx} = \frac{V_{GS} - V_{Tx}}{\mathbf{P}_{\mathbf{VFx}}} \tag{3.13}$$

$$K_{P\boldsymbol{x}} = \mathbf{K}_{\mathbf{P}\mathbf{x}\mathbf{0}} - \mathbf{K}_{\mathbf{P}\mathbf{x}\mathbf{1}}(T_M - 27)$$

(3.14)

$$y\boldsymbol{x} = \frac{10}{10 - \mathbf{P_{VFx}}} \tag{3.15}$$

$$R_{DD} = \mathbf{R_{D0}} - \mathbf{R_{D1}}(T_M - 27) \tag{3.16}$$

where  $\mathbf{x}$  should be replaced by L and H, representing low current region and high current region respectively. Furthermore, the bold variables are product-dependent parameters. Additionally, the intrinsic capacitances are defined as in equation 3.17.

$$C_{GD} = \begin{cases} \mathbf{C}_{\mathbf{GD0}} & for \ V_{DS} \leq 0\\ \mathbf{C}_{\mathbf{GD0}} + \Delta C_{GD} & for \ 0 < V_{DS} \leq 380\\ \mathbf{C}_{\mathbf{GDF}} & for \ V_{DS} > 380 \end{cases}$$

(3.17)

where  $\Delta C_{GD}$  is defined as in equation 3.17.

$$\Delta C_{GD} = 25.9 \cdot 10^{-3} (\mathbf{C}_{\mathbf{GD0}} - \mathbf{C}_{\mathbf{GDF}}) \left( 0.064 V_{DS} - \frac{V_{DS}^{0.15}}{0.15} \right)$$

(3.18)

Data extraction from the manufacturers datasheet is used to fit the parameters of the model. The model is written in Verilog-A, a language for describing analog circuits. Moreover, an inverter design is tested using the proposed SiC MOSFET model in the simulation program Questa-ADMS, and then compared to a simulation of the inverter design in OrCAD PSpice using the model of the manufacturer of the SiC MOSFET. There is no visible difference between the switching characteristics of the inverter using different engines and SiC MOSFET models. However, a significant reduction in simulation time were observed for the Questa-ADMS simulation using the proposed model. According to the authors, this is, in part, because of better modeling and a more efficient simulation engine.

A SiC MOSFET model for short-circuit analysis is proposed in [21]. It is based on non-segmented equation modeling, making it a behavioral model. Equation 3.3 describes the drain-current of the device, similar to that of the non-segmented model presented in 3.2.3 with a few adjustments. Temperature dependency is introduced by an additional function multiplied with the drain current. The short-circuit current is defined as in 3.19;

$$I_{SC} = I_{DS} \cdot f(T_j) \tag{3.19}$$

where the function  $f(T_i)$  is defined by equation 3.20.

$$f(T_j) = 1 + (T_j - 25) \cdot \frac{\left(p_1 \cdot T_j^{p_2}\right)}{\ln(p_3 \cdot T_j) + p_4 \cdot T_j^{p_5}}$$

(3.20)

where  $p_1$ - $p_5$  are related parameters from data extraction of short-circuit characteristics. The definition of the gate-drain capacitance is also similar to that of the model proposed in [18]. However, another term is added to the equations, shown in equation 3.21 and 3.22.

$$C_{GD} = s_{11} \cdot \frac{1}{1 + e^{\frac{s_{21} - V_{GD}}{s_{31}}}} + s_{41} \cdot \frac{1}{1 + e^{\frac{s_{51} - V_{GD}}{s_{61}}}} + s_{71}$$

(3.21)

$$E_{GD} = s_{11} \cdot s_{31} \cdot \ln\left[1 + e^{\frac{V_{GD} - s_{21}}{s_{31}}}\right] + s_{41} \cdot s_{61} \cdot \ln\left[1 + e^{\frac{V_{GD} - s_{51}}{s_{61}}}\right] + s_{71} \cdot V_{GD}$$

(3.22)

where  $s_{11}$ - $s_{71}$  are parameters related to the CV-characteristics. This model is able to both represent the static characteristics and CV-characteristics, and the short-circuit characteristics. However, the temperature-dependency is only used during short-circuit condition. This means that temperature changes occurring due to normal operation, ambient temperature changes and load changes are not accounted for. Hence, the model may be accurate and perform well when operating at  $25^{\circ}C$ , while performing worse for other temperatures.

#### 3.2.5 Curtice-Ettenberg Based Model

In [22], an approach to make an universal behavioral model is proposed. It is based on the Curtice-Ettenberg WBG FET model [14, 15] with some adjustments. The drain current is defined by equation 3.23.

$$I_{DS} = f_g(V_{GS}) \cdot f_d(V_{GS}, V_{DS}) \tag{3.23}$$

The first component,  $f_g$ , is related to the transfer characteristics, while the second component,  $f_d$ , is related to the shape of output characteristics.

$$f_g(V_G S) = \frac{H_t V_{GS}^{2B_t}}{\left[V_{GS}^{2C} + e^{2C}\right]^{\frac{B_t}{C}}}$$

(3.24)

where C is constant, while  $B_t$  and  $H_t$  are linear temperature-dependent functions described by equation 3.25 and 3.26,

$$B_t = B_0 + \alpha_B \cdot (T_j - T_{nom}) \tag{3.25}$$

$$H_t = H_0 + \alpha_H \cdot (T_j - T_{nom}) \tag{3.26}$$

where  $B_0$  and  $H_0$  represent parameter values at nominal temperature  $T_{nom}$ ,  $\alpha_B$  and  $\alpha_H$  are temperature coefficients, and  $T_j$  is the junction temperature.  $f_d$  is defined in equation 3.27.

$$f_d = \tanh\left[A_d V_{DS}^{k_d}\right] \cdot \left(1 + \lambda \cdot \left(V_{DS} - V_{DS,tr}\right)\right) \tag{3.27}$$

where  $\lambda$  is the channel length modulation factor,  $A_d$  a scaling function,  $k_d$  constant coefficient and  $V_{DS,tr}$  a drain-source voltage parameter chosen before the parameter extraction. The scaling function is defined as in equation 3.28.

$$A_d = A_g(T_j) \cdot V_{GS}^{k_g(T_j)} \tag{3.28}$$

where  $A_g$  and  $k_g$  are quadratic temperature dependent polynomials as given in equation 3.29 and 3.30 respectively.

$$A_g(T_j) = A_{g0} + \alpha_{A1} \cdot (T_j - T_{nom}) + \alpha_{A2} \cdot (T_j - T_{nom})^2$$

(3.29)

$$k_g(T_j) = k_{g0} + \alpha_{k1} \cdot (T_j - T_{nom}) + \alpha_{k2} \cdot (T_j - T_{nom})^2$$

(3.30)

where  $A_0$  and  $k_0$  are parameters at  $T_{nom}$ ,  $\alpha_{A1}$ ,  $\alpha_{A2}$ ,  $\alpha_{k1}$  and  $\alpha_{k2}$  are temperature coefficients. Measurement data is used for parameter extraction of the proposed model. The fitting of the curves are done to find all the parameters as follows. Firstly, fitting of  $f_g$  is performed at nominal temperature to find initial estimations of C,  $B_0$  and  $H_0$ . This is repeated for each temperature, yielding several values of  $B_t$  and  $H_t$  from which  $\alpha_B$  and  $\alpha_H$  can be estimated. A similar procedure is carried out for the fitting of  $f_d$ . The model has been fitted to four different devices with roughly the same rating and the results show good match for all four devices over the temperature range. Some discrepancies are noted for high temperature. However, the results are promising and this model is a candidate for an universal SiC MOSFET model. Although the model is able to recreate the static characteristics over a wide temperature range for different MOSFETs, the model is lacking in areas such as reverse recovery, dynamic switching behavior and breakdown. These are left to be considered in an improved model.

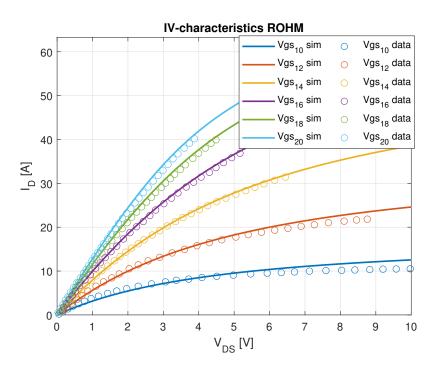

#### 3.3 Manufacturer Models

Some manufacturers provide models of their products to use in simulation programs. These models can vary in terms of implementation and accuracy. In this section, a selection of different manufacturer provided models will be briefly looked at. Both IV- and CV-characteristics will be simulated and compared to the datasheet for a Cree model, an STmicroelectronics model and a ROHM model. The simulation circuits can be found in appendix A and B.

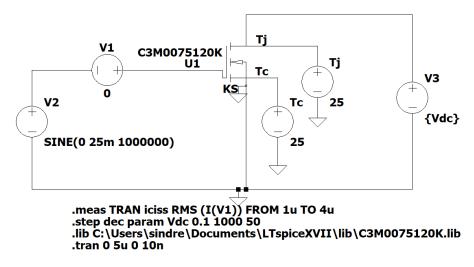

#### 3.3.1 Cree Wolfspeed: C3M0075120K SPICE Model

The model from Cree can be classified as a semi-physics-based model. It includes drain, gate and source parasitic elements, intrinsic capacitances  $C_{GD}$  and  $C_{GS}$ , and an intrinsic body diode that includes  $C_{DS}$ . Breakdown is not covered in the model. The static characteristics are realised by a voltage-controlled current source (VCCS) from drain to source. Cree has based their equations for the static characteristics on the EKV model [12, 13], with a few simplifications. Equation 3.31 represents the drain-source current.

$$I_D = 2g_m \Phi_t^2 K_s \left[ \ln \left( 1 + e^{\frac{V_{GS} - V_{th}}{2K_s \Phi_t}} \right)^k - \ln \left( 1 + e^{\frac{V_{GS} - V_{th} - nV_{DS}^a}{2K_s \Phi_t}} \right)^k \right] (1 + \lambda V_{DS})$$

(3.31)

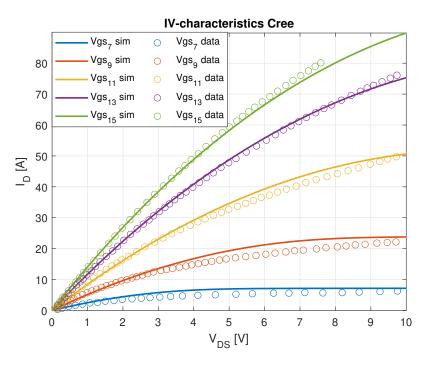

where  $g_m$  is the transconductance parameter,  $\Phi_t$  the thermal voltage,  $K_s$  the sub-threshold slope parameter, k is the law exponent,  $\lambda$  the channel length modulation parameter, and n and a are triode region parameters [23]. Figure 3.3 shows the simulated output curves compared to the datasheet.

Figure 3.3: Simulation of C3M0075120K spice model, IV characteristics compared with datasheet

The circles represent points from the datasheet, obtained using a free online tool called "Web-PlotDigitizer" [24]. The simulated lines show acceptable match with the datasheet points. Thus, the model is able to accurately reproduce the static characteristics.

Another important aspect of the modeling is the dynamic characteristics. The gate-drain capacitance is represented by a VCCS in series with a small resistance. Equation 3.32 represents the characteristic of the capacitance value as the gate-drain voltage changes.

$$k_1 \left[ 1 + (\operatorname{limit}(-V_{gd}, 0, 600)) \cdot \left( 1 + k_a \cdot \frac{(1 + \tanh\left[k_b \cdot (-V_{gd}) - k_c\right)\right]}{2} \right) \right]^{-k_2} \cdot \frac{\mathrm{d}V_{gd}}{\mathrm{d}t}$$

(3.32)

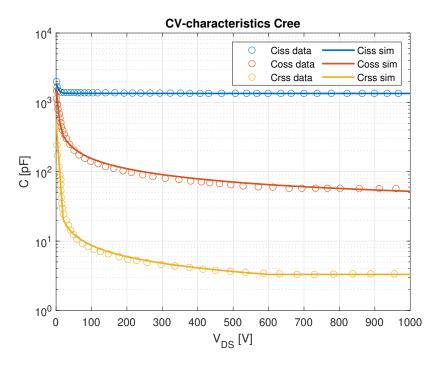

where  $k_1, k_2, k_a, k_b$  and  $k_c$  seems to be fitting parameters. The gate-source capacitance is constant. The implementation of the capacitors gives CV-characteristics as shown in figure 3.4.

Figure 3.4: Simulation of C3M0075120K spice model, CV characteristics compared with datasheet

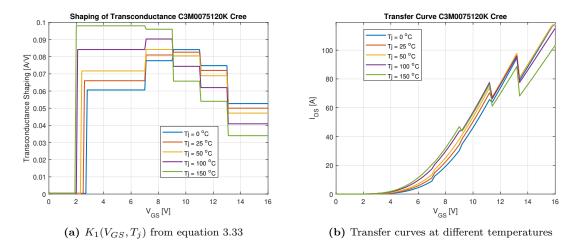

The model is able to accurately reproduce the CV-characteristics. However, the model has convergence issues. In the model file from Cree, the first term of the drain current is implemented like shown in equation 3.33.

$$2g_m \Phi_t^2 K_s = K_1(V_{GS}, T_j) \cdot (V_{GS} - V_{th}) + K_2(T_j)$$

(3.33)

where  $K_1$  is a conditional expression that uses different functions based on the gate-source voltage and junction temperature and  $K_2$  is a function of the junction temperature. Since the transconductance,  $g_m$ , depends on the gate-source voltage, it is likely that  $K_1$  is used to shape the transconductance. The transfer curves and shaping functionality for C3M0075120K can be seen in figure 3.5.

Figure 3.5: Discontinuities in the model

The transfer curves in figure 3.5b are discontinuous. This poses a problem during simulation of the device, as it will have convergence related issues.  $K_1(V_{GS}, T_j)$  is constant for certain gatesource voltage intervals. For example, when gate-source voltage is between 7 and 9V, the function has a constant value based on the junction temperature. When the gate-source voltage increases to a value larger than 9V, a step occurs. These steps happen at predefined values for  $V_{GS}$  and makes the transfer curves discontinuous. Nevertheless, this was explored in [23], and a solution was proposed to make the transconductance shaping continuous, subsequently reducing convergence related issues.  $K_1(V_{GS}, T_j)$  was changed from having steps to being smooth continuous. Equation 3.34 shows the implementation.

$$K_1(V_{GS}, T_j) = (p_{100} \cdot T_j^2 + p_{101} \cdot T_j + p_{102}) \cdot \left(\frac{V_{GS}}{(p_{200} \cdot T_j + p_{201})^2}\right) \cdot e^{-\left(\frac{V_{GS}^2}{2 \cdot (p_{200} \cdot T_j + p_{201})^2}\right)}$$

(3.34)

where  $p_{100}$ ,  $p_{101}$ ,  $p_{102}$ ,  $p_{200}$  and  $p_{201}$  are fitting parameters. Although the static characteristics from the simulations were smooth continuous, the model still has discontinuities without the improvements proposed by [23].

In summary, the Cree C3M0075120K SPICE model is classified as a semi-physics-based model. Parts of the model use equations that are not based in physics, e.g. the implementation of the transconductance shaping or the gate drain capacitance. However, most of the drain-source current are physics based, on a modified EKV model. Despite accurate results when comparing to the datasheet, the simulations using this model have high chances of convergence related issues. The main drawback is the implementation of the transconductance shaping. To reduce this issue, the improved version proposed by [23] should be used. This is also the version used in later sections of this thesis.

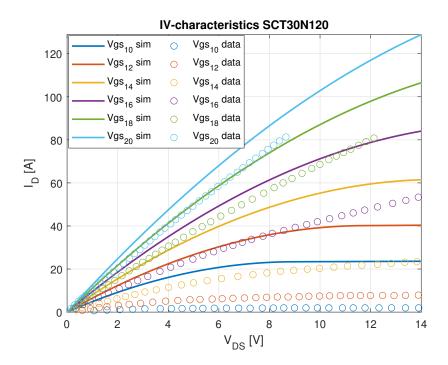

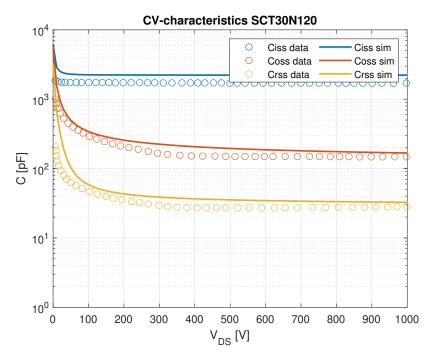

#### 3.3.2 STMicroelectronics: SCT30N120\_V3 SPICE Model

STMicroelectronics provides several versions of their components [25], ranging from basic to a more or less complete model where self-heating and package thermal modeling are included. SCT10N120\_V3

includes temperature dependence, capacitance profiles, parasitic elements, breakdown and body diode modeling. The drain current is realized by a single VCCS. It is based on a LEVEL 1 MOS model with additional temperature-dependent coefficients un,  $V_{lin}$  and kpsat. Some parameters are based on look-up tables in LTspice and certain equations are not physics-based. Thus, the model is classified as semi-physics-based. Equation 3.35 and 3.36 show the expression for the drain current.

$$I_{D} = \begin{cases} 0 & , \text{ if } V_{GS} < V_{th} \\ un \cdot A \cdot V_{DS} \cdot x_{\lambda} \cdot \left( 2(V_{GS} - V_{th}) - \frac{V_{lin}}{kpsat} V_{DS} \right) \frac{V_{lin}}{2} & , V_{DS} < (V_{GS} - V_{th}) \frac{kpsat}{V_{lin}} \\ un \cdot A \cdot x_{\lambda} \cdot (V_{GS} - V_{th})^{2} \frac{kpsat}{2} & , V_{DS} > (V_{GS} - V_{th}) \frac{kpsat}{V_{lin}} \\ x_{\lambda} = (1 + \lambda V_{DS}) \end{cases}$$

(3.36)

where  $V_{GS}$  and  $V_{DS}$  are gate-source and drain-source voltages,  $V_{th}$  the threshold voltage, A the chip area,  $\lambda$  the channel length modulation parameter, un, kpsat and  $V_{lin}$  are dependent on junction temperature  $(T_j)$ . Equations 3.37 shows the modeled temperature dependency of un and kpsat.

$$un(T_j) = b \cdot \left(\frac{T_j + 273}{300}\right)^{unt}$$

(3.37)

$$kpsat(T_j) = kpsat0 \cdot \left(\frac{T_j + 273}{300}\right)^{ksat}$$

(3.38)

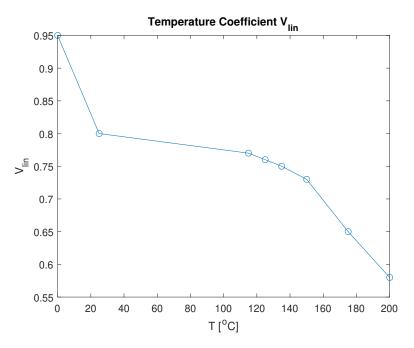

where b, unt, kpsat0 and ksat are fixed value parameters hardcoded in the library file.  $V_{lin}$  is defined by a look-up table in the code. Based on the junction temperature,  $V_{lin}$  will be linearly interpolated between two points in the table. It looks like in figure 3.6.

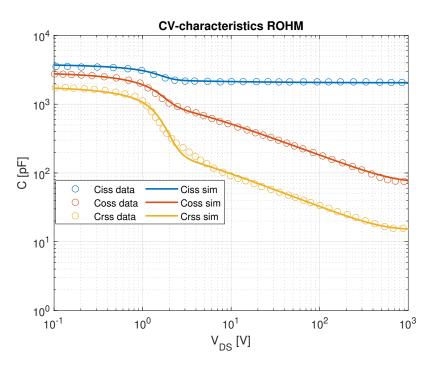

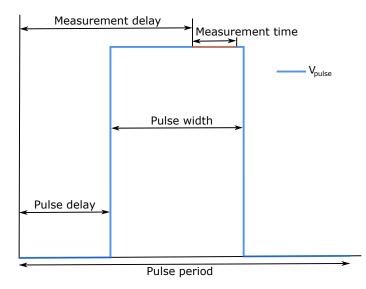

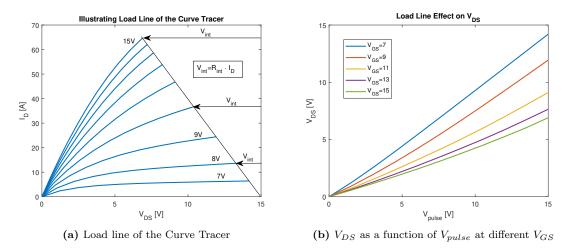

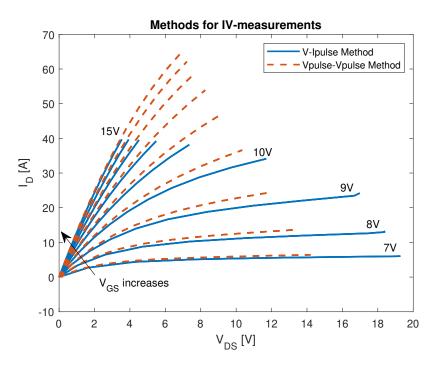

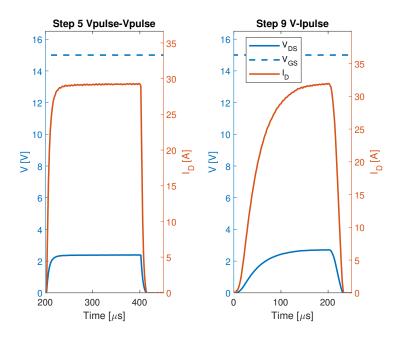

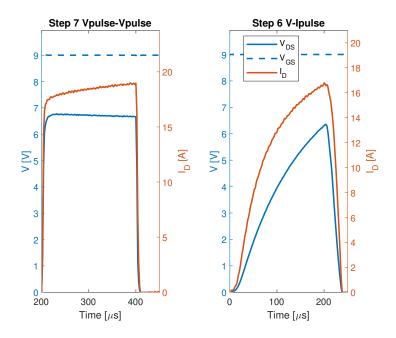

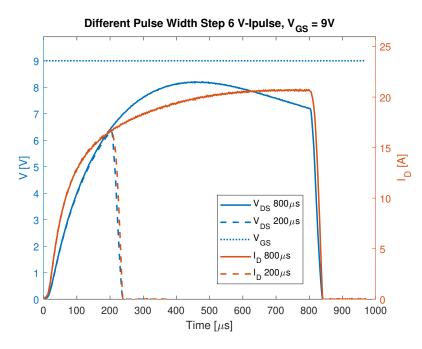

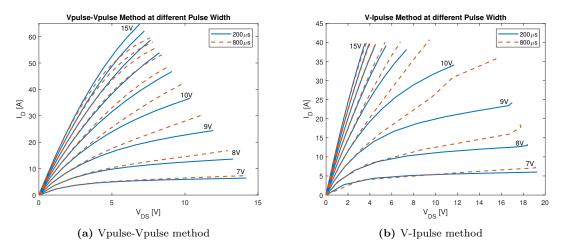

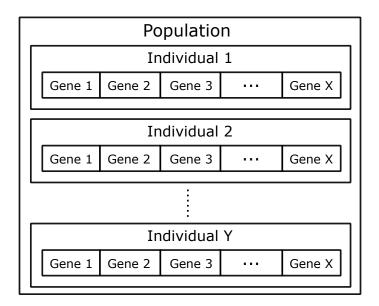

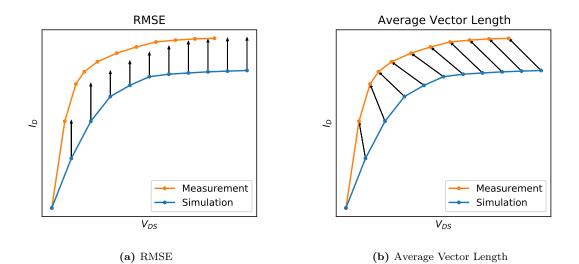

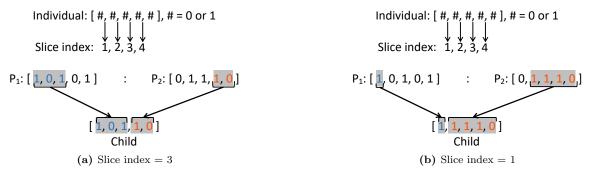

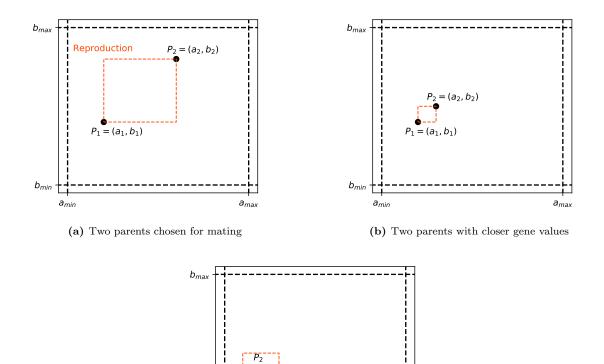

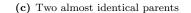

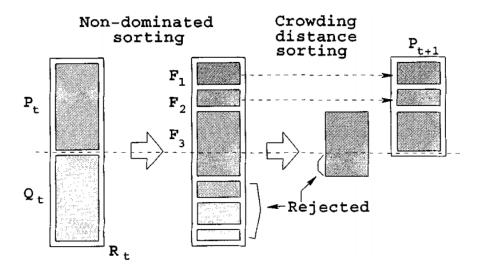

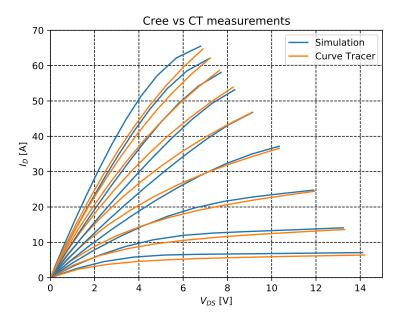

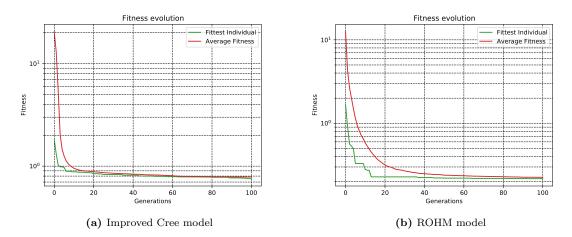

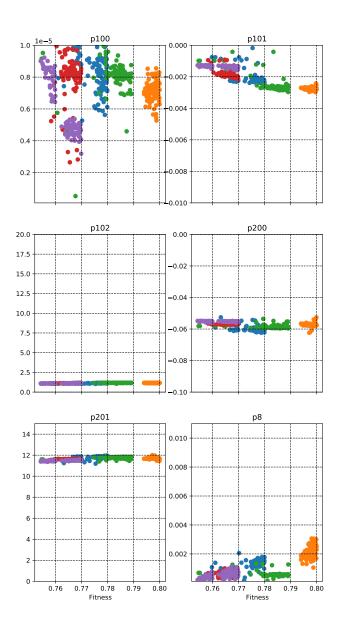

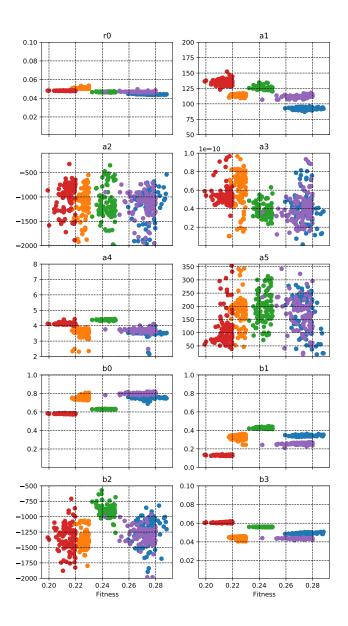

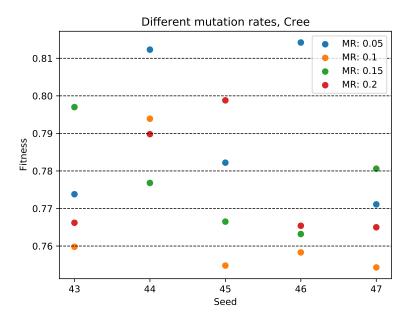

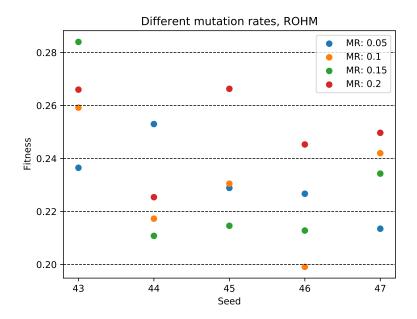

Figure 3.6:  $V_{lin}$  look-up table from LTspice illustrated