Nicolay Anker Kavli

# PSCAD Simulation of Distance Protection Performance in a Grid with Inverter Interfaced Generation

Master's thesis in Master of Energy and Environmental Engineering Supervisor: Hans Kristian Høidalen June 2020

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Nicolay Anker Kavli

# PSCAD Simulation of Distance Protection Performance in a Grid with Inverter Interfaced Generation

Master's thesis in Master of Energy and Environmental Engineering Supervisor: Hans Kristian Høidalen June 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

## Abstract

In this thesis, the performance of distance protection in a grid with inverter interfaced generation has been studied through PSCAD simulations. Statnett expects problems related to their distance protection relays close to the Fosen Wind project, where several wind farms will be finalized in 2020. At which point distance protection problems should be expected due to the increasing share of inverter interfaced generation, serves as the main problem of the thesis.

The developed PSCAD model consists of a transmission line with 3.6 MVA inverters connected to the left side, and a grid equivalent connected to the right side. Distance protection relays have been installed on both ends of the line to analyze how their performance is influenced by the inverters. Balanced three-phase to ground short circuits located on the center of the line have been used for the protection studies.

Simulation set 1 showed that a single inverter connected to the line caused unsatisfactory tripping for the inverter side relay.

Simulation set 2 showed that ten inverters connected to the line caused unsatisfactory tripping for the inverter side relay, however there was a slight performance improvement compared to Simulation set 1.

Simulation set 3 showed that when inverter generation was compared with synchronous generation, higher inverter generation shares caused reduced inverter side relay performances. For fault resistances of 1  $\Omega$  or less, the inverter side relay was able to trip satisfactorily for inverter generation shares of 50% or less.

Simulation set 4 showed that the ratio of the short circuit current contributions from the two sides of the line had a negative influence on the relay installed on the side with the lowest contribution. The influenced relay was able to trip satisfactorily for fault resistances of 0.1  $\Omega$  or less, with up to roughly 70 times larger short circuit current contribution from the other side.

The distance protection relay located on the grid side of the line did not experience any problems during any of the simulations.

However, due to the model assumptions and weaknesses, the obtained results cannot be used to give any general statements regarding the performance of distance protection in a grid with inverter interfaced generation. More research is needed to be able to give accurate statements related to which problems should be expected and under which circumstances they will occur.

## Sammendrag

I denne oppgaven har ytelsen til distansevern i et kraftnett med vekselrettertilkobede produksjonskilder blitt studert gjennom simuleringer i PSCAD. Statnett forventer at problemer for distansevern vil oppstå i nærheten av vindprosjektet Fosen Vind, hvor fleretalls vindparker blir ferdigstilt i 2020. Problemstillingen i oppgaven går ut på å finne et svar på når det dukker opp problemer for distansevernet, som følge av en stadig økende andel av vekselretter-tilkoblede produksjonskilder.

PSCAD modellen består av en transmisjonslinje med vekselrettere på 3,6 MVA tilkoblet venstre ende, og en nett-ekvivalent tilkoblet høyre ende. Distansevern har blitt installert i begge endene av linjen for å analysere hvordan ytelsen deres blir påvirket av vekselrettere. Symmetriske tre-fase-til-jord-feil midt på linjen har blitt brukt som utgangspunkt for studien.

Simuleringssett 1 viste at når én enkel vekselretter var tilkoblet linjen medførte det uakseptabel håndtering av feilen for reléet på vekselretter-siden.

Simuleringssett 2 viste at når ti vekselrettere var tilkoblet linjen medførte det uakseptabel håndtering av feilen for reléet på vekselretter-siden, men med en liten forbedring i ytelsen sammenliknet med Simuleringssett 1.

Simuleringssett 3 viste at når produksjon fra vekselrettere ble sammenliknet med produksjon fra synkronmaskiner medførte en høyere andel vekselretterproduksjon en redusert ytelse for reléet på vekselretter-siden. For feilmotstander på 1  $\Omega$  eller mindre klarte reléet på vekselretter-siden å håndtere feilen korrekt for en vekselretter-andel på 50% eller lavere.

Simuleringssett 4 viste at forholdet mellom kortslutnings-strømbidraget fra de to endene av linjen hadde en negativ påvirkning på reléet installert på siden med lavest bidrag. Reléet klarte å håndtere feilen korrekt for feilmotstander på  $0.1 \Omega$  eller mindre, med opp mot 70 ganger høyere bidrag fra den andre siden.

Distansevernet på nett-siden av linjen opplevde ingen problemer under noen av simuleringene.

På grunn av antakelsene og svakhetene i modellen kan resultatene ikke bli brukt til å gi noen generelle uttalelser om ytelsen til distansevern i et kraftnett med produksjon fra vekselrettere. Mer forskning er nødvendig for å kunne gi nøyaktige uttalelser om hvilke problemer som kan forventes, og under hvilke omstendigheter de vil inntreffe.

## Preface

This master thesis finalizes my work at NTNU's master program Energy and Environmental Engineering with specialization in Electric Energy Technology and Smart Grids. I have always had a great interest for the electric power systems as it is critical for our society. It has been interesting to follow the progress of renewable energy technologies the recent years, which has lead to new important research topics. How to deal with the challenges emerging from the shift towards new renewable energy technologies has been my main motivation for choosing this topic for my master thesis.

I would like to give a big thanks to my supervisor Pr. Hans Kristian Høidalen for the continuous support and guidance I have received along the way. It has been rewarding to join the ProDig cooperation project and for getting the opportunity to present my work for all the participants. This has been very motivating as I have received positive response, and it has helped me to better understand the importance of my work.

The cooperation with Statnett throughout this project has been very valuable. Magnus Kolgrov, leader of protection in Statnett, has proposed the main research question of the thesis and provided great material to work with. Jorun Irene Marvik, relay planner in Statnett and co-supervisor, has offered continuous assistance and provided key parameters for the PSCAD model. I am very thankful for the help I have received, which has been essential for the progress of the thesis.

I would like to thank PhD candidate Maciej Grebla for great assistance with the development of the inverter model. Sharing of the inverter model developed in Simulink has been very helpful and has speeded up the model development significantly. I am also very thankful for Pr. Mohammad Amin's sharing of knowledge regarding inverter design.

Additionally, the conversations I have had with scientists at Sintef have been very helpful, and I would like to thank Jon Are Wold Suul, Kjell Ljøkelsøy and Salvatore D'Arco for sharing their knowledge.

At last, I would like to thank family and friends for the great support throughout the project.

It has been most rewarding to work with this master thesis, and I hope it will prove useful.

June 2020 Nicolay Anker Kavli

## Contents

| Li            | st of             | Figures                                                         |  |  |  |

|---------------|-------------------|-----------------------------------------------------------------|--|--|--|

| $\mathbf{Li}$ | List of Tables ix |                                                                 |  |  |  |

| Al            | bbre              | viations                                                        |  |  |  |

| 1             | Intr              | roduction 1                                                     |  |  |  |

|               | 1.1               | Background and Motivation                                       |  |  |  |

|               | 1.2               | Approach                                                        |  |  |  |

|               | 1.3               | Scope 1                                                         |  |  |  |

| <b>2</b>      | The               | eory 1                                                          |  |  |  |

|               | 2.1               | Grid short circuits                                             |  |  |  |

|               | 2.2               | Symmetrical components                                          |  |  |  |

|               |                   | 2.2.1 The use of symmetrical components in power systems 1      |  |  |  |

|               | 2.3               | Distance Protection                                             |  |  |  |

|               |                   | 2.3.1 Fundamentals of Distance Protection                       |  |  |  |

|               |                   | 2.3.2 Fault loops                                               |  |  |  |

|               |                   | 2.3.3 Impact of different short circuit current contributions 2 |  |  |  |

|               |                   | 2.3.4 Underreaching and overreaching                            |  |  |  |

|               |                   | 2.3.5 Current and voltage transformers                          |  |  |  |

|               |                   | 2.3.6 Pilot distance protection                                 |  |  |  |

|               | 2.4               | Per Unit values                                                 |  |  |  |

|               | 2.5               | Control systems                                                 |  |  |  |

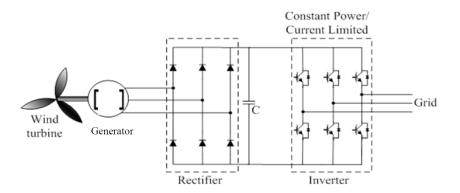

|               | 2.6               | Inverters                                                       |  |  |  |

|               |                   | 2.6.1 Fundamentals of inverters                                 |  |  |  |

|               |                   | 2.6.2 Control systems                                           |  |  |  |

|               |                   | 2.6.3 Semiconductor switches                                    |  |  |  |

|               |                   | 2.6.4 Filter design for inverters                               |  |  |  |

|               | 2.7               | Wind turbines 3                                                 |  |  |  |

|               |                   | 2.7.1 Wind turbine classification types                         |  |  |  |

|               |                   | 2.7.2 Type 4 wind turbines                                      |  |  |  |

|               | 2.8               | Grid codes                                                      |  |  |  |

| 3             | Met               | thod 3                                                          |  |  |  |

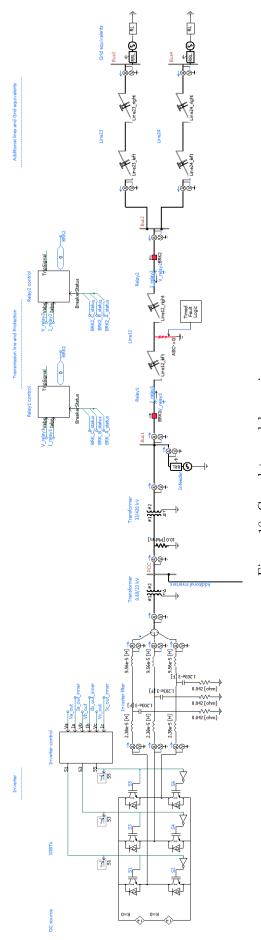

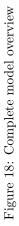

|               | 3.1               | Model overview and component description                        |  |  |  |

|               |                   | 3.1.1 Inverter control system                                   |  |  |  |

|               |                   | 3.1.2 Relay algorithm for distance protection                   |  |  |  |

|               |                   |                                                                 |  |  |  |

|               |                   | i O I                                                           |  |  |  |

|               | 3.2               |                                                                 |  |  |  |

| <b>4</b>     | Ver   | ification of the model                                                                            | <b>64</b> |

|--------------|-------|---------------------------------------------------------------------------------------------------|-----------|

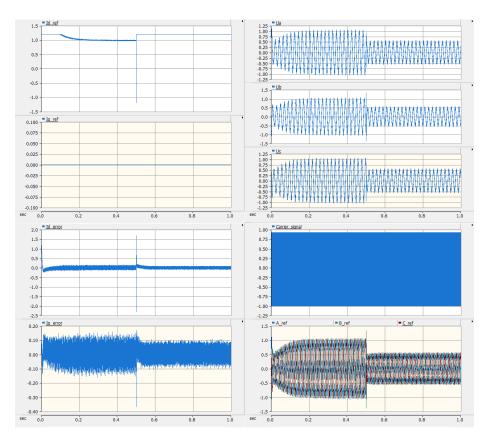

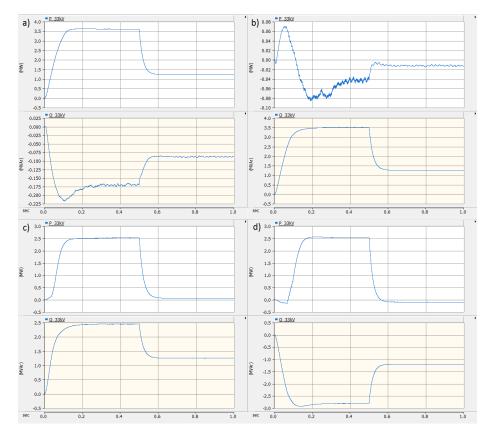

|              | 4.1   | Verification of the inverter model                                                                | 64        |

|              |       | 4.1.1 Verification 1 - Detailed                                                                   | 64        |

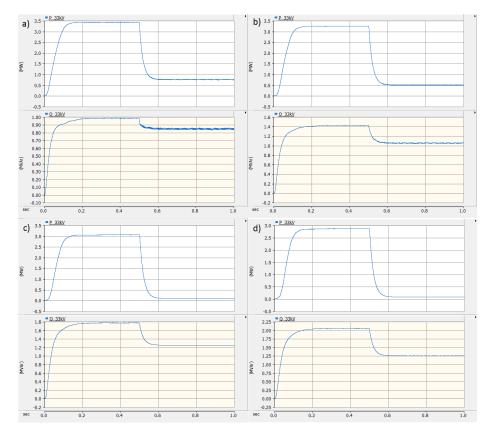

|              |       | 4.1.2 Influence of PI controller tuning                                                           | 70        |

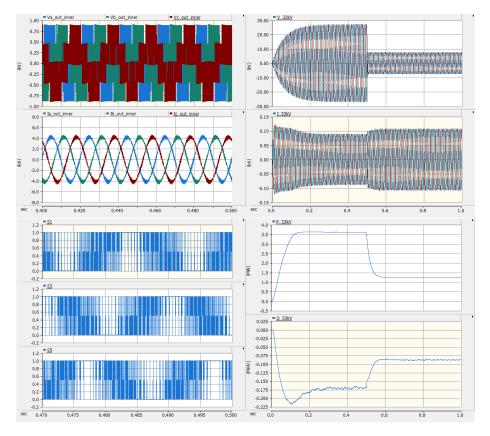

|              |       | 4.1.3 Further verification of the power output                                                    | 73        |

|              |       | 4.1.4 Current limiter                                                                             | 76        |

|              | 4.2   | Verification of the Distance Protection Relay                                                     | 77        |

|              |       | 4.2.1 Detailed examination of Relay 1                                                             | 77        |

|              |       | 4.2.2 Different fault resistances                                                                 | 81        |

|              |       | 4.2.3 Different fault locations                                                                   | 82        |

|              |       |                                                                                                   |           |

| <b>5</b>     | Res   | ults                                                                                              | 83        |

|              | 5.1   | Simulation set 1 - Generation from one single inverter                                            | 84        |

|              | 5.2   | Simulation set 2 - Generation from ten inverters                                                  | 87        |

|              | 5.3   | Simulation set 3 - Share of inverter generation                                                   | 89        |

|              | 5.4   | Simulation set 4 - Influence of different short circuit current con-                              |           |

|              |       | tributions                                                                                        | 91        |

|              |       |                                                                                                   |           |

| 6            |       | cussion                                                                                           | 92        |

|              | 6.1   | Discussion of model assumptions and weaknesses                                                    | 92        |

|              | 6.2   | Discussion of the Results                                                                         | 96        |

|              |       | $6.2.1  \text{Simulation set } 1  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 96        |

|              |       | $6.2.2  \text{Simulation set } 2  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 97        |

|              |       | $6.2.3  \text{Simulation set } 3  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 97        |

|              |       | $6.2.4  \text{Simulation set } 4  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 98        |

|              |       | 6.2.5 General conclusion from simulations                                                         | 98        |

|              | 6.3   | Discussion of additional topics of interest                                                       | 98        |

|              |       | 6.3.1 Pilot distance protection                                                                   | 98        |

|              |       | 6.3.2 Direction determination - polarisation                                                      | 99        |

|              |       | 6.3.3 Subsequent tripping                                                                         | 100       |

|              |       | 6.3.4 The ENTSO-E report                                                                          | 100       |

| _            | -     |                                                                                                   |           |

| 7            | Cor   | nclusion                                                                                          | 102       |

| 8            | Fur   | ther work                                                                                         | 104       |

| R            | efere | nces                                                                                              | 106       |

|              |       |                                                                                                   |           |

| $\mathbf{A}$ |       |                                                                                                   | 110       |

|              |       | endix A                                                                                           |           |

|              |       | endix B                                                                                           | 114       |

|              |       | bendix C                                                                                          | 118       |

|              | App   | endix D                                                                                           | 139       |

## List of Figures

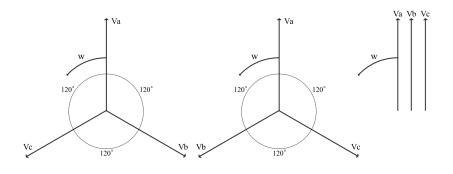

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1  | Symmetrical components                                                              | • | 15 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------|---|----|

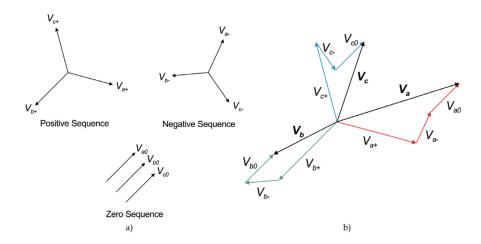

| 4Distance protection zone reaching205Multiple-system relay216Single-system relay227Single line with distance protection238Three-phase two-level inverter279Pulse Width Modulation 12810Pulse Width Modulation 12911Grid-forming inverter3012Grid-feeding inverter3113Grid-feeding inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4010Left half of the model4110Right half of the model4421Inverter control4822Relay control5423Relay control5424Relay control5526Verification: G90V terminal6629Verification: Control 16729Verification: PI Tuning Stable7130Verification: PI Tuning Critical7231Verification: Current limiter7633Verification: Current limiter7634Verification: Current limiter7633Verification: Relay control - detailed8034Verification: Relay control - detailed8035Verification: Relay inpedance - detailed8036Verification: Relay inpedance - detailed80 <td>2</td> <td>Symmetrical components visualization</td> <td></td> <td>16</td>                                          | 2  | Symmetrical components visualization                                                |   | 16 |

| 5Multiple-system relay216Single-system relay227Single line with distance protection238Three-phase two-level inverter279Pulse Width Modulation 12810Pulse Width Modulation 12911Grid-forming inverter3022Grid-feeding inverter3113Grid-feeding inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4110Right half of the model4421Inverter control4822PWM - labelled4923PWM - labelled4924Relay control - with IDs5525Verification: Control 16627Verification: Control 16728Verification: PI Tuning Stable7130Verification: PI Tuning Critical7231Verification: Current limiter7633Verification: Current limiter7634Verification: Relay control - detailed8035Verification: Relay control - detailed7936Verification: Relay control - detailed7737Verification: Relay control - detailed7738Verification: Relay control - detailed7039Verification: Relay control - det                                                                                                            | 3  | Distance protection impedance diagram with multiple zones .                         |   | 19 |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4  | Distance protection zone reaching                                                   |   | 20 |

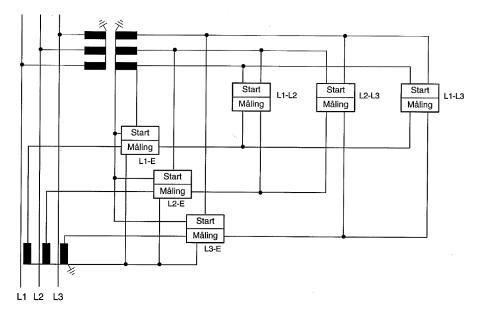

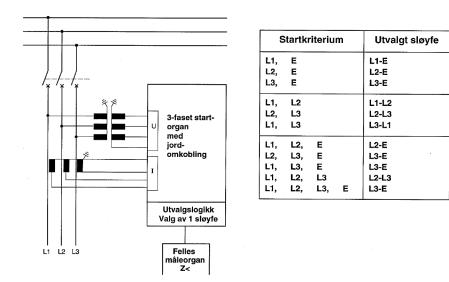

| 7Single line with distance protection238Three-phase two-level inverter279Pulse Width Modulation 12810Pulse Width Modulation 12911Grid-forming inverter3022Grid-feeding inverter3133Grid-feeding inverter3214Reference frames3335PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Hwerter control5224Relay control5224Relay control5425Relay control5426Verification: Control 16627Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Relay control - detailed8033Verification: Relay control - detailed8034Verification: Relay - fault location8235Verification: Relay - fault location8236Verification: Relay - fault location8237Verification: Relay - fault location8237Verification: Relay - fault location <td< td=""><td>5</td><td>Multiple-system relay</td><td></td><td>21</td></td<>                                      | 5  | Multiple-system relay                                                               |   | 21 |

| 7Single line with distance protection238Three-phase two-level inverter279Pulse Width Modulation 12810Pulse Width Modulation 12911Grid-forming inverter3022Grid-feeding inverter3133Grid-feeding inverter3214Reference frames3335PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Hwerter control5224Relay control5224Relay control5425Relay control5426Verification: Control 16627Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Relay control - detailed8033Verification: Relay control - detailed8034Verification: Relay - fault location8235Verification: Relay - fault location8236Verification: Relay - fault location8237Verification: Relay - fault location8237Verification: Relay - fault location <td< td=""><td>6</td><td>Single-system relay</td><td></td><td>22</td></td<>                                        | 6  | Single-system relay                                                                 |   | 22 |

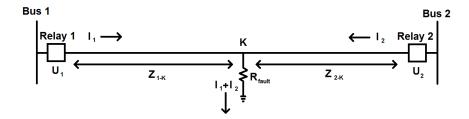

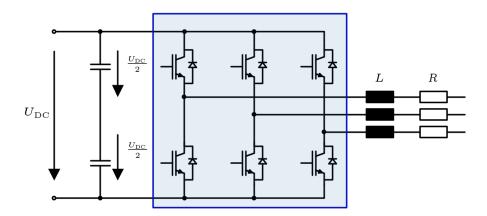

| 8Three-phase two-level inverter279Pulse Width Modulation 12810Pulse Width Modulation 12911Grid-forming inverter3012Grid-feeding inverter3113Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4110Right half of the model4411Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5524Relay control - with IDs5525Verification: 690V terminal6627Verification: Control 16728Verification: PI Tuning Stable7130Verification: PI Tuning Critical7231Verification: Current limiter7633Verification: Current contribution from both sides7734Verification: Relay control - detailed8035Verification: Relay impedance - detailed8036Verification: Relay - fault location8237Verification: Relay - fault location8238Verification: Relay - fault location8239Verification: Relay - fault location8230Verification: Relay - fault location82 <tr< td=""><td>7</td><td>Single line with distance protection</td><td></td><td>23</td></tr<> | 7  | Single line with distance protection                                                |   | 23 |

| 10Pulse Width Modulation 12911Grid-forming inverter3012Grid-feeding inverter3113Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4923PWM - labelled5224Relay control5425Relay control5526Verification: 690V terminal6627Verification: Control 16728Verification: PI Tuning Stable7130Verification: PI Tuning Stable7331Verification: Current limiter7632Verification: Current contribution from both sides7733Verification: Relay control - detailed8034Verification: Relay inpedance diagrams8135Verification: Relay inpedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                   | 8  | Three-phase two-level inverter                                                      |   | 27 |

| 11Grid-forming inverter3012Grid-feeding inverter3113Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4823PWM - labelled4924Relay control5224Relay control5425Relay control5526Verification: 690V terminal6627Verification: Control 16728Verification: PI Tuning Stable7130Verification: PI Tuning Critical7233Verification: Pi Tuning Critical7234Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed8038Verification: Relay inpedance - detailed8039Verification: Relay inpedance diagrams8134Verification: Relay if and tocation8237Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                      | 9  | Pulse Width Modulation 1                                                            |   | 28 |

| 11Grid-forming inverter3012Grid-feeding inverter3113Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4823PWM - labelled4924Relay control5224Relay control5425Relay control5526Verification: 690V terminal6627Verification: Control 16728Verification: PI Tuning Stable7130Verification: PI Tuning Critical7233Verification: Pi Tuning Critical7234Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed8038Verification: Relay inpedance - detailed8039Verification: Relay inpedance diagrams8134Verification: Relay if and tocation8237Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                      | 10 | Pulse Width Modulation 1                                                            |   | 29 |

| 12Grid-feeding inverter3113Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4823PWM - labelled5224Relay control5425Relay control5426Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay inpedance - detailed8038Verification: Relay inpedance - detailed8139Verification: Relay inpedance diagrams8234Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                 | 11 |                                                                                     |   | 30 |

| 13Grid-supporting inverter3214Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4823PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: PI Tuning Stable7131Verification: POwer Output 17332Verification: Power Output 17333Verification: Current limiter7634Verification: Relay control - detailed7937Verification: Relay control - detailed8038Verification: Relay impedance - detailed8139Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                      | 12 |                                                                                     |   | 31 |

| 14Reference frames3315PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4121Inverter control4822Inverter control4823PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Current limiter7636Verification: Relay control - detailed8037Verification: Relay impedance - detailed8138Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                           | 13 | Grid-supporting inverter                                                            |   | 32 |

| 15PLL3416FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Current limiter7635Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                    | 14 | Reference frames                                                                    |   | 33 |

| 16FLL3417Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Current limiter7635Verification: Relay control - detailed7036Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                           | 15 | PLL                                                                                 |   | 34 |

| 17Type 4 Wind Turbine3718Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: POwer Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                             | 16 |                                                                                     |   | 34 |

| 18Complete model overview4019Left half of the model4120Right half of the model4421Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: POwer Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                         | 17 |                                                                                     |   | 37 |

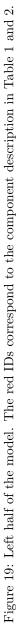

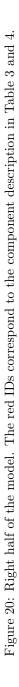

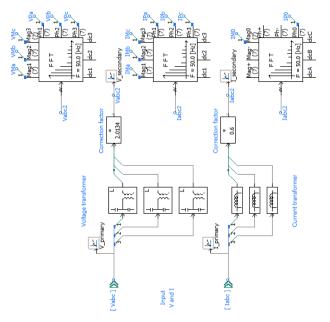

| 19Left half of the model4120Right half of the model4421Inverter control - labelled4822Inverter control - labelled4923PWM - labelled5224Relay control - with IDs5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: POwer Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7735Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                         | 18 | 01                                                                                  |   | 40 |

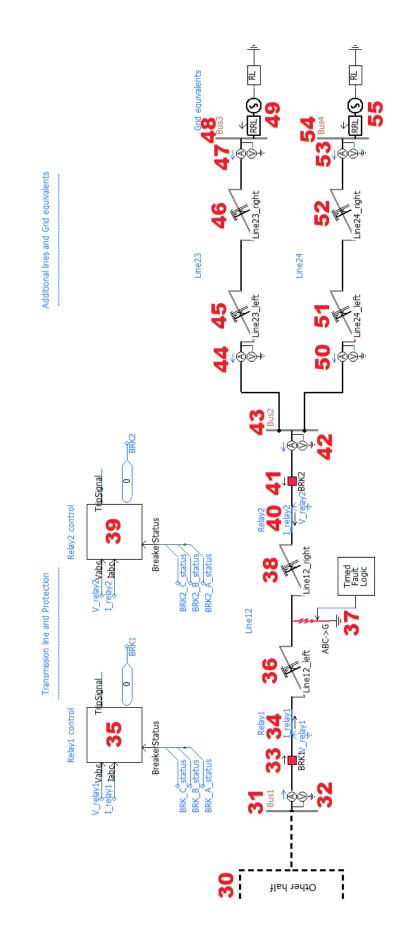

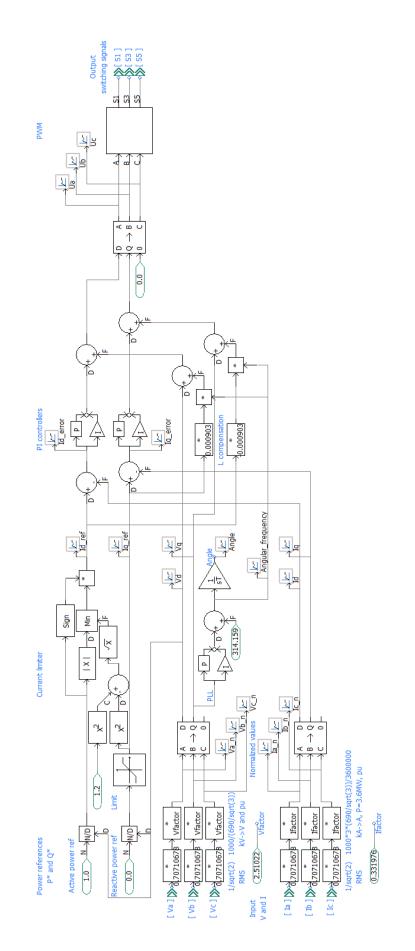

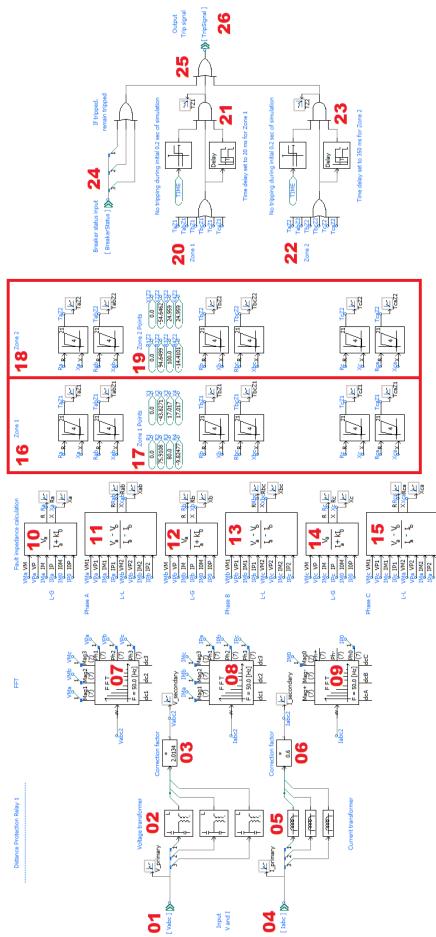

| 20Right half of the model4421Inverter control .4822Inverter control - labelled4923PWM - labelled5224Relay control5224Relay control .5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: POwer Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7735Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                    | 19 |                                                                                     |   | 41 |

| 21Inverter control4822Inverter control - labelled4923PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: Power Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7735Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |                                                                                     |   | 44 |

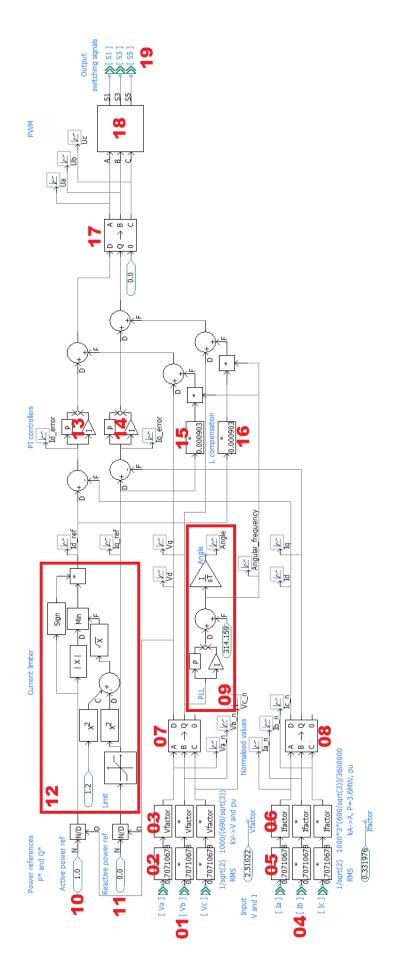

| 22Inverter control - labelled4923PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: POwer Output 17333Verification: Current limiter7534Verification: Current contribution from both sides7735Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                                                     |   | 48 |

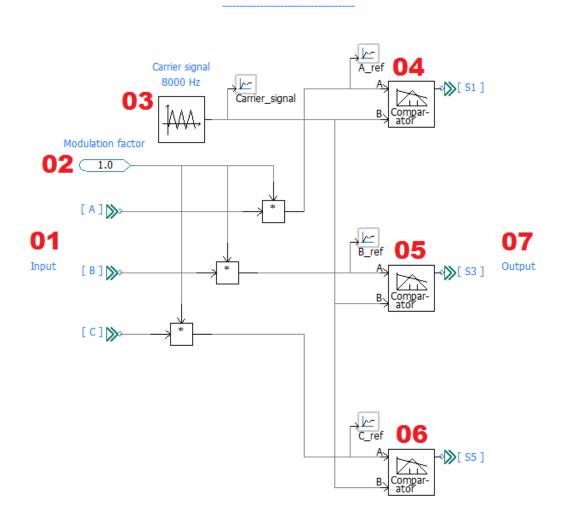

| 23PWM - labelled5224Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7735Verification: Relay control - detailed7936Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                   | 22 |                                                                                     |   | 49 |

| 24Relay control5425Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Current limiter7634Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 | PWM - labelled                                                                      |   | 52 |

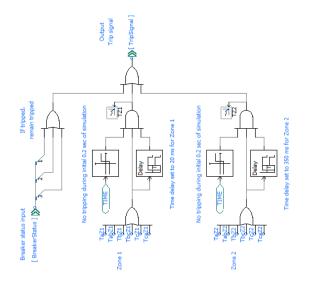

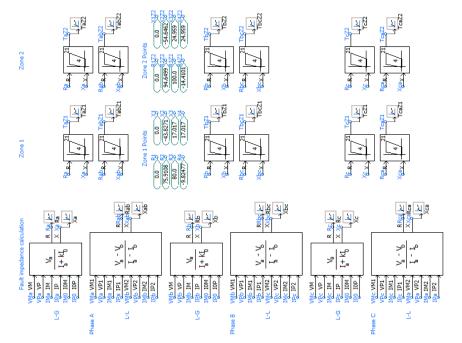

| 25Relay control - with IDs5526Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Current limiter7534Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |                                                                                     |   | 54 |

| 26Verification: 690V terminal6627Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Relay control - detailed7937Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                                                                                     |   | 55 |

| 27Verification: Control 16728Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Current limiter7534Verification: Current contribution from both sides7735Verification: Relay control - detailed7937Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |                                                                                     |   | 66 |

| 28Verification: Control 26829Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Relay control - detailed7736Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                                                                     |   | 67 |

| 29Verification: Inner and 33kV6930Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 | Verification: Control 2                                                             |   | 68 |

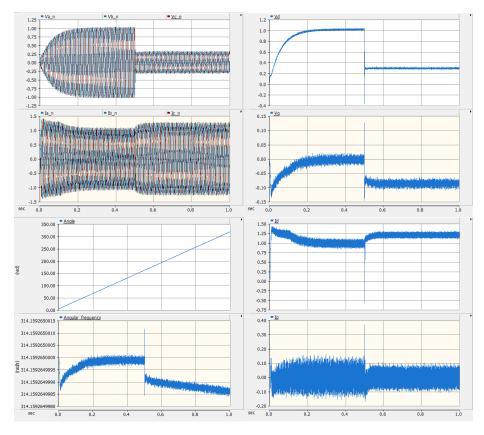

| 30Verification: PI Tuning Stable7131Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 |                                                                                     |   | 69 |

| 31Verification: PI Tuning Critical7232Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 |                                                                                     |   | 71 |

| 32Verification: Power Output 17333Verification: Power Output 27534Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31 | Verification: PI Tuning Critical                                                    |   | 72 |

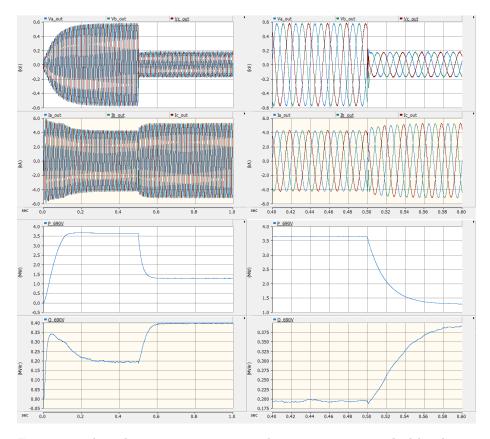

| 33Verification: Power Output 27534Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 | Verification: Power Output 1                                                        |   | 73 |

| 34Verification: Current limiter7635Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |                                                                                     |   | 75 |

| 35Verification: Current contribution from both sides7736Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34 | Verification: Current limiter                                                       |   | 76 |

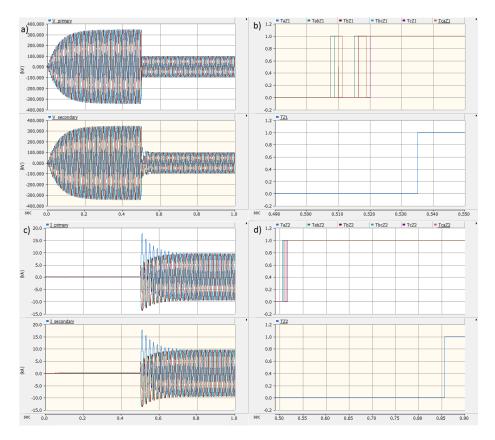

| 36Verification: Relay control - detailed7937Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35 |                                                                                     |   | 77 |

| 37Verification: Relay impedance - detailed8038Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                                                                     |   | 79 |

| 38Verification: Relay - fault resistance8139Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37 |                                                                                     |   | 80 |

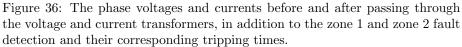

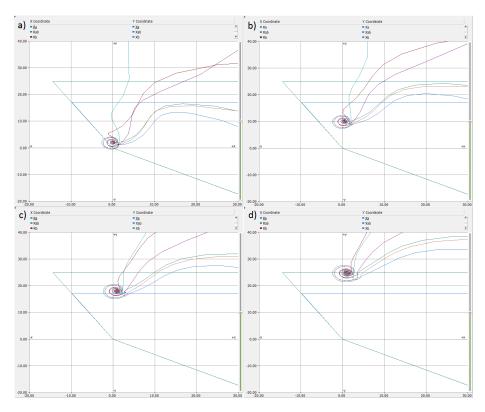

| 39Verification: Relay - fault location8240Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | Verification: Relay - fault resistance                                              |   |    |

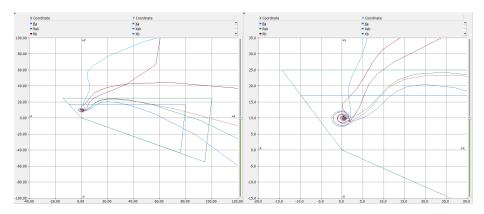

| 40Simulation set 1 - Impedance diagrams8541Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                                                     |   |    |

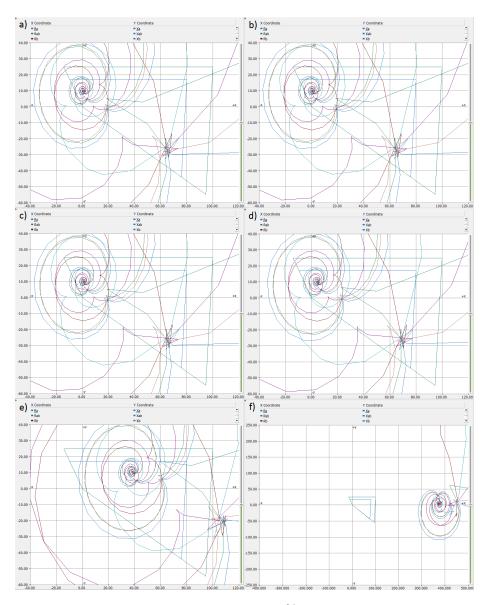

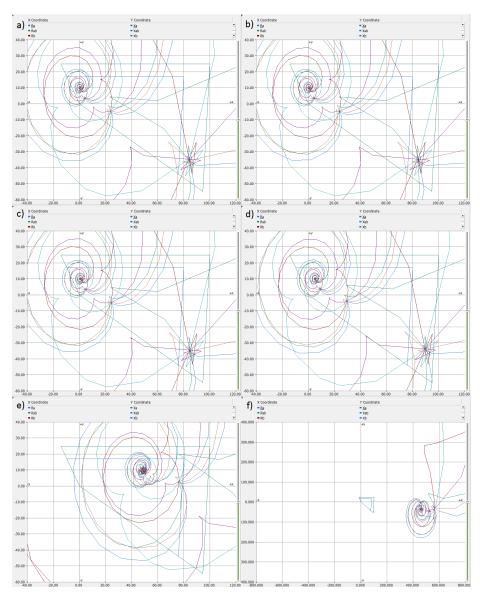

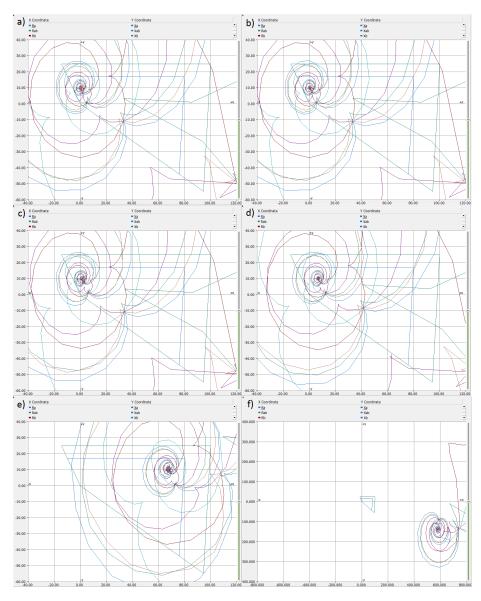

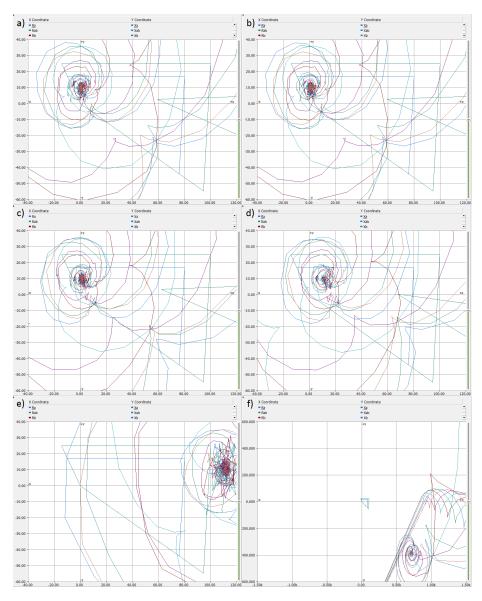

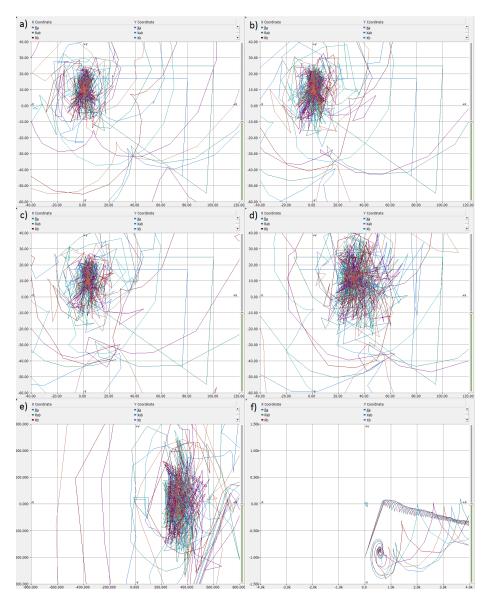

| 41 Simulation set 1 - Impedance diagrams for both relays with $R_{fault}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                                                                     |   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                                                                     |   |    |

| $= 0.0001 \ \Omega  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | $= 0.0001 \ \Omega  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ |   | 86 |

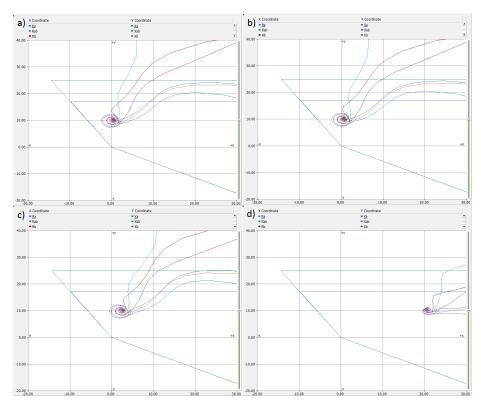

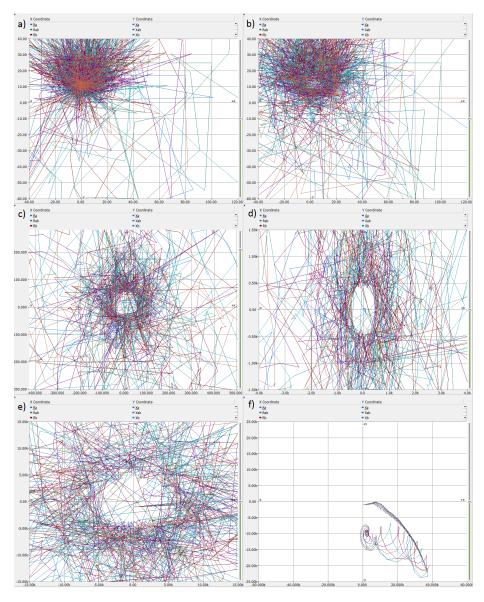

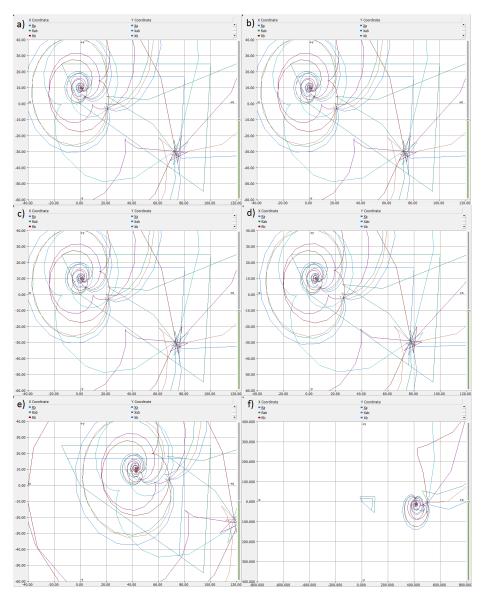

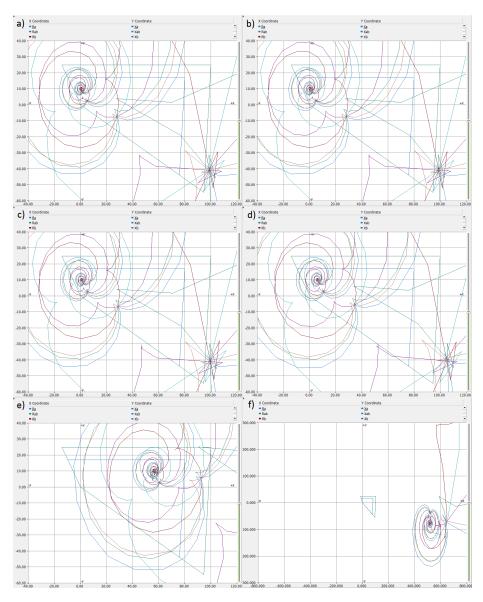

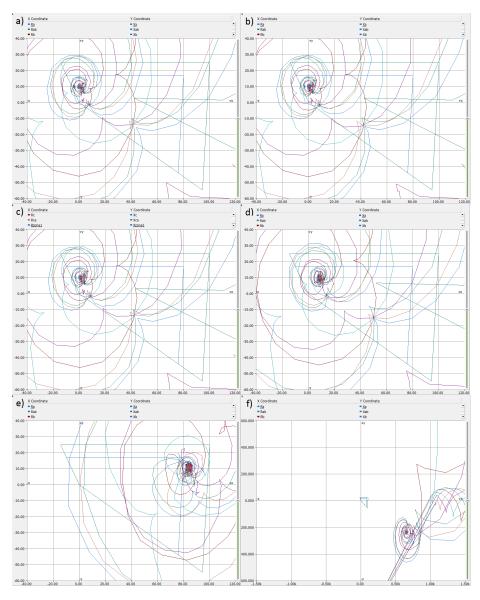

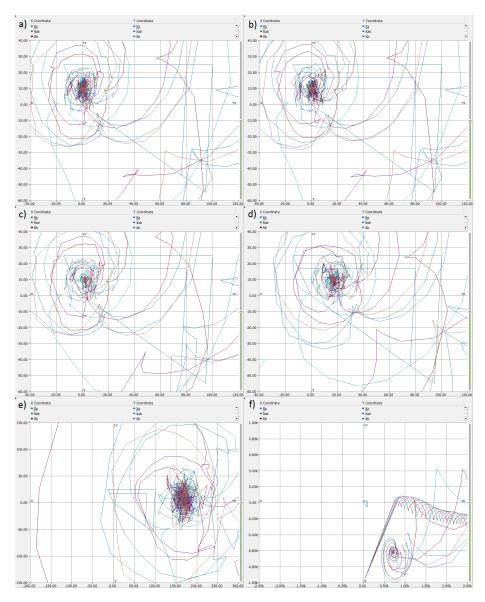

| 42 Simulation set 2 - Impedance diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42 |                                                                                     |   |    |

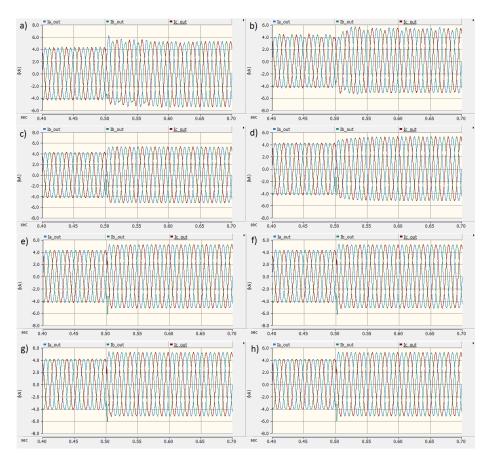

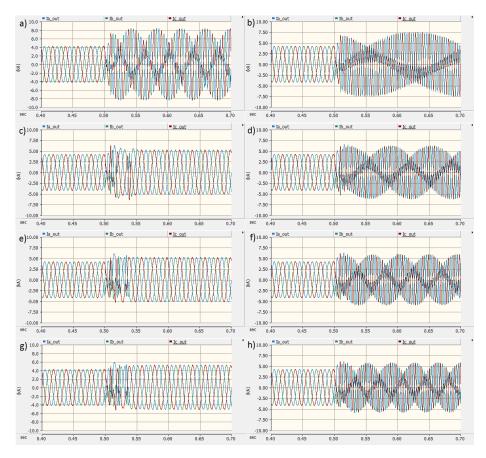

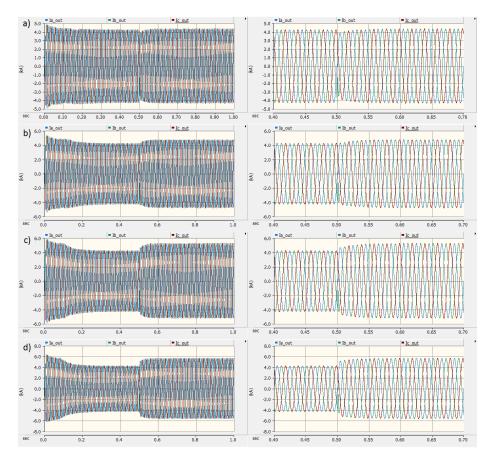

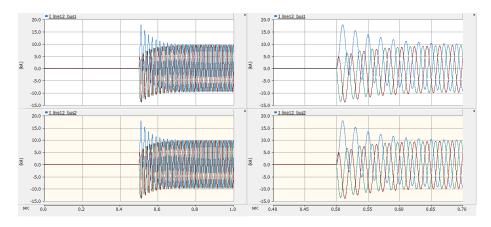

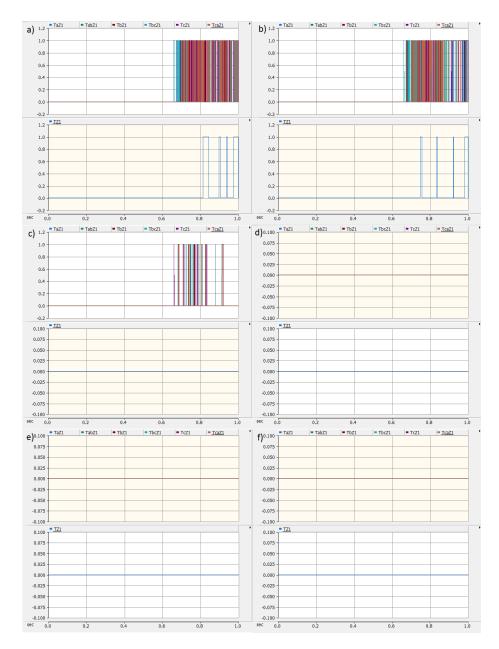

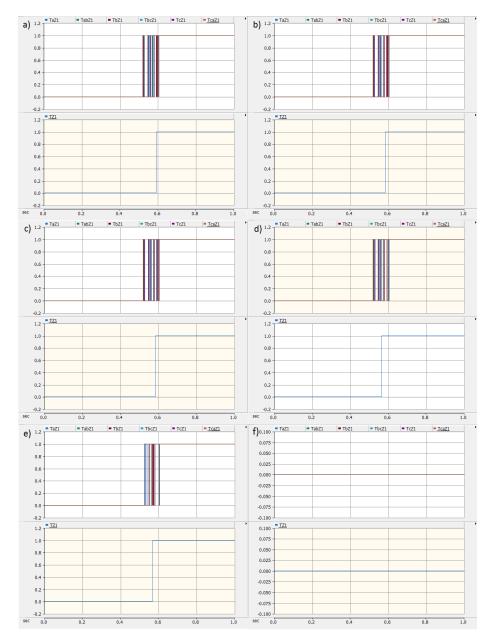

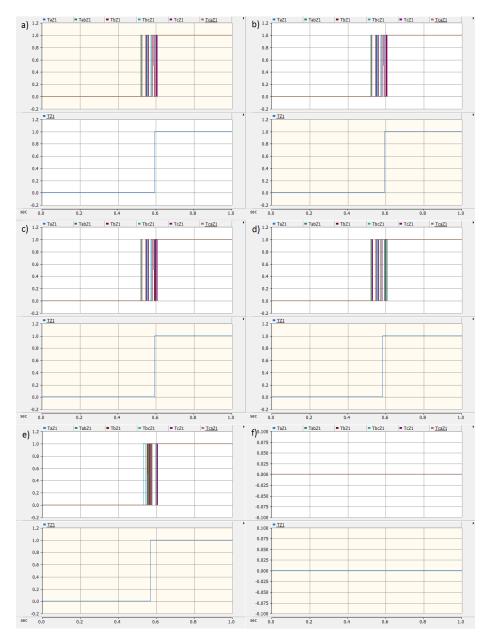

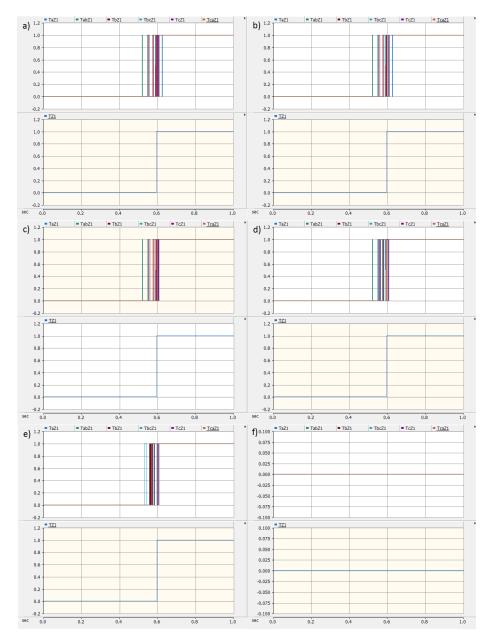

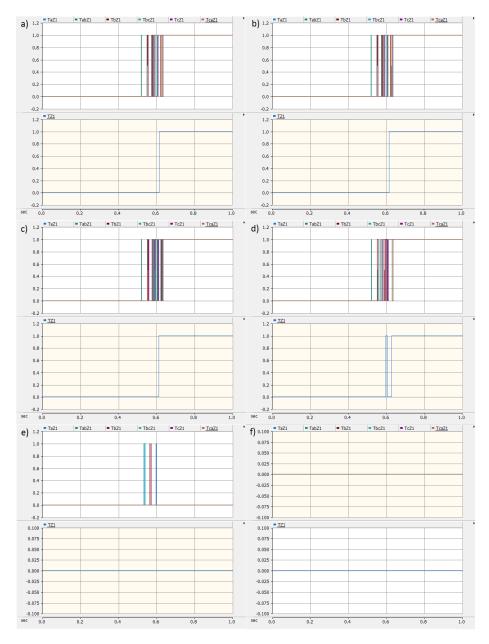

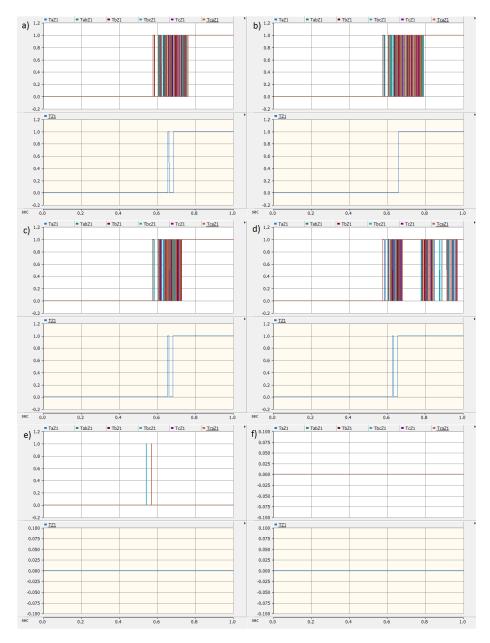

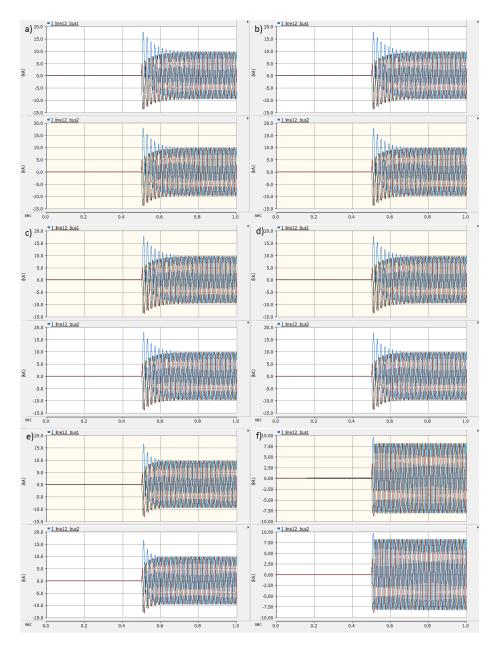

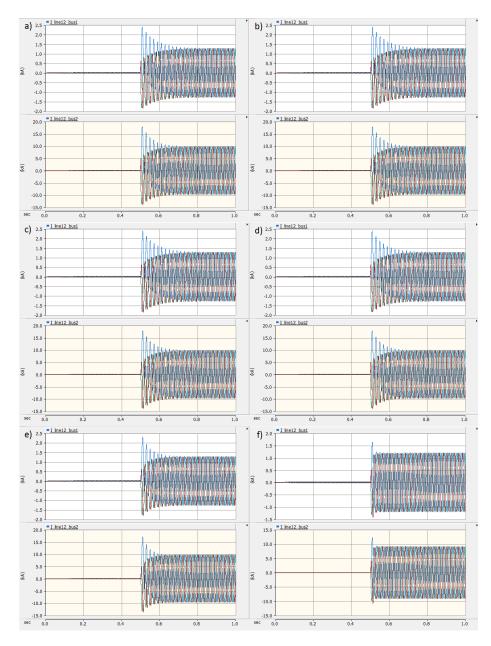

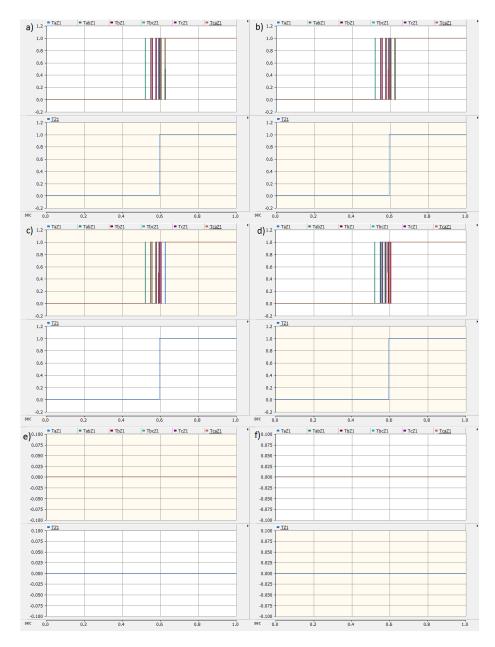

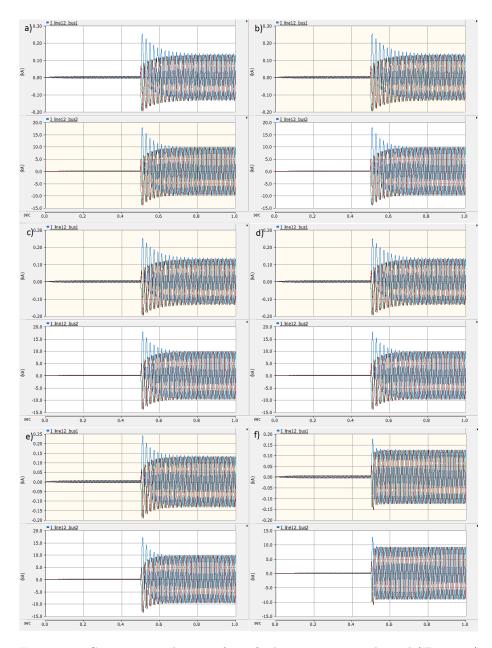

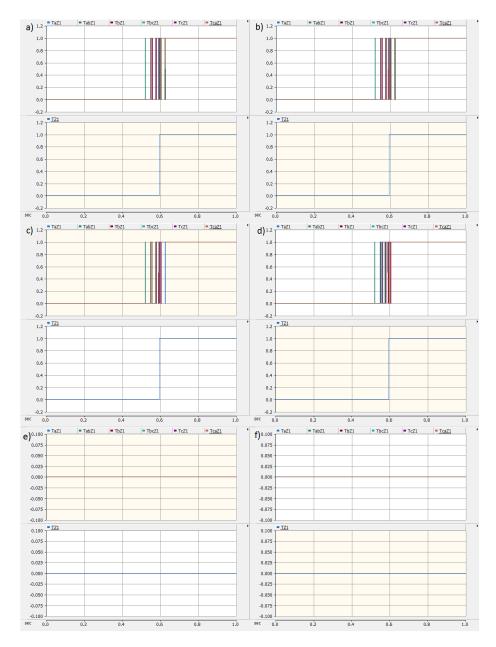

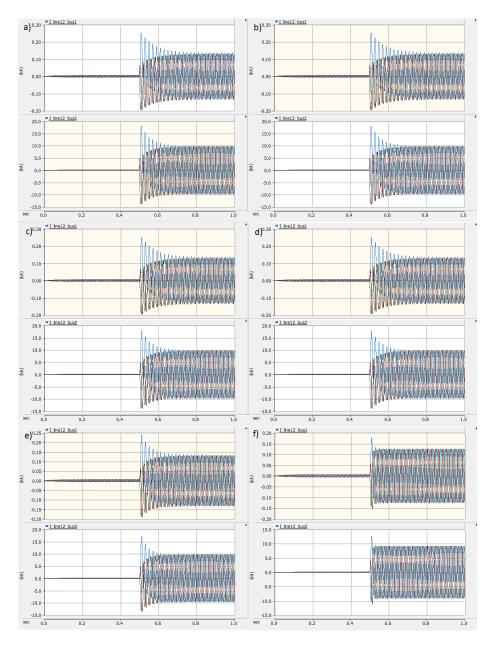

| 43              | Simulation set 1 - Zone 1 fault detection and tripping for one                                                                               |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                 | single inverter connected to PCC                                                                                                             |

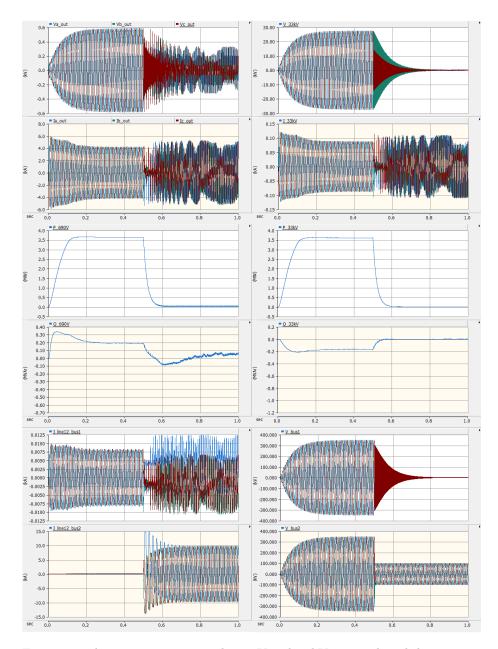

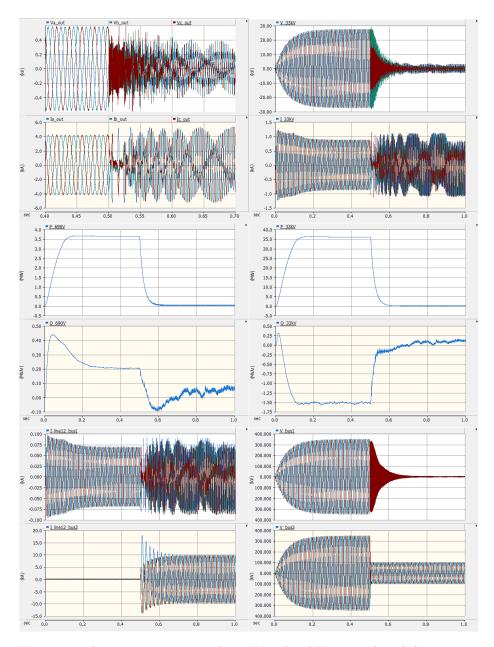

| 44              | Simulation set 1 - Inverter output and current contributions for                                                                             |

|                 | $R_{fault} = 0.0001 \ \Omega  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $                                                |

| 45              | Simulation set 1 - Inverter output and current contributions for                                                                             |

|                 | $R_{fault} = 10 \ \Omega \dots \dots$        |

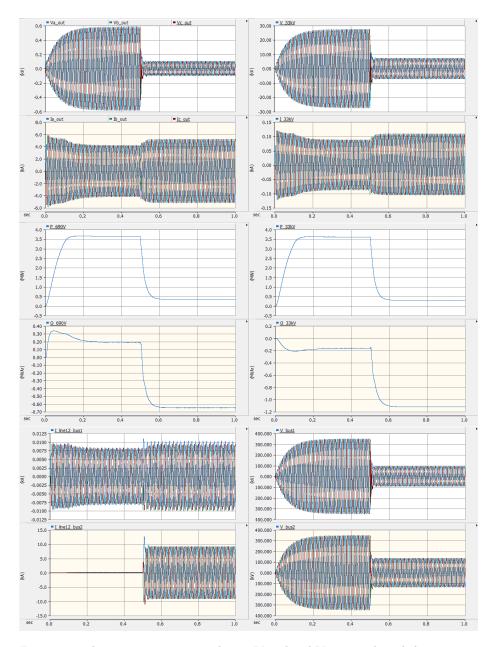

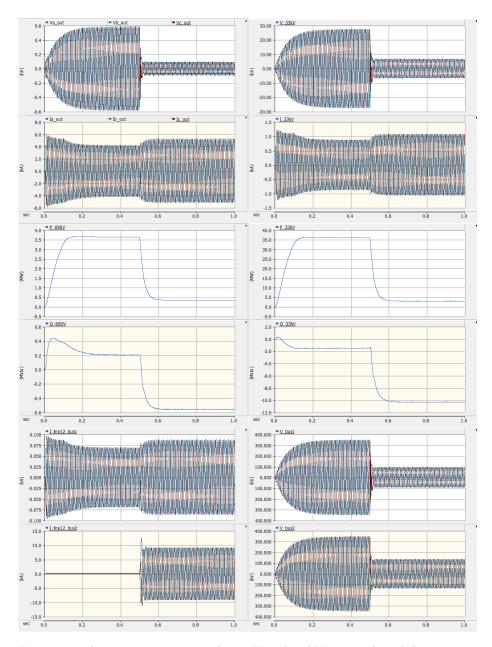

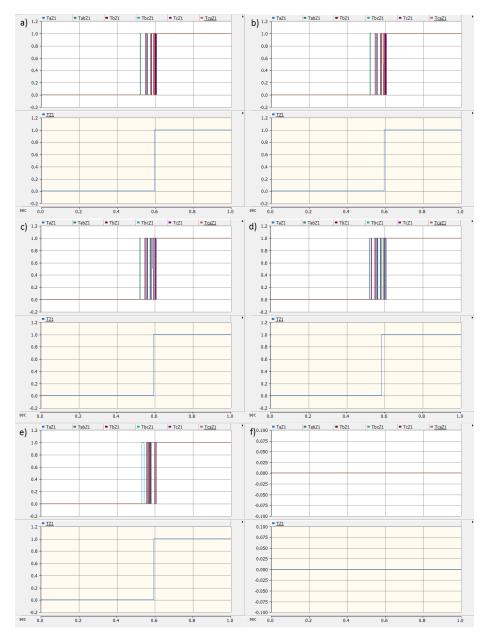

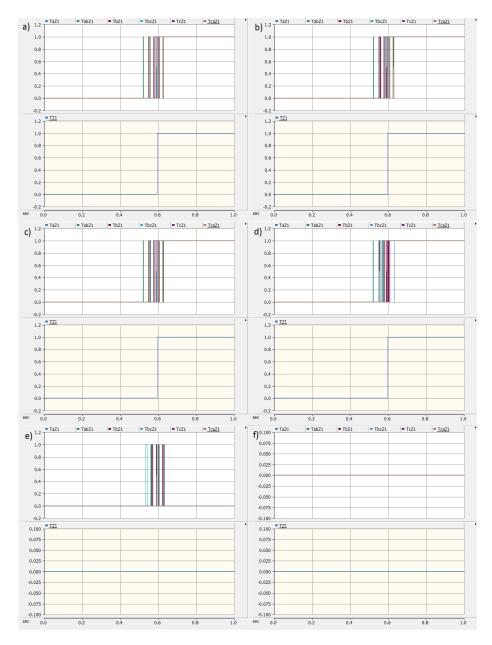

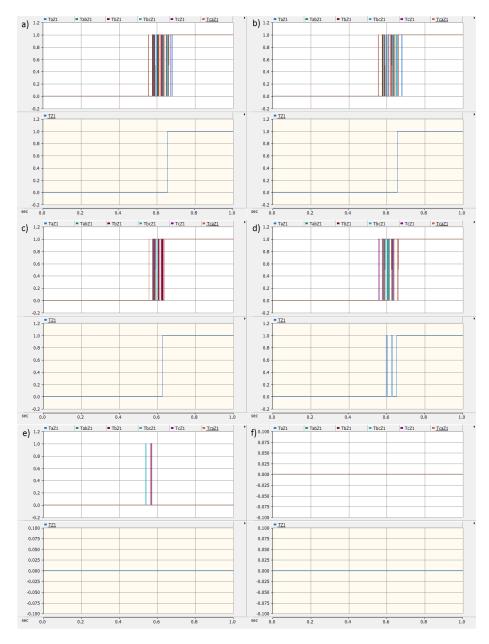

| 46              | Simulation set 2 - Zone 1 fault detection and tripping for 10                                                                                |

| 10              | inverters connected to PCC                                                                                                                   |

| 47              | Simulation set 2 - Inverter output and current contributions for                                                                             |

| 11              | $R_{fault} = 0.0001 \ \Omega$                                                                                                                |

| 48              | Simulation set 2 - Inverter output and current contributions for                                                                             |

| 40              | $R_{fault} = 10 \ \Omega \dots \dots$        |

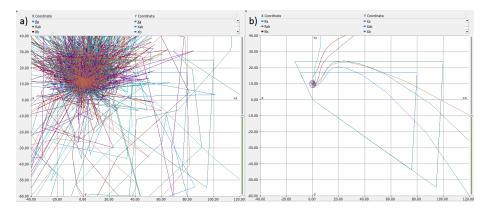

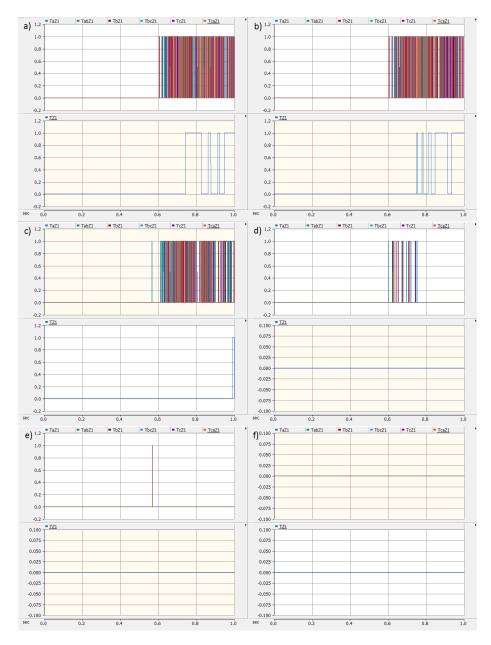

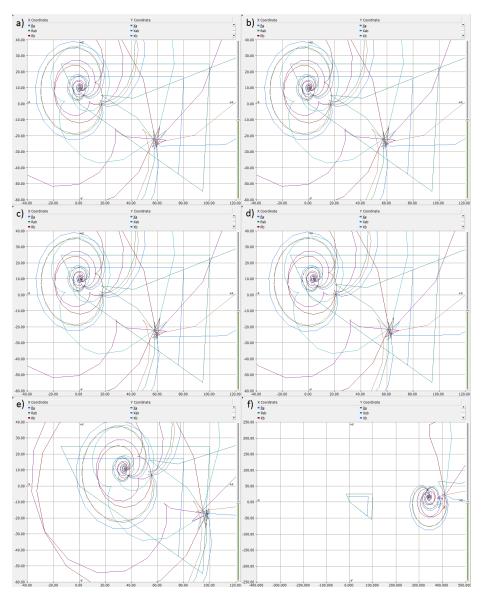

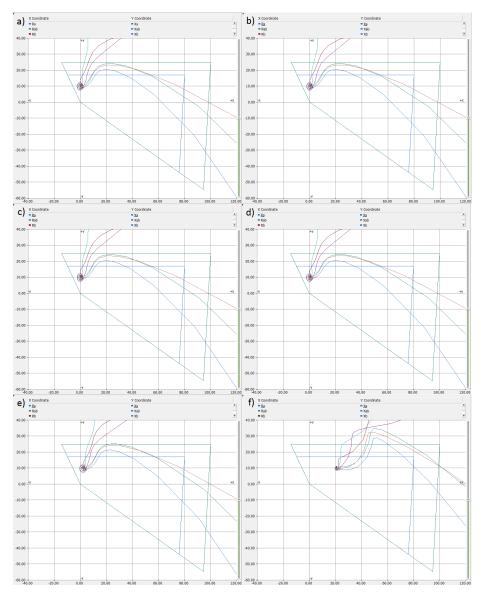

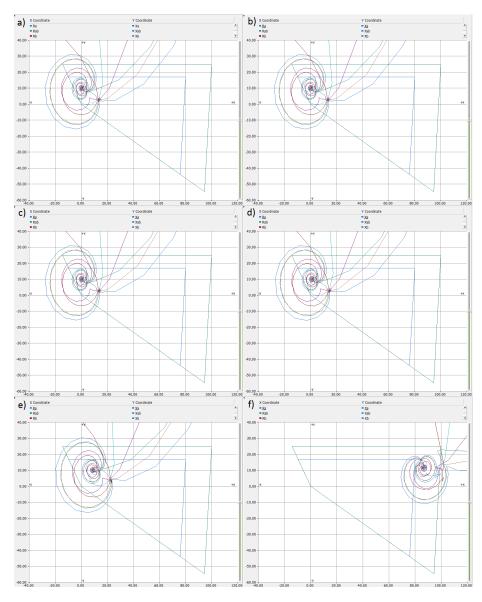

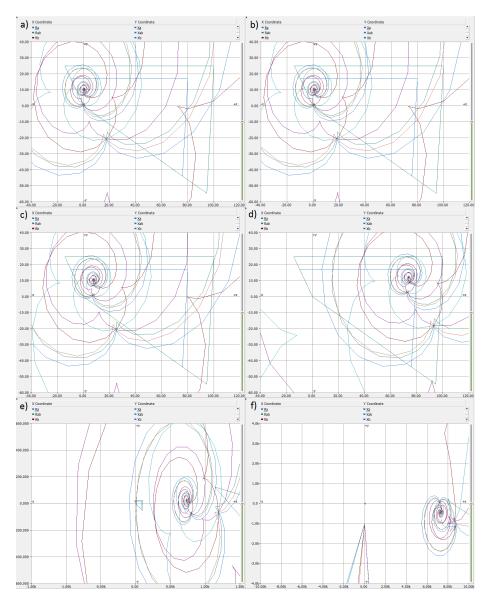

| 49              | Simulation set 3 - Impedance diagrams for $0\%$ inverter generation 119                                                                      |

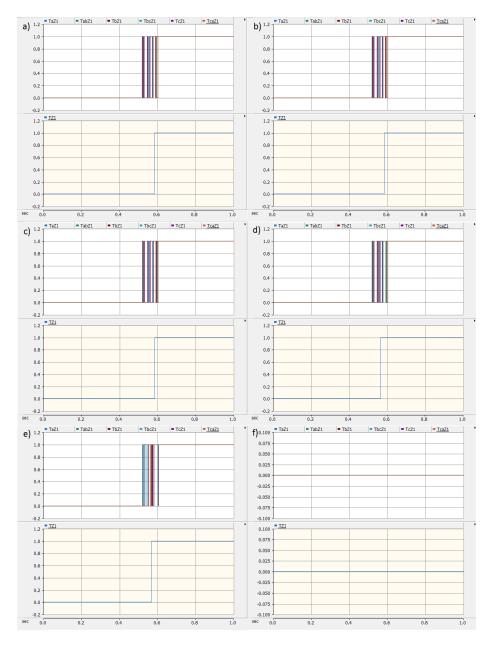

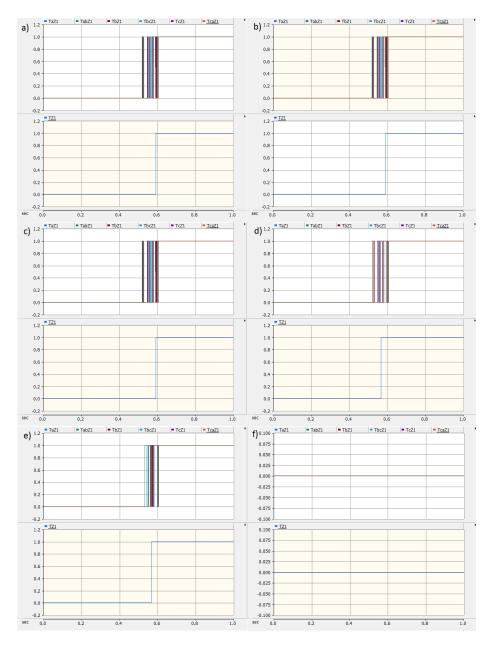

| $\frac{49}{50}$ | Simulation set 3 - Impedatice diagrams for $0\%$ inverter generation 119<br>Simulation set 3 - Zone 1 fault detection and tripping for $0\%$ |

| 50              | inverter generation                                                                                                                          |

| 51              | Simulation set 3 - Impedance diagrams for 10% inverter generation 121                                                                        |

| $51 \\ 52$      | Simulation set 3 - Impedance diagrams for 10% inverter generation 121<br>Simulation set 3 - Zone 1 fault detection and tripping for 10%      |

| 52              | inverter generation                                                                                                                          |

| 53              | Simulation set 3 - Impedance diagrams for 20% inverter generation 123                                                                        |

|                 |                                                                                                                                              |

| 54              | Simulation set 3 - Zone 1 fault detection and tripping for 10%                                                                               |

|                 | inverter generation                                                                                                                          |

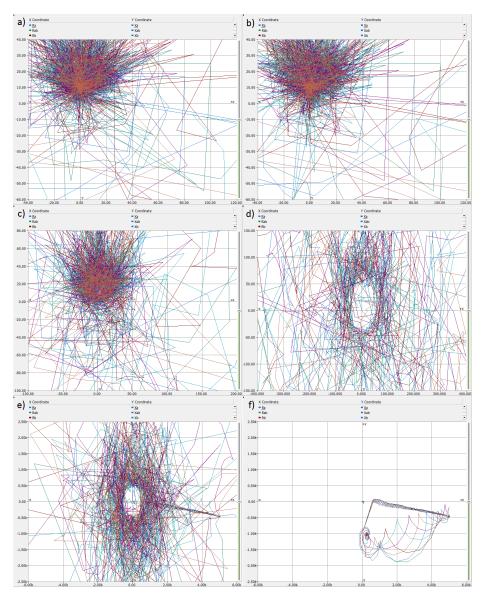

| 55<br>56        | Simulation set 3 - Impedance diagrams for 30% inverter generation 125                                                                        |

| 56              | Simulation set 3 - Zone 1 fault detection and tripping for 30%                                                                               |

|                 | inverter generation                                                                                                                          |

| 57<br>E 0       | Simulation set 3 - Impedance diagrams for 40% inverter generation 127                                                                        |

| 58              | Simulation set 3 - Zone 1 fault detection and tripping for 40%                                                                               |

| 50              | inverter generation                                                                                                                          |

| 59<br>60        | Simulation set 3 - Impedance diagrams for 50% inverter generation 129                                                                        |

| 60              | Simulation set 3 - Zone 1 fault detection and tripping for 50%                                                                               |

| C1              | inverter generation $\dots \dots \dots$      |

| 61<br>co        | Simulation set 3 - Impedance diagrams for $60\%$ inverter generation 131                                                                     |

| 62              | Simulation set 3 - Zone 1 fault detection and tripping for $60\%$                                                                            |

| <u>co</u>       | inverter generation                                                                                                                          |

| 63              | Simulation set 3 - Impedance diagrams for 70% inverter generation 133                                                                        |

| 64              | Simulation set 3 - Zone 1 fault detection and tripping for $70\%$                                                                            |

| ~~              | inverter generation                                                                                                                          |

| 65              | Simulation set 3 - Impedance diagrams for 80% inverter generation 135                                                                        |

| 66              | Simulation set 3 - Zone 1 fault detection and tripping for 80%                                                                               |

|                 | inverter generation                                                                                                                          |

| 67              | Simulation set 3 - Impedance diagrams for 90% inverter generation 137                                                                        |

| 68              | Simulation set 3 - Zone 1 fault detection and tripping for 90%                                                                               |

|                 | inverter generation                                                                                                                          |

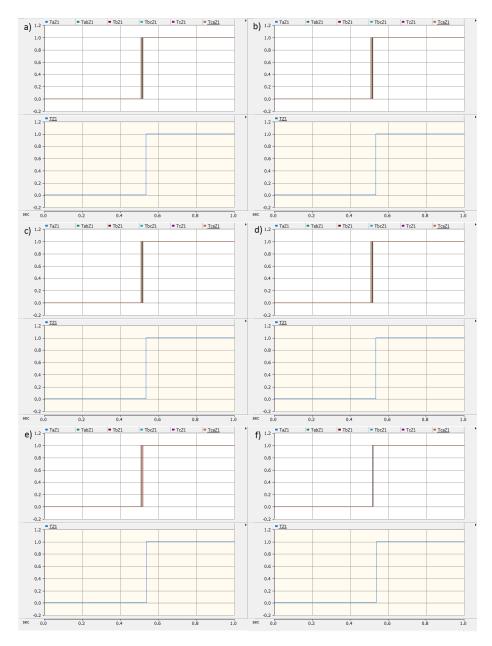

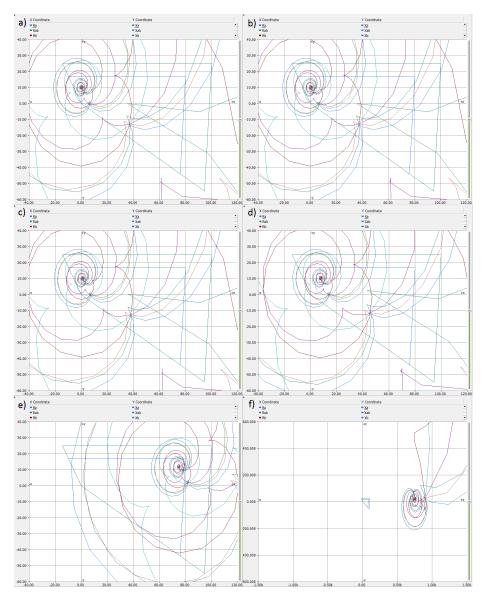

| 69              | Simulation set 4 - Impedance diagrams for infeeder generation                                                                                |

|                 | only and $ Z_{infeeder} $ set to 25.76 $\Omega$                                                                                              |

| 70              | Simulation set 4 - Trip times for infeeder generation only and                                                                               |

|                 | $ Z_{infeeder} $ set to 25.76 $\Omega$                                                                                                       |

| 71 | Simulation set 4 - Current contributions for infeeder generation |

|----|------------------------------------------------------------------|

|    | only and $ Z_{infeeder} $ set to 25.76 $\Omega$                  |

| 72 | Simulation set 4 - Impedance diagrams for infeeder generation    |

|    | only and $ Z_{infeeder} $ set to 257.6 $\Omega$                  |

| 73 | Simulation set 4 - Trip times for infeeder generation only and   |

|    | $ Z_{infeeder} $ set to 257.6 $\Omega$                           |

| 74 | Simulation set 4 - Current contributions for infeeder generation |

|    | only and $ Z_{infeeder} $ set to 257.6 $\Omega$                  |

| 75 | Simulation set 4 - Impedance diagrams for infeeder generation    |

|    | only and $ Z_{infeeder} $ set to 2576 $\Omega$                   |

| 76 | Simulation set 4 - Trip times for infeeder generation only and   |

|    | $ Z_{infeeder} $ set to 2576 $\Omega$                            |

| 77 | Simulation set 4 - Current contributions for infeeder generation |

|    | only and $ Z_{infeeder} $ set to 2576 $\Omega$                   |

| 78 | Simulation set 4 - Impedance diagrams for infeeder generation    |

|    | only and $ Z_{infeeder} $ set to 25760 $\Omega$                  |

| 79 | Simulation set 4 - Trip times for infeeder generation only and   |

|    | $ Z_{infeeder} $ set to 25760 $\Omega$                           |

| 80 | Simulation set 4 - Current contributions for infeeder generation |

|    | only and $ Z_{infeeder} $ set to 25760 $\Omega$                  |

## List of Tables

| 1  | Model description - Left 1               | 42 |

|----|------------------------------------------|----|

| 2  | Model description - Left 2               | 43 |

| 3  |                                          | 45 |

| 4  | Model description - Right 2              | 46 |

| 5  | Inverter control description 1           | 50 |

| 6  | Inverter control description 2           | 51 |

| 7  | PWM description                          | 51 |

| 8  | Relay control description                | 56 |

| 9  | Line parameters                          | 57 |

| 10 | Short circuit grid equivalent parameters | 58 |

| 11 | Standard system parameters               | 65 |

| 12 | Model parameter set 1                    | 83 |

| 13 | Simulation set 1 - Trip times            | 84 |

| 14 | Simulation set 2 - Trip times            | 87 |

| 15 | Simulation set 3 - Overview              | 89 |

| 16 | Simulation set 3 - Trip times            | 90 |

| 17 | Simulation set 4 - Trip times            | 91 |

## Abbreviations

| AC             | Alternating Current                                  |

|----------------|------------------------------------------------------|

| DC             | Direct Current                                       |

| DER            | Distributed Energy Resources                         |

| DSOGI          | Dual Second-Order Generalized Integrator             |

| EMTDC          | Electromagnetic Transient Program Including DC       |

| $\mathbf{FLL}$ | Frequency Locked Loop                                |

| FRT            | Fault Ride Through                                   |

| IGBT           | Insulated-Gate Bipolar Transistor                    |

| $\mathbf{LC}$  | Inductance-Capacitance filter                        |

| LCL            | Inductance-Capacitance-Inductance filter             |

| L-G            | Single-phase to ground short circuit                 |

| L-L            | Two-phase short circuit                              |

| L-L-G          | Two-phase to ground short circuit                    |

| L-L-L          | Three-phase short circuit                            |

| L-L-L-G        | Three-phase to ground short circuit                  |

| PCC            | Point of Common Coupling Bus for the Inverters       |

| PSCAD          | Power System Computer Aided Design                   |

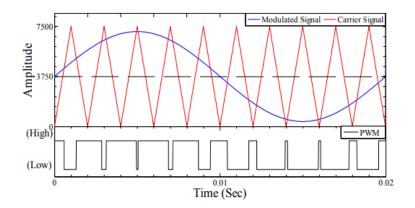

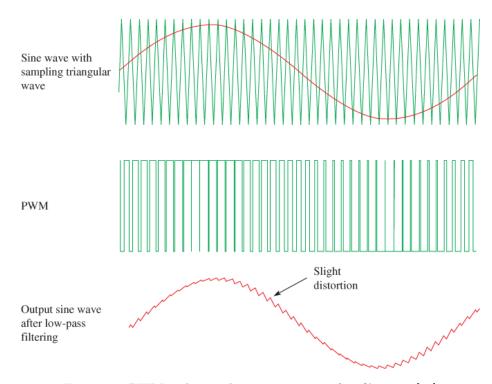

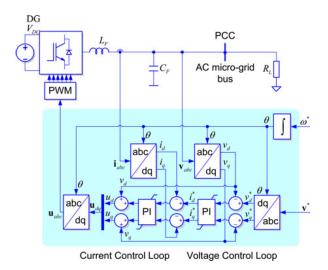

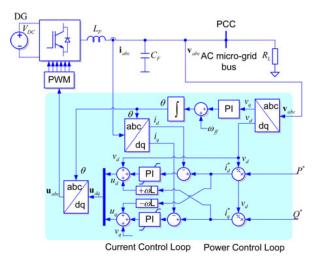

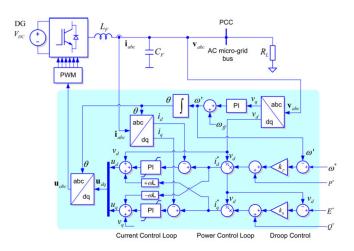

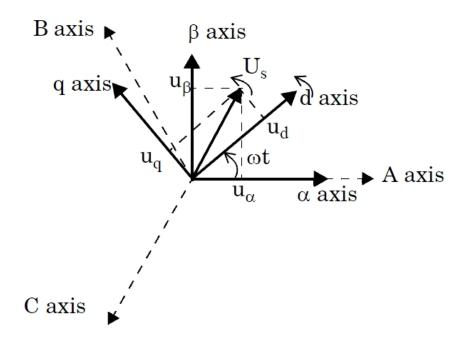

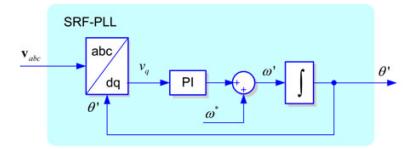

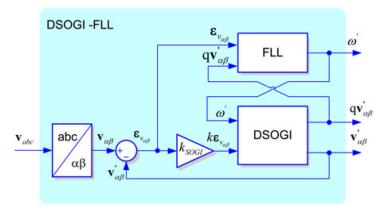

| $\mathbf{PV}$  | Photovoltaics                                        |