Chinmayi Hassan Shyamprasad Nadig

# Analyzing and improving graphics processing performance in microcontrollers

Master's thesis in Electronic Systems Design September 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

### ANALYZING AND IMPROVING GRAPHICS PROCESSING PERFORMANCE IN MICROCONTROLLERS

## MASTER'S THESIS IN ELECTRONIC SYSTEMS DESIGN

## CHINMAYI HASSAN SHYAMPRASAD NADIG September 2020

Academic Supervisor: Trond Ytterdal Professor, Department of Electronic Systems

Industrial Supervisor: Martin Olsson Senior R&D engineer, Nordic Semiconductor ASA

# Abstract

A typical microcontroller unit (MCU) has limited capabilities for processing and displaying graphics, due to power and size constraints. An increasing demand for rich graphical user interface (GUI) applications in battery powered systems motivates microcontroller vendors to include additional hardware to accelerate graphics processing. The goal of this master thesis was to analyze the graphics processing capability of a typical microcontroller and to explore different architectures for improving performance. A RISC-V ISA based simulator of a generic, heterogeneous, and multi-core system on chip (SoC) with shared memory and I/O written using SystemC + TLM provided the hardware environment needed for the analysis and exploration. LVGL which is a embedded graphics library was used for writing the application code for this hardware simulator.

The main phases of the thesis were - setting up the hardware simulator environment, setting up a benchmarking framework on the application code, doing baseline performance analysis and arriving at possible areas for improvement, designing architectural improvements and exploring various scenarios. The two improvements which were analyzed and performed were adding direct memory access (DMA) capability to the basic display controller, and designing a hardware accelerator for offloading fill and blend operations from the CPU, also with DMA. When these two were used together for drawing different scenes, an average 68% reduction in the cycles was obtained compared to the cycles taken to render it in the baseline scenario, thus increasing the processing speed of the application. In addition to this reduction, an average of 18% of the cycles taken were saved, thus freeing up the CPU to do something else during these cycles.

Keywords: MCU, RISC-V, Hardware Accelerator, TLM, Graphics Processing

# Preface

This report has been written in Spring 2020 to fulfill the requirements of the Master's thesis and has been submitted to the department of Electronic Systems Design at Norwegian University of Science and Technology (NTNU). This work is done in collaboration with Nordic Semiconductor and is a continuation of the specialization project done during Fall 2019.

I would like to first thank Nordic Semiconductor, especially the System Architecture Group, for providing the necessary environment to work comfortably for a year. Biggest thanks to my supervisor, Martin Olsson, who has been the backbone of this thesis by providing invaluable guidance and support since day 1.

Special thanks to my supervisor at NTNU, Trond Ytterdal, for his support and cooperation throughout. His understanding nature helped me complete this work in the midst of the various challenges I faced. My sincere gratitude to my late professor, Kjetil Svarstad, for motivating me to take up the project during Fall 2019 which formed the foundation for this thesis. I wish he could have been there till the end to see me submit this work, but I am fortunate that I got an opportunity to work with him.

The acknowledgements are incomplete without thanking my family for giving me constant comfort and happiness to push through. Big hug and thank you to my partner, Abhilash, who has been my rock for the past decade. Thank you to my mother and my pet dog, Shibu, for checking up on me everyday from 7500kms away, talking to them is a highlight of my day. Finally, thank you to all my friends, colleagues, and everyone else who helped and supported me in finishing this work.

September 2020 Chinmayi Nadig

# Table of Contents

| Ab  | strac                                    | t                                                                                                            | i                      |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------|

| Pro | eface                                    |                                                                                                              | ii                     |

| Ta  | ble of                                   | Contents                                                                                                     | iv                     |

| Lis | st of T                                  | ables                                                                                                        | vi                     |

| Lis | st of F                                  | 'igures v                                                                                                    | iii                    |

| Lis | st of L                                  | istings                                                                                                      | ix                     |

| Ab  | brevi                                    | ations                                                                                                       | x                      |

| 1   | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4 | Oduction         Motivation and Objective         Methodology         Contributions         Report Structure | 1<br>1<br>2<br>3<br>3  |

| 2   | Back<br>2.1<br>2.2<br>2.3                |                                                                                                              | 5<br>6<br>8<br>9<br>10 |

| 3   | <b>Syste</b><br>3.1<br>3.2               | Base Simulator                                                                                               | <b>15</b><br>16<br>17  |

|    | 3.3    | Graphics subsystem on the simulator                              | 20       |  |  |  |  |  |

|----|--------|------------------------------------------------------------------|----------|--|--|--|--|--|

|    |        | 3.3.1 Running LVGL on its simulator environment                  | 20       |  |  |  |  |  |

|    |        | 3.3.2 Porting LVGL to native GCC of the PC (x86)                 | 21       |  |  |  |  |  |

|    |        | 3.3.3 Porting LVGL to run on the simulator                       | 22       |  |  |  |  |  |

|    | р      |                                                                  | 25       |  |  |  |  |  |

| 4  |        | 8                                                                |          |  |  |  |  |  |

|    | 4.1    | Timing concept in TLM models                                     | 26       |  |  |  |  |  |

|    |        | 4.1.1 Types of timing styles in TLM models                       | 26       |  |  |  |  |  |

|    |        | 4.1.2 Loosely-timed coding style and temporal decoupling         | 26       |  |  |  |  |  |

|    | 4.2    | Timing model implemented on the simulator                        | 31       |  |  |  |  |  |

|    | 4.3    | Benchmarking framework for the application code                  | 34       |  |  |  |  |  |

|    | 4.4    | Results                                                          | 37       |  |  |  |  |  |

|    | 4.5    | Discussion                                                       | 48       |  |  |  |  |  |

| 5  | Arcl   | nitectural Exploration                                           | 51       |  |  |  |  |  |

| U  | 5.1    | Improvement 1 - Display Controller with DMA                      | 52       |  |  |  |  |  |

|    | 5.2    | Improvement 2 - Hardware Accelerator                             | 54       |  |  |  |  |  |

|    | 5.3    | 1                                                                |          |  |  |  |  |  |

|    | 5.5    |                                                                  |          |  |  |  |  |  |

|    |        | 5.3.2 Different widgets with the same frame buffer configuration | 57<br>59 |  |  |  |  |  |

|    | 5.4    |                                                                  | 60       |  |  |  |  |  |

|    | 5.4    |                                                                  | 00       |  |  |  |  |  |

| 6  | Con    | clusion                                                          | 63       |  |  |  |  |  |

|    | 6.1    | Future Work                                                      | 65       |  |  |  |  |  |

| Ri | hliogr | raphy                                                            | 65       |  |  |  |  |  |

| DI | unugi  | арпу                                                             | 05       |  |  |  |  |  |

| A  | Cod    | e Files                                                          | 71       |  |  |  |  |  |

|    | A.1    | LVGL Files                                                       | 71       |  |  |  |  |  |

|    |        | A.1.1 Display Driver                                             | 71       |  |  |  |  |  |

|    |        | A.1.2 Main file                                                  | 78       |  |  |  |  |  |

|    | A.2    | Simulator Files                                                  | 81       |  |  |  |  |  |

|    |        | A.2.1 Common header file                                         | 81       |  |  |  |  |  |

|    |        | A.2.2 Parser script for benchmarking                             | 82       |  |  |  |  |  |

|    |        | A.2.3 Display Controller Model                                   | 83       |  |  |  |  |  |

|    |        | A.2.4 Accelerator Model                                          | 90       |  |  |  |  |  |

|    |        | A.2.5 Domain Top files                                           | 98       |  |  |  |  |  |

|    |        |                                                                  | 105      |  |  |  |  |  |

|    |        |                                                                  |          |  |  |  |  |  |

# List of Tables

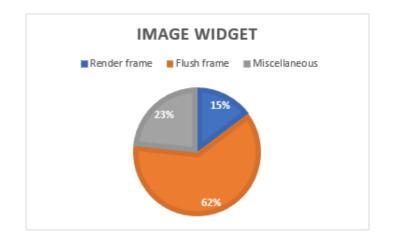

| 4.1        | Numerical breakdown of cycles taken to produce the Image widget                                                                             | 38 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2        | Breakdown of drawing operations in rendering the frame - Image widget                                                                       | 39 |

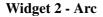

| 4.3        | Numerical breakdown of cycles taken to produce the Arc widget .                                                                             | 40 |

| 4.4        | Breakdown of drawing operations in rendering the frame - Arc widget                                                                         | 41 |

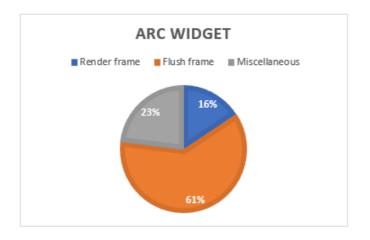

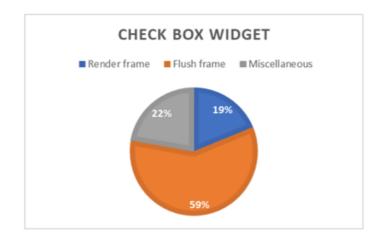

| 4.5        | Numerical breakdown of cycles taken to produce the Checkbox                                                                                 | 42 |

| 4.6        | widget                                                                                                                                      | 42 |

| 47         | box widget                                                                                                                                  | -  |

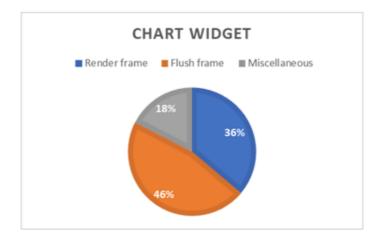

| 4.7<br>4.8 | Numerical breakdown of cycles taken to produce the Chart widget<br>Breakdown of drawing operations in rendering the frame - Chart           | 44 |

|            | widget                                                                                                                                      | 45 |

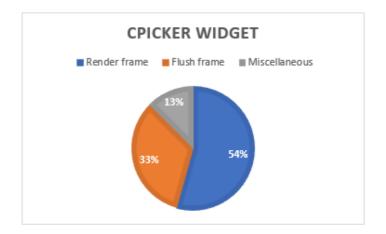

| 4.9        | Numerical breakdown of cycles taken to produce the Cpicker widget                                                                           | 46 |

| 4.10       | Breakdown of drawing operations in rendering the frame - Cpicker                                                                            | 47 |

| 4.11       | 5                                                                                                                                           |    |

|            | widget                                                                                                                                      | 48 |

| 4.12       | Basic drawing operations called by the advanced drawing opera-<br>tions in LVGL                                                             | 49 |

| 5.1        | The % reduction in total cycles relative to the baseline architecture<br>in the chart widget, under different frame buffer and architecture |    |

|            | configurations                                                                                                                              | 58 |

| 5.2        | % of total cycles saved in different widgets under same frame                                                                               |    |

|            | buffer configuration and different architecture configurations                                                                              | 58 |

| 5.3        | The % reduction in total cycles relative to the baseline architecture in the different widgets, under different architecture configurations |    |

|            | and same frame buffer configuration                                                                                                         | 59 |

|            |                                                                                                                                             |    |

| 5.4 | % of total cycles saved in different widgets under same frame  |    |

|-----|----------------------------------------------------------------|----|

|     | buffer configuration and different architecture configurations | 60 |

# List of Figures

| 2.1 | The data flow to rendering graphics in a graphics subsystem                         | 6  |  |

|-----|-------------------------------------------------------------------------------------|----|--|

| 2.2 | General architecture of a MCU                                                       |    |  |

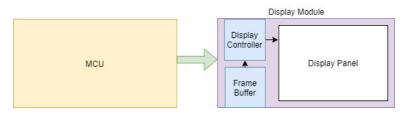

| 2.3 | Configuration 1: Display module with frame buffer and display controller            | 8  |  |

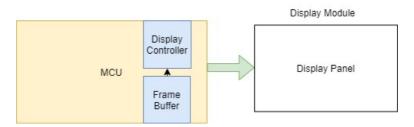

| 2.4 | Configuration 2: MCU with frame buffer and display controller present on-chip       | 8  |  |

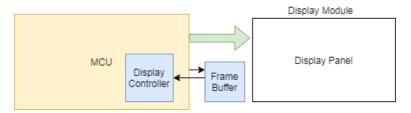

| 2.5 | Configuration 3: MCU with display controller on-chip and exter-<br>nal frame buffer | 9  |  |

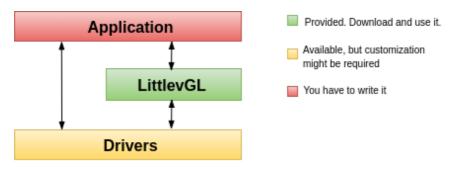

| 2.6 | Structure of LVGL [27]                                                              | 10 |  |

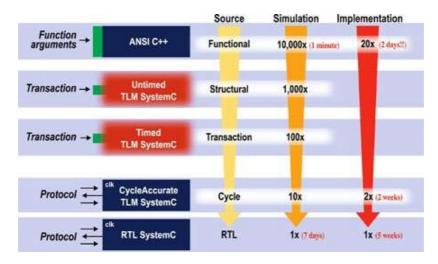

| 2.7 | Implementation and simulation speeds at different levels of ab-<br>straction        | 11 |  |

| 2.8 | Representation of the flow of a TLM transaction from Initiator to Target            | 12 |  |

| 3.1 | Structure of the base RISCV-ISA Simulator [18]                                      | 16 |  |

| 3.2 | Structure of the Customized Simulator used in this thesis                           | 18 |  |

| 3.3 | Result of the print test being run on the App domain CPU                            | 19 |  |

| 3.4 | Steps to port LVGL for use in a project                                             | 20 |  |

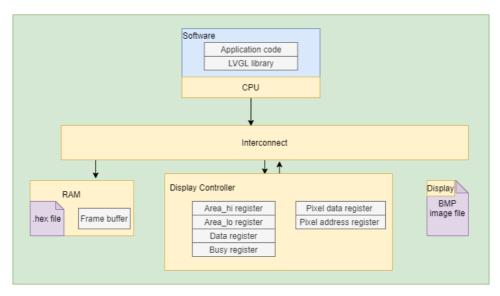

| 3.5 | Graphics subsystem on the SystemC + TLM simulator                                   | 22 |  |

| 4.1 | Blocking transport synchronized explicitly                                          | 27 |  |

| 4.2 | Blocking transport with temporal decoupling synchronized explic-<br>itly            | 28 |  |

| 4.3 | Illustration of temporal decoupling concept with time quantum                       | 29 |  |

| 4.4 | Blocking transport with temporal decoupling synchronized implic-                    | -  |  |

|     | itly                                                                                | 30 |  |

| 4.5 | Output by the python parser script when the arc widget is drawn .                   | 36 |  |

| 4.6 | Image of the Image widget produced on the display                                   | 38 |  |

| 4.7 | Graphical breakdown of cycles taken to produce the Image widget                     | 38 |  |

| 4.8 | Image of the Arc widget produced on the display                                     | 40 |  |

| 4.9  | Graphical breakdown of cycles taken to produce the Arc widget . 4    |    |  |

|------|----------------------------------------------------------------------|----|--|

| 4.10 | 10 Image of the Checkbox widget produced on the display              |    |  |

| 4.11 | Graphical breakdown of cycles taken to produce the Checkbox          |    |  |

|      | widget                                                               | 42 |  |

| 4.12 | Image of the Chart widget produced on the display                    | 44 |  |

| 4.13 | Graphical breakdown of cycles taken to produce the Chart widget      | 44 |  |

| 4.14 | Image of the Cpicker widget produced on the display                  |    |  |

| 4.15 | 15 Graphical breakdown of cycles taken to produce the Cpicker widget |    |  |

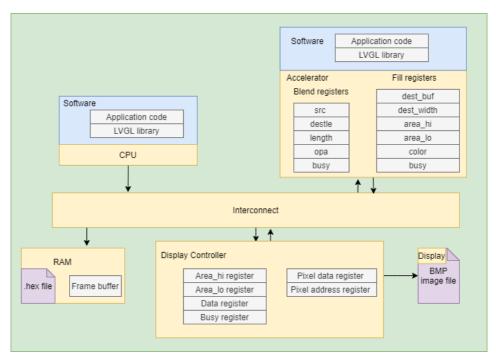

| 5.1  | Graphics subsystem with display controller having DMA                | 52 |  |

|      |                                                                      | 52 |  |

| 5.2  | Graphics subsystem with display controller having DMA and hard-      |    |  |

|      | ware accelerator to offload some application code from the CPU .     | 55 |  |

# Listings

| 4.1  | Code snippet showing setting up timing in an initiator                     |     |  |  |

|------|----------------------------------------------------------------------------|-----|--|--|

| 4.2  | Code snippet showing setting up timing in a target                         |     |  |  |

| 4.3  | <sup>3</sup> Code snippet showing adding a csr instruction in an LVGL draw |     |  |  |

|      | function                                                                   | 34  |  |  |

| 4.4  | Code snippet showing the CPU model reacting to the CSR write               |     |  |  |

|      | instruction                                                                | 35  |  |  |

| 5.1  | Code snippet of the lv_color_mix function in LVGL                          | 54  |  |  |

| A.1  | Display Driver header file                                                 | 71  |  |  |

| A.2  | Display Driver source file                                                 | 72  |  |  |

| A.3  | GUI code main file                                                         | 78  |  |  |

| A.4  | Common macros of the system                                                | 81  |  |  |

| A.5  | Parser script for benchmarking                                             | 82  |  |  |

| A.6  | Display Controller header file                                             | 83  |  |  |

| A.7  | Display Controller source file                                             | 85  |  |  |

| A.8  | Accelerator header file                                                    | 90  |  |  |

| A.9  | Accelerator source file                                                    | 93  |  |  |

| A.10 | App domain top header                                                      | 98  |  |  |

| A.11 | App domain top source file                                                 | 100 |  |  |

| A.12 | Shared domain top header                                                   | 102 |  |  |

|      |                                                                            | 104 |  |  |

|      |                                                                            | 106 |  |  |

# Abbreviations

| GUI | = | Graphical User Interface          |

|-----|---|-----------------------------------|

| MCU | = | Microcontroller Unit              |

| SoC | = | System on Chip                    |

| RAM | = | Random Access Memory              |

| DMA | = | Direct Memory Access              |

| ISA | = | Instruction Set Architecture      |

| TLM | = | Transaction Level Modelling       |

| RGB | = | Red Green Blue                    |

| RGB | = | Red Green Blue Alpha              |

| API | = | Application Programming Interface |

| SDL | = | Simple DirectMedia Layer          |

| CSR | = | Control and Status Register       |

# Introduction

This chapter first talks about the motivation for selecting this topic, then the objective of the thesis, the methodology followed, contribution made by the author and ends with an overview of the chapters in the report.

# 1.1 Motivation and Objective

GUIs are omnipresent in today's world. Computers are conventional devices which can drive excellent quality graphics, but they are general-purpose and power-hungry. The demand for rich GUIs in battery powered systems like watches, smartphones, medical devices, handheld gaming devices to name a few is on the rise [16]. Many of these specialized devices employ MCUs because they cost less, are not power intensive, and are relatively less complex compared to general-purpose computers. Typically, MCUs have limited capabilities for driving graphics owing to the power and size constraints. Therefore, MCUs with graphics capabilities is a niche and developing market [9].

A theoretical study [19] was done as a part of the specialization project during Fall 2019 which discussed and compared the various hardware architectures which can be used for accelerating graphics processing performance in MCUs along with the various kinds of software libraries which can be used to write the GUI code. Of the various graphics libraries compared in the project, LVGL was concluded to be best suited for use in research because it is free, open-source, lightweight, and has support for hardware acceleration. LVGL is therefore used for writing graphics application code in this thesis.

The aim of this thesis is to keep the specialization project as a theoretical foundation and develop upon it. The thesis focuses on analysis of the graphics processing capability of a typical MCU and seeks to explore various architecture topologies for improving the same. A simulator of a SoC is needed for performance analysis and architectural exploration. A RISC-V ISA based simulator written in SystemC + TLM is used and the reason for this choice is elaborated in the background chapter. To explain briefly, Nordic Semicondutor currently uses the ARM ISA which is licensed. RISC-V on the other hand is free, open source, and royalty-free [4]. It has huge potential for use in research and education due to its simple, modular and extensible nature. SystemC + TLM is used to write the simulator because it is highly suited for use in SoC modelling and architectural exploration owing to its high level of abstraction [7]. Having a RISC-V based simulator model in SystemC + TLM which can run the same software code as ARM makes it the perfect choice for use in this thesis.

The thesis primarily seeks to be a study backed by simulation results which aims to understand graphics subsystem in microcontrollers first, set up the system on a simulator, add a benchmarking framework to it, and then analyze its performance along with exploring various architectures to improve the graphics processing performance.

### 1.2 Methodology

The first part of the project was literature review. The search engines used for this purpose were NTNU's Oria, Scopus, ACM digital library, Google Scholar, and IEEE Xplore. The thesis can be broadly divided into three phases - setting up phase, benchmarking phase, and architectural exploration phase.

The setting up phase consists of setting up the simulator and running the LVGL graphics library for writing GUI code on it. The benchmarking phase consists of setting up timing information for the hardware components of the simulator and benchmarking the application code running on the simulator. The benchmarking phase encompasses the baseline analysis phase where the graphics processing performance is analyzed on a baseline architecture and the areas for improving the performance are identified. This phase also provides us a quantitative way to analyze the improvement in performance. The architecture exploration phase consists of designing architectural improvements and exploring various architectural topologies for improving the graphics processing performance.

### 1.3 Contributions

The contributions made by the author are:

- Explaining how to set up a RISC-V based simulator of a SoC which is configurable and represents a modern day, generic, heterogeneous, and multicore SoC systematically. The code listings are also added in the appendix and they can be referred to understand the process better. Here, the simulator is used for graphics processing analysis, but it can also be used for other types of analyses.

- Setting up timing in the TLM models of hardware components in the simulator. This helps to mirror a real-life situation where there are different kinds of components with different latencies connected together in a SoC and quantify the time spent in doing different operations. This general methodology can be referred to set up timing in other TLM models.

- Here, the graphics application code is benchmarked to understand which operations act as a bottleneck on the simulation speed. The methodology can also be followed to benchmark other kinds of application code.

- The graphics processing performance is analyzed in a baseline architecture configuration and then improvements are identified, designed, and explored. The ease of adding new components, changing the topologies, and adding latencies to perform architectural exploration on TLM models is demonstrated here.

### 1.4 Report Structure

#### **Chapter 1 - Introduction**

Chapter 1 introduces the thesis along with its motivation and objective. The methodology adopted in this thesis has then been described along with the contribution made by the author. The chapter concludes with the report structure.

#### Chapter 2 - Background

Chapter 2 provides the background theory needed to read this report. It first explains the graphics subsystem in a MCU environment and also introduces the graphics software libary LVGL which will be used for writing GUI code. The chapter also explains why a RISC-V ISA based simulator of a SoC written using SystemC + TLM is used in the thesis by providing relevant background.

#### Chapter 3 - System Setup

Chapter 3 provides a detailed account of how the SoC simulator was set up, the graphics subsystem of a typical MCU emulated on it, and a simple graphics test written using LVGL was run on it. The chapter is divided into sub-chapters as needed to break up the process and for easy understanding.

#### Chapter 4 - Benchmarking

Chapter 4 is an integral one. The first part explains the concept of timing in TLM models and the next part explains how timing is set up in the TLM models of the hardware components which make up the simulator. The middle part explains how the benchmarking framework is set up to analyze the breakdown of the cycles taken to draw a scene to the display. The last two parts of the chapter are results and discussion where the baseline performance is analyzed by drawing different scenes to the display and the bottleneck operations which hog the most cycles are identified for improvement.

#### **Chapter 5 - Architectural Exploration**

Chapter 5 begins by presenting the design of two architectural improvements - Adding DMA to the display controller model, and a hardware accelerator model for accelerating blend and fill drawing operations, also with DMA. These improvements are then explored under various scenarios in the results section and the observations are summarized in the discussion section.

#### **Chapter 6 - Conclusion**

Chapter 6 summarizes the entire work done and concludes the thesis by presenting the future scope of the work.

# Chapter 2

# Background

This chapter helps to establish the theoretical knowledge needed to understand the report. The first part provides an overview of graphics subsystem in a MCU by explaining its high-level architecture. It also introduces the GUI software library LVGL which is used for application code development in this thesis. The next part explains modelling systems using SystemC + TLM and its advantages. The final part talks about the RISC-V ISA and why it is used in processors. The first parts provide relevant background knowledge, but the last two parts along with providing knowledge answer why a RISC-V ISA based simulator written using SystemC + TLM is used in this thesis.

# 2.1 Graphics Subsystem

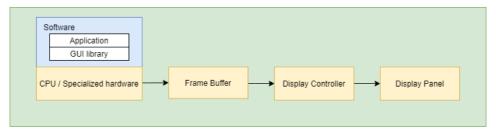

Figure 2.1: The data flow to rendering graphics in a graphics subsystem

The basic flow to displaying graphics is as shown in the figure 2.1. The application code can be run on the CPU or a specialized hardware unit. The code is usually written using a GUI software library. When the code runs, the graphical instructions build the image in the frame buffer which is a memory unit. The display controller is responsible for picking up the image built from the frame buffer and driving it to a display panel which displays it [15].

### 2.1.1 Components

The primary components which make up a graphics subsystem are the microcontroller, software, frame buffer, display controller, and the display panel which are described briefly in the following subsections.

### Microcontroller

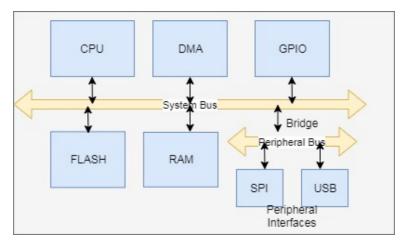

Figure 2.2: General architecture of a MCU

Figure 2.2 shows the general architecture of an MCU. The system bus is connected to the Flash Memory, RAM, DMA (optional) and General Purpose Input Output (GPIO) units. Units for interfacing with the outside world, called the peripheral units are connected through a peripheral bridge which is connected to the system bus via a bridge. The application code is run on the CPU, but it can also be made to run on a dedicated hardware unit. The graphical instructions build the image in the frame buffer. The frame buffer is a memory unit which can be present internally in the MCU or be external to the MCU [3].

#### Software

The application code which runs on the microcontroller is called the software. It is usually written using a GUI software library. A GUI library has callback functions to the driver of the hardware units if present. The library helps to set up the GUI by implementation of APIs for drawing fundamental shapes, 2D image processing and providing support for hardware acceleration of graphics functions [3].

#### **Frame Buffer**

It is also known as the Graphic Random Access Memory (GRAM). The frame buffer is a volatile memory space that is used for storing the final image that is shown on the screen. Its size depends on the resolution of the display and the color depth.

Frame buffer size (Bytes) = Number of Pixels x Color Depth (Bits)/8

Example: For a display at 24 bpp color depth and resolution of 480x272, the frame buffer memory required is 480x272x24/8 = 391,680 Bytes (392 kB)

It can be stored in the microcontroller RAM, in an external RAM or integrated in the display controller. Double buffering (having two frame buffers) is commonly used to avoid a glitch called tearing which occurs when two frames are displayed simultaneously. In double buffering, one buffer is used for drawing to compose the next image while the other stores the current image and is driven to display [20].

#### **Display Controller**

The purpose of the display controller is to transfer the contents of the frame buffer to the display panel. In this way, it continuously refreshes the display panel and the frequency with which this is done is called the refresh rate. If the screen is refreshed 60 times in a second, then the refresh rate is 60Hz. The display controller can be present either in the MCU or external to the MCU [20].

### **Display Panel**

The display panel is driven by the display controller and it displays the final image. The data is driven to it by the controller from the frame buffer by formatting it. The data output to the panel has many signals for synchronization. Display panels come in many varieties and sizes, and they are chosen depending on the preference of the system [20].

### 2.1.2 Configurations

The components of a graphics subsystem can be connected together in different configurations. The most common configurations are:

Figure 2.3: Configuration 1: Display module with frame buffer and display controller

The configuration in figure 2.3 is used in MCUs which do not have built-in graphics support. The frame buffer and the display controller are both located on a display module and connected to the MCU through it. A serial interface like SPI is used for the transfer of data from the MCU to the display module.

Figure 2.4: Configuration 2: MCU with frame buffer and display controller present onchip

As compared to the previous configuration, the configuration in figure 2.4 has both the frame buffer and display controller present on the MCU and connected to an external display panel. This configuration can lead to significant savings in terms of memory accesses as having an internal frame buffer maximizes performance and minimizes bandwidth limitations for the display controller. A parallel interface like RGB is used for the transfer of data from the MCU to the display module. Another advantage is that on-the-fly custom transformations of pixel data is possible when the controller is on the chip. It is also a configuration preferred by some customers as they can buy a simple display panel cheaply and there is no need to buy one with both the frame buffer and controller.

Figure 2.5: Configuration 3: MCU with display controller on-chip and external frame buffer

The configuration in figure 2.5 is similar to the one above and offers the same advantages. The only difference is the frame buffer can be external in case of storage constraints on the chip.

#### 2.1.3 GUI library - LVGL

The GUI library which is used for application code development in this thesis is LVGL [12]. It is a graphical library which helps to create embedded GUI. Some of its key features are:

- Open-source and free under the MIT license.

- Hardware-independent and can be used without any MCU or display.

- Written in C but also compatible with C++.

- Made of building blocks like lists, blocks, charts, images and also supports advanced graphics like animations, opacity, anti-aliasing, etc.

- All the graphic elements are fully customizable.

- Supports multi input devices and multi displays.

- Has a very less memory footprint and is scalable.

- Can also support OS, external memory and GPU.

The reason it is used in this thesis is because it is open-source, completely free, easy to use, hardware-independent, and supports external memory and GPU. It can start an embedded GUI design by running it on its PC simulator environment. This offers a major advantage of writing and testing real LVGL applications without the need for embedded hardware. There are plenty of tutorials, examples, themes, and documentation which facilitates its ease of use and GUI designing. The structure of LVGL is as shown in figure 2.6 [27].

Figure 2.6: Structure of LVGL [27]

*Application* creates the GUI and handles the tasks. It is written using the LVGL API which makes calls to the functions of the LVGL library or directly to the drivers.

*LVGL* is the layer with which the application communicates to create the GUI. It registers the input and display device drivers using a Hardware Abstraction Layer (HAL).

*Drivers* contains functions which make calls to functions that drive the display, to hardware accelerator/GPU, or to the display controller.

### 2.2 SystemC + TLM modelling

The SoC designs today are complex with multiple heterogeneous processors, onchip buses and caches, peripheral control devices, and hardware accelerators for dedicated functions. There are a growing number of Intellectual Property (IP) blocks that interact through bus technologies or networks on chip (NoC). Using the traditional RTL modelling for design and verification takes too much effort for development, provides slow simulation, and it is not ready early in the design flow for architectural exploration and early hardware/software integration. Until the final chip is ready, software cannot be written for the system which slows down the development cycle and increases the time-to-market. This makes RTL costly and has limited debugging capabilities. One solution to these limitations is raising the abstraction level and creating models which have less details compared to the RTL models. To address these limitations of RTL, SystemC transaction level models are used widely for SoC design and verification. The system functionality is represented using the concept of transaction that is, operations and interactions between the components by hiding the low level implementation details [26] [25].

SystemC [2] is a system level design and verification language built on top of C++. It allows modelling and execution of both hardware and software at different levels of abstraction. The high level of abstraction enables faster and more productive analysis, design, and redesign of architectural trade-offs compared to the RTL level. TLM [28] is a transaction based methodology approach and is based on C++ and SystemC. TLM provides an abstraction level in which the behavior of the functional blocks in the system is separated from the communication. The focus is on communication and it is performed by passing a high level data structure called transaction between the blocks through abstract channels or interfaces. Transaction level models use software function calls to model the communication between the blocks in a system in contrast to the RTL models where signals are used [11].

Figure 2.7: Implementation and simulation speeds at different levels of abstraction

TLMs have multiple abstraction levels from cycle accurate to un-timed models as shown in figure 2.7. Initially, designers use higher level models with minimum details and these models can then be refined over time to include more information as the design cycle progresses.

Figure 2.7 also shows how the implementation and simulation speed increases with higher level of abstraction. The main concept in TLM is abstracting away the communication on the buses by using transactions. Instead of modelling all the bus writes and monitoring changes in their states, only logical operations like reading, writing, etc done by the buses are considered in the model. These abstractions increase the simulation speed by many orders of magnitude [1].

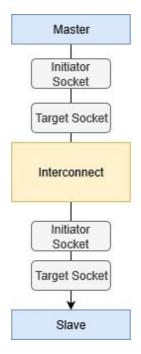

Figure 2.8: Representation of the flow of a TLM transaction from Initiator to Target

A transaction is an atomic exchange of data between the initiator or master and target or slave. The transactions are forwarded from the master to the slave. Example of a master is the CPU and a slave is Memory. The initiator initiates and issues the transaction through an initiator socket and a target is always ready to receive it through a target socket. The transactions are routed by the interconnects to their destination using the address. This corresponds to the classical concept in bus protocols [17]. The initiator communicates with the target using a transport interface and the target needs to implement the transport method. This is done by having the target register a callback method with the socket. This concept is represented in figure 2.8. Some components have only initiator sockets, some have only target sockets, and some have both initiator and target sockets. The type of information which is exchanged via a transaction depends on the bus protocol being used. Generic payload is the class type used for the transaction objects which are passed through the interfaces and these objects have attributes that are typically found in memorymapped bus protocols. Some are common to all protocols like:

- Type or command is the direction of data exchange, if it is read or write

- · Address which determines the target and the register or component address

- Data that is sent and received

- Type of transfer like single word transfer or burst transfer

- Response status like success or failure

In RTL everything is synchronized using clocks and are synchronous in nature, whereas TLM models do not use clocks and are asynchronous in nature. In TLM, the synchronization happens when data is communicated between components. By modeling at this level early in the design cycle, designers can perform architectural exploration and find an optimal architecture before committing to the low-level details of a complete implementation. The TLMs can also be reused during functional verification to ensure that the design is equivalent to the RTL implementation [7] [10]. In conclusion, SystemC + TLM offers many advantages as mentioned above and is highly suitable for use in SoC modelling and architectural exploration thus making it the right choice to be used in this thesis.

### 2.3 RISC-V ISA

Custom SoCs are becoming ubiquitous and it is rare to find an electronics product which does not have an on-chip processor. The semiconductor industry today has been revolutionized by open source products from networking standards, to software to operating systems. Similarly, having an open ISA will enable greater innovation in processor architectures as a result of the free-market competition.

Many companies have patents on their ISAs which prevents others from using it without a license. The negotiations for obtaining a license can take a long time and it is also very expensive. This makes it very inaccessible to the academia and research sector which could have greatly contributed to the improvement of the ISA. On the other hand, a shared open core design translates to faster innovation, shorter time to market, low cost from reuse, transparency and processors becoming more affordable for smaller devices.

RISC-V was developed with the goal of creating a universal instruction set which is open and free to all users [4]. RISC-V [21] is a royalty-free and open-source general-purpose ISA used for designing processor architectures which builds and improves upon the original RISC architectures. It has a common base set ISA and a toolchain that can handle both the base ISA and customized instructions defined by a SoC architect. Some of its key advantages are [30]:

- Enabling SoC architects in customizing processor architecture is one of its biggest advantages which differentiates it from the other ISAs in the market. Specific application issues can be solved by adding various customizations like hardware accelerators, custom instructions, different cache sizes all without breaking compatibility and causing fragmentation.

- 2. The base ISA is very simple and modular. The instruction coding is very regular and does not have complicated memory instructions. This simplifies the implementation and keeps it architecture clean as a result of which RISC-V cores are smaller than ARM and x86 cores [22].

- 3. As the ISA is open, the designs can be optimized for different scenarios like low power, performance, security, etc. It provides higher control over the hardware implementation and fewer compromises.

- 4. It is a frozen ISA which means that the base instructions are frozen and optional extensions when added are also frozen. This leads to stability of the ISA and provides solid foundation to preserve the software investments. Software development can be done more confidently because the software written for RISC-V will run on all similar cores of RISC-V forever.

Though the ISA is incomplete and its ecosystem is in its early stages of development, it is very promising. On one hand, its structure of a small base ISA makes it suitable for research and education while also making it capable of being a suitable ISA for inexpensive and low-power embedded devices. On the other hand, the option of adding a variety of extensions allows it to form a powerful ISA which could be used for general-purpose and high-performance computing.

# Chapter 3

# System Setup

This chapter describes in detail how the SoC simulator used in this thesis was set up and a simple graphics test was run on it. A RISCV-ISA based SoC simulator has been used in this thesis which has been structured as per our requirements. This simulator is written using SystemC + TLM. A base RISCV-ISA simulator written in SystemC + TLM provides important components needed for our simulator. The description of this base simulator is provided in one of the sections. How our simulator is customized and structured is also described in the next section followed by simple testing to check its sanity.

The next section of this chapter is emulating a graphics subsystem in our simulator. To emulate a simple graphics subsystem, the GUI code is written using a graphics library and run on the CPU model, a frame buffer is prepared in the RAM model and a display controller gets the data from the frame buffer and outputs it to a display unit. The graphics library used for writing the GUI code is LVGL. It is set up in our simulator by first running it in its own simulator environment, then compiling it using native GCC of the PC (x86) and then finally compiling it using GCC for RISC-V. The display is emulated by using a library which prints the data in the frame buffer to a bmp file and a simple display controller is modelled in SystemC + TLM.

### 3.1 Base Simulator

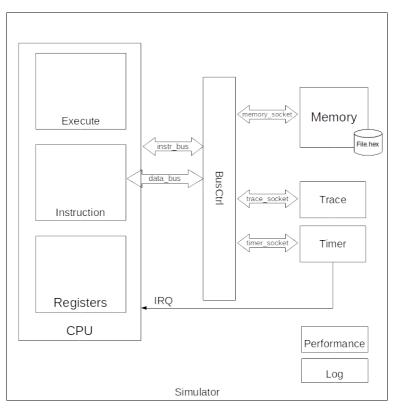

The RISCV-ISA simulator [18] which was used as the starting point for setting up the system was found on GitHub and is licensed under the GNU General Public License [8] giving permission for private use and modification. This simulator is coded in SystemC + TLM thus making it suitable for this thesis as discussed in the background chapter. The structure of the simulator is explained in the figure 3.1.

Figure 3.1: Structure of the base RISCV-ISA Simulator [18]

It is to be noted that this is how the components are connected in the simulator and in our model, this configuration of connection is not used as is. This configuration is used as an example and our simulator is connected along similar lines. Also not all the components in this simulator are used in our model and only the necessary ones are picked out, modified if needed and connected. CPU is a top-level initiator model and encompasses the Registers, Instruction, and Execute models. The Registers model implements register files, PC register, and CSR registers. The software to be run on the CPU is stored in the Memory (loaded as a hexfile) and it has read and write capability. The Instruction model fetches the instruction to be decoded through the instruction bus (instr\_bus) and decodes it. If the instruction requires any data to be read from or written to the Memory, it is fetched using the data\_bus and the Execute model executes it.

The CPU model is an ISA based processor and it has capability to decode and execute three kinds of instructions:

- Compressed instructions having a C extension

- Multiplication and Division instructions having a M extension

- Atomic instructions having an A extension

BusCtrl is an interconnect model and a bus manager. It has target sockets for connecting initiator models like the CPU and initiator models for connecting target models like the Memory, Trace, and Timer. It only forwards transactions to the correct target without modifying the transactions. Trace is a simple trace peripheral which creates a xterm window for printing out the received data and timer is a simple real-time IRQ programmable counter peripheral. There are also some helper classes like the Performance model used for storing the performance indicators of simulation and Log class for logging.

All of these components are connected together as shown in the figure 3.1 in the Simulator Top file. This simulator was studied to get a basic understanding of modelling a SoC in SystemC + TLM. The simulator package also comes with many tests which can be run to test various criteria and it provided a good starting point to understand how the tests are written and run on the simulator.

### 3.2 Customized simulator

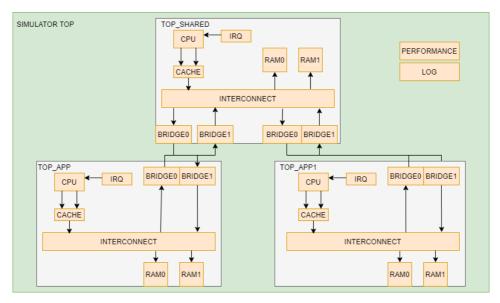

The simulator which is used throughout this thesis is connected as shown in figure 3.2 to start with. A few modifications are made to it as the thesis progresses which are described when they are done. It derives its components from the base simulator described in the previous section, in-house Nordic Semiconductor models and some models developed specially for this thesis. The simulator is structured to model a generic, heterogeneous, and multi-core system with shared memory and I/O.

Our simulator has 3 domains namely the Shared domain, App domain, and App1 domain. All the domains have their own Top file in which the component models are instantiated and connected. The App domain is the one which will be used for running the application code on. The shared domain acts like a global domain with shared memory and I/O, and all the other domains are connected to it. The App1 domain is not used in this thesis. It is connected to show that the simulator is easily configurable and extendable where new components and domains can be added with ease.

Figure 3.2: Structure of the Customized Simulator used in this thesis

In the Simulator Top file, the three domains are instantiated and connected. The CPU model and the Memory model (renamed here as Ram) are taken from the base simulator along with the helper models Performance and Log. The IRQ model, the Interconnect model, and the Bridge models have been developed in-house.

Each domain has a CPU with a Cache and IRQ. The CPU is a master or initiator model connected to the Interconnect through its Cache. The Memory model is renamed as the Ram model and used here. Two instances of Ram are connected in each domain where instance 0 is the ROM and instance 1 is the RAM. The Ram instances are connected as slaves or targets to the Interconnect. The Interconnect is a bus manager to which any number of master and slave components can be connected and it forwards the transaction without modifying it. It is similar to the BusCtrl model in the base simulator, but is designed differently.

The transactions are initiated in the CPU model and forwarded either to the Ram model or to the Bridge through the Interconnect depending on the target address. Bridge0 and Bridge1 are Bridge models having one initiator socket and one target socket. They are used for forwarding transactions out of the domain (Bridge0 connected as a target to the Interconnect) or for receiving transactions forwarded from other domains (Bridge1 connected as an initiator to the Interconnect). The App domain is the Application domain and used for running majority of the applications. The App1 is a replica of the Application domain. The Shared domain is connected to both App and App1 domains. Programs can be run on all the three domains. This functionality is tested by running a simple print test on all the CPUs.

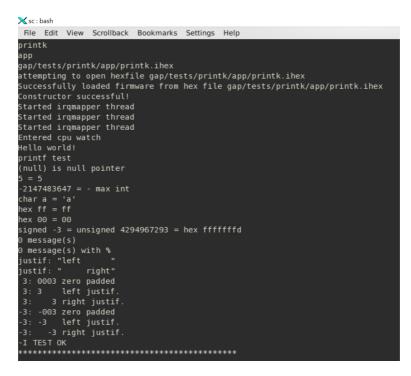

Figure 3.3: Result of the print test being run on the App domain CPU

The program ran successfully on all the three CPUs and the snapshot of the the test running on the App domain is shown in figure 3.3. The first line in the screenshot is the name of the test running and the second line is the name of the domain in which it is running.

### 3.3 Graphics subsystem on the simulator

The graphics subsystem in a MCU and its components were described in detail in the background chapter. This section describes how it will be set up in our SoC simulator. First, we need a software graphics library which is used for writing the GUI code by making calls to its API. The graphics library chosen to be used in this thesis is the LVGL library and it is described in the background chapter. Understanding the library is the first part in setting it up to run our simulator which is done by running LVGL in its own simulator environment. Next, LVGL was ported to run on the native GCC of the PC (x86) to understand the process of porting. The last part is emulating the entire graphics subsystem on the simulator and porting LVGL to run on our simulator. All these are explained in following sub-sections.

### 3.3.1 Running LVGL on its simulator environment

LVGL has the feature of running in its own simulator environment without the need for any development board [24]. This is a very useful feature as it allows one to write and experiment with real LVGL applications. Other advantages of having this feature are it makes the LVGL code hardware independent, cross-platform compatible, and portable.

The PC simulator was set up on Windows using Visual Studio. Everything was set up and only the main file had to be run by uncommenting the test to be run which can be chosen. There are a variety of tests to check the working of different LVGL objects, LVGL themes, LVGL fonts, etc. The simulator uses SDL [23] which is a cross platform libray for simulating the display and the input.

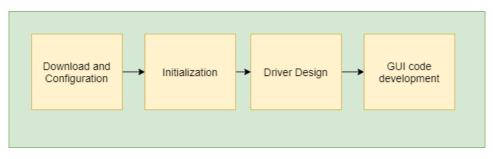

Figure 3.4: Steps to port LVGL for use in a project

The entire method for using LVGL was studied, the figure 3.4 illustrates the steps.

- 1. The first step is to download or clone its Github repository [13]. It should be copied to the project directory and then in the configuration file, only the modules and functions which will be used are enabled. Only enabling the parts of the library which will be used helps in keeping a small memory footprint of the library.

- 2. Next step is to initialize the library and its components.

- 3. Drivers make calls to functions that drive the display/input/file systems and also to hardware accelerators defined for specific functions. The drivers which are used must be designed, templates for which are provided in the library and they have to be modified according to the system being used. The three primary steps in the design of drivers is the initialization of the driver, definition of the driver, and finally registration of the driver. Drivers have two fields namely data fields and callback functions which must be defined.

- 4. Next part is the GUI code development. The LVGL repository has lot of examples for using different kinds of objects, themes, and applications. The examples can be used directly or new code can be written as required. The code is written by creating different kinds of objects like lists, widgets, images and defining their attributes like position, size, color, style, etc. The GUI functions are called and the final part is calling the task handler of the library periodically by using a timer interrupt to handle the tasks.

#### **3.3.2** Porting LVGL to native GCC of the PC (x86)

Using the knowledge obtained by running the library in its simulator environment, LVGL was set up on native GCC of the PC in this part. In the simulator, SDL is used for simulating the display and input layers. The linux environment which was used for doing the simulations in this thesis did not have access to SDL. Assuming that the GUI we are making is static is nature, an input device would not be required. The display must still be present so that the GUI is output somewhere. Therefore, as an alternative to SDL for technical reasons, the display was emulated by writing the image which is in the frame buffer to a BMP (bitmap) image file. To do this a library called QDBMP [14] which stands for "Quick N Dirty BMP library" was used. This is a minimalistic C library which is used for handling BMP image files. The QDBMP header and C files are added to the work folder.

The LVGL repository was cloned to the work folder and a simple makefile was written for compiling the various source code files in the library. A main file was written where initialization was done and a simple GUI function for creating some objects of different shapes and colors was defined and called. A display driver is written which has the data field as the frame buffer and a callback function to flush the contents of the frame buffer to the QDBMP file.

The frame buffer is screen sized meaning it is the size of the display screen and equal to resolution to the screen. The LVGL code is run on the CPU model which writes pixel data to the internal frame buffer and after it has finished preparing the frame, the display driver callback function writes it a BMP image file pixel by pixel by using functions from the QDBMP library.

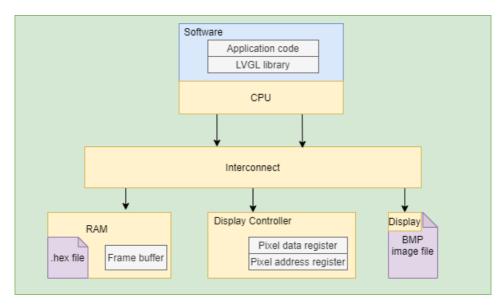

### 3.3.3 Porting LVGL to run on the simulator

A graphics subsystem in a MCU as seen in the figure 2.1 is made up of - CPU, software, frame buffer, display controller, and display panel. The figure 3.5 illustrates how the entire graphics subsystem was emulated on our simulator. The GUI application code was written using the LVGL library. The same procedure like in porting LVGL to native GCC of the PC was followed. The application code is common for all the domains. We can choose which CPU the application code runs on by giving the test name and the domain name as command line arguments.

Figure 3.5: Graphics subsystem on the SystemC + TLM simulator

Instead of compiling it on native GCC of the PC(x86), to run it on our simulator it is compiled on GCC for RISC-V. It is compiled to the hex format, loaded to the RAM model and run on the CPU model. When the application is run on the CPU, it prepares the frame in the frame buffer which is stored in the RAM model. The CPU decodes the instructions and if the instruction requires read or write it has the capability to perform it.

Once the entire GUI has been prepared in the frame buffer, the callback function in the display driver to flush the contents of the buffer to the display is called. The CPU then transfers the data from the frame buffer to the display controller by writing the RGB data and 2D coordinates of the pixels one by one to the registers of the display controller. The baseline display controller is modelled using SystemC + TLM and connected to the simulator as shown in figure 3.5. It has one target socket which receives the pixel data in the form of transactions. It is connected as a target to the interconnect model which is a bus manager model for forwarding the transactions by address decoding. It has two registers one for the pixel address register stores the 2D coordinates of the pixel and pixel data register stores the RGB color data of the pixel. The controller model implements a transport function. When the controller model sees that data has been written to both its registers, it uses the QDBMP functions to place the pixel in the BMP image file which emulates a display panel.

# Chapter 4

# Benchmarking

The simulator has both hardware and software parts. The simulator is made up of various hardware components modelled in SystemC + TLM like CPU, RAM, Bridge, etc. The software which runs on the simulator is the application code written using LVGL. Every operation takes some amount of cycles to complete be it a simple line drawing operation done by LVGL or a transaction moving from the CPU to the RAM through a interconnect.

The first section is explaining the timing concepts in TLM models followed by a section on setting up a suitable concept of timing in the hardware models of the simulator. The third section is setting up a benchmarking framework for the application code running on the simulator. The next section is the results section where the application code is run on the simulator for drawing different scenes on the display and the total cycles taken by the CPU is broken down to cycles taken for individual operations. The final section is the discussion section which analyzes and discusses the results presented in the previous section. Potential areas for improvement are identified by doing baseline performance analysis.

This chapter is integral as it helps us to understand which operations hog most cycles and gives a concept of time to the simulator as a whole. Otherwise, the simulation would complete in an infinitesimally small amount of time and would not mirror real-life situations well. It also helps to establish a baseline which can be compared with when architectural improvements are done on the simulator in the next chapter.

# 4.1 Timing concept in TLM models

Understanding the timing concepts and styles in TLM models is important in order to set up timing on our simulator. The types of timing styles in TLM models are briefly described first and the timing style which is used in our simulator is explained in detail.

## 4.1.1 Types of timing styles in TLM models

- 1. Loosely-timed: The timing is provided at the level of the individual transaction. It makes use of the blocking transport interface. This interface has only two timing points - the initiators call to b\_transport which carries the transaction request (beginning of the request) and the return from the target which carries the response (beginning of the response). This style supports the temporal decoupling concept in which the individual SystemC processes are allowed to run ahead in their own local time wrap without advancing the actual simulation time until they reach a time when they should synchronize with the rest of the system. This style is ideal for use in our simulator since it uses (b\_transport) and is explained in detail in the next subsection.

- 2. **Approximately-timed:** This is supported by the non-blocking transport interface which provides timing annotation for multiple phases and points during the life of a transaction. The transaction is broken down into many phases and this is used when working with particular hardware protocols. This style is detailed and slow to simulate and is not ideal for use in our simulator.

- 3. Untimed style: TLM has no explicit support for this as they have no value since all models need a concept of time. Loosely timed models with zero timing annotation can be used as untimed models. Here, b\_transport is only used to send the data to the target and does not carry any information about response times [29].

## 4.1.2 Loosely-timed coding style and temporal decoupling

In loosely-timed style, the initiator communicates with the target using a blocking transport interface, the target implements the transport method and registers it as a callback with its target socket so that when the initiator calls the method it receives it. The initiator initiates transactions and forwards to the interconnect which routes the transaction to the correct target depending on the address embedded in the transaction.

Transaction argument is passed through reference using the b\_transport function and has no return value. The target receives and responds to the transaction. It can perform some actions to modify the attributes of the transaction and finally it returns the transaction response status to the initiator. The b\_transport of the target executes in the context of a thread process in initiator module and when it returns, the control is unwound through the call chain back to the initiator [29].

Another argument which is passed through reference using the b\_transport function is the timing annotation which is the local time offset. The timing annotation is active on both the call to and the return from the transport method. Since it is sent as a reference, this means that the receiving function in target can directly modify it and that change is reflected on the sender side.

**sc\_time\_stamp** returns the current simulation time of the system. The recipient of a transaction is required to behave as if it had received the transaction at **effective\_local\_time = sc\_time\_stamp() + local\_time\_offset**. There are two ways in which synchronization of the local\_time\_offset with the system simulation time returned by sc\_time\_stamp() can be achieved.

#### Explicit synchronization

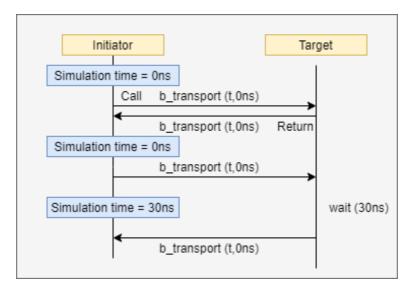

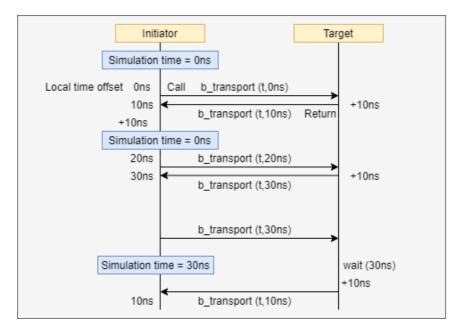

Figure 4.1: Blocking transport synchronized explicitly

In explicit synchronization, wait can be called explicitly on both the initiator and the target side. Untimed models can easily be implemented by setting the timing parameter in the transport calls to zero as shown in figure 4.1 where the transport method returns immediately. Wait can be called explicitly on the target side to represent the response time of the target. The wait models the time taken by the target to process the transaction and it waits for this time to return. We can observe that the simulation time is advanced when the wait is called and on return from the target, the time parameter is reset to 0.

Figure 4.2: Blocking transport with temporal decoupling synchronized explicitly

Temporal decoupling is the running of the initiator thread ahead of the simulation time as shown in figure 4.2. The transport method passes a non-zero value for the time argument. The initiator and the target can each increase the value of the time argument to further advance the local time offset. The time argument is returned untouched to the initiator from the target if it is not incremented on the target side. Adding the time returned by the call to the simulation time can give the time at which the transaction completes, but the simulation time itself does not advance. For the time argument to be added to the simulation time, wait must be called either on the target or initiator side. After the wait is called, the local time offset must be reset to zero. A disadvantage of using temporal decoupling like this is that an initiator thread can hog the processing time indefinitely until wait is explicitly called [5].

#### **Implicit synchronization**

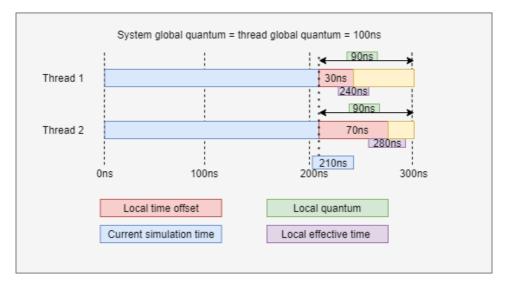

Loosely-timed models can also progress in the absence of explicit synchronization points. In SystemC a single synchronized view of time is present which is used by all the threads. When time quantum is used, the initiator can only run ahead as far as the end of the quantum before implicitly calling wait to synchronize with the SystemC simulation time. This is called temporal decoupling and it allows each initiator thread to keep its own local view of time and it can run ahead of the simulation time until it has to synchronize with the other threads. This concept is illustrated in figure 4.3 [6].

Figure 4.3: Illustration of temporal decoupling concept with time quantum

The system global quantum time is the time unit on which all the threads synchronize. Here, the system global quantum is taken as 100ns, so all the threads synchronize on 100ns, 200ns, 300ns and so on. The thread global quantum is the time unit on which a particular thread synchronizes. Both the system global quantum and the thread global quantum are taken to be 100ns. The current system time stamp is assumed to be 210ns. Both the threads can advance from the system time stamp and the time by which they advance is called the local time offset which is 30ns for thread 1 and 70ns for thread 2. The time remaining for both the threads until the end of the quantum as relative to the current system time is called local quantum and is equal to 90ns. The local effective time which is the sum of the current system time and the local time offset of the thread is 240ns for thread 1 and 280ns for thread 2.

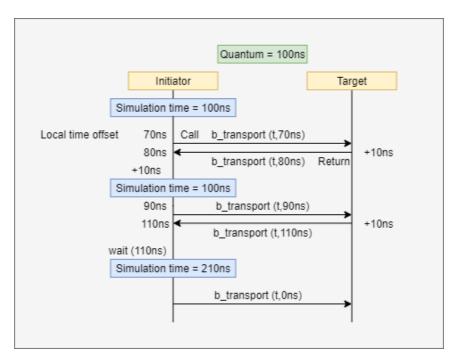

Figure 4.4: Blocking transport with temporal decoupling synchronized implicitly

Synchronization happens implicitly when temporal decoupling is used with time quantum as shown in the figure 4.4. A quantum is the greatest amount of time that a thread can differ from the system simulation time. Once, the local time of the thread exceeds the quantum, the wait is called implicitly in the thread to synchronize with the system time and the local time is reset to zero.

The temporally decoupled initiator advances its local time offset until the time quantum is exceeded. This happens when the transport method returns from the target with a local time offset of 110ns which exceeds the quantum 100ns. So, wait is called implicitly in the initiator thread for the time unit 110ns and the simulation time advances to 210ns. We can also observe that when wait is called, the local time offset is reset to 0ns.

#### 4.2 Timing model implemented on the simulator

The loosely-timed style with temporal decoupling and time quantum is implemented in our simulator. The advantages of this is:

- It allows multiple system initiators to progress ahead of the system time and they synchronize due to the presence of the time quantum.

- The performance of loosely-timed models with blocking interfaces is improved and bottlenecks in processing are avoided. It ensures that a thread does not hog all the processing time and synchronizes with the simulation time regularly.

- Easy to implement. Latency is given as an argument in the constructor while initialising new objects of a target and when the transaction gets routed to the target, this latency is added to the delay sent from the initiator and gets reflected in the total simulation time when it is synchronized each quantum.

The methodology for setting up the timing model involves two parts - set up in the initiator and set up in the target. Both are described using code snippets compiled from various files. The snippets are not complete and are complied from various files to show the general methodology.

#### Set up in initiator

```

1 /* In header file */

2 #include "tlm_utils/tlm_quantumkeeper.h"

3 tlm_utils::tlm_quantumkeeper qk; // Declaring a time keeping

thread

4

5 /* In constructor */

6 gk.set_global_quantum(sc_time(1, SC_US)); // Update the global

quantum

7 qk.reset(); // Reset the local time offset to 0

8

/* Function initiating transactions to targets */

9

10 void CPU::single_step(int benchmark)

11 {

sc_time delay;

delay = qk.get_local_time(); // Returns the current local time

14

offset

instr_bus->b_transport(*trans, delay); // Annotate b_transport

with local time

qk.set(delay); // Update qk with time consumed by target

16

```

```

18 // qk.inc( sc_time(100, SC_NS) ); // Further time consumed by

18 initiator

19 if (qk.need_sync()) // Check local time offset against quantum

20 {

21 qk.sync(); // Updation of the global time sc_time_stamp

22 }

```

Listing 4.1: Code snippet showing setting up timing in an initiator

The code listing 4.1 above shows how timing is set up in the CPU initiator, the same methodology is followed in all the initiators. In this example, the timing thread is declared as qk in the header file of the CPU model. The global quantum is updated to the required value, taken to be 1us and the local time offset is zeroed by calling the reset function in the constructor function of the CPU called when a new object of CPU is initialized.

In the function which initiates transactions to the target, the SystemC time variable, delay, is updated with the local time offset of the CPU thread using the get\_local\_time method and then the blocking transport function of the target is called with the transaction and timing arguments. The timing annotation of the b\_transport function is active on both the call to and the return from the transport method. The timing argument can be updated in the target to indicate its response time and on return, using the set method, qk is updated with the time consumed in the target.

There is also an option to further increase the time consumed by the initiator by using the inc method. On return from every transaction, the local time offset of the thread checked against the quantum using the need\_sync method. If it is equal to or greater than the quantum, wait is implicitly called and the system simulation time is updated using the sync method.

#### Set up in target

```

1 /* In header file */

2 const sc time LATENCY;

3

4 /* In constructor */

5 Ram::Ram(sc_module_name name, sc_time latency)

: sc_module(name), socket("socket"), LATENCY(latency)

6

7 {

socket.register_b_transport(this, &Ram::b_transport); //

8

Registering callback for incoming interface method call

9 }

10

11 /* Function receiving the transactions from the initiator*/

12 void Ram::b_transport(tlm::tlm_generic_payload & trans, sc_time &

delay)

```

13 {

delay += LATENCY; // Updating the delay with the latency of

the target

The code listing 4.2 above shows how timing is set up in the RAM target, and the same methodology is followed in all the targets. Latency is given in the constructor as an argument while initialising new objects of the target. In the b\_transport method of the target, which is called when it receives transactions from the initiator, this latency is added to the local time offset of the initiator thread calling the target.

It was observed that having a small quantum helps keep the system simulation time more accurate by frequent synchronization but at the same time adds an overhead on the system. This is because when the quantum is small, frequent calls are made to the wait function to synchronize which causes the control to be switched back to the SystemC simulation kernel. This context switch can be expensive in terms of simulation performance. On the other side, having a large quantum reduces the overhead as the synchronization is not as frequent, but the system simulation time might not be as accurate. If the quantum is big, code can execute full speed for a long time without having to stop frequently for SystemC kernel context switch. All the initiators in the simulator have a global quantum of 1us which can be changed and the latency of the targets is configurable.

# 4.3 Benchmarking framework for the application code

The software running on the simulator is written using the LVGL GUI library. The GUI is created using the 30+ widgets present in the library which can be customized and drawn on the screen using the various drawing functions in the library. The LVGL repository has programs to test the drawing of its widgets. 5 widgets were arbitrarily chosen and tested. The total cycles taken to produce these widgets on the display was calculated. The total cycles is the sum of the CPU executing 1 instruction per clock cycle and the cycles consumed by waiting for the read/write transactions to the bus/memory. The total cycles consists of 3 components:

- 1. Cycles taken to render the frame, that is draw the frame in the frame buffer

- 2. Cycles taken to flush the contents of the frame from the frame buffer to the display via the display controller

- 3. Cycles taken to do miscellaneous operations other than the drawing and flushing operations, cycles taken due to the waits in the components, etc

All these 3 components were calculated to understand the breakdown of the total cycles spent in producing the widget on the screen. Out of these three, the cycles taken to render the frame was studied in detail. The aim here is to benchmark the cycles taken to perform various operations by the application code on our simulator, so that the operations which hog the most cycles can be found.

The methodology for setting up a benchmarking framework in the application code is described using the example of one drawing function - drawing an arc. LVGL has various drawing functions, each of these are benchmarked by adding a csr\_write instruction at the entry and exit of the function. CSR is a register in the CPU for storing additional information. A unique value is written to this register both when the function is entered and when it is exited.

Listing 4.3: Code snippet showing adding a csr instruction in an LVGL draw function

The code snippet 4.3 shows a value of 0x0009 written to the CSR when the arc drawing function is entered and a value of 0x0010 is written when the function is

exited (not shown here in the snippet). There are many CSR registers in the CPU and one register having the address CSR\_MCYCLE is used for benchmarking all the drawing functions. Different values are written to this register for identifying if it is the start/end of which function.

Next, the CPU model is modified so that it reacts to these csr\_writes. We can see how the timing implemented in the simulator and explained in the previous section is used in this snippet. qk is the timing thread which holds the timing information and the function get\_current\_time returns the sum of the SystemC simulation time and the local time offset thereby giving the effective local time for accuracy. The cycle time is the time taken by the CPU to process one instruction and it is assumed to be 10ns in our simulator.

```

uint32_t csr_temp;

1

sc_time cycle_time(10, SC_NS);

2

csr_temp = register_bank->getCSR(CSR_MSTATUS); // Read the CSR

4

register

5

6

else if (csr_temp == 0x0009)

{

draw_arc_num+=1;

7

draw_arc_start = qk.get_current_time()/cycle_time;

8

if(lvgl_print) cout << "START arc" << endl;</pre>

9

register_bank->setCSR(CSR_MSTATUS, 0x0); //Reset the CSR

10

register

}

else if (csr_temp == 0x0010) {

draw_arc_total = qk.get_current_time()/cycle_time -

13

draw_arc_start;

draw_arc_sumtotal+= draw_arc_total;

14

if(lvgl_print) cout << "CYCLES arc:" << dec << (int)</pre>

15

draw_arc_total << endl;</pre>

register_bank->setCSR(CSR_MSTATUS, 0x0); //Reset the CSR

16

register

17

}

```

Listing 4.4: Code snippet showing the CPU model reacting to the CSR write instruction