# TFE4930 Electronic Systems Design, Master's Thesis Thesis Report

# Virtual prototype of low-power digital architectures in SystemC

Written by :

Motaz Thiab

Supervisors :

Milica Orlandic

Isael Diaz

June 18, 2020

# Abstract

Nordic Semiconductor is considering to include the use of SystemC virtual prototypes into their System-on-Chip (SoC) design flow. These prototypes would be useful in the development of embedded software. Nowadays, the software team at Nordic semiconductors tests their software in two stages, the first one is the Unit test, It's a set of functional tests of the software, which they run completely on the machine. And the second one is the Target test, They run more complex tests, it tests the communication between peripherals. The tests use one or two development boards, in the case of two devices, One device runs the software under test and the other runs a test program.

Our goal was to investigate the feasibility of using a virtual prototype in the design flow of Nordic Semiconductor. We selected some of the tests used by the software team at Nordic Semiconductor to decide what are the peripherals to be modeled and how detailed these models need to be. We have then modeled and verified the individual components and the overall system. Before running the tests, we had to modify them to be compatible with the SystemC prototype before running them on it. We evaluated the performance of the prototype for the tests and compare it with the performance of the development boards. The results showed that the virtual prototype provided a huge speedup in the testing which we believe would increase the testing productivity and test coverage. The prototype provides more visibility over the system components, allowing for more debugging capabilities. It is also proven to be easily expandable, either expanding the system by adding more models or expanding the individual models by adding extra functionalities.

# Table of Contents

| Ał | ostrac  | t                                                  | i    |

|----|---------|----------------------------------------------------|------|

| Ta | ble of  | Contents                                           | iii  |

| Li | st of T | <b>Fables</b>                                      | vi   |

| Li | st of H | Figures                                            | viii |

| 1  | Intro   | oduction                                           | 1    |

|    | 1.1     | Background                                         | 1    |

|    | 1.2     | Thesis scope                                       | 2    |

|    | 1.3     | Outline                                            | 3    |

| 2  | Theo    | ory                                                | 5    |

|    | 2.1     | Software testing                                   | 5    |

|    | 2.2     | Current testing methodology                        | 6    |

|    |         | 2.2.1 Unit tests                                   | 7    |

|    |         | 2.2.2 Target tests                                 | 8    |

|    | 2.3     | Virtual Prototyping, SystemC and TLM               | 9    |

|    |         | 2.3.1 Virtual prototyping                          | 9    |

|    |         | 2.3.2 Transaction level modeling (TLM) methodology | 10   |

|    |         | 2.3.3 SystemC                                      | 12   |

|    | 2.4     | Multiprotocol Service Layer (MPSL)                 | 17   |

|    | 2.5     | System components and peripherals                  | 18   |

|    |         |                                                    |      |

|   |      | 2.5.1   | Nested Vector Interrupt Controller (NVIC)                        | 18 |

|---|------|---------|------------------------------------------------------------------|----|

|   |      | 2.5.2   | System Control Block (SCB)                                       | 20 |

|   |      | 2.5.3   | СLOCК                                                            | 21 |

|   |      | 2.5.4   | RADIO                                                            | 22 |

|   |      | 2.5.5   | Real-time counter (RTC)                                          | 23 |

|   |      | 2.5.6   | TIMER                                                            | 23 |

|   |      | 2.5.7   | Temperature sensor                                               | 26 |

|   |      | 2.5.8   | General purpose input/output (GPIO)                              | 26 |

|   | 2.6  | System  | n core Bauhaus                                                   | 27 |

| 3 | Met  | hodolog | SY                                                               | 29 |

|   | 3.1  | The in  | itial subset of tests                                            | 30 |

|   | 3.2  | Identif | ying hardware accesses                                           | 31 |

|   | 3.3  | Extrac  | ted peripherals                                                  | 33 |

|   | 3.4  | Model   | ing of peripherals                                               | 34 |

|   |      | 3.4.1   | Nested Vector Interrupt Controller (NVIC) model                  | 35 |

|   |      | 3.4.2   | CLOCK peripheral's model                                         | 36 |

|   |      | 3.4.3   | General purpose input/output (GPIO) module model                 | 44 |

|   | 3.5  | Model   | s verification                                                   | 44 |

|   |      | 3.5.1   | General purpose input/output (GPIO) model behaviour verification | 45 |

|   |      | 3.5.2   | CLOCK model behaviour verification                               | 45 |

|   |      | 3.5.3   | NVIC Verification                                                | 46 |

|   |      | 3.5.4   | System Verification                                              | 48 |

|   | 3.6  | Runnir  | ng tests on the virtual platform                                 | 49 |

|   |      | 3.6.1   | Running the base test                                            | 49 |

|   |      | 3.6.2   | CLOCK peripheral tests                                           | 50 |

| 4 | Resi | ults    |                                                                  | 53 |

|   | 4.1  | Result  | s of Models verification                                         | 53 |

|   |      | 4.1.1   | CLOCK model verification                                         | 53 |

|   |      | 4.1.2   | GPIO model verification                                          | 56 |

|   |      | 4.1.3   | NVIC model verification                                          | 58 |

|    |             | 4.1.4   | System verification                                                    | 60  |

|----|-------------|---------|------------------------------------------------------------------------|-----|

|    | 4.2         | Execut  | ed tests on the platform                                               | 61  |

|    |             | 4.2.1   | Results of the base test                                               | 61  |

|    |             | 4.2.2   | Results of CLOCK's tests                                               | 63  |

|    | 4.3         | Verbos  | ity and visibility                                                     | 64  |

|    | 4.4         | Reusat  | vility and expandability                                               | 65  |

|    | 4.5         | Virtual | prototype vs. development boards                                       | 65  |

| 5  | Disc        | ussion  |                                                                        | 67  |

| 6  | Con         | clusion |                                                                        | 69  |

| A  | Acro        | onyms   |                                                                        | 71  |

| B  | Cod         | e       |                                                                        | 73  |

|    | <b>B</b> .1 | Templa  | te code                                                                | 73  |

|    | B.2         | Nested  | Vector Interrupt Controller (NVIC) model as part of the CPU $\ldots$ . | 75  |

|    | B.3         | CLOC    | K code                                                                 | 79  |

|    | B.4         | GPIO o  | code                                                                   | 101 |

|    | B.5         | Verific | ation tests                                                            | 110 |

|    |             | B.5.1   | NVIC verification tests                                                | 110 |

|    |             | B.5.2   | GPIO verification tests                                                | 113 |

|    |             | B.5.3   | CLOCK verification tests                                               | 117 |

|    |             | B.5.4   | System verification tests                                              | 124 |

|    | B.6         | The ba  | se test code                                                           | 125 |

| Bi | bliogr      | aphy    |                                                                        | 126 |

# List of Tables

| 2.1 | List of used Nested Vector Interrupt Controller (NVIC) registers | 20 |

|-----|------------------------------------------------------------------|----|

| 2.2 | List of used System Control Block (SCB) registers                | 21 |

| 2.3 | List of used registers in RADIO peripheral                       | 23 |

| 2.4 | List of used registers in RTC peripheral                         | 24 |

| 2.5 | List of used registers in timer peripheral                       | 25 |

| 2.6 | List of used registers in temperature sensor peripheral          | 26 |

| 3.1 | immediate functions after <i>mpsl_init</i>                       | 32 |

| 3.2 | NVIC's registers                                                 | 35 |

| 3.3 | List of used Nested Vector Interrupt Controller (NVIC) registers | 35 |

| 3.4 | Registers of the CLOCK model                                     | 37 |

| 3.5 | List of Low Frequency Clock (LFCLK) sources                      | 40 |

| 3.6 | List of General purpose input/output registers                   | 44 |

| 3.7 | General purpose input/output verification conditions and test    | 45 |

| 3.8 | CLOCK verification conditions and test                           | 46 |

| 3.9 | NVIC verification conditions and test                            | 47 |

| 4.1 | Verification results HFCLK controller                            | 54 |

| 4.2 | Verification results LFCLK controller                            | 55 |

| 4.3 | Verification results of LFCLK's oscillator calibration           | 57 |

| 4.4 | General purpose input/output verification results                | 58 |

| 4.5 | NVIC verification results                                        | 60 |

| 4.6 | Comparison table of virtual prototype and development board      | 66 |

# List of Figures

| 2.1  | Unit testing                                                  | 8  |

|------|---------------------------------------------------------------|----|

| 2.2  | Target test                                                   | 9  |

| 2.3  | Model setup to communicate using TLM transaction              | 11 |

| 2.4  | SystemC language architecture                                 | 13 |

| 2.5  | SystemC simulation kernel                                     | 14 |

| 2.6  | Nested Vector Interrupt Controller (NVIC) Block diagram       | 19 |

| 2.7  | clock control block diagram, ©Nordic Semiconductors           | 21 |

| 2.8  | Real-time counter (RTC) block diagram, ©Nordic Semiconductors | 24 |

| 2.9  | The timer block diagram, ©Nordic Semiconductors               | 25 |

| 3.1  | Proposed steps of methodology                                 | 29 |

| 3.2  | <b>mpsl_init</b> functions that access the peripherals        | 32 |

| 3.3  | <b>mpsl_uninit</b> functions that access the peripherals      | 33 |

| 3.4  | The virtual prototype structure                               | 34 |

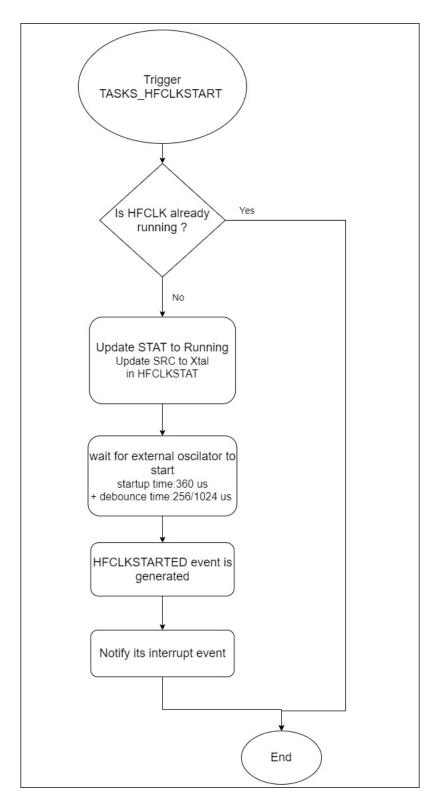

| 3.5  | The steps to start the external high frequency oscillator     | 38 |

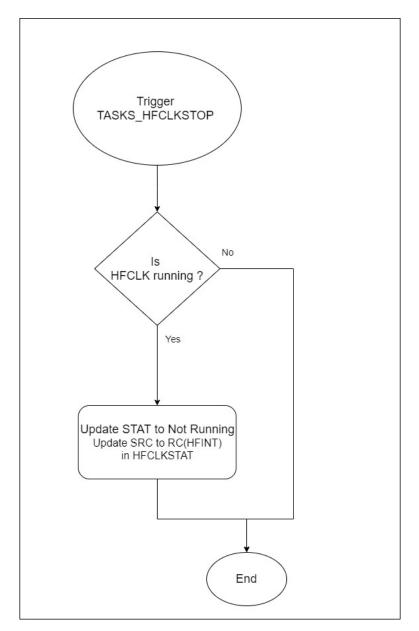

| 3.6  | Steps to stop the external High frequency oscillator          | 39 |

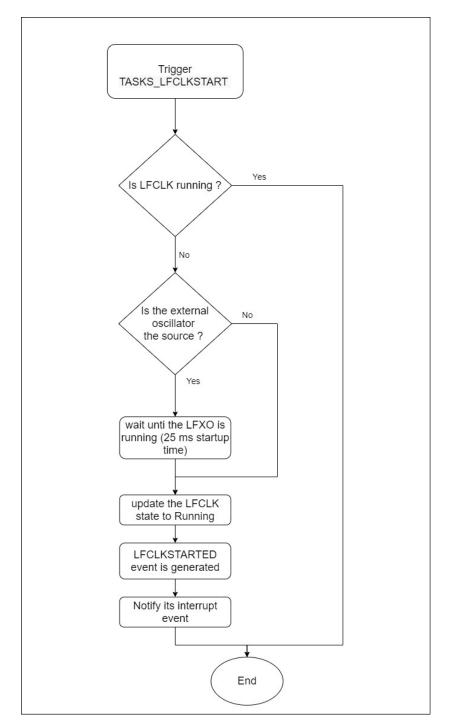

| 3.7  | Steps to start the LFCLK                                      | 41 |

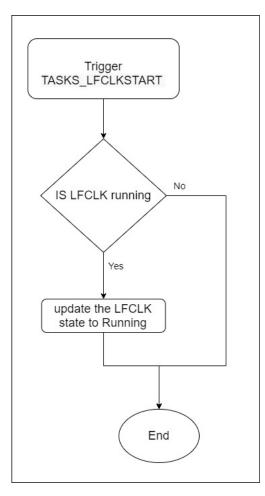

| 3.8  | Steps to stop the LFCLK                                       | 42 |

| 3.9  | Low Frequency Clock (LFCLK) calibration flowchart             | 43 |

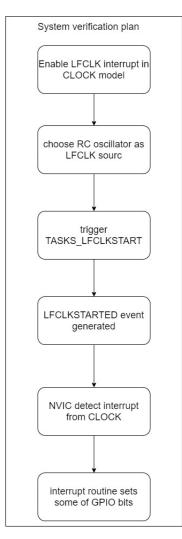

| 3.10 | system verification plan                                      | 48 |

| 4.1  | HFCLK controller start Verification                           | 54 |

| 4.2  | HFCLK controller stop Verification                            | 54 |

|      |                                                               |    |

| 4.3  | LFCLK controller start Verification                                          | 55 |

|------|------------------------------------------------------------------------------|----|

| 4.4  | LFCLK controller stop Verification                                           | 55 |

| 4.5  | external oscillator start Verification                                       | 55 |

| 4.6  | verification of calibration timer operation                                  | 56 |

| 4.7  | verification of calibration process operation                                | 56 |

| 4.8  | verification of GPIO bits individually                                       | 57 |

| 4.9  | verification of GPIO bits cumulatively                                       | 57 |

| 4.10 | <i>EnableIRQ</i> function verification                                       | 58 |

| 4.11 | DisableIRQ function verification                                             | 58 |

| 4.12 | ClearPendingIRQ function verification                                        | 59 |

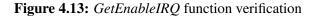

| 4.13 | GetEnableIRQ function verification                                           | 59 |

| 4.14 | GetPendingIRQ function verification                                          | 59 |

| 4.15 | system verification results                                                  | 60 |

| 4.16 | The results of the initialization routine                                    | 61 |

| 4.17 | The results of the base test                                                 | 62 |

| 4.18 | The results of One-shot CLOCK callback test                                  | 63 |

| 4.19 | The results of No CLOCK callback is called when HFCLK started by protocol    |    |

|      | test                                                                         | 63 |

| 4.20 | The results of CLOCK callback is called when HFCLK is already triggered test | 64 |

L Chapter

# Introduction

### 1.1 Background

In System-on-Chip (SoC) development, both software and hardware need to be developed, where the hardware will interface with the external environment like peripherals and sensors. The software provides the interfaces between high-level software and the hardware components of the chip, which makes the software development an essential part of the hardware design. Software content on System-on-Chip (SoC) comprises low-level firmware or telecom/communication stacks, and these need to be tested and validated.

Here we are interested in the software testing of Nordic Semiconductor, where their software team relies on two types of software testing, unit tests, and target tests.

The issue that we are interested in is the productivity of testing, and we going to focus on the second stage of testing used by Nordic Semiconductor, target test. One of the target test drawbacks is its dependency on development boards. And in the early stages of SoC design flow, they will not be available which will force the delay of the SoC testing until the board design is finished and the board itself has been manufactured. A workaround to reduce the waiting time for development boards is the use of FPGAs. The FPGA can be configured to behave similarly as the under-development board. Even though the use of FPGAs will save the waiting issue it would add extra cost to the product development which is proportional to the number and type of used FPGAs.

Another issue target tests are suffering from is the time need to execute the tests. The number of tests that need to be run to cover a specific system increases with system complexity. And having a complex system with different peripherals requires extensive software testing. With a massive number of cases and states to be tested, the testing time will increase drastically. This could force the developers to decrease the number of tests and focus on the corner cases to stay within a reasonable testing time.

An approach to reduce this effect is the use of virtual prototypes. A virtual prototype is a hardware-mimicking software that can run its software. The main principle of virtual prototypes is to have a trade-off between accuracy and simulation speed. It would provide a functional simulation while abstracting some of the unnecessary details to increase the simulation speed. Transaction level modeling (TLM) is one of the methodologies used to abstract the communication details between different system components. Its principle is to have an object of the payload that we would like to send from the initiator to a target, and instead of passing the whole object, the initiator would pass a pointer to that object. SystemC is one of the virtual prototyping languages that also use TLM methodology to transmit transactions between different system's components.

### **1.2** Thesis scope

This thesis is working with another one [1] to address the previously mentioned issue where we gonna be working on different parts of the same system, and the results for both theses will be based on the complete system which will be the combination of our work. We will try to answer on the following questing:

Does the use of SystemC virtual prototypes in the design flow of Nordic Semiconductor provide a good testing platform for their software? and whether it can replace the physical boards in software development?

We will be trying to develop a virtual prototype to run and evaluate the performance of these tests. The prototype will use some of the components that are already available and used by Nordic Semiconductor like a simple CPU that initiates simple read and write transactions, interconnect between the CPU and the rest of the models, and a system builder to connect different models into a single complete system. Our focus will be on the modeling of the peripherals and some CPU components like Nested Vector Interrupt Controller (NVIC) and System Control Block (SCB). We will also evaluate the performance of the prototype and

compare it with the tests' performance on the development boards.

## 1.3 Outline

The thesis consists of 6 chapters including the introduction, acronyms appendix, and appendix for some of the code mentioned through the thesis. Chapter 2 is the theory chapter and it discusses software testing in general then it narrows down to the testing methodology used at Nordic Semiconductor. It will also talk a bit about the software that we are going to test. Then it moves to talk about the hardware components that will be modeled either in this thesis or in [1]. We will also discuss SystemC as the used modeling language and explain some of its concepts and components, in addition to the in-house components that we have used from Nordic Semiconductor.

Chapter 3 will list the methodology and the steps taken through the thesis. It will start by discussing the selection of the initial subset of tests and the identifying of the hardware accesses performed by that subset of tests. It will also move to peripherals that are going to be modeled followed by their modeling and verification plans. Finally, it will discuss the modification of tests to be compatible with the prototype.

Chapter 4 will have the results of the verification plans and the results of executing the tests. It will also mention some of the features the prototype has like visibility and expandability. It will finish by listing a comparison between the virtual prototype and the development boards for different tests.

Chapter 5 will discuss the results and findings of the thesis and comment on them, and try to answer the thesis question. While chapter 6 will summarize the work, findings, and conclusion of the research.

# Chapter

# Theory

## 2.1 Software testing

The correctness of embedded software functionality and performance plays a big role in software quality. Software testing is an important asset of software quality assurance[7]. The embedded software testing stretches across the software and the hardware. It deals with the software and hardware issues, as well as their coordination [11].

There are several embedded development models that deal with different stages of development including the writing and testing of software. They are different level of testing that can be applied to embedded systems. We will discuss two of them here which are relevant to this thesis. The two types of embedded software testing are:

• Software unit testing:

It tests a function or a class from the software, a single unit of the software. The test cases are developed based on the specification, and it tests the logic of the software.

• Software/hardware integration testing:

It could also be referred to as target testing. It focuses on testing the interaction between the software within hardware components. It tests the integrity of communication between different parts of the software. It usually requires the use of physical boards, either development boards of the target hardware or configured FPGAs.

The main goal of all types of testing is to discover design bugs and errors at earlier stages of development. The later the bugs are being detected the higher the cost and the delay of fixing them. The delay caused by discovering a bug depends on if we have to go back to previous stages of the design flow to fix it or how many stages we would have to revisit. The further we have to roll back in the design flow the more time and cost are needed.

The testing gets more complicated when moving to target testing as the target hardware of the software might not be available at this point in the design flow. As the software is tightly coupled with the hardware in an embedded system, this could be a bottleneck of the design flow. There are different ways to deal with this issue, either by delaying the software development until the target hardware is available, but the product development time would increase. Another solution is the use of configured FPGAs, that behaves similarly to the target hardware. This would overcome the bottleneck and save time in the development, but it would add extra costs to the development due to the high cost of FPGAs. A more recent approach is the use of virtual prototypes, which promises to allow for early testing at a cost cheaper than the use of FPGAs. This would be the focus of this thesis and will be discussed more in details later on in this chapter.

So to recap, all models aim to develop a design that fits the requirements and specifications as soon as possible while trying to minimize the development cost. Having the right testing solution for a certain product will increase the testing productivity. If the testing productivity increased this will lead to better test coverage or shorter software development time, which both can be translated to saved development costs. That might impact the final product in two major ways, first is being able to publish the product earlier to the market, in other words, it shortens the time-to-market (TTM). Second, is with lower development costs for the product there is the potential to have the product available for customers at a competitive price or increase the profit margin.

### 2.2 Current testing methodology

This thesis is building on the current testing approach at Nordic Semiconductor to try and provide a proof-of-concept for a potentially improved approach with increased testing productivity. Nordic Semiconductor design its own System-on-Chip (SoC), the Hardware access layer (HAL) to access it and its software.

And this part will present the software testing approach used at Nordic Semiconductor in their design flow. Their testing methodology consists of two stages, unit tests, and target tests.

#### 2.2.1 Unit tests

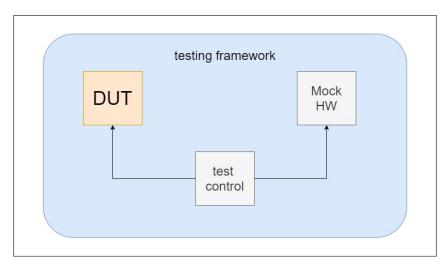

Unit tests testing is an early stage of testing, that tests the software logic. It tests that individual pieces of code software are functioning correctly, separate from other software components. The unit tests are run on a machine, with a simple mock hardware file to mimic the existence of hardware. Mock hardware is a C code that has a dummy definition for some of the functions called in the tested software. The testing framework of unit tests is illustrated in 2.1. The unit testing framework consists of three main elements:

1. DUT (device under test) :

Even though it is called the device-under-test it refers to the software to be tested. It represents the newly developed software that needs to be tested before further development. The DUT is being tested by checking the correctness of its functions' implementations. Its access to correct peripherals' registers in the correct order is also being covered in unit testing.

2. Mock hardware:

This is a simplified virtual platform usually a single C file. it is a functional model to perform simple tests written in C. Each test has its own mock hardware to cover the function calls needed by each test.

3. Test control:

It is a C file contains the definition of multiple tests that will be performed on a piece of the software. It initializes both mock hardware and the software. It returns the results of all tests indicating which tests have passed and which has not. It uses a unit test testing framework for C to define the tests and run them. The test control will return the results of the tests if they pass or fail.

Figure 2.1: Unit testing

#### 2.2.2 Target tests

This is a later stage of testing, which tests the communication between different peripherals and different parts of the system. It uses development boards to flash and run the tests. The test setup consists of two boards, one is loaded with the compiled software to be tested and the other contains the tester software as shown in figure 2.2. Both boards communicate via radio channel if the test requires. The test control block for figure 2.2 represents a machine, where both boards are connected to a machine during the testing. The machine runs the tests which include flashing both boards with tests code and logging the test steps and results.

Figure 2.2: Target test

# 2.3 Virtual Prototyping, SystemC and TLM

This section will discuss the approach and the literature behind the methodology that will be used in this thesis. The topics that will be presented are wide and has extensive material describing all different aspects of them, but here we will introduce them and focus on the components and parts which are relevant to this work.

### 2.3.1 Virtual prototyping

In a general definition virtual prototype is an executable software that models a hardware system that runs on a host computer. A virtual prototype is binary compatible, meaning it can run unmodified binary images of entire software stacks. It abstracts away levels of hardware details essential to hardware developer but not relevant to a software developer, where it can be used similar to development boards by a software developer to load, execute and debug.

This abstraction allows the virtual prototype to run the simulation at higher performance compared to other hardware-oriented emulation. Virtual prototypes can be modeled to simulate part of the software stack, and continuously extend the virtual prototype along with software development.

It shows that virtual prototyping allows software development to start earlier concurrently with hardware. Software/Hardware integration becomes easier using a virtual prototype instead of using FPGAs or development boards from a software developer perspective. The ultimate goal from the previously mentioned features that virtual prototypes provided is to reduce development time and effort, and subsequently, it could lower the development cost[4].

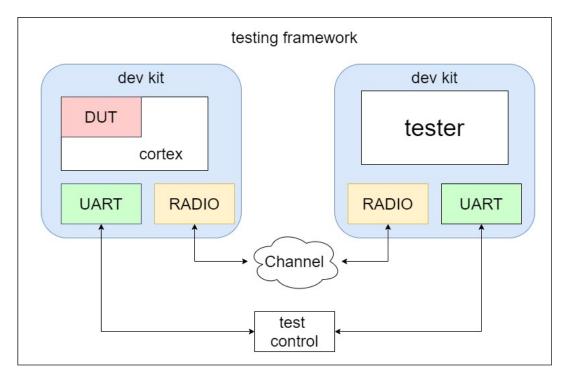

#### 2.3.2 Transaction level modeling (TLM) methodology

Transaction level modeling (TLM) is a transaction-based modeling approach founded on high-level programming languages such as SystemC. It highlights the concept of separating communication from computation within a system. It is also used as a set of standards like TLM2.0, which ensures interoperability between different TLM compliant models. TLM compliant models referrers to the models that use the abstraction provided by TLM approach.

In TLM approach, the components of a system are modeled as modules, with concurrent processes to represent their behavior and functionalities. The modules exchange communication through interfaces, where processes can access these interfaces through module sockets. The communication exchanged is in the form of transactions, which is passed through channels. Channels are used by TLM to encapsulate communication protocol by implementing interfaces within channels. [3].

Various communication protocols can be defined on top of the core TLM interface layer. These protocols rely fully on the core TLM interface to transfer a transaction between two different points (modules) in a system.

The transfers of TLM are refined by these protocols in terms of transaction payload and blocking/non-blocking transfer[5]. The following Figure 2.3 shows how payload objects transferred as a transaction through the sockets of the modules from initiator socket to target socket. It also shows a typical TLM communication setup which consists of:

• An initiator component: it is a module that initiates (constructs and send) new transactions.

- A target component: it is the target module of transactions that acts as the endpoint of the transaction. It is responsible for executing requests from the initiator and send responses.

- An interconnect component: It forwards and routes transaction objects between initiator and target.

References to the object are passed along the forward path from the initiator socket to the target socket, and the responses are passed through return path form target sockets to initiator sockets.

Figure 2.3: Model setup to communicate using TLM transaction

TLM models have different coding styles depending on the timing-to-data dependency that they must obey:

• Loosely-timed models:

These models have a loose dependency between timing and data. They can provide timing information and the requested data at the point when a transaction is being initiated. These models prioritize the speed of the simulation, and so they are particularly useful for doing software development on a Virtual Platform. The processes in this style of TLM can run ahead of simulation time (temporal decoupling). Transactions completes in one blocking function call.

• Approximately-timed models:

These models have a much stronger dependency between timing and data. They are not able to provide timing information and/or the requested data when a transaction is being initiated. they are forced to trigger multiple context switches in the simulation, resulting in performance penalties. It is sufficient for architectural hardware design space exploration, since it introduced more details than the previous style.

Processes run in locksetp with simulation time and cannot run ahead of it, unlike the previous style. Transactions in this style have usually four timing points and non-blocking behaviour.

The TLM coding style that will be used is loosely-timed since the focus is to enhance software testing. And therefore the transactions will all be blocking transactions.

#### 2.3.3 SystemC

There are different virtual prototyping languages, and here the focus is on *SystemC*. SystemC addresses the modeling of both hardware and software using C++ as it is not a separate language, but rather a set of classes and macros in a C++ library that supports hardware modeling. SystemC provides several hardware-oriented constructs that are not normally available in a software language like modeling concurrency, synchronization, inter-process communication and simulation kernel (scheduler) and figure 2.4 shows some of the elements used to do so. These constructs are essential for simulating hardware behaviour[2].

And here we will discuss the some of SystemC components from figure 2.4, and provide an overview of them.

#### **Modules and Hierarchy**

Large designs are mostly broken down hierarchically to manage the design complexity and ease the understanding of the design. SystemC provide constructs to implement hardware hierarchy. Some of these constructs is module entity. Modules are classes that inherit from the *sc\_module* base class. They encapsulate design component and they may contains other modules, processes and channels and ports for connectivity. Instantiating these module classes in other modules creates the system hierarchy.

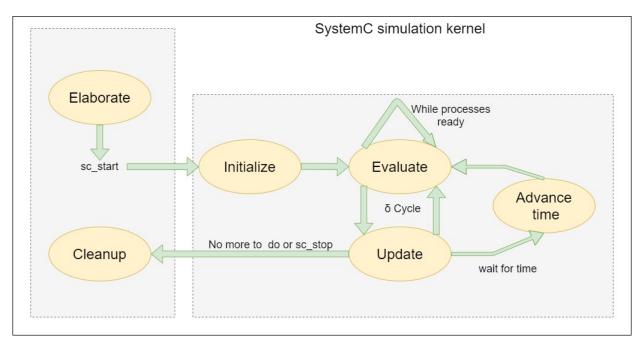

#### SystemC simulation kernel

SystemC simulation kernel consists of 6 phases, that govern the behaviour of the models and

| Simulation | Methods<br>& Threads                  | Channels<br>& Interfaces | Data Types:                                         |

|------------|---------------------------------------|--------------------------|-----------------------------------------------------|

| Kernel     | Events, Sensitivity<br>& Notification | Modules<br>& Hierarchy   | Logic, Integers,<br>Fixed point &<br>Floating point |

|            | C+                                    | +                        |                                                     |

Figure 2.4: SystemC language architecture

simulate their execution concurrency. Figure 2.5 shows the phases of systemC simulation kernel.

1. Elaboration phase:

This phase referrers to the execution of all states prior to the  $sc\_start()$  call. All  $SC\_MODULES$  are called during this phase and the connection between modules is checked, and if there a port which is not bound the simulation will complain about it at the beginning.

2. Initialization phase:

During this phase, all processes are invoked in unspecific deterministic. Methods are executed once while threads will be executed if its synchronization point is reached(i.e. *wait()*).

3. Evaluation phase:

SystemC simulator implements a cooperative multitasking environment where processes keep executing until they yield control At this phase, all processes marked as executable are executed successively an in undefined order, and their marking is removed. Methods are executed until they return, while threads get suspended by *wait()*. During their execution processes cannot be interrupted. Some of the processes might generate

Figure 2.5: SystemC simulation kernel

"update request" by writing to *sc\_signal* or *sc\_fifio* etc. These requests are created for assignments to be made in the update phase. Furthermore, the execution of a *wait()* may result in a "timeout". This means that this process should be continued at a later time and they are stored in the event queue.

4. Update phase:

In this phase the previously requested updates are performed. And the simulator estimates if any of the process are sensitive to the updates of these signals and if so marks them as executable. The scheduler goes back to evaluation phase to execute the processes marked as executable which might generate new update requests. The loop between the evaluation and the update phases is called delta cycle. This loop keeps going until there are no update requests left and no processes to execute.

5. Advance time phase:

In this stage the simulation time is advanced to to time of events in the event queue with the smallest time. The processes sensitive to these events are marked as executable and the scheduler proceeds to the evaluation phase.

6. cleanup phase:

If there are no events left in the event queue or if sc\_stop() is called, the scheduler

proceeds to the cleanup phase. In the cleanup phase all destructors are called and the simulation is over.

#### SystemC Threads and Methods

The systemC simulation kernel schedules the executions of all simulation processes. Simulation processes are member functions of  $sc_module$  class that is registered with the simulation kernel during the elaboration phase. There are two ways of representing processes in systemC modules, Methods, and Threads. They register with the simulation kernel using  $SC_METHOD$  or  $SC_THREAD$  SystemC macro. Methods are similar to VHDL's process, and they can be invoked as often as needed. Methods are being executed atomically with no preemption, therefore, infinite loops must be avoided. Methods are usually sensitive to signals and events in the sensitivity list, and they do not take arguments and return no value.

While threads are started once at begin of the simulation and die when the end of its scope is reached, and for that, they can be suspended using *wait()* statements to wait for an event to be notified. Threads are recommended to have infinite loops to prevent the thread from reaching the end of its scope.

Both methods and threads are the basic blocks to simulate concurrency of execution. They are invoked by the simulation kernel, where the user has indirect control over which and when a process is invoked through events, notifications, and sensitivity.

#### **Events, Sensitivity, and Notification**

Events, sensitivity, and notification are essential for the simulation of concurrency in SystemC models. Events are implemented with the SystemC *sc\_event* and *sc\_event\_queue* like shown.

```

1 //creating event that can be notified once during evaluation phase.

2 sc_event myEvent;

3 // create an event that could be notified multiple times during the

evaluation phase.

4 sc_event_queue myEvent_queue;

```

Events are caused or notified through the event member function *notify*. The notification can occur within a simulation process or as a result of activity in a channel. Events are notified during evaluation phase of SystemC kernel but the effect of the notification could occur at the immediately at the current evaluation phase or it could be time stamped to be notified at a point

in the future as shown below.

```

void triggerProcess() {

//notify the event at next update phase

myEvent.notify();

//notify the event after 10 ns from current time

myEvent.notify(10,SC_NS);

}

```

The difference between *sc\_event* and *sc\_event\_queue* rises when the same event is notified multiple times at evaluation phase. In the case of *sc\_event* only the first notification will be registered and all the following ones will be ignored, so in the example shown before the second notification will not be executed. While for *sc\_event\_queue* all the notifications will be stored and executed at their perspective times. There are two types of sensitivities, static and dynamic. Static sensitivities are specified in the constructor of the model at the elaboration phase for both methods and threads, and cannot be changed. While dynamic sensitivities allow the simulation process to change their sensitivity by calling different functions with the process. function *wait(myEvent)* is used for threads' dynamic sensitivity, and *next\_triger(myEvent)* for methods' dynamic sensitivity.

#### SystemC Data Types

Digital hardware requires data types which are not provided inside the natural boundaries of C++ native data types. SystemC provides hardware-compatible data types that support explicit bit width for both integral and fixed-point. Non-binary hardware types are supported with four-state logic (0,1,X(unknown),Z(high impedance)) data types (e.g.,  $sc_logic$ ). Familiar data types like  $sc_logic$  and  $sc_lv < T >$  are provided for RTL hardware designers who need a data type to represent basic logic values or vectors of logic values. SystemC also allows the user to define new hardware types for new hardware technology.

#### **Ports, Interfaces, and Channels**

processes need to communicate with other processes both locally and in other modules. Processes communicate locally using events or channels. processes can also communicate across the boundaries of modules which may interconnect with other modules using channels. Channels are used to separate communication from functionality and they act as a container of communication protocols and synchronization events. SystemC provides several built-in channels common to hardware and software design. They include locking mechanisms and hardware concepts like FIFOs, signals, and others. The ability to have interchangeable channels is implemented through a component called interface. An interface is defined as a set of pure virtual functions which is used as a base class. While channels provide the implementation of one or more interface(s).

### 2.4 Multiprotocol Service Layer (MPSL)

As this work is trying to improve the testing methodology used at Nordic Semiconductor, it uses Multiprotocol Service Layer (MPSL). It is a library that provides access to the peripherals of Real-time counter (RTC)0, TIMER0, CLOCK, and Temperature sensor. It allows higher-level software to communicate with the peripherals using MPSL functions.

The target tests of the MPSL runs test for different peripherals and different functionalities of the library. All different target tests have a similar structure. Each test calls the initialization routine *mpsl\_init* and the beginning of the test. And an un-initialization *mpsl\_uninit* routine is called when hardware accesses for the test are done. The function *mpsl\_init* initializes the peripherals, configures some of their registers, and resets the interrupt lines (clear pending requests and disable them). While the function *mpsl\_uninit* would stop some of the peripherals like CLOCK and resets others like the temperature sensor and the radio.

The following shows how MPSL tests are structured.

```

void mpsl_test(void){ //The test main function

//initializing the mpsl library

mpsl_init(&mpsl_clock_config,MPSL_TEST_IRQn, mpsl_assert_handler);

//*

*The body of the test

*all the function calls to mpsl library function happen here

*/

//uninitializing the mpsl library

```

```

12 mpsl_uninit();

13

14 /*

15 *you can assert some values here,

16 *but not use any of the mpsl library functions

17 */

18 }

```

### **2.5** System components and peripherals

This section is discussing and explaining the behavior and functionalities of the components that we will base the models on. It includes the peripherals used by the tests and some CPU components. We will discuss the peripherals and components within the scope of this thesis since their description can get a bit complex and lengthy. So not all registers or functionalities of each peripheral will be explained, it will be limited to the functionalities and registers used by the selected tests.

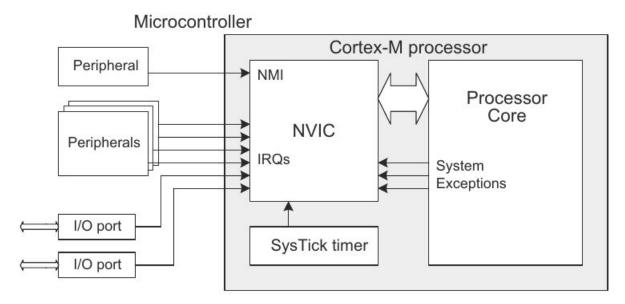

#### 2.5.1 Nested Vector Interrupt Controller (NVIC)

It is part of the CPU, and it controls the incoming interrupt requests from peripherals to the CPU. Interrupts are used as a way to divert the CPU from its current task to another task with a higher priority. The CPU can be triggered internally from the processor and it is called exceptions, or externally by external peripherals, and it is called interrupts. NVIC uses interrupt vectors to determine which service routine should be executed for a specific interrupt request. Each vector holds the address of interrupt handler function to a specific interrupt request. Interrupt vectors are arranged in interrupt vector tables. Interrupts have different priorities, which decide which interrupt service routine should be performed in case of multiple interrupt requests at the same time.

In ARM Cortex-M CPUs which are used in Nordic Semiconductor's System-on-Chip (SoC), the CPU receive the interrupt requests via Nested Vector Interrupt Controller (NVIC) as shown in figure 2.6. The Nested Vector Interrupt Controller (NVIC) manages and prioritizes the external interrupts, where it can be used to enable or disable interrupt request lines. Some interrupt lines cannot be masked out(disable), they are referred to as Non-maskable interrupts

(NMI). NVIC interrupts the CPU with the highest priority interrupt request and the CPU stops the currently executing process and uses the interrupt request number to access the vector table and get the interrupt handler to start address for this specific request, which the CPU starts executing.

Figure 2.6: Nested Vector Interrupt Controller (NVIC) Block diagram

The Nested Vector Interrupt Controller (NVIC) consists of the multiple registers, but for the scope of the thesis we will limit the discussion to the ones used for the modeling, which are the following registers:

• Interrupt Set Enable Register (ISER):

The bits in ISER correspond to different Interrupt request line (IRQ). The value of each bit decides if the corresponding IRQ is enabled or not in the NVIC. Setting any of the bits in ISER enables the interrupt of the corresponding IRQ, while clearing it does not affect the status of IRQ.

• Interrupt Clear Enable Register (ICER):

ICER is similar to ISER that each bit corresponds to an IRQ. However, it differ in the functionality, where setting a bit in ICER would disable the corresponding IRQ, and its interrupt requests will not interrupt the execution of the CPU. Clearing bits in ICER has no effect of the IRQ.

| Function             | Description                       |

|----------------------|-----------------------------------|

| NVIC_DisableIRQ      | Enable interrupts                 |

| NVIC_EnableIRQ       | Disable interrupts                |

| NVIC_ClearPendingIRQ | Clears the status of IRQ pending  |

| NVIC_GetEnableIRQ    | Returns if IRQ is enabele or not  |

| NVIC_GetPendingIRQ   | Returns the status of IRQ pending |

| NVIC_SetPriority     | Sets the priority of IRQ          |

Table 2.1: List of used Nested Vector Interrupt Controller (NVIC) registers

• Interrupt Set Pending Register (ISPR):

ISPR is modified by the NVIC, where the the NVIC would set a bit if its corresponding IRQ has a pending interrupt request waiting for a process with higher priority to be over.

• Interrupt Clear Pending Register (ICPR):

This register is a complement to ISPR, where ICPR is used to flag the IRQs which its pending requests have been cleared. If a bit is set, it means that its corresponding IRQ is no longer pending an interrupt request.

• Interrupt Priority Register (IPR):

This register used to configure the priority of different IRQs. This register, unlike the ones before, takes an integer value to represent the priority of interrupt requests. The IRQ with lower integer value is the one with the highest priority and vice versa.

The table 3.3 lists the NVIC functions that are needed by the tested software. These functions operate on the NVIC registers mentioned earlier. All functions take IRQ as a sole argument expect *NVIC\_SetPriority* which takes additionally the priority value of associated IRQ.

#### 2.5.2 System Control Block (SCB)

SCB is also another component of the CPU similar to NVIC. It provides system implementation information and system control. This includes configuration, control, and reporting of the system exceptions. And it has different registers to store this information or to be configured, but here we will limit the discussion to the ones which are used by the tests. For the tests that we ran, there is a need for two register from System Control Block's registers, System Control Register (SCR) and System Handler Priprity Register (SHP) as shown in table

| Register | Function                         |

|----------|----------------------------------|

| SCR      | System Control Register          |

| SHP      | System Handler Priprity Register |

Table 2.2: List of used System Control Block (SCB) registers

2.2. *SCR* controls features of entry and exit from low power state. While *SHP* is used to configure the priority of system interrupts (exceptions).

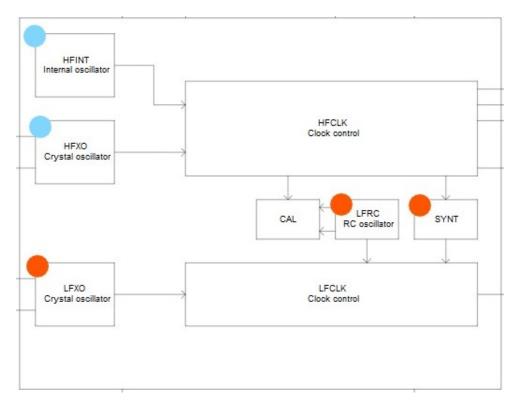

### 2.5.3 CLOCK

The clock control system can provide the system clocks from a range of high and low frequencies from internal or external oscillators. It also distributes different clocks to different modules based on the individual module's needs. Clock distribution is automated and grouped independently by modules to limit current consumption in unused branches of the clock tree [9].

Figure 2.7 shows the internal and external oscillators of the clock control of both High Frequency Clock (HFCLK) and Low Frequency Clock (LFCLK) controllers. The blue marked blocks are the sources of HFCLK. while the orange ones for the LFCLK.

Figure 2.7: clock control block diagram, ©Nordic Semiconductors

The High Frequency Clock (HFCLK) controller provides the high-frequency clocks when requested otherwise it enters power-saving mode. It can provide the following frequencies:

- 64 MHz CPU clock.

- 1 MHz peripheral clock.

- 16 MHz peripheral clock.

- 32 MHz peripheral clock.

On the other hand, Low Frequency Clock (LFCLK) controller can provide only a CLOCK of 32.768 KHz. It can generate this frequency from the supported following sources(marked in orange in figure 2.7):

- 32.768 KHz RC oscillator .

- 32.768 kHz crystal oscillator.

- 32.768 kHz synthesized from High Frequency Clock (HFCLK).

The RC oscillator is the default source of LFCLK. The RC oscillator can be calibrated since its frequency will be affected by variation in temperature. The High Frequency Clock (HFCLK) oscillator is used as a reference to calibrate the RC oscillator. A calibration timer is used to time the calibration interval of the 32.768 kHz RC oscillator, where the block *CAL* in figure 2.7 is responsible for the calibration process of the RC oscillator.

#### 2.5.4 RADIO

The RADIO contains a 2.4 GHz radio receiver and a 2.4 GHz radio transmitter that is compatible with Nordic's proprietary 1 Mbps and 2 Mbps radio modes in addition to 1 Mbps and 2 Mbps Bluetooth® low energy mode. For the tests we are planning to run, they will not use the RADIO peripheral, but it is still part of the initialization routine. The register that is used from the CLOCK peripheral in the initialization routine is the power register to power up and shut off the peripheral.

| Register         | Function                 |

|------------------|--------------------------|

| NRF_RADIO->POWER | Peripheral power control |

Table 2.3: List of used registers in RADIO peripheral

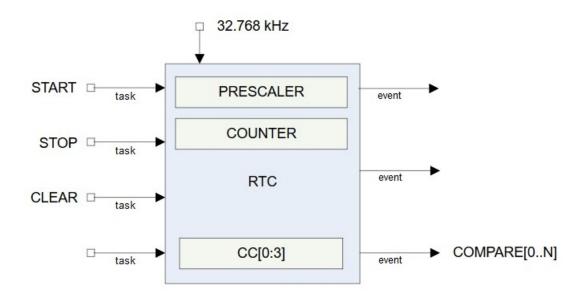

#### 2.5.5 Real-time counter (RTC)

The RTC peripheral features a 24-bit COUNTER, a 12-bit (1/X) Prescaler, capture/compare registers, and a tick event generator for low power, tickless RTOS implementation. the RTC runs off 32.768 kHz of Low Frequency Clock (LFCLK) [10]. The value of the counter's *PRESCALER* register decides the overflow time value and the counter frequency (resolution) based on the following equation:

$$f_{RTC}[KHz] = \frac{32.768}{(PRESCALER+1)}$$

For example, if the desired frequency is 100Hz (100ms counter period) then the *PRESCALER* register value will be as follow:

$$PRESCALER = (\frac{32.768kHz}{100Hz}) - 1 = 327$$

The RTC contains four compare registers CC[0] - CC[3], these registers are configured with the counter values at which the RTC would trigger match event. When the *COUNTER* register value transitions from M-1 to M and one of the compare registers has the value M, an event for the corresponding compare register will be triggered. When a match event is triggered the corresponding *EVENT\_COMPARE[i]* register value will be set to 1.

The figure 2.8 shows the block diagram of Real-time counter (RTC). And table 2.4 lists names and descriptions of the registers used by selected tests.

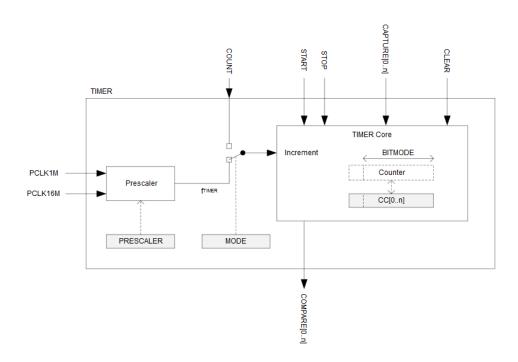

#### 2.5.6 **TIMER**

The TIMER runs on the High Frequency Clock and it contains a four-bit (1/2X) Prescaler to divide the timer input clock from the HFCLK controller.

It operates in two modes Timer mode and Counter mode as shown in figure 2.9. In both modes, the timer starts by triggering the *START* task and stops by triggering the *STOP* task. Counting/timing can be resumed if it has been stopped by triggering *START* task again, and it

Figure 2.8: Real-time counter (RTC) block diagram, ©Nordic Semiconductors

| Register                    | Function                              |

|-----------------------------|---------------------------------------|

| NRF_RTC0->TASKS_START       | Start RTC COUNTER                     |

| NRF_RTC0->TASKS_STOP        | Stop RTC COUNTER                      |

| NRF_RTC0->TASKS_CLEAR       | Clear RTC COUNTER                     |

| NRF_RTC0->CC[ <i>i</i> ]    | Capture/Compare register <i>i</i>     |

| NRF_RTC0->EVENTS_COMPARE[i] | Compare event on CC[ <i>i</i> ] match |

| NRF_RTC0->INTENCLR          | Disable interrupt                     |

| NRF_RTC0->EVENTCLR          | Disable event routing                 |

| NRF_RTC0->EVENTSET          | Enable event routing                  |

| NRF_RTC0->COUNTER           | Current COUNTER value                 |

Table 2.4: List of used registers in RTC peripheral

continues from the prior value it had before stopping.

During timer's mode, the TIMER internal register is incremented by 1 for each tick of the timer frequency. The timer frequency is derived from 16 MHz peripheral clock (PCLK16M) using the value specified in *PRESCALER* register according to the following equation:

$$f_{TIMER} = \frac{16MHz}{(2^{PRESCALER})}$$

. If  $f_{TIMER}$  is less than 1 MHz the timer will use 1 MHz peripheral clock (PCLK1M) instead of 16 MHz peripheral clock (PCLK16M). During the timer's mode, the *COUNTER* register is not used. On the other hand, in counter mode, the TIMER's internal register increments its value each time the COUNTER task is triggered. The timer's frequency and the timer prescaler are

not used in counter mode.

The timer can generate *COMPARE* events. One *COMPARE* event is generated for each capture/compare register. The *COMPARE* event is triggered when the *COUNTER* register's value reaches a value similar to one of the *capture/compare* (*CC[i]*) registers.

Figure 2.9: The timer block diagram, ©Nordic Semiconductors

| Register                      | Function                              |

|-------------------------------|---------------------------------------|

| NRF_TIMER0->TASKS_START       | Start Timer                           |

| NRF_TIMER0->TASKS_STOP        | Stop Timer                            |

| NRF_TIMER0->TASKS_SHUTDOWN    | Shut down timer                       |

| NRF_TIMER0->INTENSET          | Enable interrupt                      |

| NRF_TIMER0->INTENCLR          | Disable interrupt                     |

| NRF_TIMER0->CC[i]             | Capture/Compare register <i>i</i>     |

| NRF_TIMER0->EVENTS_COMPARE[i] | Compare event on CC[ <i>i</i> ] match |

Table 2.5: List of used registers in timer peripheral

## 2.5.7 Temperature sensor

The temperature sensor measures the die temperature over the temperature range of the device. It has a resolution of 0.25 degrees. The temperature measurements triggered by the *START* task, and a *DATARDY* event is generated when the measurement is done and the result can be read from *TEMP* register. Temperature measurement supports the only one-shot operation and it powers down after measurement is completed to save power.

The temperature measurement does not start automatically and has to be explicitly started using *START* task. The table 2.6 lists the registers of temperature sensor which are used by selected tests.

| Register                 | Function                                     |

|--------------------------|----------------------------------------------|

| NRF_TEMP->TASKS_START    | Start temperature measurement                |

| NRF_TEMP->TASKS_STOP     | Stop temperature measurement                 |

| NRF_TEMP->EVENTS_DATARDY | Temperature measurement complete, data ready |

| NRF_TEMP->INTENSET       | Enable interrupt                             |

| NRF_TEMP->INTENCLR       | Disable interrupt                            |

| NRF_TEMP->TEMP           | Temperature in °C (0.25° steps)              |

Table 2.6: List of used registers in temperature sensor peripheral

# 2.5.8 General purpose input/output (GPIO)

The General purpose input/output has multiple ports with each port having 32 pins. The use of this module in our test is very limited. It is mainly used to set or clear some of the GPIO pins. The functionalities of the GPIO can be performed at a bit level, setting and clearing individual bits, where each bit in the GPIO registers corresponds to a pin of the port. Table **??** lists the registers used by the selected tests.

The register *OUTSET* of the GPIO sets the values of the pins based on their corresponding bits, if the bit is set then its corresponding bit in register *OUT* is also set. While if the bits are set in register *OUTCLR* then the corresponding bit in register *OUT* is cleared.

And the values of *OUT* register corresponds to the output of the port's pins, where the pin's value is HIGH if its corresponding pin in *OUT* register is set and it is LOW if it is cleared.

# 2.6 System core Bauhaus

The work of this thesis will focus mainly on modeling the peripherals for the system. Our system will be built on existing models at Nordic Semiconductor called Bauhaus. Bauhaus is a proof-of-concept and experimentation testbench for virtual modeling with SystemC used by Nordic Semiconductor [8].

It provides a simple CPU that initiate blocking read and write transactions to system components. It also provides system builder functionality to easily add new modules to the system with their base addresses. The top-level of Bauhaus institute the system CPU and allow developers to add their modules to the system. The binding of modules ports and signals is done at the top level as well.

When Bauhaus simulation start it starts be executing the CPU initialization thread. The CPU initialization thread calls the software routine after running initialization checks. The software routine is a member function of one of the CPU elements. The software routine's implementation contains the user-defined software or in our case the tests that we want to run on Bauhaus. The software routine uses a pointer to the CPU object to initiate read and write transactions to different modules of the system. Once the function is executed the CPU stops and the simulation is over.

Bauhaus generates log files of the simulation which capture all the transaction that have been carried out by the simulation with their time stamps. So as a user of Bauhaus you would have to take care of correctly binding the ports of your modules to the system. and write the read or write transaction that you want the system to simulate in the software routine using a pointer to a CPU object.

# Chapter 3

# Methodology

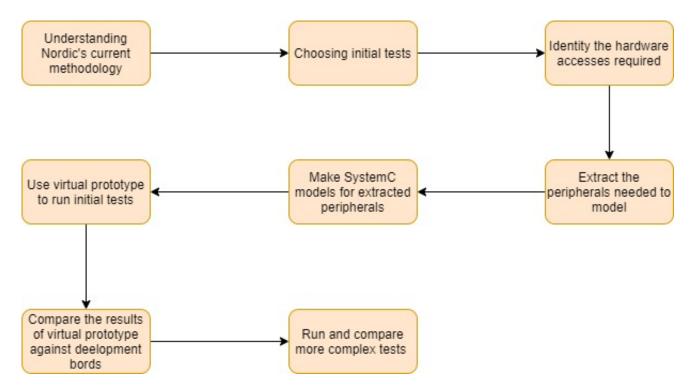

Figure 3.1 illustrates the proposed steps to carry out throughout this work. Steps have been explained in more detail in separate sections of this chapter. Methodology steps start with understanding and getting familiar with Nordic Semiconductor's technology and testing process. The work moved from simple to more complex tests to have an easier and less complicated debugging process.

Figure 3.1: Proposed steps of methodology

# **3.1** The initial subset of tests

The first task of the thesis was to define an initial test to focus on, from the different tests performed by the software team at Nordic Semiconductors. Any chosen test to run on our virtual platform will affect its architecture in the following points:

Modeled hardware

Each test is performed to verify specific functionalities of the system carried by one or more peripherals. And in turn, only some of the peripherals' models will be needed for each test. And that will govern which of the system's peripherals are going to be modeled in our virtual platform.

• Peripherals' models' Details

After deciding which peripherals are needed to be modeled to run a certain test on the platform, we had to decide how many details are present in the models. The details of each model include the registers and the different functionalities of each peripheral. The introduced details to each model should mainly cover the registers and functionalities of tests to be run.

The previous points show how significant the effect of tests on the complexity of the platform. That makes selecting the initial test to start model the system based on very critical. The initial test needs to provide meaningful testing to compare its results and performance with the development boards later on. It also should use a range of common peripherals that are reusable by future tests.

As mentioned in section 2.4, running any of Multiprotocol Service Layer (MPSL) tests follows a standard structure. All of MPSL tests assert the function *mpsl\_init* at the beginning of the test and call the function *mpsl\_uninit* at the end of the test as shown in script below 1.

```

void dummy_test (void)

{

ASSERT_EQ(mpsl_init(arguments),0);

/*

*

```

```

7 *The rest of the test body

8 *

9 */

10 mpsl_uninit();

11 }

```

Listing 3.1: MPSL test structure

The function *mpsl\_init* initializes the system for other operations. It initializes some registers' values, configures the Nested Vector Interrupt Controller, and triggers different peripherals needed for the system to operate. While the function *mpsl\_unint* performs similar to *mpsl\_init* except it turns off some of the peripherals as they are not needed anymore.

For the initial test, the initialization test has been selected which we will refer to as the base test since it fits the criteria of the initial test and will be the base of all further tests to be implemented. The initialization test uses the functions *mpsl\_init* and *mpsl\_unint* and asserts the values of Nested Vector Interrupt Controller (NVIC)'s registers. The base test will access the peripherals implemented in *mpsl\_init* and *mpsl\_unint*. The next section will elaborate on the peripherals and functionalities that need to be implemented for the base test.

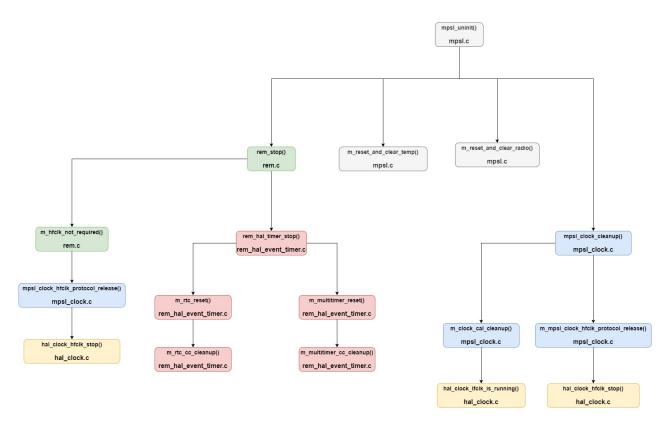

# 3.2 Identifying hardware accesses

To identify the accessed register for the base test we had to account for the peripherals' accesses by NVIC which implemented in the body of the test, and the hardware accesses due to the functions *mpsl\_init* and *mpsl\_uninit*. And to identify the accessed peripherals from the functions *mpsl\_init* and *mpsl\_unint* we went over the definition of each of the functions. We also identified which functionalities of the accessed peripherals are used. The figure 3.2 illustrates the used functions in *mpsl\_init* which perform accesses to one or more peripherals. For example, in figure 3.2, the main routine *mpsl\_init* calls for four immediate functions. They are listed with their accessed peripherals in table 3.1.

And figure 3.3 does the same for the function *mpsl\_uninit*. The blocks with the same color indicate that the functions are in the same C file.

| Functions                       | accessed peripheral |

|---------------------------------|---------------------|

| <i>m_reset_and_clear_temp()</i> | temperature sensor  |

| m_reset_and_clear_radio         | RADIO               |

| mpsl_clock_init                 | CLOCK               |

| rem_start()                     | TIMER and RTC       |

Table 3.1: immediate functions after *mpsl\_init*

In both graphs, they software start from calling the main function either *mpsl\_init* or *mpsl\_uninit*. The arrows represent a function call from the function at the arrow's base to the function at its base. Each block has the name of the function and its containing file, with blocks with the same color existing in the same file. The functions illustrated are only the ones that perform one peripheral access or more. While other functions that do not access peripherals are used by the tests, they are not visible in the graph to keep its size from exploding and for irrelevance to the modeling process.

Figure 3.2: mpsl\_init functions that access the peripherals

Figure 3.3: mpsl\_uninit functions that access the peripherals

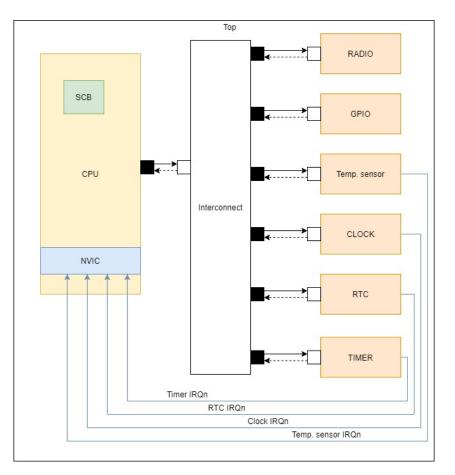

# **3.3** Extracted peripherals

After going through the peripherals' accesses needed to perform the base test, we have listed the peripherals that need to be modeled to be able to run the base test. The list is made by finding registers accesses performed in by the software and gather the accessed registers of each peripheral to form to realize how would the peripheral model will consist of. After gathering registers accesses to different peripherals we got a list of the following peripherals to model:

- CLOCK peripheral

- RADIO peripheral

- Real-time counter (RTC) peripheral

- Temperature sensor peripheral

- TIMER peripheral

- General purpose input/output (GPIO) peripheral

Figure 3.4: The virtual prototype structure

Figure 3.4 illustrates the architecture of the virtual platform in the SystemC environment. A detailed description of each peripheral models is in the next section.

# **3.4 Modeling of peripherals**

We are both working on the same virtual prototype to cover its peripherals with each thesis developing a different set of peripherals models. To simplify the collaboration between two theses we have used a peripheral's model template. It aims to standardize the modeling process and reduce the complexity of integrating the models together to build the platform.

The template provides a target socket for the models to connect to the interconnect with a blocking transport implementation to communicate over the interconnect. It also has a generic base structure to define registers of each peripheral and generic read and write functions to and from these registers. The interaction (read and write) with a peripheral registers in the template

| NVIC registers                          |

|-----------------------------------------|

| Interrupt Set Enable Register (ISER)    |

| Interrupt Clear Enable Register (ICER)  |

| Interrupt Clear Pending Register (ICPR) |

| Interrupt Set Pending Register (ISPR)   |

| Interrupt Priority Register (IPR)       |

Table 3.2: NVIC's registers

| Function             | Description                       |

|----------------------|-----------------------------------|

| NVIC_DisableIRQ      | Enable interrupts                 |

| NVIC_EnableIRQ       | Disable interrupts                |

| NVIC_ClearPendingIRQ | Clears the status of IRQ pending  |

| NVIC_GetEnableIRQ    | Returns if IRQ is enabele or not  |

| NVIC_GetPendingIRQ   | Returns the status of IRQ pending |

| NVIC_SetPriority     | Sets the priority of IRQ          |

Table 3.3: List of used Nested Vector Interrupt Controller (NVIC) registers

is implemented using *BusRead* function and *BusWrite* functions. These functions allow the registers of the peripherals' models to be accessed. Each transaction that occurs to a peripheral will be either read or write and based on the transaction type the functions *BusRead* or *BusWrite* will be called. Both functions use switch expression based on the register's address to perform read, write, and other required changes. The template of the models can be found in appendix B.1.

#### 3.4.1 Nested Vector Interrupt Controller (NVIC) model

The implementation of NVIC model has been added to the CPU model by defining its registers and functions as part of the CPU model. Only the registers used by the running tests are implemented.

The registers in table 3.2 were represented by a struct inside the CPU constructor. The functionalities of the Nested Vector Interrupt Controller present as CPU methods and table **??** list the NVIC functions that have been implemented.

The interrupt lines are modeled using  $sc\_signal$  to connecting the interrupt output from the peripherals models to the CPU model. the interrupt output at the peripherals is of type  $sc\_out$  while at CPU is defined of type  $sc\_in$ . All different interrupt signals are binded in the *TOP* model to create the Interrupt request line (IRQ) for different peripherals.

We have used *std::function* type as pointer to interrupt handler routines(interrupt vector). This type can be considered as a safer version of a function pointer and can reference any type of callable target. A vector type  $cb\_arg\_t$  was made to store the addresses of all interrupt vectors. Type  $cb\_arg\_t$  is defined as follows:

```

struct cb_arg_t {

//the callback - takes a uint32_t input.

std::function<void(void)> cb;

//value to return with the callback.

uint32_t arg;

};

std::vector<cb_arg_t> callbacks_;

```

New interrupt vectors can be added to interrupt vector table bu passing a pointer to the interrupt handler and an integer representing the IRQ number. The code written to implement the NVIC can be found in appendix B.2.

For now, the interrupt handlers are predefined as simple print commands. While the current NVIC model can detect interrupt requests from other peripherals models. It is still can not execute complex interrupt handlers. This could be further developed but for our test which uses NVIC to enable or disable some interrupt lines without actually using interrupts to trigger other actions.

#### 3.4.2 CLOCK peripheral's model

The CLOCK model has been implemented as a separate peripheral unlike the NVIC which was part of the CPU. The model follows the peripherals' template structure where it has the following registers:

The description of the registers in table 3.4 can be found in section 2.5.3.

When starting the platform, the initialization thread of the CLOCK model runs a wait command and triggers the internal High Frequency Clock (HFCLK) to simulates the startup delay in the peripheral til the High Frequency Clock signal is stable and ready to be used by the system. After the initialization of the CLOCK peripheral, there are three main functionalities the CLOCK provides:

| CLOCK model registers | Description                                        |

|-----------------------|----------------------------------------------------|

| nrfclockHFCLKSTART    | Start HFCLK crystal oscillator                     |

| nrfclockHFCLKSTOP     | Stop HFCLK crystal oscillator                      |

| nrfclockLFCLKSTART    | Start LFCLK source                                 |

| nrfclockLFCLKSTOP     | Stop LFCLK source                                  |

| nrfclockCAL           | Start calibration of LFRC oscillator               |

| nrfclockCTSTART       | Start calibration timer                            |

| nrfclockCTSTOP        | Stop calibration timer                             |

| nrfclockHFCLKSTARTED  | HFCLK oscillator started                           |

| nrfclockLFCLKSTARTED  | LFCLK oscillator started                           |

| nrfclockDONE          | Calibration of LFCLK RC oscillator complete event  |

| nrfclockCTTO          | Calibration timer timeout                          |

| nrfclockINTENSET      | Enable interrupt                                   |

| nrfclockINTENCLR      | Disable interrupt                                  |

| nrfclockHFCLKSTAT     | HFCLK status                                       |

| nrfclockLFCLKSTAT     | LFCLK status                                       |

| nrfclockLFCLKSRC      | Clock source for the LFCLK                         |

| nrfclockHFXODEBOUNCE  | Sets the debounce time to start the external HFCLK |

|                       | oscillator                                         |

| nrfclockCTIV          | Calibration timer interval                         |

Table 3.4: Registers of the CLOCK model

- High Frequency Clock (HFCLK) control.

- Low Frequency Clock (LFCLK) control.

- Low Frequency Clock (LFCLK) calibration.

#### High Frequency Clock (HFCLK) control

As mentioned when the CLOCK powers up, it starts with the internal High Frequency Clock (HFCLK). After that the external High Frequency Clock could be used changing different sources for the High Frequency Clock can be performed.

The figure 3.5 shows how to start the external high frequency oscillator. It starts by triggering the *TASKS\_HFCLKSTART* which can be done by writing 1 to register *nrfclockHFCLKSTART*. After that, the model checks the status of the High Frequency Clock (HFCLK) if it is already running, If so, it returns a message reporting that the external oscillator is already in use. If it is not running, the status register will be updated to change the state of the external oscillator to "Running" and the source of High Frequency Clock (HFCLK) to the external oscillator. followed by a simulation of the start-up time needed for the external oscillator to generate a stable clock. The waiting period depends on the sum of the oscillator

Figure 3.5: The steps to start the external high frequency oscillator

startup time (which is 360us) and the debouncing time. The debouncing time is either 256us or 1024us depending on the value of *nrfclockHFXODEBOUNCE* register. After the waiting period has passed the model will set the value of *nrfclockHFCLKSTARTED* and notify the

interrupt event of starting external High Frequency Clock which could trigger an interrupt of its conditions are met.

Figure 3.6: Steps to stop the external High frequency oscillator

Alternatively, to stop the external High Frequency Clock (HFCLK) the tasks *TASKS\_HFCLKSTOP* has to be triggered by writing 1 to register *nrfclockHFCLKSTOP*. It model first checks the status of the external oscillator, if it isn't running, it displays a message stating that. If the external oscillator is running it will update the status register *nrfclockHFCLKSTAT* to indicate changing the state to "Not Running" and the source to internal RC oscillator. And the figure 3.6 illustrates these steps.

| Value | Source                               |

|-------|--------------------------------------|

| 00    | 32.768 kHz RC oscillator (LFRC)      |

| 01    | 32.768 kHz crystal oscillator (LFXO) |

| 10    | 32.768 kHz synthesized from HFCLK    |

|       | (LFSYNT)                             |

Table 3.5: List of Low Frequency Clock (LFCLK) sources

#### Low Frequency Clock (LFCLK) control

Unlike the High Frequency Clock (HFCLK) which starts when the CLOCK's model powers up, the Low Frequency Clock (LFCLK) needs to be explicitly started regardless of its source. To use the Low Frequency Clock (LFCLK) the source needs to be decided by writing the source value into register *nrfclockLFCLKSRC* like shown in table 3.5. If the source has not been chosen the default option is 32.768 kHz RC oscillator.

Figure 3.7 shows the steps to start the Low Frequency Clock (LFCLK), it is started when the task *TASKS\_LFCLKSTART* is triggered by writing 1 to register *nrfclockLFCLKSTART*. The model checks the state register of Low Frequency Clock (LFCLK), if it is already running it prints a message stating that. While if it was not running, it then checks which oscillator is the source for the Low Frequency Clock, in the case of the external oscillator as the source, the model will delay the simulation to imitate the start-up time needed by the external oscillator. Then it updates the state of LFCLK to "Running", generate *LFCLKSTARTED* event and he notifying interrupt event for starting starting LFCLK. This event might trigger an interrupt to the CPU if its conditions are met.

The stopping process of the LFCLK is illustrated in figure 3.8 the task *TASKS\_LFCLKSTOP* need to be triggered by writing 1 to the register *nrfclockLFCLKSTOP*. The model then checks the state of LFCLK, if it is "Not Running" it prints a message indicating that. While if the state is "Running" the state is changed to "Not Running".

#### Low Frequency Clock (LFCLK) calibration

As mentioned before the frequency of the RC internal oscillator might be affected by

Figure 3.7: Steps to start the LFCLK

variation in temperature. And it can be calibrated to compensate for these variations. The calibration uses the external high-frequency oscillator to calibrate the RC oscillator, so before performing the calibration the Low Frequency Clock (LFCLK) needs to be running with RC oscillator as its source as well as the high-frequency oscillator. Before running the calibration process the calibration timer needs to run first. To run the calibration timer the register *CTIV*

Figure 3.8: Steps to stop the LFCLK

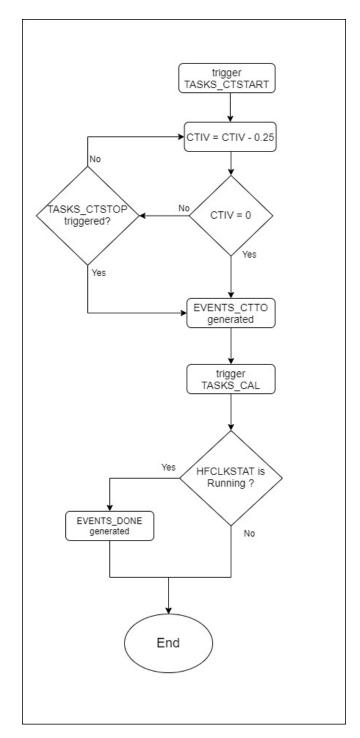

should configure first with the calibration timer interval. The start of the calibration timer is triggered by writing to the *TASKS\_CTSTART* register.