David Barahona Pereira

Virtual Prototypes for Embedded Software Testing: A SystemC Based Proof of Concept Implementation for Nordic Semiconductor

Master's thesis in Embedded Computing Systems Supervisor: Milica Orlandic June 2020

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Master's thesis

David Barahona Pereira

Virtual Prototypes for Embedded Software Testing: A SystemC Based Proof of Concept Implementation for Nordic Semiconductor

Master's thesis in Embedded Computing Systems Supervisor: Milica Orlandic June 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

### Acknowledgment

I would like to extend my sincere thanks to my supervisors in NTNU and Nordic Semiconductor. To my NTNU supervisor, Milica Orlandic, thank you for always making time between your many obligations to provide valuable feedback and guidance throughout this thesis. To Isael Diaz, Joakim Urdahl, and Shankar Gunasekaren in Nordic Semiconductor, thank you for giving me the opportunity to execute my thesis in such an amazing company, and especially, for all the dedication, effort, and support that went into making this project possible. I would also like to extend my gratitude to Motaz Thiab for being a great companion when working together with me on this project. I would like to recognize the effort of the European Commission to sustain programs like the Erasmus Mundus Joint Master Degrees to promote and facilitate the access to first-class education in the most prestigious European universities. Completing this thesis would not have been possible without the support of my friends and family. I would like to thank all my friends in Costa Rica for always being in touch and supporting me despite the distance. I would also like to thank all the friends I made during this Masters in Germany and Norway. Thank you for all the fantastic memories and for making my time abroad such a joyful experience. Lastly, I want to extend my deepest gratitude to my family who despite the distance, has always been there to support me and be the motivation behind everything I do.

David Barahona Pereira

### Abstract

The use of virtual prototypes in the semiconductor industry has proven to be a successful approach to deliver products earlier and with superior quality. This thesis focuses on implementing a system that can serve as a proof of concept to evaluate the use of virtual prototypes for embedded software testing in Nordic Semiconductor. To achieve this goal, one software test was selected, and all the hardware interactions present in this test were extracted and modelled in the form of a virtual prototype using SystemC. Once the system model was able to run that test, it was scaled to execute two more tests. Results show that the virtual prototype was able to replicate passing and failing tests, provide configurable levels of hardware observability that were not available before, and execute tests close to 150 times faster. These results could translate into shorter times for product delivery, new resources for architectural improvements, and enhancements in the test design productivity.

## Contents

|   | Ack  | nowledgment                                                | i  |

|---|------|------------------------------------------------------------|----|

|   | Abs  | tract                                                      | ii |

| 1 | Intr | roduction                                                  | 2  |

|   | 1.1  | Background                                                 | 2  |

|   | 1.2  | Thesis Statement                                           | 4  |

|   | 1.3  | Outline                                                    | 4  |

| 2 | The  | eory                                                       | 6  |

|   | 2.1  | Embedded Software Testing at Nordic Semiconductor          | 6  |

|   |      | 2.1.1 Unit Tests                                           | 6  |

|   |      | 2.1.2 Target Tests                                         | 7  |

|   | 2.2  | MPSL Library Target Tests                                  | 9  |

|   |      | 2.2.1 Hardware Interaction in the MPSL Init Test           | 10 |

|   | 2.3  | Virtual Prototyping                                        | 16 |

|   |      | 2.3.1 Virtual Prototypes for Embedded Software Development | 17 |

|   | 2.4  | SystemC Library Core                                       | 18 |

|   |      | 2.4.1 Origins of SystemC                                   | 18 |

|   |      | 2.4.2 Virtual Prototyping with SystemC                     | 19 |

|   |      | 2.4.3 Overview of the SystemC Components                   | 20 |

|   | 2.5  | System C and TLM                                           | 23 |

|   |      | 2.5.1 TLM Concept                                          | 23 |

|   |      | 2.5.2 Overview of TLM 2.0                                  | 24 |

|   |      | 2.5.3 TLM 2.0 Coding Styles                                | 25 |

|   |     | 2.5.4   | Direct Memory Interface and Debug Transport Interface | 27 |

|---|-----|---------|-------------------------------------------------------|----|

|   | 2.6 | Bauha   | us: Nordic Semiconductor's Generic Virtual Prototype  | 28 |

| 3 | Met | hods    |                                                       | 30 |

|   | 3.1 | Embeo   | ded Software Testing Approach Understanding           | 31 |

|   | 3.2 | Tests S | election and Determination of Required Models         | 32 |

|   | 3.3 | Virtua  | Prototype Implementation                              | 33 |

|   |     | 3.3.1   | Bauhaus as a Base for the Virtual Prototype           | 34 |

|   |     | 3.3.2   | Peripheral Template                                   | 34 |

|   |     | 3.3.3   | 2.4 GHz Radio Peripheral Model                        | 36 |

|   |     | 3.3.4   | Temperature Sensor Peripheral Model                   | 37 |

|   |     | 3.3.5   | Real-time Clock Peripheral Model                      | 39 |

|   |     | 3.3.6   | Timer Peripheral Model                                | 41 |

|   |     | 3.3.7   | System Control Block                                  | 41 |

|   |     | 3.3.8   | Assembly Function Calls                               | 42 |

|   |     | 3.3.9   | Memory Accesses                                       | 42 |

|   |     | 3.3.10  | Complete Virtual Prototype                            | 43 |

|   | 3.4 | Virtua  | Prototype Verification                                | 45 |

|   |     | 3.4.1   | 2.4 GHz Radio Peripheral Verification                 | 45 |

|   |     | 3.4.2   | Temperature Sensor Peripheral Verification            | 45 |

|   |     | 3.4.3   | Real-Time Clock Peripheral Verification               | 46 |

|   |     | 3.4.4   | Timer Peripheral Verification                         | 46 |

|   |     | 3.4.5   | System Control Block and Assembly Calls Verification  | 46 |

|   |     | 3.4.6   | Complete Virtual Prototype Verification               | 47 |

|   | 3.5 | MPSL    | Init Test Execution                                   | 47 |

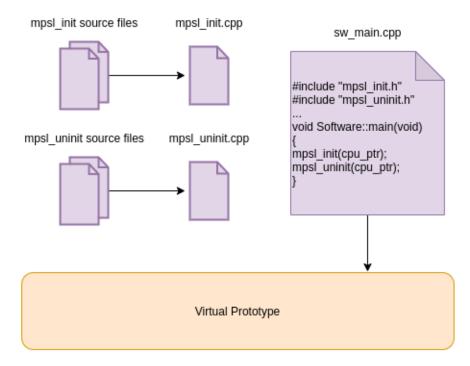

|   |     | 3.5.1   | Running the MPSL Init and Uninit Functions            | 47 |

|   |     | 3.5.2   | Running the Complete Test                             | 49 |

|   | 3.6 | Virtua  | Prototype Scaling                                     | 50 |

|   |     | 3.6.1   | Temperature Measurement Test                          | 50 |

|   |     | 3.6.2   | One-shot Timer Callback Test                          | 51 |

|    | 3.7            | Perfor  | mance Evaluation                                   | 53 |

|----|----------------|---------|----------------------------------------------------|----|

|    |                | 3.7.1   | Test Timing and Verbosity Control                  | 53 |

| 4  | Res            | ults    |                                                    | 56 |

|    | 4.1            | Virtua  | al Prototype Simulation                            | 56 |

|    |                | 4.1.1   | 2.4 GHz Radio Peripheral Simulation                | 56 |

|    |                | 4.1.2   | Temperature Sensor Peripheral Simulation           | 57 |

|    |                | 4.1.3   | Real-Time Clock Peripheral Simulation              | 58 |

|    |                | 4.1.4   | Timer Peripheral Simulation                        | 60 |

|    |                | 4.1.5   | System Control Block and Assembly Calls Simulation | 62 |

|    |                | 4.1.6   | Complete Virtual Prototype Simulation              | 63 |

|    | 4.2            | Hardy   | vare vs. Virtual Prototype Comparison              | 65 |

|    |                | 4.2.1   | Test Execution                                     | 65 |

|    |                | 4.2.2   | Hardware Observability                             | 67 |

|    |                | 4.2.3   | Execution Time                                     | 68 |

| 5  | Disc           | cussior | 1                                                  | 71 |

| 6  | Con            | clusio  | ns                                                 | 74 |

| A  | Abb            | reviati | ons and Acronyms                                   | 75 |

| Bi | ibliography 77 |         |                                                    | 77 |

## List of Tables

| 3.1 | Register accesses for the TEMP peripheral            | 37 |

|-----|------------------------------------------------------|----|

| 3.2 | Register accesses for the RTC peripheral             | 39 |

| 3.3 | Register accesses for the TIMER peripheral           | 41 |

| 3.4 | CPU functions that implement assembly function calls | 42 |

| 4.1 | Execution time comparison                            | 70 |

# **List of Figures**

| 2.1  | Testing approach of the embedded software team                     | 7  |

|------|--------------------------------------------------------------------|----|

| 2.2  | Simplified call sequence in a target test                          | 8  |

| 2.3  | Block diagram of the CLOCK peripheral                              | 11 |

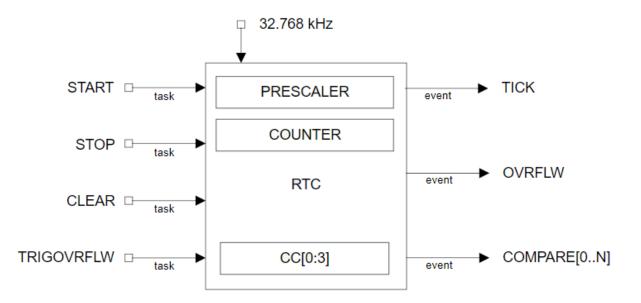

| 2.4  | Block diagram of the RTC peripheral                                | 12 |

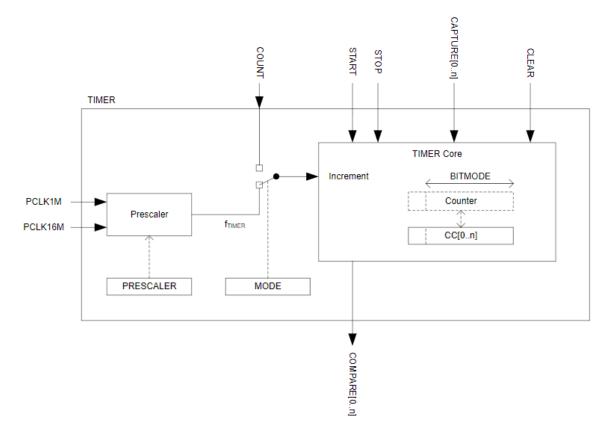

| 2.5  | Block diagram of the TIMER peripheral                              | 13 |

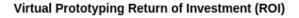

| 2.6  | Net profit from a real case study of the use of virtual prototypes | 17 |

| 2.7  | Architecture of the SystemC library                                | 19 |

| 2.8  | Simplified SystemC simulation kernel                               | 22 |

| 2.9  | TLM components                                                     | 25 |

| 2.10 | Example of a message sequence in TLM LT                            | 26 |

| 2.11 | Example of a message sequence in TLM AT                            | 27 |

| 2.12 | Components of the Bauhaus generic virtual prototype                | 29 |

| 3.1  | Thesis development approach                                        | 30 |

| 3.2  | Behaviour of the TEMP peripheral model                             | 38 |

| 3.3  | Behaviour of the RTC peripheral model                              | 40 |

| 3.4  | Representation of the complete virtual prototype                   | 44 |

| 3.5  | Execution approach of the MPSL initialization routines             | 48 |

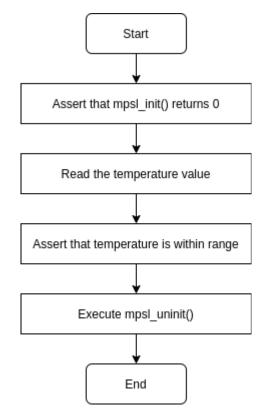

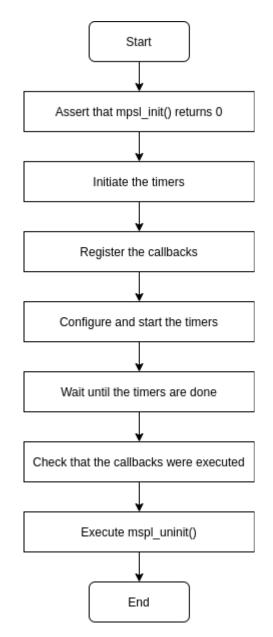

| 3.6  | Execution flow of the Temperature Measurement test                 | 51 |

| 3.7  | Execution flow of the One-shot Timer Callback test                 | 52 |

| 4.1  | Simulation accessing the POWER register of the RADIO peripheral    | 56 |

| 4.2  | Simulation of a stopped temperature measurement                    | 57 |

| 4.3  | Simulation of a normal temperature measurement without interrupts     | 58 |

|------|-----------------------------------------------------------------------|----|

| 4.4  | Simulation of a normal temperature measurement with interrupts        | 58 |

| 4.5  | Simulation testing the normal counter operation                       | 59 |

| 4.6  | Simulation testing a count compare event without interrupts           | 59 |

| 4.7  | Simulation testing a count compare event with interrupts              | 60 |

| 4.8  | Simulation testing the normal timer operation                         | 61 |

| 4.9  | Simulation testing a count compare event without interrupts           | 61 |

| 4.10 | Simulation testing a count compare event with interrupts              | 62 |

| 4.11 | Simulation of accesses to the SCR register in the SCB                 | 63 |

| 4.12 | Simulation of the assembly calls                                      | 63 |

| 4.13 | Simulation of two components communicating in the virtual prototype   | 64 |

| 4.14 | Passing execution of the MPSL Init test on the board                  | 65 |

| 4.15 | Passing execution of the MPSL Init test on the virtual prototype      | 65 |

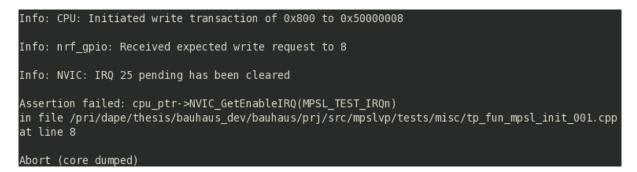

| 4.16 | Failing execution of the MPSL Init test on the board                  | 66 |

| 4.17 | Failing execution of the MPSL Init test on the virtual prototype      | 66 |

| 4.18 | Log file after executing the MPSL Init test on the virtual prototype  | 68 |

| 4.19 | Execution time measurement for the MPSL Init test                     | 68 |

| 4.20 | Simulation output without verbosity                                   | 69 |

| 4.21 | Simulation output displaying information only for the TEMP peripheral | 69 |

# Listings

| 2.1 | Structure of a MPSL target test                                       | 9  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | SystemC description of a 2-input OR gate                              | 20 |

| 3.1 | Simplified peripheral template header file                            | 35 |

| 3.2 | MPSL Init test                                                        | 49 |

| 3.3 | Execution time measurement approach                                   | 54 |

| 3.4 | Verbosity control function                                            | 55 |

| 4.1 | Log file after executing the MPSL Init test on the development boards | 67 |

## Chapter 1

## Introduction

## 1.1 Background

Nordic Semiconductor is a Norwegian fabless semiconductor company with headquarters in the city of Trondheim. The company specializes in ultra-low-power wireless system on a chip (SoC) commonly found in wireless PC peripherals, fitness devices, game controllers, and many others. As the semiconductor market demands grow, embedded SoCs become more powerful and complex. These factors have started to influence more and more companies to incorporate non-traditional approaches during the design and development of their products to remain competitive.

Virtual prototypes represent a successful approach for improving productivity and reducing the time to market (TTM) of new products [1]. A virtual prototype is an executable software model of a hardware system that can run software just as a physical system would. These prototypes have been exploited by big semiconductor companies around the world. For example, Texas Instruments adopted virtual prototypes during the development of their OMAP SoC, allowing them to bring up Linux and Android on the eventual hardware in just a few days when this milestone used to take weeks or months instead. Other companies like Siemens, Altera, Fujitsu, Bosch, Hitachi, General Motors, and ARM share similar experiences with this technology. Given the potential benefit these prototypes can provide, Nordic Semiconductor is considering to adopt them in several stages of their SoC design flow. One of the applications in which Nordic Semiconductor is planning to exploit their capabilities is the development of embedded software. Currently, the software team in charge of developing the low-level software that goes into the wireless communication software stack of Nordic Semiconductor's SoCs, test their code using a two-step approach divided into what they call unit tests and target tests.

The main goal of the unit tests is to check the software logic. Unit tests run on a host PC, so all the code sections that interact with the hardware are replaced by mock functions. These are just empty functions that let the code execute due to the absence of a hardware device that should support these interactions. On the other hand, target tests are more complex. They exercise both the software logic and the remaining pieces of code that unit tests cannot cover. Target tests cannot run on a host PC, so they require a specific hardware device to execute. For this reason, they run using development boards equipped with Nordic Semiconductor's SoCs.

During target tests, hardware interactions involve accesses to different peripherals and CPU registers. Register accesses intend to trigger a specific behaviour or to return some value needed for the execution. The idea at Nordic Semiconductor is to implement a new testing stage in which these hardware interactions could carry out in a virtual prototype. This prototype should model the behaviour of the SoC at a higher level of abstraction. By doing so, the virtual prototype can simulate whatever occurs in the hardware when a test executes, and the same target tests that used to require a physical SoC to run can now also run in any host PC.

The use of virtual prototypes for embedded software testing has a lot of potential benefits for different teams. In the case of the system architecture group, they could measure the performance of their device in the presence of the software it supports, allowing them to make significant architectural improvements. For the software team, not depending on the hardware device could mean the possibility to enable more complex testing scenarios. It could also mean that they should not wait until the hardware is ready to start testing the software, resulting in a shorter TTM for new products. Lastly, the fact that virtual prototypes work on higher abstraction levels allows them to execute faster than the real hardware, improving the test design productivity.

### **1.2 Thesis Statement**

This thesis aims to deliver a proof of concept of how a virtual prototype modelling an SoC from Nordic Semiconductor can be used to test their embedded software. This system was developed by taking an existing generic virtual prototype as a base, expanding the functionalities of its abstract CPU model, and by creating models of different system peripherals. The first design of the virtual prototype can execute one specific software test, and different extensions allowed it to execute two more tests. Therefore, the final virtual prototype can execute a total of three tests. Benefits, limitations, and recommendations for this software testing approach are derived from the implementation so that Nordic Semiconductor can consider whether to integrate it or not into their design flow. Given the magnitude of this work, two different projects were working in parallel to achieve this goal. Both projects worked on different tasks of the hardware components modelling and verification, the simple test interface and execution, and the system refinement effort to run more tests. This thesis emphasizes the work done by this particular project but also references components borrowed from the other.

## 1.3 Outline

Chapter 1 includes background information to help the reader understand what motivated Nordic Semiconductor to consider virtual prototypes for embedded software testing. It states the goal behind this project and also indicates the approach taken to achieve this goal.

Chapter 2 introduces the software testing methodology at Nordic Semiconductor and explains what unit and target tests are. It describes the Multi-Protocol Service Layer (MPSL) library, more specifically the MPSL target tests and the hardware interactions carried out during the execution of one simple test. This chapter also includes a literature study about what is virtual prototyping and how it could improve the software development cycle, basics of the C++ SystemC library for hardware modelling as well as the concept of Transaction-Level Modelling (TLM). Lastly, it describes the Bauhaus generic virtual prototype from Nordic Semiconductor that was used as a base to develop the virtual prototype proof of concept.

Chapter 3 delves into the methodology followed throughout this thesis. It explains the approach taken to understand the current testing methodology and also the criteria used to select a specific set of tests to focus as a starting point. Since the project scope did not include modelling a whole SoC, this chapter explains the reasoning that led to the selection of which components to model. It also describes in a detailed manner how each of these models works. This chapter also includes a verification plan for each hardware model. It covers how it was possible to interface the virtual prototype with a simple test and describes the implementation of two extra tests. Finally, it presents the procedure used to evaluate the potential benefits of the virtual prototype implementation.

Chapter 4 is devoted to the implementation results. It presents simulations for each of the hardware models that show how they meet their functional specifications. The chapter also includes a simulation of the entire system in which different peripherals communicate with each other by using interrupts. After the virtual prototype simulation results, this section compares the virtual prototype implementation to the current testing approach. The execution of passing and failing tests was employed to verify the virtual prototype's capability to execute MPSL target tests. Lastly, the chapter compares the hardware observability of the new implementation to the current testing approach as well as test execution times.

Chapters 5 and 6 deal with results discussion and conclusions. The discussion chapter provides insights into what the results mean, why they are relevant, as well as their limitations and recommendations for future work. The conclusions wrap-up this project by presenting a summary of the most important ideas discussed during this thesis.

## **Chapter 2**

## Theory

## 2.1 Embedded Software Testing at Nordic Semiconductor

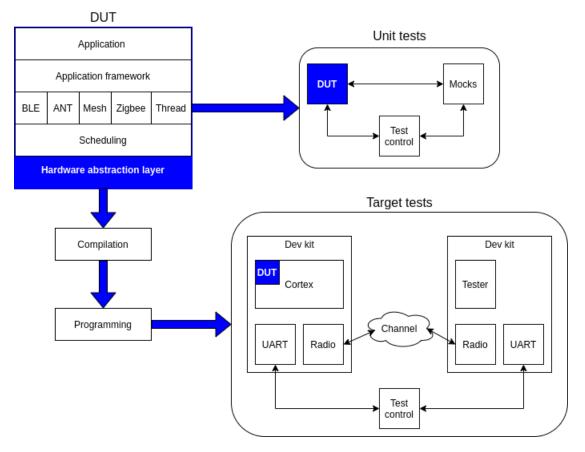

The software stack that makes it possible to implement wireless communication in Nordic Semiconductor's SoCs is quite complex. Wireless protocols require thousands of lines of code that interact with peripherals like clock controllers, timers, counters, radio, among others. It is because of this magnitude and complexity that each component of the software stack goes through an extensive testing process before being deployed as a part of real applications. The software team in charge of this matter currently tests their software stack using the approach depicted in Figure 2.1. This approach makes a distinction between unit tests and target tests based on their goal and on the platform in which they execute.

#### 2.1.1 Unit Tests

Unit tests are simple and have a scope usually limited to a single source file. An important characteristic of these tests is that they execute on a host PC, which means they do not require a Nordic Semiconductor's SoC to run. Unit tests exist mostly to evaluate the logic of the software. When these source files need to perform activities that demand some action from the hardware, mock functions, which are empty, come into play so the code can continue its execution. These mock functions have the same name but different implementations from the original ones that interact with the hardware when the source code runs in an SoC.

Figure 2.1: Testing approach of the embedded software team

#### 2.1.2 Target Tests

Target tests have a broader scope than unit tests, and they exercise specific behaviours that involve one or more source files. Target tests, unlike unit tests, do not run on a host PC and require a physical connection to a Nordic Semiconductor's SoC. Because of this, they execute using development boards that hold extra circuitry for peripheral access and debugging. Since target tests run on real boards, they need to compile and flash the program into the device memory to run as a regular application would. As Figure 2.1 shows, two boards are required to execute target tests. One of the boards becomes the device under test (DUT), and the other becomes a tester. They communicate through a radio channel and coordinate the test control using the UART peripheral. However, not all the tests demand two boards to execute, tests that do not exercise any wireless communication require only a single board. These tests verify behaviours related to the clock control, timing, interrupt handling, and other functionalities in which the wireless protocols rely on to operate correctly. Not every single file of the software stack performs some class of hardware interaction. There is a lowermost software layer that is in charge of performing most of the register accesses. Register names are the same for all Nordic Semiconductor's SoCs, but their addresses may differ between devices. The tests remain generic by referring to the same register names but associating them to different addresses. It is possible to employ header files that replace the register names with the correct address value on the SoC. These header files are also known as the hardware abstraction layer shown in Figure 2.1.

Figure 2.2 shows an example of how this abstraction works. In this particular case, a test from the Multi-Protocol Service Layer (MPSL) library reads the temperature sensor value by calling a generic initialization routine defined in the mspl.c file. This routine calls a function that initializes only the clock by modifying several registers of the clock peripheral. Inside this function, one of the modified registers is used to disable interrupts. During compilation, a library header file assigns the correct address of this specific hardware register.

Figure 2.2: Simplified call sequence in a target test

### 2.2 MPSL Library Target Tests

Given the fact that target tests are present in different software stacks, this thesis focuses only on the ones from the MPSL library that require one board. MPSL includes services for single and multi-protocol wireless implementations. There are some peripherals which are exclusive to this library and should not be accessed by application software such as one real-time clock (RTC0), one timer/counter (TIMER0), the 2.4 GHz radio peripheral (RADIO), the clock control peripheral (CLOCK), and temperature sensor peripheral (TEMP) [2].

All MPSL target tests follow a similar structure as the one shown in Listing 2.1. To test different parts of the library, it is necessary to execute a shared initialization and uninitialization routine. These routines perform tasks like peripheral resets, temperature checks, clock parameter checks, clock calibration, clock triggering, among others. Usually, these two functions are considerably bigger than the actual test which is designed to target a specific behaviour. This behaviour could be returning a value from a temperature sensor, making sure a timer callback executes, or performing a particular clock calibration sequence.

```

void sample_mpsl_test(void){

mpsl_init();

/* Test body */

mpsl_uninit();

}

```

#### Listing 2.1: Structure of a MPSL target test

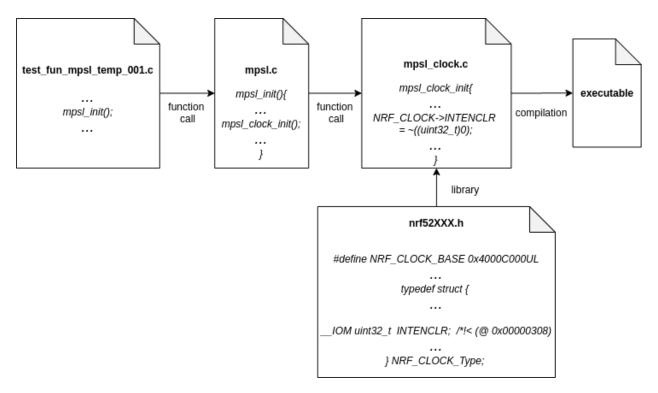

#### 2.2.1 Hardware Interaction in the MPSL Init Test

The MPSL library is composed of several tests that range from very simple tests to very elaborate ones. The development of this thesis revolves around one of the most basic MPSL tests, the MPSL Init test. The MPSL Init test purpose is to check that the initialization routines enable or disable interrupts for the different peripherals.

To execute MPSL target tests in a virtual prototype, it is necessary to identify which hardware is accessed by the different tests. These hardware accesses need to be defined since they dictate the minimum hardware components that the virtual prototype needs to model. All the hardware interactions that occur during the MPSL Init test are listed and described below. The virtual prototype that models these accesses works as the base that enables the execution of more complex tests. Hardware interactions in the MPSL Init test include:

- Peripherals

- Clock control

- Real-time counter

- Timer/counter

- General purpose input/output (GPIO)

- 2.4 GHz radio

- Temperature sensor

- CPU components

- Nested vector interrupt controller (NVIC)

- System control block (SCB)

- Assembler function calls

- Memory accesses

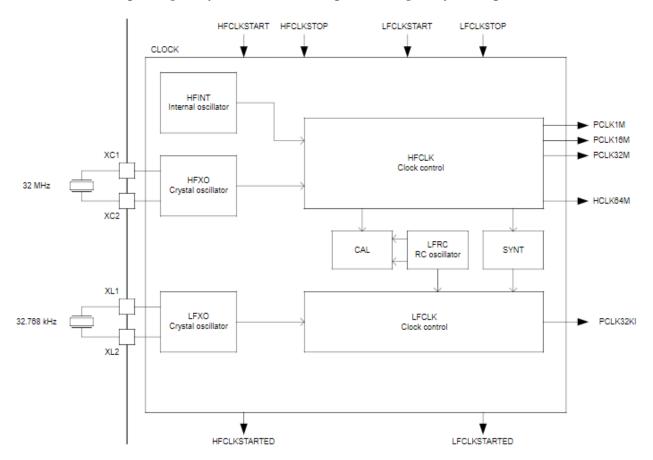

#### **Clock Control Peripheral**

The CLOCK peripheral is the one in charge of sourcing system clocks from a range of internal or external oscillators. It is also the one in charge of distributing them to the modules according to their specific needs. Figure 2.3 shows the components of the CLOCK.

This peripheral holds both a high-frequency and a low-frequency controller. The high-frequency controller can use a 64 MHz internal oscillator or an external crystal oscillator to provide a 64 MHz clock for the CPU and also clocks at 1 MHz, 16 MHz, and 32 MHz for the peripherals. The internal oscillator is active when there is a clock request, and the crystal oscillator is not running. Starting a high-frequency clock generates an event. The low-frequency controller can use a 32 kHz RC oscillator, a 32 kHz crystal oscillator, or a 32 kHz clock synthesized from the high-frequency clock as sources to provide a single 32 kHz clock. Just like in the high-frequency controller, starting a low-frequency clock generates an event.

Figure 2.3: Block diagram of the CLOCK peripheral [3]

The CLOCK is the most used peripheral during the mspl\_init() and mpsl\_uninit() routines. The mpsl\_init() function employs this peripheral for the clock initialization. During this process, the initialization routine disables interrupts and clears pending requests for the CLOCK in the interrupt controller. It also resets the events that show when the high or low-frequency clocks start, as well as events for the calibration termination and timeout. Part of the routine checks that the high-frequency clock was not triggered before the initialization and also that it was not running. The last part of the initialization is in charge of starting the low-frequency clock. On the other hand, the mpsl\_uninit() routine stops the high-frequency clock, clears events, stops the calibration timer if it was running, and disables the interrupts for both the interrupt controller and the CLOCK.

#### **Real-time Clock Peripheral**

The RTC works as a simple timer that runs from the low-frequency clock source. The RTC can also use a prescaler. Figure 2.4 shows a simplified block diagram of this hardware component.

Figure 2.4: Block diagram of the RTC peripheral [3]

The RTC can be started, stopped, or cleared at any time. The trigger overflow task sets the counter to the value of 0xFFFFFF to let the software test the overflow condition. When the internal count matches the value set in one of the compare registers, a compare event triggers an interrupt if they were previously enabled. This peripheral includes an overflow event to indicate that the count reached the maximum value, and a tick event that generates a signal for each counter increment.

There are several RTC peripherals. However, the MPSL initialization functions only make use of the RTC0. During both the mpsl\_init() and mpsl\_uninit() functions, a routine in charge of resetting and clearing the peripheral registers and interrupts employs the RTC0. The counter is started once during the execution of the mpsl\_init() function.

#### **Timer/Counter Peripheral**

There are several timers in each SoC, but just like the case of the RTC, TIMER0 belongs to the MPSL library. Figure 2.5 illustrates how the TIMER works.

Figure 2.5: Block diagram of the TIMER peripheral [3]

The TIMER can operate either as a timer or as a counter. In both modes, the peripheral can receive the order to start or stop at any time. However, when it stops and then starts again, the count does not start from scratch, but it resumes in the value before the stop request. In the timer mode, the internal counter value increments after every tick of the timer frequency signal, which can use the prescaler from either a 16 MHz or a 1 MHz reference clock. In counter mode, the internal counter value increments every time the counting task triggers. If interrupts are enabled, a compare event triggers when the internal counter value matches the value of one of the compare registers. On the other hand, when a capture task triggers, the value of the counter is copied in one of the compare registers.

TIMERO finds use in both mpsl\_init() and mpsl\_uninit() functions by routines in charge of resetting and cleaning up the timer. These routines stop the timer from running, disable interrupts, reset the events, set to zero the compare registers, and shut down the timer.

#### **General Purpose Input/Output Peripheral**

A GPIO is a digital signal pin whose behaviour is controlled by the user at run time. They have no predefined use, so the user can specify the pin's functionality depending on the application requirements. These pins are unused by default. The pins of the GPIO peripheral appear in groups defined as ports. Each port holds up to 32 GPIOs. This peripheral appears only once during the mpsl\_init() routine when the RTC starts. One pin of the GPIO works as a debugging tool to inform that the RTC startup is taking place.

#### 2.4 GHz Radio Peripheral

The RADIO is mainly composed of a 2.4 GHz radio receiver and a 2.4 GHz radio transmitter. It is a complex peripheral which also integrates modules to simplify direct memory access (DMA), automate packet assembly and disassembly, and also to automate cyclic redundancy check (CRC) generation and checks.

This peripheral barely finds use during the MPSL library's initialization routines. Only one function in charge of resetting the RADIO employs this peripheral. This routine is present in both the mpsl\_init() and mpsl\_uninit() functions, and the only thing it does is to turn the peripheral off and then on, to cause a full reset.

#### **Temperature Sensor Peripheral**

The TEMP measures the die temperature and has a resolution of 0.25 degrees. After the software triggers a temperature measurement, an event notifies that the measurement is complete, and that means the result is ready to be read from the temperature register.

It is only used during the mspl\_init() function to return a temperature value during the clock initialization. In this specific routine, interrupts are disabled, and the temperature data is obtained by polling a status register.

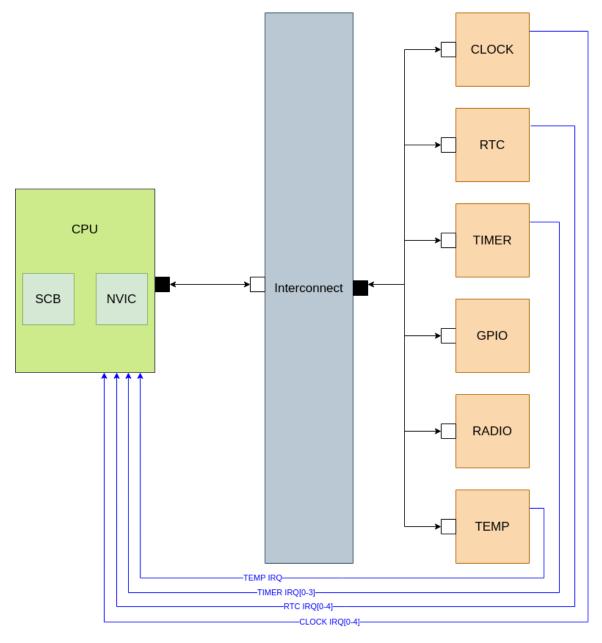

#### **Nested Vector Interrupt Controller**

The NVIC is not a peripheral but a part of the ARM CPU. Some of its functionalities need to be included in the CPU model since the abstract CPU in the virtual prototype only performs function calls instead of modelling a real ARM processor. The NVIC provides configurable interrupt handling abilities to the processor. It acts as an intermediary between the peripherals and the CPU. During the execution of the initialization routines and the test body of the MPSL Init test, the NVIC enables, disables, and checks for interrupts. It also clears pending interrupts in the CPU.

#### System Control Block

The SCB is also part of the CPU, and it provides system implementation information and system control. During the execution of the mpsl\_init() and mpsl\_uninit() functions, the SCB accesses only one register. A bit can be set to either cause all interrupts and events to wake the processor, or only to restrict this action to the enabled interrupt and events.

#### **Assembler Function Calls**

Some parts of the MPSL library include direct references to assembler functions for the CPU core. Since they cannot run as they are on the host computer, they also need to be considered inside the virtual prototype. During the MPSL initialization, assembler calls handle system interrupts, perform wait-for-event instructions, and no-operation instructions.

#### **Memory Accesses**

Certain parts of the code present in the mpsl\_init() and mpsl\_uninit() routines attempt to access values by dereferencing a pointer from a fixed address. These pieces of code are not able to execute in the host PC as they are. The virtual prototype needs to somehow take care of these accesses, given the absence of a device from Nordic Semiconductor. Luckily, normal accesses to specific peripherals can replace them, or in some cases, they can be ignored by the implementation since they are not relevant to run the two initialization routines of interest.

## 2.3 Virtual Prototyping

There are many definitions for virtual prototype both in literature and in industry. They usually differ in aspects like the difference between a virtual prototype and a digital mock-up, the functions of a virtual prototype, the fact that a virtual prototype should include human-product interaction or not, among others. Considering all these factors, [4] provides the following definition: *"Virtual prototype, or digital mock-up, is a computer simulation of a physical product that can be presented, analyzed, and tested from concerned product life-cycle aspects such as design/engineering, manufacturing, service, and recycling as if on a real physical model. The construction and testing of a virtual prototype is called virtual prototyping (VP)".*

In terms of hardware design, a virtual prototype is a high-speed functional software model of physical hardware. This system model often describes the system at a higher abstraction level while keeping the same functionality as the hardware. The most significant benefit of virtual prototypes is that they simplify the hardware design space exploration and allow concurrent hardware and software development. All this ends up saving time to market and resources, finding and fixing bugs earlier, allowing good test coverage, and even improving teamwork between hardware engineers, software developers, and testers [1]. There are different opinions about the use of hardware, virtual or hybrid prototypes in the SoC design flow. However, most of them agree that given the complexity of modern designs and market demands, the integration of virtual prototypes into the design flow is a growing need [5].

#### 2.3.1 Virtual Prototypes for Embedded Software Development

Virtual prototypes have a broad range of applications [6]. They can be used to develop high-level models that can be synthesized directly into hardware when written using specific guidelines. These models could also find use in verification activities. A virtual prototype can be used as a golden reference to verify an equivalent piece of RTL. A test can apply identical stimuli to both the prototype and the RTL, to later compare their response. System architects could also use prototypes to perform design space exploration. Take the example of an engineer who is trying to evaluate different RAM technologies for a particular design. The engineer could have a virtual prototype of a complete system in which he or she can add and remove different RAM models, measure their performance, and make a decision based on the results. All this without the need of having any physical hardware component. In general, the use of virtual prototypes can reduce development time, get products to the market faster, and deliver better products. This can result in great economic benefits as shown in an example case study depicted in Figure 2.6 [1].

Figure 2.6: Net profit from a real case study of the use of virtual prototypes

One of the most important applications for these models is early software development. The amount of software that engineers can develop and test before a device is out of the factory is usually limited. Engineers may develop some software components in advance, but the fact that specific information on the physical chip is not yet available can become a limitation. Testing can also start only after the device has left the factory. Software development and testing is not an easy task. Therefore once the device is ready, it takes several weeks or months to deliver a functional version of a software stack. If software developers could have a model of the SoC that is accurate enough to allow them to run the software just as it would on the physical device, the development and testing could be done much earlier in the design flow.

A virtual prototype could precisely serve this purpose. A model of the SoC does not need to be cycle-accurate to be able to run the software. Many details of the internals of the design can be abstracted to produce a functional model that fulfils the purpose of executing the software. There are many ways to develop these models. However, SystemC is the IEEE standard and the most popular approach. The SystemC standard also includes information regarding guidelines on how to develop models for this specific purpose.

## 2.4 SystemC Library Core

#### 2.4.1 Origins of SystemC

In the past, there have been efforts to find an electronic system-level (ESL) design language that can be suited for both hardware and software high-level descriptions [7]. Attempts to develop an entirely new language like Rosetta [8] or SuperLog [9] have been made. Other attempts have tried to extend VHDL or Verilog without big success. Considering that the biggest component of modern systems is software, C/C++ based approaches have proven to be the most promising ones. It is easier to adapt C to make it work for hardware designs, and in most cases, hardware designers already know how to use the language.

SystemC was born as an effort to find a standard ESL design language. It was developed in 1999 by the Open SystemC Initiative (OSCI), and it became an IEEE standard [10] in 2006. It is a system design and modelling language based on C++. In the strictest sense, SystemC is not a language itself but a C++ class library. SystemC finds use in industry for the development of hardware blocks at various levels of abstraction, architectural exploration, development of virtual prototypes for hardware/software co-design, verification, and even high-level synthesis.

#### 2.4.2 Virtual Prototyping with SystemC

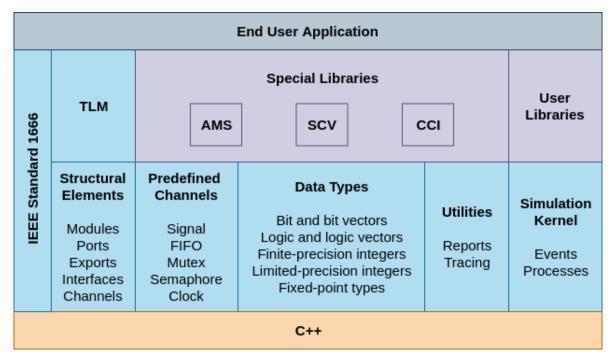

As mentioned, SystemC is no more than a C++ class library. SystemC focuses on modelling both hardware and software using C++. Since C++ already covers most of the software issues, SystemC focus is more on the side of the non-software issues. As depicted in Figure 2.7, the SystemC library sits on top of C++. It consists of a set of structural elements, predefined channels, data types, utilities, and an event-driven simulation kernel. One important component of the SystemC library is TLM, which stands for Transaction-Level Modeling. TLM and its components are the ones that make ESL design practical by focusing on communication-centric high-level modelling. On top of the SystemC core, there are special libraries like the Analog/Mixed-Signal (AMS), SystemC Verification (SCV), and the Configuration, Control and Inspection (CCI) library. For detailed information about SystemC refer to [11].

Figure 2.7: Architecture of the SystemC library

#### 2.4.3 Overview of the SystemC Components

#### **Structural Elements**

In SystemC, hardware or software design components are encapsulated as modules. A module is no more than a C++ class definition. Therefore, it is possible to use a regular class or the sc\_module macro to declare one. Every module must, at least, include a constructor that is in charge of performing SystemC specific setup tasks. Listing 2.2 shows a module that describes an OR gate. First, the model includes the systemc.h library and uses the sc\_module macro for the module declaration. Sc\_in and sc\_out declare input and output ports of type sc\_bit, which is a SystemC specific data type. A process describes the model behaviour, which in this case, is a simple OR operation between both inputs. Finally, the sc\_ctor macro is in charge of the constructor creation. This constructor registers the process in the SystemC specific using the sc\_method macro and, in this case, defines a sensitivity list for the SystemC process.

```

#include "systemc.h"

3 SC_MODULE(or_gate) {

sc_in<sc_bit> a;

4

sc_in<sc_bit> b;

5

sc_out<sc_bit> c;

6

void prc_or_gate() {

8

c = a | b;

9

}

10

11

SC_CTOR(or_gate) {

12

SC_METHOD(prc_or_gate);

13

sensitive << a << b;</pre>

14

}

16 };

```

Listing 2.2: SystemC description of a 2-input OR gate

Ports, exports, interfaces, and channels are ways to achieve communication in SystemC. Ports are bound to communication channels, and they can interface modules. In VHDL and Verilog, signals are the ones in charge of communication. Nevertheless, in SystemC, a signal is just a particular case of a channel. Channels are, in general, containers of communication protocols and synchronization events. They sit on top of interfaces that define a set of pure virtual methods that channels must implement. This feature enables to implement modules that are independent of the implementation details of the communication channel. For example, two different channels can describe a fast and a slow memory protocol using the same interface. As long as the system's modules communicate using the same interface, the implementation details of these protocols are not relevant, and they can easily switch. Exports are specific types of ports that work as a pointer to a channel inside another module.

#### **Predefined Channels**

SystemC also includes several predefined channels known as primitive channels. Among others, these channels include sc\_signal, sc\_fifo, sc\_mutex, and sc\_semaphore. The predefined channel sc\_signal provides simple write and read methods that generate events only when the signal changes its value. A channel that behaves like a FIFO can use sc\_fifo which provides methods for blocking and non-blocking read and write operations. It also has methods to return the number of busy and free elements. Access to shared resources is possible using primitive channels like sc\_mutex or sc\_semaphore. The fist provides methods to lock or unlock a resource while the second provides methods to wait, signal, or get the semaphore value.

#### **Data Types**

C++ does not provide a wide variety of data types that digital hardware requires. SystemC can provide data types that support arbitrary bit widths, digital representations such as tri-state or unknown, and special types for integers, floating-point numbers, literals, and strings. SystemC also provides methods to operate over these data types such as bit selection, range selection, conversions, testing, and bit reduction.

#### Utilities

Reports and error handling are essential components of simulations. SystemC provides an error report system that simplifies this task. Messages have different classifications, which include sc\_info, sc\_warning, sc\_error, and sc\_fatal. Also, every type of message can trigger actions like writing information into a log file, displaying the message on the screen, and stopping the simulation. The SystemC library even allows performing signal tracing for debugging purposes. There is no built-in graphic viewer in SystemC. However, it is possible to copy values into a VCD file that is compatible with most waveform viewers.

#### **Event-driven Simulation Kernel**

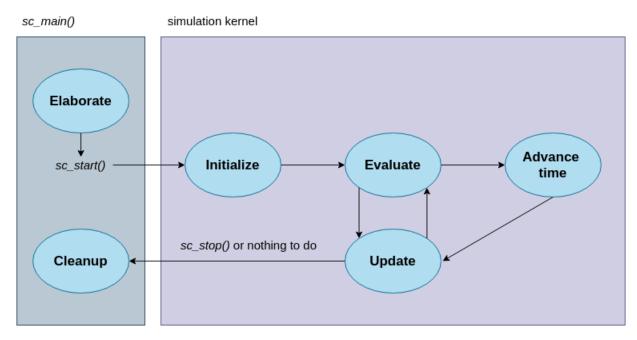

Concurrency is a fundamental part of SystemC simulations. SystemC uses an event-driven simulation kernel to model this concurrency. This kernel uses non-preemptive simulation processes, which can be defined either as methods, as shown in line 13 of Listing 2.2 or as threads using the sc\_thread macro. Figure 2.8 shows a simplified model of the simulation kernel.

Figure 2.8: Simplified SystemC simulation kernel

A SystemC simulation can be divided into six stages:

- Elaborate: components are instantiated and connected to create a model ready for simulation. Process registration happens here. A call to sc\_start invokes the simulation kernel and moves to the next stage.

- 2. Initialize: processes are identified and placed in a runnable or waiting state.

- 3. **Evaluate:** all the processes marked as runnable execute successively and in an undefined order until they hit a wait statement or return. During execution, processes can perform update requests, which are noted by the scheduler. A wait statement tells the scheduler that a process should run later.

- 4. **Update:** here the update requests are performed. The scheduler marks a process as runnable if it is sensitive to the performed updates and goes again into the evaluation phase. When there are no runnable processes, the simulation advances in time.

- 5. Advance time: simulation time moves forward and processes marked as runnable execute in the evaluate stage. If there are no more processes to run, the scheduler moves into the cleanup stage. The cleanup stage is also scheduled next if a process has stopped simulation calling sc\_stop or a timeout occurs.

- 6. Cleanup: simulation is over, and necessary cleanup routines are performed.

### 2.5 System C and TLM

#### 2.5.1 TLM Concept

As mentioned earlier in this chapter, TLM and its components make ESL design practical. TLM is a transaction-based modeling approach in which communication details are independent of the implementation details. It is more important what data moves to and from which locations than the protocol used for the data transfer. Cycle accurate simulations, like RTL simulations, consider all the events on all pins. Therefore, they are usually very slow. TLM makes use of transactions, which represent data transfers, to simulate only the relevant events. This concept

makes TLM simulations considerably faster than cycle-accurate simulations. TLM use cases cover software development, software performance analysis, architectural analysis, and hardware verification.

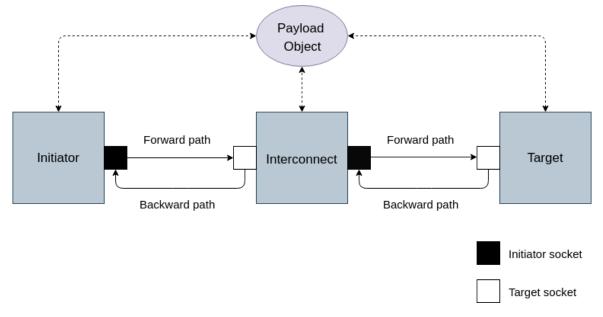

#### 2.5.2 Overview of TLM 2.0

TLM 2.0 [12] is the transaction-level modeling standard for SystemC. Its main focus is the modeling of systems based on memory-mapped busses. It provides a standard API for both blocking and non-blocking transports as well as a standard payload object. TLM models are written using initiators, interconnects, and targets. These modules act over a generic payload object, which includes typical attributes of memory-mapped buses. This payload object also enables the use of extensions to implement more complex communication schemes. The initiator is in charge of creating new transactions, the target executes requests and sends back responses, and the interconnect routes transaction objects between initiators and targets. Communication employs function calls that pass a reference to a single transaction object along the backward and forward paths, as shown in Figure 2.9. Targets must implement the methods defined by the forward path interface, while initiators must implement the backward path interface methods.

For example, to model a CPU read request from memory, a transaction can involve a CPU acting as a initiator, a bus as the interconnect and a memory device as a target. The CPU will set the payload object by specifying parameters like the action (read), and the memory location that wants to be accessed. It can use the forward path to give control of the transaction to the interconnect which modifies the address of the payload object to route the read request to the correct memory block. The target will read the data and place it in the data field of the payload object which can be now accessed by the CPU.

Figure 2.9: TLM components

# 2.5.3 TLM 2.0 Coding Styles

#### **Loosely-Timed TLM**

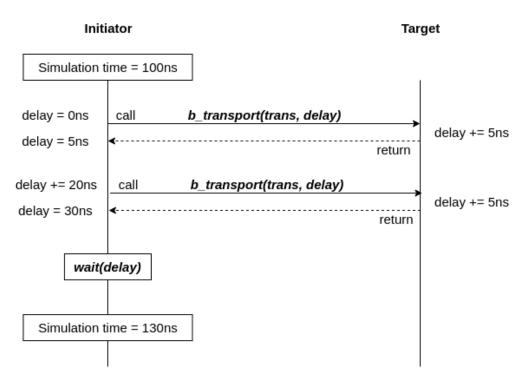

Loosely-Timed (LT) TLM uses a single-phase blocking API and finds applications in software development and software performance analysis. This blocking API associates only two points in time with a transaction; these are the blocking transport function call and return. This mechanism only uses the forward path from the initiator to the target. The b\_transport method takes a reference to a generic payload object and a timing annotation as arguments. The idea of the timing annotation is to model the behavior of a receiver getting the information with a specific delay. A diagram explaining a blocking transport message sequence is shown in Figure 2.10. TLM LT also supports temporal decoupling. Individual processes that use temporal decoupling can run ahead with no progress in the simulation time until they execute for a specific time slice known as quantum or until they reach a synchronization point. This technique reduces the context switches between processes, accelerating the simulation time.

Figure 2.10: Example of a message sequence in TLM LT

#### **Approximately Timed TLM**

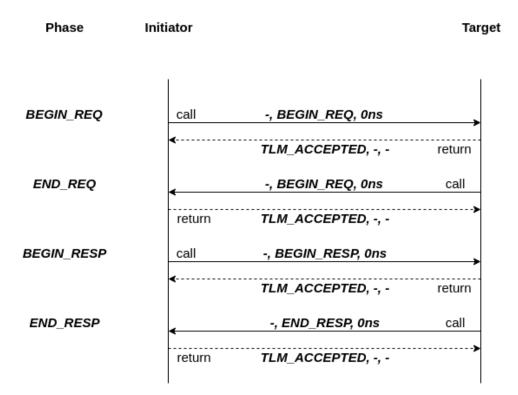

Approximately-Timed (AT) TLM uses a multi-phase non-blocking API and is mostly used for architectural analysis and hardware verification. For the base protocol case, a transaction involves exactly four timing points. These points represent the beginning and end of a request or a response. Since TLM AT needs accurate timing, it runs in lockstep with the simulation time, and it cannot make use of temporal decoupling. In this coding style, every interaction has a delay, representing data transfer times and the latency of the target. The characteristics of the non-blocking API facilitate the modeling of pipelined transactions. The non-blocking transport uses both the forward and the backward communication paths; each of these paths has its own interface. In addition to the payload object reference and timing annotation, a phase indicating the state of the transaction must be passed as a parameter. Calling a non-blocking function will return a status value representing the state of the transaction. Figure 2.11 shows a diagram that illustrates the non-blocking base protocol. In addition to this four-phase handshake protocol, the base protocol can terminate transactions sooner and also offers the possibility of implementing specific communication protocols by adding further timing points.

Figure 2.11: Example of a message sequence in TLM AT

## 2.5.4 Direct Memory Interface and Debug Transport Interface

Besides the blocking and non-blocking transport APIs, the forward and the backward interfaces provide methods to grant direct access and debug access to a memory block. Direct Memory Interface (DMI) is widely used in TLM AT, and it provides a considerable speedup in simulation time. When DMI is active, an initiator can bypass the interconnect and access the memory directly. It uses both a forward and a backward path interface. The debug transport interface is, as the name implies, for debug proposes. It provides the possibility of accessing memory like a regular transaction but free of delays and the overhead that regular transactions posses. This interface only uses the forward interface.

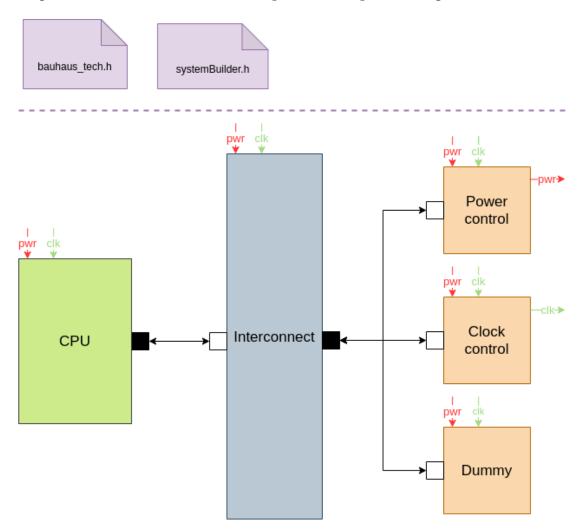

# 2.6 Bauhaus: Nordic Semiconductor's Generic Virtual Prototype

Bauhaus is a proof of concept and experimentation testbench for modelling Nordic Semiconductor's devices with SystemC. It serves as a framework under which more complex systems can be developed. These are some of its most important features:

- **CPU:** many virtual prototypes use an instruction set simulator (ISS) and a specific processor model to execute each instruction just like a physical processor does. However, the CPU model in Bauhaus does not intend to work this way to keep the system simple and generic. Instead, the CPU model implements only functions to write and read from registers in specific memory addresses. The CPU module points to a software class that holds the software to be executed in the CPU. This software will then execute as any other software in the host PC but will need to use the read or write functions when interacting with the virtual prototype's elements.

- **Interconnect:** the Bauhaus model also comes with an interconnect element. This module is in charge of receiving the transactions created in the CPU and routing them to the correct address so that the CPU can interact with other peripherals.

- **Dummy IP:** the virtual prototype lacks any peripheral implementation. However, it has a dummy module that can serve as a base for other peripherals. This module has no particular functionality, and it only logs an event every time the CPU writes to it.

- **System Builder:** one of the most important features of Bauhaus is the system build automation. It possesses functions to add a CPU element, an interconnect, and peripherals, respectively. It also has a system build function that binds the initiator ports of the CPU to the interconnect's target ports, as well as the initiator ports of the interconnect to each peripheral's target ports. This functionality allows having a generic interconnect which can hold an arbitrary number of peripherals and also automates and simplifies the binding process in the top-level module of the system.

- Other features: the Bauhaus virtual prototype works on top of Nordic Semiconductor's library for SystemC development. The library offers a power control module that can switch the system to different power modes to which each module can react. It also offers a clock control module that can offer different clock frequencies to the system and can provide reset events. Bauhaus also offers a specific header file to set technology-specific parameters, including timing and power. Some files can be modified to set different timing and power parameters like clock default period, startup time, power-off time, power modes, power transition times, among others.

- A diagram of Bauhaus with its main components is depicted in Figure 2.12.

Figure 2.12: Components of the Bauhaus generic virtual prototype

# **Chapter 3**

# **Methods**

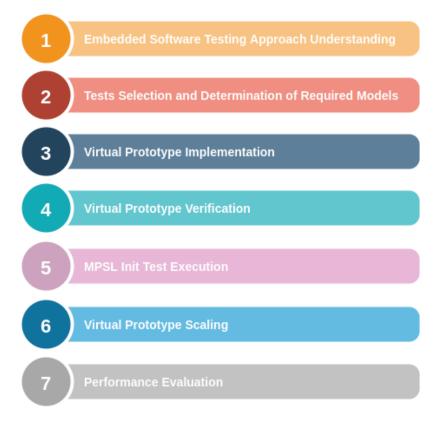

The goal of this thesis is to develop a virtual prototype that can run a subset of the MPSL target tests and explore the potential benefits of this approach. In order to achieve that goal, the process depicted in Figure 3.1 was followed.

The first step of this project involved getting familiar with the embedded software testing approach. Understanding MPSL tests was necessary to provide a baseline to evaluate the final implementation. The following step involved selecting a simple test to focus on since targeting to cover all tests is out of the scope of this thesis. Selecting one simple test also helped determine precisely which hardware components needed to be modelled by inspecting the code and extracting the hardware that is accessed by this specific test. After this was decided, the models were developed in order to build a functional virtual prototype based on the test requirements. Once the virtual prototype was complete, each of its components, as well as the system as a whole, had to be verified in order to make sure its behaviour matched the specifications. When the system was fully verified, it was possible to interface the virtual prototype with the MPSL software to execute the MPSL Init test. Once this test could execute successfully on top of the virtual prototype, the system was scaled to execute two more tests and demonstrate how it is possible to expand the virtual prototype to cover more tests. As the final step, the performance of the virtual prototyping approach was measured and compared against the baseline of the current approach using development boards.

# 3.1 Embedded Software Testing Approach Understanding

In order to get a clear idea of how the virtual prototype would fit the current testing framework, it was necessary to study the relationship between the software stack source files, the tests, and the parts of the code dedicated to interact with the hardware. After examining the code of several tests, it was noticed that the software under test usually does not access the hardware directly. However, instead, it uses dedicated files that are in charge of most of the hardware interactions. This set of files is known as the hardware access layer. This layer holds some logic but is mostly surrounded by register accesses to peripherals, which are the primary way software can interact with the hardware elements in the SoC. Other hardware interactions include the manipulation of CPU registers, interrupt controllers, assembly language instructions, and even memory accesses to fixed addresses. Identifying these hardware interactions was essential to define what needed to be modelled.

It was important not only to understand the purpose and dynamics of the target tests but also to execute them just like the software team does. This execution would allow defining a baseline for future comparison between the implementation using a virtual prototype and the current approach. Running the tests on the development boards is not a plug and play process. Since there are hundreds of tests, the process to build, compile, and flash the software stack is quite complex. For this reason, there is a complex framework in charge of automating all this process. In order to run target tests on the development boards, it was necessary to set up a virtual environment running Linux. Inside this environment, it was required to run a docker container holding the packages and dependencies for the tests. It was also necessary to share the USB control between the host, virtual machine, and docker container. Once this was all set, it was possible to run target tests on physical boards and use these executions as a reference for the upcoming implementation.

# 3.2 Tests Selection and Determination of Required Models

Given the fact that there is a significant number of tests and also because different tests access different hardware components, it was unrealistic for the scope of the thesis to implement a virtual prototype capable of running all the tests. Therefore, it was necessary to select a test or a subset of tests that are feasible to run on a virtual prototype as a proof of concept. One of the goals of this proof of concept is to provide a prototype that can easily be scaled in case there are promising results. It was noticed by inspecting the tests, that all of them share a similar structure in which they use the same initialization routines. Between these routines, the tests usually exercise some specific behaviour like returning a temperature value, triggering a couple of timers, among others. The MPSL Init test was selected as the test to be run on the virtual prototype. It employs the initialization functions, and the main test consists of checking flags in the interrupt controller. The execution of a single test may not seem significant, considering there is a large number of tests in the MSPL library. However, if this test runs successfully, it is possible to extend this idea to all the other tests since they share most of the code in these initialization routines. Other tests would require small tweaks and system additions to run. Once the MPSL Init test was selected as a candidate to run on top of the virtual prototype, it was necessary to define which hardware components are accessed by this test. A single test usually deals only with some parts of the SoC. Clearly defining these interactions enables focusing the development for only these components. This avoids spending time on hardware models that are not relevant for the moment. When determining the hardware to model, it was necessary to go through each function called during the test. Each line of code was inspected in order to find any register access to a peripheral, CPU, references to the interrupt controller, assembly instructions, or memory accesses. Once this was performed, it was possible to list all the hardware references along with the specific functionalities exercised in each component. There are hardware components that only require access to a couple of registers. Therefore their model should be relatively simple since all the behaviour related to the rest of the registers can be ignored. On the other hand, others access many different registers, requiring a more complex model.

# 3.3 Virtual Prototype Implementation

Having decided which hardware components needed to be modelled and how complex each model should be, it was possible to start with the models' development. Before doing so, it was necessary to get familiar with SystemC and how hardware models can be written using this C++ library. After covering the basics of SystemC and experimenting with simple models, the experimental virtual prototype from Nordic Semiconductor, Bauhaus, was chosen as a base for developing the models and final prototype. Since two simultaneous projects were working on writing the system models, a peripheral template was developed to establish a standard modelling style for all the peripherals. Once the template was ready, each of the peripheral models was developed on top of it, CPU register accesses and interrupt handling were covered, as well as assembly calls and memory accesses. When all the components were separately modelled, they were put together into a complete system that constitutes the virtual prototype over which the target tests can execute. This thesis focused on modelling the RADIO, TEMP, RTC, and TIMER peripherals as well as the SCB in the CPU, the assembly function calls, and the direct memory accesses.

## 3.3.1 Bauhaus as a Base for the Virtual Prototype

Before developing the hardware components models, it was discussed whether to start the virtual prototype from scratch or use an existing virtual prototype as a base. Since Nordic Semiconductor already made efforts into developing a generic virtual prototype for SystemC experimentation, this was an excellent place to start looking. After studying the prototype and running simple tests, it was determined that Bauhaus provided a solid base to build the desired system. It already contemplates a simple CPU model that can be scaled up to the needs of the project, an automated interconnect element and a lack of peripherals. This last characteristic is not a problem since one of the main activities of this thesis is peripherals model development. These features make Bauhaus a perfect base for the virtual prototype. The use of Bauhaus represented considerable time savings by avoiding activities related to the virtual prototype framework, which, in the end, are necessary for the system to work correctly but not relevant for this thesis.

# 3.3.2 Peripheral Template

A peripheral template was created to standardize the development of the peripheral models. A simplified version of the peripheral template header file is shown in Listing 3.1. The main objective of this template is to provide all the common infrastructure around the model of a peripheral so that it is necessary only to include peripheral specific information like registers and functions that implement the peripheral behaviour. Another motivation for this was to standardize the development of the models for the two projects involved in this work. The use of this peripheral template reduced the development time of the peripheral models significantly. It also made it easier to integrate and understand models written by others.

```

1 #include "systemc.h"

2 #include "tlm.h"

3 #include "n_ip_apb.h"

4 // Define here the register names

5 #define DUMMY_ADDR_MASK OxFFF

6 #define DR

0x000

7 . . .

8 struct nrf_dummy : Nip_Apb{

public:

9

nrf_dummy(sc_module_name name_, int ahb_base_addr);

10

sc_signal <bool > pwr_sig;

// Define here a struct for the registers

struct {

14

uint32_t dummy_DR;

15

...} regs;

16

void b_transport(tlm::tlm_generic_payload &payload, sc_time &delay);

18

unsigned int transport_dbg(tlm::tlm_generic_payload& gp);

19

20

// If needed implement functions to handle power and reset

void power_domain_handler(); void reset_handler();

22

23

void set(...); void clr(...); bool isSet(...); bool isClr(...);

24

25

private:

26

// Placeholder for peripheral functionalities

27

void dummy_thread(); void dummy_function();

28

29

// Implement actions when writing or reading to a register if needed

30

virtual void

busWrite(uint32_t uaddr, uint32_t wdata);

31

uint32_t

busRead(uint32_t uaddr);

32

<sub>33</sub> };

```

Listing 3.1: Simplified peripheral template header file

The main features of the peripheral template are (code lines refer to Listing 3.1):

- Incorporates all the dependencies to attach any peripheral to Bauhaus (line 3).

- Provides a reset and a power domain handler to manage reset events and reactions to different power states in the system if needed (lines 11 and 22).

- Provides a section for register address definition and a predefined data structure to hold each register. The user only needs to provide register names and addresses for the desired peripheral (lines 5-6 and 14-16).

- Abstracts TLM communication details, so the only thing to worry about is the model itself. The blocking transport and debug transport, along with all the generic payload handling is already covered. To write the model, it is only necessary to associate behaviours to register accesses in the template. (lines 18-19 and 31-32).

- Provides functions to set, clear, check if set, and check if clear for specific register bits to simplify register handling (line 24).

## 3.3.3 2.4 GHz Radio Peripheral Model

The radio peripheral itself is substantially complex since it involves packet assembly and disassembly, data whitening and dewhitening, cyclic redundancy checks, and some other complex processes. However, during the execution of the mpsl\_init() and mpsl\_uinit() functions, it is barely used. Only one register out of more than 60 registers of the peripheral is accessed. Therefore the model for this peripheral is greatly simplified. The register that is accessed is the POWER register, which is in charge of turning on and off the peripheral. The peripheral model is written to log simulation information when the POWER register is accessed. When the least significant bit (LSB) of the register is set to 1, it informs that the radio peripheral is on, and when it is 0, it informs that it is off. Since no other functionality is required from the radio peripheral at this point, this implementation is enough to run the MPSL Init test.

## 3.3.4 Temperature Sensor Peripheral Model

Table 3.1 specifies the registers that were modelled for the TEMP peripheral along with the corresponding register description.

| Register       | Description                   |

|----------------|-------------------------------|

| TASKS_START    | Start temperature measurement |

| TASKS_STOP     | Stop temperature measurement  |

| EVENTS_DATARDY | Measurement is complete       |

| INTENSET       | Enable interrupt              |

| INTENCLR       | Disable interrupt             |

| ТЕМР           | Temperature value             |

Table 3.1: Register accesses for the TEMP peripheral

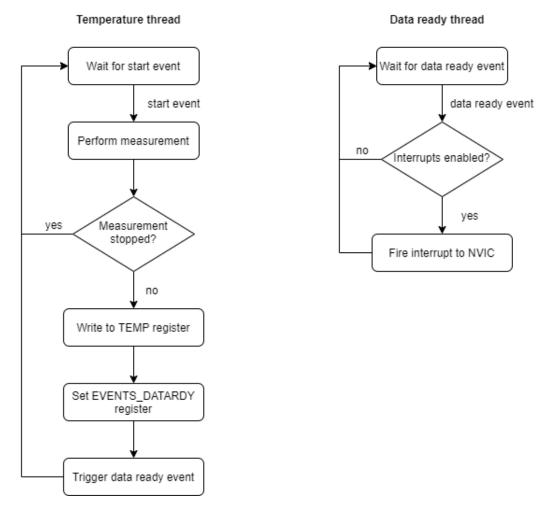

The peripheral model is based on two threads that run in parallel thanks to the SystemC simulation kernel. The behaviour of the temperature sensor peripheral model is shown in Figure 3.2. The first thread is in charge of performing the temperature measurement. A start event is triggered when a logic 1 is written to the LSB of the TASK\_START register. The thread waits for the start measurement event to be triggered and then performs the temperature measurement, which in this case, is simulated by just waiting for some predefined amount of time. In case the measurement was stopped while it was being carried out, the thread waits for the next start event. If not, it writes the temperature value to the TEMP register, sets the EVENTS\_DATARDY register, and triggers the data ready event. In the case of the model, the temperature value is just a constant since this physical quantity cannot be obtained from the host CPU.

The second thread waits for the data ready event, which is triggered by the first thread when a temperature measurement is complete. When this event is triggered, the model checks if the interrupts have been enabled or not, in case they are, it forwards an interrupt to the NVIC in the CPU. Otherwise, it just waits for the next data ready event.

Figure 3.2: Behaviour of the TEMP peripheral model

## 3.3.5 Real-time Clock Peripheral Model

Table 3.1 specifies the registers that were modelled for the RTC peripheral along with the corresponding register description.

| Register            | Description                    |

|---------------------|--------------------------------|

| TASK_START          | Start the counter              |

| TASK_STOP           | Stop the counter               |

| TASKS_CLEAR         | Clear the counter              |

| EVENTS_COMPARE[0-2] | Compare event on CC[0-2] match |

| EVTENCLR            | Disable event routing          |

| INTENCLR            | Disable interrupt              |

| COUNTER             | Current counter value          |

| CC[0-2]             | Capture/Compare register 0-2   |

Table 3.2: Register accesses for the RTC peripheral

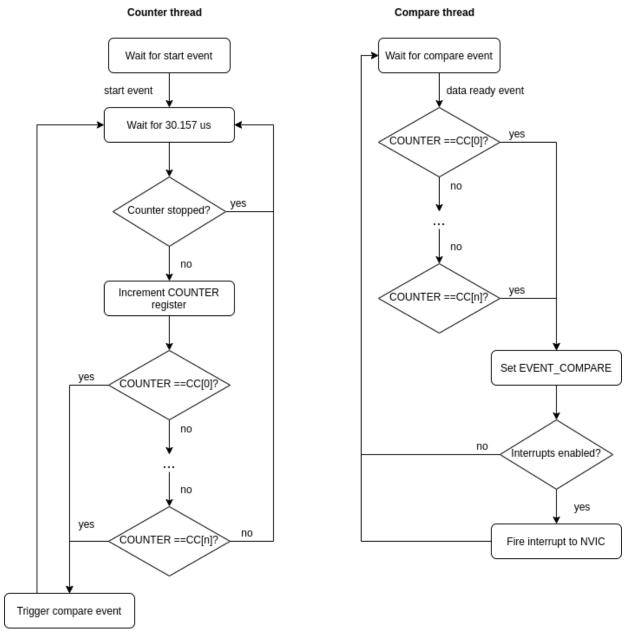

The RTC peripheral model behaviour is also based on two parallel threads, as shown in Figure 3.3. The counter thread waits for a start event, triggered when the LSB of the TASK\_START register has a logic 1. It waits for the clock period, which in this case, since the preescaler has a value of 0, is 30.157 us. If the counter was stopped in the meantime, it does not increase the COUNTER register. If it was not stopped, it increments the COUNTER register by one. Every time the counter is increased, the counter value is compared to each of the CC registers. In case the count equals the value in one or more of these registers, a compare event is triggered.

The other thread, the compare thread, waits for a compare event. When it is triggered, the COUNTER value is compared to each of the CC registers. When a match is found, the EVENT\_COMPARE register is set. In case interrupts have been enabled for that specific CC register, an interrupt is fired to the NVIC. If the interrupts are disabled, only the EVENT\_COMPARE is set, and the thread waits for the next compare event.

Figure 3.3: Behaviour of the RTC peripheral model

## 3.3.6 Timer Peripheral Model

Table 3.1 specifies the registers that were modelled for the TIMER peripheral along with the corresponding register description.

| Register            | Description                    |

|---------------------|--------------------------------|

| TASK_START          | Start the timer                |

| TASK_STOP           | Stop the timer                 |

| TASKS_CLEAR         | Clear the timer                |

| TASKS_SHUTDOWN      | Shut down the timer            |

| EVENTS_COMPARE[0-3] | Compare event on CC[0-3] match |

| INTENCLR            | Disable interrupt              |

| CC[0-3]             | Capture/Compare register 0-3   |

Table 3.3: Register accesses for the TIMER peripheral

The TIMER peripheral model shares most functionalities with the RTC model. For the purposes of this thesis, and in order to run the MPSL Init test, the TIMER and the RTC present only subtle differences in their models. The behaviour shown in Figure 3.3 applies for both. However, the TIMER peripheral does not have an accessible register with the counter value, therefore, for the TIMER model it is just presented as an internal variable. Also, the TIMER runs on the high-frequency clock in contrast to the RTC, which runs on the low-frequency one. This means the wait time between counts is much shorter, and in this case, since the preescaler value is also zero, there is a count every 62.5 ns instead of 30.157 us.

### 3.3.7 System Control Block

The SCB was implemented as a part of the CPU model. A structure that holds the SCB registers was created from which, during the MPSL Init test, only one register is accessed. This register is the System Control Register (SCR) which can configure all interrupts and events to wake up the processor or to only restrict this action to the ones enabled. Two generic functions to read and write to CPU registers were developed so that these can be used not only for this register but also for the other CPU registers in case the functionality of the model needs to be scaled. When the software needs to either set the SCR register in the SCB or to read it, it can make use of these generic functions.

## 3.3.8 Assembly Function Calls

The assembly function calls were also implemented inside the CPU model. The idea is that the software running in the virtual prototype substitutes the assembly calls for the ones implemented in the CPU. The CPU functions that implement the assembly calls during the tests are summarized in Table 3.4. The \_\_NOP() assembly instruction is the most straightforward since as its name implies it does nothing. In the case of the \_\_WFE() call, since it is only used to enter the sleep mode while the low-frequency clock starts, there is no real need to model it, and it can also be used as a \_\_NOP(). This because the starting time of the low-frequency clock for the virtual clock model can be neglected. In the case of the \_\_enable\_irq() and \_\_disable\_irq() calls, they only need to take care of setting and clearing the PRIMASK register inside the CPU. The PRIMASK register prevents the activation of all exceptions with configurable priority in the CPU. Finally, the \_\_get\_PRIMASK() call is mapped to a function call that returns the value of the PRIMASK register.

Table 3.4: CPU functions that implement assembly function calls