ISBN 978-82-326-5046-0 (printed ver.) ISBN 978-82-326-5047-7 (electronic ver.) ISSN 1503-8181

**O** NTNU

**•** NTNU Norwegian University of Science and Technology

# Design and optimisation of an auxiliary power supply with medium-voltage isolation using

Ole Christian Baumann Spro

# Design and optimisation of an auxiliary power supply with medium-voltage isolation using GaN HEMTs

Thesis for the Degree of Philosophiae Doctor

Trondheim, November 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

© Ole Christian Baumann Spro

ISBN 978-82-326-5046-0 (printed ver.) ISBN 978-82-326-5047-7 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2020:350

Printed by NTNU Grafisk senter

# Abstract

This PhD thesis shows that compact and efficient converter systems can be obtained by leveraging the inherent characteristics of GaN HEMT devices. In the targeted application of an auxiliary power supply with medium-voltage isolation, the design, optimisation and experimental validation of the auxiliary power supply demonstrate that the high frequency characteristics of GaN HEMTs allow for high-efficiency even at multi-megahertz frequencies. The high operating frequency enables the use of coreless planar transformers with solid insulation that is sandwiched with PCB windings, where the insulation thickness is significantly increased while upholding the converter efficiency compared to the literature. Additionally, the design methodology of the transformer is modified to include the coupling capacitance of the transformer. This capacitance constitutes a highfrequency noise path and must be minimised in order to avoid affecting the operation of the main converter.

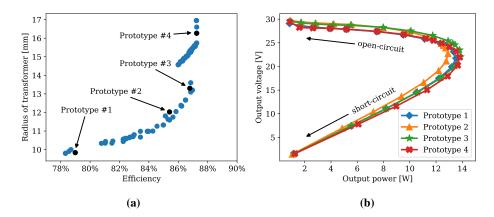

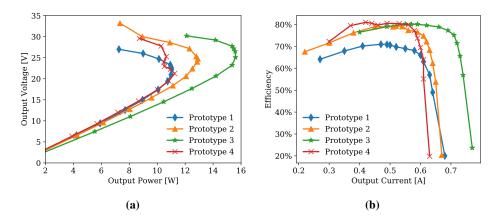

In this PhD work, an auxiliary power supply is designed based on a resonant topology operating at 6.78 MHz. The design methodology results in a compact rectifier with inherent output voltage regulation. Simulation-based design methodologies for both the converter topology and the isolation transformer are presented, followed by experimental validation. For the converter, the optimisation process uses a genetic algorithm. Designs are evaluated through 2D finite element analysis and SPICE simulations. Four prototypes were made from the identified Pareto front. These prototypes were able to transfer from 11 to 16 W with a measured peak efficiency of 81% and the output voltage regulation is experimentally validated. However, there is a discrepancy in simulated and measured inverter losses despite the effort to model the additional loss factors of GaN HEMTs, namely dynamic on-state resistance and  $C_{oss}$ -losses. Thus, these losses represent a hindrance for improving the efficiency of converters operating at high frequency. Consequently, virtual prototyping, which is more time- and material-efficient than design by prototyping, also becomes more challenging.

Finally, the thesis presents a design methodology for a compact, printed, highfrequency isolation transformer with medium-voltage isolation that can be used in the previously presented resonant converter. The methodology takes the coupling capacitance of the transformer into account. Additionally, possible field-grading methods are investigated with permittivity field-grading showing the most promise for the application. Experimental breakdown tests are performed according to IEC standards. Using printed windings allows for producing windings with higher accuracy and higher precision. Characterisation of the transformers shows low variation in transformer parameters from the simulated values. ii

# Acknowledgements

Looking back, I strongly believe that the support of our families builds the inner strength that we carry with us and can draw upon when needed. Their smiling eyes of love and expressions of how proud they are of our efforts stay with us for a lifetime.

My thoughts go, in particular, to my father, who passed away one early morning in August 2018 and thus did not get the chance to see me defend my PhD. Although unconsciously, my heritage weighed strongly on the path I have taken. Being the son of an engineer that graduated from NTH, Trondheim results in the likelihood that I would be one too. Not because he would try to influence my choice, but because of how he shared his own history and interests with my brother and me. The only exception was his ultimatum to both of us that we should go to high school and obtain our *examen artium* because "our heads were too good to go to waste". I guess he wasn't wrong.

If he was here for the occasion, he would also have gotten the chance to meet some of the people who helped me along the way and made this path possible. The availability and informal tone of professor Dimosthenis 'Dimos' Peftitsis made him a great support in many times. His technical interest and friendly nature has led us to have countless discussions, both technical and social, in the office as often as elsewhere. Also, I thank professors Ole-Morten Midtgård and Tore Undeland for believing in my capabilities and selecting me for this position. They have supported my initiatives and, at times, accepted my stubbornness. Moreover, the technical staff at the department have been most helpful through all of my experiments.

As my exchange experience, I got to spend three highly memorable months at G2Elab in Grenoble, France with professor Pierre Lefranc and his group. In contrast to the stereotypical view of researchers, Pierre looks more like a rock star, driving a motorcycle in his leather jacket to the office. But his dedication, attention to detail and presence in the moment make him an excellent collaboration partner and researcher. This stay marked a turn in my research and, consequentially, will likely follow the rest of my career. Additionally, the French *apero* is a great tool for improving work relations and quality of life in general.

During any PhD period, there are surely both good times and frustrating times. For the latter, missing results, short deadlines and experimental setups blowing up two weeks before the paper deadline were part of mine. For those frustrating times, it is crucial to be surrounded by people one can discuss with and vent to. Just remember to also share the good times with these same people. At times serving as unofficial supervisor and personal mentor, Gilbert Bergna-Diaz has been a great support during the PhD years. Other colleagues at SINTEF Energy Research, particularly Giuseppe Guidi and Andrzej Holdyk, have also been a great support in both good and frustrating times. Also, what is any workplace without office mates ... and coffee breaks? I had the pleasure of sharing time with many, but above all, Subhadra Tiwari, Andreas Giannakis and Santiago Sanchez made it into a friendly and witty atmosphere.

And to Mariève who supported me through all periods of this journey, with her love, her listening, and her constructive input. Also, taking more than her share on the home front, taking care of both me and Samuel. Samuel may not have put in any effort to accelerate my work, but I would not be without him. He adds a completely new dimension to life. His wonder, joy and curiosity about the world are traits to be desired by researchers. I will, to the extent of my capabilities, support and encourage him to observe and explore, while letting him form his own path... to engineering.

iv

# List of Abbreviations

| 2DEG                                                      | 2-dimensional electron gas                                                                                                                                                                                                                                       |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ССМ                                                       | Continuous-current mode                                                                                                                                                                                                                                          |

| CMCD                                                      | Current-mode class D (inverter)                                                                                                                                                                                                                                  |

| EMI                                                       | Electromagnetic interference                                                                                                                                                                                                                                     |

| ESR                                                       | Equivalent series resistance                                                                                                                                                                                                                                     |

| FEA                                                       | Finite element analysis                                                                                                                                                                                                                                          |

| FFT                                                       | Fast Fourier transform                                                                                                                                                                                                                                           |

| FHA                                                       | Fundamental harmonic approximation                                                                                                                                                                                                                               |

| FOM                                                       | Figure of merit                                                                                                                                                                                                                                                  |

| HEMT                                                      | High electron mobility transistor                                                                                                                                                                                                                                |

| IEC                                                       | International Electrotechnical Commission                                                                                                                                                                                                                        |

|                                                           |                                                                                                                                                                                                                                                                  |

| ISM                                                       | Industrial, scientific, and medical (radio bands)                                                                                                                                                                                                                |

| ISM<br>LVMOSFET                                           | Industrial, scientific, and medical (radio bands)<br>Low-voltage MOSFET                                                                                                                                                                                          |

|                                                           |                                                                                                                                                                                                                                                                  |

| LVMOSFET                                                  | Low-voltage MOSFET                                                                                                                                                                                                                                               |

| LVMOSFET<br>MOSFET                                        | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor                                                                                                                                                                                          |

| LVMOSFET<br>MOSFET<br>PCB                                 | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor<br>Printed circuit board                                                                                                                                                                 |

| LVMOSFET<br>MOSFET<br>PCB<br>PFC                          | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor<br>Printed circuit board<br>Power factor correction                                                                                                                                      |

| LVMOSFET<br>MOSFET<br>PCB<br>PFC<br>PTFE                  | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor<br>Printed circuit board<br>Power factor correction<br>Polytetraflouorethylene – also known as Teflon <sup>TM</sup>                                                                      |

| LVMOSFET<br>MOSFET<br>PCB<br>PFC<br>PTFE<br>SJ FET        | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor<br>Printed circuit board<br>Power factor correction<br>Polytetraflouorethylene – also known as Teflon <sup>TM</sup><br>Super-junction field effect transistor                            |

| LVMOSFET<br>MOSFET<br>PCB<br>PFC<br>PTFE<br>SJ FET<br>WPT | Low-voltage MOSFET<br>Metal oxide semiconductor field effect transistor<br>Printed circuit board<br>Power factor correction<br>Polytetraflouorethylene – also known as Teflon <sup>TM</sup><br>Super-junction field effect transistor<br>Wireless power transfer |

vi

# Contents

| 1 | Introduction 5                                        |          |                                                                       |    |  |

|---|-------------------------------------------------------|----------|-----------------------------------------------------------------------|----|--|

|   | 1.1                                                   | Backg    | round                                                                 | 5  |  |

|   | 1.2                                                   | Resear   | ch questions                                                          | 7  |  |

|   |                                                       | 1.2.1    | Scope and limitations                                                 | 8  |  |

|   |                                                       | 1.2.2    | Outline of the thesis                                                 | 9  |  |

|   |                                                       | 1.2.3    | Research contributions                                                | 9  |  |

|   | Refe                                                  | erences. |                                                                       | 11 |  |

| 2 | 2 Characteristics and application of GaN HEMT devices |          |                                                                       | 13 |  |

|   | 2.1                                                   | GaN n    | naterial and the HEMT device                                          | 14 |  |

|   |                                                       | 2.1.1    | Normally-on and normally-off device, and related gate struc-<br>tures | 16 |  |

|   | 2.2                                                   | Circuit  | t behaviour and device modelling                                      | 19 |  |

|   |                                                       | 2.2.1    | Forward conduction and blocking region                                | 20 |  |

|   |                                                       | 2.2.2    | Reverse current conduction                                            | 21 |  |

|   |                                                       | 2.2.3    | Parasitic capacitances and small signal model                         | 22 |  |

|   |                                                       | 2.2.4    | Dynamic on-state resistance, $\mathbf{R}_{\mathbf{DS,on}}$            | 23 |  |

|   |                                                       | 2.2.5    | Output capacitor hysteresis losses, $C_{OSS}$ losses                  | 26 |  |

|                | 2.3  | Identification of application areas utilising the qualities of GaN<br>HEMTs |                                                   |    |

|----------------|------|-----------------------------------------------------------------------------|---------------------------------------------------|----|

|                |      | 2.3.1                                                                       | Hard-switching versus soft-switching applications | 35 |

|                |      | 2.3.2                                                                       | Drop-in replacement                               | 35 |

|                |      | 2.3.3                                                                       | Changing circuit topology                         | 37 |

|                |      | 2.3.4                                                                       | High-frequency application                        | 38 |

|                | 2.4  | Conclu                                                                      | usion                                             | 39 |

|                | Refe | rences.                                                                     |                                                   | 41 |

| 3              | Reso | onant ci                                                                    | rcuit topologies for high-frequency application   | 49 |

|                | 3.1  | High-f                                                                      | requency resonant inverters                       | 51 |

|                |      | 3.1.1                                                                       | Class D and class DE inverters                    | 51 |

|                |      | 3.1.2                                                                       | Class E inverter                                  | 53 |

|                |      | 3.1.3                                                                       | Class EF and $\Phi_2$ inverter $\ldots$           | 54 |

|                |      | 3.1.4                                                                       | Comparison of inverter topologies                 | 55 |

|                | 3.2  | High-f                                                                      | requency resonant rectifiers                      | 57 |

|                |      | 3.2.1                                                                       | Class DE rectifier                                | 57 |

|                |      | 3.2.2                                                                       | Class E rectifier                                 | 59 |

|                |      | 3.2.3                                                                       | Comparison and discussion of rectifier topologies | 61 |

|                | 3.3  | Series-                                                                     | -L class E rectifier                              | 63 |

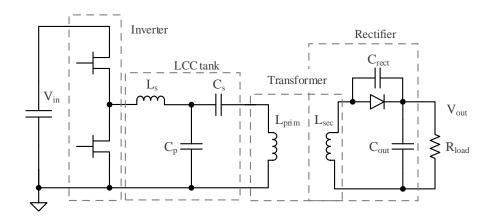

|                | 3.4  | Compl                                                                       | lete converter topology                           | 69 |

| 3.5 Conclusion |      | usion                                                                       | 73                                                |    |

|                | Refe | erences.                                                                    |                                                   | 74 |

| 4              | Aux  | iliary p                                                                    | ower supply with high isolation voltage           | 79 |

|                | 4.1  | Backg                                                                       | round                                             | 80 |

|                | 4.2  | Desigr                                                                      | a spects of the converter                         | 83 |

|                |      | 4.2.1                                                                       | Output voltage regulation                         | 85 |

|   |      | 4.2.2 Efficiency                                         | 87  |

|---|------|----------------------------------------------------------|-----|

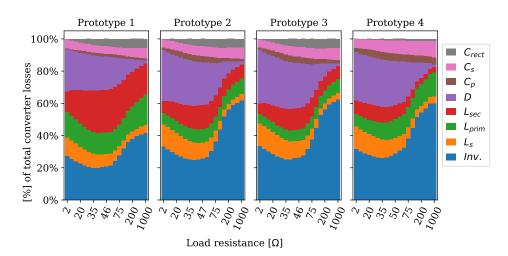

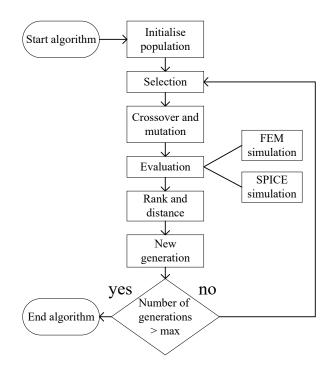

|   | 4.3  | Optimisation of the converter                            | 88  |

|   |      | 4.3.1 Genetic algorithm                                  | 90  |

|   |      | 4.3.2 Simulation results                                 | 91  |

|   | 4.4  | Experimental results                                     | 93  |

|   | 4.5  | Conclusion                                               | 96  |

|   | Refe | prences                                                  | 99  |

| 5 | Prin | ted planar transformer design for high-voltage isolation | 103 |

|   | 5.1  | Background                                               | 104 |

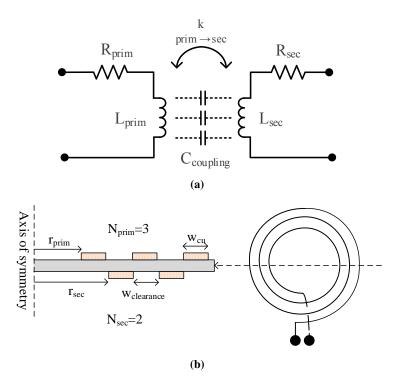

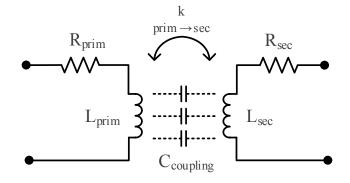

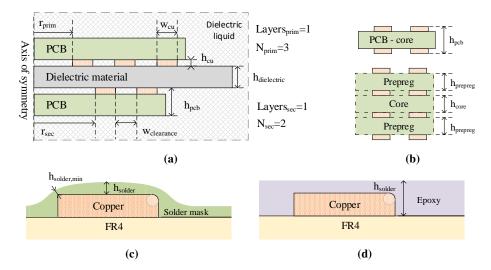

|   | 5.2  | Modelling of the transformer                             | 106 |

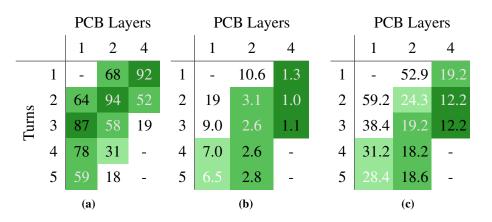

|   | 5.3  | Mapping of the design space                              | 107 |

|   | 5.4  | Investigations of dielectric simulations                 | 109 |

|   |      | 5.4.1 Impact of insulation thickness                     | 111 |

|   |      | 5.4.2 Field-grading techniques                           | 112 |

|   |      | 5.4.3 Transformer prototypes                             | 114 |

|   | 5.5  | Electrical characterisation                              | 116 |

|   | 5.6  | Breakdown voltage results                                | 118 |

|   | 5.7  | Other design aspects                                     | 124 |

|   | 5.8  | Conclusion                                               | 125 |

|   | Refe | erences                                                  | 127 |

| 6 | Con  | clusions 1                                               | 129 |

|   | 6.1  | Future work                                              | 131 |

|   | Refe | erences                                                  | 133 |

4 CONTENTS

# Chapter 1

# Introduction

# 1.1 Background

Based on the growing knowledge of the planet's biosphere and climate change, decarbonisation of the economy has become one of the major goals of global politics in the last few decades. This is achieved through the use of renewable energy sources, increased energy efficiency, and electrification of large societal sectors, e.g. transport and industry. Thre electrification and digitalisation of society is not possible without the use of power electronic converters. Moreover, the use of converters enables high-efficiency energy conversion, ensures grid stability, and controls power flow between sources and loads. High efficiency is achieved through the use of power electronic converters to optimise the operation point and switching loads on and off only when they are needed. Among the numerous technologies needed for this shift in society, medium-voltage grids, both DC and hybrid AC-DC grids, are considered to be an enabling technology for efficiency improvement in distribution grids, charging infrastructure, and industrial applications, as well as accelerating the integration of renewable energy sources and energy storage systems [1, 2, 3, 4, 6, 8, 9, 10, 12]. The most vital grid components in such grids are the power electronic converters.

Up until recently, state-of-the-art silicon-based converters have been the only alternative. However, Si devices have reached the theoretical limit of the material. Hence, to further increase efficiency and power density, new materials and device structures have to be explored. In this context, the manufacturers have been introducing new power semiconductor devices based on wide-bandgap materials, namely SiC and GaN. These materials exhibit characteristics that allow for improved performance compared to the Si counterparts, i.e. lower losses for the

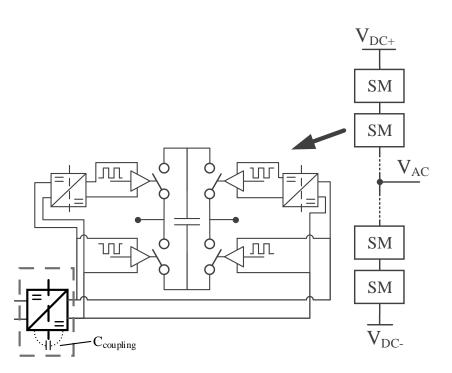

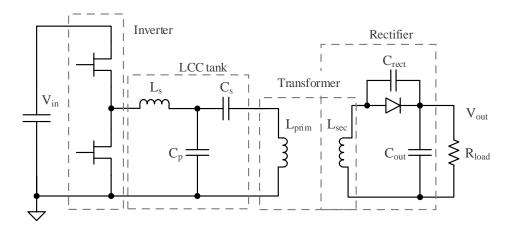

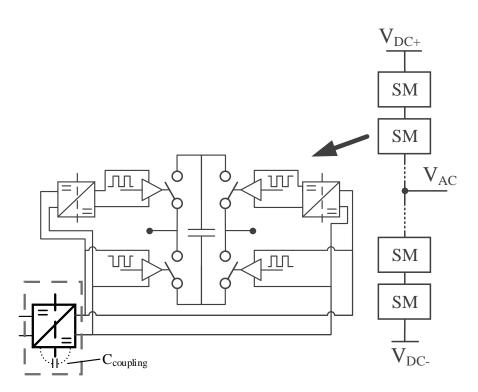

**Figure 1.1:** Phase.leg of a modular multilevel converter where a sub-module is fed by an auxiliary power supply connected to an external power source.

same rated voltage and current capability, improved performance at higher operating temperatures and higher power density due to the potential for increased switching frequency, albeit at a higher unit cost for the time being. In the last decade, GaN devices have shown increasing maturity and thus have been increasing their market share, going from around \$8 million in 2017 to an estimated well above \$50 million in 2020 [11]. The current device development indicates that SiC devices are targeting higher voltage and power levels while GaN devices cover lower voltage ranges, with an overlapping area at around 600 V [5, 11]. However, in terms of frequency, the roles are interchanged and GaN performs better at high frequencies. Current application areas for GaN devices are point-of-load converters, and power supplies for lidar and telecom, with expected near-future expansion to electric transport and wireless charging [11].

Modular multilevel converters (MMC) or series-connected switches in 2- or 3level converters are feasible topologies for medium-voltage converters. Regardless of the topology, these converters need auxiliary converters to supply gate drivers, sensors and control circuitry for individual power electronic switches or for whole converter modules [7]. Figure 1.1 shows the phase-leg of an MMC where one submodule is energised by an auxiliary power supply. The coupling capacitance over the isolation barrier is a possible source for electromagnetic interference (EMI) issues for the medium-voltage converter. High operating frequency could benefit the transformer design of the auxiliary power supply by decreasing the coupling capacitance. From the voltage, power, and frequency levels, GaN components rise as suitable candidates for this application.

## 1.2 Research questions

This work is part of the research project HiPPE<sup>1</sup> that was funded by the Norwegian Research Council. The objective of this research project was to advance the field of power electronics using wide-bandgap devices. For the project, the primary objective was defined as:

"to develop ancillary electronics and passive components needed for the efficient use of wide-bandgap devices in power electronics converters, as well as to implement prototypes of new converters based on the new devices and the ancillary systems and components developed in this project, ideally both for SiC and GaN devices."

In 2016, when the research questions were formulated, the technology and markets of GaN devices were different compared to today. Devices were only available from a few manufacturers with much smaller market share than today, and device reliability was largely unknown. A consequence of the high unit price was that other system costs had to be reduced or the system had to offer better performance than the state-of-the-art. Based on these aspects, the following research questions were formulated:

- Which application areas would benefit by exploiting the characteristics of GaN devices, resulting in increased performance over other semiconductor technologies?

- How can GaN devices be modelled so they can be used for design and optimisation processes?

- How should the topology and the other converter components, e.g. passives, be optimised to maximise the system benefits?

<sup>&</sup>lt;sup>1</sup>High Performance Power Electronics with Wide Bandgap Power Semiconductors for Industrial, Marine, Renewable Energy and Smart Grid Applications

### 1.2.1 Scope and limitations

This thesis aims to demonstrate that compact and efficient converter systems can be obtained by leveraging the GaN-device characteristics. The content covers the design, optimisation and experimental validation of an auxiliary power supply that consists of a dc-dc converter employing GaN HEMT devices and with a highfrequency isolation transformer that is rated for medium-voltage applications. As described in the presented background, auxiliary power supplies with high isolation voltage is an application that could potentially benefit from the inherent characteristics of GaN devices.

To successfully demonstrate the suitability of GaN devices for the targeted application, several objectives had to be set:

- Investigate a simulation model that can account for the behaviour of the GaN device dynamic on-state losses.

- Identify a circuit topology that is suitable for a low-power, high-frequency auxiliary power supply.

- Optimise the power supply based on SPICE simulation, followed by experimental validation.

- Design and optimise a compact transformer with medium-voltage isolation, followed by experimental validation.

The application use case is built around standard and expected voltage and power levels. For the input, the voltage is selected to be 48 V - a common dc-bus voltage level suitable for supplying auxiliary converter systems. Furthermore, the output voltage was set in the range of 20 to 25 V, which covers the expected drive voltages of the SiC MOSFETs that are used as the main switching component in the medium-voltage converter. Finally, the operating frequency is targeted to 6.78 MHz, the first available frequency in the ISM bands<sup>2</sup>. In many countries, emissions in these bands are allowed, which results in reduced EMI requirements for the design of the converter.

<sup>&</sup>lt;sup>2</sup>Radio bands that are intended for industrial, scientific and medical (ISM) purposes

### 1.2.2 Outline of the thesis

- **Chapter 1** introduces the thesis with a macro-view background and briefly presents the scope, outline and contributions of the thesis.

- **Chapter 2** presents an updated status of GaN device technology including historical, technological and application-oriented aspects.

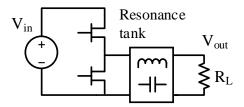

- **Chapter 3** analyses and justifies the choice of topology for the targeted application. The topology is a combination among several presented resonant inverter and rectifier topologies.

- **Chapter 4** presents the design, optimisation and experimental validation of an auxiliary power supply operating at multi-megahertz frequency.

- **Chapter 5** presents the design methodology for high-frequency printed planartransformer with high isolation voltage. Additionally, the results of high-voltage experimental breakdown testing and characterisation are presented.

- **Chapter 6** summarises and concludes the thesis and gives suggestions and directions for future work.

## 1.2.3 Research contributions

The contributions from this PhD thesis work are given in the beginning of each chapter. In summary, the main contributions of this PhD are:

- Demonstration of the feasibility of using simulation-based optimisation of a resonant converter employing GaN HEMTs.

- Design and demonstration of a class E rectifier that utilises the transformer self-inductance instead of the leakage inductance or an added discrete inductor which improves the power density.

- Design and experimental validation of a compact high-frequency transformer with high isolation voltage that uses PCB windings.

The scientific findings made during this PhD work have been published in two journal articles and four conference articles. These are listed in the 'List of Publications' found below. In addition, five other publications, with this author either as the first or second author, were published during the PhD period. These are listed under 'Other Publications'.

# List of Publications

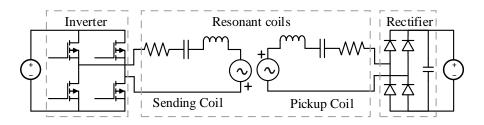

- [P1] Ole Christian Spro, Ole-Morten Midtgård, Tore Undeland and Giuseppe Guidi. 'Development of a Full Bridge GaN HEMT Converter for Inductive Power Transfer Application'. In: 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA). Nov. 2016, pp. 30–34. DOI: 10.1109/WiPDA.2016.7799905.

- [P2] Ole Christian Spro, Supratim Basu, Ibrahim Abuishmais, Ole-Morten Midtgård and Tore Undeland. 'Driving of a GaN Enhancement Mode HEMT Transistor with Zener Diode Protection for High Efficiency and Low EMI'. In: 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe). Sept. 2017, pp. 1–10. DOI: 10.23919/EPE17ECCEEurope.2017.8099200.

- [P3] Ole Christian Spro, Dimosthenis Peftitsis, Ole-Morten Midtgård and Tore Undeland. 'Modelling and Quantification of Power Losses Due to Dynamic On-State Resistance of GaN E-Mode HEMT'. In: 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL). July 2017, pp. 1–6. DOI: 10.1109/COMPEL.2017.8013410.

- [P4] Ole Christian Spro, Dimosthenis Peftitsis and Pierre Lefranc. 'High-Voltage and High-Frequency Design of Planar Transformer with Minimum Coupling Capacitance'. In: 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe). Sept. 2019, pp. 1– 10. DOI: 10.23919/EPE.2019.8915570.

- [P5] Ole Christian Spro et al. 'Optimized Design of Multi-MHz Frequency Isolated Auxiliary Power Supply for Gate Drivers in Medium Voltage Converters'. In: *IEEE Transactions on Power Electronics* 35.9 (Sept. 2020), pp. 9496–9511. ISSN: 1941-0107. DOI: 10.1109/TPEL.2020.2972977.

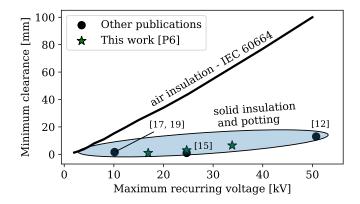

- [P6] Ole Christian Spro, Frank Mauseth and Dimosthenis Peftitsis. 'Design of Coreless, Planar PCB Transformers with High Isolation Voltage for Multi-MHz Power Supplies'. In: *submitted for review* ().

# **Other Publications**

- [O1] Ole Christian Spro. 'Trådløs Kraftoverføring i Fremdig Elektrisk Transport'. In: *Teknisk Møte 2017 - Det Digitale Energiskiftet*. Trondheim, Norway: SINTEF Energi AS, Apr. 2017, pp. 79–87. ISBN: 978-82-594-3772-3.

- [O2] Fredrik Göthner, Ole Christian Spro, Magnar Hernes and Dimosthenis Peftitsis. 'Challenges of SiC MOSFET Power Cycling Methodology'. In: 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe). Sept. 2018, P.1–P.8.

- [O3] Ole Christian Spro et al. 'Driver Stage Implementation with Improved Turn-on and Turn-Off Delay for Wide Band Gap Devices'. In: 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe). Sept. 2018, P.1–P.10.

- [O4] Håvard Lefdal Hove, Ole Christian Spro, Giuseppe Guidi and Dimosthenis Peftitsis. 'Improved SiC MOSFET SPICE Model to Avoid Convergence Errors'. In: International Conference on Silcon Carbide and Related Materials 2019 (ICSCRM'2019). Kyoto, Japan, Nov. 2019.

- [O5] Håvard Lefdal Hove, Ole Christian Spro, Dimosthenis Peftitsis, Giuseppe Guidi and Kjell Ljøkelsøy. 'Minimization of Dead Time Effect on Bridge Converter Output Voltage Quality by Use of Advanced Gate Drivers'. In: 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia). May 2019, pp. 883–890.

## References

- H. Abu-Rub, J. Holtz, J. Rodriguez and G. Baoming. 'Medium-Voltage Multilevel Converters State of the Art, Challenges, and Requirements in Industrial Applications'. In: *IEEE Transactions on Industrial Electronics* 57.8 (Aug. 2010), pp. 2581–2596. ISSN: 0278-0046. DOI: 10.1109/TIE. 2010.2043039.

- M. E. Baran and N. R. Mahajan. 'DC Distribution for Industrial Systems: Opportunities and Challenges'. In: *IEEE Transactions on Industry Applications* 39.6 (Nov. 2003), pp. 1596–1601. ISSN: 0093-9994. DOI: 10.1109/ TIA.2003.818969.

- [3] Dushan Boroyevich, Igor Cvetkovic, Rolando Burgos and Dong Dong. 'Intergrid: A Future Electronic Energy Network?' In: *IEEE Journal of Emerging and Selected Topics in Power Electronics* 1.3 (Sept. 2013), pp. 127– 138. ISSN: 2168-6785. DOI: 10.1109/JESTPE.2013.2276937.

- [4] A. Giannakis and D. Peftitsis. 'MVDC Distribution Grids and Potential Applications: Future Trends and Protection Challenges'. In: 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe). Sept. 2018, pp. 1–9.

- Kai Kriegel. 'Overview on Industrial Applications of WBG Devices'. In: 2017 Summer School of Information Engineering (SSIE 2017). Bressanone, Italy, 2017, pp. 1–45.

- [6] F. Mura and R. W. De Doncker. 'Design Aspects of a Medium-Voltage Direct Current (MVDC) Grid for a University Campus'. In: 8th International Conference on Power Electronics - ECCE Asia. May 2011, pp. 2359–2366. DOI: 10.1109/ICPE.2011.5944508.

- [7] V. S. Nguyen, P. LeFranc and J. C. Crebier. 'Gate Driver Architectures for High Speed Power Devices in Series Connection'. In: PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management. May 2017, pp. 1–8.

- [8] H. Polinder et al. 'Trends in Wind Turbine Generator Systems'. In: *IEEE Journal of Emerging and Selected Topics in Power Electronics* 1.3 (Sept. 2013), pp. 174–185. ISSN: 2168-6777. DOI: 10.1109/JESTPE.2013. 2280428.

- [9] G. F. Reed, B. M. Grainger, A. R. Sparacino and Z. Mao. 'Ship to Grid: Medium-Voltage DC Concepts in Theory and Practice'. In: *IEEE Power* and Energy Magazine 10.6 (Nov. 2012), pp. 70–79. ISSN: 1540-7977. DOI: 10.1109/MPE.2012.2212613.

- J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt and S. Kouro. 'Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives'. In: *IEEE Transactions on Industrial Electronics* 54.6 (Dec. 2007), pp. 2930–2945. ISSN: 0278-0046. DOI: 10.1109/TIE.2007.907044.

- [11] Milan Rosina. GaN and SiC Power Device: Market Overview. Munich, Germany, Nov. 2018. URL: http://wwwl.semi.org/eu/sites/ semi.org/files/events/presentations/02\_Milan % 5C % 20Rosina\_Yole.pdf (visited on 27/03/2020).

- [12] Juergen K. Steinke, Philippe Maibach, Gabriel Ortiz, Francisco Canales and Peter Steimer. 'MVDC Applications and Technology'. In: PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management. May 2019, pp. 1–8.

# Chapter 2

# Characteristics and application of GaN HEMT devices

This chapter presents the characteristics of GaN material and the GaN-based power device structure that is prominent today. An initial historical context is given to the development of the semiconductor field using GaN material. Subsequently, the characteristics of GaN power devices are detailed and compared to competing semiconductor technologies, namely SiC MOSFETs and Si super-junction (SJ) MOSFETs, in an effort to highlight the fundamental performance differences between these technologies. The final goal of the chapter is to identify relevant application areas and justify that the characteristics of the GaN power device enable crucial performance benefits, in particular for high-frequency applications.

### Contributions

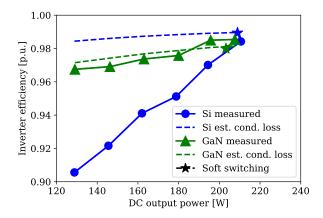

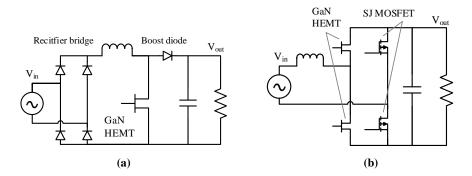

Contributions to the literature on the topic of this chapter have been made through publications [**P1**,**P2**,**P3**,**P5**]. In [**P1**] and [**P2**], the performance of GaN HEMTs is demonstrated in a wireless power transfer (WPT) application and a power factor correction (PFC) converter. While improvements in efficiency for the converters are shown, the system efficiency might only be marginally increased due to other dominating loss elements. Hence, the goal must be to find an application where the new GaN HEMT technology makes a large impact. In [**P5**], this is demonstrated for a high-frequency auxiliary power supply with high isolation voltage. However, as will be shown in this chapter, the GaN technology has new aspects that need to be modelled. In [**P3**], contributions were made to the discussion on measurements of one of these phenomena, namely the dynamic on-state resistance. In particular, measurement errors and SPICE modelling were discussed.

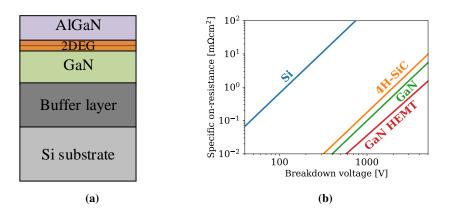

**Figure 2.1:** a) Heteroepitaxial structure of a GaN HEMT, indicating the location of the 2DEG between the GaN and AlGaN layers (layer height is not shown to scale). b) Theoretical lower limit of specific on-resistance of vertical devices based on Si, SiC and GaN, and for the lateral GaN HEMT device.

# 2.1 GaN material and the HEMT device

The development of GaN for use in the semiconductor industry has primarily been driven by the desire to produce light emitting diodes (LEDs) using GaN as the main semiconductor material [9, 43]. GaN has a direct band gap that results in light emission in the near-UV spectrum. Furthermore, by making different alloys with AlN or InN, the band gap can be slightly adjusted. This has led to the development of highly efficient violet and blue LEDs. Such LEDs are in turn used for advancing more efficient technology for emitting white light, an achievement that was rewarded with the Nobel Prize in Physics in 2014 [53].

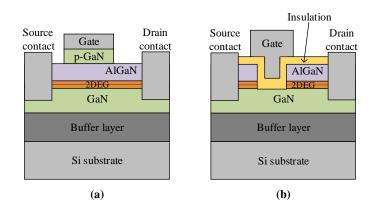

Additionally, the GaN material is suitable for making power devices in a structure known as the high electron-mobility transistor (HEMT). A HEMT does not rely on doping to obtain a highly conductive channel in the semiconductor material. Rather, a polarisation charge is established in the interface between two different material layers. Figure 2.1(a) shows the heteroepitaxial structure of a GaN HEMT made on a Si substrate [34]. In the GaN HEMT, this polarisation charge is formed between a GaN and an AlGaN layer. This interface layer of charge is referred to as a 2-dimensional electron gas (2DEG). To handle the mismatches in the material properties between Si and GaN, a buffer layer is grown on top of the substrate. Subsequently, the GaN and the AlGan layers are grown to establish the 2DEG. Finally, a transistor is made by adding a gate structure across this layer that can neutralise the polarisation charge in such a way that the device can be turned on and off. A consequence of this structure type is that it is only fabricated as a lateral

device. Vertical structures are preferred for power devices due to better current distribution and improved use of the chip area [6, 27, 1]. However, this could limit the voltage rating of such devices due to cost and fabrication yield. Several vertical GaN device structures are currently being explored: current-aperture vertical electron transistor (CAVET), trench MOSFET and vertical fin power FET [59]. The latter has shown promising performance [56, 59]. Nevertheless, most of the vertical device structures have to be grown on high-quality GaN substrates which are currently expensive and too small for large-scale power device fabrication [27]. Some researchers are circumventing this limitation by fabricating vertical GaN structures on Si substrates in an effort to cut component cost [27].

Reports in the literature in the late 1990s and in the 2000s indicate that a method for producing GaN devices on Si wafers was successfully implemented, which was the foundation for modern GaN-based power electronics [1, 22, 34]. Si wafers are significantly cheaper than wafers based on GaN, SiC or sapphire, and the available wafer size is much larger. Furthermore, existing fabrication infrastructure for Si can be reused for producing this new device [34]. Hence, it became conceivable that costs for GaN HEMT devices could be lowered sufficiently to enter the very price-competitive power electronics market. GaN devices were first available in the RF market where the high price could be leveraged by the device performance. These devices are usually made on SiC or sapphire substrates, although GaN-on-Si was also available [34]. EPC was one of the first companies to launch a GaN HEMT device for the power electronics market in 2009 and they were closely followed by many other companies in the start of the last decade. The market size for GaN power devices is still modest in comparison to the total market for power devices. In 2017, the total GaN market was estimated to be approximately \$8M [14] while the SiC market was valued at \$311M [48]. Yet, both markets are small compared to the total market size of \$15.4B for power devices [48]. However, finding suitable markets for the introduction of a new technology is the key to its adoption among converter designers [38]. The current adoption rate of GaN is increasing and the market is predicted to increase between 55 and 93% annually in the period 2017-2023 [14].

Furthermore, the high channel mobility means that smaller devices can be made for a similar rating, which results in a smaller device area [1]. Typically, device technologies are compared using specific on-resistance and plotted for different breakdown voltages. This results in on-state values that are independent of chip area, and, hence, the conduction losses of different technologies can easily be compared. Figure 2.1(b) shows the lower theoretical limit in on-state resistance for vertical Si, SiC, and GaN devices, and a theoretical lower limit for the GaN HEMT device [1] (although there are small variations in these limits in the literature [18]).

### 16 Characteristics and application of GaN HEMT devices

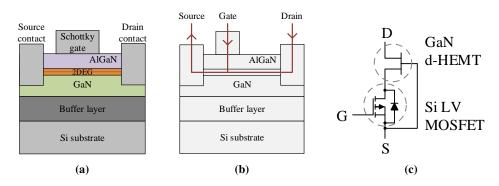

**Figure 2.2:** a) Semiconductor structure of the GaN HEMT with a Schottky gate contact. b) Diagram showing the current flow between the external contacts, highlighting that the device is lateral. c) Schematic diagram of GaN HEMT cascode configuration of a low-voltage Si MOSFET and a GaN d-HEMT.

This figure shows that GaN devices can achieve lower resistance than Si and SiC devices for the same rated breakdown voltage, and the GaN HEMT device can achieve even lower resistance due to its high channel mobility. However, while commercial SiC MOSFET devices are closing in on the theoretical value of specific on-resistance, modern GaN HEMT devices are further away from their theoretical potential, with very few reported GaN devices crossing the theoretical limit of 4H-SiC [6, 20, 59]. Thus, there is still considerable room for improvement for future GaN power devices.

### 2.1.1 Normally-on and normally-off device, and related gate structures

The GaN HEMT is inherently a normally-on, or depletion mode, device (d-HEMT) due to the formation of a 2DEG between the AlGaN and GaN layers. This entails that the device is in on-state with a zero gate-to-source voltage and requires a negative voltage to be turned off. In its simplest form, a Schottky contact can be made on top of the AlGaN layer to serve as the gate contact (shown in Fig 2.2(a)). When the device is turned on, the current flows in the device structure, as indicated in Fig. 2.2(b). As can be seen, the currents go through the 2DEG between the AlGaN and GaN layers. Notably, the currents do not go in the substrate since it is a lateral device. The 2DEG is turned off by applying a negative voltage on the gate contact. However, application engineers tend to avoid normally-on devices. The converter system must be designed so that it goes to a safe state in the case of a gate driver failure or a loss of power to the gate driver. This is perceived as easier when using a normally-off device despite demonstrations of driver circuits that can handle the start-up and loss-of-power conditions for normally-on switches [42].

As an example, a bridge converter using normally-on devices would short-circuit the dc-link capacitor in case of a fault, which is a highly undesirable situation. Accordingly, the GaN industry is currently focusing on manufacturing normallyoff devices.

The GaN HEMT can be made normally-off by two main techniques. Either the HEMT is series-connected with a normally-off device in a cascode configuration, or a gate structure is implemented such that the device becomes an enhancement mode device (e-HEMT).

In the first technique, the d-HEMT is combined with a low-voltage MOSFET (LVMOSFET) to appear as a normally-off device (Fig. 2.2(c)). This is known as cascode configuration. The internal connection of the HEMT gate to the external source terminal leads to inherent negative driving of the GaN HEMT gate when the auxiliary MOSFET is off. When the LVMOSFET is on, the GaN HEMT sees a gate voltage close to zero or higher, and, hence, is turned on. When the LVMOSFET is off, the blocking voltage is seen as a negative gate voltage for the GaN HEMT which is then also turned off. However, the losses of the device are governed by the two devices in series. It has been shown that for high-voltage HEMTs, the added channel resistance of the LVMOSFET is relatively low, thus it becomes a feasible solution [34]. Consequentially, cascode devices are only seen commercially for devices rated for 600V. This device type has two main benefits. Firstly, the structure lowers the reverse conduction losses compared to normallyoff devices. When a negative current goes through the device, the gate-source voltage of the d-HEMT equals the forward voltage drop of the LVMOSFET. This entails that the GaN HEMT sees a gate-source voltage greater than zero and is thus turned on. Secondly, existing driver circuitry and voltage levels can be used to drive the cascode device. However, the cascode device will have reverse recovery losses due to the body diode in the LVMOSFET. The LVMOSFET will also have higher gating losses than other GaN HEMT devices since the input capacitance and the driving voltage are higher. This, in turn, limits the cascode at a lower operating frequency compared to other GaN HEMT device types. Other negative aspects of cascode devices are added parasitic inductance of the on-chip bond wires connecting the series-devices [58], and reduced control of the switching speed.

The alternative technique to make the HEMT normally-off is to make an enhancement mode device (e-HEMT) [25, 46]. This entails that the semiconductor design is modified so that the charge of the 2DEG under the gate structure is depleted with zero gate-source voltage, effectively raising the threshold voltage above zero volts. To re-establish the 2DEG, a positive gate voltage must be applied that reintroduced the channel charge. In the literature, there are two main concepts that are followed.

#### 18 Characteristics and application of GaN HEMT devices

**Figure 2.3:** Semiconductor structure of different gate structures for normally-off GaN HEMT. a) p-GaN gate structure. b) Recess gate structure.

The first concept is p-GaN gate shown in Fig. 2.3(a) and the second is the recess gate structure shown in Fig. 2.3(b). Although there are more gate structure concepts, these are the most actively researched concepts. In addition, the p-GaN gate structure is the only structure used in commercial e-HEMT devices [46]. Furthermore, the reported specific on-resistance for e-HEMTs is lower than for d-HEMT devices [1].

In the p-GaN gate structure, a p-doped GaN layer is deposited on top of the AlGaN layer. In semiconductor terms, this leads to a shift in the valence band under the gate structure that brings the interface layer above the Fermi level. In other words, the holes of the p-GaN layer diffuse into the 2DEG and deplete the channel charge. Consequently, there is no forming of the 2DEG in that area. The lack of an insulation layer in this gate structure leads to strict gate voltage rating of these devices, usually in the range of 5 to 6 V. For higher voltage, the gate current increases drastically which can, in turn, lead to device overheating and failure.

In the recessed gate structure, the AlGaN layer is thinned sufficiently so that the valence band is above the Fermi level under the gate, and thus there is no polarisation charge and 2DEG. An undesired effect of this structure is the high gate leakage current. To counter the leakage current, an insulating layer is introduced and the gate contact is made on top of the insulating layer, making a metal-insulator-semiconductor HEMT (MISHEMT) device. In comparison with the p-GaN gate structure, the recess gate introduced several new steps in the manufacturing process and increased complexity of the design. Although the gate leakage current decreases and the voltage rating of the gate increases, the reported performance and additional reliability issues do not make this a commercially viable design to

**Figure 2.4:** The different operating regions for forward voltages shown in a IV curve of a GaN HEMT (GS66508T).

date [46].

Despite the lack of insulated gate structures among the commercial devices, there is still a differentiation in the driving scheme between current-driven (Panasonic, Infineon) and voltage-driven (EPC, GaN Systems, etc) devices. Common for all devices is that they have low threshold voltages that result in strict requirements for the driving circuit [**P2**]. With low threshold voltage, the device becomes more prone to parasitic-turn on and more sensitive to noise. On the contrary, the gate terminal of cascode devices are connected to a low-voltage MOSFET, hence these devices have voltage-driven isolated gates with the same immunity to noise as Si devices (Transphorm). For most of the published work of the author, voltage-driven devices from GaN Systems have been used, in addition to devices from Texas Instruments with integrated drivers.

# 2.2 Circuit behaviour and device modelling

In this section, the static and dynamic behaviour of GaN HEMTs is presented in detail to identify the similarities and differences with other power devices. Firstly, the different conduction modes are investigated. Following this, the parasitic elements will be discussed. As will be seen, the standard small signal model of unipolar devices is suitable for modelling the circuit behaviour of GaN HEMTs. Yet, there are two supplementary loss aspects that are reported in the literature, which are not covered in conventional device modelling, namely dynamic on-state resistance and

|                |              |      |                  | $R_{\rm DS,on}$ | Relative        |                   |

|----------------|--------------|------|------------------|-----------------|-----------------|-------------------|

| Device         | Manufacturer | Туре | $V_{\rm DS,max}$ | @25 °C          | $R_{\rm DS,on}$ | $V_{\mathrm{SD}}$ |

|                |              |      | [V]              | $m\Omega$       | @150°C          | [V]               |

| IPT60R065S7    | Infineon     | Si   | 600              | 100             | 2.35            | 0.82              |

| C3M0065090J    | Wolfspeed    | SiC  | 900              | 65              | 1.38            | 4.8               |

| IMZA65R072M1H  | Infineon     | SiC  | 650              | 72              | 1.31            | 4.0               |

| SCTH35N65G2V-7 | STM          | SiC  | 650              | 55              | 1.31            | 4.5               |

| SCT3060AL      | Rohm         | SiC  | 650              | 60              | 1.33            | 3.2               |

| GS66506T       | GaN Systems  | GaN  | 650              | 67              | 2.61            | 3.0               |

| IGT60R070D1    | Infineon     | GaN  | 600              | 55              | 2.18            | 2.2               |

| PGA26E07BA     | Panasonic    | GaN  | 600              | 56              | 1.96            | 2.1               |

| TP65H050WS     | Transphorm   | GaN  | 650              | 50              | 2.06            | 1.3               |

#### 20 Characteristics and application of GaN HEMT devices

**Table 2.1:** Comparison of a selection of devices from competing technologies with similarly rated blocking voltage and nominal on-resistance.  $V_{\rm SD}$  is given for a drain current in the range of -8 to -13 A.

output capacitor hysteresis losses. Subsequently, these loss aspects are covered in depth. As will be made clear, both of them scale with frequency and voltage, and they become prominent at high frequencies. The research trends and future outlook will also be discussed. Based on the device characteristics, the subchapter is concluded with suitable application areas where GaN HEMTs exhibit a clear advantage over other technologies.

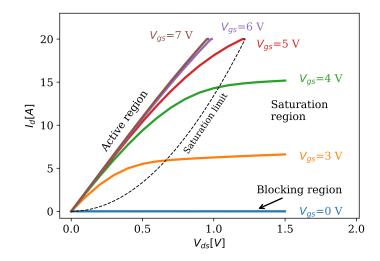

### 2.2.1 Forward conduction and blocking region

The behaviour of the GaN HEMT is comparable to other unipolar devices such as n-type JFETs and MOSFETs. A voltage or a current signal is applied to the gate, which, in turn, controls the channel of the device. As shown in Fig. 2.4, the first quadrant behaviour can be divided into three regions: saturation, blocking and active. In the blocking region, the device has a small leakage current for drain-source voltages below the blocking capability of the device. In the saturation region, increasing the drain-source voltage does not lead to a substantial increase in the drain current, as expected. In the active region, approximate linear relationship between device current and voltage drop means that the device can be modelled as a resistor,  $R_{on}$ . The device on-resistance is often quoted in the datasheet for a given drain current and allows for fast comparison between devices. A selection of GaN HEMTs and competing technologies with similar on-resistance are provided in Table 2.1. A visible trend in the table data is that commercial GaN HEMTs have a high temperature coefficient (Relative  $R_{ds,on}@150 \,^{\circ}C$ ) compared with SiC

**Figure 2.5:** a) Diagram of the GaN HEMT diagram to highlight the parasitic elements. In particular, the distance between gate-drain is longer than for gate-source, making the channel resistance higher. b) Small signal model of GaN HEMT without any package parasitics.

MOSFETs. The increase in on-resistance from room temperature to  $150 \,^{\circ}$ C is in the range from 100 to 160% for the GaN HEMTs while only 30 to 40% for the SiC MOSFETs. Yet, the selected Si SJ FET has a comparable increase in on-resistance with temperature as the GaN HEMT. A consequence of the high temperature coefficient is that nominal operation will be at higher on-resistance than the quoted datasheet value, which, on the one hand, leads to higher conduction losses. On the other hand, a positive and high temperature coefficient makes such devices suitable for paralleling.

### 2.2.2 Reverse current conduction

The third quadrant operation for GaN HEMT is slightly different than for other unipolar devices. Since there is no doping in the HEMT structure, there is no body diode either. Yet, the HEMT can still conduct a current in the reverse direction. When the drain-gate voltage reaches the threshold voltage of the device, the device channel opens [25, 34]. The basis for the reverse conduction property of HEMTs lies in the symmetry of the structure. Since there is no doping, there is no difference between drain and source contacts with respect to the gate contact. This symmetry is transferred to the circuit diagram shown in Fig. 2.5(a). The only difference is the distance. Hence, the channel will start conducting if either  $V_{gs}$  or  $V_{dg}$  are higher than the threshold voltage [44]. The effective gate voltage,  $V_{gs,eff}$ , is expressed as:

$$V_{gs,eff} = V_{gs} - R_{gs}I_d$$

in forward conduction (2.1)

$$V_{gs,eff} = V_{ds} - V_{as} - R_{ad}I_d$$

in reverse conduction (2.2)

where  $R_{gs}$  and  $R_{gd}$  are the contact and channel resistance between source-gate and drain-gate, respectively. However, the transconductance will be lower in reverse conduction than in forward conduction [44]. As mentioned, the distance between drain and gate is longer than for source and gate, as illustrated in Fig. 2.5(a). With a given sheet resistance of the channel, the drain-gate resistance,  $R_{gd}$ , and, hence, the voltage drop, will be higher than for source-gate for the same current amplitude. This voltage drop leads to a decrease in the effective gate voltage, and thus the voltage drop over the device will be higher for the same current. Additionally, if the device is driven with a negative gate voltage during the off-state,  $V_{gs,neg}$ , this voltage is added to the device voltage drop.

As a circuit analogy, e-HEMT devices can be modelled as having a body diode with high forward voltage drop ( $\geq 2 V + V_{gs,neg}$  if looking to Table 2.1), and no reverse recovery charge. Nevertheless, if the device is turned on, the channel can conduct in the reverse direction with similar on-resistance as for the forward current direction.

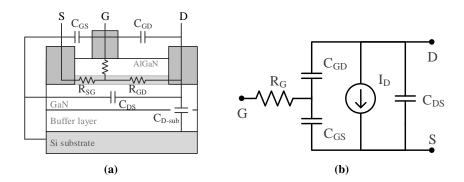

## 2.2.3 Parasitic capacitances and small signal model

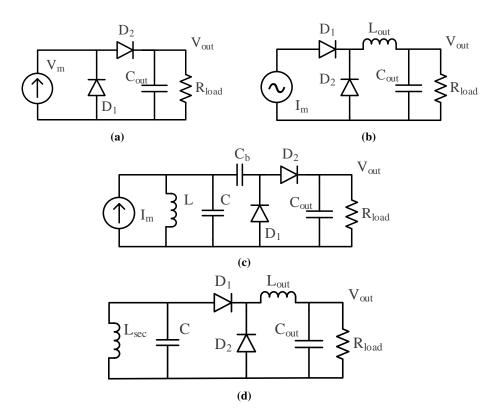

Due to the extent of the geometry, there are parasitic capacitances between the device terminals and the substrate, as indicated in Fig. 2.5(a). Since the parasitic elements and channel behaviour are similar to other power devices, the same small signal model can be used (ref Fig. 2.5(b)). The effect of the capacitors  $C_{gs}$ ,  $C_{da}$ , and  $C_{ds}$  on the device behaviour is, again, the same as for other unipolar devices; the drain current source depends on the gate-source voltage, and, during turn-on and turn-off, the gate-drain and drain-source capacitors are charged and discharged. However, since GaN HEMTs are lateral devices with an insulating layer (buffer layer) between the active region and the substrate, there are also parasitic capacitances between the device terminals and the substrate. Usually, the substrate is shorted to the source terminal, thus the source-substrate capacitor is not shown in Fig. 2.5(a). In contrast, the capacitor  $C_{d-sub}$  is not shorted and plays a role in the device losses that will be discussed in Section 2.2.5. However, it is of less importance for the switching behaviour. In total, the GaN HEMT can be modelled with the same small signal model as used for other unipolar devices; the three parasitic capacitances and the channel current determined from the device transfer function. However, some modifications must be made to account for third quadrant behaviour and the applied gate voltage. Additional parasitic inductance and resistance due to packaging can also be included in the modelling, yet this is standard procedure for all types of devices.

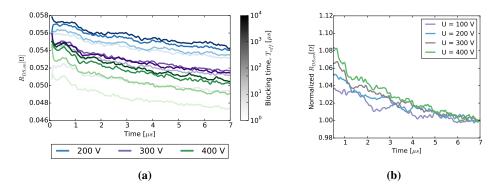

**Figure 2.6:** Example waveforms of the development in the device resistance with time that show the effect of dynamic on-state resistance. Test object is a 55 m $\Omega$  GaN HEMT (GS66506T). a) Measured resistance in absolute terms from 200 ns to 7 µs for different dc-link voltages and blocking times [**P3**]. b) Comparing the relative change in resistance for the same blocking time of 50 µs, but with different dc-link voltages [**P3**].

## 2.2.4 Dynamic on-state resistance, $R_{DS,on}$

An added characteristic of GaN HEMT devices compared to other power devices is that the on-state resistance is not a static parameter. Common to all power device types is that the on-state resistance depends on the junction temperature. In addition, the GaN HEMT on-resistance has a time dependency, and is thus dynamic in nature. The dynamic on-state resistance is also known in the literature as current collapse, or gate lag in the radio frequency domain. The dynamic behaviour contains several time constants which further complicate the phenomenon [23, 30]. The increase in resistance depends on many operating parameters, among which the most influential are off-state voltage, on- and off-times (frequency and duty cycle), junction temperature, and switching mode (hard- or soft-switching, HS/SS). Naturally, the influence of each parameter also varies among manufacturers. Figure 2.6 shows example waveforms of the time variation in the device resistance [P3]. After blocking the dc-link voltage for the indicated blocking time, the device is turned on and the resistance is measured from 200 ns to  $7 \,\mu s$ . In Fig. 2.6(a), the resistance is shown in absolute value for varying blocking time and dc-link voltage. For reference, the datasheet resistance value is  $55 \text{ m}\Omega$ . In Fig. 2.6(b), the relative change from start to end is plotted for the same blocking time. The current is kept constant at 10 A for all tests. The device resistance is observed to decrease over time.

The underlying mechanism of the current collapse is the trapping of charge in different parts of the HEMT structure; in interface layers around the gate or originating from traps in the buffer layer [5, 57, 65]. Early reports showed a substantially increased on-resistance in GaN HEMT devices. To address this issue, manufacturers worked on improving the surfaces in interface layers. Additionally, using field plates to shape the electric field around the gate terminal towards the drain terminal was shown to counter the current collapse. Later, injection of holes on the drain side using p-GaN has also been demonstrated to be an effective technique to decrease the impact of the issue [10, 26, 52] (see Fig 2.5(a)).

The literature contains many circuit suggestions for measuring the dynamic onstate resistance. A common limitation for the circuits is the time delay from when the device is switched on until the measurement can begin. In 2017, the author presented such a measuring circuit in [P3] with a time delay of approximately 200 ns and high measurement precision. Most circuits have had a limitation of 200 ns or more, and improvements are made continuously. The lowest reported time delay is approximately 10 ns [31]. This delay relates to how long it takes to discharge the capacitance of the blocking device and for any oscillations to settle. Hence, the delay time is constant and poses a limitation to the maximum frequency for which the on-resistance can be measured. An alternative is to measure the dc input power to a test circuit while accurately estimating other loss factors [13]. The remaining losses are attributed to the conduction losses of the device under test. Several works highlight the need to run measurement tests over several pulses since the first pulse in a double pulse test is not representative for the steady state behaviour. However, in pulsed operation or steady state, it becomes increasingly difficult to separate the dynamic resistance behaviour from static resistance.

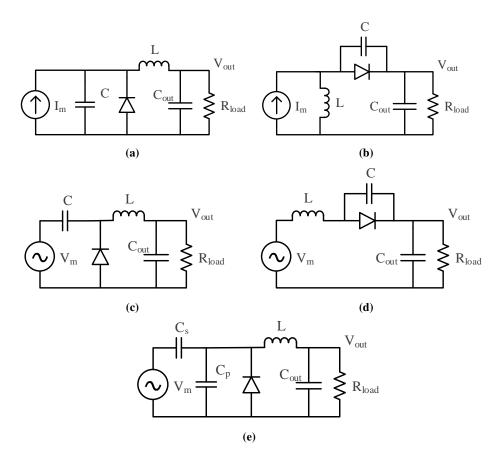

Although there is an increasing number of papers on the subject, it is difficult to draw clear conclusions. As summarised in [65], variations in testing methodology and reporting technique lead to confusion. One particular aspect that creates confusion is that the reported dynamic resistance is relative to 25 °C. Since the static resistance of GaN HEMTs has a substantial temperature coefficient (ref Table 2.1), it becomes difficult to differentiate between the loss contribution of the dynamic resistance and the known static behaviour of the tested device. Thus, the reported increase in device resistance might be exaggerated. Despite the current state of reporting in literature, a summary of the effect of operational parameters most commonly found in the literature is given in Table 2.2 along with (non-exhaustive) examples.

Regarding the off-state voltage, the literature is almost unanimous in stating that higher voltage leads to increased on-resistance. However, the device-specific trends are not equal. Some devices increase resistance linearly with voltage while some hit a knee voltage after which the dynamic resistance decreases with voltage [32]. This could potentially be linked with the wafer production, as increased leakage

current at higher voltages leads to de-trapping in off-state [40, 57]. Moreover soft-switching can limit the significance of the off-state voltage on dynamic resistance [65].

In addition, the literature is unanimous in expressing that increased operating frequency leads to increased on-resistance. This is related to the difference in trapping and de-trapping time constant, where the latter is significantly larger than the former. Hence, increased frequency leads to less de-trapping and increased resistance. Using some examples of results, [32] shows that the resistance increases up to twice the nominal value at 1 MHz. At an operating frequency of 3 MHz, the on-resistance of GaN HEMT devices is reported in the range of 4 to 61 times the  $R_{ds,on}$  at 25 °C depending on blocking voltage and junction temperature [13]. Similarly, an increased duty cycle will give more time for de-trapping and, hence, the resistance decreases [2, 3, 65].

As indicated in Table 2.2, the effect of temperature is not consistent across recent literature. Although increased junction temperature leads to higher static resistance, [37, 65] demonstrate that high temperature does not lead to increased dynamic resistance. Rather, it is shown that higher temperature leads to shorter detrapping time and, consequentially, lower dynamic resistance compared to low temperature measurements. In contrast, [33] states the opposite, although this could be due to wafer quality (see difference in 'epi vendors' in [57]). A consequence of the negative temperature coefficient of the dynamic on-resistance is that the device is less prone to thermal runaway. Moreover, it has been shown that minimal trapping can be achieved by optimising the device production process [39].

In addition, the effect of hard-switching and soft-switching modes on the dynamic on-resistance has also been investigated. If operating in hard-switching mode, hotelectrons generally lead to more trapping of charge, thus the dynamic resistance is

| Parameter         | Effect on dynamic $R_{ds,on}$ | Citation                |  |  |

|-------------------|-------------------------------|-------------------------|--|--|

| Off-state voltage | Increase                      | [65, 12, 32, 4, 13, 29] |  |  |

| Frequency         | Increase                      | [65, 29, 12, 32, 4]     |  |  |

| Temperature       | Depends                       | [65, 37, 33, 4]         |  |  |

| Hard-switching    | Depends                       | [65, 32]                |  |  |

Table 2.2: Overview of influence from different operational parameters on the dynamic on-resistance.

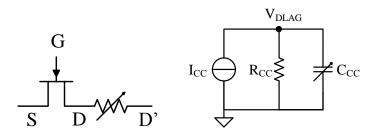

**Figure 2.7:** GaN HEMT model to model dynamic on-state resistance **[P3]**. The value of the resistance between D and D' depends on the voltage value, *VDLAG*.

more pronounced compared to the soft-switching mode [10, 65]. In contrast to this finding, the GaN HEMT structure with hole-injection at the drain contact [26] has been shown to have higher losses in soft-switching compared to hard-switching when subjected to high voltage during the off-state [32]. Consequentially, the choice of device manufacturer can be influenced by the intended application.

It is clear from the historic trends that manufacturers are finding ways to alleviate the problem. The industry is continuously demonstrating advances in device performance [24, 26]. Regardless of future improvements, the lack of dynamic on-resistance after microseconds of conduction shows that this effect is of lesser importance for converters operating with frequencies lower than 100 kHz. To date, there is no standard way of reporting dynamic on-state resistance even though some initial attempts have been made [12, 65].

Attempts have been made to include dynamic resistance in device models [41], **[P3]**. In **[P3]**, an implementation of dynamic on-state resistance was demonstrated in a SPICE simulator software. The model, shown in Fig. 2.7, is used to change the resistance element of the active device with a time-dependent behaviour. The capacitance value is changed according to the operating point. Although shown with a single time constant, additional time constants could be added. However, the large amount of operational parameters that affect the on-state resistance make it difficult to suggest a global model. Furthermore, without a global model, it becomes challenging to include this dynamic effect in design tools such as SPICE simulators. Thus, for the time being, engineers in high-frequency applications will have to expect increased resistance and include margins during the design phase.

### 2.2.5 Output capacitor hysteresis losses, C<sub>OSS</sub> losses

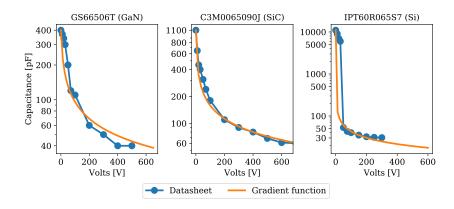

All power devices are characterised by a parasitic output capacitance between the power terminals, often referenced as  $C_{OSS}$  (small-signal output capacitance) taken

from the designation in device datasheets. When using a soft-switching technique such as zero-voltage switching (ZVS), external reactive components are used to discharge the capacitor before the device turns on. Thus, the turn-on losses are eliminated. However, it is reported that GaN HEMT devices experience losses even though the devices are not conducting a current through the channel but only experiencing charging and discharging of the output capacitor [50, 61, 63]. The loss mechanism appears as a hysteresis effect when charging and discharging the output capacitor, similar to Si super-junction devices [11, 47]. The implication of this effect is that soft-switching converters will experience additional losses despite the implementation of soft-switching techniques.

This hysteresis loss component has been shown to depend on dv/dt, device manufacturer and substrate biasing [61, 63]. Further investigations show that the losses stem from the current going through the parasitic capacitance between drain and substrate [16, 62]. The buffer layer, as for dynamic on-resistance, is identified as one of the perpetrators. More specifically, the trapping and de-trapping process leads to losses that are temperature dependent, with room temperature identified as the worst-case condition [62]. Moreover, losses occur as the drain-substrate current passes resistance of the buffer layer and the substrate resistance [62]. Although the details are scarce, it has been demonstrated that buffer layer optimisation can dramatically reduce  $C_{OSS}$  losses [16]. The continuous efforts demonstrated by researchers and manufacturers give reason to believe that this loss factor can be reduced for future commercial devices.

Since the loss scales with frequency and voltage, significant losses occur for converters operating at switching frequencies in the range of megahertz and above. Yet, for a given application, these losses can be taken into account at a design stage. In the literature, the losses are expressed as a percentage loss of the output capacitance energy per switching cycle [63]. In resonant converters, the frequency and switch voltage are not only known, but they are also mostly static in steady-state operation. Hence, the losses can be included in the design phase, and even in SPICE-based circuit optimisations, as demonstrated in [**P5**]. For completely static operation, the additional loss component can be estimated as:

$$P_{C_{OSS}} = \%_{percycle} \cdot E_{oss} \cdot f$$

= 0.5 \cdot \%\_{percycle} \cdot C\_{OSS} \cdot V\_{ds}^2 \cdot f (2.3)

where  $\%_{percycle}$  is the per cycle percentage loss of the  $E_{OSS}$  that can be approximated from  $C_{OSS}$ , the small signal capacitance, at the maximum switch voltage,  $V_{ds}$ . In SPICE, this loss can be included by using equation-based current sources.

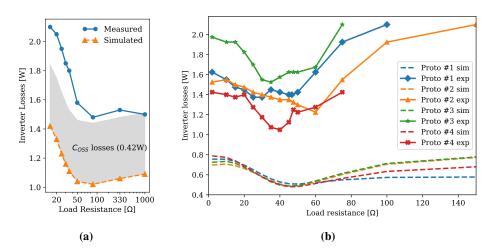

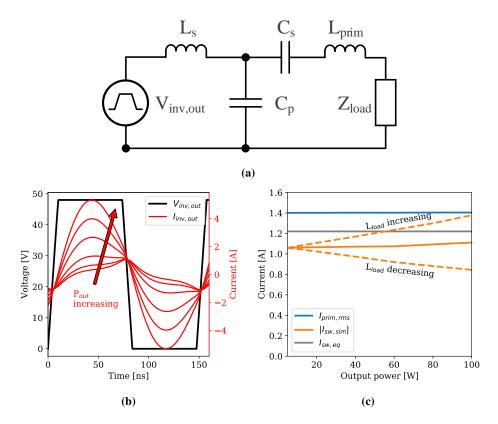

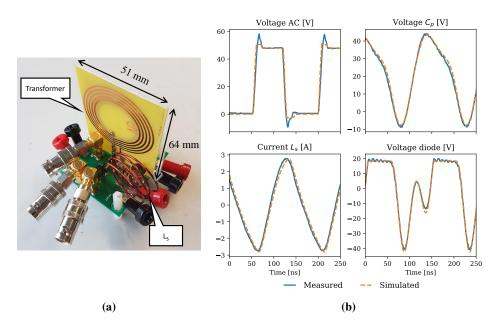

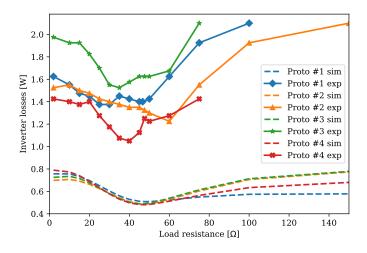

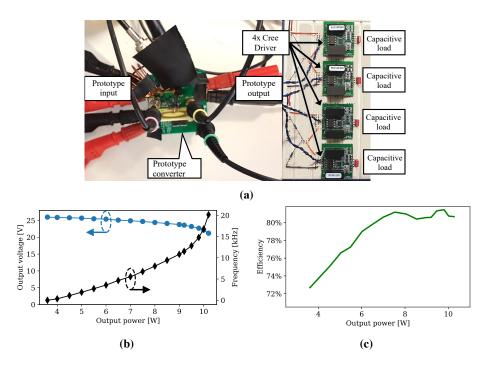

If no actions are taken to model the additional losses, the discrepancy between the expected losses and the experimental results will be high. Examples from measurements in [**P5**] are shown in Fig. 2.8. The experimental inverter losses are estimated using a calibrated loss model with the measured inverter temperature as input. Figure 2.8(a) shows the inverter losses for the initial prototype that was used to tune the simulations. The grey shaded area shows the added  $C_{OSS}$  losses as estimated from Eq. 2.3. Consequently, the gap between the simulated and the experimental losses is decreased. For the converter optimisation, the  $C_{OSS}$  losses were added in the SPICE environment.

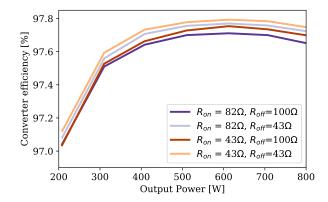

The comparisons between simulated losses and experimental losses for the four prototypes are shown in Fig. 2.8(b). Even though the added loss would decrease the gap, there are other challenges in estimating inverter losses. Firstly, the temperature coefficient and the dynamic behaviour of the on-state resistance will have to be accounted for. One approach to this challenge could be the common engineering practice of adding a margin, e.g. by multiplying the datasheet resistance with a safety factor to account for these additional losses in an early design phase. Secondly, a substantial loss contribution comes from parameter variation for both the active and the passive components. In case the variation results in a loss of softswitching, the additional losses are considerable. This has been observed for several operating points of the four prototypes. The design engineer should therefore guide the design parameters towards more robust solutions. In [P5], this was done for the experiment where prototype #4 supplied power to four Cree SiC drivers (CRD-001). The series capacitance was increased slightly, and the length of the PWM signal adjusted so that soft-switching was ensured for the whole operating range. As a result, the converter operation was well within thermal limits.

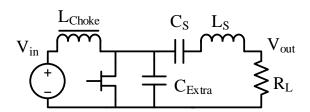

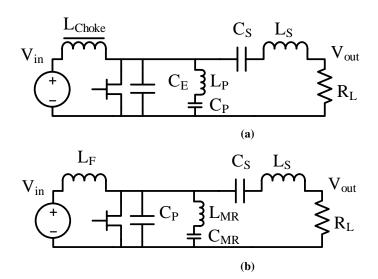

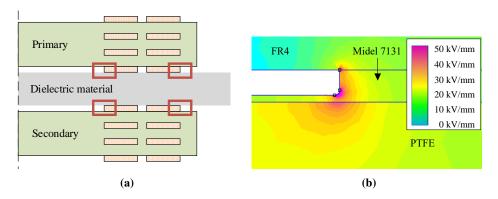

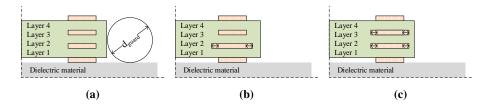

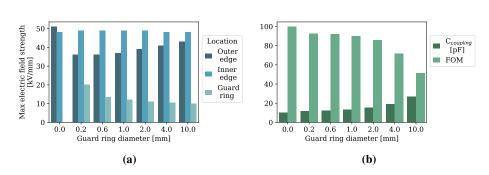

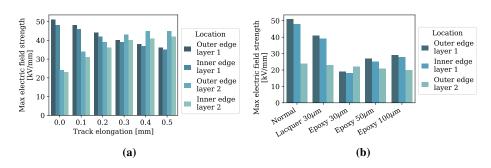

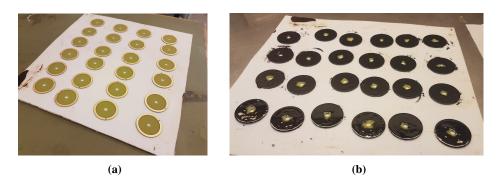

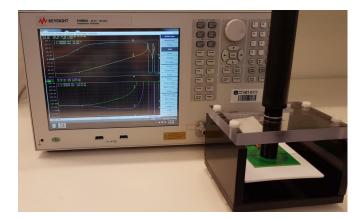

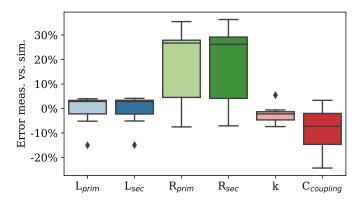

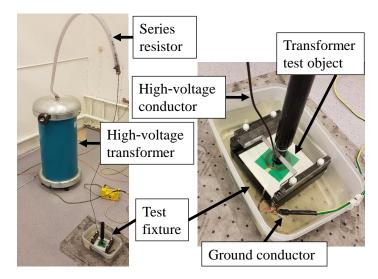

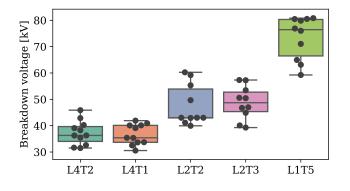

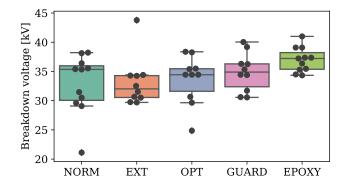

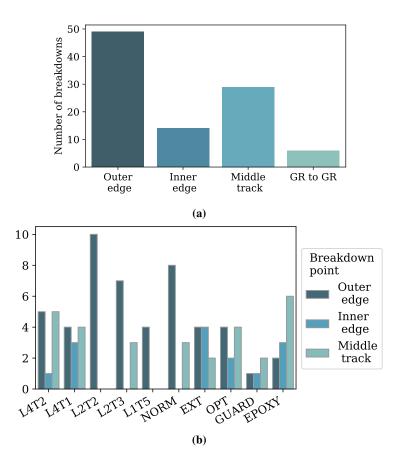

# 2.3 Identification of application areas utilising the qualities of GaN HEMTs