# A Power Efficient Low-noise and High Swing CMOS Amplifier for Neural Recording Applications

Kebria Naderi, Erwin Shad, Marta Molinas, Ali Heidari

Abstract— In this paper, a power efficient, low-noise and high swing capacitively-coupled amplifier (CCA) for neural recording applications is proposed. The use of current splitting technique and current scaling technique in a current mirror operational transconductance amplifier (CM-OTA) has lead to a very good trade-off between power and noise. The presented architecture is simple, without cascode transistor while it has more than 80 dB open-loop gain without extra power consumption. As a result, the proposed strucuture has a better power efficiency factor (PEF) and output swing in comparison with previous reported architectures is increased to the  $2V_{ov}$ below the maximum supply voltage. In order to reduce flicker noise and achieve better trade-off between the power and noise, PMOS transistors with an optimum size have been utilized which operate in sub-threshold region. The amplifier is designed and simulated in a commercially available 0.18 µm CMOS technology. Monte Carlo simulations for process and mismatch have been carried out. The gain of the proposed amplifier is 39.22 dB in its bandwidth (3 Hz - 5 kHz). Total input-referred noise is 3.03 µVrms over 1 Hz - 10 kHz. The power consumption of the amplifier is 2.98 µW at supply voltage of 1.4 V. The noise efficiency factor (NEF) and PEF are 2.4 and 8.06, respectively. The output swing is about 1.16 V. It means the proposed amplifier can tolerate up to 13.2 mV peakto-peak input signal while its total harmonic distortion (THD) is less than 1%.

*Index terms*— bio-signal amplifier, neural amplifier, low-noise, low power

### I. INTRODUCTION

Neural signals have wide range amplitude from a few tens of micro-volts to several milli-volts and their bandwidth range is from 10 - 200 Hz for local field potential (LFP) and 300 Hz - 5 kHz for action potential (AP) [1]. In this case, one of the significant blocks on neural recording system is a suitable amplifier for such a low frequency and amplitude signals.

The power consumption is a crucial parameter to design a neural amplifier. The amplitude of neural signals is low. Therefore, for clean signal acquisition, the amplifier must

Marta Molinas is with the Faculty of Information Technology and Electrical Engineering, Engineering Cybernetics, Norwegian university of Science and Technology NTNU, O. S. Bragstads Plass 2D, 7034 Trondheim, Norway. (e-mail: <u>marta.molinas@ntnu.no</u>)

Ali Heidari is with the Faculty of Engineering, Electrical Engineering, Guilan University, Rasht, Iran. (e-mail: <u>Ali.heidari@tudelft.nl</u>)

have sufficiently low input-referred noise. The electrode-

tissue has DC offset voltage, and this must be blocked by on chip high pass filter. The designed structure must be small enough to be implantable. In addition, the amplifier should have a high CMRR and a PSRR to minimize interference from power line (50/60 HZ) and power supply [1]. Our purpose is to design a high-performance amplifier. Specially we focused on NEF and PEF improvement while we increase output swing. In this article, a current mirror OTA with parallel current source is optimized by current scaling technique for a neural amplifier. As a result, the proposed structure reaches a high output swing while it has less PEF in comparison with state-of-the-art neural amplifiers.

## II. CAPACITIVELY-COUPLED AMPLIFIER

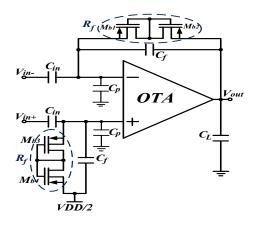

The CCA architecture (Fig. 1) has been presented first in [2]. Neural signal is coupled with input capacitors ( $C_{in}$ ) and therefore DC offset voltage caused by electrode tissue will be blocked. Due to eliminating DC level of the signal by filtration, the amplifier has rail-to-rail common mode input [3]. Combination of pseudo resistor ( $R_f$ ) and feedback capacitor ( $C_f$ ) define the low-frequency cutoff ( $f_L = 1/2\pi R_f C_f$ ).

R<sub>f</sub> has been implemented by two back-to-back PMOS transistors that results high resistance in a low space and added negligible noise and a small parasitic capacitor. Also, it has good linearity and it is possible to achieve more linearity if multiple pseudo resistor connects in series if it's desired. More linearity will be achieved since in series connection, a lower voltage drops across each  $R_f$  [4]. Higher R<sub>f</sub> results in lower loading effect. Using the R<sub>f</sub> also sets input and output common mode voltage on VDD/2. If the DC gain of the OTA is high enough, the midband gain of amplifier (A<sub>M</sub>) will be set with ratio of input capacitor to feedback capacitor ( $C_{in}/C_f$ ). This ratio is about 31.25dB which defines amplifier gain. High cutoff frequency is determined with dominant pole of OTA and bandwidth is approximately calculated by  $f_{\rm H} = G_{\rm m}/2\pi C_{\rm L}A_{\rm M}$ , where  $C_{\rm L}$  is load capacitance and G<sub>m</sub> is transconductance of OTA. The R<sub>f</sub> contribution noise is minimized by satisfying equation (1) [1].

$$\frac{c_L}{c_{in}} \ll \frac{2f_H}{3f_L} \tag{1}$$

Thus, input-referred noise of the amplifier  $(V_{nl,amp}^2)$  is given by:

$$\overline{V_{nl,amp}^2} = \frac{(c_{in} + c_f + c_p)^2}{c_{in}^2} \overline{V_{nl,OTA}^2}$$

(2)

Kebria Naderi is with the Faculty of Engineering, Electrical Engineering, Guilan University, Rasht, Iran. (e-mail: kebria.naderi@gmail.com)

Erwin Shad is with the Faculty of Information Technology and Electrical Engineering, Engineering Cybernetics, Norwegian university of Science and Technology NTNU, O. S. Bragstads Plass 2D, 7034 Trondheim, Norway. (corresponding author to provide e-mail: <u>Erwin.shad@ntnu.no</u>)

Figure1. Capacitively coupled neural amplifier

Where  $C_p$  is the OTA input parasitic capacitance and  $V_{nl,OTA}^2$  is the OTA input-referred noise. Therefore, in order to reduce  $\overline{V_{nl,amp}^2}$ , the OTA noise must be minimized. By increasing the  $C_{in}$ ,  $\overline{V_{nl,amp}^2}$  will be decrease in the cost of area consumption. On the other hand, with increasing the  $C_{in}$ , the input impedance has been lessened and the input signal will be attenuated. Also, with a fixed  $A_M$ , by increasing  $C_{in}$ , the CMRR will become higher. Therefore, there is a trade-off between these parameters.

## III. LOW-POWER LOW NOISE AND HIGH SWING OTA DESIGN

## A. OTA topology

Choosing an appropriate architecture is one of the most important part that should be considered. Folded cascode (FC) topology can have good open loop gain with one stage. Using current scaling technique in FC leads to a good tradeoff between noise and power [5]. By Using a large current scaling of 16:1 (input bias current: output branch current), the total current consumption got reduced and also, the noise effect of output branch transistors on input got decreased. But, utilizing this technique will lead to effective transconductance (G<sub>m,eff</sub>) attenuation. In order to solve this problem, one cascode stage and source degeneration resistors have been utilized which increased area and voltage headroom. Additionally, in [6] recycling FC with current scaling technique for increasing G<sub>m,eff</sub> has been presented which was relatively noise efficient. However, in this structure, a large source degeneration resistor has been used which leads to a high voltage drop across it (about 600 mV). Although [5, 6] are the best reported designs according to trade-off between noise and power they have a large area consumption and a high supply voltage.

A current mirror OTA has wide output swing, although its open loop gain is low. The Cascode transistors are added to the output branch in order to increase the gain while the output swing is limited [2]. Since this topology totally consumes  $2I_{tail}$ , it is not power efficient.

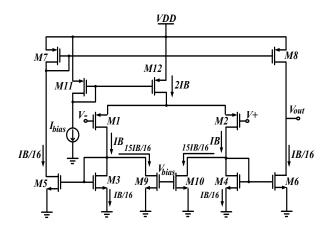

The topology of CM-OTA with shunt current source was introduced first in [7] to enhance the DC gain and it was utilized in switched capacitor applications. Although this structure had rail-to-rail output swing, its gain was less than

Fig.2 Schematic of the proposed OTA

TABLE I. OPERATING POINT FOR TRANS. IN THE OTA

| Devices           | W/L(µm) | I <sub>D</sub> (nA) | gm/I <sub>D</sub> (V <sup>-1</sup> ) | Operating region |

|-------------------|---------|---------------------|--------------------------------------|------------------|

| M <sub>1,2</sub>  | 200/1   | 1000                | 25.9                                 | Sub-threshold    |

| M <sub>3-6</sub>  | 1/20    | 62.6                | 15.9                                 | MI               |

| M <sub>7,8</sub>  | 1/5.5   | 62.6                | 14.4                                 | MI               |

| M <sub>9,10</sub> | 3.75/20 | 937.4               | 10                                   | Near SI          |

60 dB which might led to high gain error in many applications. In addition, this design is not power efficient.

In Fig. 2, the proposed modified CM-OTA and each branch current are shown. In this article, by utilizing the current scaling technique, the DC gain is enhanced more than 10 times with 1.4 times less power consumption and the same noise. Input transistors current IB is set to 1uA. The small signal and large signal currents of M<sub>1</sub> and M<sub>2</sub> are split by bottom current source  $(M_{9,10})$ . Moreover, the small signal current goes through M<sub>3,4</sub> and it is mirrored to output. The  $M_{9,10}$  are designed with  $15I_B/16$  and only  $I_B/16$  passes through M<sub>3,4</sub>. Therefore, each output branch consumes only  $I_B/16$ . Current scaling of 16:1 ( $I_{1,2}$ : $I_{3-8}$ ) have been utilized to lessen the noise effect of M<sub>3-8</sub> at the input. Besides, the total current consumption is decreased by this technique. Furthermore, due to the low current which goes through output branches, the output resistance is quite large. Accordingly, the low frequency gain is relatively high. Thus, the need for cascode transistor in order to boost DC gain is eliminated.

### B. Optimum sizing of OTA

A flicker noise (1/f noise) is the first concern in lowfrequency and low-noise amplifiers. PMOS transistors have lower 1/f noise in comparison with NMOS transistors. Thus, PMOS differential pair is used at inputs. The flicker noise for each transistor in differential pair is given by

$$\overline{V_{fn}^2} = \frac{k_p}{C_{ox}^2 \cdot W_{1,2} \cdot L_{1,2}} \times \frac{1}{f}$$

(3)

where  $K_P$  is the flicker noise coefficient,  $C_{ox}$  is oxide capacitances per unit area,  $L_{1,2}$  and  $W_{1,2}$  are length and width of transistor. By enlarging ( $L_{1,2} \times W_{1,2}$ ), the flicker noise decreases at the cost of bigger area consumption. Also, with increasing ( $L_{1,2} \times W_{1,2}$ ), parasitic capacitor  $C_P$  will be increased.

| Parameter                 | 2007 [5]              | 2011 [6]             | 2011 [8]              | 2013 [9]              | 2018[10]                | This work              |

|---------------------------|-----------------------|----------------------|-----------------------|-----------------------|-------------------------|------------------------|

| Technology                | 0.5 μm                | 0.6 µm               | 0.18 µm               | 0.18 μm               | 0.18 µm                 | 0.18 µm                |

| V <sub>dd</sub> (V)       | 2.8                   | 2.8                  | 1.8                   | 1.8                   | 1.8                     | 1.4                    |

| Power (µW)                | 7.56                  | 2.4                  | 7.92                  | 1.5                   | 4.07                    | 2.98                   |

| Gain (dB)                 | 40.85                 | 39.4                 | 39.4                  | 40.17                 | 39.75                   | 39.22                  |

| Bandwidth (Hz)            | 45 – 5.32 k           | 0.36 – 1.3 k         | 10 – 7.2 k            | 8 m – 1.68 k          | 0.3 – 4.4 k             | 3 – 5 k                |

| $V_{ni,amp}(\mu V_{rms})$ | 3.06                  | 3.07                 | 3.5                   | 2.99                  | 3.19                    | 3.03                   |

| NEF                       | 2.67                  | 3.09                 | 3.35                  | 2.6                   | 2.78                    | 2.4                    |

| PEF                       | 19.96                 | 26.73                | 20.2                  | 12.17                 | 13.91                   | 8.06                   |

| Max.signal (THD 1<br>%)   | 7.3 mV <sub>p-p</sub> | 10 mV <sub>p-p</sub> | 5.7 mV <sub>p-p</sub> | 5.9 mV <sub>p-p</sub> | 14.86 mV <sub>p-p</sub> | 13.2 mV <sub>p-p</sub> |

| CMRR (dB)                 | 66                    | 66                   | 70.1                  | 70                    | 76                      | > 70                   |

| PSRR (dB)                 | 75                    | 80                   | 63.8                  | N/A                   | 77.6                    | > 77                   |

| Area (mm <sup>2</sup> )   | 0.16                  | 0.13                 | 0.065                 | N/A                   | 0.058                   | 0.046                  |

| Sim./Meas.                | Meas.                 | Meas.                | Meas.                 | Sim.                  | Post-layout Sim.        | Post-layout Sim.       |

Table II. PERFORMANCE COMPARISON WITH CAPACITIVELY COUPLED BIO-SIGNAL AMPLIFIER

According to (2), the input-referred noise of overall circuit will be increased. However, till  $C_p$  is much smaller than  $C_{in}$ , this effect will be negligible. The total input-referred thermal noise can be approximately calculated by (4).

$$\overline{V_{nl,OTA}^2} \cong \frac{8kTc}{g_{m1,2}} \left( 1 + \frac{g_{m3,4}}{g_{m1,2}} + \frac{g_{m5,6}}{g_{m1,2}} + \frac{g_{m7,8}}{g_{m1,2}} + \frac{g_{m9,10}}{g_{m1,2}} \right)$$

(4)

Where *k* is Boltzmann's constant, *T* is the absolute temperature,  $g_{mi}$  is the transconductance of its transistor and *c* is approximately 2/3 though it varies slightly according to the biasing of the transistor. According to different operation regions of transistors, transconductance to drain current ratio  $(g_m/I_D)$  is different.  $M_{1,2}$  are designed in sub-threshold region to maximize  $g_{m1,2}$ . In this case, the total input-referred noise decreases. Additionally, apart from reducing the noise, considering to small  $V_{ov1,2}$ , mismatch of differential pair is permissible. To attain maximum possible ratio of  $g_m/I_D$  (about 27 V<sup>-1</sup>), the transistor can be designed in deep sub-threshold region but at the cost of increasing the dimensions of transistors and parasitic capacitors.  $g_{m1,2}/I_{D1,2}$  ratio is optimized by setting it on 26 V<sup>-1</sup>.

In order to reduce the noise effect of  $M_3 - M_8$ , the  $g_{m3-8}$ must be significantly smaller than g<sub>m1, 2</sub>. With designing M<sub>3</sub>- $M_8$  in the SI region, the  $g_{m3-8}$  become minimum. But it costs of increasing the over drive voltage which leads to decrease the output swing. The M<sub>3,4</sub> and M<sub>7</sub> are diode connected and with reducing  $g_{m3,4}$  and  $g_{m7}$ , their equivalent impedance seen by the gate of them will be increased. As a result, the nondominating pole of the circuit becomes effective and it might reduce the phase margin (PM) significantly. In order to have a better balance between noise with phase margin and swing, M<sub>3-8</sub> are designed in the moderate inversion (MI) region. Regarding the relatively high current of the  $M_9$  and  $M_{10}$ , the contribution of them in input-referred noise is high. Therefore, M<sub>9,10</sub> are at the border of MI and SI region. By this low ratio of g<sub>m</sub>/I<sub>D</sub>, their effect on input-referred noise is reduced. In addition, the high value of the over drive voltage is the reason of increasing the accuracy of the current scaling. The table I illustrates the main transistors operating points.

## IV. SIMULATION RESULTS

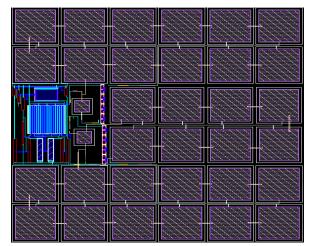

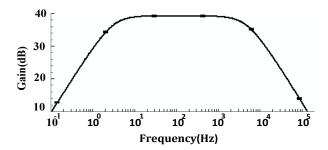

The proposed amplifier was designed and simulated in a commercially available 0.18  $\mu$ m CMOS technology. The layout of the proposed amplifier is depicted in Fig. 3. The capacitors C<sub>in</sub> and C<sub>f</sub> are implemented by MIM capacitors. The proposed amplifier occupies 0.046 mm<sup>2</sup> (218  $\mu$ m×215  $\mu$ m) area and consumes 2.13  $\mu$ A current from a 1.4 V supply. The simulated frequency response of neural amplifier is shown in the Fig. 4. The midband gain is 39.22 dB, -3 dB low and high cutoff frequencies are 3 Hz and 5 kHz for a load capacitance of 7 pF.

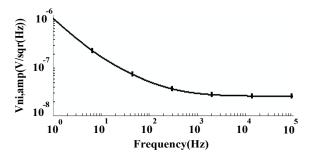

The input-referred noise is shown in Fig. 5. Simulations represent that the thermal noise floor is  $26 \text{ nV}/\sqrt{\text{Hz}}$ . The total input-referred noise of amplifier is  $3.03 \text{ }\mu\text{V}$  over 1Hz - 10 kHz. In order to compare amplifiers according to their noise, noise efficiency factor (NEF) is defined [11]

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi V_T 4kTBW}}$$

(5)

Where  $V_{ni,rms}$  is the input-referred rms noise,  $I_{tot}$  is the total supply current and BW is the amplifier bandwidth. The NEF is a significant criterion for representing the tradeoff between noise, bandwidth and current consumption.

Figure 3. Layout of the amplifier with the size of (218  $\mu$ m×215  $\mu$ m)

Figure 4. Frequency response of the amplifier

Figure 5. Input-referred noise spectra of the amplifier

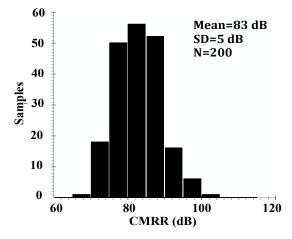

Figure 6. Mont Carlo simulation (200 runs) of CMRR at 50 Hz

However, it does not include  $V_{DD}$ . The PEF is another merit which adds supply voltage to noise efficiency factor, and it can be expressed as NEF<sup>2</sup>.V<sub>DD</sub>. In our design,  $I_{tot}=2.125I_B$ ,  $V_{DD}=1.4$  and input noise is 1.47 time of input noise of a differential pair in the sub-threshold region. In this regard, The NEF and PEF are 2.4 and 8.06, respectively.

The THD of the proposed amplifier stays below 1% with a maximum 13.2 mV<sub>p-p</sub> input signal while the output signal swing is 1.16 V<sub>p-p</sub>. Also, the Monte Carlo simulation has been carried out to show the sensitivity of the circuit to the mismatches and process variations. Fig. 6 represents the CMRR of the amplifier for the process and mismatch simulation for 200 runs. It reveals that the amplifier CMRR is not too sensitive to process and mismatch. In addition, the mean values of open loop gain and close loop gain are 83.12 dB and 39.22 dB, respectively.

According to Monte Carlo simulation, CMRR and PSRR are in worst case, more than 77 and 70 at 50 Hz, respectively. In table II, the proposed amplifier is compared to the state-of-the-art capacitively-coupled biomedical amplifiers.

## V.CONCLUSION

In this paper, a low-power, low-noise and high swing capacitively-coupled amplifier is proposed for biomedical application, especially neural recording. We have used several low-power and low-noise design techniques in a suitable structure to make an efficient trade-off. In this regard, the amplifier has a good NEF while it has a much better PEF and higher output swing with a same supply voltage. Finally, The Monte Carlo simulation showed the good performance of the circuit against mismatches and process variation.

#### References

- R. R. Harrison, "The Design of Integrated Circuits to Observe Brain Activity," in *Proceedings of the IEEE*, vol. 96, no. 7, pp. 1203-1216, July 2008.

- [2] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, Jun. 2003.

- [3] Q. Fan, F. Sebastiano, J. H. Huijsing and K. A. A. Makinwa, "A 1.8 μW 60 nV/√Hz Capacitively-Coupled Chopper Instrumentation Amplifier in 65 nm CMOS for Wireless Sensor Nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534-1543, July 2011.

- [4] H. Rezaee-Dehsorkh, N. Ravanshad, R. Lotfi, K. Mafinezhad and A. M. Sodagar, "Analysis and Design of Tunable Amplifiers for Implantable Neural Recording Applications," in *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 1, no. 4, pp. 546-556, Dec. 2011.

- [5] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136–147, Jun. 2007.

- [6] C. Qian, J. Parramon, and E. Sanchez-Sinencio, "A micropower lownoise neural recording front-end circuit for epileptic seizure detection," *IEEE J. Solid-State Circuits*, vol. 46, no. 6, pp. 1392–1405, Jun. 2011.

- [7] Libin Yao, M. Steyaert and W. Sansen, "A 0.8-V, 8-/spl mu/W, CMOS OTA with 50-dB gain and 1.2-MHz GBW in 18-pF load," ESSCIRC 2004 -29th European Solid-State Circuits Conference (IEEE Cat. No.03EX705), Estoril, Portugal, 2003, pp. 297-300.

- [8] V. Majidzadeh, A. Schmid, and Y. Leblebici, "Energy efficient lownoise neural recording amplifier with enhanced noise efficiency factor," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 3, pp. 262– 271, Jun. 2011.

- [9] Kumaravel, S., Tirumala, K. N. B., Venkataramani, B., & Raja, R, "A power efficient low noise preamplifier for biomedical applications" Journal of Low Power Electronics, 9(4), 501–509, 2013.

- [10] Sanjay, R., V. Senthil Rajan, and B. Venkataramani. "A low-power low-noise and high swing biopotential amplifier in 0.18 μm CMOS." *Analog Integrated Circuits and Signal Processing* 96, no. 3 565-576, 2018.

- [11] M. S. J. Steyaert, W. M. C. Sansen, and Z. Chang, "A micropower low-noise monolithic instrumentation amplifier for medical purposes," *IEEE J. Solid-State Circuits*, vol. SC-22, pp. 1163–1168, Dec. 1987.