# Investigation of High Accuracy Mixed-Signal Time-to-Digital Converter

Ghassan Al-Omari

Master of Science Department of Electronic Systems Norwegian University of Science and Technology

February, 2020

# Contents

1

2

| Preface                          | iv  |  |  |  |  |  |  |  |  |  |

|----------------------------------|-----|--|--|--|--|--|--|--|--|--|

| Abstract vi                      |     |  |  |  |  |  |  |  |  |  |

| Acknowledgements vii             |     |  |  |  |  |  |  |  |  |  |

| List of Figures ix               |     |  |  |  |  |  |  |  |  |  |

| List of Tables x                 |     |  |  |  |  |  |  |  |  |  |

| Abbreviations                    | xii |  |  |  |  |  |  |  |  |  |

| Introduction                     | 1   |  |  |  |  |  |  |  |  |  |

| Theory                           | 3   |  |  |  |  |  |  |  |  |  |

| 2.1 Performance Metrics          | 4   |  |  |  |  |  |  |  |  |  |

| 2.1.1 Resolution (LSB)           | 4   |  |  |  |  |  |  |  |  |  |

| 2.1.2 Non-linearities            | 5   |  |  |  |  |  |  |  |  |  |

| 2.1.3 The Linear Bits            | 5   |  |  |  |  |  |  |  |  |  |

| 2.1.4 Conversion Speed           | 6   |  |  |  |  |  |  |  |  |  |

| 2.1.5 Dynamic Range              | 6   |  |  |  |  |  |  |  |  |  |

| 2.1.6 Area and Power             | 6   |  |  |  |  |  |  |  |  |  |

| 2.1.7 Noise                      | 6   |  |  |  |  |  |  |  |  |  |

| 2.1.7.1 Jitter                   | 7   |  |  |  |  |  |  |  |  |  |

| 2.1.7.2 Process and Mismatch     | 7   |  |  |  |  |  |  |  |  |  |

| 2.1.7.3 Supply Voltage Variation | 7   |  |  |  |  |  |  |  |  |  |

| 2.1.7.4 Temperature Variation    | 7   |  |  |  |  |  |  |  |  |  |

| 2.2 TDC Architectures            | 8   |  |  |  |  |  |  |  |  |  |

| 2.2.1 Analog-type TDCs           | 8   |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.2   | Digital-Type TDCs                             | 10 |

|---|------|---------|-----------------------------------------------|----|

|   |      |         | 2.2.2.1 Delay Line TDC                        | 10 |

|   |      |         | 2.2.2.2 Vernier Delay Line TDC                | 11 |

|   |      |         | 2.2.2.3 Ring Oscillator Vernier TDC           | 12 |

|   |      |         | 2.2.2.4 Two Dimensional TDC                   | 13 |

|   |      |         | 2.2.2.5 Stochastic TDCs                       | 14 |

|   | 2.3  | TDC c   | calibration                                   | 16 |

|   | 2.4  | Therm   | nometer-to-Binary Encoder                     | 17 |

|   | 2.5  | Motiva  | ation and Selection                           | 19 |

| 3 | Desi | gn and  | Simulation Methodologies                      | 20 |

|   | 3.1  | Delay   | Segment                                       | 21 |

|   |      | 3.1.1   | Proposed Vernier Segment                      | 23 |

|   | 3.2  | Less C  | Complex Approach of Encoding                  | 26 |

|   |      | 3.2.1   | Proposed method for encoding                  | 29 |

|   | 3.3  | Test an | nd Verification                               | 30 |

|   |      | 3.3.1   | Simulation Assumptions                        | 31 |

|   |      | 3.3.2   | Corners and Temperature                       | 31 |

|   |      | 3.3.3   | Layout                                        | 31 |

|   |      | 3.3.4   | The Proposed Delay Segment                    | 31 |

| 4 | Sim  |         | Results                                       | 34 |

|   | 4.1  | Propos  | sed TDC Implementation                        | 35 |

|   | 4.2  | Proces  | ss and Mismatch Variations for Delay Segments |    |

|   | 4.3  | Encodi  | ing Circuit                                   | 39 |

|   | 4.4  | Nonlin  | nearities (DNL and INL)                       | 40 |

|   | 4.5  | Area .  |                                               | 46 |

|   | 4.6  | TDC S   | Speed                                         | 46 |

|   | 4.7  |         | Consumption                                   |    |

|   | 4.8  | TDC S   | Survey                                        | 48 |

| 5 | Disc | ussion  |                                               | 49 |

|   | 5.1  | Propos  | sed Implementation                            | 50 |

|   | 5.2  | Proces  | ss and Mismatch Variations                    | 50 |

|   | 5.3  | Encodi  | ing Circuit                                   | 52 |

|   | 5.4  | Nonlin  | nearities                                     | 53 |

|    | 5.5                                            | Con    | versi | on S | Spee | ed . | •••  |     |      |      | •   |    |     | •   | •   |     | • |   |       | • | • • | •   | • | • | <br>   |   | ••• | 54 |

|----|------------------------------------------------|--------|-------|------|------|------|------|-----|------|------|-----|----|-----|-----|-----|-----|---|---|-------|---|-----|-----|---|---|--------|---|-----|----|

|    | 5.6                                            | Area   | a     |      |      | •    | •    |     |      |      |     |    |     | •   | •   |     | • |   | <br>• | • |     | • • | • | • | <br>•• | • |     | 55 |

|    | 5.7                                            | Pow    | er.   |      |      |      | •    |     |      |      |     |    |     | •   | •   |     | • | • | <br>• | • |     | • • | • | • | <br>•• | • |     | 55 |

|    | 5.8                                            | Sum    | mar   | у.   |      | •    | •    |     |      |      | • • |    |     | •   | •   |     | • | • | <br>• | • |     | •   | • | • | <br>   | • | ••• | 56 |

| 6  | Conc                                           | clusic | n     |      |      |      |      |     |      |      |     |    |     |     |     |     |   |   |       |   |     |     |   |   |        |   |     | 58 |

|    | 6.1                                            | Futu   | ire W | ork  | •••  | •    | •    |     |      |      | • • |    |     | •   | •   |     | • | • | <br>• | • |     | •   | • | • | <br>   | • | ••• | 59 |

|    | Bibli                                          | ogra   | phy   |      |      |      |      |     |      |      |     |    |     |     |     |     |   |   |       |   |     |     |   |   |        |   |     | 63 |

| Ар | pendi                                          | ix A   | TD    | C S  | egn  | ıen  | ts l | Par | an   | nete | ers | an | d I | Lay | 70L | ıts |   |   |       |   |     |     |   |   |        |   |     | 64 |

| Ар | Appendix B Simulation Results for TDC Segments |        |       |      |      |      |      | 68  |      |      |     |    |     |     |     |     |   |   |       |   |     |     |   |   |        |   |     |    |

| Ар | pendi                                          | ix C   | Sys   | tem  | Ver  | ilo  | g N  | loc | lels | 5    |     |    |     |     |     |     |   |   |       |   |     |     |   |   |        |   |     | 74 |

## Preface

This thesis fulfills the requirements for the degree in Master of Science in Engineering for Electronic Systems Design at the Norwegian University of Science and Technology (NTNU), at the Department of Electronic Systems.

The subject of this master thesis is to measure the time between the rising edges of two separate signals. The initial suggestion for this time measurement is a Vernier Delay Line (VDL) however, other options are explored. A big concern with Vernier delay line is the consistency of the accuracy, as delay lines will have production variations. A specification for the required accuracy is established and used as the basis for the suggested solution. Even though it falls outside the scope of the thesis, calibration of the delay line or other solutions can be used as a way of further increasing the accuracy of the time measurement. The selected solution is only required to produce an unsigned logic output representing the time difference between the two separate input signals. The work done in this master thesis is not a continuation on a specialization project from previous semester and was completed in the standard time period.

### Sammendrag

I denne masteroppgaven er hovedmålet å måle tiden mellom stigende flanker av to separate signaler. Det ble foreslått å bruke en såkalt "Vernier Delay Line" (VDL), men problemet med dem er at nøyaktigheten er inkonsekvent på grunn av produksjonsvariasjoner. Derfor er det motivasjon til å prøve ut andre løsninger for å måle tidsforskjell. Det blir utviklet et krav til nøyaktigheten av målingen, som brukes som veiledning til den foreslåtte løsningen. Selvom det er utenfor omfanget av oppgaven kan kalibrering av forsinkelseslinjen eller andre løsninger øke nøyaktigheten ytterligere. Den valgte løsningen trenger kun å produsere en "unsigned logic" på utgangen for å representere tidsforskjellen mellom de to inngangsignalene. Denne masteroppgaven er ikke en fortsettelse av en prosjektoppgave utført semesteret før, og den ble fullført på normert tid.

Oppgaven tar for seg en TDC arkitektur som bruker flere VDLer i parallell for å måle tidsforskjell. TDC arkitekturen oversetter "thermometer"-kode til binærkode uten å bruke konvensjonelle enkodere. I oppgaven brukes både digitale og analoge designmetoder. De analoge designene er implementert med 28nm FDSOI CMOS teknologi, og de digitale designene er implementert ved hjelp av SystemVerilog.

Den foreslåtte TDC arkitekturen er en 6-bits monotonisk TDC med 4.62 lineære bits. TDCen sampler i en hastighet av 110 MS/s over et dynamisk område av 630ps. Prosess og "mismatch" variasjoner er ekstrahert fra det analoge designet, og ikke-lineæriteter er ekstrahert fra det digitale designet. Den foreslåtte arkitekturen har en DNL av +1.4/-1.0 og INL av +1.6/-1.0 som viser fordelen av å bruke parallelle forsinkelseslinjer. Arkitekturen forbruker 0.887 *mW* fra en 0.9V spenningskilde, og opptar 0.0039 *mm*<sup>2</sup>. Resultatene i denne oppgaven er fra målinger tatt fra et "pre-layout" design.

### Abstract

A TDC architecture that uses a multiple VDLs operating in parallel to measure time is discussed in this thesis. The TDC converts the thermometer code to a binary code without using conventional encoders. The thesis took advantage of both analog and digital workspaces, the analog workspace is implemented using 28nm FDSOI CMOS technology, while the digital workspace is implemented in SystemVerilog.

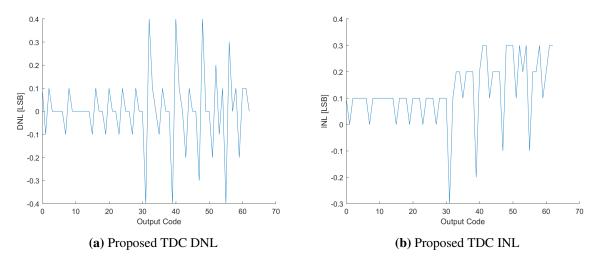

The proposed TDC is 6 bits monotonic TDC, with 4.62 linear bits. The TDC samples at a rate of 110MS/s over 630ps dynamic range. Process and mismatch variation are extracted from the analog workspace, while nonlinearities are extracted from the digital workspace. The proposed TDC has a DNL of +1.4/-1.0 and INL of +1.6/-1.0, which shows the benefit of using parallel delay lines. The TDC consumes a 0.877 *mW* from a 0.9V voltage supply and occupies a 0.0039  $mm^2$ . The results in this thesis are reported from pre-layout measurements.

### Acknowledgements

I want to express my sincere gratitude to Professor Morten Olavsbråten, Engineer Svein Henninen, and Engineer Carolina Velezmoro. Their motivation, support and technical insight have guided me during my master thesis. I would like to take a moment of silence for my late advisor professor Kjetil Arnt Svarstad, who has always been a source of motivation for me.

I wish to show my appreciation for the Norwegian University of Science and Technology (NTNU), and for Nordic Semiconductor to give me the opportunity to use the available tools and for their continuous support. I would like to thanks Aslak Holen, Khalil Gammoh, Somayeh Zadeh, and Harri Kinnunen, whose assistance was a milestone in the completion of this thesis. A special thanks to Yohan Sandvik for assisting me in writing the preface in Norwegian.

Thanks to my parents Ali and Khawla, my dear sisters Farah, Raghad, Duha, Shatha, Gheed, and to my dearest friends Aaliyah, Elias, Giovanna, Khalid, Milla, Musa, Omar, and Saed, for their support and encouragement. They have always been part of my life and part of this thesis.

In the end, I want to thanks everyone and every institution that helped and supported me. I could not have completed my master's degree successfully without it.

# List of Figures

| 2.1                                                                                                                                            | Illustration for Simple TDC                                                                                                                                                                                                                                                                                                                             | 3                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 2.2                                                                                                                                            | Quantization Curve for TDC                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                      |

| 2.3                                                                                                                                            | Block Diagram of Basic Analog TDC                                                                                                                                                                                                                                                                                                                       | 8                                                                                                                      |

| 2.4                                                                                                                                            | Block Diagram of Dual Slope Analog TDC                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                      |

| 2.5                                                                                                                                            | Block Diagram of Basic DL TDC                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                     |

| 2.6                                                                                                                                            | Block Diagram of Vernier Delay Line TDC                                                                                                                                                                                                                                                                                                                 | 11                                                                                                                     |

| 2.7                                                                                                                                            | Block Diagram of RO Vernier Delay Line TDC                                                                                                                                                                                                                                                                                                              | 12                                                                                                                     |

| 2.8                                                                                                                                            | Block Diagram of 5x5 2-D GRO-VDL TDC [1]                                                                                                                                                                                                                                                                                                                | 13                                                                                                                     |

| 2.9                                                                                                                                            | Block Diagram of Stochastic TDC Based on Latches                                                                                                                                                                                                                                                                                                        | 14                                                                                                                     |

| 2.10                                                                                                                                           | Block Diagram of Stochastic TDC Based on DL                                                                                                                                                                                                                                                                                                             | 15                                                                                                                     |

| 2.11                                                                                                                                           | Block Diagram for Calibration of a DL TDC                                                                                                                                                                                                                                                                                                               | 16                                                                                                                     |

| 2.12                                                                                                                                           | 3 Bit Wallace-Tree Encoder Block Diagram                                                                                                                                                                                                                                                                                                                | 17                                                                                                                     |

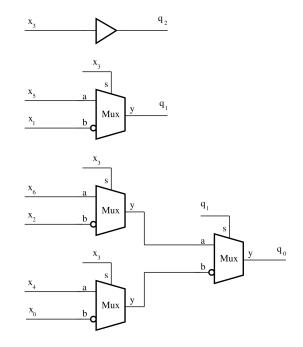

| 2.13                                                                                                                                           | 3 Bit Mux-Based Encoder Block Diagram                                                                                                                                                                                                                                                                                                                   | 18                                                                                                                     |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                        |

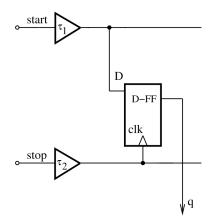

| 3.1                                                                                                                                            | Typical Vernier TDC Segment                                                                                                                                                                                                                                                                                                                             | 21                                                                                                                     |

| 3.1<br>3.2                                                                                                                                     | Typical Vernier TDC Segment                                                                                                                                                                                                                                                                                                                             | 21<br>22                                                                                                               |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                        |

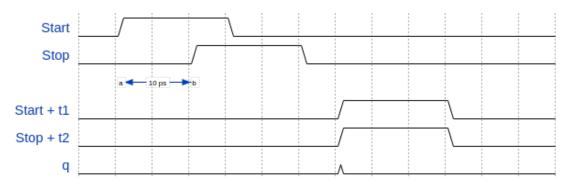

| 3.2                                                                                                                                            | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22                                                                                                                     |

| 3.2<br>3.3                                                                                                                                     | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22<br>23                                                                                                               |

| <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                                                                                  | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22<br>23<br>24                                                                                                         |

| <ol> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ol>                                                                                 | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22<br>23<br>24<br>24                                                                                                   |

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>                                                                    | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22<br>23<br>24<br>24<br>25                                                                                             |

| <ol> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ol>                                                       | Vernier TDC Segment Timing DiagramBlock Diagram for the Proposed VDL TDCTiming Diagram for the Proposed Delay SegmentProposed Delay Segment SchematicLayout for the Proposed Delay Segment with 10ps LSBEarly Attempt Encoder Solution                                                                                                                  | <ul> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> <li>27</li> </ul>                                     |

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul>                                          | Vernier TDC Segment Timing Diagram                                                                                                                                                                                                                                                                                                                      | 22<br>23<br>24<br>24<br>25<br>27<br>28                                                                                 |

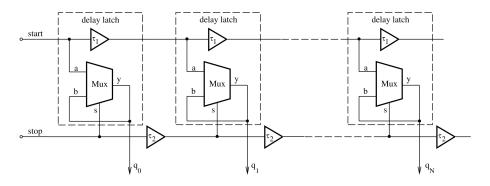

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> </ul>                             | Vernier TDC Segment Timing DiagramBlock Diagram for the Proposed VDL TDCTiming Diagram for the Proposed Delay SegmentProposed Delay Segment SchematicLayout for the Proposed Delay Segment with 10ps LSBEarly Attempt Encoder SolutionModification for the Encoder SolutionProposed TDC Implementation                                                  | <ul> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> <li>27</li> <li>28</li> <li>29</li> </ul>             |

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> <li>3.10</li> <li>3.11</li> </ul> | Vernier TDC Segment Timing DiagramBlock Diagram for the Proposed VDL TDCTiming Diagram for the Proposed Delay SegmentProposed Delay Segment SchematicLayout for the Proposed Delay Segment with 10ps LSBEarly Attempt Encoder SolutionModification for the Encoder SolutionProposed TDC ImplementationTiming Diagram of the Proposed TDC Implementation | <ul> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> </ul> |

| 4.1  | Block Diagram for the Proposed TDC Architecture      | 35 |

|------|------------------------------------------------------|----|

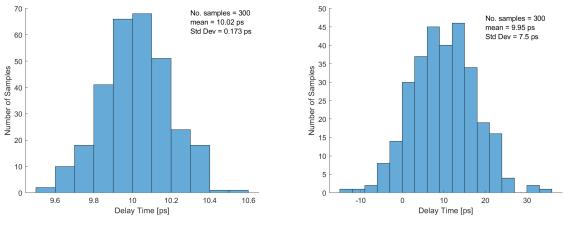

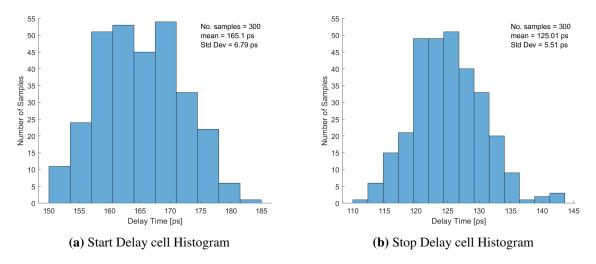

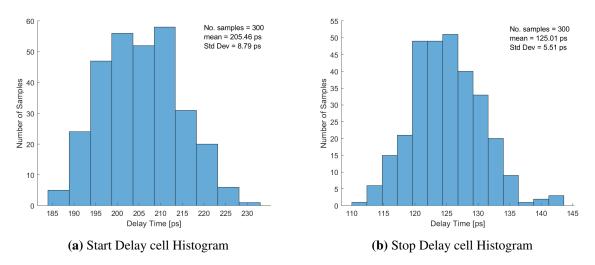

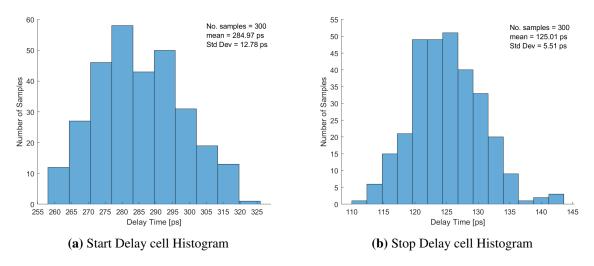

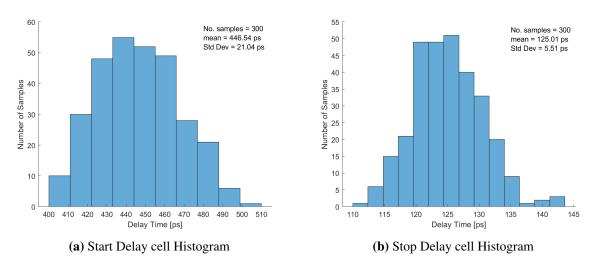

| 4.2  | Monte Carlo Histogram for 10ps Delay Segment         | 36 |

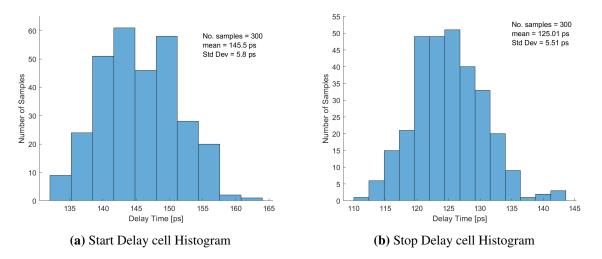

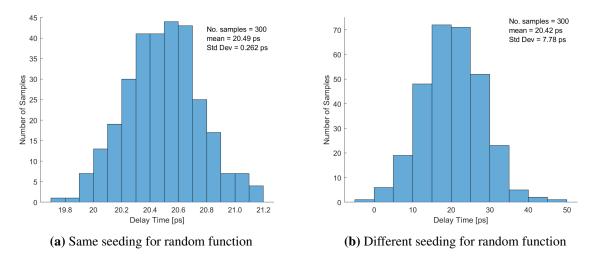

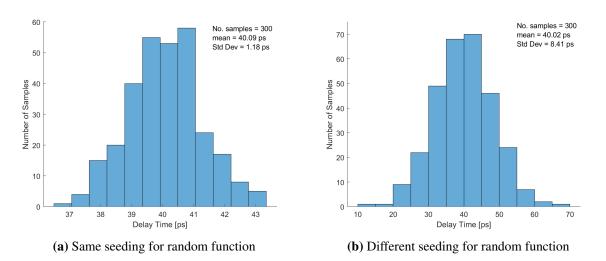

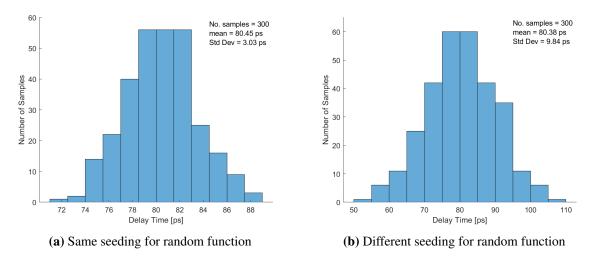

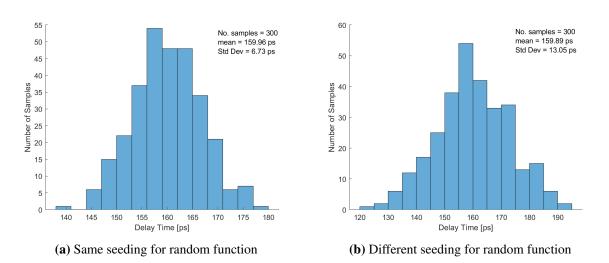

| 4.3  | Histogram for Simulated 10ps LSB Segment             | 37 |

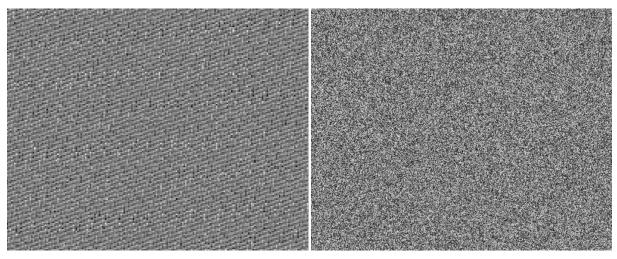

| 4.4  | Grayscale Images for Random Functions                | 40 |

| 4.5  | Grayscale Images for Random Functions                | 41 |

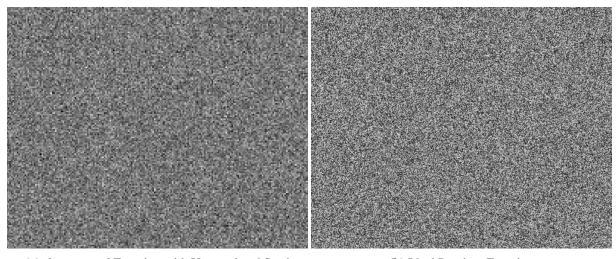

| 4.6  | Proposed TDC DNL                                     | 42 |

| 4.7  | Proposed TDC INL                                     | 42 |

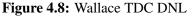

| 4.8  | Wallace TDC DNL                                      | 42 |

| 4.9  | Wallace TDC INL                                      | 42 |

| 4.10 | First Case Scenario DNL and INL                      | 42 |

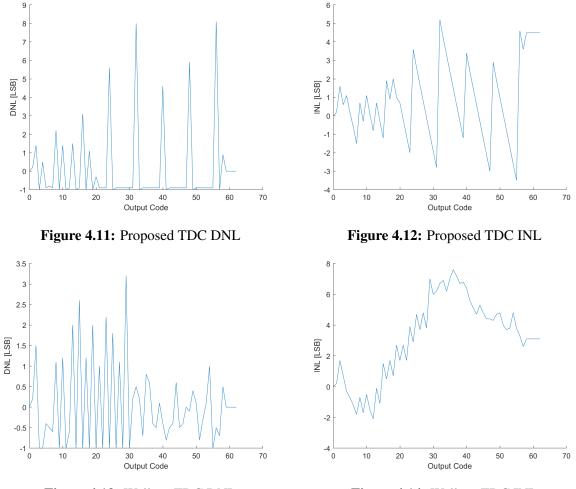

| 4.11 | Proposed TDC DNL                                     | 43 |

| 4.12 | Proposed TDC INL                                     | 43 |

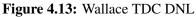

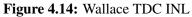

| 4.13 | Wallace TDC DNL                                      | 43 |

| 4.14 | Wallace TDC INL                                      | 43 |

| 4.15 | Second Case Scenario DNL and INL                     | 43 |

| 4.16 | Third Case Scenario                                  | 44 |

| 4.17 | Output From All Delay Lines                          | 45 |

| A.1  | Layout for the proposed delay segment with 20ps LSB  | 65 |

| A.2  | Layout for the proposed delay segment with 40ps LSB  | 65 |

| A.3  | Layout for the proposed delay segment with 80ps LSB  | 66 |

| A.4  | Layout for the proposed delay segment with 160ps LSB | 66 |

| A.5  | Layout for the proposed delay segment with 320ps LSB | 67 |

| B.1  | Monte Carlo Histogram for 20ps Delay Segment         | 68 |

| B.2  | Monte Carlo Histogram for 40ps Delay Segment         | 69 |

| B.3  | Monte Carlo Histogram for 80ps Delay Segment         | 69 |

| B.4  | Monte Carlo Histogram for 160ps Delay Segment        | 70 |

| B.5  | Monte Carlo Histogram for 320ps Delay Segment        | 70 |

| B.6  | Histogram for Simulated 20ps LSB Segment             | 71 |

| B.7  | Histogram for Simulated 40ps LSB Segment             | 71 |

| B.8  | Histogram for Simulated 80ps LSB Segment             | 72 |

| B.9  | Histogram for Simulated 160ps LSB Segment            | 72 |

| B.10 | Histogram for Simulated 320ps LSB Segment            | 73 |

# **List of Tables**

| 2.1  | Comparative Analysis of 5-bits Encoder Architectures | 18 |

|------|------------------------------------------------------|----|

| 3.1  | TDC Initial Specification                            | 20 |

| 3.2  | Delay Segment Component Values and Sizes             | 26 |

| 4.1  | Delay Segments Parameters                            | 36 |

| 4.2  | Delay Segments Variations                            | 37 |

| 4.3  | Segments Resolution Variations (with fixed seed)     | 38 |

| 4.4  | Segments Resolution Variations (with different seed) | 38 |

| 4.5  | Proposed Encoding Circuit Gate Count                 | 39 |

| 4.6  | Simulated Nonlinearities                             | 44 |

| 4.7  | Number of Linear Bits ( $N_{linear}$ )               | 45 |

| 4.8  | Vernier Delay Lines Area                             | 46 |

| 4.9  | Vernier Delay Lines Power Consumption                | 47 |

| 4.10 | Performance Summary and Comparison                   | 48 |

| 5.1  | Proposed Encoding Circuit Vs Wallace Encoder         | 52 |

| A.1  | Capacitor $C_1$ Values for Different Resolutions     | 64 |

# Abbreviations

ADC Analog to Digital Converter. 4, 8

AI Artificial Intelligence. 1

CMOS Complementary Metal Oxide Semiconductor. 1

CV Coefficient of Variation. 37

DL Delay Line. 3

**DLL** Digital Phase-Looked Loop. 1, 2

**DNL** Differential Nonlinearity. 5

**DUT** Design Under Test. 31

ENOB Effective Number of Bits. 5

FDSOI Fully Depleted Silicon on Insulator. 20, 49

GRO Gated Ring Oscillator. 12

**INL** Integral Nonlinearity. 5

LIDAR Light Detection and Ranging. 1

LSB Least Significant Bit. 4

MOM Metal Oxide Metal. 25

NMOS N-Channel MOSFET. 26, 31

**PET** Positron Emission Tomography. 2

PLL Phase Lock Loop. 2

PMOS P-Channel MOSFET. 26, 31

**PVT** Power, Voltage and Process Variation. 1

**RO** Ring Oscillator. 12

SR Set-Reset. 22

**TDC** Time to Digital Converter. 1, 2, 4

**TOF** Time of Flight. 2

VCO Voltage Controlled Oscillator. 8

**VDL** Vernier Delay Line. 11

# Chapter 1

## Introduction

The industry today is pushing for more tasks to be done autonomously (i.e. using robots and Artificial Intelligence (AI)), such as Light Detection and Ranging (LIDAR) used in autonomous cars, Digital Phase-Looked Loop (DLL), and various biomedical applications. Many of these applications require a highly precise time measurement to achieve the expected performance.

Designing a circuit that can achieve a nanosecond or even a picosecond precision can elevate the performance of these systems dramatically [1]. A circuit with such performance should also be compact and power-efficient. Analog building blocks could achieve such a performance, but they often have large area and high power consumption. Digital building block can overcome these drawbacks and offers a more compact, and power-efficient design. Moreover, digital circuits benefit substantially from the advancing of the Complementary Metal Oxide Semiconductor (CMOS) technology.

Time to Digital Converters (TDC) are circuits that convert a time measurement into a digital code. TDCs have become very popular in recent years due to their performance and scaling of CMOS process. The latter one is important since the TDC can be designed using all-digital blocks, which means that the TDC can have the advantages of digital circuits while being tolerant to Power, Voltage and Process Variation (PVT).

The scaling down of CMOS technology combined with architectural improvements made TDC a very attractive choice for systems that depend on time measurement. For example, in communication and mixed-signal systems, recent works [2], [3] have shown a significant increase in the performance by replacing the phase detector in the Phase Lock Loop (PLL)/Digital Phase-Looked Loop (DLL) with a TDC because it is more accurate and area/power efficient. Other applications have adopted TDC to take advantage of their superior performance, such as biomedical imaging using Positron Emission Tomography (PET) technique [4]. Furthermore, the automotive industry took these advantages as well by developing laser rangefinders using Time of Flight (TOF) [5]. Measurement instruments implemented TDC to achieve state of the art instrument accuracy, such as oscilloscopes, logic analyzers, and timing jitter measurement [6] [7].

This work focuses on studying and comparing different TDC architectures and find a suitable implementation for the given specifications. Moreover, study the effects of process variations on the implemented TDC and overcome these variations. The rest of this work is organized as follows; Chapter 2 gives a background on TDC, their classification, and a comparison between different implementations. Based on that, Chapter 3 describes the TDC design and simulation methods. Chapter 4 presents simulation results, Chapter 5 discusses these results and deliver conclusions which are represented in chapter 6.

## Chapter 2

## Theory

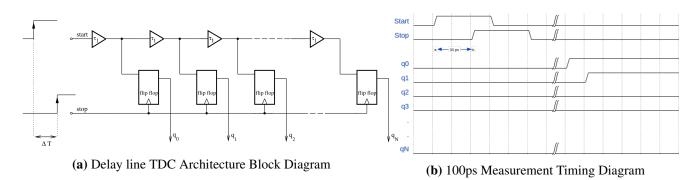

Figure 2.1: Illustration for Simple TDC

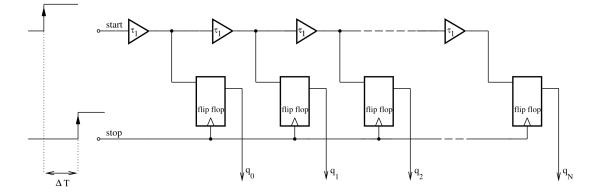

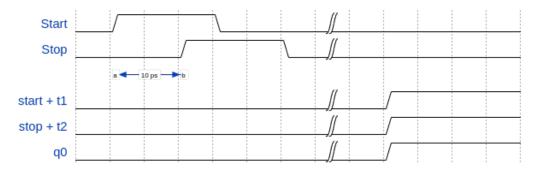

A simple TDC architecture consists of a Delay Line (DL) with a D-flip flop, as shown in figure 2.1 (a). The TDC measures the time difference between start and stop signals ( $\Delta T$ ) by sampling the state of delayed start signal through flip-flops. The output of TDC is a digital word in Unary coding (thermometer code), where the output is represented with n ones followed by zeros. For example, 4 will be represented as (111100...). Figure 2.1 (b) shows the timing diagrams of measuring a 100ps ( $\Delta T$ ) using the previous TDC. The thermometer code output q is (11000...), which is defined by the TDC metrics.

### 2.1 **Performance Metrics**

There are several numbers of TDC architectures, each of which has its advantages and disadvantages. In order to study these architectures some performance metrics should be defined. These metrics will allow a systematic comparison between TDC architectures since these metrics can be applied to any TDC.

#### 2.1.1 Resolution (LSB)

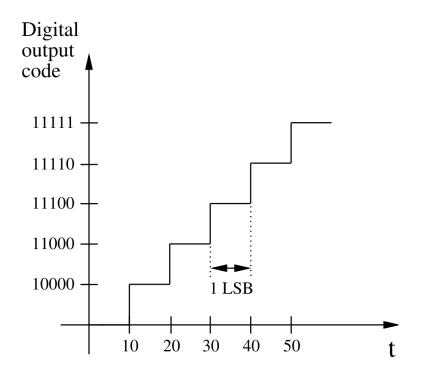

The smallest time difference that a TDC can detect is called the resolution. This difference is converted to a digital output word defined by the term Least Significant Bit (LSB). Since TDC operates similarly to Analog to Digital Converter (ADC), one can look at this metric as the step width of the input-output transfer curve (quantization curve) of TDC shown in figure 2.2. Ideally, step width is defined by the application and it should be constant along the curve. Each step (1 LSB) represents a digital output word increment to a time input increment [8].

Figure 2.2: Quantization Curve for TDC

#### 2.1.2 Non-linearities

Various noise sources affect the performance of TDC, causing the input-output transfer curve to deviate from its ideal values, resulting in a non-linear curve. These errors can come from delay time mismatch of delay cells and PVT variations. Mainly these nonlinearities can be represented as two parameters, Differential Nonlinearity (DNL) and Integral Nonlinearity (INL). Since different noise sources will cause a deviation on the ideal transfer curve, DNL parameter represents the difference between actual and ideal curves. INL, on the other hand, represents the integration of that difference along the transfer curve (DNL) up to the calculation position. In other words, the INL represents the accumulations of nonlinearities along the time conversion. There are multiple techniques to overcome these nonlinearities in TDC, such as architectural manipulation or calibration circuits.

Nonlinearities are measured in LSB, and can predict the behavior of TDC output as in ADC output [8]. Monotonicity means the output of TDC will always increase as input increases. To guarantee that a TDC is monotonic, the maximum DNL has to less than 1 LSB, or the maximum INL has to less than 0.5 LSB. In many cases, the TDC might have a DNL error greater than 1 LSB and still consider monotonic [8]. Monotonicity is essential to some applications where TDC is used in a feedback loop, where a decrease in the digital output code could make the system oscillate. Missing Codes is also an essential behavior for TDC, where if INL is larger or equal to 1 LSB can indicate a missing digital output code from the TDC [8].

#### 2.1.3 The Linear Bits

The Effective Number of Bits (ENOB) is a metric used in ADCs to represents the number of linear bits. Since TDC and ADC are similar in performance metrics, the  $N_{linear}$  is used to represents the effective number of linear bits in a given TDC. This metric is introduced to TDC since it is challenging to generate a pure sinusoidal signal for the inputs of TDC (start and stop signals) [9] [10].  $N_{linear}$  can be calculated using equation 2.1, where N is the number of bits for TDC.

$$N_{linear} = N - log_2(INL + 1) \tag{2.1}$$

#### 2.1.4 Conversion Speed

The process of measuring time intervals and transform it into a digital word requires time; this time is known as the Dead Time, in which TDC cannot perform another measurement during it. In other words, the dead time measures how fast a TDC can perform one measurement. The speed in which is usually called the conversion speed, and it is given as a sample per second (S/s). This metric might be considered essential and that TDC should be designed to operate as fast as possible. However, in reality, the conversion speed depends on the application utilizing the TDC. Some architectures separate the sampling rate from the conversion speed to achieve higher speeds. By separating both operations (i.e. pipelining), TDC could convert a measured time interval into a digital word while sampling a new one at the same time [11].

#### 2.1.5 Dynamic Range

Since TDC measure time, the maximum interval that can be measured is defined as the dynamic range. This parameter depends on the LSB and TDC architecture. In basic concepts, a higher dynamic range means that TDC can detect a broader range of measurements. This will reflect, on the LSB and conversion speed for some architectures, thus causing TDC to become slower since the measured signal has to propagate longer in TDC before it gets converted into a digital code. As with conversion speed, the wight of this parameter in designing a TDC is application dependent as well.

#### 2.1.6 Area and Power

As for most CMOS designs, area and power consumption are considered essential parameters. Especially with the advancing of technology and the need for more efficient chips in recent years. Different architectures will have better performance metrics than others but at the cost of area and power. In order to have a more compact design, the area and power for the desired circuit must be considered before implementation because the architectural implementation has a significant effect on them.

#### 2.1.7 Noise

Noise sources in TDC come from transistors changing the signal delay time in each stage due to jitter and PVT variations. This will cause the output of TDC to vary around the expected value for the same input. The variations of TDC output generally follow Gaussian distribution [1], which can be estimated by calculating the standard deviation (sigma) for each source.

#### 2.1.7.1 Jitter

Jitter is a random noise added to signal from each stage by its transistors. This noise is represented as Gaussian distribution. Usually, for TDC, the jitter is less than 1% of the nominal delay; thus, it can be ignored.

#### 2.1.7.2 Process and Mismatch

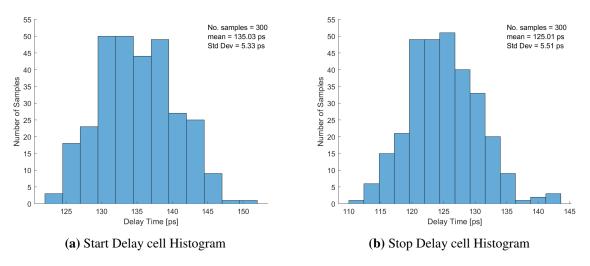

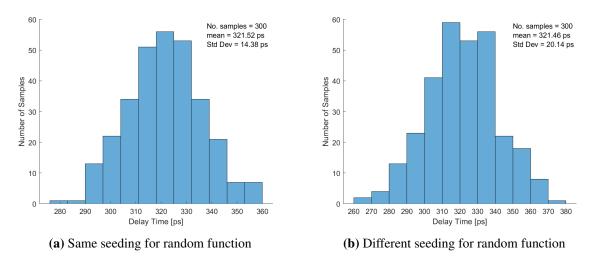

The delay times of different cells cannot be the same since no two transistors can be alike. These changes are caused by process and mismatch variations, where process variations represent changes between two transistors on different silicon wafers for the same circuit. Mismatch, on the other hand, is the difference between transistors on the same silicon wafer. These variations come from imperfections in transistors fabrications and can be modeled as Gaussian distribution using Monte Carlo simulations [12]. These effects will be studied further in this work.

#### 2.1.7.3 Supply Voltage Variation

Supply variations affect the speed of the transistors in the circuit, thus changing the overall performance. These variations are ignored in this work by assuming a well designed band-gap voltage supply is available.

#### 2.1.7.4 Temperature Variation

The temperature change affects the threshold ( $V_{th}$ ) of transistors, which will reflect on their speed and the overall performance of TDC. However, in this work, the temperature is considered fixed at 27°

### **2.2 TDC Architectures**

TDC measures time intervals between two different signals (i.e. START and STOP); for some applications such as DLL/PLL, TDC is used to lock the loop by comparing the output frequency with a reference frequency to use it as a control signal for the Voltage Controlled Oscillator (VCO). However, in this work, the input signals (START and STOP) will be provided from the same source. Since there are various architectures, there is no general operation for TDCs, and every architecture performs the time measurement differently. These variations mean that performance metrics of a TDC are defined by the time measurement technique (architecture of the TDC). In other words, the overall performance of a system that uses time measurements depends significantly on the TDC architecture. In the following section, popular architectures will be presented along with how they operate and their pros and cons. Finally, a comparison will be made to discuss and select a suitable architecture for this work.

#### 2.2.1 Analog-type TDCs

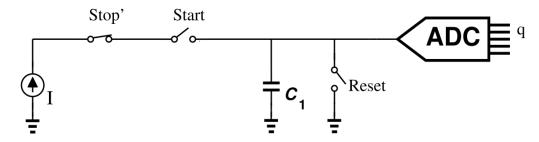

Analog architectures are considered to be the first generation of TDCs. The most straightforward approach is to change the charge in a capacitor with respect to time differences (i.e. convert the time to voltage level), as shown in figure 2.3. Then convert this voltage into a digital code using either an ADC or a voltage comparator. Although this method is a straight forward, the resolution and the dynamic range depends on the number of bits for the ADC (the resolution of the ADC), which limits TDC performance [13].

Figure 2.3: Block Diagram of Basic Analog TDC

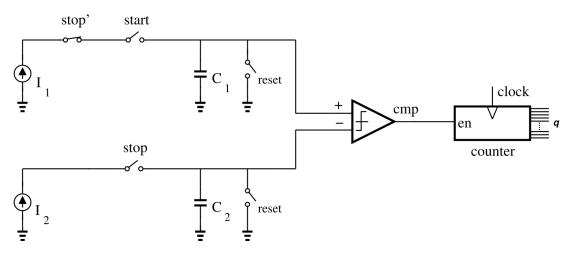

To improve the resolution, dual-slope (pulse stretching) architecture is developed, where a voltage comparator and a second capacitor ( $C_2$ ) are introduced, as shown in figure 2.4. During the measurement of the time interval, the voltage on the positive node of the comparator is larger than the negative node. This difference will make the output of the comparator to be +1. When the stop signal comes, the current source  $i_2$  will start to return the output voltage

Figure 2.4: Block Diagram of Dual Slope Analog TDC

of the comparator to zero. Using a counter with a known reference clock, the time needed to compensate for the voltage difference on the node can be measured, which represents the time interval. This method can achieve high time resolution and high dynamic range [14].

Time-Amplifier architecture (TA) is introduced to improve the resolution of TDC by having coarse-fine measuring paths. TA TDC takes the residue of time measurement from the coarse path and amplified it to be measured again. Architecture that uses TAs has an excellent resolution, such as [15]. However, the main disadvantage is that time-amplifiers have a small linear region in which they can operate, which results in a very narrow dynamic range [1].

Although analog TDCs offer good metrics, they still suffer from PVT variations, high INL for long-dynamic range, require careful design and take large area [1], which makes them unpopular in modern CMOS design.

#### 2.2.2 Digital-Type TDCs

Digitally implemented TDCs overcome the drawbacks of the analog implementations and achieve the same or even better metrics as CMOS technology advances. There are many techniques to implement digital TDC; the simplest is to count the number of ticks for a reference clock during the time interval. However, to achieve high resolution, a very accurate Giga-Hz reference clock and a compatible counter are needed, which is not practical in real-life applications.

#### 2.2.2.1 Delay Line TDC

Figure 2.5: Block Diagram of Basic DL TDC

In order to obtain a high-resolution TDC without the need for an accurate clock signal, a delay line can be placed in the start signal path with the output of every delay element is connected to a flip-flop as shown in figure 2.5. To measure a time interval, the start signal has to propagate through the delay line within a specific delay time ( $\tau_1$ ) added by each delay cell, and when stop signal toggles to one, it will latch all the outputs of the delay line. The final output word will be a thermometer code with every one represents a single time measurement (LSB =  $\tau_1$ ). For example, if  $\Delta T$  is 30ps, and the resolution (LSB) is 15ps, each delay cell will add 15ps delay to the start signal until stop signal becomes one. The output q, in this case, will be (11000...). The drawback of delay line TDCs is the limitation on their resolution (LSB), which is limited by the minimum propagation delay of transistors. Moreover, it requires calibration against PVT, and it is only suitable for a short dynamic range [1].

#### 2.2.2.2 Vernier Delay Line TDC

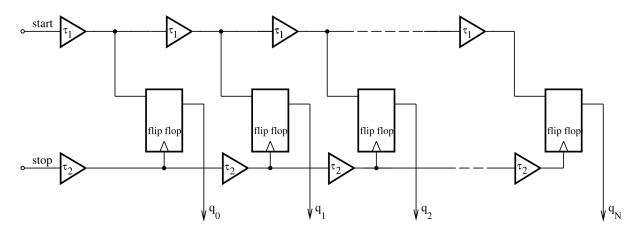

The Vernier Delay Line (VDL) overcome technical limitations on the resolution by introducing a faster second delay line for the stop signal, as shown in figure 2.6. A sub-gate resolution is now achievable through the difference between delay lines cells  $LSB = \tau_1 - \tau_2$ , where  $\tau_1$  and  $\tau_2$  are the delay for cells in the start line and stop line, respectively. For example, if  $\Delta T$  is 15,  $\tau_1$  and  $\tau_2$  are 20ps and 15ps, respectively. The resolution (LSB) will be 5ps; each signal will experience different delay times while propagating. Since the stop signal will propagate faster, it will catch up with the start signal at  $q_2$  and sample the outputs of the flip-flops. The output q, in this case, will be (11100...).

Furthermore, since the resolution is the difference in the delay time, the VDL architecture can compensate first order PVT variation if the two delay lines are well-matched [16]. Although the VDL implementation solved the resolution issue, it still requires an exponential increment in the number of stages to increase the dynamic range  $(2^N)$ .

Figure 2.6: Block Diagram of Vernier Delay Line TDC

#### 2.2.2.3 Ring Oscillator Vernier TDC

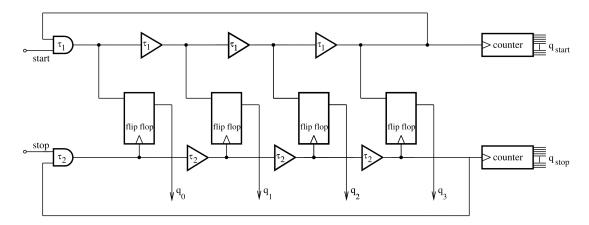

Ring Oscillator (RO) VDL solves the dynamic range issue of the normal VDL while maintaining a high resolution. By looping back the input signals (i.e start and stop) around and connects the end of the loop to a counter, as shown in figure 2.7. The counter output will indicate how many times the signals have passed, thus increasing the dynamic range dramatically, which will depend on the counter output and the number of delay stages. However, this architecture has worse nonlinearities, since noise and jitter will be accumulated throughout the ring [1].

Figure 2.7: Block Diagram of RO Vernier Delay Line TDC

Gated Ring Oscillator (GRO) VDL architecture [17] is introduced to eliminate the noise accumulation problem, by adding an enable signal to the delay cells in the fast and slow delay lines for the TDC in figure 2.7. The enable signal will be on at the beginning of measurement and will make the delay lines work as regular oscillators. When stop signal catches up with start signal, the enable will be off, thus saving the current values of delay cell nodes. Any new measurement starting point to be the ending point of the previous one, which will make the residue at the end of the previous measurement transfer to the new one. This transfer will provide first-order noise shaping and reduce the mismatch between delay cells [1], [18]. The drawback of GRO is the need for holding previous values until the next measurement starts. This means the need for a capacitor with low leakage to keep old values valid, which is difficult to obtain in modern CMOS process. Moreover, even if the first-order noise is eliminated, the GRO architecture still requires calibration against PVT variations.

#### 2.2.2.4 Two Dimensional TDC

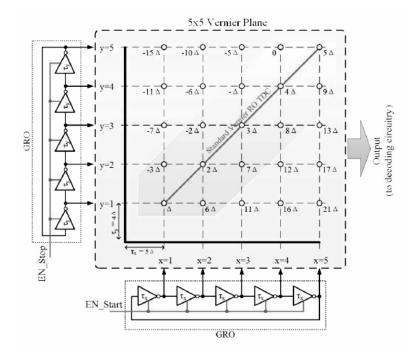

Another method for improving the narrow dynamic range for VDL is 2-D architectures VDL [19], which solves the dynamic range issue by constructing a two-dimensional matrix from the output of GRO vernier delay lines as shown in figure 2.8. This architecture makes the growth in the delay line elements to the  $\sqrt{N}$  instead of exponentially (2<sup>N</sup>) while maintaining a high resolution (LSB). Figure 2.8 shows the output matrix of the 2-D GRO VDL, where the diagonal line represents the output expected from the normal VDL (i.e. $\Delta = LSB$ ) and the lower-half part represents the extended delay using the slow chain. The upper-half part, however, represents invalid measurements, where the stop signal will arrive before the start signal.

For example, if  $\Delta T$  is 60ps,  $\tau_x$  and  $\tau_y$  are 50ps and 40ps, respectively. The resolution will be 10ps. In the beginning, for the time measurement, the control circuit will enable both GROs. Both signals will circulate since  $\Delta T$  is larger than 50ps; at X = 2, and Y = 2 stop signal will pass start signal, which will set the enable to off. An encoding circuit will detect the signals circulation and modify the coordinates with respect to the number of circulations, decrementing Y by one in this example. The final coordinates for the Vernier plane are X = 2 and Y = 1, which indicate 6 LSB (60 ps). Although this architecture improves the dynamic range, the overall complexity of TDC increases, plus the need for advanced control and decoding circuitry.

Figure 2.8: Block Diagram of 5x5 2-D GRO-VDL TDC [1]

#### 2.2.2.5 Stochastic TDCs

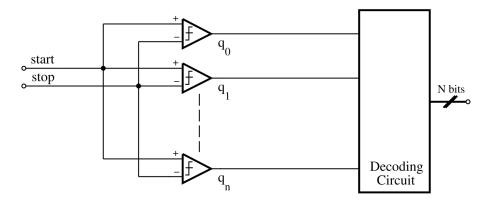

All TDCs will have mismatch and jitter between different stages, which affect the performance of most TDCs. Nevertheless, stochastic architecture takes this drawback and uses stochastic properties to achieve high resolution and stability. The stochastic TDC implemented in [20] uses a set of latches known as arbiters  $(q_0 - q_n)$  shown in figure 2.9, with different offset voltages  $(V_{th})$  which represents process variations. When the start signal crosses the voltage  $(V_{th})$  of a latch before the stop signal, the output of that latch will be +1; otherwise, it will be -1. Since all latches are identical, their cumulative summation of input voltage offsets follows a normal or Gaussian distribution. This will produce a resolution equal to  $\frac{\sqrt{2\pi} * \sigma_{vth}}{2^N - 1}$ , where  $\sigma_{vth}$  is the standard deviation of the offset voltage  $(V_{th})$  and the  $2^N - 1$  represents the number of latches. Even though this TDC takes advantage of process variations, it stills suffers from PVT variations and requires calibration to overcome it[21].

Figure 2.9: Block Diagram of Stochastic TDC Based on Latches

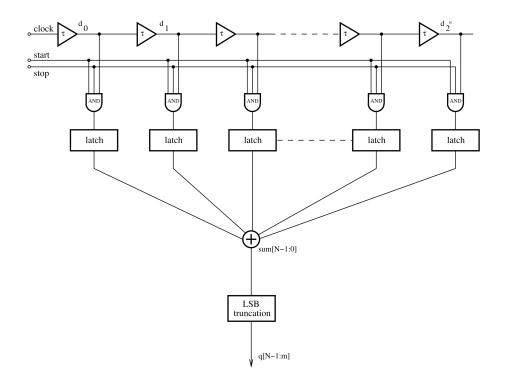

Recent developments in the stochastic TDC, such as [22], has overcome the PVT variations without the need for calibration. Figure 2.10, shows the implementation of the architecture, which counts the number of edges  $(d_n)$  produced by a fast refrence clock (i.e. 850MHz) in the delay line during the start and stop signals. Since the random mismatch and jitter will have a Gaussian distribution across all edges and delay cells, the summation of the output from the delay line will have a uniform distribution. Thus PVT variations will only change the delay for delay cell, not the distribution of the edges. This ensures that the total number of edges will stay the same across different corners. Furthermore, to achieve higher resolution and eliminate irregularities, an LSB bits truncation circuit is also implemented since most PVT variations will affect the lower bits of the TDC output code (the fine measurement). This architecture has shown excellent performance and resilient to variations. However, to achieve high characteristic

Figure 2.10: Block Diagram of Stochastic TDC Based on DL

distributions of PVT variations and jitter, the delay line has to be extremely long. For this TDC to achieve these characteristics, the delay line has to have  $2^{14}$  delay cells. Furthermore, the authors of [22] did not prove the distribution of variations mathematically, and the LSB truncation shows that they have designed a TDC with femtosecond resolution to obtain measurements in picoseconds (i.e. using a stopwatch to count years).

### 2.3 TDC calibration

Since most TDC architectures suffer from PVT variations, which can degrade TDC performance, calibration circuits or methods are necessary to maintain a consistent TDC performance over PVT variations. The need for such circuitry is considered one of the most significant drawbacks to TDC because calibration circuits are often complex and require a big area [23].

Calibration schemes vary widely depending on TDC architecture. Often, TDC is used along PLL/DLL to replace the phase detector found in them. Since the clock signal of the PLL/DLL is always running and experience the same PVT variations, it can be used to calibrate the TDC using a control voltage delay cells, thus improve the overall accuracy. The feedback loop in [24] uses a DLL to improved the overall resolution and linearity dramatically of TDC to become 60 ps with +/- 1 LSB accuracy.

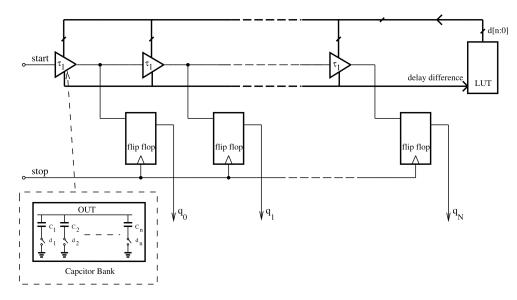

PVT variations affect the delay time of each cell in TDC differently; authors in [18] uses a different approach to calibrate TDC, as seen in figure 2.11. Using a circuit which can output the difference between the ideal delay and actual delay of the cells, by measuring the differences from outside the chip or by having a very accurate cell (ruler cell) to compare with, as in [25]. This difference is then used in a lookup table to get a digital calibration code that corresponds to that difference. This code will be substituted to a capacitor bank connected to each delay cell, which adjusts the total delay of the cell.

Figure 2.11: Block Diagram for Calibration of a DL TDC

### 2.4 Thermometer-to-Binary Encoder

Most TDC produces the output of the time measured as a thermometer code; an encoder is necessary to convert the time measurement to a binary-weighted code. The method for encoding the output of the TDC can affect the performance due to Bubble-Error, where some invalid transitions in TDC could cause the thermometer code output to have unsystematic 1s or 0s. For example, if a TDC measured a 40ps period with a resolution (LSB) of 10ps, the ideal thermometer code output should be (111100000...). However, the realistic (actual) code will be like (111100100...) or (11010000...) because of meta-stability errors, mismatch, and cross-talk [26].

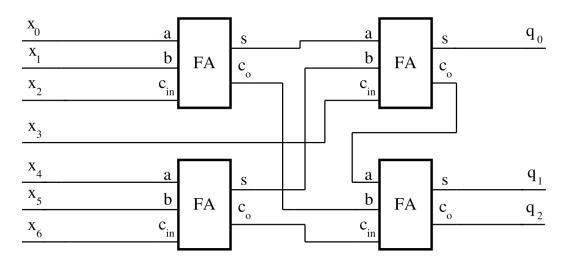

Figure 2.12: 3 Bit Wallace-Tree Encoder Block Diagram

The main contrasts between different encoders are speed, power consumption, and circuit complexity. The most straightforward architecture is the Wallace tree encoder, which counts the number of ones in the thermometer code using a  $[2^N - (N+1)]$  full-adders, as shown in figure 2.12, where N is the number of encoded bits. This architecture is used widely in TDC due to its ability to correct bubble-error [26].

Another approach for encoding thermometer codes is a multiplexer based encoder, which uses  $2^{N-1}th$  bit of the output code (pivot bit) to obtain binary-weighted code, as shown in figure 2.13. The number of multiplexers used in this approach is similar to the number of full-adders used in Wallace-Tree encoder. The work is done in [27] shows that Mux-Based encoders are less-complex and have lower power consumption than Wallace-Tree. However, it cannot correct bubble-error.

Figure 2.13: 3 Bit Mux-Based Encoder Block Diagram

Fat-Tree encoder is also a simplified approach used in TDC, where NOR gates are used to generate an intermediate code known as a one-hot code that contains no more than one logical one. For example, if the thermometer code of a TDC is (1110000), the one-hot code will be (000100), where the position of the logical one will be converter using NOR and NAND gates to represent the binary word which is (0011) in this case. One advantage of using Fat-Tree encoder is Bubble-Error correction but not to the level of Wallace-Tree [28].

Table 2.1 shows a detailed compression between different encoders architecture conducted by [28]. From the table, it can be seen that even if some encoders offer error correction to the output, using such a circuit will increase the size, power consummation while decreasing the speed of a TDC.

| Table 2.1: Comparative Analysis of 5-bits Encoder Architectures |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| Architecture         | Number<br>of transistors | Average dynamic current current, $\mu A$ | Maximum delay<br>time, ps |

|----------------------|--------------------------|------------------------------------------|---------------------------|

| Wallace-Tree encoder | 624                      | 585                                      | 1276                      |

| Mux-Based encoder    | 114                      | 261                                      | 817                       |

| Fat-Tree encoder     | 392                      | 286                                      | 471                       |

### 2.5 Motivation and Selection

The previous sections sum up the available architectures for TDC today. The selection methodology is based on the nature of this work, which focuses on the higher-level implementation and investigates the existed TDC architectures. Furthermore, experimenting with different ideas to reduce the overall complexity and improve the performance of TDC. From the previous, the most applicable architecture for this work is Vernier Delay Line (VDL) TDC. The VDL is a digital-based TDC with high resolution, usually in 10th ps and +/-1 LSB DNL [29]. Moreover, being a digital-based decreases development time, power consumption, and circuit area. Nevertheless, VDL TDC uses complex components such as flip-flops and encoders, which reduce its efficiency in measuring large time intervals.

## **Chapter 3**

### **Design and Simulation Methodologies**

The ongoing investigation in this work suggests in order to reduce the complexity of VDL TDC, it is desirable to investigate further down from the higher-level implementation of the TDC. This implies to explore various delay segments at transistor level and find a way to reduce the overhead complexity added by the delay segments, encoders, and calibration circuits. Specifications for the TDC are shown in table 3.1; these specifications are chosen arbitrarily to have a start point for the design process and guide the workflow of the project. The design and simulations for TDC at the transistor level are performed using a commercially available 28*nm* Fully Depleted Silicon on Insulator (FDSOI) CMOS process, with 0.9V supply voltage.

| Property                | Goal      |

|-------------------------|-----------|

| Architecture            | VDL       |

| Resolution (LSB)        | 10ps      |

| <b>Conversion Speed</b> | 100MS/s   |

| Dynamic Range           | 630       |

| Number of Bits          | 6         |

| DNL/INL                 | +/- 1 LSB |

| Power Supply            | 0.9 V     |

| Area & Power            | minimum   |

Table 3.1: TDC Initial Specification

### **3.1 Delay Segment**

Most implementations of VDL TDC use two delay cells and a D-flip flop to sample the time difference as shown in figure 3.1. In general, all flip-flops have delay, setup, and hold times known as timing parameters, [30] and [31] define these parameters as:

- **Delay Time:** (i.e. propagation time); the required time for a signal to propagate from the input (D) to the output (q) when a leading edge of a clock triggers the (clk) terminal.

- Setup Time: the required time for a signal to be stable at the input (D) before a leading edge of a clock triggers the (clk) terminal.

- Hold Time: the required time for a signal to be stable at the input (D) after a leading edge of a clock triggers the (clk) terminal.

Figure 3.1: Typical Vernier TDC Segment

Using a D-flip-flop in the delay segment can cause drawbacks to TDC, such as increasing area and power consumption while decreasing TDC speed. Nevertheless, violating setup and hold times will make the flip-flop output to be in meta-stability status, where the output (q) will have an undefined value (X). This can be very problematic for TDC design since setup times for flip-flops are in hundreds of picoseconds. For example, the D-flip-flops reported in [32] have a setup time of 137ps and 197ps, if a 10ps time interval to be measured using a Vernier TDC with 10ps resolution (LSB); which implies that the time difference between the start and stop delay elements should be 10ps. When the time signals (i.e. start and stop) propagate through the TDC, the output of the flip-flop in figure 3.1 will be zero instead of one after the time sampling. This can be illustrated through the timing diagram shown in figure 3.2. Since the stop signal propagates faster than the start signal, both signals will catch-up at the end of the time measurement which can cause an error in the time reading as in this case or causing the flip-flop to enter a meta-stability status if the start signal does not fulfill the setup and hold times. Thus using a standard flip-flop can deteriorate TDC performance. The work done in [19] acknowledged the limitation and utilized a Time-Comparator based on a Set-Reset (SR) latch to resolve this issue. However, even with improved architectures, the setup and hold time of flip-flops will still vary with PVT variations, which adds more varying parameters to consider for TDC.

Figure 3.2: Vernier TDC Segment Timing Diagram

#### 3.1.1 Proposed Vernier Segment

The proposed vernier segment is based on work done in [33], which uses a standard 65nm CMOS technology. The proposed segment consists of a latch integrated within the delay lines, as shown in figure 3.3. The delay latch is modeled as a zero delay multiplexer and a delay cell with the start signal directly connected to the input (a). When the select terminal (s) is low, the latch is transparent (output y = a), and when (s) is high, the latch will hold its output value.

Figure 3.3: Block Diagram for the Proposed VDL TDC

Assuming  $(\tau_1 > \tau_2)$ , in the begin of a time measurement cycle, both signals (start and stop) are zeros, and all delay latches are transparent with zero outputs when the start signal begins to propagate through the delay latch, it will increase the thermometer code (q). The stop signal begins to propagate after time  $\Delta T$ , catching up with the start signal and setting the delay latches into their hold status. At the delay stage where the stop signal passes the start signal, it will set that delay latch to non-transparent status, holding zero output value, thus holding the start signal and finishing the time measurement. Therefore, the output thermometer code (q) is linearly dependent on the time difference of  $\Delta T$  (linear thermometer code versus delay).

The integration of the latch within the delay cells eliminates the metastability issue, since output of latch and output of start delay cell will be one at the same time. Recall the previous example, where  $\Delta T$  is 10ps, the TDC has an LSB of 10ps, and that both delay cells have a propagation delay of 210ps and 200ps delay time for ( $\tau_1$  and  $\tau_2$ ), respectively. Since the start signal is connected directly to the multiplexer, the output ( $q_0$ ) will be set to high after 210ps (i.e. setup time), which is within time stop signal propagates through the delay cell as shown in figure 3.4. For the next stages, the stop signal will be ahead of the start signal causing the rest of latches outputs to be zeros, thus terminating the time measurement.

Figure 3.4: Timing Diagram for the Proposed Delay Segment

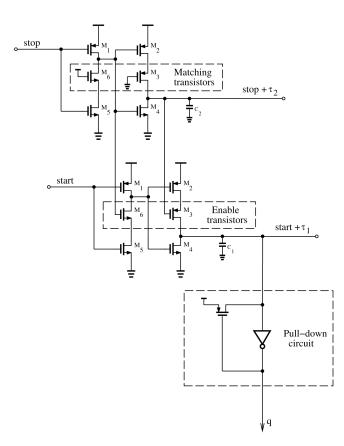

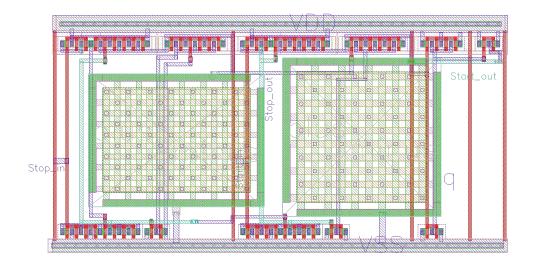

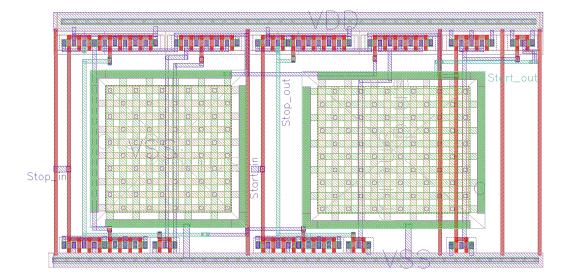

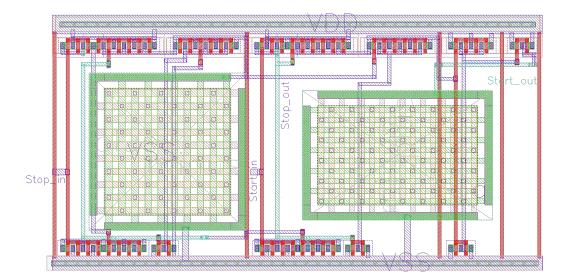

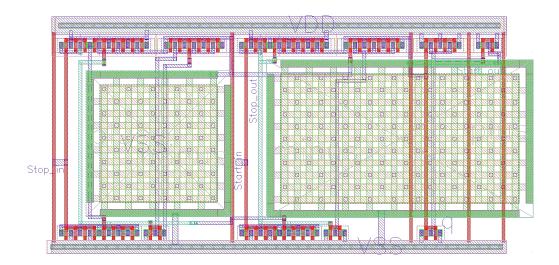

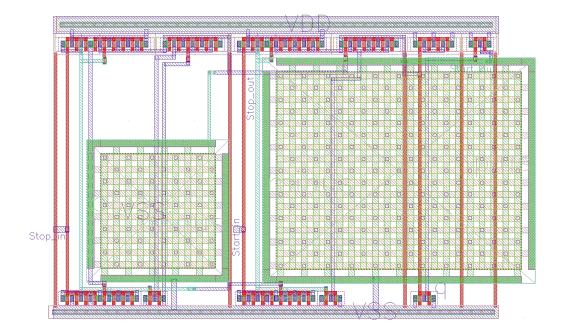

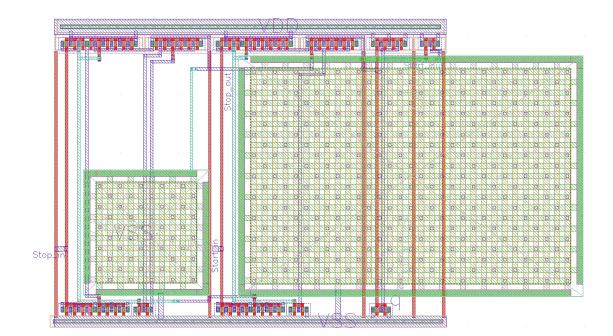

The implementation of the proposed delay segment at the transistor level and its layout are shown in figures 3.5 and 3.6, respectively.

Figure 3.5: Proposed Delay Segment Schematic

The delay cell is implemented by cascading two dynamic inverters plus connecting a Metal Oxide Metal (MOM) capacitor to the output node; the purpose of the capacitor is to control the delay time. The latching mechanism is performed by enable transistors, which are controlled by the delayed stop signal. When stop signal is zero, gate voltages for the enable transistors ( $M_6$  and  $M_3$ ) are logical high and logical low, respectively. Hence, making the start delay latch works as an ordinary non-inverting delay element. After stop signal becomes high and propagates through the delay cell, gate voltages for the enable transistors in the delay latch toggles removing the paths to supply and ground for the inverters. The output of the delay latch (q) becomes a floating node, thus holding its current value. Note that the output thermometer code (q) in the proposed delay segment is inverted, hence the pull-down circuit. Nevertheless, this can be adjusted easily using an inverter.

Figure 3.6: Layout for the Proposed Delay Segment with 10ps LSB

The pull-down circuit in figure 3.5 acts as a buffer driving the thermometer-to-binary encoder [33]. As for matching transistors ( $M_6$  and  $M_3$ ), their purpose is to assure that the two delay line are well-matched, thus compensating for PVT variations [16]. The proposed delay latch requires four transistors (two identical sets of  $M_6$  and  $M_3$ ) in delay cells, to perform the latching mechanism of the thermometer output code, which is 18 transistors less than the D-flip-flop used in [32], and eight transistors less than the Time Comparator implemented in [19]. This results in a more power-efficient and smaller size TDC [33].

Transistors sizes for the proposed delay segment are summarized in table 3.2. Initially, they are taken from [33] and modified to match the differences in technologies used. Throughout the designing process, sizes is increased to reduce the effect of process variations. These increments are based on, the square root of the transistor area (i.e. A = W \* L) is inversely proportional to the process variations [34], and personal observation of various simulation runs. The length (L) of all transistors is set to 45nm (1.5 times the minimum length) to reduce the leakage current [35], which necessary for this implementation since the output of the delay latch (q) becomes a floating node and must maintain its value. Nevertheless, these increments will create a trade-off between process variations and cell leakage against the area, power, and speed [34] [35]. The values for capacitors ( $C_1$  and  $C_2$ ) are set to achieve the required resolution (LSB) of 10ps.

| Element    | Туре      | <b>W</b> (μm) |

|------------|-----------|---------------|

| $M_1$      | PMOS      | 0.3           |

| $M_2, M_3$ | PMOS      | 0.6           |

| $M_4$      | NMOS      | 0.2           |

| $M_5, M_6$ | NMOS      | 0.4           |

| $C_1$      | Capacitor | 4.4 fF        |

| $C_2$      | Capacitor | 4.1 fF        |

Table 3.2: Delay Segment Component Values and Sizes

## 3.2 Less Complex Approach of Encoding

An essential building block for any VDL TDC is the thermometer to binary encoder, but as mentioned earlier, these encoders often add an overhead complexity and increase size and power consumption. The authors of [33] reported that the multiplexer based encoder used in their TDC accounts for approximately 50% and 60% of the total area and the dynamic power, respectively. These figures raise an important question; is there any way to design a more efficient encoder? Or is this block necessary for TDCs? Can it be replaced by a smarter design?

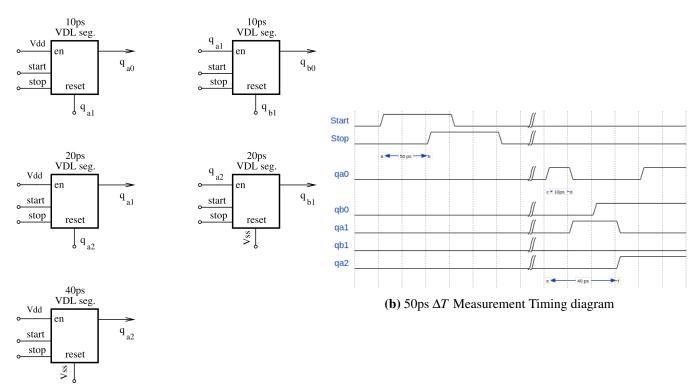

The original need for the encoder block in a TDC comes from the usage of delay lines with sampling latches. These lines produce the output as a thermometer code with the weight of the resolution (LSB) is represented for every logical one in the code, not as a binary-weighted digital code. In other words, if a TDC has an LSB of 10ps and the measured time difference ( $\Delta T$ ) is 320ps, by using a thermometer code, the output will be a 32 bits code (111.....111) since every bit represents a 10ps measurement. Whereas, if a binary-weighted code is used, it will only require 6 bits code (100000) to represents the same measurement. From that, it is evident that by modifying the architecture of the VDL TDC, one can overcome this issue. Three main architectures are implemented using Verilog-A, where only one architecture proves prudent to be implemented at the transistor level.

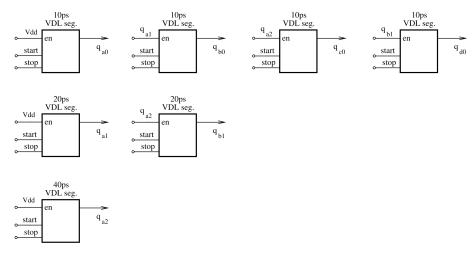

Figure 3.7 (a) shows a high-level implementation of an early attempt for solving the encoder issue. It consists of a modified VDL segment with different resolutions running in parallel. The segments have an enable pin (en), and a reset pin to control the start signal, a simple delay cell for the stop signal, and a latch for sampling the measured time. The configuration in figure 3.7 (a) gives a 3 bits TDC with 10ps LSB using only 5 Vernier segments.

(a) TDC Architecture Block Diagram

Figure 3.7: Early Attempt Encoder Solution

The simplicity of this design comes from the ability to control the start signal propagation (enabling and resetting), while the stop signal propagates. A 50ps time difference ( $\Delta T$ ) measurement timing diagram is shown in figure 3.7 (b), where the output of the  $q_{a0}$  segment (i.e. 10ps LSB), is controlled by the output of  $q_{a1}$  segment (i.e. 20ps LSB) and so on. When  $q_{a1}$  becomes high (which indicates a 20ps measurements), it will enable the  $q_{b0}$  segment to measure the last 10ps and reset  $q_{a0}$  segment. The output code can be extracted as a binary code by using simple logic gates. However, it is found out that designing such a Vernier delay segment to produce an accurate enable and reset signal is complicated at the transistor level. Furthermore, since TDC has 10ps resolution, the Vernier segment must be capable of resetting within this time to be able to measure the next 10ps.

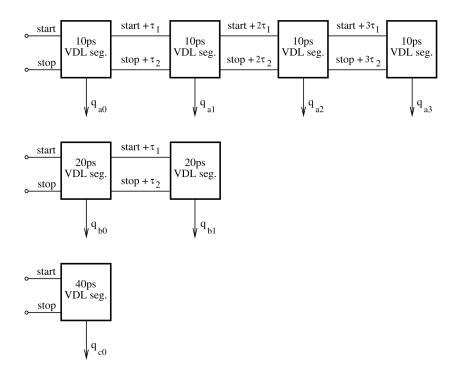

Figure 3.8: Modification for the Encoder Solution

Since matching between the reset and enable signal is difficult, a modification to the previous implementation is done by removing the reset pin for segments and adding two 10ps segments, as shown in figure 3.8. These modifications result in a simpler design for the Vernier segment and remove the requirement for resetting within 10ps. The implementation works in similar way as figure 3.7 (a), but with a difference that the 40ps segment ( $q_{a2}$ ) will enable  $q_{b1}$  and  $q_{c0}$ . Another way to look at it, that the 40ps segment ( $q_{a0}$ ) will start the fine measurement using the  $q_{b1}$ ,  $q_{c0}$  and  $q_{d0}$ . Nevertheless, the main problem for this implementation on the transistor level is relying on the enable signal to start the next measurement. For example, if the time difference is 30ps,  $q_{a1}$  will become high indicating a 20ps measurement which will enable the 10ps ( $q_{b0}$ ) segment. However,  $q_{a1}$  will not be logic one until the start signal propagates through it. This propagation delay will result in the start and stop losses of the time difference between them (both of the signals will be high at the time the enable signal comes), thus losing time information.

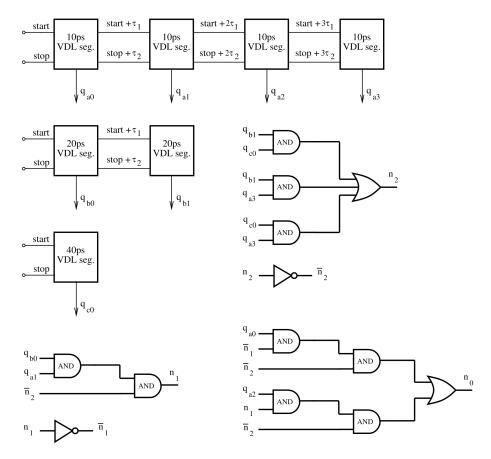

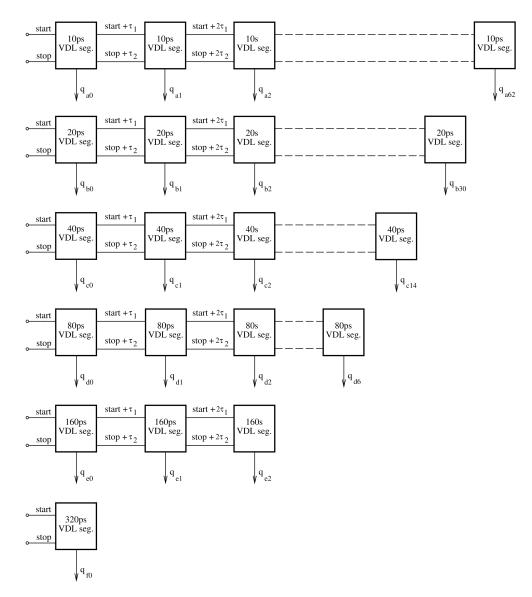

### 3.2.1 Proposed method for encoding

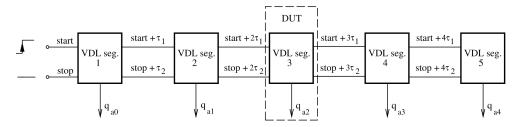

Figure 3.9 shows the proposed TDC implementation, which solves all of the previous issues by implementing multiple (parallel) VDLs with different resolutions measuring the time difference in parallel. The resolutions for the lines have to be in the power of  $[(2^n) * LSB]$ ; this will simplify the encoding producer for thermometer codes.

Figure 3.9: Proposed TDC Implementation

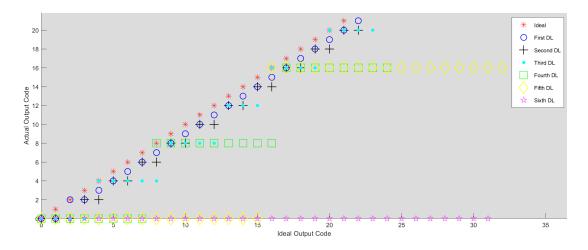

The TDC in figure 3.9 has a 3 bits binary output code, 40ps dynamic range with 10ps LSB. The 3 bits output can be encoded from 7 thermometer bits using standard logic gates, as demonstrated in the boolean equations 3.1, where n and q represent the binary and thermometer codes, respectively.

$$n_{0} = \bar{n}_{2}.\bar{n}_{1}.q_{a0} + \bar{n}_{2}.n_{1}.q_{a2}$$

$$n_{1} = \bar{n}_{2}.q_{b0}.q_{a1}$$

$$n_{2} = q_{c0}.q_{b1} + q_{b1}.q_{a3} + q_{c0}.q_{a3}$$

(3.1)

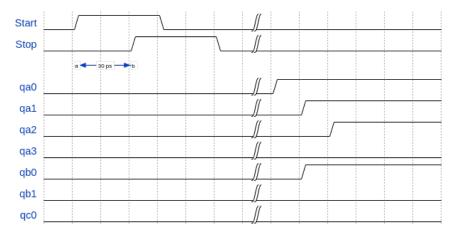

An example of measuring a 30ps time difference ( $\Delta T$ ) is shown in the timing diagram shown in figure 3.10, the parallel VDLs independently generate thermometer codes with different resolutions. The thermometer code from the first delay line  $(q_{a0} - q_{a3})$  is 1110, since it has an LSB of 10ps. As for the second delay line  $(q_{b0} - q_{b1})$  the thermometer code will be 10, correspond to its 20ps LSB. The last line  $(q_{c0})$  thermometer code will be 0 since  $(\Delta T)$  is less than its resolution (i.e. 40ps).

Figure 3.10: Timing Diagram of the Proposed TDC Implementation

Substituting the values of delay lines from figure 3.10 into equations 3.1 will produce the output word as a binary-weighted code, which is in this example (011). Theoretically, adding more lines to compute the final binary output should add more robustness to TDC output since every delay line will experience different PVT variations, as the binary output code for TDC is a combination of all lines. Moreover, the usage of simple logic gates can offer a new method for encoding the thermometer code, thus reducing the complexity of TDC encoders. To the author's best knowledge, the proposed parallel Vernier delay lines architecture has not been implemented in previous papers nor patents.

The proposed TDC architecture uses the delay segment shown in figure 3.5. The values for the capacitors  $C_1$  used to achieve the different resolutions is shown in table A.1 in Appendix A. Layout for different resolution segments are shown in Appendix A, the only difference between figures is the capacitor size.

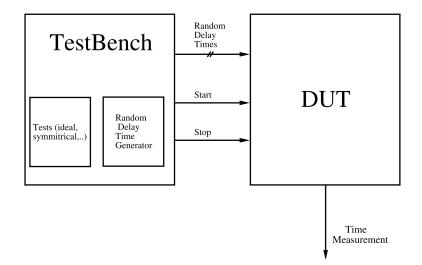

### **3.3** Test and Verification

Simulations performed in this work are divided into main sections; analog simulations at the transistor level and digital simulations in SystemVerilog. The analog simulations are performed to extract the behavior of the proposed delay cells before it is passed to the digital workspace to implemented the TDC.

### 3.3.1 Simulation Assumptions

To simplify the designed procedure, start and stop signals are assumed to be independent and jitter-free. Furthermore, the rise time is 20ps for both signals, and the pulse width is long enough for transistors to pass values in the TDC.

#### **3.3.2** Corners and Temperature

The proposed implementation is designed and simulated at  $27^{\circ}$  c, typical process corner. Other corners and temperature simulations could be considered to analyze their impact on TDC performance.

#### 3.3.3 Layout