**O** NTNU

# Ultra Low-Power/Low-Energy CMOS Mixed-Signal Building

Norwegian University of Science and Technology

Ali Asghar Vatanjou

## Ultra Low-Power/Low-Energy CMOS Mixed-Signal Building Blocks

Thesis for the Degree of Philosophiae Doctor

Trondheim, December 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

© Ali Asghar Vatanjou

ISBN 978-82-326-4322-6 (printed ver.) ISBN 978-82-326-4323-3 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2019:362

Printed by NTNU Grafisk senter

## ACKNOWLEDGEMENTS

This thesis is submitted to Department of Electronic Systems, Faculty of Information Technology and Electrical Engineering at Norwegian University of Science and Technology as a part of the requirements for fulfilling the Degree of Doctor of Philosophy.

First, I would like to thank my main supervisor professor Snorre Aunet and my co-supervisor professor Trond Ytterdal for their guidance and support during my PhD studies. Thanks also to Norwegian Nano-Network for funding chip fabrications. Thanks to my colleague at NTNU Even Låte for his collaboration in my publications and his friendship. I wish to acknowledge Jonathan Edvard Bjerkedok for the collaboration we had in the first publication for this PhD work.

I would like to thank my family specially my wife Mahsa and my parents for their unlimited support and encouragement during my work towards this PhD.

## CONTENTS

| 1. | Int | rodu   | ction                                                  | 3  |

|----|-----|--------|--------------------------------------------------------|----|

|    | 1.1 | CMC    | OS circuits operation in subthreshold                  | 3  |

|    | 1.2 | Moti   | vation for ultra-low voltage CMOS circuits             | 5  |

|    | 1.3 | Chall  | lenges for ultra-low voltage design                    | 6  |

|    | 1.4 |        | of publications                                        | 8  |

|    | 1.5 | Sum    | mary of paper contributions                            | 10 |

| 2. | Th  | esis S | Summary                                                | 12 |

|    | 2.1 | Subtl  | hreshold logic gates design                            | 12 |

|    |     | 2.1.1  | Logic gates based on 4 transistors slices              | 12 |

|    |     | 2.1.2  | Symmetrical VTC and balancing Pull-up and pull-down    |    |

|    |     |        | networks                                               | 13 |

|    |     | 2.1.3  | Minority-3 logic gates                                 | 15 |

|    | 2.2 | Devie  | ce sizing for ultra-low voltage applications           | 18 |

|    |     | 2.2.1  | Threshold voltage choice for subthreshold applications | 19 |

|    |     | 2.2.2  | Higher order effects                                   | 20 |

|    |     | 2.2.3  | Back-gate and poly biasing                             | 24 |

|    |     | 2.2.4  | Physical implementation and layout choices             | 25 |

|    | 2.3 | Ultra  | low-power/voltage full adder design                    | 26 |

|    |     | 2.3.1  | FA based on min-3 and Boolean logic gates              | 27 |

|    |     | 2.3.2  | Characteristics of the RCAs developed in 65 nm and     | -  |

|    |     | -      | 28 nm                                                  | 27 |

|    |     | 2.3.3  | MAC and multiplier blocks based on developed FAs       | 27 |

|    | 2.4 |        | gn considerations for ultra-low voltage flip-flops     | 32 |

|    | 2.5 |        | hreshold level-shifter design                          | 40 |

| 3. | Co  | nclus  | $\sin n$                                               | 42 |

|    |     |        |                                                        |    |

#### Contents

| 4. | Pu   | blicat. | ions  |  |  |  |  |  |  |  |  |  |  |  |  |  | 44  |

|----|------|---------|-------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|    | 4.1  | paper   | Ι     |  |  |  |  |  |  |  |  |  |  |  |  |  | 45  |

|    | 4.2  | paper   | Π.    |  |  |  |  |  |  |  |  |  |  |  |  |  | 52  |

|    | 4.3  | paper   | III . |  |  |  |  |  |  |  |  |  |  |  |  |  | 59  |

|    |      | paper   |       |  |  |  |  |  |  |  |  |  |  |  |  |  |     |

|    |      | paper   |       |  |  |  |  |  |  |  |  |  |  |  |  |  |     |

|    |      | paper   |       |  |  |  |  |  |  |  |  |  |  |  |  |  |     |

|    |      | paper   |       |  |  |  |  |  |  |  |  |  |  |  |  |  |     |

|    |      | paper   |       |  |  |  |  |  |  |  |  |  |  |  |  |  |     |

|    | 4.9  | paper   | IX .  |  |  |  |  |  |  |  |  |  |  |  |  |  | 97  |

|    | 4.10 | paper   | Χ.    |  |  |  |  |  |  |  |  |  |  |  |  |  | 107 |

|    | 4.11 | Apper   | ndix  |  |  |  |  |  |  |  |  |  |  |  |  |  | 113 |

#### Abstract

In the present day microelectronics, supply voltage scaling has received an intense attention as an efficient approach to reduce the power consumption in battery-operated and energy-harvested wireless systems. However, process, voltage and temperature (PVT) variations increase with lowering the supply voltage. This poses a challenge to ultra-low voltage (ULV) design to make robust circuits while maintaining the energy efficiency.

In this dissertation, ultra-low voltage building blocks are developed in 65 nm Bulk CMOS and 28 nm FDSOI technologies. The work focuses on making an optimal trade-off between the energy efficiency and the robustness of the building-blocks. At device level, combinations of higher order effects were considered. Static CMOS logic was used throughout the logic cells development. A constant effort was made to balance the drive strengths of the pull-up and pull-down networks with less area overhead and increase the functional yield of the cells. For the sequential elements, a single-phase clocked and contention free flip-flop structure was used. Measurement results confirmed robustness and energy efficiency of the circuits both in the 65 nm Bulk and 28 nm FDSOI technologies.

In 65 nm, the obtained 119 mV and 84 mV minimum supply voltages for the Ripple Carry Adders (RCA) proved the robustness of two types of logic cells with thick and thin Gate-Oxide thicknesses. The functionality of the single-phase clocked D type flip-flops were proven down to 132 mV in a divide-by-3 circuit.

In 28 nm FDSOI, a minimum functional supply voltage of 110 mV was achieved for RCAs and 8-bit multiplier based on Regular Threshold Voltage (RTV) devices. This is a demonstration of the functionality of both the combinational and sequential elements as the 8-bit multiplier contains the single-phased clocked flip-flops to sample outputs of the multiplier. Moreover, the minimum supply voltages of the 32-bit RCA samples reduced down to 80 mV by applying reverse back-gate voltages to the PMOS transistors. The 32-bit RCA based on minority-3 gates in 28 nm achieved an average energy per 1-bit addition of 0.65 fJ from the measurement results of nine samples. The average of measured energy per 1-bit addition of the 16-bit RCA was 0.77 fJ. From the measurements of ten samples, the implemented 8-bit multiplier in 28 nm obtained a minimum energy point of 47.2 fJ/cycle on average. The implemented logic cell library based on the Low Threshold Voltage (LVT) devices in 28 nm FDSOI was extended by adding specialized

| Contents |

|----------|

|----------|

inverters for clock tree distribution and fixing the hold time violations. A simple approach for clock distribution is also presented when the sequential elements of the circuit are single-phase clocked and race free.

A level-shifter capable of up-converting 39 mV to 1 V was implemented in 28 nm FDSOI. The diode connected devices were utilized to reduce the leakage current and decrease the minimum convertible input voltage levels. Moreover, the Single-NWELL (SNW) layout strategy was used along with the back-gate biasing and poly-biasing to create an adequate balance between the PMOS and NMOS drive strengths.

## 1. INTRODUCTION

#### 1.1 CMOS circuits operation in subthreshold

Supply voltage scaling has been considered as a fundamental design parameter for reducing the power consumption and hence improving the energy efficiency of digital systems over the past decades due to the quadratic dependence of active power and energy on the supply voltage. Scaling supply voltage down to below the absolute values of devices threshold voltages, known as subthreshold region, has been known since late 1960 [1]. However, the increasing demand for low-power and energy efficient circuits along with new features of modern technologies brings the significance of ultra-low voltage (ULV) design back. The drain current in the subthreshold region is due to diffusion in a weakly inverted channel and hence has an exponential dependency on the threshold and gate-source voltages. The drain current of an NMOS transistor in the subthreshold region is given by [2]:

$$I_{SUBTH} = \mu_N C_{ox} \frac{W_N}{L_N} V_t^2 exp\left[\frac{V_{GS} - V_{TH}}{nV_t}\right] \left[1 - exp\left[-\frac{V_{DS}}{Vt}\right]\right]$$

(1.1)

In the above equation,  $\mu_N$  is the electron carrier mobility,  $C_{ox}$  is the gate capacitance per unit area,  $V_t$  is the thermal voltage,  $V_{TH}$  is the threshold voltage,  $W_n$  is the device width,  $L_n$  is the devices length,  $V_{GS}$  is the gate-source voltage,  $V_{DS}$  is the drain-source voltage and n is the inverse slope of the subthreshold current which is given by:

$$n = 1 + \frac{C_D}{C_{ox}} \tag{1.2}$$

In Eq 1.2,  $C_D$  is the depletion channel region capacitance per unit area. The advantage of operating digital CMOS circuits in the subthreshold region for achieving minimum energy per operation was first introduced in [3]. The concept of minimum energy point (MEP) was revisited and its dependence on activity factor ( $\alpha$ ) was explained in [4]. The total power consumption of a digital circuit can be explained as:

$$P_{tot} = P_{dyn} + P_{stat} = \alpha f C_{tot} V dd^2 + I_{leak} V_{dd}$$

(1.3)

In equation 1.3,  $\alpha$  is activity factor, f is operating clock frequency,  $C_{tot}$  is the total switched capacitance of the circuit and  $I_{leak}$  is the total leakage current of the circuit. The leakage current can be determined from equation 1.1 when  $V_{GS} = 0$ . With  $t_{clk}$  being period of the clock signal, the total energy of the digital circuit can be explained as:

$$E_{tot} = E_{dyn} + E_{stat} = P_{tot} \times t_{clk} = \alpha C_{tot} V dd^2 + I_{leak} V_{dd} t_{clk}$$

(1.4)

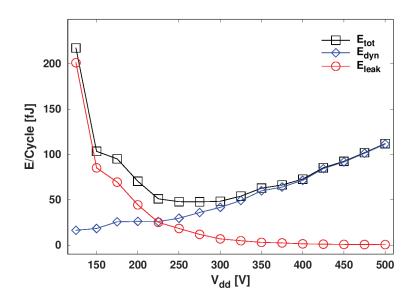

Fig. 1.1: Dynamic and static energy consumption of an 8-bit parallel multiplier as a function of  $V_{dd}$

By reducing  $V_{dd}$ , dynamic energy reduces while the static energy increases because of exponential increment in the circuit delay. Theoretically, the supply voltage ( $V_{ddopt}$ ) at which the MEP occurs can be found by solving  $\partial E_{tot}/\partial V_{dd} = 0$  [5]. Figure 1.1 shows the measured total, dynamic and static energy consumptions of an 8-bit parallel multiplier implemented in 28 nm FDSOI CMOS technology as an example. This circuit achieves a minimum energy of 47.7 fJ at 275 mv while the static energy reaches dynamic energy consumption at a supply voltage of 225 mV. A detailed description and more measurement results of the multiplier circuit are provided in section 2.3.3.

#### 1.2 Motivation for ultra-low voltage CMOS circuits

Circuits operating in ultra-low voltage domain provide solution for a wide range of applications with limited power or energy budget.

Battery operated wireless sensor networks (WSNs) are becoming more common with the advent of the Internet-of-Things (IoT). As the MEP of digital circuits occurs in the subthreshold or nearthreshold region, considerable improvement in energy efficiency (up to 10x [6]) can be achieved by lowering the supply voltage down to the threshold voltage of transistors. This in turn prolongs the battery lifetime of WSNs.

While the energy efficiency is the main focus for the battery-operated systems, there are some applications where the power consumption and the minimum operating voltage of the circuit is the main concern. Battery-less systems operating directly from the energy harvesting source and always-on circuits in a microcontroller (e.g. wake-up circuitry) are examples for systems where the limiting factor comes from the power budget and the minimum required supply voltage.

Schmitt-Trigger based logic cells operating down to 62 mV supply voltage were used in [7] to reduce the minimum functional supply voltage of the digital circuits. This in turn reduces the required supply voltage at which an active operation can start. Dynamic leakage-suppression logic (DLSL) is introduced in [8] to dramatically reduce the static power of logic cells. The power consumptions of the developed logic gates were in the range of few fW at extremely low operating frequencies. The size of the energy harvesting source can be reduced by using DLSL thanks to the extremely low power consumptions of circuits based on DLSL.

The power and energy density of CMOS processors increase as transistors density increases without supply voltage scaling. As a result, part of silicon, known as dark silicon [9], cannot be powered-on at any given time. Despite the performance degradation of ultra-low voltage circuits, near-threshold circuits can be useful in processors with multiple cores. The functionality and energy efficiency of an IA-32 processor in ULV domain has been proven in [10]. Furthermore, it has been discussed in [11], [12] that processors operating in near-threshold helps to overcome the dark silicon effect in a chip multiprocessor.

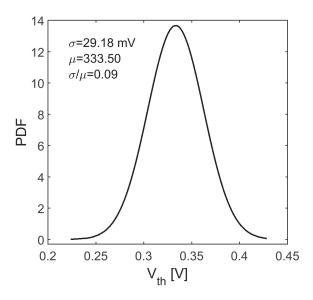

Fig. 1.2: NMOS threshold voltage distribution

#### 1.3 Challenges for ultra-low voltage design

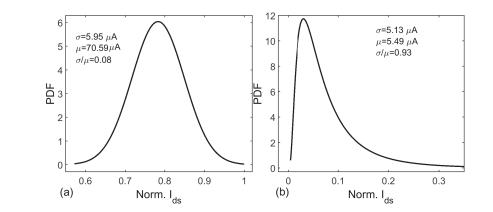

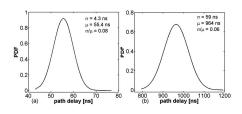

The threshold voltage variations in CMOS technologies follows a Gaussian distribution [13]. Due to the quadric dependence of on-current on the threshold voltage, the drain current of the CMOS devices shows also a normal distribution in super-threshold region. However, the on-current of the CMOS transistors exhibit a lognormal distribution in subthreshold region because of the exponential dependence of the drain current on threshold voltage in this region [14].

A Lognormal distribution has a long tail and hence higher variability  $(\sigma/\mu)$ . Figure 1.2 shows the statistical distribution of threshold voltage for a minimum sized NMOS (W=80 nm and L=30 mn) transistor in a 28 nm UTBB-FDSOI CMOS technology obtained from 2000 Monte Carlo (MC) runs at  $V_{ds} = V_{gs} = 1 V$ . The threshold voltage has an average ( $\mu$ ) value of 333.5 mV and a standard deviation ( $\sigma$ ) of 29.18 mV. The resultant statistical distributions of drain current for a minimum sized NMOS at 1 V and

Fig. 1.3: NMOS on-current distribution in (a) super-threshold and (b) subthreshold regions

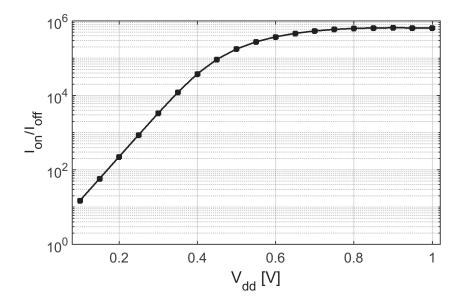

Fig. 1.4: Ion/Ioff Ratio of a minimum sized NMOS as a function of  $V_{dd}$

200 mV are also depicted in Figure 1.3(a) and (b), respectively. As can be observed from Figure 1.3, the variability of the drain current at 200 mV is 0.93 which is much higher that the variability at 1 V. The delay of CMOS logic gates is proportional to the transistors on current in the subthreshold region  $(t_d \propto \frac{C_l V_{dd}}{I0exp(V_{dd}-V_{th}/nV_t)})$  [14]. Therefore, the delay in the subthreshold region

exhibits much wider variations compared to the delay in super-threshold region because of the wider variations range of devices current in subthreshold. Another main issue that makes circuit design more challenging in subthreshold region is extremely degraded  $I_{on}/I_{off}$ -ratio of transistors in ultra-low supply voltages. This can be seen in Figure 1.4 where the  $I_{on}/I_{off}$  ratio for a minimum sized NMOS transistor in 28 nm UTBB FDSOI technology is shown as a function of supply voltage. Process, voltage and temperature (PVT) variations can worsen the weak  $I_{on}/I_{off}$  ratio in subthreshold and consequently result in functional failure.

#### 1.4 List of publications

This thesis is based on a collection of papers that are related to ultra-low voltage/power and energy efficient circuits.

In addition to the following papers, three items are also included in chapter 2: (a) It is shown in section 2.1.3 that the 10-transistor minority-3 gate we used in [15] does not restrict the functional yield of the subthreshold cell library when supply voltage is above a specific value (i.e.  $V_{dd} > 130mV$ ). (b) Measurement results of an 8-bit multiplier which is based on the same full adders we reported in [15] are shown in section 2.3.3. (c) In section 2.4, the custom library cell we presented in [16] is extended by adding specialized inverters for clock tree distribution and fixing hold time violations. In the following list, Paper VIII and Paper IX are extended versions of Paper VI and Paper VII, respectively, published in the MICPRO journal. Paper II received a best paper award in 2015 IEEE ASQED conference [17] (see Appendix).

- Paper I: J. E. Bjerkedok, A. A. Vatanjou, T. Ytterdal and S. Aunet, "Modular layout-friendly cell library design applied for subthreshold CMOS," 2014 NORCHIP, Tampere, 2014, pp. 1-6.

- Paper II: A. A. Vatanjou, T. Ytterdal and S. Aunet, "Energy efficient sub/near-threshold ripple-carry adder in standard 65 nm CMOS," 2015 6th Asia Symposium on Quality Electronic Design (ASQED), Kuala Lumpur, 2015, pp. 7-12.

- Paper III: A. A. Vatanjou, T. Ytterdal and S. Aunet, "Exploiting short channel effects and multi-Vt technology for increased robustness and reduced energy consumption, with application to a 16-bit subthreshold

adder implemented in 65 nm CMOS," 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, 2015, pp. 1-4.

- Paper IV: A. A. Vatanjou, T. Ytterdal and S. Aunet, "4 Sub-/nearthreshold flip-flops with application to frequency dividers," 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, 2015, pp. 1-4.

- Paper V: A. A. Vatanjou, T. Ytterdal and S. Aunet, "28 nm UTBB-FDSOI energy efficient and variation tolerant custom digital-cell library with application to a subthreshold MAC block," 2016 MIXDES - 23rd International Conference Mixed Design of Integrated Circuits and Systems, Lodz, 2016, pp. 105-110.

- Paper VI: E. Låte, A. A. Vatanjou, T. Ytterdal and S. Aunet, "Comparative analysis of flip-flop architectures for subthreshold applications in 28nm FDSOI," 2015 Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on Systemon-Chip (SoC), Oslo, 2015, pp. 1-4.

- Paper VII: A. A. Vatanjou, E. Låte, T. Ytterdal and S. Aunet, "Ultralow voltage adders in 28 nm FDSOI exploring poly-biasing for device sizing," 2016 IEEE Nordic Circuits and Systems Conference (NOR-CAS), Copenhagen, 2016, pp. 1-4.

- Paper VIII: Even Låte, Ali Asghar Vatanjou, Trond Ytterdal, Snorre Aunet, "Extended Comparative Analysis of Flip-Flop Architectures for Subthreshold Applications in 28 nm FD-SOI", Microprocessors and Microsystems, Volume 48, 2017, Pages 11-20, ISSN 0141-9331.

- Paper IX: Ali Asghar Vatanjou, Even Låte, Trond Ytterdal, Snorre Aunet, "Ultra-low voltage and energy efficient adders in 28 nm FD-SOI exploring poly-biasing for device sizing", Microprocessors and Microsystems, Volume 56, 2018, Pages 92-100, ISSN 0141-9331.

- Paper X: A. A. Vatanjou, T. Ytterdal and S. Aunet, "An Ultra-Low Voltage and Low-Energy Level Shifter in 28-nm UTBB-FDSOI," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 6, pp. 899-903, June 2019.

#### 1.5 Summary of paper contributions

The major contributions and achievements of the publications related to this thesis are as following:

In Paper I [18], the development of logic cells based on the identical slices of stacked transistors has been proposed. This leads to less variability in the delay of the logic cells, increases manufacturability of the logic cells and decreases the leakage current.

In Paper II [35], it has been shown that the required  $W_p/W_n$  ratio for balancing the switching point of an inverter at  $V_{dd}/2$  reduces by increasing the channel length of the transistors up to an optimal value even though the on-current of NMOS and PMOS do not increase with increasing the channel length. Additionally, the required PMOS width for balancing its drive strength with the NMOS decreases more rapidly thanks to the Inverse Narrow Width Effect (INWE). This in turn results in less parasitic switching capacitance and reduces the energy consumption of the circuit. The delay of the circuit, on the other hand, increases as the on-current of the transistors decreases by increasing the channel length. However, the rise in the propagation delay can be compensated by increasing the operating supply voltage while consuming less energy for given delay. The reported 84 mV operating voltage of the 32-bit RCA was, to the best of the author's knowledge, the lowest reported supply voltage for the static CMOS logic gates.

In Paper III [20] and Paper IV [21], we used Reverse Short Channel Effect (RSCE) and Inverse Narrow Width Effect (INWE) together with different threshold voltage flavors in the pull-up and pull-down networks to achieve a robust ultra-low voltage operation and increase the energy efficiency of the logic cells. Measurement results confirmed a minimum operating voltage of 132 mV for the divide-by-3 circuit based on the single-phase clocked D flip-flops. A minimum operating voltage of 119 mV was also achieved for a 16-bit Ripple Carry Adder (RCA) based on the Boolean logic gates.

In paper V [16], we developed an energy efficient custom logic cell library based on LVT 28 nm transistors for subthreshold applications. We focused on making a satisfactory trade-off between sensitivity to the variations and energy consumption of the digital logic cells. We considered the threshold voltage reduction with the transistors width, knows as Narrow width Effect (NWE), to make a trade-off between the robustness and parasitic switching capacitance of the logic cells. Moreover, use of longer channel length resulted in 46% improvement in the  $I_{on}/I_{off}$  ratio of the transistors at the cost of a 13.4% increase in the energy consumption. The asymmetric back-gate biasing scheme provided much better balance between the drive strength of the NMOS and PMOS. Compared to the state of the art MAC blocks, the synthesized MAC block based on the developed cell library reveals more energy efficiency for the clock frequencies in the MHz-range. The presented library cell in this paper was extended by adding proper inverters for clock distribution and buffers for fixing hold-time violations.

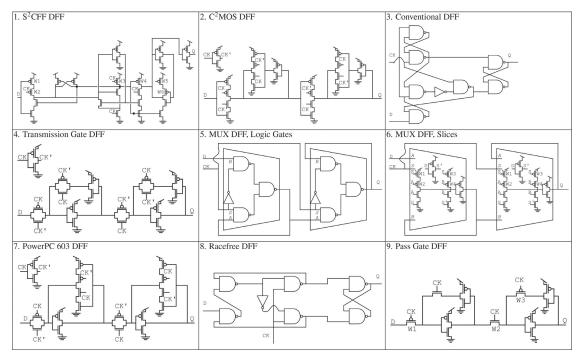

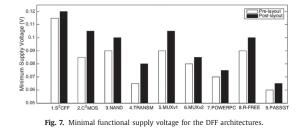

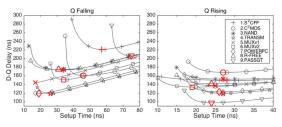

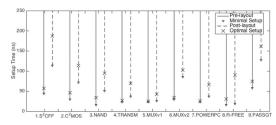

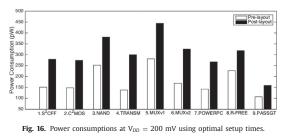

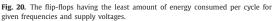

In paper VI [22] and paper VIII [23], nine D-type flip-flop architectures were implemented in 28 nm FDSOI technology. The flip-flops structures were evaluated in terms of timing constraints, energy consumption, leakage, area and minimum operating supply voltage.

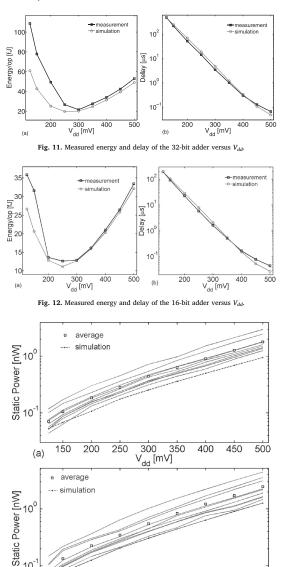

In paper VII [24] and paper IX [15], ultra-low voltage and energy efficient adders based on min-3 and Boolean logic gates has been presented. The logic cells implemented using the Regular Threshold Voltage (RVT) devices in 28 nm FDSOI technology. We explored poly-biasing and back-gate biasing techniques to balance the drive-strength of the pull-up and pull-down networks with relatively equal area for the PMOS and NMOS transistors. This causes both the standard deviation and mean values of the inverter to have similar values. Both the adders obtained a minimum  $V_{dd}$  of 110 mV while the minimum  $V_{dd}$  of the 32-bit adder based on min-3 gates decreased to 80 mV by applying reverse back-bias voltages to the PMOS transistors. One sample was functional at 79 mV with a 430 mV reverse back bias voltage applied to its PMOS devices. From the measurement results of nine samples, the 32-bit adder based on min-3 gates and the 16-bit adder based on Boolean gates achieved an average minimum energy per 1-bit addition of 0.65 fJ and 0.77 fJ, respectively.

In Paper X, we reported an energy efficient level-shifter in 28 nm FDSOI technology. The level shifter topology uses top diode connected devices together with the current limiter diodes. This topology along with the single-NWELL layout strategy allows to achieve a balanced pull-up network (PUN) and pull-down network (PDN) at extremely low  $V_{ddL}$ s. The level-shifter were capable of up-converting 39 mV input voltage to 1 V.

## 2. THESIS SUMMARY

#### 2.1 Subthreshold logic gates design

Although static logic families provide the most simple and robust approach to implement logic gates [26], several logic styles have been proposed for ULV applications to meet specific requirements. In [27], stacked NMOS transistors utilized in transmission gate (TG) logic to have a relaxed PMOS sizing and reduced leakage. Operating frequencies in the MHz range were achieved in subthreshold region by implementing highly pipelined datapath blocks (MAC and ADDER) based on TG-logic with stacked NMOSs and low-Vt (LVT) transistors. It has been demonstrated in [7] that digital circuits based on Schmitt-trigger (ST) logic gates are able to operate at very low supply voltages down to 62 mV. The main application of the ST logic gates is in systems powered by energy harvesting sources (e.g. thermal generator) where the use of ST logic gates reduces the minimum  $V_{DD}$  that an active operation can start. Another proposed logic style for ultra low power (ULP) applications is Dynamic Leakage-Suppression Logic (DLSL) [8] that consumes 10 fW active power per gate. DLSL family is proper for battery-less WSNs power by energy harvesting source with very low throughput requirements (operating frequency in the range of few Hz).

For works related to this thesis, we used static CMOS logic style as basic topology in our subthreshold logic libraries due to simplicity and robustness of this topology. We focused on optimizing static logic gates for subthreshold applications by accurate device sizing.

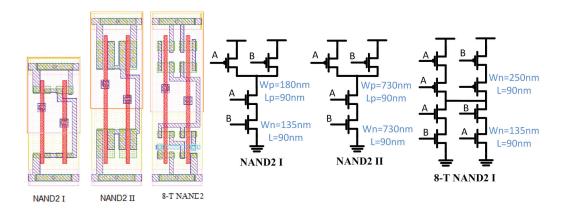

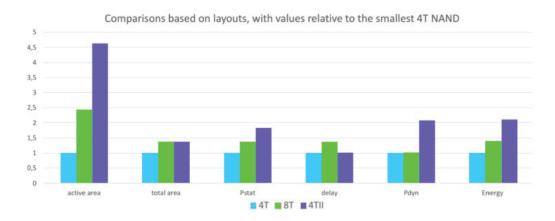

#### 2.1.1 Logic gates based on 4 transistors slices

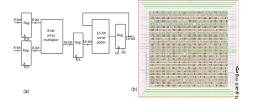

Logic gates based on identical slices of stacked transistors (2 stacked NMOS and 2 stacked PMOS) have been introduced and discussed in Paper I [18]. The main idea behind developing logic gate libraries based on identical slices of stacked transistors is to improve manufacturability and yield for scaled CMOS technologies through increasing the regularity of the design. It has been shown in Paper I [18] that the delay variability  $(\sigma/\mu)$  of logic gates based on the identical slices of stacked transistors is lower compared to the conventional static CMOS logic gates with the same total area. As an example, parameters of the NAND gate based on identical slice of stacked transistors (8T-NAND2) were compared to the parameters of two conventional NAND gates. One with the same footprint area (4T-NAND2II) and one with the minimum device dimensions (4T-NAND2I). The schematic and layouts of NAND gates are shown in figure 2.1. It has been shown that the 8T-NAND2 has less rise and fall delays variability compared to 4T-NANDI and less power consumption compared to the 4T-NAND2II. The delay variability for 8T-NAND2 was about 53.5% lower than the corresponding value for the 4T-NAND2I while energy per operation of the 4T-NANDI was 38% lower than energy per operation of the 8T-NAND2. The 8T-NAND had 44%more delay variability and 51% less energy per operation in comparison to 4T-NANDII with equal total area. Figure 2.2 [18] shows relative comparison between these three NAND implementations.

Fig. 2.1: Schematic and layout of the 4T-NANDI, 4TNAND2II 8T-NAND2 gates.

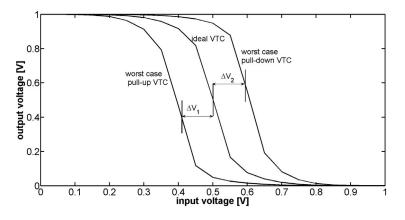

#### 2.1.2 Symmetrical VTC and balancing Pull-up and pull-down networks

Balancing pull-up network (PUN) and pull-down network (PDN) drive strengths is a key issue to increase the functional yield of static CMOS logic gates especially in deep subthreshold applications. To have equal rise and fall delays,

Fig. 2.2: Relative comparisons between the three NAND implementations [18].

Fig. 2.3: Sizing of logic gates with symmetrical VTC [20].

drive strength of the pull-up and pull-down networks must be identical. Additionally, unbalanced high and low noise margins leads to extra leakage energy overhead in subthreshold circuits [28]. As shown in paper III [20], equalizing the switching point deviation of worst cases voltage transfer curves (VTC) from  $V_{DD}/2$  maximizes the static noise margin (SNM) in the logic gates with more than one inputs. This is shown graphicly in figure 2.3

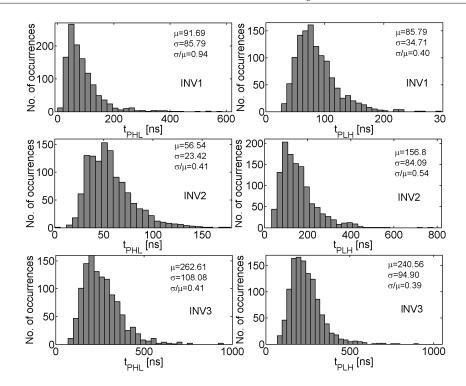

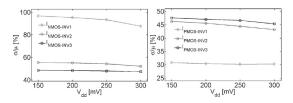

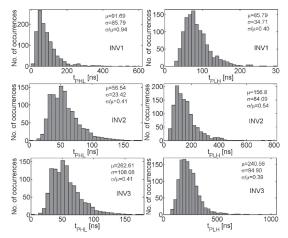

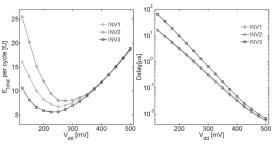

For minimum sized devices, the on-current ratio of the PMOS with respect to the NMOS is usually too small in the ULV domain. So, in a balanced logic gate the PMOS transistors must be much wider than the NMOS transistors. For example, to balance PUN/PDN the PMOS gate width should be more than 7x [20] and 4x [15] of the NMOS gate width in 65 nm bulk and 28 nm FDSOI technologies, respectively. This in turn leads to wider variations in the fall time of a logic gate compared to its rise time. It is proposed in paper IX [15] to use relatively equal active areas for PUN and PDN to achieve a better match in the rise and fall delays variability. Figure 2.4 [15] <sup>1</sup> compares the mismatch simulations of rise and fall FO4 delays for three inverters. The schematics of the inverters are shown in figure 2.5. In figure 2.4, the drive strengths of PMOS and NMOS are balanced by upsizing PMOS width in INV1. INV2 has the same total area as INV1 but the PMOS/NMOS drive strengths are unbalanced. The PMOS and the NMOS of INV3 are balanced with relatively equal active areas. Although the average values of rise and fall delays are equal in INV1, the fall delay standard deviation is 2.5x of the rise delay standard deviation. Despite the small difference in rise and fall delays variability in INV2, its rise delay mean value is 2.8x fall delay mean value. The difference in fall and rise delay variability of INV3 is only 2%, and its fall delay mean value is comparable to the rise delay mean value. Therefore, the importance of balancing PUN and PDN derive strengths with relatively equal active area for PMOS and NMOS transistors is recognized when the variations are considered in subthreshold region. The balancing of NMOS and PMOS drive strengths will be discussed furthermore in sections 2.2.3 and 2.2.4.

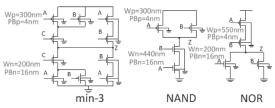

#### 2.1.3 Minority-3 logic gates

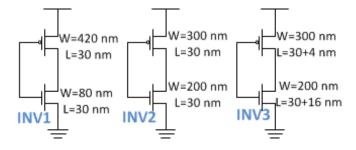

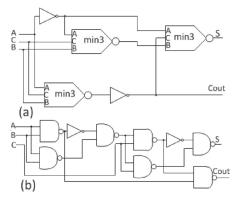

Minority-3 (min-3) is a three-input logic gate, and its output is high only when two or three inputs are low. Figure 2.6 [29] represents the schematic and truth table of a 10-transistor min-3 logic gate. The robustness and reliability of different min-3 logic gates have been discussed in [30], and the possibilities of making synchronous or asynchronous systems from min-3 gates has been demonstrated.

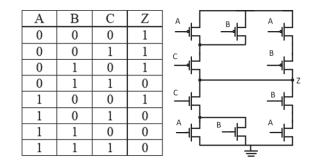

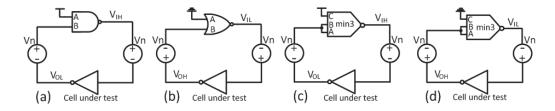

The 10-transistor min-3 logic gate is used in developed logic libraries of this work due to its energy efficiency, robustness, regular topology and relatively small area. In [31], the functionality of logic cells has been evaluated by connecting a minimum sized inverter back-to-back with the logic cells whose outputs provide worst cases input-high  $(V_{IH})$  and input-low  $(V_{IL})$  voltages.

<sup>&</sup>lt;sup>1</sup> In [15], the  $t_{PHL}$  distribution for INV2 was incorrectly placed in the position of INV3  $t_{PHL}$  distribution. This is corrected in the current version of the figure.

*Fig. 2.4:* Rise and fall FO4 delays variability with different sizing approaches at a supply voltage of 200 mv.

Fig. 2.5: Schematic of three inverters used for rise and fall delays analysis.

Assuming a library cell with the maximum fan-in of two and logic cells with symmetrical VTCs [20], the worst case configuration to evaluate the outputlow  $(V_{OL})$  voltage of a 1x strength inverter is shown in Figure 2.7(a). The test-bench for quantifying the output-high  $(V_{OH})$  voltage is illustrated in Figure 2.7(b). If minority-3 (min3) gates are also added to the library, min3

Fig. 2.6: schematic and truth table of a 10-transistor min-3 logic gate.

gates with input configurations shown in Figure 2.7(c) and (d) provide the most stringent  $V_{IH}$  and  $V_{IL}$ , respectively. Therefore, the test-benches for evaluating  $V_{OL}$  and  $V_{OH}$  of a 1x strength inverter are shown in Figure 2.7(c) and (d), respectively. The static noise margin (SNM) follows a Gaussian distribution and is determined by the methodology presented in [32]. Assuming that a logic cell to be failing when its SNM is less than  $V_L$ , the corresponding functional failure probability of the logic cell is as equation 2.1 [33]

$$P_{fail} = \frac{1}{\sigma_{SNM}\sqrt{2\pi}} \int_{-\infty}^{V_L} exp\left(-\frac{(x-\mu_{SNM})^2}{\sigma_{SNM}^2}\right) dx \qquad (2.1)$$

Fig. 2.7: Benchmark circuits to measure SNM of logic cells (a)  $V_{IH}$  is generated by NAND2 (b)  $V_{IL}$  is generated by NOR2 (c)  $V_{IH}$  is generated by min3 (d)  $V_{IL}$  is generated by min3.

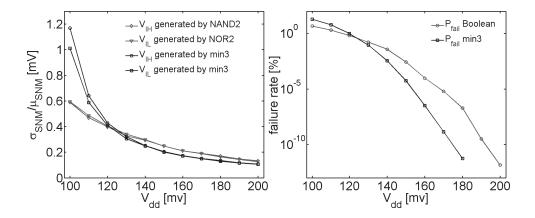

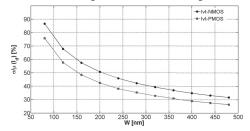

In equation 2.7,  $\sigma_{SNM}$  is the standard deviation and  $\mu_{SNM}$  is the average of the SNM. From equation 2.1, the functional failure rate of logic cells depends on the variability ( $\sigma/\mu$ ) of the SNM. Figure 2.8(a) shows the variability of an inverter SNM when  $V_{IH}$  and  $V_{IL}$  are generated by NAND2, NOR2 and min3 gates. The analysis here considers a logic cell to be failing when its

SNM is less than 0. The output swing failure rate of the inverter is depicted in Figure 2.8(b). As can be observed from Figure 2.8(b), the probability that the 1x strength inverter functionality fails is lower when  $V_{IH}$  and  $V_{IL}$  are generated by the min-3 gate instead of NAND2/NOR2 gates if  $V_{dd} > 130 \ mV$ . Thereby, the min-3 gate does not restrict the functional yield of the logic cells developed in [15] when  $V_{dd} > 130 \ mV$ . The maximum  $\sigma/\mu$  of the inverter high or low SNM was used to calculate the failure rate in Figure 2.8(b). It is worth noting that for  $V_{dd} > 190 \ mV$ , the functional failure probability of the inverter is 0 when skewed VTCs of the min-3 gate are assumed to give the worst  $V_{IH}/V_{IL}$ .

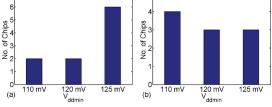

The measurement results of the full adders (FA) based on the min3 and Boolean logic gates, reported in paper IX [15], showed that the worst minimum operating voltage of different chip samples were 125 mV for both adder topologies. This is in agreement with the results that are presented here.

Fig. 2.8: (a) Variability of the SNM vs  $V_{dd}$  (b) output swing failure rate vs  $V_{dd}$ .

#### 2.2 Device sizing for ultra-low voltage applications

In the subthreshold region, the performance of circuits changes drastically with fluctuations in the threshold voltage of the transistors due to the exponential dependency of drain-source current on threshold voltage. As discussed in the previous section, imbalanced PUN and PDN drive strengths results in functional failure and more leakage power consumption in ULV circuits. Moreover, PMOS and NMOS devices should have relatively equal active area to have similar variability in rise/fall delays and reduce parasitic capacitance and leakage of CMOS logic gates [15]. Therefore, higher order effects and different techniques offered by the available technology should be taken into account during circuit design to suppress variations and create a good balance between PMOS and NMOS drive strength. In this thesis, 65 nm bulk CMOS and 28 nm FDSOI technologies are used to develop building blocks and cell libraries for subthreshold applications.

#### 2.2.1 Threshold voltage choice for subthreshold applications

Multi-Vt devices are featured in both 65 nm bulk and 28 nm FDSOI technologies used here. A good trade-off between the static power consumption and performance of logic cells can be achieved through the proper selection of the devices threshold voltage taking the required data throughput into account. This means that low threshold voltage devices are appropriate for the applications with high throughput requirements and transistors with high threshold voltage are preferable when the data throughput is low [34]. Therefore, we developed libraries based on devices with different threshold voltages. The 65 nm bulk technology that has been used offers low-power (LP) and general-purpose (GP) devices. The GP process features a thin gate oxide and hence GP transistors are proper choice for applications with high operating frequencies. The LP process, on the other hand, offers devices with thick gate oxide and lower leakage. Additionally, multi-Vt transistors are implemented through different dopant in channel area. We developed an energy efficient 32-bit adder in paper II [35] based on the low-Vt GP transistors for medical ultrasound applications (2.3 ns delay per 1-bit addition) [36]. The power consumption of 8-bit Ripple-Carry Adders (RCA) based on standard-Vt (SVT), low-Vt (LVT) or high-Vt GP-devices operating at different frequencies are listed in TABLE 2.1 [35]. As can be seen from Table 2.1, LVT transistors provided the lowest power consumption for the frequencies above 50 MHz.

Transistor level intra-cell multi-Vt design has been used in [37] to make a trade-off between delay and leakage current of static CMOS logic cells. In the logic gates we developed in paper III [20], low-power (LP) LVT-PMOS devices are in the PUN of all the logic gates and LP-SVT-NMOS devices are in the PDN of all the logic gates. In addition to smaller PMOS dimensions, this offers the possibility of utilizing reverse short channel effect (RSCE)

|                                        | SVT   | LVT   | HVT   |

|----------------------------------------|-------|-------|-------|

| P [nW]@ 10MHz                          | 77.1  | 118.5 | 100.9 |

| $V_{dd} \text{ [mV]} @ 10 \text{MHz}$  | 240   | 175   | 340   |

| P [nW]@ 50MHz                          | 569.1 | 546.5 | 758.3 |

| $V_{dd} \text{ [mV]} @ 50 \text{MHz}$  | 355   | 280   | 430   |

| P [nW]@ 100MHz                         | 1520  | 1400  | 2250  |

| $V_{dd} \text{ [mV]} @ 100 \text{MHz}$ | 420   | 350   | 520   |

Tab. 2.1: 8-bit RCA power consumption as a function of threshold voltage and operating frequency

in both NMOS and POMS transistors. This in turn decreases the energy consumption and increases the robustness of the logic cells.

#### 2.2.2 Higher order effects

Short channel effect (SCE) [38], Reverse Short channel Effect (RSCE) [39], Narrow Width Effect (NWE) [40] and Inverse Narrow Width Effect (INWE) [41] are notable examples of various high order effects that cause modification in the threshold voltage of devices in deep sub-micron technologies. These effects should be considered carefully during logic cell development for subthreshold applications because any change in the threshold voltage of devices has an exponential effect on the drain-source current. RSCE:

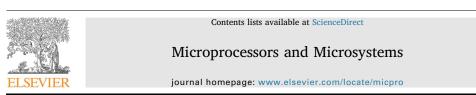

A non-uniform channel doping (HALO doping) can be used to mitigate variations in the threshold voltage due to the short channel effect (SCE) and drain induced barrier lowering (DIBL) [39]. As a result, the threshold voltage of devices with HALO doping decreases when increasing the device channel length. Since the drain-source current has an exponential dependency on the threshold voltage in subthreshold region, the RSCE can be used to increase the drive capability of the MOS devices [42]. In addition, the total gate capacitance can be reduced by increasing the channel length up to an optimal value [42]. Thereby, a given on-current can be achieved with less load capacitance by increasing the channel length rather than the channel width.

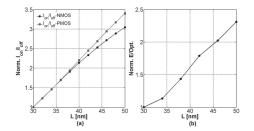

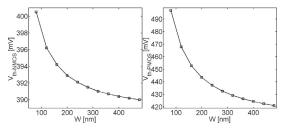

The mechanism of RSCE is not identical for all transistor types, and for some devices it might results in non-monotonic changes in the drain current. In paper II [35], we used RSCE to balance drive strengths of the NMOS and PMOS transistors. The optimum channel length results in min-

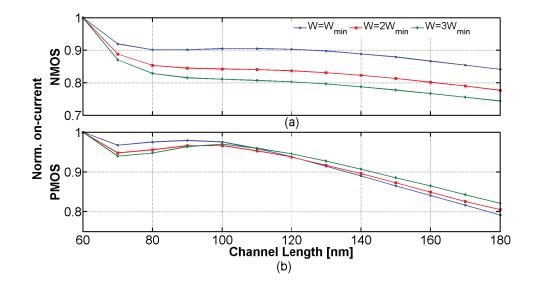

Fig. 2.9: (a) Normalized on-currents vs. channel length (a) NMOS (b) PMOS [35].

imum PMOS/NMOS width ratio in the procedure for balancing the drive strengths of the NMOS and PMOS. Figure 2.9 shows normalized LVT-GP NMOS and PMOS drain current ratios for three different multiples of the minimum transistor widths (135 nm) in 65 nm bulk technology. The optimum channel length is the channel length for which the PMOS on-current ratio over NMOS on-current ratio is minimum.

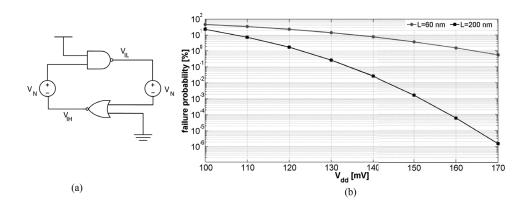

In the dual-Vt logic gates of paper III [20], LVT-LP PMOS devices are used in the PUN and SVT-LP NMOS transistors are used in the PDN of all the logic gates. By doing so, the RSCE is strong enough in both PMOS and NMOS transistors to increase the drain current with the channel length increment. In dual-Vt logic gates [20], longer channel length results in improved energy efficiency, less variability in cells delay and significant improvement in the functional yield. By using a channel length of 200 nm instead of 60 nm, a five-stage ring-oscillator which was comprised of dual-Vt basic logic gates showed 17% less variability in the propagation delay and 31% less energy consumption for a supply voltage of 150 mV. The overhead of having a 200 nm channel length was 12% larger footprint area. Additionally, as shown in figure 2.10, a significant improvement in the functional yield of the logic gates were achieved by increasing the channel length to 200 nm. INWE:

Fig. 2.10: (a) Test-bench to evaluate the worst case logic output swing (b) probability of output swing failure as a function of  $V_{dd}(T = 27 \text{ °C} \text{ and } 2 \text{ k MC} \text{ runs})$  [20].

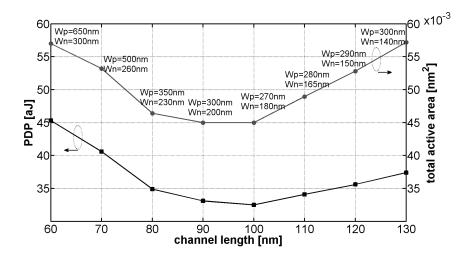

Fig. 2.11: PDP and total area of an inverter versus channel length [35].

The mechanism of device threshold voltage shift as a function of the channel width depends on the isolation oxide structure [43]. The threshold voltage increases with increasing the channel width when shallow trench isolation (STI) is used to isolate transistors [43]. Both subthreshold logic cells in paper II [35] and paper III [20] we developed in 65 nm bulk technology are INWE-aware.

It is shown in paper II [35] that the required  $W_p/W_n$  to balance the switch-

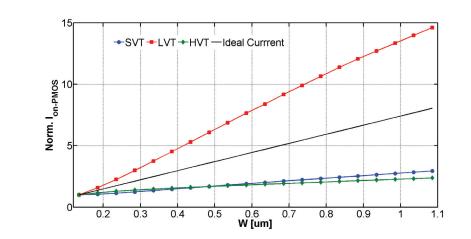

Fig. 2.12: Normalized on-current of PMOS transistors with different threshold voltages as a function of W [20].

ing point of an inverter at  $V_{dd}/2$  reduces by increasing the channel length up to 100 nm. In figure 2.11, the total active area of the NMOS was kept constant (not to lose robustness) and the PMOS width selected to balance an inverter. This reduction in the required  $W_p/W_n$  ratio is for two reasons. Firstly, as discussed earlier, the RSCE strength on used PMOS and NMOS devices is not identical and  $I_{on-NMOS}/I_{on-PMOS}$  decreases by increasing the channel length up to 100 nm [35]. Secondly, the PMOS on-current per width increases by decreasing its width due to the INWE.

Figure 2.12 [20] illustrates the normalized on-current of the LP-PMOS transistors with different threshold voltages versus the channel width. The black line represents the normalized ideal drain-source current which is proportional to the channel width. The drain-source current of SVT and HVT devices increases more slowly than what was expected because their threshold voltage increases with channel width as a result of INWE. The drain-source current of the LVT-PMOS transistor on the other hand increases even more rapidly than what was expected due to the lower bulk implant dose. Therefore, the reduced drain-source current due to the INWE can be avoided in the developed subthreshold logic gates in paper III [20] by using minimum sized SVT-NMOS devices in pull-down transistors and LVT-PMOS devices in pull-up transistors.

NWE:

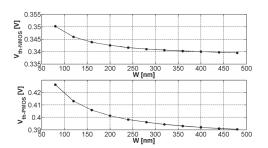

In silicon on isolator (SOI) technology, threshold voltage shift with respect

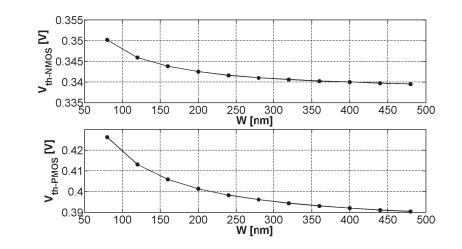

Fig. 2.13: Threshold voltage shift of PMOS and NMOS as a function of channel width,  $V_{ds} = 0.2$  V and L=34 nm. [16].

to the channel width depends on the buried oxide (BOX) thickness, and the threshold voltage decreases with increasing the channel width for SOI technologies with thin oxide thickness [44]. The threshold voltage of transistors in the 28 nm FDSOI technology that was used increases by decreasing the channel with as shown in figure 2.13 [16]. To mitigate threshold voltage variations due to lithography effects on matching property of the transistors, a minimum gate width was selected considering the threshold voltage shift as a function of channel widths in both logic gates in paper V [16] and paper IX [15].

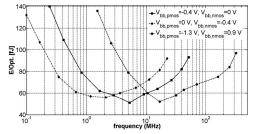

#### 2.2.3 Back-gate and poly biasing

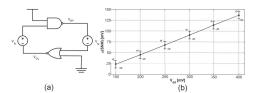

The 28 nm FDSOI technology that was used offers effective knobs such as back-gate biasing (BB) and poly biasing (PB). For an authorized poly pitch in the 28 nm FDSOI technology, the poly-biasing allows to modulate the effective channel length of transistors from 24 nm up to 40 nm without area overhead [45]. Thanks to the ultra-thin buried oxide of this technology, a wide range of back-gate biasing voltages can be applied to the back-gate of devices to adjust the leakage current and the performance of logic cells. In the logic cells we developed based on the 28 nm FDSOI LVT device in paper V [16], a 46% improvement in the  $I_{on}/I_{off}$  ratio was achieved at the cost of 13% more energy consumption by applying a poly-biasing of 4 nm to all the logic gates. Moreover, after choosing the minimum used channel width considering NWE, an additional constant forward back-gate biasing (FBB) voltage was applied to the back-gate of PMOS transistors to balance PMOS/NMOS strength ratio.

The logic cells based on the 28 nm FDSOI RVT devices in paper IX [15] were developed for applications with lower throughput requirements and we aimed to reduce the leakage current. Therefore, we created a balance between the NMOS and PMOS drive strength by applying a 16 nm poly-biasing to the NMOS devices. In these logic cells, the NMOS transistors channel length was also increased by 4 nm through the poly-biasing to reduce the leakage current further and improve the functional yield of the cells. We did not apply a reverse bias to the back-gate of PMOS transistors and the back-gate of PMOS transistors had same potential as that of the NMOS transistors [15] (both grounded for normal back-biasing).

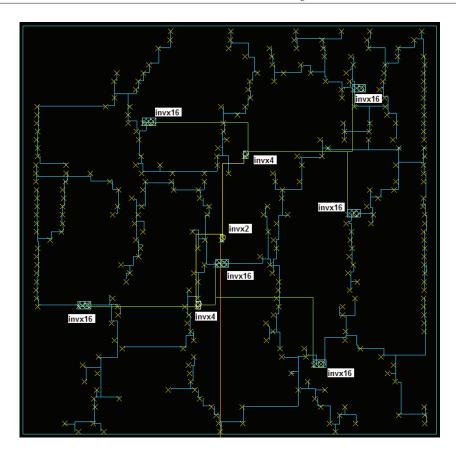

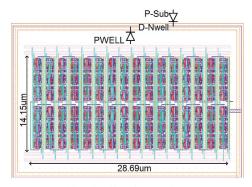

#### 2.2.4 Physical implementation and layout choices

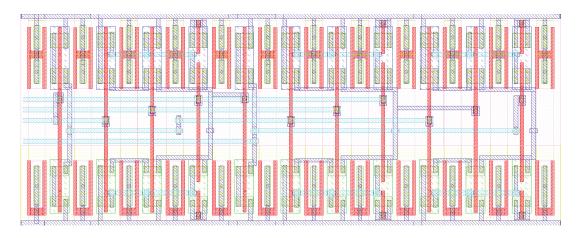

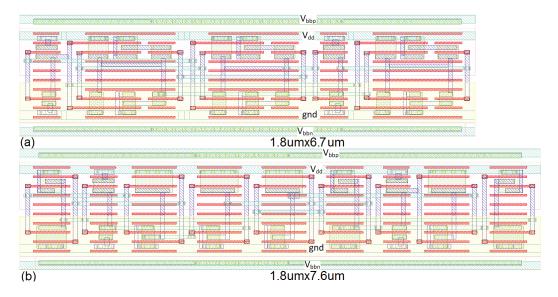

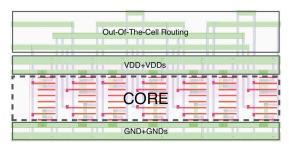

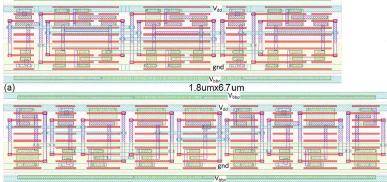

Layout-induced physical effects have been considered in the layout of all the subthreshold blocks as this has a significant influence on the device matching and manufacturability. To limit systematic shifts in the threshold voltage and mobility of the transistors, both the Well Proximity Effect (WPE) and the STI stress effect [46] have been taken into account. The WPE was mitigated by increasing the gate distances to the well edge. To limit the STI stress effect on the channel mobility and threshold voltage the number of transistors fingers were limited to be less than two [46]. Additionally, we focused on developing very regular layout for subthreshold blocks to increase the matching properties of the devices [47]. In the layout of the logic cells, there is no rounding and routing in the poly layer. Moreover, regular diffusion areas have been drawn in the layout and all the poly polygons have single direction. Well ties are placed close to the devices active area to provide a uniform potential for the channel area or the back-gate of transistors. Figures 2.14 [35] and 2.15 [15] illustrate the representative layout of 1-bit full adders implemented in 65 nm bulk and 28 nm FDSOI technologies.

Fig. 2.14: Layout of the 1-bit Full Adder developed in 65 nm [35].

Fig. 2.15: Layout view of the 1-bit full adder (a) implemented with min-3 gates (b) implemented with Boolean gates [15].

### 2.3 Ultra low-power/voltage full adder design

As one of the fundamental components of datapath circuits, the full adder is an important element of digital systems. Therefore, full adders have been considered in the development of ultra-low voltage building blocks of this thesis both in 65 nm Bulk and 28 nm FDSOI technologies. To have robust circuits we used static CMOS logic gates in the implementation of all the FAs. The ripple carry adder (RCA) topology has been chosen because the energy consumption of the serial adders may be lower than the parallel adders while maintaining the same speed, when operated in subthreshold [48].

#### 2.3.1 FA based on min-3 and Boolean logic gates

A 16-bit RCA based on Boolean gates and a 32-bit RCA based on min-3 logic gate have been implemented with same device sizing strategy in paper IX [15]. It has been reported in [15] that more samples of RCA based on Boolean gates achieves minimum supply voltage of 110 mV. However, this comes at the cost of higher energy consumption and larger area. Additionally, all the samples of 32-bit and 16-bit RCAs were able to operate correctly down to 125 mV. This is in line with the results in section 2.1.3, which show that the designed min-3 logic gate does not mitigate the functional yield of a subthreshold cell library for supply voltages higher than 130 mV. The minimum operating voltage of all the 32-bit RCA samples in [15] reduced to 80 mV by applying reverse back bias voltages to the back-gate of the PMOS transistors. This indicates that the min-3 logic cells have a robust performance against the mismatch variations.

#### 2.3.2 Characteristics of the RCAs developed in 65 nm and 28 nm

TABLE 2.2 compares the developed adders in this thesis to the state-of-theart subthreshold adders. To the best of author's knowledge and up until publication dates of [35] and [15]: I) The minimum operating voltage of 84 mV is the lowest reported supply voltage for static CMOS logic gates [35]. II) The 32-bit adder based on min-3 logic gates in [15] achieved 0.65 fJ per 1-bit addition, which was the lowest reported energy per 1-bit addition based on the measurement results.

#### 2.3.3 MAC and multiplier blocks based on developed FAs

An 8-bit multiply-accumulate (MAC) was implemented in 28 nm FDSOI using the FAs based on min-3 gates. The MAC is reported in paper V [16]. Comparing specifications of the designed MAC to the state of the art subthreshold MAC blocks, reveals better energy efficiency for the MAC block

|                                  | [35]              | [15]              | [15]               |                   |         |                    |               |               |  |  |  |

|----------------------------------|-------------------|-------------------|--------------------|-------------------|---------|--------------------|---------------|---------------|--|--|--|

|                                  | paperII           | paperIX           | paperIX            | [49]              | [50]    | $[51]^*$           | [51]*         | [52]*         |  |  |  |

| # bits                           | 32                | 32                | 16                 | 32                | 32      | 32                 | 16            | 9             |  |  |  |

| technology                       | 65nm              | 28nm<br>FDSOI     | 28nm<br>FDSOI      | 90nm              | 90nm    | 28nm<br>FDSOI      | 28nm<br>FDSOI | 28nm<br>FDSOI |  |  |  |

| $E_{min}$ 1-bit                  | 1.59fJ*           | 0.65fJ            | $0.77 \mathrm{fJ}$ | 2.96fJ            | 12.75fj | $6.48 \mathrm{fJ}$ | 4.68fJ        | 1.03fJ        |  |  |  |

| Delay@MEP                        | 82.52ns           | $3.24\mu$ s       | 6.2us              | $10\mu$ s         | 52.6ns  | $0.898\mu$ s       | $0.448 \mu$ s | $0.555 \mu$ s |  |  |  |

| $V_{dd}$ @MEP                    | $275 \text{mV}^*$ | $300 \mathrm{mV}$ | $250 \mathrm{mV}$  | 330mV             | 190mV   | $300 \mathrm{mV}$  | 300mV         | 240mv         |  |  |  |

| $V_{ddmin}$                      | 84mV              | 110mV             | 110mV              | $250 \mathrm{mV}$ | 190mV   | N. A.              | N. A.         | N. A.         |  |  |  |

| * Post-layout simulation results |                   |                   |                    |                   |         |                    |               |               |  |  |  |

Tab. 2.2: Comparison with existing ULV full adders

Post-layout simulation results.

in [16], so that the speed drop could be overcompensated by increasing the supply voltage. The minimum energy point of the 8-bit MAC block was 0.051 pJ at 275 mV and 5.3 MHz clock frequency.

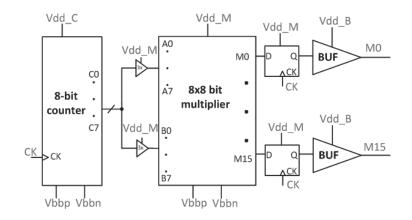

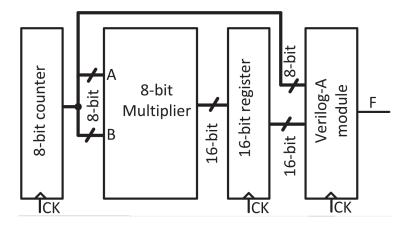

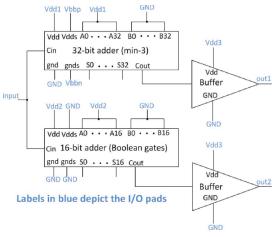

Fig. 2.16: Block Diagram of test circuit for the 8x8 bit multiplier.

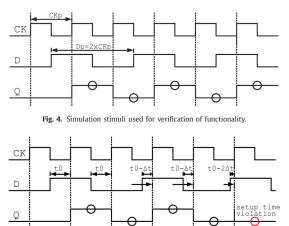

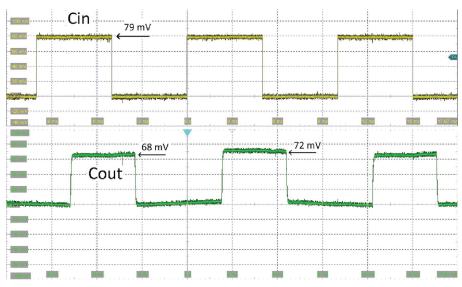

An 8x8 parallel multiplier based on the min-3 FAs of paper IX [15] was fabricated in the same 28 nm FDSOI technology. Figure 2.16 shows the block diagram of the circuit that was implemented to test the multiplier. The binary counter generates input test vectors for the multiplier. M0 (LSB output) and M15 (MSB output) output signals are sampled at the rising edge of the clock signal. The outputs of the flip-flops are buffered to the I/O pads using LVT inverter chains. The counter counts from (00000000)2 to (1111111)2. The state of M0 switches at each rising edge of the clock signal. The M15 output stays at 0 until the input test vector switches from (10110101)2 to (10110110)2 and then returns to 0 when the input becomes (00000000)2 again. Therefore, the frequency of the M0 will be half of the clock frequency and its duty cycle will be 50%. The M15, on the other hand, will have a positive duty cycle of 28.9% and its frequency will be 1/256th of the clock frequency. The race-free flip-flop topology that we presented in paper IV [21] were used in implementation of the multiplier. The imple-

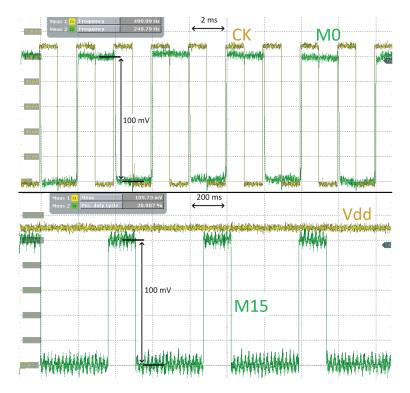

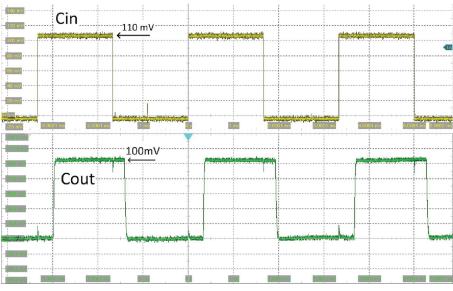

Fig. 2.17: Oscilloscope plots of output signals at a 110 mV supply voltage (a) LSB output of the multiplier (b) MSB output of the multiplier.

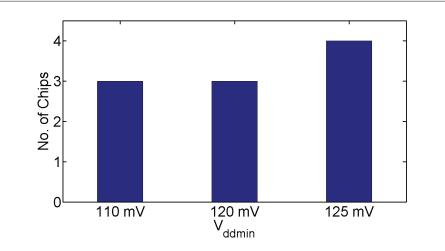

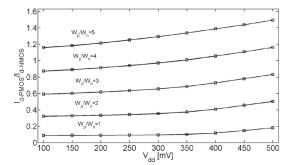

mented multiplier was able to operate correctly down to a supply voltage of 110 mV while back-gate of NMOS and PMOS transistors were grounded. Figure 2.17 shows the oscilloscope plots of the MSB and the LSB outputs of the multiplier. To assess the minimum functional voltage of the multiplier, we measure ten chip samples. Figure 2.18 illustrates the minimum  $V_{dd}$  of the adders as a histogram for ten measured samples. According to the measurement results of ten chip samples, the minimum energy per cycle of the

Fig. 2.18: Distribution of the measured minimum functional Vdd of ten samples.

Fig. 2.19: Measured energy per cycle and maximum operating frequency of the multiplier as a function of Vdd for ten samples.

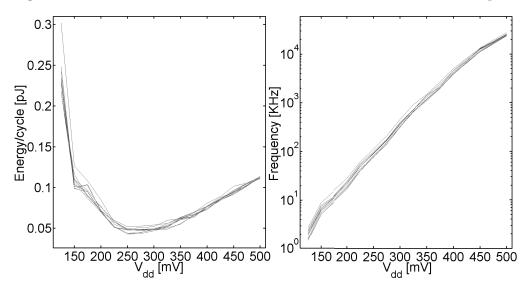

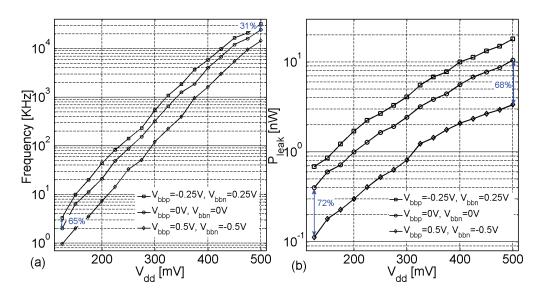

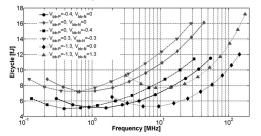

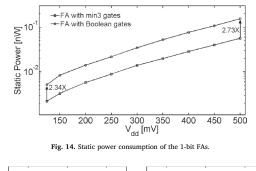

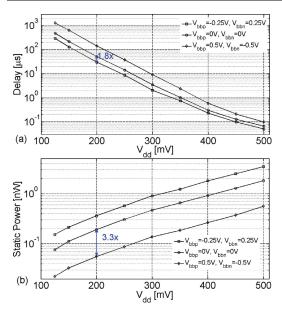

implemented 8x8 multiplier was down to 43 fJ/cycle for the sample with the lowest energy consumption and it had a robust performance. Figure 2.19(a) illustrates the energy dissipation per cycle of 8x8 multiplier versus supply voltage for ten measured chips. For the power measurements of the circuit, the maximum applicable clock frequency for a given supply voltage was ap-

plied. From Figure 2.19(a), the average minimum energy point of ten samples is 47.2 fJ/cycle at 250 mV. The measured maximum operating frequency of ten multiplier samples versus supply voltage is shown in Figure 2.19(b). The

Fig. 2.20: Measured (a) maximum operating frequency and (b) leakage power consumption of multiplier versus  $V_{dd}$  for multiple back-gate bias voltages.

performance and the leakage of the multiplier were investigated for reverse and forward back-gate biasing schemes. To apply a forward back-gate bias, we applied 0.25 V to the back-gate of NMOS transistors  $((V_{bbn})$  and -0.25 V to the back-gate of PMOS transistors  $(V_{bbp})$ . The leakage current through the parasitic PWELL/NWELL diodes was measured to be 31.5 nA in this case with 0.25 V forward back-gate bias. For a forward back-bias voltage of 0.3 V, the voltage drop over the parasitic WELL diodes is 0.6 V and the leakage current through the diodes increases to 1.5  $\mu$ A. Thus, we limited the forward back-gate bias to be 0.25 V. As shown in figure 2.20(a), the maximum operating frequency of the circuit increased by 65% and 31% at supply voltages of 125 mV and 500 mV, respectively. The reverse back-biasing scheme of the multiplier was explored with  $V_{bbn} = -0.5$  V and  $V_{bbp} = 0.5$  V. The leakage current through the parasitic diodes in this case was 1.1 nA. The power consumption due to the parasitic diodes leakage current was not taken into account for calculating power consumption of the multiplier. Figure 2.20(b)illustrates the static power of the circuit with three different back-biasing schemes. The static power of the multiplier decreases by 72% at 125 mV and 68% at 500 mV by applying a 0.5 V reverse back-gate bias. We did not apply higher reverse back-gate bias voltages because the speed of circuit at lower supply voltages drops drastically with larger reverse back-gate bias voltage. As shown in Figure 2.21, a Verilog-A module was used to analyze the output of the multiplier and check the functionality of the circuit at the low supply voltages. The Verilog-A module compares the outputs of the multiplier with the expected values of multiplication. The F output will be 1 if the output of the multiplier equals the expected value of the multiplication, otherwise it will be 0. To determine the minimum operating supply voltage,  $V_{dd}$  was reduced with 5 mV steps. The multiplier was functional down to a  $V_{dd}$  of 85 mV in both FS and SF process corners.

Fig. 2.21: Test-bench to apply stimuli to the multiplier circuit and analyze its output to verify functionality of the circuit.

### 2.4 Design considerations for ultra-low voltage flip-flops

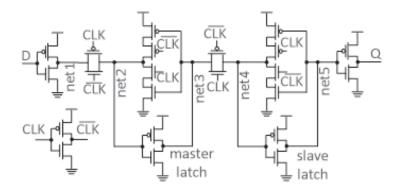

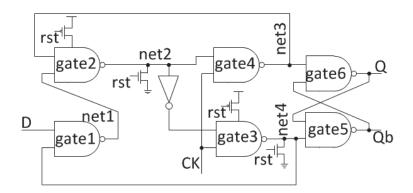

Flip-flops are the fundamental elements of synchronous systems and are reported to have a significant impact on power and robustness of the digital systems [53]. Sequential elements are more susceptible to PVT variations in comparison to combinational logic gates. Conventional master-slave flipflops operating with true and complementary clock phases have drawbacks such as: a) High dynamic power consumption due to the redundant toggling of local clock inverters; b) Sensitivity to the overlap between clock and its complement when the slope of the clock is not high [54]. These disadvantages of the master-slave DFFs with two-phase clocking schemes make them less attractive to be used in ultra-low voltage applications [55]. A PowerPC 603 D flip-flop is shown in Figure 2.22 as an example of a generic master-slave flip-flop to show contention in its internal nodes. 28 nm FDSOI technology was used to implement the DFF in Figure 2.22. RVT devices were used and Ln=30+16 nm (poly-biasing of 16 nm), Lp=30+4 nm(poly-biasing of 4 nm), Wn=200 nm and Wp=300 nm.

Fig. 2.22: Conventional PowerPC 603 D flip-flop.

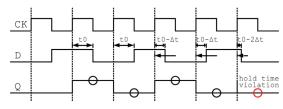

As the clock slope is not high at ULV domain, one challenge of using DFFs with two clock phases is that the overlap between the main clock and inverted clock signals might cause a contention in the internal nodes of a master-slave flip-flop and consequently results in a functional failure. Figure 2.23 demonstrates the race condition between the inverter of the master latch and the clocked inverter of the slave latch. In Figure 2.23 example, before the falling edge of the clock both net3 and net4 are high and when clock is low net4 remains at high and net3 switches to low. However, due to the clock-overlap at the falling edge of the clock signal, the PMOS transistor of the second transmission gate and the PMOS transistor of the clocked inverter in the slave latch are simultaneously on for a short period of time. This results in a race condition at node net4 where the inverter of the slave latch tries to keep it at logic-1. An inverter was added between the master latch and the second

transmission-gate of the PowerPC 603 DFF (see figure 2.22) to delay the turn-on of the master latch and avoid reverse current flow and hence mitigate the contention [31]. Additionally, the overlap time between CLK and CLKb signals depends on the slope of the input clock signal and is susceptible to PVT variations. This increases sensitive of master-slave DFFs to the slope of the input clock signal [54]. Larger or more clock tree inverters are required to make sure that clock slope is steep enough in the sinks, which in turn, results in a higher power consumption or a larger clock skew, respectively.

Fig. 2.23: Sensitivity to clock overlap in 603 D flip-flop.

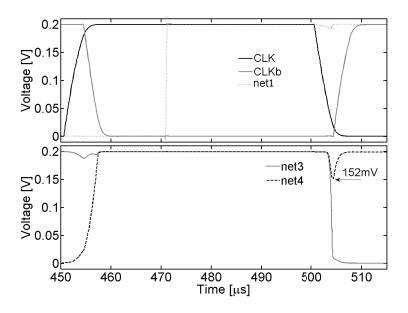

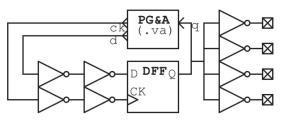

The race-free single-phase clocked D flip-flop (R-DFF) structure, introduced in [56], was used in the ULV logic cell libraries developed in this thesis. The circuit topology of a rising edge triggered race-free D flip-flops is shown in figure 2.24. A falling edge triggered version can be implemented by replacing all the NAND gates with NOR gates. Four extra transistors are required to add an asynchronous reset signal to these flip-flops. The measurement results of a divide-by-3 circuit implemented based on different versions of this DFF topology [21] (paper IV) confirm its functionality in ultra-low voltages domain down to 132 mV. The operation principle of the positive edge triggered DFF in figure 2.24(a) is that when CK=0 the outputs of gate3 and gate4 are 1 and the output of these gates will not change with changes in net2, thus the state of the output latch (gate5 and 6) will not change. For CK=1, D signal flows through the gate1, gate2 and inverter and changes the state of net3 or net4 to 0 this in turn changes the output latch state. As net3 or net4 discharged to 0 the output of gatet2 or gate1 will be tied to Vdd, hence net2 will be completely isolated from changes in D.

Fig. 2.24: Race-free single-phase clocked D flip-flop with asyncronous reset.

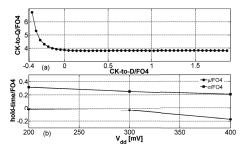

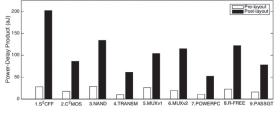

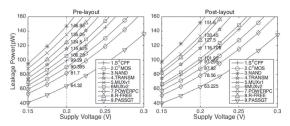

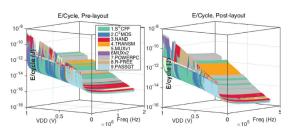

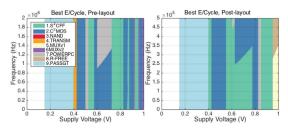

We have made a comparison between nine D-type flip-flops in paper VII [23]. According to the results reported in [23], the race-free (R-free) flip-flop has the second smallest core area and the second lowest energy per cycle (E/cycle) after the pass gate DFF. However, the pass gate DFF does not have a high yield compared to the other DFFs in Table 2 of paper VII [23]. According to the results presented in paper VII [23], the race-free DFF is among the flip-flops with low hold time and set-up time variations. It is worth mentioning that the applied clock signal to the flip-flops during the simulations in [23] had relatively sharp edges as it was buffered through two inverters and the load of the buffer was only a single flip-flop. Recall that the master-slave DFFs with two clock phases are more sensitive to the clock slew and longer transition times increases overlap between the clock and its complement.

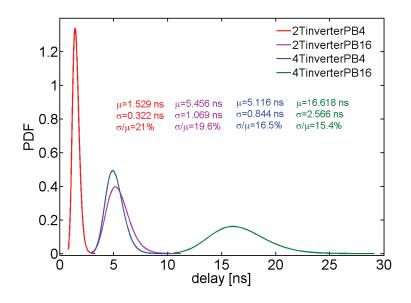

The number of transistors in the race-free DFF can be reduced by merging the logically equivalent transistors [57]. In figure 2.24, the NMOS transistors of gate3 and gate4 with gate terminals connected to the clock can be shared. By the same token, the NMOS transistors in gate2 and gate6 with gate terminals connected to net3, and the NMOS transistors in gate1 and gate5 with gate terminals connected to net4, can be merged. Therefore, total number of the transistors in the R-free DFF can be reduced to 23 devices. I avoided transistor sharing during the DFF development as we aimed at having layouts based on identical patterns to increase the regularity of the logic cells. The custom library cells, introduced in paper V [16], was expanded by adding hold buffers for fixing hold-time violations and specialized inverters to be used in the clock tree.

Fig. 2.25: Delay distributions of four different inverters.

As presented in paper I [18], the stacked logic cells have larger delay and less delay variability compared to the conventional static CMOS logic cells. Therefore, the stacked inverters together with a slight increase in the gate length were added to the library cell to be used in buffering for fixing holdtime violations. The gate length of logic cells in the developed custom cell library [16] have increased by 4 nm to improve  $I_{on}/I_{off}$  ratio of the cells. Another inverter with 16 nm poly biasing was also added to the library for fixing hold-time violations. Figure 2.25 shows delay distribution of different version of inverters. 2T-inverter-PB4 is a 2-transistors inverter with 4 nm poly biasing. T-inverter-PB16 is a 2-transistors inverter with 16 nm poly biasing. 4T-inverter-PB16 is an inverter with 4 stacked transistors and 4 nm poly biasing. 4T-inverter-PB16 is an inverter with 4 stacked transistors and

Fig. 2.26: 3-level clock tree clock tree architecture.

16 nm poly biasing.

Tab. 2.3: Parasitic capacitance and number of inverters at each level of the clock

| tree.   |         |      |                          |           |      |

|---------|---------|------|--------------------------|-----------|------|

| INVs@   | INVs@   | CL1  | max/min                  | max/min   | Skew |

| Level-2 | Level-3 | [fF] | $\operatorname{CL2}[fF]$ | CL3[fF]   | [ns] |

| 2INVx4  | 6INVx16 | 13.7 | 28.7/27.2                | 98.2/89.2 | 0.6  |

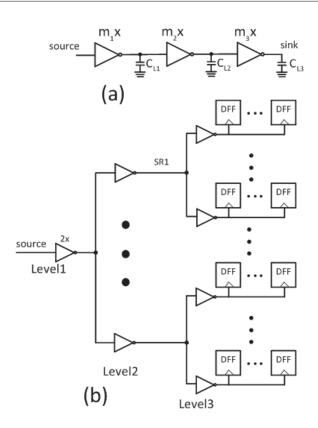

It is shown in [58] that in ultra-low voltage (ULV) domain, wires resistance is negligible compared to the devices on-resistance. Consequently, developing clock networks with few levels of clock hierarchy and large buffers for sub-modules result in less clock skew imposed by clock buffers mismatch.

Fig. 2.27: 3-level clock tree routed for a pipeline multiplier with 296 sinks.

However, as demonstrated in [59] and [60], input slew variations can result in larger buffer delay variations, and hence, larger clock skew. Therefore, clock slew rate must be taken into account during the clock tree design in ULV domain.

As shown in figure 2.26, a 3-level clock-tree is designed for a 16-bit pipeline multiplier [61] with 296 sinks (i.e. flip-flops). Table 2.3 lists parasitic capacitance, number of inverters at each level, drive strength of inverters and estimated deterministic clock skew achieved from place and route tool (Cadence Encounter) for the developed clock network. Layout view of the routed clock tree for a 16-bit pipeline multiplier is shown in figure 2.27.

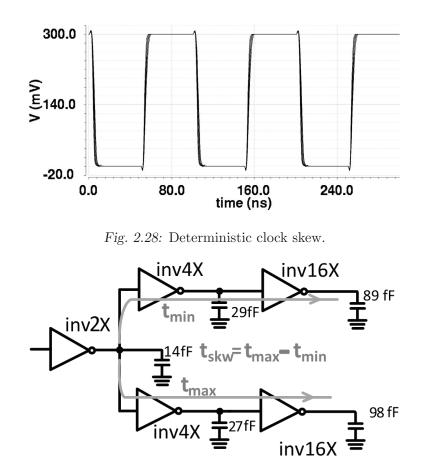

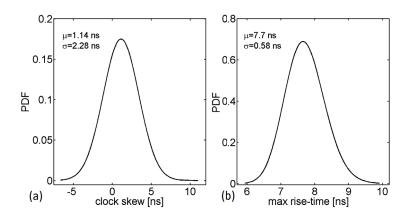

Figure 2.28, shows clock signals at the sinks of the 16-bit pipeline multiplier. An extracted netlist of the multiplier was used to draw the clock signal at the sinks. The worst interconnect corner (RC-max) was used during the extraction. The maximum deterministic clock skew from Figure 2.28 is 0.8 ns. To estimate the statistical clock skew, clock paths with minimum and maximum delays were extracted from the place and route tool. The benchmark in Figure 2.29 was used to calculate the statistical clock skew of the implemented clock tree. 3000 Monte Carlo runs were carried out at typical process corner and 300 mV supply voltage. Figure 2.30(a) shows the clock skew distribution at 300 mV. The distribution of the slew-rate at the sink of the maximum clock path is shown in 2.30(b).

Fig. 2.29: Benchmark for statistical clock skew analysis.

Fig. 2.30: Statistical clock skew and slew

Fig. 2.31: Measured minimum  $V_{ddLs}$  of ten LS samples as a histogram.

Multiple voltage domains are usually employed to address issues such as speed, area and robustness of ultra-low voltage and ultra-low power systems.

Level-shifters (LS) are essential blocks to ensure correct signal communication between different voltage levels. For example, more than hundred levelshifters were used in [6] to communicate between 14 voltage domains including an ARM Cortex-M0+ processor which had a minimum operating voltage of 250 mV. Energy harvesting systems scavenge energy from extremely lowinput voltage levels. A robust level-shifter capable of up-converting extremely low-voltage levels can be used to drive the charge-pump switches [62] in energy harvesting systems.

In paper X [25], we presented an energy efficient level-shifter with ability to upconvert sub-50mV input voltage to nominal 1 V. The top diode connected devices are proposed to be used along with the current-limiter diodes. Additionally, a single-NWELL (SNW) configuration together with backgate and poly biasing techniques create an adequate balance between the drive strength of PUN and PDN.

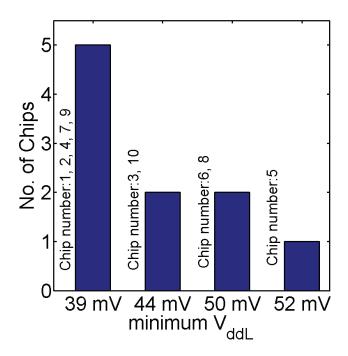

The distribution of the minimum convertible  $V_{ddL}$  for ten measured chip samples is shown in figure 2.31. Five samples were able to up-convert a 39 mV input to 1V while the minimum convertible input voltage level was 52 mV for one sample. At 0.2 V and 1 MHz, the energy per switching and the delay of the design LS was 5.2 fJ and 10.1 ns, respectively.

### 3. CONCLUSION

This thesis focused on developing ultra-low voltage building blocks for power and energy efficient systems. Design considerations for development of ultralow voltage and robust logic cell libraries demonstrated throughout this thesis at different abstraction levels. We developed building blocks in 65 nm bulk and 28 nm FDSOI technologies including logic cells, full adders, flip-flops and a level-shifter. The logic cell library based on low-threshold 28 nm FDSOI devices (reported in paper V) extended by adding delay elements for fixing hold-time violations and inverters to be used for developing a robust and low-power clock tree.

In 65 nm bulk technology, we designed logic cells based on thin-oxide (paper II) and thick-oxide (paper III and IV) transistors. Reverse short-channel effect and inverse narrow width effect were considered in the design of the logic cells to improve the robustness and energy efficiency of the cells. Moreover, different threshold voltage flavors examined to meet the required performance or power consumption. We also utilized very regular layout techniques to improve manufacturability of the cells. The developed logic cells were used in implementation of the full-adders and flip-flops. The measurement results were reported in papers II, III and IV.

In 28 nm FDSOI technology, we developed logic cells based on low-Vt (flipped well) and regular-Vt devices. The low-Vt based library cell was reported in Paper V and are proper for applications where the circuit throughput can be an important parameter. Logic cells based on the regular-Vt devices were reported in Paper IX. These cells are appropriate for applications with more relaxed throughput requirements. For the 28 nm FDSOI cells, we used knobs such as back-gate biasing and poly biasing and the narrow width effect was taken into account to have a good balance between area and robustness of the cells. An ultra-low voltage and energy efficient level-shifter with a single-NWEL layout was also implemented in 28 nm FDSOI technology and reported in Paper X.

To the best of author's knowledge: 1) the minimum operating voltage of 84 mV in Paper II was the lowest reported supply voltage for the static CMOS logic gates. 2) The 32-bit adder based on min-3 logic gates in Paper IX achieved the lowest reported energy per 1-bit addition of 0.65fJ. 3) the level-shifter in Paper X achieved the lowest reported  $V_{ddL}$  of 39 mV. We also showed a very robust performance for the flip-flop cells. According to the measurement results presented in Paper IV, the minimum operating voltage of 132 mV was achieved for a divide-by-3 circuit which was implemented using the race-free flip-flop structure. The same flip-flop topology was used in the implementation of the reported 8x8 multiplier in section 2.3.3.

# 4. PUBLICATIONS

4.1 paper I

# Modular Layout-friendly Cell Library Design Applied for Subthreshold CMOS

Conference publication presented at IEEE NORCHIP 2014. Publication date: 08 January 2015.

This paper is not included due to copyright available at https://doi.org/10.1109/NORCHIP.2014.7004747

4.3 paper III

Exploiting short channel effects and multi-Vt technology for increased robustness and reduced energy consumption, with application to a 16-bit subthreshold adder implemented in 65 nm CMOS

Conference publication presented at IEEE European Conference on Circuit Theory and Design (ECCTD-2015). Publication date: 19 October 2015.

This paper is not included due to copyright available at https://doi.org/ 10.1109/ECCTD.2015.7300053

4.4 paper IV

# 4 Sub-/near-threshold flip-flops with application to frequency dividers

Conference publication presented at IEEE European Conference on Circuit Theory and Design (ECCTD-2015). Publication date: 19 October 2015.

This paper is not included due to copyright available at https://doi.org/10.1109/ECCTD.2015.7300058

4.5 paper V

### 28 nm UTBB-FDSOI energy efficient and variation tolerant custom digital-cell library with application to a subthreshold MAC block

Conference publication presented at IEEE 23rd International Conference Mixed Design of Integrated Circuits and Systems (2016 MIXDES). Publication date: 04 August 2016.

## 28 nm UTBB-FDSOI Energy Efficient and Variation Tolerant Custom Digital-Cell Library with Application to a Subthreshold MAC Block

Ali Asghar Vatanjou, Trond Ytterdal, Snorre Aunet

Department of Electronics and Telecommunications, Norwegian University of Science and Technology

O. S. Bragstads Plass 2 A, 7491 Trondheim, Norway

Email: ali.vatanjou@iet.ntnu.no

Abstract—This paper presents the design of digital logic cells for subthreshold applications using 28 nm ultra-thin body and box fully depleted silicon on insulator technology. The sizing approach relies on balancing pull-up/pull-down networks (PUN/PDN) strength ratio by applying an additional forward back-gate biasing (FBB) voltage to the back-gate of PMOS transistors. The minimum width of PMOS and NMOS transistors have been chosen by taking the narrow width effect into account. Moreover, to increase the functional yield of the logic cells, a trade-off has been made between  $I_{on}/I_{off}$  ratio and energy consumption through increasing the channel length by 4 nm. Energy consumption of logic gates analyzed using ring-oscillators consisting of basic logic gates. It has been shown that balancing logic gates through applying an additional FBB to the PMOS back-gate instead of up-sizing PUN results in 30% lower energy consumption in ring-oscillators. An 8-bit multiply-accumulate (MAC) block was synthesized using the fully customized logic cells with asymmetric back-gate biasing. Compared to a state-ofthe art MAC, the energy consumption of our MAC was improved by 21% at a relatively high speed (147 MHz).

Index Terms—Subthreshold, CMOS FDSOI, back-gate biasing, Low-power/voltage.

#### I. INTRODUCTION

Various process techniques have been introduced to reduce short channel effects in CMOS devices. Among them, the ultra-thin body and box (UTBB) fully depleted silicon on insulator (FDSOI) technology is one of the potential technologies to continue the CMOS technology roadmap. Lower random dopant fluctuations (RDF) and reduced short channel effects such as higher subthreshold slope and lower drain induced barrier lowering (DIBL) make this technology a proper choice for ultra-low voltage (ULV) applications [1]. Additionally, UTBB-FDSOI provides effective knobs such as back-gate biasing (BB) and poly biasing, which helps designers to make trade-offs between power, speed and area [2].

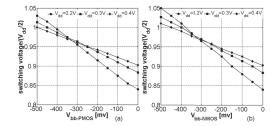

In this paper, the design of logic cells for subthreshold applications is demonstrated using 28 nm UTBB-FDSOI technology. Dimensioning of the logic cells has been done in different steps. As variability is the primary concern in subthreshold design, device dimensions have been chosen to be larger than minimum allowed dimensions to mitigate variability of the cells. In the first step, the gate length of the transistors was increased by 4 nm using poly-biasing. This leads to a tradeoff between energy consumption and noise margin where with 13.4% more energy consumption 46% improvement in  $I_{on}/I_{off}$  ratio of the transistors was achievable. Threshold voltage of 28 nm UTBB-FDSOI transistors decreases with increasing the device width owing to the Narrow Width Effect (NWE). In the second step, a minimum width for PMOS and NMOS transistors was chosen considering threshold voltage variations versus devices width to reduce threshold voltage variations due to NWE. Subsequently in third step, an additional constant FBB voltage was applied to the back-gate of PMOS to balance PMOS/NMOS strength ratio.

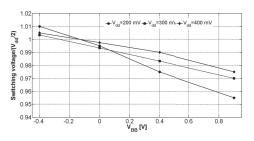

Various back-gate biasing schemes of the FDSOI technology have been discussed in [3] and it has been shown that adaptive and inverse adaptive BB schemes are very effective approaches to cancel systematic mismatch between PMOS and NMOS in subthreshold region. However in [3], different BB schemes on commercial standard cell library are investigated at schematic level. In this paper, we developed a full custom cell library at layout level. Moreover, we will demonstrate that with a constant additional BB voltage applied to the back-gate of the PMOS, strength ratio of the PMOS and NMOS can be modified over a  $V_{dd}$  range from 0.15 V to 0.4 V and backgate voltage from -400 mV to 900 mV. Therefore, the design of on-chip body bias generator [4] is more straightforward because additional back-gate biasing voltage which is applied to the PMOS is constant over  $V_{dd}$  and BB voltages. Ringoscillators made of basic logic gates used to evaluate energy consumption of the logic gates. Logic gates sized to have maximum Static Noise Margin (SNM) using symmetric and asymmetric back-gate biasing schemes. SPICE simulations confirmed that energy per operation of the ring-oscillator with asymmetric back-gate biasing was improved by 30% compared to energy per operation of the ring-oscillator with symmetric back-gate biasing. We synthesized an 8-bit MAC using the developed costume cell library. The designed MAC was compared to the other subthreshold MACs [5], [6] and [7].The MAC presented in this work achieves lower energy and EDP (21% and 24% saving, respectively) at 147 MHz operating frequency compared to the MAC in [7].

In this paper, first we will describe logic cells dimensioning. The back-gate biasing scheme is discussed in section III. In section IV, the design of sequential element is shown. Section V presents design of an 8-bit MAC block.

Fig. 1. (a)  $I_{on}/I_{off}$  ratio of NMOS and PMOS vs. L (b) Energy per operation of the ring-oscillator vs. L ( $V_{ds}{=}200$  mV).

#### II. DEVICE SIZING

#### A. Increasing the channel length to improve $I_{on}/I_{off}$