## Kristoffer Krav Skjølseth

## Design and Characterization of a 20 W Dual-Input Doherty Power Amplifier

Master's thesis in Electronic Systems Design Supervisor: Associate Professor Morten Olavsbråten July 2019

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Master's thesis

Kristoffer Krav Skjølseth

## Design and Characterization of a 20 W Dual-Input Doherty Power Amplifier

Master's thesis in Electronic Systems Design Supervisor: Associate Professor Morten Olavsbråten July 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

# Abstract

The high PAPR characteristic of signals used in modern wireless communication systems causes poor RFPA performance in terms of efficiency.

The Doherty power amplifier architecture (DPA) employs two amplifiers to implement load modulation in order to increase the poor back-off efficiency typically seen in conventional RFPA's. This thesis explores the benefits of dynamically controlling the relative phase between the input signals to the two amplifiers, as well as using adaptive auxiliary device biasing in order to improve the performance of DPA's.

A 20 W dual-input DPA prototype utilizing two GaN HEMT's as its main and auxiliary device is designed using ADS, with focus on maintaining the bandwidth in the low power and Doherty region.

The designed prototype is characterized in a fully automated measurement setup which utilizes scalar power measurements to approximate the relative phase between the two input signals in order to align them in phase. The prototype is characterized with both dynamic and fixed phase and bias.

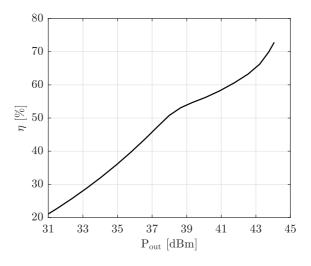

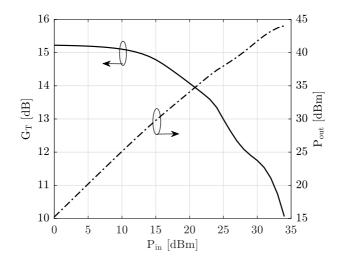

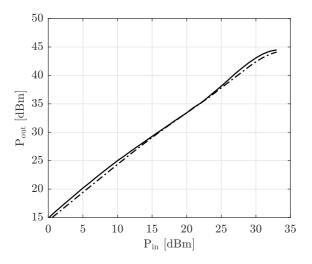

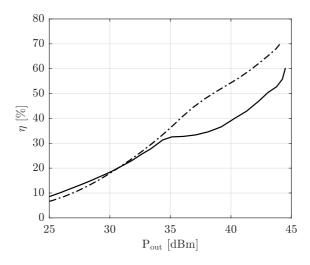

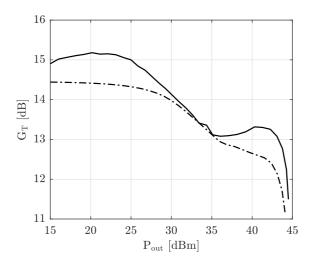

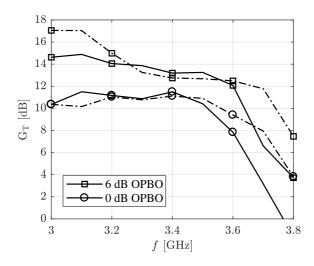

With fixed phase and bias, the measured results show that the prototype delivers a peak output power of 44 dBm at a peak efficiency of 58 %. When the phase is allowed to vary dynamically as a function of input power, and the bias is kept fixed, the prototype delivers a peak output power of 43 dBm at a peak efficiency of 63 %.

The back-off efficiency is measured to be only 33% due to not having used a sufficiently large auxiliary device bias sweep range in the measurement setup. However, with dynamic phase the efficiency in the Doherty region is around 10% higher than in the case with fixed phase.

With both dynamic phase and dynamic bias, the prototype shows an extremely flat gain response, although at the expense of efficiency.

# Sammendrag

Signaler som brukes i moderne systemer for trådløs kommunikasjon har typisk høy PAPR. Dette gjør at ytelsen til RF-effektforsterkerne som brukes er lav når det gjelder virkningsgrad.

Doherty-effektforsterkerarkitekturen benytter to forsterkere til å implementere lastmodulasjon for å øke den lave gjennomsnittsvirkningsgraden som vanligvis sees i konvensjonelle RF-effektforsterkere. Denne masteroppgaven utforsker fordelene ved dynamisk styring av den relative fasen mellom inngangssignalene til de to forsterkerne, samt bruk av adaptiv forspenning av transistoren i auxiliary-forsterkeren for å øke ytelsen til Dohertyeffektforsterkeren ytterligere.

En 20 W DPA-prototype med to innganger – bestående av to forsterkere basert på to GaN HEMT – designes i ADS, med fokus på å opprettholde båndbredden i lav-effektog Doherty-regionen.

Prototypen karakteriseres i et helautomatisert måleoppsett som benytter skalare effektmålinger for å approksimere den relative fasen mellom de to inngangssignalene for å synkronisere de to signalene i fase. Prototypen karakteriseres med både dynamisk og fast fase og forspenning.

Med fast fase og forspenning viser de målte resultatene at prototypen leverer en maksimal utgangseffekt på 44 dBm med en maksimal virkningsgrad på 58 %. Når fasen tillates å variere dynamisk som funksjon av inngangseffekt, og forspenningen holdes fast, leverer prototypen en maksimal utgangseffekt på 43 dBm med en virkningsgrad på 63 %.

Gjennomsnittsvirkningsgraden måles til å være bare 33 %, grunnet et utilstrekkelig sveipeområde for forspenningen når målingene er gjort. Virkningsgraden i Doherty-regionen er imidlertid rundt 10 % høyere enn i tilfellet med fast fase.

Med både dynamisk fase og dynamisk forspenning viser prototypen en ekstremt flat gainrespons, men på bekostning av virkningsgrad.

# Preface

This thesis is submitted in partial fulfillment of the requirements for the degree of Master of Science at the Department of Electronic Systems at the Norwegian University of Science and Technology (NTNU) in Trondheim, Norway. The work was carried out between January and July 2019.

I would like to express my sincere gratitude to my supervisor, Assiociate Professor Morten Olavsbråten at the Department of Electronic Systems. His commitment to his students and his never-ending support and encouragement has been invaluable during my time as a master's student.

Trondheim, July 2019 Kristoffer Krav Skjølseth

# Table of Contents

| Ab | ostrac  | t                                      | Ι   |

|----|---------|----------------------------------------|-----|

| Sa | mmei    | ndrag                                  | II  |

| Pr | eface   |                                        | III |

| Li | st of H | ligures                                | XI  |

| At | obrevi  | ations                                 | XII |

| 1  | Intro   | oduction                               | 1   |

|    | 1.1     | Background                             | 1   |

|    | 1.2     | Scope of Work                          | 2   |

|    | 1.3     | Outline of Report                      | 2   |

| 2  | The     | oretical Background                    | 3   |

|    | 2.1     | Transmission Line Theory               | 3   |

|    |         | 2.1.1 Microstrip Line                  | 5   |

|    | 2.2     | S-Parameters                           | 7   |

|    | 2.3     | The Quarter-wave Transformer           | 8   |

|    | 2.4     | Basic RF Power Amplifier Design Theory | 9   |

|    |         | 2.4.1 Matching Networks                | 9   |

|    |         | 2.4.2 Bias Networks                    | 9   |

|   |       | 2.4.3 Stabilization Network                            | 10 |

|---|-------|--------------------------------------------------------|----|

|   | 2.5   | Conduction Angle and Amplifier Classes                 | 11 |

|   | 2.6   | Efficiency of Conventional RF Power Amplifiers         | 12 |

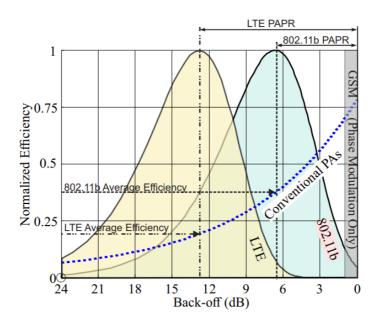

|   | 2.7   | High PAPR – Effects on Efficiency                      | 14 |

|   | 2.8   | Increasing the Back-off Efficiency                     | 15 |

|   | 2.9   | Active Load Modulation                                 | 17 |

|   | 2.10  | The Doherty Power Amplifier                            | 19 |

|   | 2.11  | Efficiency of the Doherty Power Amplifier              | 22 |

|   | 2.12  | Bandwidth of the Doherty Power Amplifier               | 23 |

|   | 2.13  | Variations of the Doherty Architecture                 | 24 |

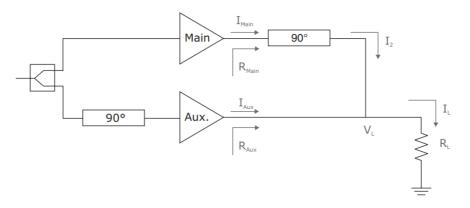

|   |       | 2.13.1 Digital Doherty Power Amplifier                 | 24 |

| 3 | Desig | gn methodology                                         | 25 |

|   | 3.1   | Preliminary Design Considerations                      | 25 |

|   | 3.2   | Transistors and Biasing                                | 26 |

|   | 3.3   | Initial Matching Networks                              | 28 |

|   | 3.4   | Finding R <sub>opt</sub>                               | 34 |

|   | 3.5   | Bias Networks                                          | 35 |

|   | 3.6   | Main Amplifier Output Network                          | 36 |

|   | 3.7   | Auxiliary Amplifier Output Network                     | 39 |

|   | 3.8   | Connecting it All Together                             | 41 |

| 4 | Auto  | mated Measurement Setup                                | 45 |

|   | 4.1   | General Measurement Considerations                     | 45 |

|   | 4.2   | Phase Coherence and Phase Control                      | 46 |

|   |       | 4.2.1 Measuring the Relative Phase Between Two Signals | 46 |

|   |       | 4.2.2 Phase Alignment                                  | 48 |

|   | 4.3   | Preamplification and Isolation                         | 52 |

|   |       | 4.3.1 Linearization and Gain Correction                | 53 |

|   | 4.4   | Transistor Biasing                                     | 54 |

|   | 4.5   | Output Power Measurements                              | 54 |

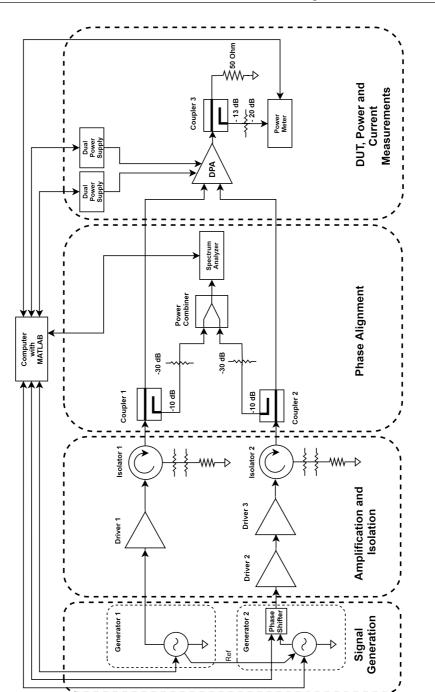

|   | 4.6   | Complete Measurement Setup                             | 55 |

|   |       | 4.6.1 The MATLAB script                                | 56 |

|   |       |                                                        |    |

| 5                                   | Results                           |                                           |    |  |

|-------------------------------------|-----------------------------------|-------------------------------------------|----|--|

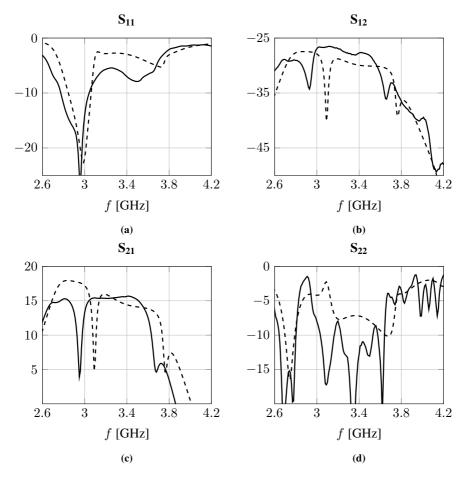

|                                     | 5.1                               | Small-Signal Results                      | 59 |  |

|                                     |                                   | 5.1.1 Main Amplifier                      | 60 |  |

|                                     |                                   | 5.1.2 Auxiliary Amplifier                 | 61 |  |

|                                     | 5.2                               | Large-Signal Results                      | 62 |  |

|                                     |                                   | 5.2.1 Fixed $\varphi$ and $V_{GS}$        | 62 |  |

|                                     |                                   | 5.2.2 Dynamic $\varphi$ , Fixed $V_{GS}$  | 67 |  |

|                                     |                                   | 5.2.3 Dynamic $\varphi$ and $V_{GS}$      | 70 |  |

| 6                                   | Disc                              | ission                                    | 73 |  |

|                                     | 6.1                               | Main Amplifier Performance                | 73 |  |

| 6.2 Auxiliary Amplifier Performance |                                   |                                           |    |  |

|                                     | 6.3 Doherty Amplifier Performance |                                           |    |  |

|                                     |                                   | 6.3.1 Fixed $\varphi$ and V <sub>GS</sub> | 74 |  |

|                                     |                                   | 6.3.2 Dynamic $\varphi$ and $V_{GS}$      | 75 |  |

|                                     | 6.4                               | Other Comments and Future Work            | 76 |  |

| 7                                   | Con                               | clusion                                   | 77 |  |

# List of Figures

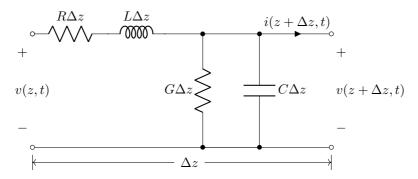

| 2.1  | Equivalent Circuit of Two-Conductor Transmission Line | 4  |

|------|-------------------------------------------------------|----|

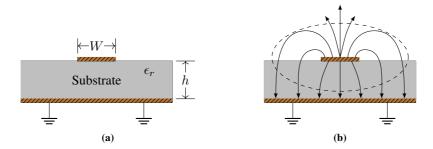

| 2.2  | Microstrip                                            | 5  |

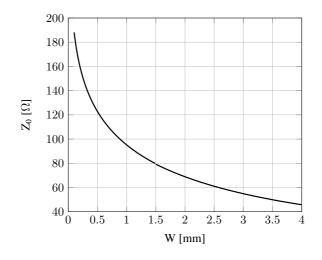

| 2.3  | Microstrip Characteristic Impedance versus Line Width | 6  |

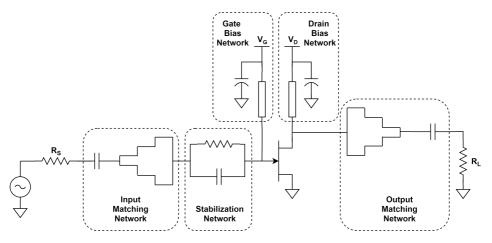

| 2.4  | Generic Power Amplifier Circuit                       | 9  |

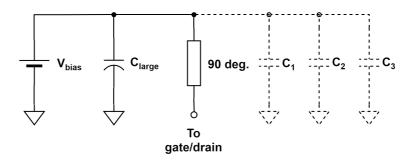

| 2.5  | Bias Network Example                                  | 10 |

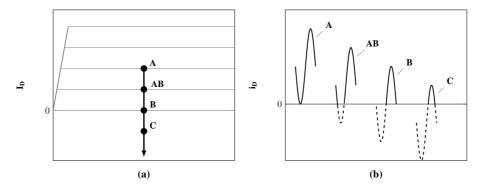

| 2.6  | Amplifier Class of Operation                          | 11 |

| 2.7  | Conduction Angle                                      | 11 |

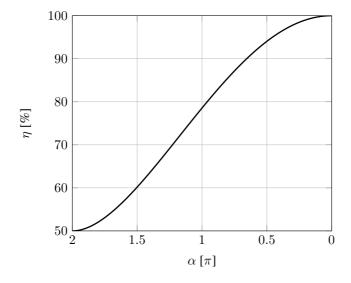

| 2.8  | Efficiency as a Function of Conduction Angle          | 13 |

| 2.9  | Efficiency as a Function of OPBO                      | 14 |

| 2.10 | Maximum Voltage and Current Swings                    | 15 |

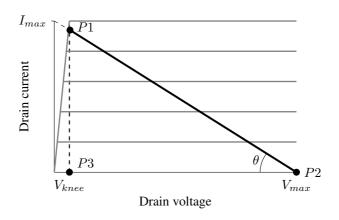

| 2.11 | Idealized Transistor I-V Curves and Load Line         | 16 |

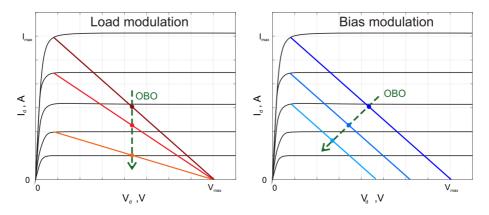

| 2.12 | Load and Bias Modulation                              | 16 |

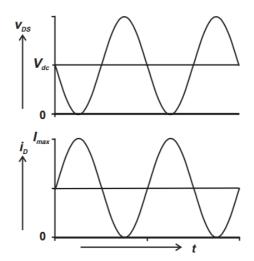

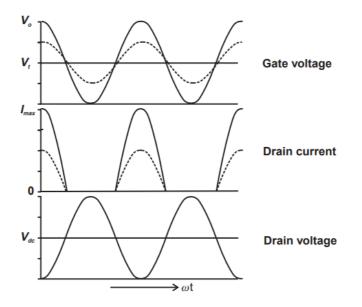

| 2.13 | Waveforms For Efficiency Analysis                     | 17 |

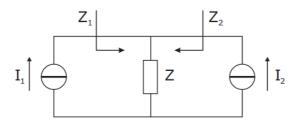

| 2.14 | The Active Load Principle                             | 19 |

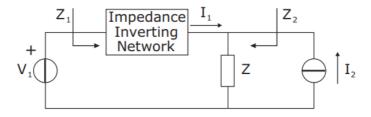

| 2.15 | Active Load with Impedance Inverter                   | 19 |

| 2.16 | Typical Doherty Configuration                         | 20 |

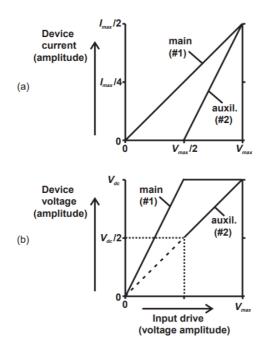

| 2.17 | RF Amplitude Variations versus Input Drive            | 20 |

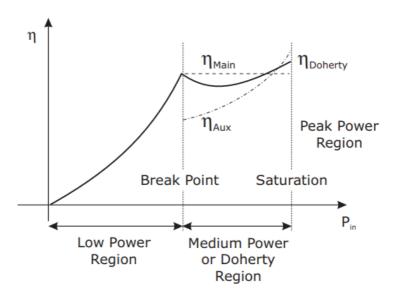

| 2.18 | Theoretical Efficiency of the Doherty Power Amplifier | 22 |

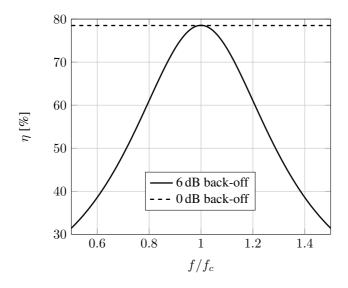

| 2.19 | Efficiency vs. Normalized Frequency                   | 23 |

| 3.1  | Doherty Design Basis                                  | 26 |

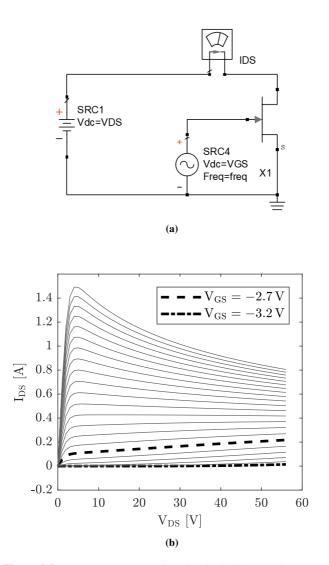

| 3.2                                                                                                                                                         | I-V Curve Generation Curcuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

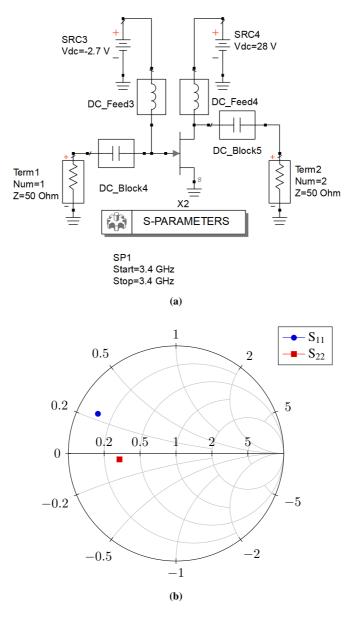

| 3.3                                                                                                                                                         | S-Parameters Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                             |

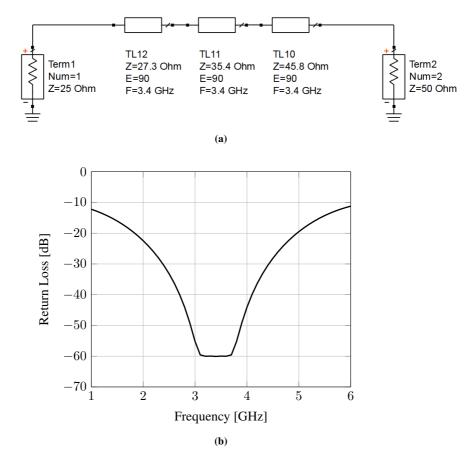

| 3.4                                                                                                                                                         | 3-Section Matching Transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                                                             |

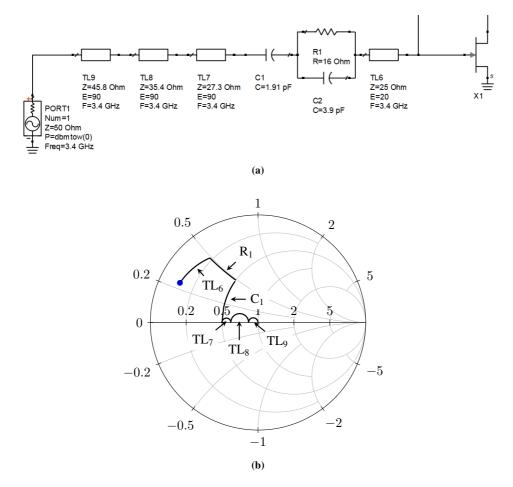

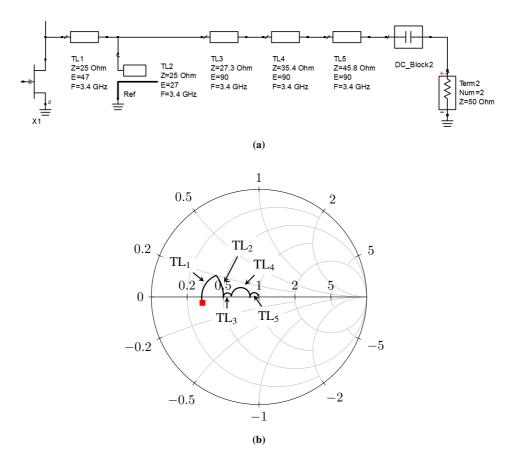

| 3.5                                                                                                                                                         | Initial Input Matching Network using Ideal Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                             |

| 3.6                                                                                                                                                         | Initial Output Matching Network using Ideal Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                                                             |

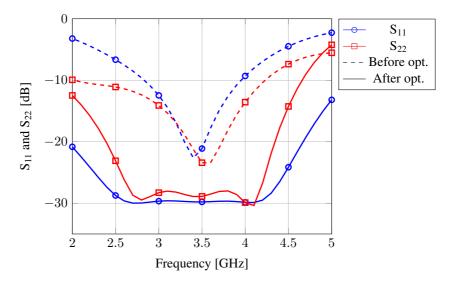

| 3.7                                                                                                                                                         | $S_{11}$ and $S_{22}$ with Initial Matching Networks $\hfill \hfill \hf$ | 33                                                                                                                                             |

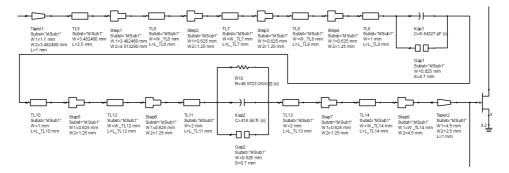

| 3.8                                                                                                                                                         | Input Network using Microstrip Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                                                                                             |

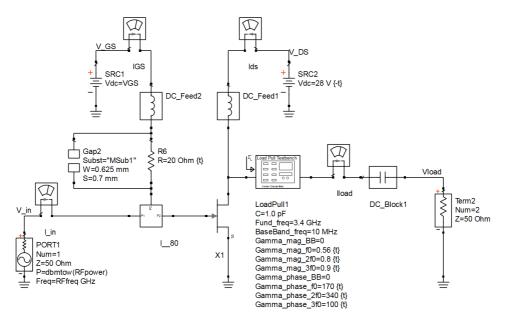

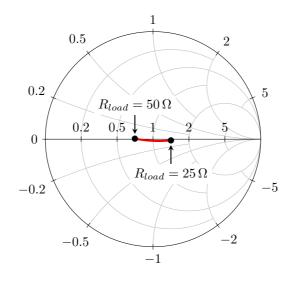

| 3.9                                                                                                                                                         | Simulation Setup to Determine $R_{opt}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                                                                                             |

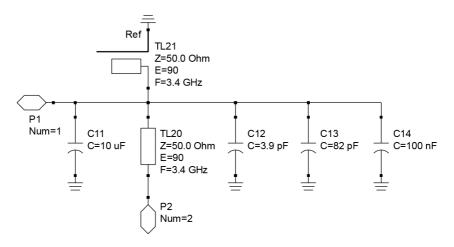

| 3.10                                                                                                                                                        | Ideal Bias Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                                                                                             |

| 3.11                                                                                                                                                        | Final Bias Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                                                             |

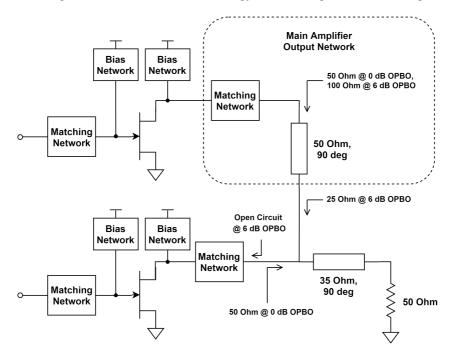

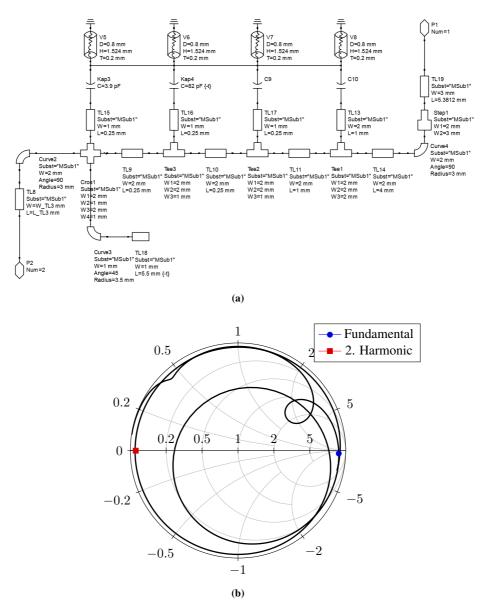

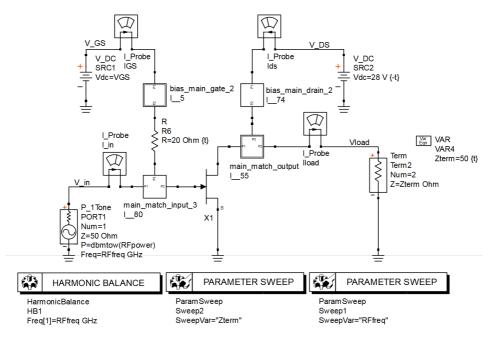

| 3.12                                                                                                                                                        | Simulation Setup to Synthesize Output Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                             |

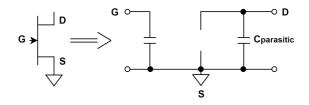

| 3.15                                                                                                                                                        | Simplified Small-Signal Model when the Transistor is not Conducting $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                                             |

| 3.16                                                                                                                                                        | Auxiliary Amplifier Output Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40                                                                                                                                             |

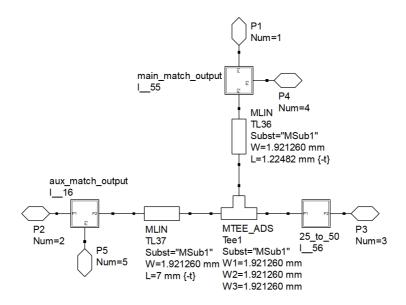

| 3.17                                                                                                                                                        | Connection of the Amplifier Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41                                                                                                                                             |

| 3.18                                                                                                                                                        | Output Multisection Transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                             |

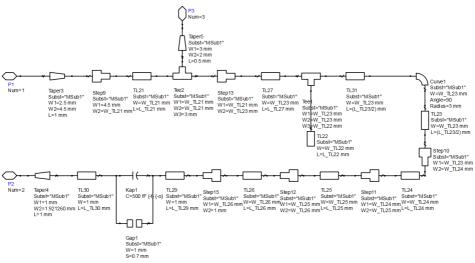

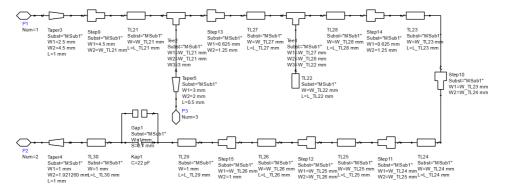

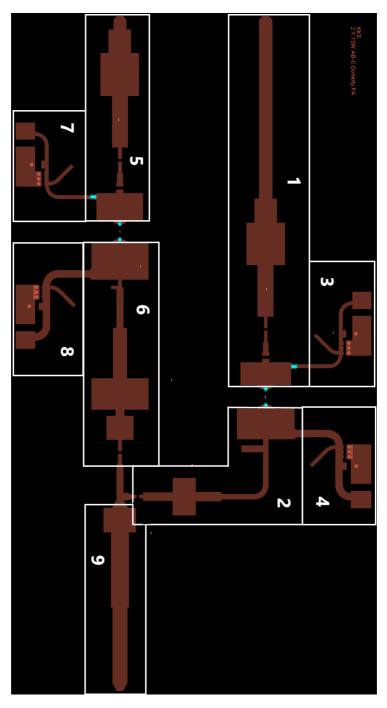

| 2 10                                                                                                                                                        | DPA Prototype Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                                                                                                             |

| 5.19                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                                             |

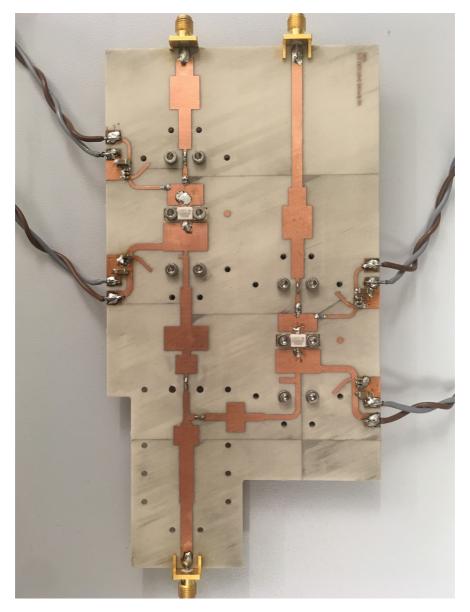

|                                                                                                                                                             | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44                                                                                                                                             |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

| 3.20                                                                                                                                                        | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44                                                                                                                                             |

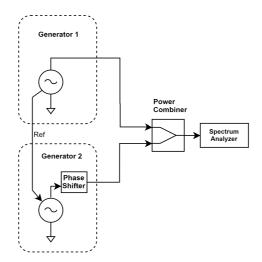

| 3.20<br>4.1                                                                                                                                                 | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47                                                                                                                                       |

| <ul><li>3.20</li><li>4.1</li><li>4.2</li></ul>                                                                                                              | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48                                                                                                                                 |

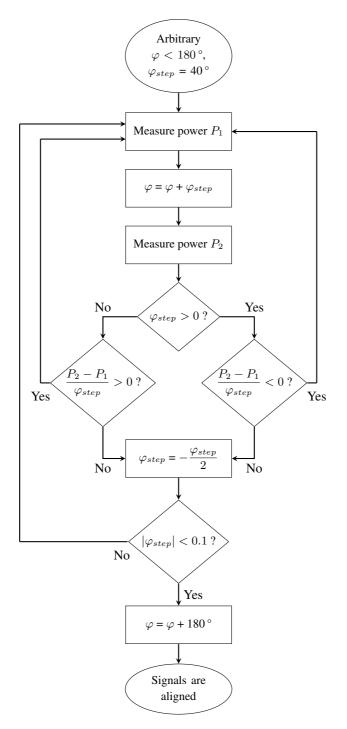

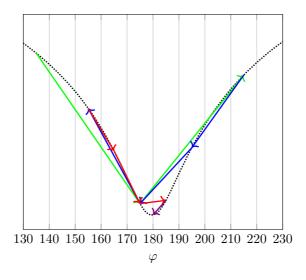

| <ul><li>3.20</li><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                                                                  | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48<br>50                                                                                                                           |

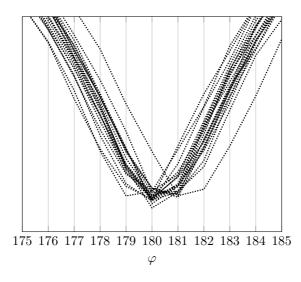

| <ul> <li>3.20</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul>                                                                                | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48<br>50<br>51                                                                                                                     |

| <ul> <li>3.20</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                                                   | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48<br>50<br>51<br>51                                                                                                               |

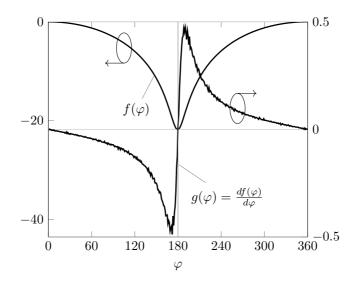

| <ul> <li>3.20</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                                                      | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48<br>50<br>51<br>51<br>52                                                                                                         |

| <ul> <li>3.20</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                                         | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44<br>47<br>48<br>50<br>51<br>51<br>51<br>52<br>53                                                                                             |

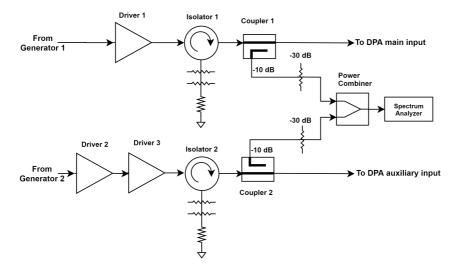

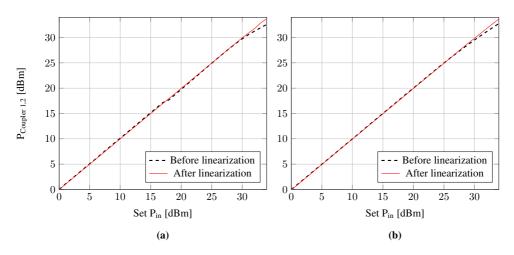

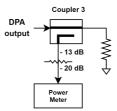

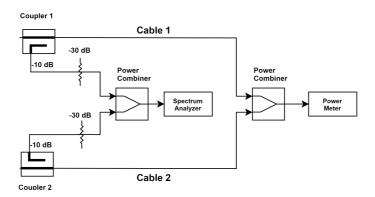

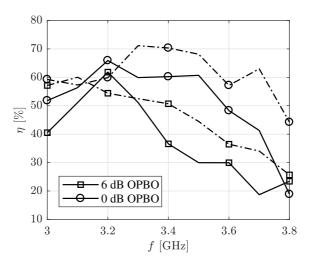

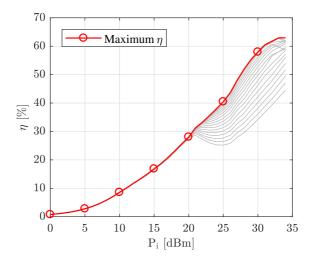

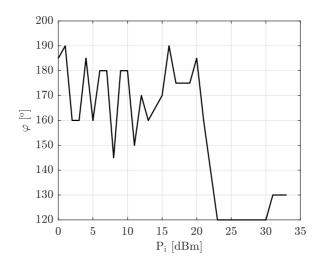

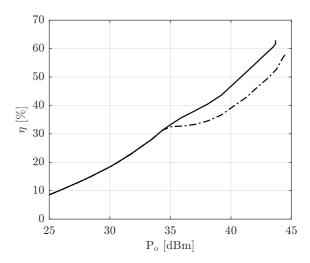

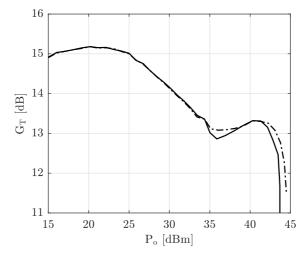

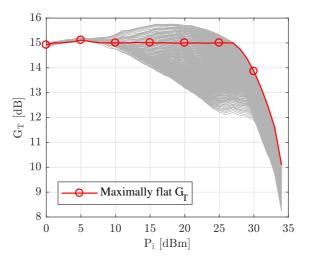

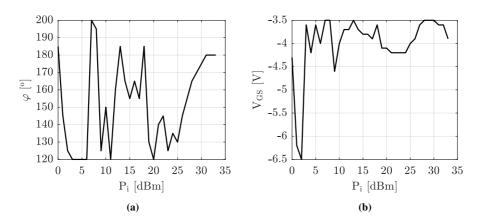

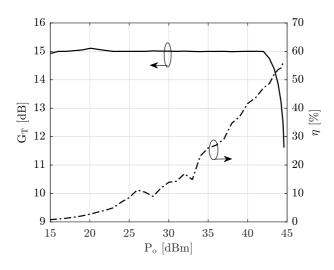

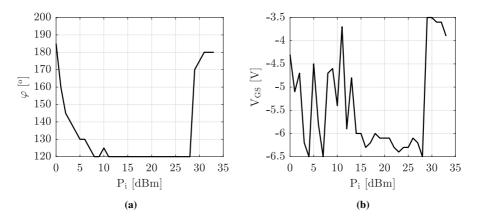

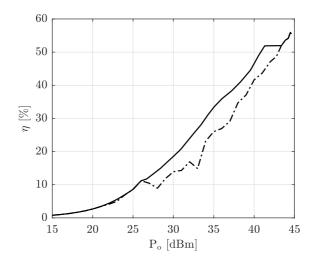

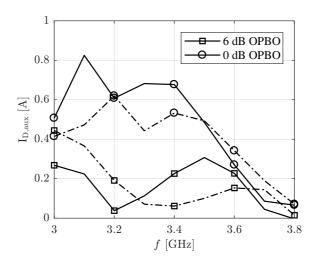

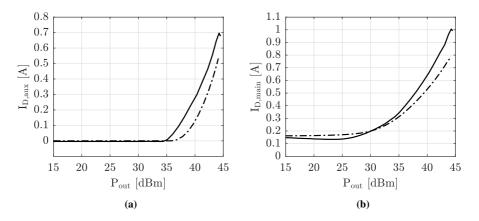

| <ol> <li>3.20</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ol>               | Assembled DPA Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>44</li> <li>47</li> <li>48</li> <li>50</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> <li>54</li> </ul>                         |