# Implementing Open flow switch using FPGA based platform

Ting Liu

Master of Telematics - Communication Networks and Networked Services (2 Submission date: June 2014 Supervisor: Yuming Jiang, ITEM Co-supervisor: Ameen Chilwan, ITEM Kashif Mahmood, Telenor

Norwegian University of Science and Technology Department of Telematics

Title:Implementing OpenFlow Switch using FPGA based platformStudent:Ting Liu

#### **Problem description:**

Network infrastructure has become critical in our schools, homes and business. However, current network architecture is static and unprogrammable. Recently, SDN (Software-Defined Networking) is appealed to make network programmable. OpenFlow is a typical protocol of SDN, which has gained attention because of its flexibility in managing networks. Control plane and data plane are separated in OpenFlow Switch. The intelligence of the network is OpenFlow controller and the traffic forwarding is done in the data plane based on the input from the control plane. One of OpenFlow benefits is that researchers and developers can develop intelligent new service rapidly and independently without waiting for new features to be released from equipment vendors. Additionally, OpenFlow Switch has already been implemented on NetFPGA [1]. This implementation has high latency to insert a new flow into OpenFlow Switch, which is still bottleneck. However the implementation of distributed multimedia plays (DMP) network nodes indicates lower latency and scalability features on FPGA based platform [2]. Therefore, this project is motivated to implement OpenFlow Switch (data plane and control plane) using FPGA based platform (Xilinx Virtex6) and also to analyse the performance to figure out whether it is better than current implemented OpenFlow Switch.

Planned tasks:

- Reviewing literatures about SDN (Software-Defined Networking) and OpenFlow Switch

- Learning the FPGA-based platform for SDN (OpenFlow Switch), especially hardware architecture in NTNU (Xilinx Virtex6)

- Implementing OpenFlow Switch (data plane and control plane) by VHDL using FPGA based platform (Xilinx Virtex6)

- Performance analysis of OpenFlow Switch implemented on FPGA based plat-form(Xilinx Virtex6) (e.g, delay, latency, loss)

| Responsible professor: | Yuming Jiang, Telematics  |

|------------------------|---------------------------|

| Supervisor:            | Ameen Chilwan, Telematics |

| External Collaborator: | Kashif Mahmood, Telenor   |

#### Abstract

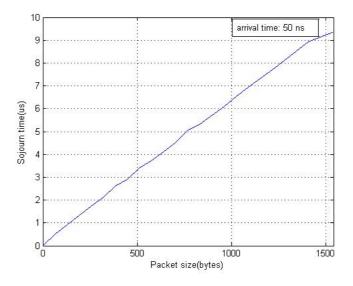

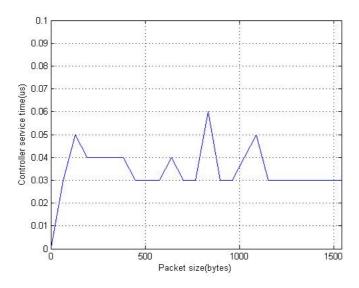

OpenFlow based SDN, is currently implemented in various networking devices and software, providing high-performance and granular traffic control across multiple vendors network devices. OpenFlow, as the first standard interface designed specifically for SDN, has gained popularity with both academic researchers and industry as a framework for both network research and implementation. OpenFlow technology separates the Control Plane from the Data Path and this allows the network managers to develop their own algorithms to control data flows and packets. Several vendors have already added OpenFlow to their features such as HP Labs, Cisco researchers, NEC, etc. Currently, OpenFlow Switch is already implemented on several different platforms e.g, in software (Linux, Open-WRT) and hardware (NetFPGA). More and more researchers implement the switch on FPGA-based platform, because FPGA-based platform is flexible, fast and reprogrammable. However, there are limited number of studies about the performance of the OpenFlow switch, which motivates this project. In order to do the research of OpenFlow performance, the simulation model of OpenFlow system is implemented in this project. The main objective of this project has two sides. On one hand, it is to implement OpenFlow system (switch and controller) using a hardware language on FPGA-based platform. On the other hand, it is also to measure the performance metrics of the OpenFlow switch, especially the service time (switch and controller) and the sojourn time. More specifically, data plane and control plane are both implemented on FPGA-based platform. It is designed in VHDL language by ISE design tools. FPGA-platform is Virtex6 type from Xilinx. It is observed from the results that the service time and the sojourn time both have almost linear increase with the increase in payload size. Moreover, the results indicate that the switch takes 2 clock cycles to respond to the writing request of the controller.

### Contents

| $\mathbf{Li}$ | st of | Figures                              | v         |

|---------------|-------|--------------------------------------|-----------|

| $\mathbf{Li}$ | st of | Tables                               | vii       |

| $\mathbf{Li}$ | st of | Algorithms                           | ix        |

| 1             | Intr  | oduction                             | 1         |

|               | 1.1   | Background and Motivation            | 1         |

|               | 1.2   | Problem Statement                    | 2         |

|               | 1.3   | Objectives                           | 3         |

|               | 1.4   | Methodology                          | 3         |

|               | 1.5   | Outline                              | 3         |

| <b>2</b>      | The   | oretical Background and Related Work | <b>5</b>  |

|               | 2.1   | Software-defined Networking (SDN)    | 5         |

|               | 2.2   | Advantages of OpenFlow-based SDN     | 6         |

|               | 2.3   | OpenFlow Architecture                | 7         |

|               |       | 2.3.1 OpenFlow Controller            | 8         |

|               |       | 2.3.2 OpenFlow Switch                | 10        |

|               | 2.4   | Components of OpenFlow Switch        | 10        |

|               |       | 2.4.1 OpenFlow protocol              | 10        |

|               |       | 2.4.2 OpenFlow flow tables           | 11        |

|               |       | 2.4.3 OpenFlow Channel               | 15        |

|               | 2.5   | FPGA-based platform                  | 15        |

|               | 2.6   | Related Work                         | 18        |

| 3             | Оре   | enFlow Switch Design Framework       | <b>21</b> |

|               | 3.1   | OpenFlow Switch Framework            | 21        |

|               |       | 3.1.1 Brief description              | 21        |

|               | 3.2   | Flow Table Entry Composer            | 23        |

|               |       | 3.2.1 Queue block                    | 24        |

|               |       | 3.2.2 Header parser block            | 25        |

|               |       | 3.2.3 Lookup entry composer          | 31        |

|              |                                         | 3.2.4   | Signals                                                                         | . 35          |

|--------------|-----------------------------------------|---------|---------------------------------------------------------------------------------|---------------|

|              |                                         | 3.2.5   | Simulation test                                                                 | . 36          |

|              | 3.3                                     | Flow 7  | Fable Controller                                                                | . 39          |

|              |                                         | 3.3.1   | Flow table controller module $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 39          |

|              |                                         | 3.3.2   | Signals                                                                         | . 41          |

|              |                                         | 3.3.3   | Simulation test                                                                 | . 43          |

|              | 3.4                                     | Action  | Processor                                                                       | . 46          |

|              |                                         | 3.4.1   | Action processor module                                                         | . 46          |

|              |                                         | 3.4.2   | Signals                                                                         | . 48          |

|              |                                         | 3.4.3   | Simulation test                                                                 | . 49          |

|              | 3.5                                     | Contro  | oller Policy                                                                    | . 49          |

|              |                                         | 3.5.1   | Controller policy module                                                        | . 50          |

|              |                                         | 3.5.2   | Signals                                                                         | . 51          |

|              |                                         | 3.5.3   | Simulation test                                                                 | . 52          |

| 4            | Perf                                    | formar  | ace Simulation                                                                  | <b>53</b>     |

| -            | 4.1                                     |         | rces utilization                                                                |               |

|              | 4.2                                     |         | e time and Sojourn time                                                         |               |

|              |                                         |         |                                                                                 |               |

| 5            | Con                                     | clusio  | ns and Future Work                                                              | <b>59</b>     |

| Re           | efere                                   | nces    |                                                                                 | 61            |

| AĮ           | open                                    | dices   |                                                                                 |               |

| Α            | Ope                                     | enFlow  | Switch Top Level Module                                                         | i             |

| в            | Pre-                                    | -proces | ssor Module                                                                     | ix            |

| С            | Hea                                     | der Pa  | arser Block                                                                     | xvii          |

|              |                                         |         | !                                                                               |               |

| D            | D Lookup Entry Composer Block xxix      |         |                                                                                 | XXIX          |

| $\mathbf{E}$ | E Flow Table Controller Top Module xxxv |         |                                                                                 | xxxv          |

| F            | F Flow Table Lookup Block xxxix         |         | xxxix                                                                           |               |

| $\mathbf{G}$ | Con                                     | troller | Policy Module                                                                   | $\mathbf{lv}$ |

| н            | Pac                                     | ket Fo  | rwarding Module                                                                 | lvii          |

|              | - 40                                    |         |                                                                                 |               |

### List of Figures

| 0.1  |                                              | 17 |

|------|----------------------------------------------|----|

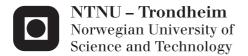

| 2.1  | OpenFlow Switch [3]                          | 7  |

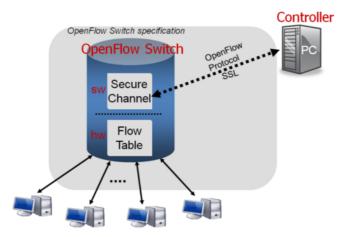

| 2.2  | OpenFlow Reactive Module [4]                 | 9  |

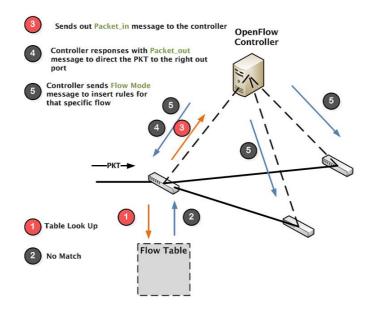

| 2.3  | OpenFlow Proactive Module [4]                | 9  |

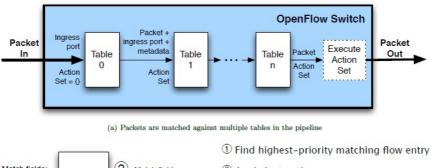

| 2.4  | Pipeline processing $[3]$                    | 12 |

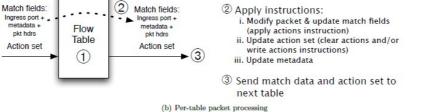

| 2.5  | FPGA-based platform [5]                      | 16 |

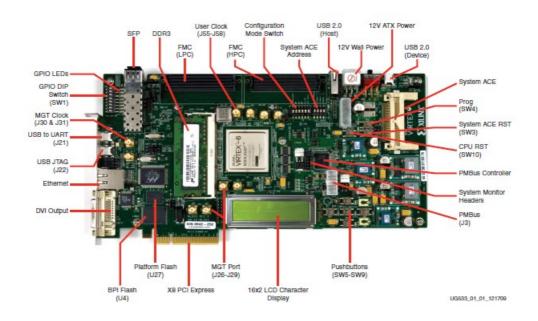

| 2.6  | Xilinx Virtex 6 block digram [6]             | 17 |

| 2.7  | FPGA plugged in PC                           | 18 |

| 3.1  | OpenFlow System Architecture                 | 21 |

| 3.2  | Output Port Lookup                           | 22 |

| 3.3  | Flow Table Entry Composer                    | 24 |

| 3.4  | Ethernet Packet                              | 26 |

| 3.5  | L2 parser state machine                      | 26 |

| 3.6  | IP header                                    | 27 |

| 3.7  | ICMP header                                  | 27 |

| 3.8  | TCP header                                   | 28 |

| 3.9  | UDP header                                   | 28 |

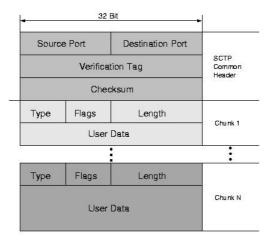

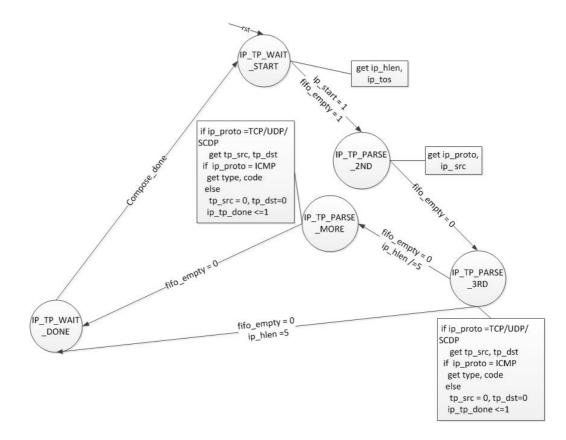

| 3.10 | SCTP header                                  | 28 |

| 3.11 | L3/L4 (IPv4) parser state machine            | 29 |

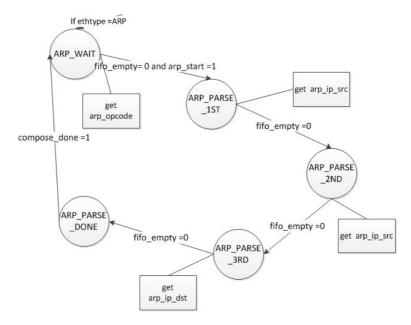

|      | ARP header                                   | 30 |

|      | ARP parser state machine                     | 30 |

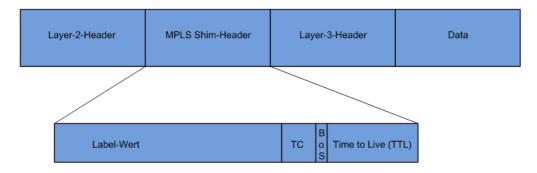

|      | MPLS header                                  | 31 |

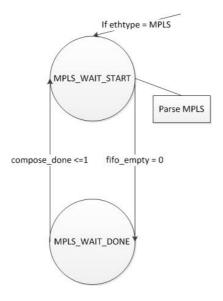

|      | MPLS parser state machine                    | 31 |

|      | Lookup entry composer                        | 32 |

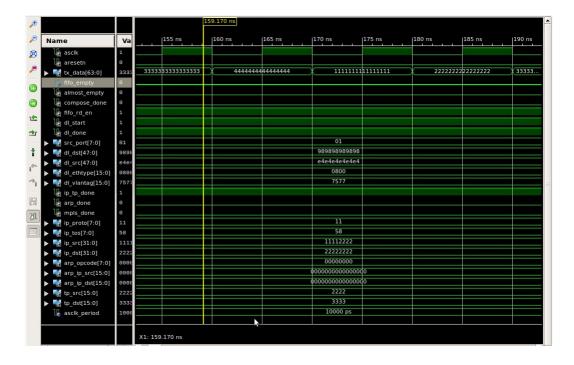

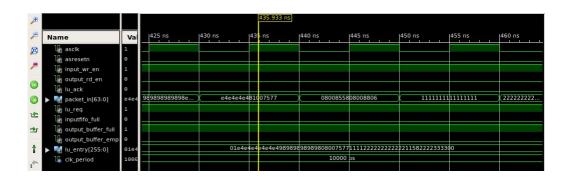

|      | Header parser simulation test result         | 36 |

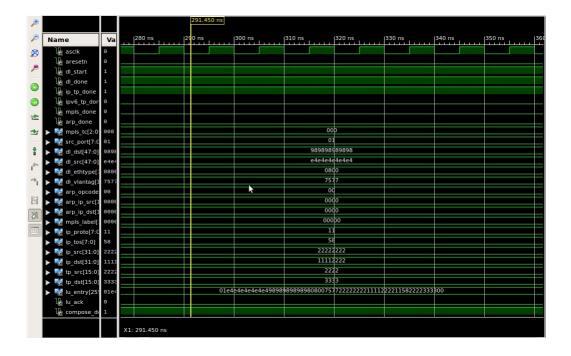

| 3.18 | Lookup entry composer simulation test result | 37 |

|      | Flow entry composer simulation test result   | 37 |

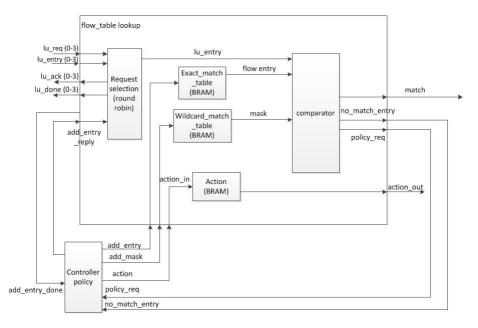

|      | Flow table controller module                 | 39 |

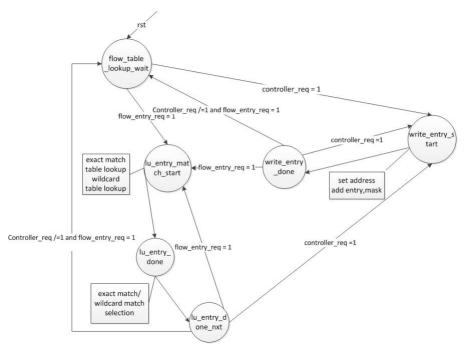

|      | Flow table controller state machine          | 40 |

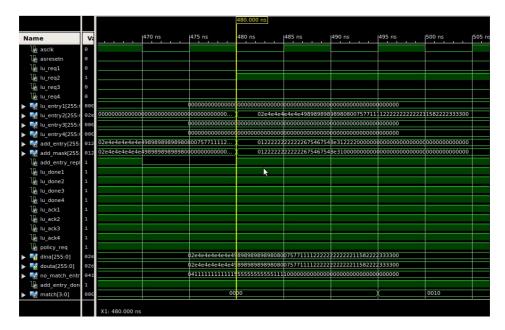

|      | Flow table lookup simulation test results    | 45 |

|      | Writing flow entry simulation test results   | 45 |

|      | Action processor                             | 46 |

| 3.25 | Action processor simulation test results | 49 |

|------|------------------------------------------|----|

| 3.26 | Controller policy module                 | 50 |

| 3.27 | Policy state machine                     | 50 |

| 3.28 | Controller policy simulation test result | 52 |

|      |                                          |    |

|      |                                          |    |

| 4.1  | Switch service time                      | 56 |

|      | Switch service time                      |    |

| 4.2  |                                          | 57 |

### List of Tables

| 2.1  | The top 5 Controllers available today and the main features        | 8  |

|------|--------------------------------------------------------------------|----|

| 2.2  | Symmetric messages                                                 | 10 |

| 2.3  | Asynchronous messages                                              | 11 |

| 2.4  | Controller-to-switch messages                                      | 11 |

| 2.5  | Main match fields                                                  | 12 |

| 2.6  | Main match fields description                                      | 13 |

| 2.7  | Main match fields lengths                                          | 14 |

| 2.8  | OpenFlow actions description                                       | 14 |

| 2.9  | Set-field action                                                   | 15 |

| 2.10 | XC6VLX240T main features                                           | 17 |

| 3.1  | Match fields                                                       | 25 |

| 3.2  | Ethernet type                                                      | 27 |

| 3.3  | IP protocol type                                                   | 27 |

| 3.4  | Flow tables and action lists size storage                          | 40 |

| 3.5  | The 'match' value description                                      | 44 |

| 3.6  | Action                                                             | 47 |

| 3.7  | Action flag                                                        | 47 |

| 4 1  | Desim supersonu (non onto                                          | 53 |

| 4.1  | Design summary/reports                                             |    |

| 4.2  | Comparison of OpenFlow switch implementations on three FPGA boards | 54 |

| 4.3  | Performance simulation results                                     | 55 |

### List of Algorithms

| 3.1 | Ethernet fields (no L3/L4 fields), program in VHDL   | 33 |

|-----|------------------------------------------------------|----|

| 3.2 | ARP Ethernet type, program in VHDL                   | 33 |

| 3.3 | MPLS Ethernet type, program in VHDL                  | 34 |

| 3.4 | IPv4 Ethernet type, program in VHDL                  | 34 |

| 3.5 | Header parser testbench, program in VHDL             | 38 |

| 3.6 | Flow table lookup testbench example, program in VHDL | 43 |

## Chapter – Introduction

#### 1.1 Background and Motivation

Network infrastructure has become critical in the Internet and enterprise network. However, with the explosion of mobile devices and the rise of cloud services but with limited available bandwidth, network architecture has become complex which results in that current network capacity can not match users' requirements. Networking technologies exert limitations such as complexity, inconsistent policies, inability to scale and vendor dependence, which can't satisfy high requirements of network architecture in enterprises, homes and schools [7]. At the same time, changing traffic patterns, "IT consumerization", the rise of cloud services and bandwidth limitation trigger the need of new network architecture [7]. Moreover, some network vendors are unhappy that researchers run experiments or test new protocols in their Internet environment, because it may lower or interrupt production traffic. Thus, the network innovation is needed to satisfy more users' requirements and also to optimize the current network.

Recently, Software-Defined Networking (SDN) created by Open Networking Foundation (ONF) attracted many academic researchers and vendors. ONF, a non-profit organization, is responsible to control and publish the different OpenFlow specifications and gives the trademark license "OpenFlow Switching" to companies that adopt this standard. OpenFlow is a new technology based on the SDN concept where is the switch that decides the actions that have to do. OpenFlow technology separates the control plane from the data path and this allows network managers to develop their own algorithms to control data flows and packets, resulting in more efficient network management, more flexibility in response to demands and faster innovation [7]. Furthermore, it implements the control logic on an external controller (typically an external PC) and this controller is responsible for deciding the actions that the switch must perform. The communication between the controller and the data path is made on the network itself, using the protocol that provides OpenFlow (OpenFlow

#### 2 1. INTRODUCTION

Protocol) via Secure Socket Layer (SSL) [7]. Now the researchers are not required to wait for new features to be released from equipment vendors and they can develop intelligent new services rapidly and independently in multiple-vendor environment [8]. Thus, OpenFlow has gained popularity with both academic researchers and industry as a framework for both network research and implementation, due to its advantages (decouple data and controller path, and routing intelligence).

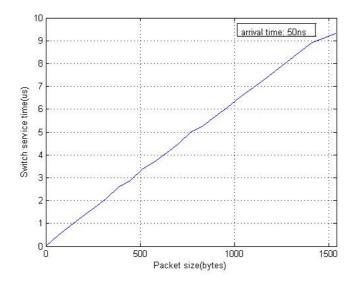

Actually, OpenFlow switch has already been implemented on several different platforms (Linux, OpenWRT and NetFPGA). There are many studies about the OpenFlow switch implementation on FPGA-based platform. Because FPGA-based switches are open-source hardware, which are faster than software-based switch. Besides, FPGA hardware is reprogrammable so that researchers can develop their own OpenFlow switches. And OpenFlow switch prototypes on FPGA-based platform can forward packets at 1-10Gbps. Thus, More and more people care about the OpenFlow switch implementation on FPGA-based platform and try to improve the OpenFlow switch. However, only a few works on the performance analysis of the OpenFlow switch are done. The implementation of OpenFlow Switch on NetFPGA has high latency to insert a new flow into OpenFlow Switch, which is still bottleneck [1]. However, the implementation of distributed multimedia plays (DMP) network nodes indicates lower latency and scalability features on FPGA based platform [2]. Therefore, this project is motivated to implement simulation model of OpenFlow system (data plane and control plane) on FPGA-based platform and also measure the performance metrics of the OpenFlow switch. However, our switch is designed only for research, not for the market. It is observed from the results that the service time and the sojourn time both have almost linear increase with the increase in payload size. Moreover, the results indicate that the switch takes only 2 clock cycles to respond to the writing request of the controller, which decreases the communication time between the switch and the controller.

#### 1.2 Problem Statement

Current network architecture is static and non-programmable. Recently, SDN is appealed to make network programmable. OpenFlow is a typical protocol for SDN, which has gained attention because of its flexibility in managing networks. Many OpenFlow switch implementations have already been done on different platforms, but few works of performance analysis are available. Thus, this project is meant to implement both data plane and control plane on FPGA in order to do the performance simulation.

#### 1.3 Objectives

The main objective of this project has two sides. On one hand, it is to implement OpenFlow Switch (data plane and control plane) using hardware language on FPGAbased platform. The OpenFlow specification v1.1 [3] is implemented in our switch. More specifically, the OpenFlow switch and controller are both implemented on FPGA due to lack of enough Ethernet ports and PCIe communication problem. On the other hand, the performance metrics of the OpenFlow switch are measured, especially the service time (switch and controller) and the sojourn time.

#### 1.4 Methodology

It is implemented on hardware using Xilinx Virtex6 which is plugged into a Linux PC. Additionally, it is designed in VHDL language using ISE design tool. More specifically, flow table entry composer module, flow table controller, action processor, controller policy are implemented on FPGA. Besides, the analysis of the performance metrics is done from the data obtained from the hardware. In order to measure metrics, the method used is to generate packets with different sizes.

#### 1.5 Outline

In Chapter 2, the theoretical background (e.g, SDN, OpenFlow Switch, OpenFlow controller, FPGA-based platform) is introduced in details and previous related works are described briefly. Chapter 3 depicts the details of the OpenFlow switch components (i.e, flow table entry composer module, flow table controller module, action processor module) and the controller (controller policy module). Chapter 4 is dedicated to show the results of performance simulation and comparison of resource utilization with other OpenFlow switches implemented on other platforms . Chapter 5 gives a conclusion, and highlights limitations and suggestions for future research.

Chapter 6

### Theoretical Background and Related Work

In this chapter, related theoretical concepts such as software-defined networking (SDN), OpenFlow switch, OpenFlow controller and FPGA-based platform are described in details. It also gives the overview of previous related works.

#### 2.1 Software-defined Networking (SDN)

Current network architecture is static and non-programmable. Network designers can not add new services into current network architecture arbitrarily because of the limitation of networking technologies (e.g., complexity, inconsistent policies, inability to scale and vendor dependence) [7]. Vendor dependence is the main reason of creating Software-Defined Networking (SDN). Recently, SDN has become popular in both academia and industry. Because of it, researchers and developers develop a new service or a new protocol without waiting many years for new features to be released from equipment vendors. More details of SDN can be found in [7].

SDN, created by non-profit ONF (open networking foundation) solved the problem, resulting in more efficient network management, more flexibility in response to demands and faster innovation. SDN in [7] is defined as "an emerging network architecture where network control is decoupled from forwarding and is directly programmable". The main characteristics of SDN include

- Control and data planes are decoupled and abstracted from each other

- Intelligence is logically centralized, resulting in having a global view of network and changing demands

- Underlying network infrastructure abstracted from applications, which makes it possible to develop different applications

- Programmable data plane brings automation and flexibility to networks

#### 6 2. THEORETICAL BACKGROUND AND RELATED WORK

• Faster innovation [9]

Besides, SDN simplifies the network design and operations. For example, researchers and network vendors can program the network without disrupting production traffic and also develop new services rapidly and independently. Moreover, the flexibility of SDN allows network managers to configure, manage, secure, and optimize network resources automatically [7]. With SDN, the static network can evolve into an extensible service delivery platform capable of responding rapidly to changing business, end-user, and market needs. Thus, a variety of networking devices and software currently have adapted OpenFlow-based SDN which delivers substantial benefits to both enterprises and carriers, including

- Centralized management and control

- Improved automation and management

- Rapid innovation

- Programmability

- Increased network reliability and security

- More granular network control

- Better end-user experience [7].

#### 2.2 Advantages of OpenFlow-based SDN

In [10], many advantages of SDN for network administrators are indicated. Firstly, network administrations expand SDN to the network, so network resources can be shared safely by multiple groups of users [10]. Secondly, through SDN, administrators can easily maintain entire virtual networks with their associated compute and storage resources even when VMs are migrated to different hosts [10]. Thirdly, with SDN, administrators can implement load-balancing with an OpenFlow switch and a commodity server [10]. This high cost-effective solution lets administrators better control traffic flow throughout the network to improve network performance. In addition, because administrators strive to expand the benefits of server and storage virtualization to the network, they are limited by the physical network infrastructure itself. However, a virtualized OpenFlow network removes these limitations, allowing administrators to create a flow-based virtual network abstraction that expands the benefits of virtualization to the network level.

#### 2.3 **OpenFlow Architecture**

Figure 2.1: OpenFlow Switch [3]

OpenFlow, as the first standard interface for SDN, has gained popularity within both academia and industry as a framework for both network research and implementation. It provides high-performance and granular traffic control across multiple vendors network devices. Flexibility is the key advantages of OpenFlow compared to existing protocols such as IP and Ethernet. Generally, using OpenFlow results in the following advantages: network virtualization and route distribution [11].

The communication procedure between OpenFlow switch and OpenFlow controller is described briefly here. The OpenFlow switch mainly consists of two flow tables (exact match table and wildcard table) and an interface for modifying flow table entries (e.g, adding, deleting) [3]. The OpenFlow controller decides the path of new packet (unmatched packet). Figure 2.1 describes the OpenFlow Switch briefly. The controller connects to OpenFlow switch via Secure Socket Layer (SSL) and modifies flow table entries through interface. The communication procedure between them is easily understood. For example, unmatched packet is encapsulated and sent to the controller over SSL. Then controller examines it, updates flow table entries and sends it back to the switch. The next arriving packet belonging to the same flow is then forwarded through the switch without consulting the controller. Several vendors have already added OpenFlow to their features such as HP Labs, Cisco researchers, NEC etc. More information about the OpenFlow architecture is described in the OpenFlow Standard[3]. The OpenFlow switch and OpenFlow controller are introduced in detail continually in the following subsection.

#### 2.3.1 OpenFlow Controller

The controller is the main device, responsible for maintaining all of the network rules and distributing the appropriate instructions for the network devices. In other words, the OpenFlow controller is responsible for determining how to handle packets without valid flow entries, and it manages the switch flow table by adding and removing flow entries over the secure channel using the OpenFlow protocol. The controller essentially centralizes the network intelligence, while the network maintains a distributed forwarding plane through OpenFlow switches and routers. For this reason the controller provides an interface to manage, control and administrate the switch's flow tables. Because the network control plane is implemented in software, rather than the firmware of hardware devices, network traffic can be managed more dynamically and at a much more granular level [4]. The controller is able to program a switch through reactive behaviour and proactive behaviour, shown in Figure 2.2 and Figure 2.3. The reactive behaviour takes advantage of the flow table efficiently. In other words, the first packet of flow triggers controller to insert flow entries and the switch limits the utility if control connection lost [12]. While proactive behaviour means that the controller pre-populates flow table in switch and loss of control connection does not disrupt traffic [12]. More information about the OpenFlow controller can be found in the OpenFlow Standard [3]. There are different controller implementations available today, shown in the following Table 2.1.

| Controllers                                                        | Main characteristic                                    |  |

|--------------------------------------------------------------------|--------------------------------------------------------|--|

| Beacon                                                             | A fast, cross-platform, modular, Java-based controller |  |

| Deacon                                                             | supporting both event-based and threaded operation     |  |

| NOX Open-source, a simplified platform written in C++ or Pythor    |                                                        |  |

| Trema                                                              | Full-Stack OpenFlow Framework for Ruby/C               |  |

| Maestro scalable, written in Java which supports OpenFlow switches |                                                        |  |

| SNAC using a web-based policy manager to manage the network        |                                                        |  |

Table 2.1: The top 5 Controllers available today and the main features

Figure 2.2: OpenFlow Reactive Module [4]

Figure 2.3: OpenFlow Proactive Module [4]

#### 2.3.2 OpenFlow Switch

The theory of OpenFlow switch is introduced briefly here. As shown in Figure 2.1, OpenFlow switch mainly consists of three parts: OpenFlow table, OpenFlow secure channel and OpenFlow protocol [3]. Packets are forwarded based on flow tables and controller can modify these flow tables via secure channel using OpenFlow protocol. The flow tables consist of a set of flow entries and each flow entry is associated with actions [3]. When OpenFlow switch receives a packet, it looks up the flow table (comparing received packet header with entries of the flow tables). If the packet header matches the flow table, associated actions are executed. According to the OpenFlow specification [3], actions include packet forwarding, packet modification and addition, removing packet header, dropping packet etc. On the other hand, if the packet doesn't match, it is transmitted to controller and the controller builds a new flow table. More information about the OpenFlow switch is explained in the OpenFlow Standard [3]. The details of OpenFlow components are described in the following section.

#### 2.4 Components of OpenFlow Switch

This section explains three components of OpenFlow Switch: OpenFlow protocol, OpenFlow flow tables and OpenFlow channel.

#### 2.4.1 OpenFlow protocol

Three message types are defined in the OpenFlow protocol: *controller-to-switch*, *asynchronous* and *symmetric* [3]. Symmetric messages (see Table 2.2) are used to keep connection between the controller and the switch. Asynchronous messages (see Table 2.3) are sent from the switch to the controller to denote a packet arrival, switch state change, or error [3]. While controller-to-switch message (see Table 2.4) is sent from controller to switch. Controller can manage and modify the state of OpenFlow switch through those messages.

| Symmetric messages | Description                                              |

|--------------------|----------------------------------------------------------|

| Hello              | Exchanged upon connection startup                        |

| Echo               | Request/reply messages from the switch or the controller |

| ECHO               | Measures the latency or bandwidth of a connection        |

| Experimenter       | Offer additional functionality                           |

Table 2.2:

Symmetric messages

| Asynchronous messages | Description                                        |

|-----------------------|----------------------------------------------------|

| Packet-in             | Sent to the controller for unmatched packets       |

| Flow-Removed          | Remove as an idle timeout or a hard timeout occurs |

| Port-status           | Send to the controller as port state changes       |

| Error                 | Notify the controller of problems                  |

Table 2.3:

Asynchronous messages

Table 2.4:

Controller-to-switch messages

| Controller-to-switch messages | Description                              |

|-------------------------------|------------------------------------------|

| Features                      | Query capabilities of a switch           |

| Configurations                | Set and Query configuration parameters   |

| Modify-State                  | Add/delete and modify flows/groups table |

|                               | Set switch port properties               |

| Read-State                    | Collect statistics                       |

| Packet-out                    | Send packets out of a specified port     |

|                               | Forward packets received via Packet-in   |

| Barrier                       | Ensure message dependencies              |

#### 2.4.2 OpenFlow flow tables

This subsection introduces components of OpenFlow tables, along with the mechanics of matching and action handling. OpenFlow switch has two flow tables: exact match table and wildcard match table. Each flow table includes many flow entries. Main components of a flow entry in a flow table include the match fields (matching against packets), counters (updating for matching packets) and instructions (modifying action set) [3]. Packet flow through the pipeline processing is shown in Figure 2.4. The incoming packet is looked up orderly through each flow table. If the packet matches a flow entry, pipeline processing stops and the corresponding action is executed. If the packet does not match, the default is to send the packet to the controller. In our design, two match fields associated with actions are designed (exact match table and wild card table), which is described further in Chapter 3.

Figure 2.4: Pipeline processing [3]

| Fields                               | When applicable                       |

|--------------------------------------|---------------------------------------|

| Ingress port                         | All packets                           |

| Metadata                             | All packets                           |

| Ethernet source address              | All packets on enabled ports          |

| Ethernet destination address         | All packets on enabled ports          |

| Ethernet type                        | All packets on enabled ports          |

| VLAN id                              | packets with VLAN tags                |

| VlAN priority                        | packets with VLAN tags                |

| MPLS label                           | packets with MPLS tags                |

| MPLS traffic class                   | packets with MPLS tags                |

| IPv4 source address                  | IPv4 and ARP packets                  |

| IPv4 destination address             | IPv4 and ARP packets                  |

| IPv4 protocol/ARP opcode             | IPv4, IPv4 over Ethernet, ARP packets |

| IPv4 ToS bits                        | IPv4 packets                          |

| Transport source port/ICMP Type      | TCP, UDP,SCTP, and ICMP packets       |

| Transport destination port/ICMP Code | TCP, UDP,SCTP, and ICMP packets       |

| Table 2.5: Main m | natch fields |

|-------------------|--------------|

| Table 2.5: Main n | laten neids  |

As for match fields, it is used to lookup the flow table depending on the packet type. Each entry in flow table contains a specific value. Table 2.5, Table 2.6 and Table 2.7 list the contents of the required match fields and details on the properties of each field of the OpenFlow specification v1.1 [3]. It can be seen from those tables that each header field has fixed size and is placed in the specific position of the match field. Flow table design procedure is explained further in Chapter 3.

| Fields                               | When applicable                           |  |  |

|--------------------------------------|-------------------------------------------|--|--|

| Ingress port                         | a physical or switch-defined virtual port |  |  |

| Metadata                             |                                           |  |  |

| Ethernet source address              | Can use arbitrary bitmask                 |  |  |

| Ethernet destination address         | Can use arbitrary bitmask                 |  |  |

| Ethernet type                        | after VLAN tags                           |  |  |

| VLAN id                              | VLAN identifier                           |  |  |

| VlAN priority                        | VLAN PCP field                            |  |  |

| MPLS label                           | MPLS tags                                 |  |  |

| MPLS traffic class                   | MPLS tags                                 |  |  |

| IPv4 source address                  | subnet mask or arbitrary bitmask          |  |  |

| IPv4 destination address             | subnet mask or arbitrary bitmask          |  |  |

| IPv4 protocol/ARP opcode             | ARP opcode (lower 8 bits)                 |  |  |

| IPv4 ToS bits                        | upper 6 bits                              |  |  |

| Transport source port/ICMP Type      | ICMP Type(lower 8 bits)                   |  |  |

| Transport destination port/ICMP Code | ICMP Type(lower 8 bits)                   |  |  |

Table 2.6:

Main match fields description

As for instructions, it mainly consists of action set which is associated with each packet. Supported instructions include **Apply-Actions**, **Clear-Actions**, **Write-Actions**, **Write-Metadata** and **Goto-Table** [3]. The action list (see Table 2.8) is included in the *Apply-Actions* as well as in the *Packet-out* message. The matched packets are forwarded and also modified according to the action list. After matching, the header field shown in Table 2.9 is required to be updated in the packets. However, only *Output* action is implemented in our OpenFlow switch. More details of forwarding action are introduced in Chapter 3.

| Fields                               | Bits |

|--------------------------------------|------|

| Ingress port                         | 32   |

| Metadata                             | 64   |

| Ethernet source address              | 48   |

| Ethernet destination address         | 48   |

| Ethernet type                        | 16   |

| VLAN id                              | 12   |

| VlAN priority                        | 3    |

| MPLS label                           | 20   |

| MPLS traffic class                   | 3    |

| IPv4 source address                  | 32   |

| IPv4 destination address             | 32   |

| IPv4 protocol/ARP opcode             | 8    |

| IPv4 ToS bits                        | 6    |

| Transport source port/ICMP Type      | 16   |

| Transport destination port/ICMP Code | 16   |

Table 2.7:

Main match fields lengths

Table 2.8:

OpenFlow actions description

| Actions                     | Description                                    |  |  |

|-----------------------------|------------------------------------------------|--|--|

| Output (Required)           | Forwards to a specific port                    |  |  |

| Set-Queue (Optional)        | Sets queue id                                  |  |  |

| Drop (Required)             | Drop packets with no output actions            |  |  |

| Group (Required)            | Process the packet through the specified group |  |  |

| Push-Tag/Pop-Tag (Optional) | Push and pop VLAN, MPLS, PBB tags              |  |  |

| Set-Field (optional)        | Modify the values of the packet header field   |  |  |

| Set-field ActionsSet Ethernet source MAC addressSet Ethernet destination MAC addressSet Ethernet destination MAC addressSet VLAN IDSet VLAN prioritySet VLAN prioritySet MPLS labelSet MPLS traffic classSet MPLS TTLDecrement MPLS TTLSet IPv4 source addressSet IPv4 destination addressSet IPv4 TTLSet transport source portSet transport destination port |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Set Ethernet destination MAC address<br>Set VLAN ID<br>Set VLAN priority<br>Set VLAN priority<br>Set MPLS label<br>Set MPLS traffic class<br>Set MPLS TTL<br>Decrement MPLS TTL<br>Set IPv4 source address<br>Set IPv4 destination address<br>Set IPv4 destination address<br>Set IPv4 ToS bits<br>Set IPv4 ToS bits<br>Set IPv4 ECN bits<br>Set IPv4 TTL<br>Decrement IPv4 TTL<br>Set transport source port                          | Set-field Actions                    |

| Set VLAN ID<br>Set VLAN priority<br>Set MPLS label<br>Set MPLS traffic class<br>Set MPLS TTL<br>Decrement MPLS TTL<br>Set IPv4 source address<br>Set IPv4 destination address<br>Set IPv4 destination address<br>Set IPv4 ToS bits<br>Set IPv4 ECN bits<br>Set IPv4 ECN bits<br>Set IPv4 TTL<br>Decrement IPv4 TTL                                                                                                                    | Set Ethernet source MAC address      |

| Set VLAN prioritySet MPLS labelSet MPLS traffic classSet MPLS TTLDecrement MPLS TTLSet IPv4 source addressSet IPv4 destination addressSet IPv4 destination addressSet IPv4 ToS bitsSet IPv4 ECN bitsSet IPv4 TTLDecrement IPv4 TTLSet transport source port                                                                                                                                                                           | Set Ethernet destination MAC address |

| Set MPLS label<br>Set MPLS traffic class<br>Set MPLS TTL<br>Decrement MPLS TTL<br>Set IPv4 source address<br>Set IPv4 destination address<br>Set IPv4 ToS bits<br>Set IPv4 ToS bits<br>Set IPv4 ECN bits<br>Set IPv4 TTL<br>Decrement IPv4 TTL<br>Set transport source port                                                                                                                                                           | Set VLAN ID                          |

| Set MPLS traffic class         Set MPLS TTL         Decrement MPLS TTL         Set IPv4 source address         Set IPv4 destination address         Set IPv4 ToS bits         Set IPv4 ECN bits         Set IPv4 TTL         Decrement IPv4 TTL         Set transport source port                                                                                                                                                     | Set VLAN priority                    |

| Set MPLS TTL         Decrement MPLS TTL         Set IPv4 source address         Set IPv4 destination address         Set IPv4 ToS bits         Set IPv4 ECN bits         Set IPv4 TTL         Decrement IPv4 TTL         Set transport source port                                                                                                                                                                                    | Set MPLS label                       |

| Decrement MPLS TTL         Set IPv4 source address         Set IPv4 destination address         Set IPv4 ToS bits         Set IPv4 ECN bits         Set IPv4 TTL         Decrement IPv4 TTL         Set transport source port                                                                                                                                                                                                         | Set MPLS traffic class               |

| Set IPv4 source addressSet IPv4 destination addressSet IPv4 ToS bitsSet IPv4 ECN bitsSet IPv4 TTLDecrement IPv4 TTLSet transport source port                                                                                                                                                                                                                                                                                          | Set MPLS TTL                         |

| Set IPv4 destination address         Set IPv4 ToS bits         Set IPv4 ECN bits         Set IPv4 TTL         Decrement IPv4 TTL         Set transport source port                                                                                                                                                                                                                                                                    | Decrement MPLS TTL                   |

| Set IPv4 ToS bits       Set IPv4 ECN bits       Set IPv4 TTL       Decrement IPv4 TTL       Set transport source port                                                                                                                                                                                                                                                                                                                 | Set IPv4 source address              |

| Set IPv4 ECN bits         Set IPv4 TTL         Decrement IPv4 TTL         Set transport source port                                                                                                                                                                                                                                                                                                                                   | Set IPv4 destination address         |

| Set IPv4 TTL<br>Decrement IPv4 TTL<br>Set transport source port                                                                                                                                                                                                                                                                                                                                                                       | Set IPv4 ToS bits                    |

| Decrement IPv4 TTL<br>Set transport source port                                                                                                                                                                                                                                                                                                                                                                                       | Set IPv4 ECN bits                    |

| Set transport source port                                                                                                                                                                                                                                                                                                                                                                                                             | Set IPv4 TTL                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                       | Decrement IPv4 TTL                   |

| Set transport destination port                                                                                                                                                                                                                                                                                                                                                                                                        | Set transport source port            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                       | Set transport destination port       |

| Copy TTL outwards                                                                                                                                                                                                                                                                                                                                                                                                                     | Copy TTL outwards                    |

| Copy TTL inwards                                                                                                                                                                                                                                                                                                                                                                                                                      | Copy TTL inwards                     |

Table 2.9: Set-field action

#### 2.4.3 OpenFlow Channel

OpenFlow switch connects to the controller through the OpenFlow channel. Through this interface, the controller can manage and modify the flow table. The OpenFlow channel may be run over TCP, and is usually encrypted [3]. Moreover, all OpenFlow channel messages between OpenFlow switch and controller must be formatted according to the OpenFlow protocol [3].

#### 2.5 FPGA-based platform

This section introduces a hardware architecture in NTNU. The board (XC6VLX240T device) used in our OpenFlow switch is Virtex-6 from Xilinx, which is also used in the implementation of distributed multimedia plays (DMP) network nodes, and it indicates lower latency and scalability features on FPGA based platform [2]. Figure

2.5 is the picture of ML605 and Figure 2.6 illustrates the block diagram of ML605. The Virtex-6 FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver integrated software and hardware components to enable designers to focus on innovation as soon as their development cycle begins, which provides the newest, most advanced features [13]. The main features of ML605 are shown in Table 2.10. It can be seen from Figure 2.6 that it has high speed interface (SFP), 200 MHz clock, compatible with 10/100/1000 Ethernet PHY (MII/GMII/RMII) and supports PCIe  $\times 8$  edge connector [6]. In addition to the high-performance logic fabric, Virtex-6 FPGAs contain many built-in system-level blocks. These features allow designers to build the highest levels of performance and functionality into FPGA-based systems. More features of the FPGA-platform are described in [13].

Figure 2.5: FPGA-based platform [5]

#### 2.5. FPGA-BASED PLATFORM 17

Figure 2.6: Xilinx Virtex 6 block digram [6]

| Logic cells | Configu | rable Logic Blocks | BRAM       | PCIe | PCIe Ethernet port | I/O |

|-------------|---------|--------------------|------------|------|--------------------|-----|

| Logic cens  | Slices  | DRAM (Kb)          | Max(Kb)    |      |                    |     |

| 241,152     | 37,680  | 3,650              | $14,\!976$ | 2    | 1                  | 720 |

Table 2.10:XC6VLX240T main features

In the current work, PC and FPGA are the two hardware sections. FPGA board is plugged into PC through PCI slots (see Figure 2.7). Our hardware platform only has one Ethernet port, which limits the OpenFlow switch implementation. However, the simulation model of OpenFlow switch is implemented on this FPGA-based paltform, which is to test the performance of OpenFlow switch. In our OpenFlow switch implementation, the design environment is as follows:

• ML605 board with XC6VLX240T FPGA

#### 18 2. THEORETICAL BACKGROUND AND RELATED WORK

- Intel Core i7 CPU 2.8 GHz 930 (4 core, 8 thread processor)

- Linux Ubuntu 10.04 LTS (2.6.32-41-generic)

- Motherboard: Gigabyte, X58A–UD7

- Xilinx ISE 14.7

Figure 2.7: FPGA plugged in PC

#### 2.6 Related Work

Many OpenFlow switches have already been implemented in different platforms such as Linux (software), OpenWRT (software) and NetFPGA (hardware). Hardware/commercial switches (e.g, HP ProCurve, NEC IP8800) and software/Test switches (NetFPGA switch, OpenWRT) have been released and used in real network

environments. Switches are open sources and can be found on the website so that everyone can download for using or modifying. This section briefly introduces some related work about current OpenFlow switch implementations.

[1] describes the Type-0 OpenFlow switch implementation on the NetFPGA platform. NetFPGA used in [1] is a Gigabit rate networking hardware, consisting of a PCI card with an FPGA, memory, and four 1-Gig Ethernet ports. This implementation could hold more than 32,000 exact-match flow entries running across four ports and the exact-match flow table can be expanded to more than 65000 entries. The implementation enhances flexibility and reusability of hardware. The performance results claim that it takes 11  $\mu$ s to insert a new flow into switch due to the PCI bus bottleneck [1]. At the same time, the bottleneck of their OpenFlow switch is that it has 240 bits flow header entry currently along with the actions, which can be aggravated when packet re-injected from controller into switch using the same communication channel (PCI bus). Additionally, OpenFlow switch can provide many functionalities at lower logic gate cost in comparison with IPv4 Router, the NIC and the learning Ethernet switch [1].

While another OpenFlow switch implemented on NetFPGA can hold more than 100000 flow entries and it is also capable of running at line-rate across the four NetFPGA ports [14]. In the software plane, OpenFlow reference software implementation is extended by using a new  $\delta$ FA data structure to create the rules instead of hash function, which is more advanced than the switch implemented on the NetFPGA. This switch provides a flexible packet forwarding architecture based on regular expression [14]. Besides, it also enables the standard-compliant OpenFlow switching, which can be easily reconfigured through its control plane to support other kinds of applications [14]. Furthermore, the performance analysis is also done in this article. The results of performance analysis indicate that the switch is able to process all traffic data even in the case of a Gigabit link saturated with minimum-sized packets [14].

Because low-level Verilog RTL severely limits the portability of OpenFlow switch, the switch in [15] is implemented with Bluespec System Verilog (BSV) which is a high-level HDL, and addresses the challenges of its flexibility and portability. The design comprises of approximately 2400 lines of BSV code. This switch meets the OpenFlow 1.0 specification and achieves a line rate of 10 Gbps, which is highly modular and parameterized, and makes use of latency-insensitivity, split-transaction interfaces and isolated platform-specific features [15]. In this article, the OpenFlow Switch is also ported into NetFPGA-10G, the ML605 (Xilinx) and DE4 (Altera). The exact match flow tables of this switch is implemented on both Block RAM and DRAM. It is found that it has lower pipeline latency of 19 cycles for a packet to go from ingress to egress when implementing exact flow tables on Block RAM

#### 20 2. THEORETICAL BACKGROUND AND RELATED WORK

[15]. Furthermore, the switch is implemented in two configurations, one is in an FPGA communication with controller via PCIe or the serial link, another is in an FPGA-based MIPS64 softcore. It is found that the switch responds to controller requests in less cycles used with the PCIe than serial link [15].

The related works about OpenFlow switch implementation have already mentioned above and most of OpenFlow switches are implemented on the NetFPGA. Except these related works, there is limited number of studies on performance analysis of the OpenFlow switch.

In order to improve the OpenFlow switching performance, the mechanisms are introduced in [16] and [17]. An architectural design is proposed to improve the lookup performance of OpenFlow switching in Linux by using a standard commodity network interface card. The results in [16] show a packet switching throughput increase of up to 25 percent compared to the throughput of regular software-based OpenFlow switching [16]. Instead, the results in [17] show a 20 percent reduction using network processor based acceleration cards to perform OpenFlow switching [17]. However, only one paper studies the performance measures of OpenFlow [18]. It is concluded that the OpenFlow implementation in Linux systems can offer very good performance and it shows good fairness capability in dealing with multiple flows [18]. Furthermore, it is also found from the results that large forwarding tables are generated due to L2 switching [18]. [19] also studies the performance measurements of not only OpenFlow switch but also OpenFlow controller. In [19], a performance model of an OpenFlow system is provided, which is based on the results from queuing theory and is verified by simulations and measurement experiments with a real OpenFlow switch and controller. The results in this article show that the sojourn time mainly depends on the processing speed of the OpenFlow controller [19]. Moreover, it indicates that lower is the coefficient of variation when the probability of new flows arriving at the switch is higher, but longer is the sojourn time [19].

Thus, it can be seen from the description above that OpenFlow-SDN has already appealed to some attentions in both researchers and vendors. At the same time, the increasing number of researchers gradually has implemented their own OpenFlow switch on FPGA-based platform. The OpenFlow network implementation described in this thesis is a little different from the related work. Our work is to do the simulation test of OpenFlow performance so that data plane and control plane are both implemented on FPGA (Virtex6). OpenFlow switch design framework is explained in details in the following chapter.

# Chapter OpenFlow Switch Design Framework

As it is mentioned in the previous chapter, the OpenFlow network architecture includes the OpenFlow switch, the OpenFlow controller and a secure channel based on the OpenFlow protocol which connects the OpenFlow switch to the OpenFlow controller. In this chapter, the main modules of OpenFlow switch designed on FPGA are described in detail, which are flow table entry composer, flow table controller, action processor and controller policy.

# 3.1 OpenFlow Switch Framework

# 3.1.1 Brief description

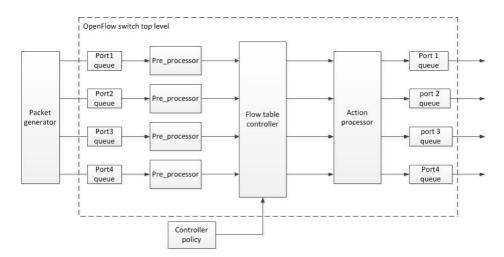

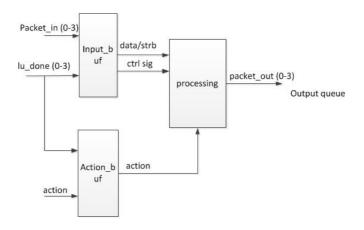

Figure 3.1: OpenFlow System Architecture

In our OpenFlow switch design, OpenFlow datapath receives the packets via packet generator. All peripherals share the same clocks (100MHz) and a reset. However, only the composed flow entry goes to the flow table controller module. 64bit pipelines are beneficial for executing many tasks per clock and also for successful FPGA implementation. Since there is the only one Ethernet port, four datapath pipelines are designed to simulate more ports with using input queue and output queue as a switching facility in the top level module. Incoming packets from each physical input port go through dedicated pipeline. Figure 3.1 illustrates the OpenFlow system architecture and the brief framework of the OpenFlow switch design. The packets are generated, and have to stay in the output queue after being processed due to only one Ethernet port. The main three parts of OpenFlow architecture are the input queue module, the output port lookup module and the output queue module. The input queue and the output queue both consist of generic modules generated by two IP cores (FIFO generator [20] and Block RAM [21]) supported by Xilinx design tools (ISE 14.7 [22]). Each input queue connects to each port and buffers the received packets. And the sizes of both the FIFO queue block and buffer block are  $64 \text{ (width)} \times 1024 \text{ (depth)}$ . The output port lookup module, clearly shown in Figure 3.2, is the most important part in the OpenFlow switch design framework, mainly consisting of flow table entry composer, flow table controller and action processor.

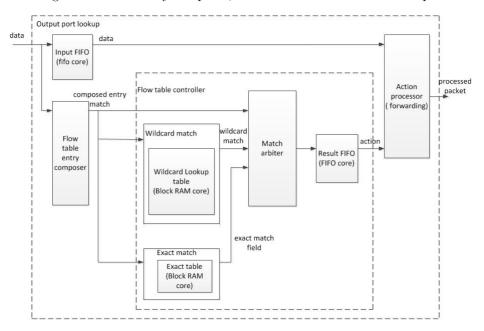

Figure 3.2: Output Port Lookup

When new packets generated from the packet generator stream into the OpenFlow

switch, important header information is extracted and then composed into fixed format which is compared with the flow table entries in two flow tables (exact match table and wildcard table). At the same time, incoming packets are buffered in the input FIFO buffer block, waiting for being forwarded. Then the matching results associated with forwarding action are sent to the action processor in order to tell the action processor how to deal with the packet (forwarding to the corresponding output queue). If the packet matches, it is forwarded to the corresponding output port according to the forwarding information in the action list. While if it doesn't match, the OpenFlow switch requests to the controller policy model to make decision of this unmatched packet. The policy of the controller policy module is to add flow entry information including the flow entry, the flow mask and the action. Here, both matched packets and unmatched packets are forwarded to the output queues finally. Output port lookup module and the policy module are depicted more in the following section.

# 3.2 Flow Table Entry Composer

After going through the FIFO queue, the packet initially goes to the flow table entry composer module. In this section, the implementation of flow table entry composer is described.

The purpose of the flow table entry composer is to extract packet headers and organizes them as a fixed form of the flow table entry. Figure 3.3 shows the process of the flow table entry composer module. It can be seen from Figure 3.3 that it is made up of the input FIFO queue block, header parser block, lookup entry composer block. Here, input FIFO queue block is also generated by IP cores (FIFO generator [20]). When a new flow comes in, the header fields are extracted. After being parsed, these extracted header information are composed into the flow entry with the fixed format in the lookup entry composer block. Then the composed flow entry is sent to flow table table modules for matching.

Figure 3.3: Flow Table Entry Composer

# 3.2.1 Queue block

Input FIFO queue block is a common block for OpenFlow switch architecture to reduce back pressure situation, also used in other modules. The FIFO block and output buffer block generated by FIFO generator IP cores [20] both buffer the incoming packets. The input FIFO block buffers incoming packets for parsing header. While the output buffer block buffers the incoming packets for action processor and also synchronous with parsed header. The buffer size  $(64 \times 1024)$  is sufficient to store data until finishing header parsing.

## 3.2.2 Header parser block

| Field                                | Bits |

|--------------------------------------|------|

| Match fields                         | 256  |

| Ingress port                         | 8    |

| Ethernet source address              | 48   |

| Ethernet destination address         | 48   |

| Ethernet type                        | 16   |

| VLAN id                              | 12   |

| VlAN priority                        | 3    |

| MPLS label                           | 20   |

| MPLS traffic class                   | 3    |

| IPv4 source address                  | 32   |

| IPv4 destination address             | 32   |

| IPv4 protocol/ARP opcode             | 8    |

| IPv4 ToS bits                        | 6    |

| IPv6 source address                  | 128  |

| IPv6 destination address             | 128  |

| Transport source port/ICMP Type      | 16   |

| Transport destination port/ICMP Code | 16   |

| Table | 3.1: | Match   | fields |

|-------|------|---------|--------|

| Table | O.T. | materia | noius  |

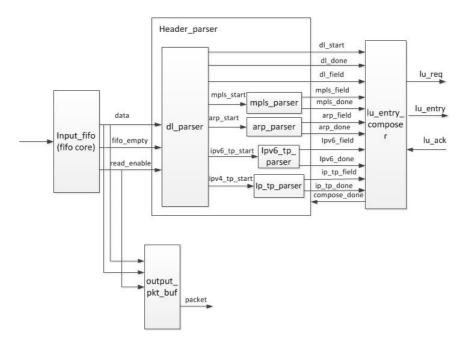

Header parser module extracts L2 header information (dl\_parser block) and also L3/L4 header information (ip\_tp\_parser block, ipv6\_tp\_parser block, arp\_parser, mpls-parser block). Each header field has the exact position in the packet. Thus, the important header fields can be extracted according to their exact positions in Ethernet frame. Table 3.1 shows the header fields that are extracted from the packet in our design according to the match fields described in OpenFlow specification v1.1 [3].

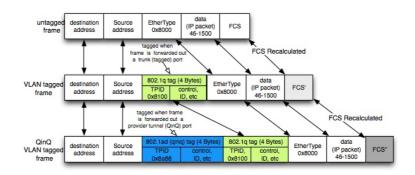

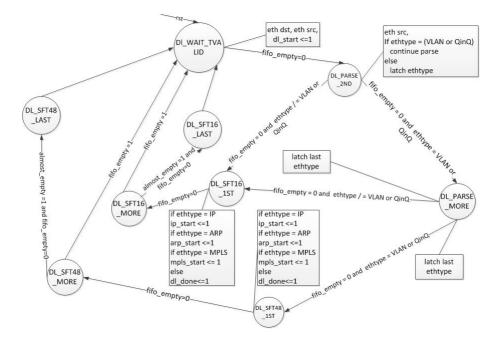

According to the Table 3.1, Ethernet source/destination address, VLAN ID, priority (if VLAN tag) and Ethernet type need to be extracted from L2 header. Figure 3.4 illustrates the structure of Ethernet frame with and without VLAN tag (0x8100) or QinQ tag (0x8a88). Figure 3.5 illustrates the process of getting L2 header fields. When the Ethernet packets (64 bits per clock) come in, Ethernet source/destination addresses are extracted firstly. At the same time, header parsing

signal is sent to lookup entry composer which waits for receiving the extracted fields. If VLAN tag is found in the packet, VLAN ID and VLAN priority are obtained from the packet. Different Ethernet types (see Table 3.2) are detected through if statements. If one of those types is found, the corresponding header fields are extracted further. Otherwise, header parser block stops to parse further.

Figure 3.4: Ethernet Packet

Figure 3.5: L2 parser state machine

| Ethernet type | IPv4   | ARP    | MPLS unicast | MPLS multicast |

|---------------|--------|--------|--------------|----------------|

| Content       | 0x0800 | 0x0806 | 0x8847       | 0x8848         |

Table 3.2:

Ethernet type

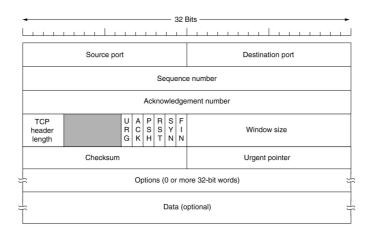

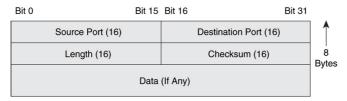

If Ethernet type is IPv4, ip\_tp\_parser starts to work. The structure of IP, ICMP, TCP/UDP and SCTP headers are described in Figure 3.6, Figure 3.7, Figure 3.8 and Figure 3.9 respectively. In L3, IP source/destination address, IPv4 protocol and IPv4 TOS need to be extracted from the IP header. Moreover, source/destination ports (TCP/UDP/SCTP) or ICMP type and ICMP code need to be extracted from L4 header. Figure 3.11 illustrates the procedure of ip\_tp\_parser. Besides, IP protocol type is also detected through if statements. If IP protocol is TCP, UDP, SCTP or ICMP (see Table 3.3), the packet is parsed further in order to extract the corresponding header fields. Otherwise, the match fields of L4 are put null.

Table 3.3:IP protocol type

| IP protocol type | TCP  | UDP  | SCTP | ICMP |

|------------------|------|------|------|------|

| Content          | 0x06 | 0x11 | 0x84 | 0x01 |

| Bits                |         |                 |                       |              |  |  |

|---------------------|---------|-----------------|-----------------------|--------------|--|--|

| 0                   | 4 8     | B 1             | 6 1                   | 9            |  |  |

| Version             | Length  | Type of Service |                       | Total Length |  |  |

|                     | Identif | ication         | Flags Fragment Offset |              |  |  |

| Time t              | o Live  | Protocol        | Header Checksum       |              |  |  |

|                     |         | Source A        | ddress                |              |  |  |

| Destination Address |         |                 |                       |              |  |  |

| Options             |         |                 |                       |              |  |  |

|                     |         | Data            | а                     |              |  |  |

Figure 3.6: IP header

| 0 |            | 8    | 16 :          | 32 |

|---|------------|------|---------------|----|

|   | Туре       | Code | ICMP checksum |    |

|   | Identifier |      | Sequence      |    |

|   |            | Subm | et mask       |    |

Figure 3.7: ICMP header

Figure 3.8: TCP header

No Sequence Or Acknowledgment Fields

Figure 3.9: UDP header

Figure 3.10: SCTP header

Figure 3.11: L3/L4 (IPv4) parser state machine

If Ethernet type is ARP, arp\_parser (Figure 3.13) starts to work. The ARP opcode, sender IP address and target IP address in the ARP header fields (Figure 3.12) are extracted.

| (                             |                               | BITS —                  | 0000                     |

|-------------------------------|-------------------------------|-------------------------|--------------------------|

| 8                             | 8                             | 8                       | 8                        |

| HARDW                         | ARE TYPE                      | PROTO                   | COL TYPE                 |

| HARDWARE<br>ADDRESS<br>LENGTH | PROTOCOL<br>ADDRESS<br>LENGTH | OPEF                    | RATION                   |

|                               | SENDER HARDW<br>(OCTET        |                         |                          |

|                               | WARE ADDRESS<br>TS 4-5)       |                         | P ADDRESS<br>ETS 0-1)    |

|                               | P ADDRESS<br>ETS 2-3)         |                         | WARE ADDRESS<br>ETS 0-1) |

|                               | TARGET HARDV<br>(OCTE         | VARE ADDRESS<br>TS 2-5) |                          |

|                               | TARGET IP                     | ADDRESS                 |                          |

Figure 3.12: ARP header

Figure 3.13: ARP parser state machine

It can be seen from Figure 3.14, MPLS label length is 20 bits and MPLS traffic

class is 3 bits in MPLS header fields. If Ethernet type is MPLS, mpls\_parser state machine (Figure 3.15) starts to extract MPLS label and MPLS traffic class.

Figure 3.14: MPLS header

Figure 3.15: MPLS parser state machine

# 3.2.3 Lookup entry composer

The lookup entry composer block is ready to compose when the header parser block begins to work (dl\_start  $\langle = '1' \rangle$ ). The lookup entry composer block organizes all the parsed fields received from the header parser block into a specific format. All extracted fields have their own specific position in the lookup entry (lu\_entry). This

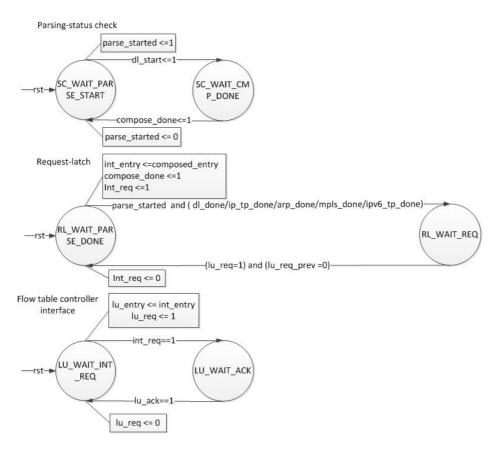

block consists of three state machines shown in Figure 3.16: parsing-status check, request-latch and flow-table module interface. Parsing-status checks state machine is to communicate with the preceding header parser block. Request-latch state machine is used to compose these extracted header fields into lookup entry format. Finally, flow table controller interface state machine is to transfer signals to the following flow table controller module.

Figure 3.16: Lookup entry composer

The content of the flow entry is different due to the different Ethernet types and IP protocol types. Each extracted field is put into the exact position in the flow entry. The structure of the flow entry these header fields defined in our design is shown in the following algorithms. It can be seen from these algorithms (see Algorithm 3.1, Algorithm 3.2, Algorithm 3.3 and Algorithm 3.4) that the extracted fields are put in the exact positions of the flow entry.

```

if (dl_done='1' and ip_tp_done='0' and arp_don ='0' and mpls_done='0')then

int_entry <= src_port</pre>

--input port

& dl_src

--Ethernet source address

& dl_dst

--Ethernet destination address

& dl ethtype

--Ethernet type

--Ethernet VLAN

& dl_vlantag

& X"00000000"

--IPv4 source address

& X"00000000"

-- IPv4 destination address

& X"00"

--IPv4 protocol type

& X"00"

--IPv4 TOS

& X"0000"

--transport layer source port

& X"0000"

--transport layer destination port

& X"00";

compose_done <= '1';</pre>

int_req_nxt := '1';

req_latch_state_nxt <= RL_WAIT_REQ;</pre>

```

Algorithm 3.1 Ethernet fields (no L3/L4 fields), program in VHDL.

Algorithm 3.2 ARP Ethernet type, program in VHDL.

```

elsif (dl_done = '1' and arp_done = '1') then

int_entry <= src_port</pre>

--input port

--Ethernet source address

& dl src

& dl_dst

--Ethernet destination address

& dl_ethtype --Ethernet type

& dl_vlantag --Ethernet VLAN

& arp_ip_src --ARP source address

& arp_ip_dst

--ARP destination address

--ARP operation code

& arp_opcode

& X"00"

--IPv4 TOS

--transport layer source port

& X"0000"

& X"0000"

--transport layer destination port

& X"000000000";

compose_done <= '1';</pre>

int_req_nxt := '1';

req_latch_state_nxt <= RL_WAIT_REQ;</pre>

```

```

Algorithm 3.3 MPLS Ethernet type, program in VHDL.

elsif (dl_done = '1' and mpls_done = '1') then

int_entry <= src_port</pre>

--input port

& dl_src

--Ethernet source address

& dl dst

--Ethernet destination address

& dl_ethtype --Ethernet type

& dl_vlantag --Ethernet VLAN

& mpls_lable --MPLS label

& mpls_tc

--MPLS traffic class

& X"00000000"

& X"00000000"

& X"0000"

& X"0000"

& B"0";

compose_done <= '1';</pre>

int_req_nxt := '1';

req_latch_state_nxt <= RL_WAIT_REQ;</pre>

```

| Algorithm 3.4 IPv4 Ethe    | rnet type, program  | n in VHDL.                       |

|----------------------------|---------------------|----------------------------------|

| elsif (dl_done             | = '1' and ip_t      | p_done = '1') then               |

| <pre>int_entry &lt;=</pre> | <pre>src_port</pre> | input port                       |

|                            | & dl_src            | Ethernet source address          |

|                            | & dl_dst            | Ethernet destination address     |

|                            | & dl_ethtype        | Ethernet type                    |

|                            | & dl_vlantag        | Ethernet VLAN                    |

|                            | & ip_src            | IPv4 source address              |

|                            | & ip_dst            | IPv4 destination address         |

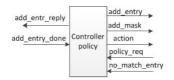

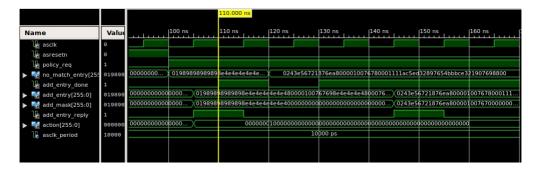

|                            | & ip_tos            | IPv4 TOS                         |