# **Fusion Network Performance**

An Integrated Packet/Circuit Hybrid Optical Network

# Edgar Gerardo Sanchez Gomez

Master in Security and Mobile ComputingSubmission date:June 2013Supervisor:Steinar Bjørnstad, ITEMCo-supervisor:Raimena Veisllari, ITEM

Norwegian University of Science and Technology Department of Telematics

#### NORWEGIAN UNIVERSITY OF SCIENCE AND TECHNOLOGY FACULTY OF INFORMATION TECHNOLOGY, MATHEMATICS AND ELECTRICAL ENGINEERING

### PROBLEM DESCRIPTION

| Project title:  | Fusion Network Performance: An Integrated<br>Packet/Circuit Hybrid Optical Network |

|-----------------|------------------------------------------------------------------------------------|

| Course:         | Master Thesis                                                                      |

| Student's name: | Edgar Gerardo Sánchez Gómez                                                        |

Problem description:

Applications and services such as online gaming, telemedicine and e-health, online banking, cloud computing, high-quality videoconferencing, etcetera are becoming more and more sensitive to timely delivery. Furthermore, traffic volumes in both fixed and mobile networks are expected to keep increasing exponentially over the next few years.

These services and traffic demand are dependent on minimal jitter and delay to run successfully, and they do not tolerate any data loss. And so they need a higher class of Quality of Service (QoS), like the one offered by circuit switching. However, in order to achieve a cost-efficient network with high throughput, packet switching technology is needed. How to achieve them both?

TransPacket is a startup-company that has implemented the novel fusion technology, also called OpMiGua integrated hybrid networks. The fusion concept has the main objective of combining the best properties from both circuit and packet switched networks into a hybrid solution.

It is the objective of this thesis work to perform a network experiment involving TransPacket H1 nodes measuring performance parameters like latency, latency variation (packet delay variation) and packet loss. The experiment shall be performed in the premises of NTNU but remote operation of experimental equipment is available.

| Deadline:        | June 30, 2013            |

|------------------|--------------------------|

| Submission date: | June 20, 2013            |

| Department:      | Department of Telematics |

| NTNU Supervisor: | Steinar Bjørnstad        |

| KTH Supervisor:  | Markus Hidell            |

# Abstract

IP traffic increase has resulted in a demand for greater capacity of the underlying Ethernet network. As a consequence, not only Internet Service Providers (ISPs) but also telecom operators have migrated their mobile back-haul networks from legacy SONET/SDH circuit-switched equipment to packet-based networks.

This inevitable shift brings higher throughput efficiency and lower costs; however, the guaranteed QoS and minimal delay and packet delay variation (PDV) that can only be offered by circuit-switched technologies such as SONET/SDH are still essential and are becoming more vital for transport and metro networks, as well as for mobile back-haul networks, as the range and demands of applications increase.

Fusion network offers "both an Ethernet wavelength transport and the ability to exploit vacant wavelength capacity using statistical multiplexing *without interfering* with the performance of the wavelength transport" [RVH] by dividing the traffic into two *service classes* while still using the capacity of the same wavelength in a *wavelength routed optical network* (WRON) [SBS06]:

- 1. A *Guaranteed Service Transport* (GST) service class supporting QoS demands such as no packet loss and fixed low delay for the circuit-switched traffic.

- 2. A *statistical multiplexing* (SM) service class offering high bandwidth efficiency for the best-effort packet-switched traffic.

Experimentation was carried out using two TransPacket's H1 nodes and the Spirent Test-Center as a packet generator/analyzer with the objective of demonstrating that the fusion technology, using TransPacket's H1 muxponders allow transporting GST traffic with circuit QoS; that is with no packet loss, no PDV and minimum delay independent of the insertion of statistically multiplexed traffic.

Results indicated that the GST traffic performance is completely independent of the added SM traffic and its load. GST was always given absolute priority and remained with a constant average end-to-end delay of 21.47  $\mu$ s, no packet loss and a minimum PDV of 50 ns while SM traffic load increased, increasing the overall 10GE lightpath utilization up to 99.5%.

# Acknowledgements

This report serves as a Master Thesis for the Master's Programme in Security and Mobile Computing at the Norwegian University of Science and Technology, NTNU and the Royal Institute of Technology, KTH. The assignment was given by TransPacket's CEO and NTNU professor Steinar Bjørnstad and the project was carried out remotely in room F251, inside the Electrical Engineering building within the Department of Telematics in the Gløshaugen campus of NTNU.

First of all, I would like to thank my supervisors Steinar Bjørnstad and Markus Hidell for their patience, their guidance, their feedback and their help throughout all this process. Furthermore, I would like to thank PhD student Raimena Veisllari for her constant help and availability. She was there to answer any question and doubt I ever had during experimentation, and she made sure to push me when I needed to be pushed. I would like to think that the quality of this thesis reflects not only on my hard work, but on the constant help from all of them.

I am also thankful to the NordSecMob Consortium and the Erasmus Mundus Commission, for without their financial support, all of this would not have happened. Thanks to May-Britt Eklund Larsson and Mona Nordaune for all of their administrative assistance and help to make sure this programme runs as smoothly as it does.

And of course, thank you to my family and friends, who have always believed in me and encouraged me every step of the way.

Trondheim, June 20, 2013

Edgar Gerardo Sánchez Gómez

# Abbreviations

**BP** Buffer Priority **CEO** Chief Executive in Office **CLI** Command Line Interface **CWDM** Coarse Wavelength Division Multiplexing **DEMUX** Demultiplexor **DVB** Digital Video Broadcast **DWDM** Dense Wavelength Division Multiplexing **D-WRON** Dynamic - Wavelength Routed Optical Network **EMS** Element Management System FDL Fiber Delay Line FDM Frequency-Division Multiplexing **GST** Guaranteed Service Transport **GUI** Graphical User Interface HCT High-Class Transport **IEEE** Institute of Electrical and Electronics Engineers **IETF** Internet Engineering Task Force **IP** Internet Protocol **IPTV** Internet Protocol Television **ISP** Internet Service Provider **IT** Information Technology **KTH** Royal Institute of Technology LTE Long Term Evolution MSc Master of Science MTU Maximum Transmission Unit

MUX Multiplexor

- NCT Normal Class Transport

- **NETCONF** Network Configuration Protocol

**NMS** Network Management System

- NTNU Norwegian University of Science and Technology

- **OBS** Optical Burst Switching

- **OEO** Optical-Electrical-Optical

- **OpMiGua** Optical Migration Capable Networks with Service Guarantees

- **OPS** Optical Packet Switching

- **ORION** Overspill Routing in Optical Networks

**OS** Operating System

**OTN** Optical Transport Network

- **OXC** Optical Cross Connect

- **PBS** Polarization Beam Splitter

**PDV** Packet Delay Variation

**PGA** Packet Generator/Analyzer

$\mathbf{PLR}$  Packet Loss Ratio

**PM** Polarization Maintaining Coupler

**QoS** Quality of Service

**RDC** Remote Network Connection

**RMON** Remote Network Monitoring

**RPC** Remote Procedure Call

SFP Small Form-factor Pluggable

**SLA** Service Level Agreement

$\mathbf{SM}$  Statistical Multiplexing

**SNMP** Simple Network Management Protocol

SONET/SDH Synchronous Optical Network / Synchronous Digital Hierarchy

**SSH** Secure Shell

S-WRON Static - Wavelength Routed Optical Network

**TDM** Time-Division Multiplexing

VLAN Virtual Local Area Network

VLP Variable Length Packet

WDM Wavelength Division Multiplexing

WRON Wavelength Routed Optical Network

XFP 10 Gigabit Small Form Factor Pluggable

XML Extensible Markup Language

# Contents

| A        | bstra | act                                                 | i        |

|----------|-------|-----------------------------------------------------|----------|

| A        | ckno  | wledgements                                         | iii      |

| A        | bbre  | viations                                            | iv       |

| 1        | Intr  | roduction                                           | 1        |

|          | 1.1   | Motivation                                          | 1        |

|          | 1.2   | Objective                                           | 2        |

|          | 1.3   | Scope                                               | 2        |

|          | 1.4   | Methodology                                         | 2        |

|          | 1.5   | Document Structure                                  | 3        |

| <b>2</b> | Bac   | ekground                                            | <b>5</b> |

|          | 2.1   | Circuit Switching and Packet Switching              | 5        |

|          |       | 2.1.1 Circuit Switching                             | 6        |

|          |       | 2.1.2 Packet Switching                              | 8        |

|          | 2.2   | Contributors of Latency in Packet-Switched Networks | 10       |

|          | 2.3   | Packet Switching versus Circuit Switching           | 14       |

|          | 2.4   | Hybrid Optical Network Architectures                | 15       |

|          |       | 2.4.1 Client-Server Hybrid Optical Network          | 16       |

|          |       | 2.4.2 Parallel Hybrid Optical Network               | 16       |

|          |       | 2.4.3 Integrated Hybrid Optical Network             | 17       |

| 3        | Fus   | ion Networking                                      | 18       |

|          | 3.1   | Fusion Networking Principle                         | 18       |

|          | 3.2   | Fusion Networking Properties                        | 19       |

|          | 3.3   | Transparent Ethernet                                | 21       |

|          | 3.4   | Hybrid Asynchronous Node Design                     | 22       |

|          |       | 3.4.1 GST and SM Packet Separation and Combination  | 22       |

|          |       | 3.4.2 GST Priority                                  | 23       |

|          |       | 3.4.3 SM QoS Differentiation                        | 24       |

| <b>4</b> | Tra   | nsPacket H1 Fusion Networking Muxponder             | 25       |

|          | 4.1   | The H1 Node                                         | 25       |

|          | 4.2   | H1 Capabilities                                     | 26       |

|          | 4.3   | H1 Key Features                                     | 26       |

|          | 4.4   | H1 Aggregation Properties                           | 27       |

|          |       | 4.4.1 Aggregation of SM Traffic                     | 27       |

|              |                    | 4.4.2 Aggregation of GST Traffic                                    | 28              |

|--------------|--------------------|---------------------------------------------------------------------|-----------------|

|              | 4.5                | H1 Management                                                       | 28              |

|              | 4.6                | H1 Comparison to other Hardware                                     | 29              |

| <b>5</b>     | Pre                | vious Work                                                          | 30              |

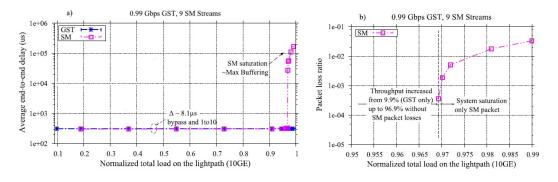

|              | 5.1                | Paper 1                                                             | 30              |

|              |                    | 5.1.1 Results                                                       | 31              |

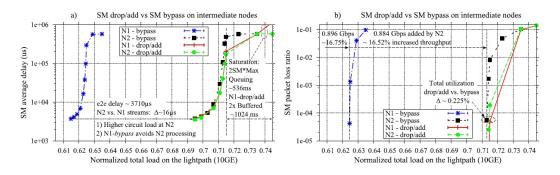

|              | 5.2                | Paper 2                                                             | 33              |

|              |                    | 5.2.1 Results                                                       | 33              |

| 6            | Lab                | oratory Environment                                                 | 35              |

|              | 6.1                | Hardware                                                            | 35              |

|              | 6.2                | Software                                                            | 37              |

|              | 6.3                | System and Network Overview                                         | 37              |

| 7            | Net                | work Scenario                                                       | 39              |

| •            | 7.1                | Physical Topology                                                   | 39              |

|              | 7.2                | Logical Topology                                                    | 40              |

|              | 7.3                | Field-trial Setup Objective                                         | 41              |

| 0            | E····              | eriment Procedure                                                   | 42              |

| 8            | <b>ь</b> хр<br>8.1 | Physical Connectivity                                               | <b>42</b><br>42 |

|              | 8.2                | H1 Configuration                                                    | 43              |

|              | 0.2                | 8.2.1 Enabling Interfaces                                           | 43<br>43        |

|              |                    | 8.2.2 Creating VLANs                                                | 43              |

|              |                    | 8.2.3 Adding Interfaces to VLANs                                    | 43              |

|              |                    | 8.2.4 Switching SM mode to GST mode                                 | 44              |

|              | 8.3                | Spirent TestCenter Configuration                                    | 44              |

|              | 0.0                | 8.3.1 Port Reservation and Configuration                            | 45              |

|              |                    | 8.3.2 Traffic Generator                                             | 46              |

|              |                    | 8.3.3 Traffic Analyzer                                              | 47              |

| 9            | Res                | ults                                                                | 49              |

| U            | 9.1                | Data                                                                | <b>4</b> 9      |

|              | 9.2                | Average End-to-End Delay                                            | 50              |

|              | 9.3                | Packet Loss Ratio                                                   | 51              |

|              | 9.4                | Packet Delay Variation                                              | 52              |

| 10           | Disc               | cussion                                                             | <b>54</b>       |

| 10           |                    | Delay Requirements for Time-Sensitive Applications and General Data | <b>54</b>       |

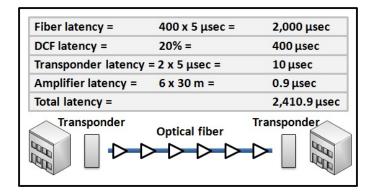

|              |                    | Adding Propagation Delay to Results                                 | 57              |

|              |                    |                                                                     | 01              |

| 11           | Con                | aclusion                                                            | 60              |

| 12           | Fur                | ther Work                                                           | 62              |

| Bi           | bliog              | graphy                                                              | 63              |

| $\mathbf{A}$ | Tra                | nsPacket H1 Technical Specifications                                | 66              |

| В | Mas  | ster Thes |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 68 |

|---|------|-----------|-----|----|---|----|-----|---|---|-------|---|---|---|-------|---|---|---|-------|---|---|-------|---|---|---|---|-------|---|---|----|

|   | B.1  | Outline   |     |    | • |    |     |   |   |       | • |   | • | <br>• |   | • |   | <br>• |   |   |       |   | • |   | • | <br>• |   | • | 68 |

|   | B.2  | Time Pla  | n.  | •  | • |    | •   | • | • | <br>• | • | • | • | <br>• | • | • | • |       | • | • | <br>• | • | • | • | • |       | • | • | 69 |

| С | H1   | Configur  | ati | on | L |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 70 |

|   |      | Running   |     |    |   | ra | tic | m |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 70 |

|   |      | VLAN SI   |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 74 |

| D | Raw  | 7 Data    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 76 |

|   | D.1  | SM $10\%$ |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 76 |

|   | D.2  | SM 20%    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.3  | SM 30%    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.4  | SM 40%    |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 77 |

|   | D.5  | SM $50\%$ |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 77 |

|   | D.6  | SM $60\%$ |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 78 |

|   | D.7  | SM $70\%$ |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.8  | SM 80%    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.9  | SM 90%    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.10 | SM $95\%$ |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 79 |

|   | D.11 | SM 96%    |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 79 |

|   | D.12 | SM 97%    |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 79 |

|   | D.13 | SM 97.2%  | δ.  |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 80 |

|   |      | SM 97.5%  |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 80 |

|   | D.15 | SM 97.8%  | δ.  |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 80 |

|   |      | SM 98%    |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

|   | D.17 | SM 99%    |     |    |   |    |     |   |   |       |   |   |   | <br>  |   |   |   |       |   |   |       |   |   |   |   |       |   |   | 81 |

|   |      | SM 99.5%  |     |    |   |    |     |   |   |       |   |   |   |       |   |   |   |       |   |   |       |   |   |   |   |       |   |   |    |

# List of Figures

| 2.1  | A simple circuit-switched network consisting of four switches and four links.    | 6  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | A MUX-DEMUX example.                                                             | 6  |

| 2.3  | With FDM, each circuit continuously gets a fraction of the bandwidth.            |    |

|      | With TDM, each circuit gets all of the bandwidth periodically during brief       |    |

|      | intervals of time.                                                               | 7  |

| 2.4  | Router architecture.                                                             | 8  |

| 2.5  | Input port functions of a router.                                                | 8  |

| 2.6  | Output port functions of a router.                                               | 9  |

| 2.7  | A simple packet-switched network with two sources sending packets through        |    |

|      | the same router creating a queue                                                 | 10 |

| 2.8  | Total nodal delay at router A                                                    | 11 |

| 2.9  | Caravan analogy.                                                                 | 12 |

| 2.10 |                                                                                  | 13 |

| 2.11 |                                                                                  | 16 |

| 2.12 | Parallel hybrid optical network [GPJKD06]                                        | 17 |

|      | Integrated hybrid optical network [GPJKD06].                                     | 17 |

|      |                                                                                  |    |

| 3.1  | Combining the best properties from packet and circuit switching into the         |    |

|      | fusion network.                                                                  | 19 |

| 3.2  | A fusion network model illustrating the efficient sharing of the physical fiber  |    |

|      | layer. The WRON can either be static (S-WRON) or dynamic (D-WRON).               |    |

|      | The OXCs and packet switches are physically co-located as separate units         |    |

|      | with a common control unit, or they can be integrated sharing physical           |    |

|      | resources in the node.                                                           | 20 |

| 3.3  | Bypassing using virtual wavelengths                                              | 21 |

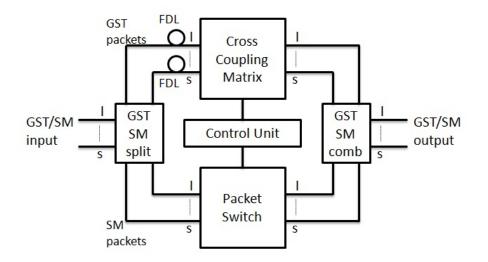

| 3.4  | Functional diagram of an asynchronous hybrid node. The number of inputs          |    |

|      | is given as $s = n * N$ , where n is the number of wavelengths per link and N is |    |

|      | the number of fibers. GST packets are delayed in FDLs to avoid contention        |    |

|      | between GST and SM packets.                                                      | 22 |

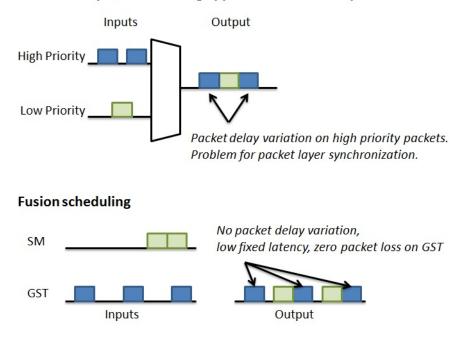

| 3.5  | Upper figure shows the strict priority QoS scheduling of packet switches and     |    |

|      | routers. If two packets of low and high priority arrive at the same time, the    |    |

|      | low priority packet will have to wait until the high priority queue is empty in  |    |

|      | order to be scheduled. However, if a high priority packet suddenly arrives       |    |

|      | while a low priority packet is being scheduled, it will have to wait until       |    |

|      | the low priority packet has been scheduled, causing PDV on high priority         |    |

|      | packets. Fusion scheduling, shown in the lower figure, avoids PDV on high-       |    |

|      | priority GST packets since low-priority SM packets are inserted only if there    |    |

|      | is a free gap between GST packets                                                | 23 |

|      |                                                                                  |    |

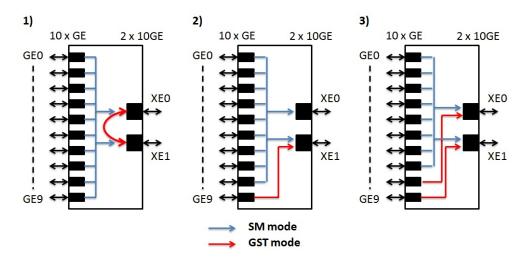

| 4.1          | TransPacket's Fusion H1 add-drop muxponder. [Tra11a]                                                                                                                                                                                                                                                                                                                   | 25       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.2          | Possible GST traffic aggregation on the H1 node in combination with SM aggregation.                                                                                                                                                                                                                                                                                    | 28       |

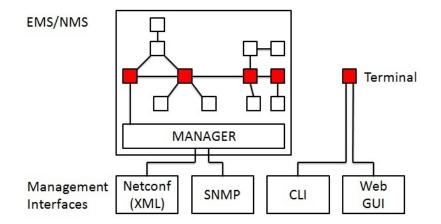

| 4.3          | H1 management system. EMS=Element Management System; NMS=Network<br>Management System. Figure adapted from [Tra11a]                                                                                                                                                                                                                                                    |          |

| 5.1          | Schematic diagram of the unidirectional transport through the fusion ad-                                                                                                                                                                                                                                                                                               |          |

|              | d/drop muxponder used in Paper 1. [RVH]                                                                                                                                                                                                                                                                                                                                | 30       |

| $5.2 \\ 5.3$ | Experimental test-bed used in Paper 1. [RVH] $\dots \dots \dots \dots \dots \dots$<br>PLR as a function of the total added SM load. For the 1 SM stream case<br>(top), you can see the PLR rises rapidly at a load of 0.91 to $1e^{-2}$ ; whereas<br>for the 4 SM streams case (bottom) this occurs at a load of 1.35; the GST                                         | 31       |

| 5.4          | average rate is 5.7 Gb/s [RVH] Delay as a function of the total added SM load. For the 1 SM stream case (top), you can see the delay rises rapidly at a load of 0.91 to 280 ms; whereas for the 4 SM streams case (bottom) this occurs at a load of 1.35 and to a delay of 780 ms; GST delay is shown and it is constant (no PDV) and its                              | 32       |

| EE           | average rate is 5.7 Gb/s. [RVH]                                                                                                                                                                                                                                                                                                                                        | 32       |

| $5.5 \\ 5.6$ | Experimental test-bed used in Paper 2. [RVB]                                                                                                                                                                                                                                                                                                                           | 33       |

| 5.7          | but the GST stream does not experience any losses. [RVB]                                                                                                                                                                                                                                                                                                               | 34<br>34 |

| 6.1          | The LAB environment at the Department of Telematics in NTNU                                                                                                                                                                                                                                                                                                            | 35       |

| 6.2          | Hardware and Software specifications of desktop computers used                                                                                                                                                                                                                                                                                                         | 36       |

| 6.3          | Spirent SPT-2000A-HS chassis. [Com07]                                                                                                                                                                                                                                                                                                                                  | 36       |

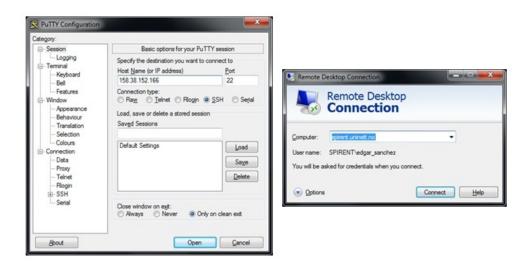

| 6.4          | Left: SSH secure connection to H1 node. Right: Connection to the Spirent<br>box using the Remote Desktop Connection.                                                                                                                                                                                                                                                   | 38       |

| 6.5          | Graphic representation of how the H1 nodes and Spirent box are remotely accessed by the users for management.                                                                                                                                                                                                                                                          | 38       |

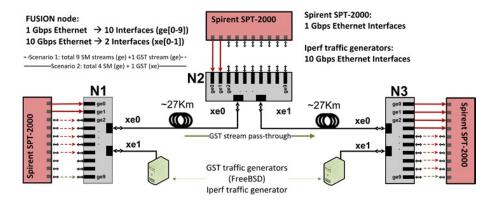

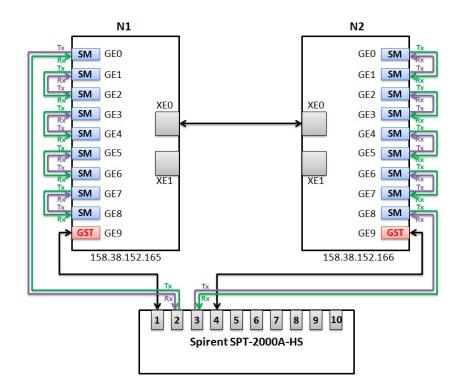

| 7.1          | Divised top closer used for the superiment                                                                                                                                                                                                                                                                                                                             | 39       |

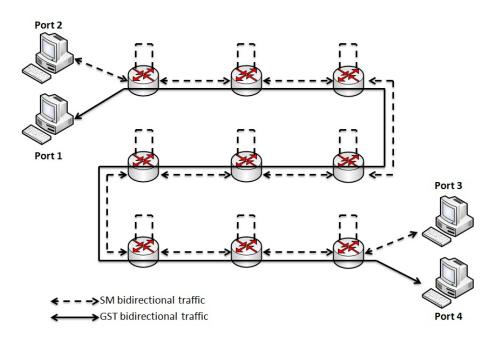

| 7.1          | Physical topology used for the experiment<br>Logical representation of the physical topology. Each computer represents a<br>Spirent port whereas each node represents a time when an SM stream needs<br>to go through the 10GE link (aggregation). The arrows are bidirectional<br>and they both represent the sigle 10GE fiber cable connected at XE0 of N1<br>and N2 | 40       |

| 8.1          | Left: Optical connections made in H1 nodes; mainly loops and the 10GE connection between each other. Right: Spirent node and its optical connections to the H1 nodes.                                                                                                                                                                                                  | 42       |

| 8.2          | Reserving ports 1 to 4 in the Spirent TestCenter.                                                                                                                                                                                                                                                                                                                      | 45       |

| 8.3          | GUI of the Spirent TestCenter.                                                                                                                                                                                                                                                                                                                                         | 45       |

| 8.4          | Port configuration in Spirent TestCenter.                                                                                                                                                                                                                                                                                                                              | 46       |

| 8.5  | Created devices per port: one for sending and one for receiving                  | 46 |

|------|----------------------------------------------------------------------------------|----|

| 8.6  | Traffic Wizard: selecting source-destination pairs.                              | 47 |

| 8.7  | Traffic analyzer displaying the results at the bottom of the Spirent Test-       |    |

|      | Center's GUI.                                                                    | 48 |

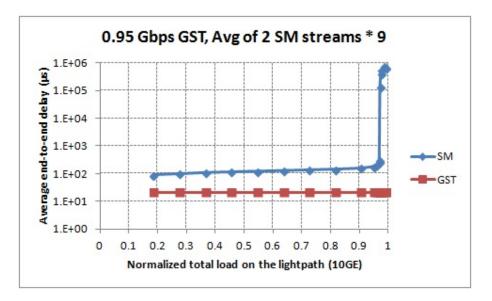

| 9.1  | The average packet latency for both SM and GST traffic as a function of          |    |

|      | the normalized offered load on the 10GE lightpath                                | 50 |

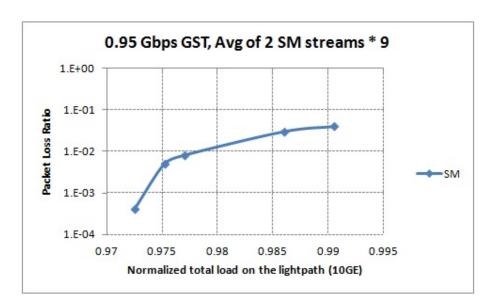

| 9.2  | The total packet loss ratio for the SM traffic added on the lightpath. The       |    |

|      | GST stream does not experience any losses                                        | 51 |

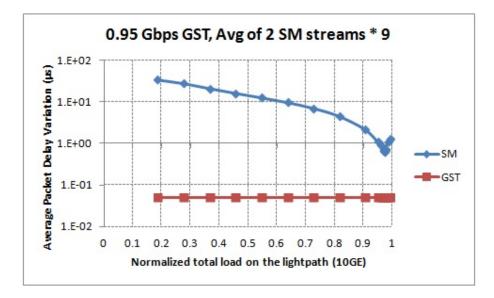

| 9.3  | The average packet delay variation for both SM and GST traffic as a func-        |    |

|      | tion of the normalized offered load on the 10GE lightpath                        | 52 |

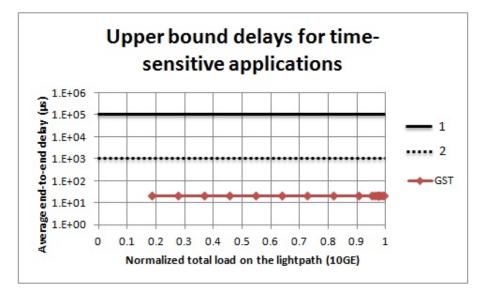

| 10.1 | The GST average end-to-end delay is 21.47 $\mu$ s through all the measurements   |    |

| 10.1 | no matter the SM insertion. Upper bound delay 1 is at 100 ms for online          |    |

|      | gaming, videoconferencing and control information. Upper bound delay 2           |    |

|      | is at 1 ms for online banking. The range between both upper bound detay 2        |    |

|      | been proven to be acceptable for telemedicine and e-health                       | 56 |

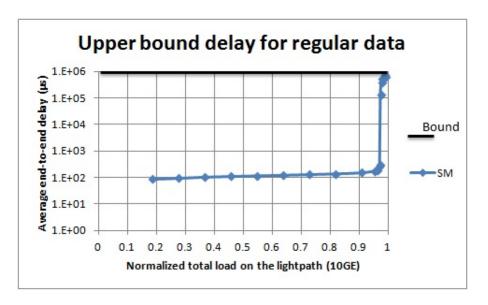

| 10.2 | The SM packet delay increases slowly as the 10GE lightpath load increases        | 00 |

| 10.2 | up until $L_{10GE}^T = 0.9698$ . At which point it increases exponentially from  |    |

|      | exactly 301.69 $\mu$ s to 134,891.18 $\mu$ s. From there on the SM delay keeps   |    |

|      | increasing dramatically to a maximum value of 712,526.37 $\mu$ s or 0.7 seconds. |    |

|      | The upper bound delay for general data is 1 second.                              | 56 |

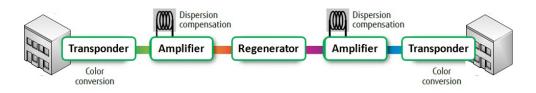

| 10.3 | Optical nerworking functions that can increase latency                           | 57 |

|      | Latency introduced on a 400 km long fiber network.                               | 58 |

|      | Lowering latency in optical networks                                             | 59 |

# List of Tables

| 4.1 | Comparison of a hybrid muxponder such as H1 to hardware from layers 1, 2 and 3 (L1, L2, L3). *On hybrid lines. **When congested on SM |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|

|     | aggregation interfaces.                                                                                                               | 29 |

| 6.1 | Software needs for each device.                                                                                                       | 37 |

| 9.1 | 1GE SM and GST load; and total load in the 10GE lightpath for the 18 experiments.                                                     | 50 |

# Chapter 1

# Introduction

Network users are not concerned with the intricacies of how the Internet works. They only want to experience fast delivery of content without any problems along the way. Whenever a user complaints about poor application performance, you rarely hear things such as 'the packets are taking a sub-optimal path to the destination' or 'the network utilization is very high'. What they will always say is 'the network is too slow' or 'it takes too much time to load this website or application', etcetera. This is due to the fact that users' complaints are based on their quality of experience when using an application and this quality of experience is almost all the time related to time [Dav08].

"Ideally, we would like Internet services to be able to move as much data as we want between any two end systems, instantaneously, without any data loss" [KR10]. However this is impossible to accomplish in reality. Instead, computer networks introduce *delays* or *latency*, as well as *jitter* or *packet delay variation* (PDV) between source and destination, which impacts negatively in the application performance. The latency and jitter concepts are explained in detail in chapter 2.

## 1.1 Motivation

While traditional applications such as web browsing, e-mail and file sharing can tolerate more than 100 milliseconds of latency [MRV10], more and more services such as IPTV, high quality video conferencing, remote surgeries, online banking and cloud computing [HWD12] demand low latency and jitter in combination with high bandwidth and low packet loss in order for them to work successfully. These applications are known as *time-sensitive applications*.

Legacy *circuit switching* technologies such as Synchronous Optical Network / Synchronous Digital Hierarchy (SONET/SDH) can offer the necessary Quality of Service (QoS) to enable zero packet loss and low predictable latency, however, since resources are permanently allocated to the established connections between source and destination, there is a low utilization of the links.

On the other hand, using *packet switching*, the link capacity is dynamically shared for traffic with changing intensity and connections with different bandwidth needs. This results in a higher throughput efficiency.

In today's networking demands "there is a need for flexibility to carry different types of services over the same converged network; hence, to enable high network throughput efficiency while still supporting demanding services like" [RVB] time-sensitive applications.

TransPacket is a startup-company that has implemented the novel *fusion* technology, also called the Optical Migration Capable Networks with Service Guarantees (OpMiGua) integrated hybrid networks. The fusion concept has the main objective of combining the best properties from both circuit and packet switched networks into a hybrid solution.

It is highly motivating to work on this thesis since it deals with a unique and patented optical networking technology developed by a Norwegian company and whose Chief Executive in Office (CEO) is my main supervisor, professor Steinar Bjørnstad.

## 1.2 Objective

It is the objective of this thesis work to perform a network experiment involving TransPacket H1 nodes measuring performance parameters like latency, latency variation (or PDV) and packet loss. The whole purpose is to be able to prove that Internet traffic can be separated into high and low priority, and that the former will experience no packet delay variation and no packet loss, while at the same time having almost no waste of resources using TransPacket's Fusion Network approach.

## 1.3 Scope

This master thesis work is meant to be based on experimental grounds, getting in touch with actual configurations of TransPacket's H1 nodes, setting up the physical connections handling optical fibers, and making tests using a packet generator and analyzer. Due to time and resource constraints, a single network scenario is explored, where both H1 nodes are situated in the same place.

## 1.4 Methodology

The method I used throughout this thesis can roughly be divided into two parts: the research of scientific papers relevant to this topic; and the hands-on experimentation. Each was then subdivided into different tasks:

Research:

- Background research

- Theoretical research of fusion network

- Previous work and results

Hand-on experimentation:

- Getting acquainted with the laboratory and hardware used

- Set up a network scenario

- Start experimentation

- Gather results and analyze them

Over 40 hours of research and around 60 hours of experimentation was done. Throughout all this time, I wrote this paper in parallel. There were feedbacks and comments from both my supervisors and PhD student Raimena.

## **1.5** Document Structure

The remainder of this paper is organized as follows:

**Chapter 2: Background** presents the background theory of circuit switching and packet switching, emphasizing their differences in how they handle data and introduce latency, PDV and ultimately packet loss. A detailed insight on latency is given as well. At the end, an overview of a hybrid solution is presented.

**Chapter 3:** Fusion Networking describes the principles, properties and main characteristics of an integrated hybrid network known as fusion. It also presents the design characteristics of a hybrid node.

**Chapter 4:** TransPacket H1 Fusion Networking Muxponder presents the capabilities, key features, aggregation properties and management system of the H1 node, and compares it with other known hardware.

**Chapter 5: Previous Work** shows past experimentations that have already been performed with fusion networking and its results; specifically the ones documented in [RVH] and [RVB] by PhD student Raimena Veisllari, and professors Steinar Bjørnstad and D. R. Hjelme in collaboration with Kurosh Bozorgebrahimi.

**Chapter 6:** Laboratory Environment lists the hardware and software necessary to perform the experiment as well as the network overview of how such hardware is remotely connected in order to make configurations.

**Chapter 7:** Network Scenario presents the physical topology chosen to perform the experiments and its logical representation as well as the objective to achieve using this network scenario.

**Chapter 8: Experiment Procedure** describes the test procedure for carrying out the experiment. From making the physical connections all the way to configuring the H1 nodes and setting up the Spirent TestCenter to generate and analyze traffic from its correspondent ports.

**Chapter 9: Results** presents the results obtained by the experiments done. A comparison of SM and GST will be made, using plots that graphically represent the results obtained.

#### CHAPTER 1. INTRODUCTION

**Chapter 10: Discussion** deals with a more comprehensive discussion based on the results presented in chapter 9. It also presents the minimum requirements in terms of delay in order for certain time-sensitive applications and general data to work properly, and compare them with the GST and SM performance achieved during experimentation.

Chapter 11: Conclusion wraps up and concludes the paper.

**Chapter 12:** Further Work gives suggestions on how to proceed with this topic or experiments that need to be further investigated since they were not covered in this paper mainly due to time constraints.

# Chapter 2

# Background

In this chapter, the background theory of circuit switching and packet switching will be presented, emphasizing their differences in how they handle data and introduce latency, PDV and ultimately packet loss. An overview of a hybrid solution will be presented as well.

## 2.1 Circuit Switching and Packet Switching

There are two fundamental approaches when transferring data through a network of links and switches: circuit switching and packet switching. In circuit-switched networks, the resources such as buffers and link transmission rate needed along a path to provide communication between a source and a destination are *reserved* for the duration of such communication session between them [KR10]. Contrary to circuit switching, in packetswitched networks, these resources are *not* reserved; the messages sent during a session use the resources *on demand*, and as a consequence, may have to wait in a queue before being able to access the communication link [KR10].

The telephone network is the best example of a circuit-switched network. Consider what happens when one person wants to communicate with another person over a telephone network. First, before any information can be sent, the 'caller' needs to establish a connection between him and the recipient by dialing the recipient's phone number. This connection is called a *circuit* [KR10]. Once this circuit has been established, communication can start with a reserved constant transmission rate [KR10] for the duration of the connection. Since bandwidth has been reserved for this circuit, the sender can transfer with a *guaranteed* constant rate.

The Internet Protocol (IP) based Internet is the perfect example of a packet-switched network. The same as with circuit switching, whenever a host wants to send data to another host, this data is transmitted over a series of communication links that connect the sender and the receiver together. However, with packet switching, the packet is sent into the network without reserving any bandwidth whatsoever [KR10]. A link is said to be *congested* when other packets also need to be transmitted over the same link at the same time. If this occurs, then our packet will have to wait in a *buffer* at the sending side of the transmission link, causing it to suffer a delay. And so, "the Internet makes its *best effort* to deliver packets in a timely manner, but it does not make any guarantees" [KR10] like circuit switching does.

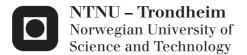

#### 2.1.1 Circuit Switching

A circuit-switched network is illustrated in Figure 2.1. In this particular example, there are four circuit switches interconnected by four links. Each link has n circuits, which means each link can support n simultaneous connections. As mentioned previously, whenever two hosts want to communicate with each other, the circuit-switched network has to first establish a dedicated *end-to-end connection* between them. And so, from this example, if Host A wants to communicate with Host B, the network must first reserve one circuit on each of the two links connecting them together. This is where it gets interesting; "because each link has n circuits, for each link used by the end-to-end connection, the connection gets a fraction 1/n of the link's bandwidth for the duration of the connection" [KR10].

Figure 2.1: A simple circuit-switched network consisting of four switches and four links.

But how can a single link carry n circuits or channels? The answer is *multiplexing*. Multiplexing is the process of subdividing a link into multiple channels for resource sharing. As seen in Figure 2.2, a multiplexor or MUX has n inputs, and 1 output with n channels; whereas a demultiplexor or DEMUX has 1 input with n channels and separates them into n outputs.

Figure 2.2: A MUX-DEMUX example.

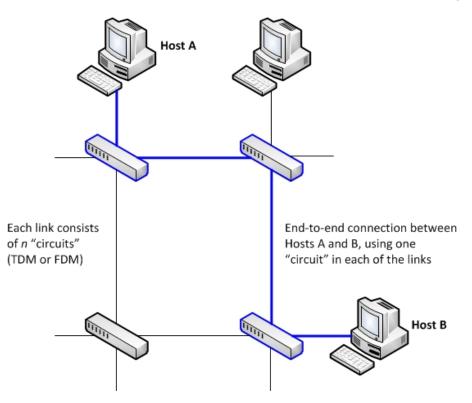

This way, multiple sender/receiver pairs can share the same link. There are two ways to implement this: using either *frequency-division multiplexing* (FDM) or *time-division multiplexing* (TDM).

Using FDM, "the frequency spectrum of a link is divided up among the connections established across the link" [KR10]. This means that each connection within a single link has a *frequency band* dedicated to it for the duration of the connection. This frequency band is said to have a specific width, for example, in telephone networks this width is of 4 kHz (4,000 hertz) [KR10], and therefore this is most commonly known as *bandwidth*.

With TDM, the transmission is divided into time slots. Once the connection between sender and receiver has been established, the network dedicates one time slot in every frame for the sole use of that connection [KR10]. Figure 2.3 illustrates both FDM and TDM for a link that supports up to four circuits. For FDM, the frequency domain is segmented into four bands, each with a bandwidth of 4 KHz. For TDM on the other hand, the time domain is segmented into frames with four time slots in each frame.

Figure 2.3: With FDM, each circuit continuously gets a fraction of the bandwidth. With TDM, each circuit gets all of the bandwidth periodically during brief intervals of time.

#### 2.1.1.1 Circuit Switching Drawback

Circuit switching is a wasteful technology because of the fact that the dedicated circuits are idle during *silent periods* [KR10]. This means that the network resources, whether they are frequency bands or time slots in the links along the connection's path, cannot be used by any other ongoing connections, even though they are not being used. As a result, network resources are being wasted and so the network capacity is not used efficiently.

#### 2.1.2 Packet Switching

Modern computer networks break long messages into smaller chunks of data known as *packets* [KR10]. These packets travel between source and destination through the communication links, however, unlike circuit switching, they can take different routes since a connection or circuit does not need to be created before transmission starts. And so, packets are transmitted with the full transmission rate of the link.

Most routers and link-layer switches use a transmission approach called *store-and-forward*. This means that the switch must receive the entire packet before it can begin to transmit the first bit of that packet onto the outbound link [KR10]. This process introduces a delay at the input link of each switch or router along the route from source to destination.

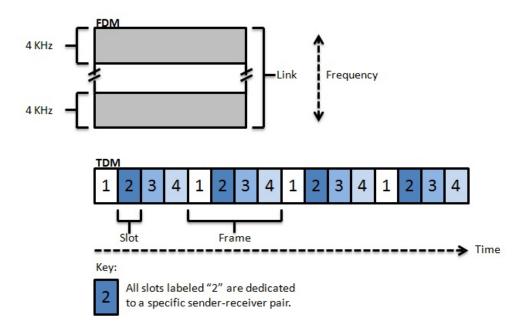

We still need to go deeper into how forwarding works, in order to understand the source of delay in packet-switched networks. Figure 2.4 shows the architecture of a router with all of its components.

Figure 2.4: Router architecture.

The *switching fabric* simply connects the router's input ports to its output ports. The *routing processor* executes the routing protocols (out of the scope for this paper) which feed information to the forwarding table [KR10]. The *input* and *output ports* need to be described in detail.

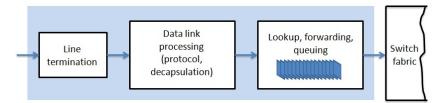

Figure 2.5 shows a detailed view of the input port with all of its functions. The *line termination* module and *link* processing module are the interfaces for the physical and data link layers [KR10].

Figure 2.5: Input port functions of a router.

The *lookup/forwarding* module is in charge of deciding which output port to send it to by looking at the forwarding table. Once the router knows which output port to forward the packet to, it is sent to the switching fabric. This is where it gets interesting. A packet

may be temporarily blocked from entering the switching fabric [KR10] if there are many other packets using it coming from the other input ports. A blocked packet is then moved to a queue at the input port and scheduled to cross the switching fabric after some time, causing delay.

Furthermore, a switch or router has an *output buffer* for every link attached to it, which stores the packets that are to be sent out on that specific link. The idea is that if a packet arrives at a switch and is meant to be transmitted out of one of the outbound links, and this link is busy with the transmission of another packet, then the arriving packet must wait in the output buffer [KR10], adding another type of delay called *queuing delay* (see section 2.2). This delay is very complicated because it is variable and depends entirely on how congested the network is and the size of the buffers. If a buffer is completely filled with other packets waiting to be transmitted, the arrival of a new packet will cause packet losses to occur.

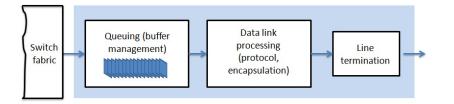

Once the output port receives a packet, it goes through a queue if the switch fabric delivers the packets at a higher rate than the output link rate (see Figure 2.6); process which also adds latency. The link processing and line termination modules are also needed as in the input port.

Figure 2.6: Output port functions of a router.

Suppose that the input line and output line speeds are identical and that there are n input ports and n output ports. Also suppose that the switching fabric speed is n times faster than the line speeds. In this case, there will not be queues at any input line, since the worst case scenario is that all n input lines are receiving packets, but the switch will be able to transfer n packets from input to output ports in the time it takes each of the n input ports to simultaneously receive a single packet [KR10].

Unfortunately this is not as simple in the output ports because in the worst case scenario, all the packets from the n input ports are destined to the same output port. And since only a single packet can be transmitted at a time, the n packets will have to wait in a queue before being transmitted out into the network [KR10]. If the number of packets in a single output port queue is too big, the router will start to drop packets.

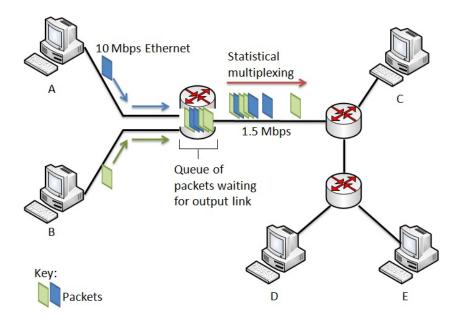

Figure 2.7 illustrates an example of a packet-switched network. As it can be seen, hosts A and B are sending packets to host E. First they send their respective packets along 10 Mbps Ethernet links to the first packet switch. This switch will then forward these packets to the 1.5 Mbps link. The problem arises when the arrival rate of the packets exceeds the rate at which these packets can be forwarded out, and so congestion occurs. There is a detailed explanation of all the kinds of delays introduced in packet switching on section 2.2.

Figure 2.7: A simple packet-switched network with two sources sending packets through the same router creating a queue.

#### 2.1.2.1 Packet Switching Drawback

Because of the output port queuing, a *packet scheduler* at the output port needs to choose which packet is to be sent next, and which other ones should remain in the queue. This process is the key to provide *quality-of-service* (QoS) guarantees such as minimizing delays. Unfortunately, the Internet today as it uses mainly IP, provides a best-effort service, which means IP does not care for minimizing end-to-end delay nor minimizing PDV.

"The Internet has mostly taken an egalitarian approach to packet scheduling in router queues. All packets receive equal service; no packets, including delay-sensitive packets, receive special priority in the router queues" [KR10].

### 2.2 Contributors of Latency in Packet-Switched Networks

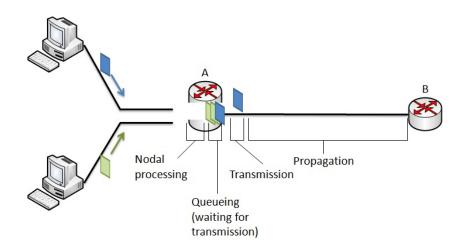

Whenever a packet travels from one node to the next, the packet suffers from several types of delay at each node along the way. These delays include the *processing delay*, *queuing delay*, *transmission delay* and *propagation delay* [KR10] as seen in Figure 2.8. The sum of all of these variables results in the *total nodal delay*. Let us closely examine each one of these delays in the context of Figure 2.8 to have a better understanding of them. As part of its end-to-end route between source and destination, a packet is sent from the sender through router A to router B. Our goal is to characterize the nodal delay at router A.

When a packet arrives at router A, it must examine the packet's header information to determine the proper outbound link that will lead to the destination and then it directs the packet to this link. In this example, there is only one outbound link which leads directly to router B. Remember also that a packet can only be transmitted on a link whenever there is no other packet being transmitted on this link and if there are no other packets in front of the queue in the router's buffer [KR10].

Figure 2.8: Total nodal delay at router A.

**Processing Delay** It is the amount of time the node takes to look at the packet's header and perform a destination address lookup to determine where to forward the packet [KR10]. It can also include the time it takes to check for bit-level errors in the packet. This kind of delay in modern high-speed routers is almost insignificant, in the order of microseconds or less [KR10]. After the node knows which outbound link to use, the router sends the packet to the queue that precedes the link to router B.

**Queuing Delay** It is the time the packet has to wait in the queue (at the buffer) before being transmitted onto the link. The queuing delay is naturally dependent on the number of packets that are queued before the specific packet. If the queue is empty and there is no packet being transmitted then the queuing delay is zero. On the other hand, if the traffic is heavy and the queue is long, the queuing delay will be large [KR10]. For time-sensitive applications the queuing delay is large. Queuing delays are on the order of microseconds to milliseconds [KR10].

**Transmission Delay** Assuming that packets are transmitted in a first-come-first-served basis, a packet can only be transmitted after all the packets in front of the queue have been transmitted. In order to calculate the transmission delay we need to define two variables; the *length of the packet* denoted by L bits [KR10], and the *transmission rate* of the link from router A to B denoted by R bits/sec [KR10]. Transmission delay is then L/R. This kind of delay is usually on the order of microseconds to milliseconds as well [KR10].

**Propagation Delay** Once a bit has been pushed into the link during the transmission, it then needs to propagate all the way to router B. Propagation delay can be defined as the time it takes for the bit to propagate or travel from the beginning of the link to router B [KR10]. Of course, the propagation speed will entirely depend on the physical medium being used. Three major mediums are fiber optics, copper cables or via satellite. Propagation delay is then d/s where d is the distance between router A and B, and s is the propagation speed of the link. This kind of delay depends on the distance between source and destination, but in general, in wide-area networks it is on the order or milliseconds [KR10].

It is very common for people to not being able to differentiate between transmission delay

#### CHAPTER 2. BACKGROUND

and propagation delay. Transmission delay is the time it takes for the router to push the packet out and it is a function of the packet's length and the link transmission rate, but has nothing to do with the distance between the two routers. Propagation delay is the time it takes for the packet to go from one router to the next and it is a function of the distance between the two routers, but has nothing to do with the packet's length or the link transmission rate.

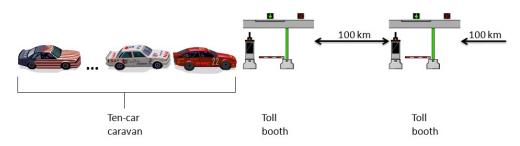

In order to understand this better, we can create an analogy. Let us assume there is a highway that has a tollbooth every 100 km as seen in Figure 2.9. The highway represents the link, whereas the tollbooths represent the routers. Let us also assume cars travel (propagate) at a constant speed of 100 km/h. 10 cars are travelling in a caravan, that is, they follow each other in a fixed order. Each car represents a bit and the whole caravan represents one packet. Another assumption is that each tollbooth services (transmits) a car at a rate of one car every 12 seconds. In this example, let us pretend there are no other cars in the highway, which means there is no queuing delay.

Figure 2.9: Caravan analogy.

The transmission delay (time for the tollbooth to push the caravan out onto the highway) is

$$\frac{L}{R} = \frac{10bits(cars)}{5bpm(carsperminute)} = 2minutes$$

The propagation delay (time for the cars to get from one tollbooth to the next) is

$$\frac{d}{s} = \frac{100km}{100km/h} = 1hour$$

So the time it takes for the caravan (packet) when is stored at the front of the tollbooth until it is stored in front of the next one is the sum of the transmission delay and the propagation delay, which in this case it is 62 minutes.

To summarize and as mentioned at the beginning of this section, the total nodal delay is the sum of the processing delay, queuing delay, transmission delay and propagation delay, which can be expressed as follows

$$d_{nodal} = d_{proc} + d_{queue} + d_{trans} + d_{prop}$$

For the purpose of this paper, we will only focus on queuing delay  $(d_{queue})$  and propagation delay  $(d_{prop})$  for the following reasons. The contribution of each of these delays can vary significantly from being negligible to being a dominant player in the total delay. However,  $d_{proc}$  is insignificant nowadays in modern routers when configured correctly [Dav08], so it is often negligible. So is the case for  $d_{trans}$ , which becomes insignificant with data rates of 10 Mbps and higher [KR10], which in today's networking environment, almost everyone has.

The  $d_{prop}$  can of course be negligible as well when the source and destination are in the same network or close together, however in a real life environment, it is very likely the transmission has to travel half around the world; and it is also an opportunity to compare different physical layer technologies and how they influence on this delay. By far the most complicated and interesting delay is  $d_{queue}$ , and in an unrealistic perfect environment, it could be negligible. The  $d_{queue}$  can be different for each packet and so in order to measure this delay, experts use statistics [KR10].

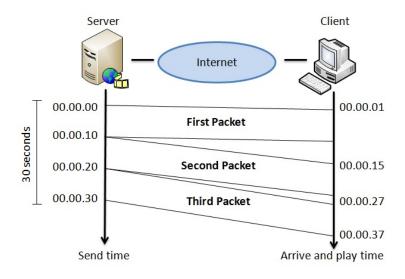

Last but not least, it is important to mention that it is highly unlikely that the end-to-end latency remains constant. There is a phenomenon called PDV explained in RFC3393 [IET02], which is most commonly known as *delay jitter*. This term "refers to the variance in the arrival rate of packets from the same data flow" [Dav08], which means the time from when a packet is generated at the source until it is received at the destination can change from packet to packet of the same message as seen in Figure 2.10.

Figure 2.10: Delay jitter between source and destination.

Let us consider two consecutive packets. The sender sends the second packet 20 milliseconds after the first packet, however the second packet arrives more than 20 milliseconds after the first one at the receiving end. This could happen for instance if the first packet arrived at an almost empty queue at the destination and just before the second packet arrived at the queue, a large number of packets from other sources arrive at the same queue, which means the second packet has a longer queuing delay. It is important to note that it could also be the case that the second packet arrives less than 20 milliseconds apart, and this would also count as delay jitter. The three main reasons delay jitter exists are:

- Variance in transmission delay due to variance in packet sizes [Dav08] (different L)

- Variance in queuing delay due to packet spacing from multiple sources at a common outbound link [Dav08] (as seen in the example above)

- Packets taking different routes to reach the destination due to load balancing or maybe some routing issues

### 2.3 Packet Switching versus Circuit Switching

Now that both packet switching and circuit switching have been thoroughly explained, can we answer the question, which one is better? This is a tricky one and I believe there is no absolute correct answer. Critics of packet switching argue that this technology is not suitable for real-time services or time-sensitive applications because of its variable and unpredictable end-to-end delays [KR10], which make it impossible to offer any QoS guarantees as the ones offered by circuit switching. On the other hand, packet switching proponents argue that it offers better sharing of bandwidth than circuit switching and that is it simpler, more efficient and less costly to implement [KR10].

But why exactly is packet switching more efficient? The best way to make this clear is by using statistics based on an example. We have the following assumptions:

- 1. There are 35 users are sharing a 1 Mbps link.

- 2. Each user generates data at a constant rate of 100 kbps whenever it is active, and generates no data at all in periods of inactivity.

- 3. A user is active only 10 percent of the time.

With circuit switching, this is easy to calculate. Since each user requires one tenth of the bandwidth to be reserved at all times even if the user is not active, this circuit-switched link can support only 10 simultaneous users (the other 25 will not be able to transmit data), that is

$$\frac{1Mbps}{100kbps} = 10users$$

With packet switching however, this calculation is not so straightforward. We know that the probability that a specific user is active is 0.1 (10%). Using the *binomial distribution*, the probability that there are 11 or more simultaneous active users (out of 35) at a given time is

$$1 - \sum_{n=0}^{10} \binom{35}{n} p^n (1-p)^{35-n}$$

Where p = 0.1 and *n* ranges from 0 to 10. I decided to calculate it this way since this implies making the calculation 11 times, instead of 25 times (from 11 to 35). This is why in the end; we need to subtract the result from 1. And so the result is 0.0004.

We can then calculate that the probability of having 10 or fewer simultaneous active users at a given time is 1 - 0.0004 = 0.9996. This means that with 99.96% probability, the aggregate arrival rate of data is less than or equal to 1 Mbps, and so packets will flow through the link without any delay as is the case with circuit switching. Of course, when there are more than 10 simultaneous active users, then packets will start to queue at the output buffer until the aggregate input rate falls back below 1 Mbps. And since the probability of this happening is 0.04%, we can say that in this particular example, packet switching provides essentially the same performance as circuit switching, but "does so while allowing for more than three times the number of users" [KR10].

Another example that clarifies how packet switching is more efficient is as follows. Let us assume there are 10 users, one of which suddenly creates one thousand packets, each of 1,000 bits. The other 9 users are idle. If the network is TDM circuit switching with 10 slots per frame (1 frame, 1 second) and each slot consists of 1,000 bits, then the active user can only use its allocated time slot. So the user sends 1,000 bits and waits for the other 9 time slots to pass even though they are not being used to send the following 1,000 bits. It will take 10 seconds to transmit the entire data. If packet switching was being used, then the active user can one else is demanding any bandwidth, and so it will take the user 1 second to transmit its data.

Both examples above show how packet switching performance can be better than that of circuit switching. It is basically because of the on-demand approach of sharing resources with packet switching, which has come to be known as *statistical multiplexing* (SM) [KR10]. However, if we were to saturate the network by having a lot of users and they are active most of the time, we would see that packet switching would introduce increasing delay to the point of overloading the network.

## 2.4 Hybrid Optical Network Architectures

What about a *hybrid optical network architecture* that combines the advantages of circuit switching and packet switching, while at the same time avoids their disadvantages? According to [GPJKD06], a hybrid network architecture is one that "does not apply one network technology to transport all traffic, but instead combines several switching technologies into one architecture". It is important to note that I have used the word optical, and this is because the focus of this paper is a hybrid technology using optical media.

In [GPJKD06], three different classes of hybrid optical networks have been identified. In order of the degree of interaction and integration (from least to most) of the networking technologies, these are:

- 1. Client-server

- 2. Parallel

- 3. Integrated

### 2.4.1 Client-Server Hybrid Optical Network

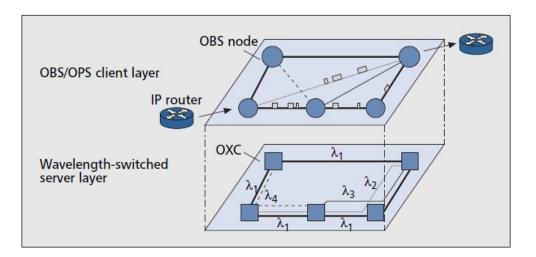

As its name implies, this class of hybrid optical network uses a hierarchy of optical layer networks, where the lower layer "functions as a server setting up a virtual topology for the upper client layer" [GPJKD06]. The client layer is an *optical burst switching* (OBS) or *optical packet switching* (OPS) network, whereas the server layer is a wavelength switching network.

And so, the OBS or OPS nodes are in charge of aggregating traffic. These nodes are interconnected by direct lightpaths at the server layer, which would work as a circuit-switched network. In other words, "optical bursts or packets are switched only in the client layer nodes and transparently flow in lightpaths through the circuit-switched server layer nodes" [GPJKD06]. Figure 2.11 shows such a hybrid network.

Figure 2.11: Client-server hybrid optical network [GPJKD06].

However, this particular hybrid architecture does not solve the problem. According to [GPJKD06], only low network utilization is achieved because to increase connectivity, this architecture uses a virtual topology which yields less traffic per link and thus reduced multiplexing gain.

### 2.4.2 Parallel Hybrid Optical Network

In this class of hybrid architecture, "two or more optical layer networks, offering different transport services, are installed in parallel" [GPJKD06]. And then, an intelligent edge node decides whether to use them individually or combine them to optimally serve customer service requirements. This decision is made based on explicit user request, traffic characteristics or QoS requirements. Figure 2.12 shows the representation of a parallel hybrid optical network.

On the downside, "the design of such parallel hybrid architectures has to trade-off efficiency and realization complexity" [GPJKD06].

Figure 2.12: Parallel hybrid optical network [GPJKD06].

### 2.4.3 Integrated Hybrid Optical Network

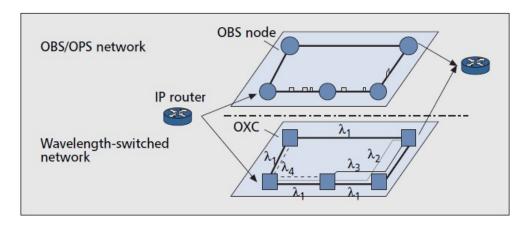

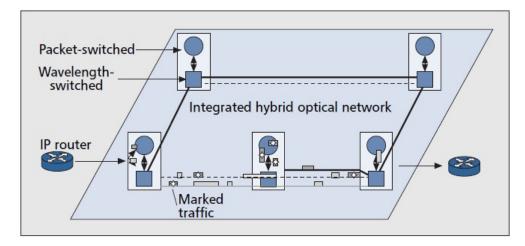

Last but not least, comes a class that completely integrates both technologies. They share the network resources such as bandwidth simultaneously. So for example, each node in an integrated hybrid network can choose to send traffic wavelength-switched through a predetermined connection or circuit; or ignore that circuit path and process the traffic in a packet-switched manner.

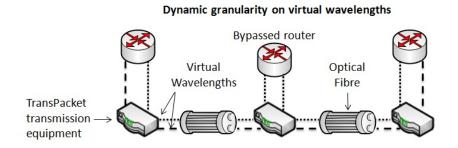

Figure 2.13 shows this kind of hybrid network. As you can see, each node has both a packet-switched and a wavelength-switched device. How do they decide which one to use? One option is to transmit all packets over the end-to-end lightpath since it removes the need for intermediate processing [GPJKD06]; and when congestion occurs, the node can switch to packet switching. A second option is to use the wavelength-switched device for high-priority traffic and the packet-switched one for the rest to achieve a certain QoS.

Figure 2.13: Integrated hybrid optical network [GPJKD06].

This method is the most resource efficient, however it is also the most complex. According to [GPJKD06], there are only two proposals of integrated hybrid optical networks: the OpMiGua and *Overspill Routing in Optical Networks* (ORION). This thesis work is entirely focused on the OpMiGua approach, also known as *Fusion Networking*.

# Chapter 3

# **Fusion Networking**

IP traffic increase has resulted in a demand for greater capacity of the underlying Ethernet network. As a consequence, not only Internet Service Providers (ISPs) but also telecom operators have migrated their mobile back-haul networks from legacy SONET/SDH circuit-switched equipment to packet-based networks.

This inevitable shift brings higher throughput efficiency and lower costs; however, the guaranteed QoS and minimal delay and PDV that can only be offered by circuit-switched technologies such as SONET/SDH are still essential and are becoming more vital for transport and metro networks, as well as for mobile back-haul networks, as the range and demands of applications increase.

This chapter describes a proposed solution for combining the best characteristics of packet switching and circuit switching into a single architecture called fusion networking.

## 3.1 Fusion Networking Principle

Fusion Network developers have cleverly explained the principle behind this technology using an interesting analogy in [Tra12b]. The analogy compares circuit, packet and fusion networking and it is summarized below:

First of all, imagine there is a direct express train from A to B with no intermediate stops whatsoever. This kind of direct train represents the properties of circuit switching: there is minimum latency, minimum PDV and no packet (passenger) loss. This is because the passengers that get on the train at station A are guaranteed a ride all the way to their destination B without any stops. However, as it is with a network, if the express train is not even remotely full since there are only a few passengers wanting to go from A to B, the train capacity will not be used efficiently.

How can this be avoided? There must be plenty of passengers in intermediate stations wanting to go to the same destination B or any other destination on the way to B, but with circuit switching, the train ignores these passengers. With packet switching on the other hand, the train stops at every intermediate station. On the downside, at each station the passengers already onboard must leave the train and queue together with the passengers that were already at the station. After they have all been checked in they are allowed to go into the train until the seats are all occupied. As expected, train capacity is more

efficiently used since passenger flows from all stations are aggregated and seats vacated by any passenger leaving the train are likely to be occupied by new passengers joining at intermediate stations. As a consequence of improving the train capacity efficiency, the travelling time from A to B has increased greatly by introducing different delays (PDV) at each station; and some passengers may not even be able to get in the train because there are no more free seats (packet loss).

Then fusion networking appeared. Let us continue with the train analogy, but it is important to remark that this is unfeasible for actual passengers. We again have the same direct express train for *first class* passengers from A to B, and this train does not stop at any of the intermediate stations. At each intermediate station there are *second class* passengers queuing and can enter or leave the train while in speed. If the train is full at any given station (meaning capacity is used efficiently), the passengers waiting at such station will not be able to get in the train, and still the first class passengers do not lose their seats (no packet loss) and experience a minimum fixed delay (no PDV). The best of both worlds have been combined in what is known as fusion networking.

### 3.2 Fusion Networking Properties

Fusion networking as originally defined by TransPacket in [Tra12a] "combines the best from packet switching and circuit switching in a unique way ... into a fully Ethernet compliant network without the use of legacy circuit-switching techniques. The combination of the properties enabled across the network is unique in the market: high throughput, zero packet loss, ultra-low latency and ultra-low latency variation".

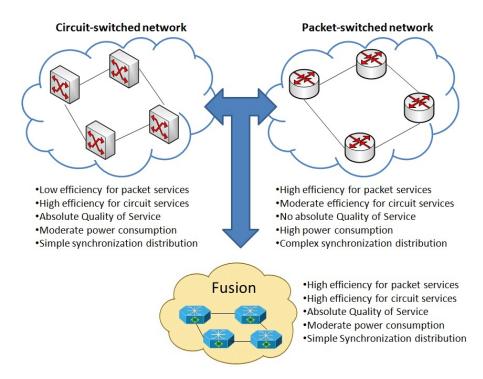

Figure 3.1: Combining the best properties from packet and circuit switching into the fusion network.

#### CHAPTER 3. FUSION NETWORKING

This way the increasing traffic demands on fixed networks (e.g., video services) and on mobile networks (e.g., Long Term Evolution (LTE) and its strict demands of synchronization and timing [Tra12b]) can be properly served. Figure 3.1 shows the best properties of packet and circuit switching, and which of those properties have been combined to create the fusion network.

But how is this accomplished? The fusion network technology divides the traffic into two *service classes* while still using the capacity of the same wavelength in a *wavelength routed optical network* (WRON) [SBS06]:

- 1. A *Guaranteed Service Transport* (GST) service class supporting QoS demands such as no packet loss and fixed low delay for the circuit-switched traffic.

- 2. A *statistical multiplexing* (SM) service class offering high bandwidth efficiency for the best-effort packet-switched traffic.

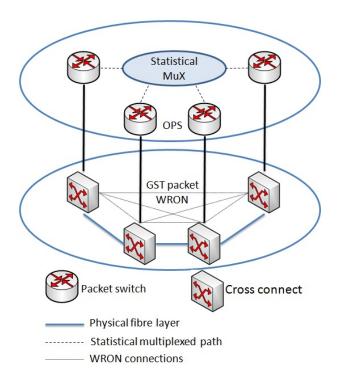

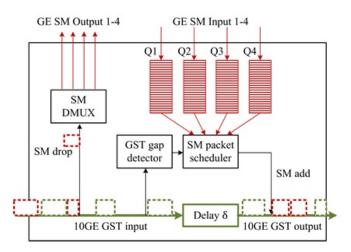

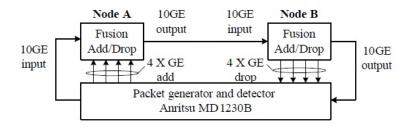

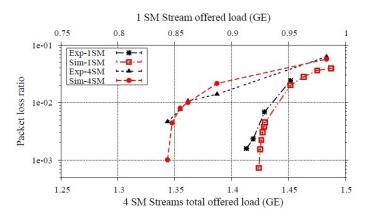

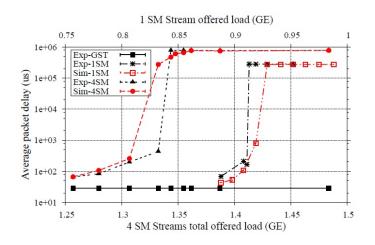

Figure 3.2: A fusion network model illustrating the efficient sharing of the physical fiber layer. The WRON can either be static (S-WRON) or dynamic (D-WRON). The OXCs and packet switches are physically co-located as separate units with a common control unit, or they can be integrated sharing physical resources in the node.