R. Luis Jalabert

# Deep Learning Based FPGA-CPU Acceleration

Master's thesis in EMECS Supervisor: Kjetil Svarstad June 2019

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Master's thesis

R. Luis Jalabert

### Deep Learning Based FPGA-CPU Acceleration

Master's thesis in EMECS Supervisor: Kjetil Svarstad June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

To all my teachers and professors

# Summary

The purpose of this project is to continue exploring new ways of accelerating sequential computer code, and finding out if the machine learning techniques available today are able to help us in this task. The core idea is trying to parallelize during run-time (in a way completely transparent to the programmer) the code that's being executed in the CPU, by snooping on the RAM-CPU communication bus, and, in case an artificial neural network considers this code to be parallelizable, it should be then converted into an FPGA module and executed on it instead. It build upon a previous project in which we used a very simple RISC CPU, called LT16x32, and created several Software applications to aid us in this enterprise. First, a parametric assembly code generator named LoopGen, allowed us to create many examples of code with different degrees of parallelism. Next, a program called LoopSim generated the neural network's input datasets by compiling the generated code and simulating its execution on the CPU. In this project we improved on the previous neural network architecture by switching from an LSTM to a convolutional model, achieving a much higher classification accuracy, while also having implemented two synthetizable hardware models of this network: one based in High Level C Synthesis (using C++ in Vivado HLS), and another one by traditional RTL means (using VHDL in Vivado). In addition, we have managed to integrate these hardware blocks with the rest of the system; namely, the CPU, memory and the instruction pre-processor, which successfully replicate the results obtained by the software model. While more work needs to be done in order to obtain a complete and more realistic system, this project paves the way for future endeavours in the quest for automatic run-time loop parallelization.

# Table of Contents

| Su                | mma     | ry      |                                                    | i   |  |  |

|-------------------|---------|---------|----------------------------------------------------|-----|--|--|

| Table of Contents |         |         |                                                    |     |  |  |

| Li                | st of [ | Fables  |                                                    | vii |  |  |

| Li                | st of l | Figures |                                                    | x   |  |  |

| Ał                | brev    | iations |                                                    | xi  |  |  |

| 1                 | Intr    | oductio | n                                                  | 1   |  |  |

|                   | 1.1     | Previo  | us Contributions                                   | 2   |  |  |

|                   | 1.2     | Thesis  | Methodology and Contributions                      | 3   |  |  |

|                   | 1.3     | Thesis  | Structure                                          | 4   |  |  |

| 2                 | Basi    | c Theo  | ry                                                 | 5   |  |  |

|                   | 2.1     | Artific | ial Neural Networks                                | 5   |  |  |

|                   |         | 2.1.1   | Multilayer Perceptron                              | 5   |  |  |

|                   |         | 2.1.2   | Convolutional Neural Networks                      | 6   |  |  |

|                   | 2.2     | Data I  | Dependencies and Automatic Loop Parallelization    | 12  |  |  |

|                   |         | 2.2.1   | Loop-level parallelism and data dependencies       | 12  |  |  |

|                   |         | 2.2.2   | Automatic Loop Parallelization                     | 14  |  |  |

| 3                 | Prev    | vious W | ork                                                | 17  |  |  |

|                   | 3.1     | Datase  | et Generation                                      | 17  |  |  |

|                   |         | 3.1.1   | LoopGen: A Parametric Assembly Loop Code Generator | 17  |  |  |

|   |      | 3.1.2       | Generating the datasets with LoopSim: from LoopGen to CPU                                                               | 9          |  |  |  |  |  |

|---|------|-------------|-------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

|   |      | 212         |                                                                                                                         |            |  |  |  |  |  |

|   |      | 3.1.3       |                                                                                                                         | 20         |  |  |  |  |  |

|   |      | 3.1.4       | LoopOracle v1: A Loop Classifier LSTM ANN                                                                               | 22         |  |  |  |  |  |

| 4 | Soft | ware A      | rchitecture and Implementation 2                                                                                        | 23         |  |  |  |  |  |

|   | 4.1  | LoopC       | bracle v2: Improving on the previous Loop Classifier ANN 2                                                              | 23         |  |  |  |  |  |

|   |      | 4.1.1       | Training a Pytorch CNN                                                                                                  | 24         |  |  |  |  |  |

|   | 4.2  | Lower       | ing the abstraction level: transforming a PyTorch CNN to C++ code 2                                                     | 26         |  |  |  |  |  |

| 5 | Har  | dware A     | Architecture and Implementation 3                                                                                       | 81         |  |  |  |  |  |

|   | 5.1  | Vivado      | HLS implementation                                                                                                      | 81         |  |  |  |  |  |

|   |      | 5.1.1       | Unoptimized Solution 3                                                                                                  | 32         |  |  |  |  |  |

|   |      | 5.1.2       | Optimizing Data-types                                                                                                   | 33         |  |  |  |  |  |

|   |      | 5.1.3       | Optimizing the Data-Flow                                                                                                | 34         |  |  |  |  |  |

|   |      | 5.1.4       | Pragma-based Parallelization                                                                                            | 6          |  |  |  |  |  |

|   |      | 5.1.5       | Increasing throughput with Array Partitioning                                                                           | 88         |  |  |  |  |  |

|   | 5.2  | VHDL        | implementation                                                                                                          | <u>8</u> 9 |  |  |  |  |  |

|   |      | 5.2.1       | VHDL challenges   3                                                                                                     | <u>9</u>   |  |  |  |  |  |

|   |      | 5.2.2       | Loop Pipelining                                                                                                         | 3          |  |  |  |  |  |

|   |      | 5.2.3       | Controlling the CNN with a simple FSM 4                                                                                 | 4          |  |  |  |  |  |

|   | 5.3  | I I I       |                                                                                                                         |            |  |  |  |  |  |

|   |      | 5.3.1       | Detecting Loops with a FSM                                                                                              | 5          |  |  |  |  |  |

|   |      | 5.3.2       | Implementing the FSM in Hardware    4                                                                                   | 17         |  |  |  |  |  |

|   | 5.4  |             |                                                                                                                         |            |  |  |  |  |  |

|   |      | 5.4.1       | VHDL System         4                                                                                                   | 8          |  |  |  |  |  |

|   |      | 5.4.2       | HLS System                                                                                                              | 9          |  |  |  |  |  |

| 6 | Disc | ussion      | 5                                                                                                                       | 53         |  |  |  |  |  |

|   | 6.1  | PyTorc      | h Neural Network                                                                                                        | 53         |  |  |  |  |  |

|   | 6.2  | C++ CNN     |                                                                                                                         |            |  |  |  |  |  |

|   | 6.3  | Vivado      | $) HLS CNN \dots \dots$ | 54         |  |  |  |  |  |

|   | 6.4  | VHDL        | CNN                                                                                                                     | 54         |  |  |  |  |  |

|   | 6.5  | Instruc     | tion pre-processor and System Integration 5                                                                             | 55         |  |  |  |  |  |

|   | 6.6  | HLS vs VHDL |                                                                                                                         |            |  |  |  |  |  |

| 7 | Con  | clusion     | 5                                                                                                                       | 57         |  |  |  |  |  |

|   | 7.1  | Future      | Work                                                                                                                    | 57         |  |  |  |  |  |

|   | 7.2  | Conclusions |                                                                                                                         |            |  |  |  |  |  |

### Bibliography

# List of Tables

| 5.1 | First solution hardware utilization                          | 32 |

|-----|--------------------------------------------------------------|----|

| 5.2 | Number representation accuracy                               | 33 |

| 5.3 | Second solution hardware utilization                         | 34 |

| 5.4 | Third solution hardware utilization                          | 36 |

| 5.5 | Fourth solution hardware utilization                         | 36 |

| 5.6 | Hardware utilization of the different parallelization levels | 37 |

| 5.7 | Loop limits and clock cycles                                 | 42 |

| 5.8 | Bit-precision and tool comparison                            | 50 |

| 61  | HLS vs VHDL hardware utilization                             | 55 |

| 0.1 |                                                              | 55 |

# List of Figures

| 1.1 | The Basic Blocks of the proposed Hardware                                  | 3  |

|-----|----------------------------------------------------------------------------|----|

| 2.1 | Graphical representation of a multi-layer fully connected ANN              | 6  |

| 2.2 | Graphical representation of a CNN. –Source: [18]                           | 7  |

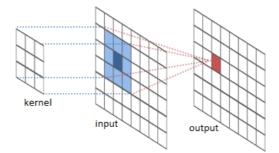

| 2.3 | Convolution high level visualization. –Source: [16]                        | 8  |

| 2.4 | Convolution example                                                        | 9  |

| 2.5 | Rectifier function                                                         | 10 |

| 2.6 | ReLU example                                                               | 10 |

| 2.7 | MaxPool example                                                            | 11 |

| 2.8 | Loop Pipelining                                                            | 15 |

| 3.1 | LoopSim Data Flow                                                          | 19 |

| 3.2 | Graphical representation of the first 400 vectorized instructions executed |    |

|     | by an IIR filter                                                           | 21 |

| 4.1 | Graphical representation of the CNN architecture                           | 23 |

| 4.2 | Training and validation loss                                               | 26 |

| 4.3 | Forward function                                                           | 30 |

| 5.1 | Scheduling of the first convolution innermost loop                         | 32 |

| 5.2 | Number representation accuracy                                             | 33 |

| 5.3 | Merged convolution+ReLU+MaxPool loop C++ code                              | 35 |

| 5.4 | Percentage of Hardware Utilization for different levels of parallelism     | 37 |

| 5.5 | Clock cycles for different levels of parallelism                           | 37 |

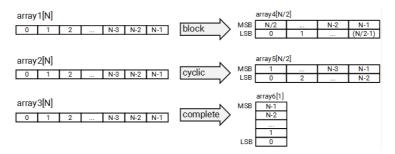

| 5.6 | Array Partitioning                                                         | 38 |

| 5.7 | Assumed program behaviour with two loops                                   | 46 |

|     |                                                                            |    |

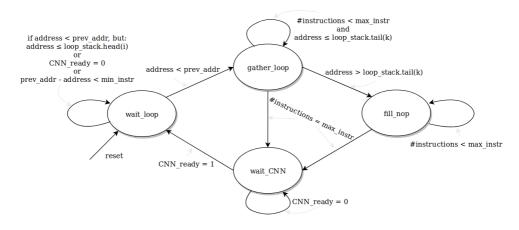

| 5.8  | Pre-processor Finite State Machine | 46 |

|------|------------------------------------|----|

| 5.9  | FSM simulation waveform: VHDL vs C | 47 |

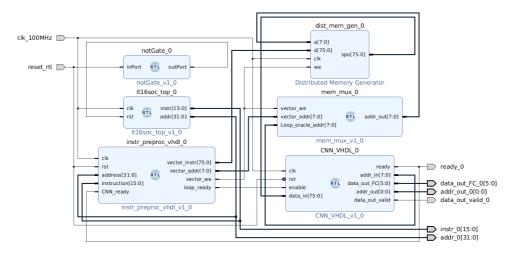

| 5.10 | VHDL System                        | 48 |

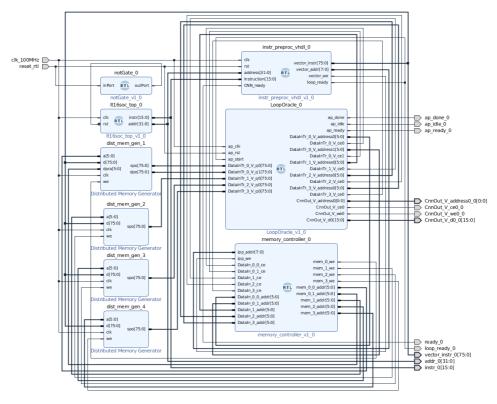

| 5.11 | HLS System                         | 49 |

# Abbreviations

| ANN    | = | Artificial Neural Network             |  |  |  |

|--------|---|---------------------------------------|--|--|--|

| CNN    | = | Convolutional Neural Network          |  |  |  |

| CPU =  |   | Central Processing Unit               |  |  |  |

| DOP    | = | Degree Of Parallelism                 |  |  |  |

| DSP    | = | Digital Signal Pprocessor             |  |  |  |

| FC     | = | Fully Connected                       |  |  |  |

| FIR    | = | Finite Impulse Response               |  |  |  |

| FPGA   | = | Field-Programmable Gate Array         |  |  |  |

| FSM    | = | Finite State Machine                  |  |  |  |

| GPU    | = | Graphics Processing Unit              |  |  |  |

| HLS    | = | High Level Synthesis                  |  |  |  |

| IC     | = | Integrated Circuit                    |  |  |  |

| IIR    | = | Infinite Impulse Response             |  |  |  |

| IP     | = | Intellectual Property                 |  |  |  |

| LSTM   | = | Long Short-Term Memory                |  |  |  |

| LUT    | = | Look-Up Table                         |  |  |  |

| OpenCL | = | Open Computing Language               |  |  |  |

| RAM    | = | Random Access Memory                  |  |  |  |

| RAR    | = | Read After Read                       |  |  |  |

| RAW    | = | Read After Write                      |  |  |  |

| ReLU   | = | Rectified Linear Unit                 |  |  |  |

| RISC   | = | Reduced Instruction Set Computer      |  |  |  |

| ROM    | = | Read-Only Memory                      |  |  |  |

| RTL    | = | Register Transfer Language            |  |  |  |

| PC     | = | Personal Computer, or Program Counter |  |  |  |

| SIMD   | = | Single Instruction Multiple Data      |  |  |  |

| VHDL   | = | VHSIC Hardware Description Language   |  |  |  |

| WAR    | = | Write After Read                      |  |  |  |

| WAW    | = | Write After Write                     |  |  |  |

# Chapter

# Introduction

The concept of using co-processors as hardware accelerators for mainstream computers dates back to the late 70's, and enjoyed an increased popularity in the subsequent decades. The first version of such co-processors was Intel's 80387: launched in 1980 [20], it was a dedicated floating-point arithmetic IC (Integrated Circuit) which was fully compliant with IEEE's 754-1985 standard, and was later embedded in Intel's 80486DX processor. In more recent years, we have seen a dramatic increase in the use of other kinds of hardware as accelerators, such as GPUs, DSPs and FPGAs, which, with the aid of programming languages such as OpenCL or CUDA, can be utilized to off-load some of the most computationally intensive work from the CPU. In addition, the stagnation in the increase of clock frequencies, combined with the transition to multi-threaded, multi-core processor designs implies that sequential code will no longer achieve the historical performance gains from advances in technology that it has obtained in the past [19]. The "Dark silicon problem" poses new challenges as well as new opportunities to IC designers: System-on-Chip designs, containing many different, specialized accelerators can take advantage of this "extra" silicon, dynamically turning on and off these parts of the chip as needed. All of this points to an apparently unavoidable necessity of changing the sequential-programmingparadigm to a parallel one. However, many factors play against designers when trying to exploit these parallel technologies: Ahmdals law imposes a harsh theoretical upper-limit to the achievable performance speed-up (even when only a small fraction of the code is sequential in nature); the continued use of sequential legacy code that was written years before the advent of mainstream parallel computers; and the sharp increase of the difficulty in writing well-optimized parallel code, which requires experienced (and often expensive) programmers to make efficient use of these circuits.

Another idea, which has proven itself very successful in mainstream CPUs (and other

kinds of ICs), is the idea of *learning* from previous executions of code. After all, if a computer is repeating the same thing over and over again, wouldn't it be clever to try to use this information when the CPU steps again into the same part of the program? And thus, the idea of space and time locality led to the implementation of ever-growing cache memories, branch predictors alleviated the burden of jumping back to the same program address, while speculative execution and simultaneous multi-threading made good use of otherwise idling units.

But what if CPUs were able to learn *more* from a program, what if they could *adapt* themselves to the current program execution? The USA' Defense Advanced Research Projects Agency (DARPA) has recently invested 1.5 billion USD in a project that aims to develop hardware and software that can be reconfigured in real time, based on the kind of data being processed, adapting the computing architecture for the workload in milliseconds [13]. The recent advances in machine learning and in deep learning in particular along with its astonishing results (often surpassing human capabilities in a growing spectrum of fields), poses the question of whether this technology could also be used to increase the performance of a CPU. It's certainly not a crazy idea to use neural networks in this way, neither is it new: today's most advanced x86 CPU architecture, AMD's "Zen", utilizes a Perceptron-based Artificial Neural Network (ANN) to implement its branch predictor [8].

### **1.1 Previous Contributions**

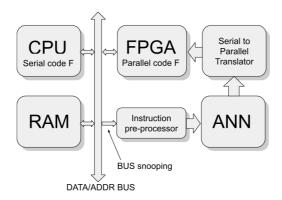

All these ideas led to my previous specialization project at NTNU, a project that proposed a novel architecture which could help solve the aforementioned problems. The concept behind it, is in its essence quite simple: embedding in a single IC a CPU, an ANN, and real-time reconfigurable logic (such as an FPGA). The ANN should then detect serial code (at run-time, by snooping on the CPU-memory bus) and accelerate the CPU by reprogramming a parallel version of this code in the FPGA. Then, the next time the CPU tries to execute this code, it will be done by the faster, and more efficient FPGA-based accelerator, possibly freeing up the processor to attend to other tasks. Rather than having a plethora of idling, highly specialized dedicated IP cores (which is the case in today's SoC architectures), a re-configurable circuit could lead to a faster, more powerful and efficient use of the same silicon area. The proposed architecture is illustrated in figure 1.1.

The accelerators running on the FPGA should be dynamically adapted to the code running on the CPU at any given time. Due to limitations in both time and human resources, the specialization project was limited to generating the training data set and developing an ANN that would detect parallelizable code and possibly extract useful features from it. To deal with the extreme complexity of this task, we only considered loop-level parallelism (as opposed to task-level parallelism), with loops fixed in length and with an upper-bound

Figure 1.1: The Basic Blocks of the proposed Hardware

in the number of instructions per loop, while also avoiding nested loops. The focus on loop acceleration comes from the fact that programs spend a large percentage of their execution time in a small portion of their code (commonly known as the 90/10 rule) [1], and that most of this code is located within loop constructs. Additionally, not only is hardware loop parallelization completely transparent to the programmer, but it also allows parallelization of loops in cases where compilers fail to do so. The project made use of a very simple CPU called LT16x32 which was developed for academic purposes by the Chair of Electronic Design Automation of the Technische Universität Kaiserslautern. This is a uni-core, 16-bit, 3-stage pipeline, 20 instruction, in-order and non-speculative execution CPU. RAM and ROM can be conveniently accessed every clock cycle, therefore avoiding the stalling problems associated with memories running at slower clock speeds than the processor (thus requiring no cache memory). Even though these assumptions can be dangerously unrealistic, all these simplifications were a necessity that allowed us to focus on the core problems at hand, and if successful, future work could improve on the idea by lifting some or all of those restrictions.

### 1.2 Thesis Methodology and Contributions

This Master's Thesis builds upon the previously mentioned project, by adopting the same hypothesis, training data-sets (although it takes a different approach on the design of the ANN) and takes it a step further by implementing this neural network not only in software but also in hardware (as well as implementing a hardware block of the bus snooping unit), integrating it with the rest of the system. Additionally, this was done in parallel with another important goal: exploring one of today's mainstream high-level synthesis tools (Vivado HLS, which synthesizes a subset of the C, C++ and SystemC languages),

and comparing its results with traditional RTL tools (Vivado, which supports VHDL development as well as integration of C and VHDL IP blocks). Furthermore, creating a functioning hardware Neural Network was a separate goal in itself. The working methodology was mostly experimental, but once the software ANN was finalized, this defined a golden model to which we were able to the compare results. Verification of the hardware modules was performed by simulating and comparing the outputs of the system to the outputs generated by the software model, for the same given input. A good amount of previous knowledge, along with the study of related articles, HLS tutorials, etc., provided a sufficient basis on which a first working model of the whole system (with the exception of the serial to parallel code translator) was successfully developed.

As a result, this work's contribution can be summarized as follows:

- Development of a PyTorch Loop-classifying Artificial Neural Network (ANN).

- Implementation of the ANN in C++.

- Synthetizable HLS version of the ANN.

- Synthetizable VHDL version of the ANN.

- Synthetizable HLS version of the instruction pre-processor.

- Synthetizable VHDL version of the instruction pre-processor.

- Synthetizable system integration of the LT16x32 with the instruction pre-processor, memory array controllers and ANN.

- Comparison of HLS vs RTL development of the same hardware blocks.

- Discovery of bugs in the Vivado HLS tool, as well as a discussion of its current limitations.

### **1.3 Thesis Structure**

The rest of this document is organized as follows: chapter 2 discusses the theoretical background of ANNs as well as loop-level parallelism topics, while chapter 3 describes the pertaining elements of the previous project's work. Chapter 4 discusses and presents the results on the ANN's architecture and implementation of the software side, while chapter 5 does the same for the hardware implementations of the ANN, the instruction pre-processor and their integration into a system. The discussion of the results obtained so far is presented in chapter 6. Finally, chapter 7 points out recommendations towards possible future work, and concludes the work. Chapter 2

# **Basic Theory**

This project focuses on the improvement of an ANN architecture designed in a previous project (while still using the same datasets), as well as its hardware implementation in both HLS and RTL. The previous project on which this Thesis is based upon, will be further described in the next chapter.

### 2.1 Artificial Neural Networks

ANNs are digital structures loosely inspired on biological brains, consisting on many copies of a basic building block called *neuron* or *perceptron*. Their excellent ability to recognize patterns made them an extremely appealing choice for our ideas on runtime parallelizable loop detection. Even though our initial assessment on Recurrent Neural Networks (such as the LSTM) did not prove to be accurate, further investigation and testing has proven that CNNs have an outstanding performance when applied to our classification problem, at least in the terms that were previously decided upon. But before we move forward on explaining CNNs, we'll begin by explaining the simplest type of neural network: the multilayer perceptron.

### 2.1.1 Multilayer Perceptron

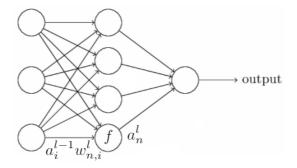

A multilayer perceptron is a type of ANN which consists of many neurons arranged in multiple layers, with the neurons of the  $l^{th}$  layer applying an affine transformation to the previous  $(l-1)^{th}$  layer neuron's outputs, and mapped through some activation function [11]. Neurons arranged in this way are said to be *fully connected* (FC).

Mathematically, in the case of an FC feed-forward network, these outputs can be modelled as follows:

$$a_{n}^{l} = f\left(\sum_{i=1}^{S^{l}} w_{n,i}^{l} a_{i}^{l-1} + b_{n}^{l}\right)$$

(2.1)

where  $w_{n,i}^{l}$  is weight of the  $i^{th}$  synapse connected to the input of the  $n^{th}$  neuron in the  $l^{th}$  layer;  $b_n^{l}$  is a bias term; f is the activation function, and  $S^{l}$  is the number of synapses connected to each neuron in the  $l^{th}$  layer. It could be graphically represented as shown in figure 2.1:

Figure 2.1: Graphical representation of a multi-layer fully connected ANN

The activation functions used in ANNs (such as the sigmoid or rectified linear unit) provide them with the non-linearities required so that they can learn any kind of arbitrary function. Among many other factors, the current success of deep learning can be attributed to some variants of these networks, the most prominent of them being the CNN, which will be described in the following subsection.

To train these ANNs, a large amount of training data is required, among their associated *targets* (i.e., the *desired output* for each given input). This training is done iteratively by measuring the error between the network's output for a certain input and the associated target value, by means of a *cost function*, and modifying the previously mentioned weights and biases accordingly, in order to minimize this difference.

#### 2.1.2 Convolutional Neural Networks

#### Introduction

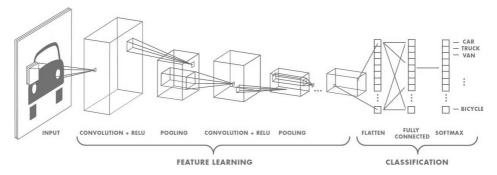

A *Convolutional Neural Network* (CNN) is a class of deep neural networks, most commonly designed to recognize image patterns directly from pixel representations (i.e., from two or three dimensional matrices) with minimal or no pre-processing required.

These networks were inspired in a connectivity pattern that resembles the organization of the brain's visual cortex. Each neuron responds to signals in a restricted region of the visual field known as the *receptive field*.

Like most neural networks, they are trained with some version of the back-propagation algorithm, that is, cleverly exploiting the chain-rule of differentiation, but since the hard-ware implementation of a CNN in this project does not deal with their training, this will not be further discussed; however, the interested reader can find more information about the subject in sources such as [11].

A typical CNN consists of an input and output layer, as well as multiple hidden layers sandwiched in between. The hidden layers of a CNN consist of convolutional layers (generally composed of multiple *channels* per layer), ReLU activation layers, pooling layers, and FC layers, all of which will be explained later. The following image shows the architectural representation of such typical CNN:

Figure 2.2: Graphical representation of a CNN. -Source: [18]

CNNs differ from the classic multilayer perceptrons mainly in their architecture: instead of connecting all neurons in one layer to all neurons in the following layer, and all connections having a different weight, neurons are instead connected locally from one layer to the next using the same weights, in the form of a *convolution* operation, hence its name. Strictly speaking, the actual mathematical operator used in CNNs is the *valid-crosscorrelation*. This operation is what gives the CNN its translation invariance characteristics.

The convolution operation can be interpreted as an FIR filter, but in contrast to traditional algorithms where these filters are hand-engineered, the network *learns* the filter's coefficients, also referred to as *kernel*. This independence from prior knowledge and human effort in feature design is not only a major advantage, but most likely a necessity in what seems an unattainable task for humans, considering the complexity of the filters in today's extremely deep neural networks.

CNNs have wide applications in many fields, not only in image recognition, but also in image and video classification, segmentation, natural language processing and many other fields. As it will be shown later in image 3.2, our input data can be interpreted as 2D black and white images, where time is nothing more than another spatial variable. It is therefore not a wild idea to think that CNNs could produce satisfactory results, and in fact, this was one of the questions that I asked myself in the previous project's conclusion [14], where I stated that "*perhaps* (...) convolutional networks could achieve better results". And indeed, they did.

#### **Convolution Layer**

Each convolutional neuron processes data only for its receptive field. Although it's possible to use traditional multilayer perceptrons to learn features and classify data, it's not exactly practical when it comes to images, since a very high number of neuron connections (weights) would be necessary (even in a shallow architecture) due to the inmense input sizes associated with images. For example, an FC layer for a very low resolution, black and white picture of size 320 x 200 pixels, would require 64000 weights **for each neuron** in the second layer. The convolution operation solves this problem by drastically reducing the number of parameters; e.g., by using a kernel of size 3x3 with 3 output channels, only 27 learnable parameters are required (or 30, if we consider the biases), regardless of the image's size.

The convolutional layer can be better understood as an FIR filter, with which most electrical engineers are more accustomed. On a high level, this operation can be better visualized in the following picture:

Figure 2.3: Convolution high level visualization. -Source: [16]

Each output is the sum of elements of the Hadamard product (i.e., entry-wise product) between the kernel and the tile composed of a window surrounding the input element in the input matrix. This process is repeated for all the input's elements to produce the final output of the convolution. In the case that no padding is used (as is the case of our project) the convolution product is only given for points where the signals overlap completely; values outside the signal boundary have no effect (i.e., it's a *valid* convolution, and not

*full*). An horizontal or vertical stride can be defined, so that this window moves across the input jumping  $n_{stride}$  positions in the horizontal or vertical axis. A dilation factor can also be defined, and this dilates the input window so that it takes non-contiguous values. FIR filters as we know them, have a stride and dilation value of 1, which is generally the default value for CNNs and it's the value used in our design.

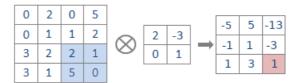

Let's consider an example by convolving a 4x4 matrix with a 2x2 kernel, as shown in the following figure:

Figure 2.4: Convolution example

The weighted sum for the element highlighted in the output is:

$$o[3][3] = (2 \cdot 2) + (1 \cdot [-3]) + (5 \cdot 0) + (0 \cdot 1) = 1$$

If there is more than one input channel, the output is produced by convolving each channel with its own 2D kernel and adding the results to the same output value; analogously, if there are more than one output channel, the process is repeated, using the same input values but different kernels, for each output channel.

In the case that the input has dimensions  $(C_{in}, H, W)$  and the output has dimensions  $(C_{out}, H_{out}, W_{out})$ , the output values can be precisely described as [5]:

$$out(C_{out_j}) = bias(C_{out_j}) + \sum_{k=0}^{C_{in}-1} weight(C_{out_j}, k) \star input(k)$$

(2.2)

where  $\star$  is the valid 2D cross-correlation operator previously explained, C denotes the number of channels, H is the height of the input planes, and W is their width.

#### **Rectified Linear Unit Layer**

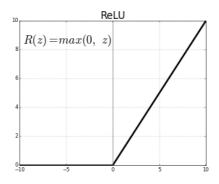

In the context of ANNs, the rectifier is an activation function defined as the positive part of its argument, i.e.:

$$R(z) = max(0, z) \tag{2.3}$$

where z is the input to a neuron.

This is also known as a ramp function which is analogous to a half-wave rectifier, and can be visualized in the following figure:

Figure 2.5: Rectifier function

The rectifier is, as of today, the most popular activation function for deep ANNs [17], not only because it's much simpler to calculate, but because it helps reduce the vanishing gradient problem: given that the derivative of this function for positive numbers is always equal to one, the successive product of derivatives that appears due to the chain rule, does not decrease the gradient in earlier layers. Moreover, the value of this derivative does not decrease as the weighted sum input z increases, which is the case with the sigmoid or with the hyperbolic tangent. In 2011, Xavier Glorot et al [9] demonstrated that using this unit as an activation function enables better training of deeper networks, compared to the other commonly used functions. Following our previous example, if we apply the ReLU layer to the output produced by the convolution, we'd have the following:

Figure 2.6: ReLU example

There are some variations of this function, such as the leaky-ReLU, which has a slope slightly greater than zero for negative values, instead of exactly equal to zero, but it hasn't been used in our project and will therefore not be further discussed.

#### **Pooling Layer**

Usually in a CNN architecture, a *Pooling layer* is inserted between successive convolutional layers. Its function is to progressively reduce the size of the feature maps, in order to reduce the amount of free parameters and computation in the network, and therefore to also control overfitting [4]. The Pooling Layer operates independently on every channel of the input and resizes it, using some fixed function, typically the *max* function (although it's possible to use *avg*, *min*, L2-norm, etc.). The most common form is a pooling layer with kernel size 2x2, with a stride of 2 along both horizontal and vertical directions, discarding 75% of the activations from the previous layer. Our architecture uses a 2x4 kernel size, with a horizontal stride of 2 and vertical stride of 4, discarding 87.5% of the activations.

In the case that the pooling function is max, the input has dimensions (C, H, W), the output has dimensions  $(C, H_{out}, W_{out})$  and the kernel has size (kH, kW), the output values can be precisely described as [5]:

$$out(C_j, h, w) = \max_{\{m=0,\dots,kH-1\}} \max_{\{n=0,\dots,kW-1\}} input(C_j, stride_x \cdot h + m, stride_y \cdot w + n)$$

(2.4)

If we apply this to our original example, with a 2x2 kernel size and stride, we'd obtain the following output:

Figure 2.7: MaxPool example

Mathematically, for the highlighted values, the output value is:

$$out(1,1) = \max\{2,1,5,0\} = 5$$

(2.5)

#### **Fully Connected Layer**

As it was shown in figure 2.2, a typical CNN consists of a sequence of convolutional, ReLU and pooling layers, after which there is a flattening operation and one or multiple FC layers. The flattening operation is nothing more than re-arranging the output tensor (3D matrix) from the previous convolutional layer into a single vector. This flattened output is then connected to an FC layer which was already described in section 2.1.1. The function of these FC layers is to perform classification based on the features extracted by the previous convolutional layers. Typically, the last FC layer uses a softmax activation function, which outputs a probability for each of the classification labels the model is

trying to predict. However, in our project we chose to use a ReLU activation function for two reasons: first, it works just fine. Second, it's much less complex and easier to calculate, since the ReLU function doesn't have to deal with exponential functions.

### 2.2 Data Dependencies and Automatic Loop Parallelization

#### 2.2.1 Loop-level parallelism and data dependencies

In order to define which high-level characteristics we want the ANN to extract from the code, we must first investigate the *meaning* of loop-level parallelism. As the term itself implies, *Loop-level parallelism* is a form of parallelism that seeks to extract certain tasks from loops which are in general independent from previous executions of the loop body, or in which the data dependencies involved allows the execution of these tasks in parallel or in a pipelined fashion. In case such tasks exist, there are various techniques that can be applied to decrease the execution time, for example: loop-pipelining, loop-unrolling, loop-merging and loop-splitting [6], which are currently being used in Vivado HLS. We will later present the first two of these techniques, since they have been extensively used in our ANN implementations.

#### Data dependencies in sequential statements

We have previously mentioned data dependencies, but we haven't discussed them yet, so let's introduce a few useful definitions. Given two consecutive, sequential statements  $S_1$  and  $S_2$ , we define the following dependencies [10]:

- True (Flow, RAW) Dependence: S1 writes to a location later read from by S2.

- Anti Dependence (WAR): S1 reads from a location later written to by S2.

- Output Dependence (WAW): S1 and S2 write to the same location.

- Input Dependence (RAR): S1 and S2 read from the same location.

To preserve the sequential behaviour of a loop after it has been parallelized, the only kind of dependence that must be sequentially preserved is *Flow Dependence*; the others can be dealt with by making copies of the involved variables for each parallel process (this technique is known as *privatization*). Input dependencies are not truly dependencies, since input-dependent statements can be freely reordered without changing the result.

#### **Dependencies in loops**

When analyzing loops, we can distinguish between two types of dependencies:

- Loop-carried dependence

- Loop-independent dependence

In the case of loop-independent dependence, loops do not present dependence between iterations; therefore each iteration may be performed in parallel. Let's look at an example code for a 2-tap FIR filter:

```

#Iteration independent loop example:

for (int i = 1; i < n; i ++) {

S1: tmp0 = x[i-1] * tap0;

S2: tmp1 = x[i] * tap1;

S3: out[i] = tmp0 + tmp1;

}

```

As we can see, there is a loop-independent, true dependence between (S1,S3) and (S2,S3), but iterations of the loop are independent of each other, therefore allowing for the execution of each iteration in a parallel or distributed manner.

In loop-carried dependencies however, statements in an iteration of a loop depend on the results of a previous iteration of the loop.

Let's take a look at an example of code which can be used for calculating the first n values of the Fibonacci sequence:

```

#Loop carried dependence example:

a[0] = 0;

a[1] = 1;

for (int i = 2; i < n; i ++) {

S1: a[i] = a[i - 1] + a[i - 2];

}

```

In this case, it is clear that the statement S1 depends on the two previous executions of S1, and therefore cannot be distributed across different processing units.

#### Metrics of parallelism in loops

In our previous project, we had defined a metric with which we could determine the *Degree Of Parallelism* present in a loop, as simply 1 or 0 (parallelizable or non-parallelizable), depending on the "kind" of loop (these kinds will be described in the next chapter). Given that our previous ANN architecture was not exactly successful in determining the DOP of a loop, introducing a more complex and precise definition would not only have taken some time to implement, but after all, if an ANN is unable to detect parallelism at this coarse level, then the prospects of detecting parallelism at a more refined level would be even lower. For these reasons, we have decided to keep this high-level definition, rather than trying to find the exact proportion of loop-carried dependent instructions.

### 2.2.2 Automatic Loop Parallelization

As we previously mentioned, there are various techniques that can be used to automatically parallelize loops, some of which will be discussed next.

#### **Loop Pipelining**

Pipelining allows operations to be computed concurrently, that is, it's not necessary to wait for the completion of all operations before the next one can start. In a loop, this means that operations can be overlapped between consecutive executions of the loop body. Let's suppose we have the following loop:

```

#Loop with dependencies:

for (int i = 0; i < N-1; i ++) {

S1: a = x[i] * y[i];

S2: b = f(a);

S3: c = g(b);

}

```

where f(a) is some operation that depends on the result of a, etc. (if there were no dependencies, all three operations could be executed in parallel). Without loop pipelining, we would have the following execution pattern: S1(i=0), S2(0), S3(0), S1(1), S2(1), S3(1), S1(2), S2(2), S3(2), etc, which would take  $3 \cdot N$  clock cycles to complete. In contrast, when pipelining the loop, we can use the hardware that computes S2 and S3 in parallel with S1, allowing for the following execution pattern: S1(0), S1(1) + S2(0), S1(2) + S2(1) + S3(0), S1(3) + S2(2) + S3(1), etc., which would take N + 2 clock cycles.

| Non-pipelined |           |                  |           |            |            |            |            |                  |  |

|---------------|-----------|------------------|-----------|------------|------------|------------|------------|------------------|--|

| S1            | \$2       | \$3              | \$1       | <b>S</b> 2 | <b>S</b> 3 | \$1        | \$2        | S3               |  |

| Pipelined     |           |                  |           |            |            |            |            |                  |  |

| S1            | S1        | <mark>S</mark> 1 | S1        | S1         | <b>S</b> 1 | <b>S</b> 1 | S1         | <mark>S1</mark>  |  |

|               | <b>S2</b> | <b>S2</b>        | <b>S2</b> | <b>S2</b>  | <b>\$2</b> | <b>S2</b>  | <b>S2</b>  | <mark>\$2</mark> |  |

|               |           | <b>S</b> 3       | S3        | S3         | <b>S</b> 3 | <b>S</b> 3 | <b>S</b> 3 | S3               |  |

Graphically, this can be represented as follows:

Figure 2.8: Loop Pipelining

In the case shown, pipelining the loop results in hardware roughly three times as fast (when N >> 1), at the expense of slightly more complex steering and control logic, more execution units (in case these instructions share some) and perhaps a few extra registers.

#### Loop Unrolling

Loop unrolling consists of making multiple copies of the loop body, and instead of using the same hardware in different clock cycles, copies of the same hardware are instantiated so that operations can be performed in parallel, if allowed by data dependencies and available resources. For instance, if we consider the following loop:

```

#Rolled Loop:

for (int i = 0; i < 3; i ++) {

z[i] = x[i] * y[i];

}

```

leaving the loop rolled would require 4 clock cycles to complete, but if we partially unroll the loop with a factor of two, we end up with the following loop instead:

```

#Partially unrolled Loop:

for (int i = 0; i < 1; i ++) {

z[i] = x[2*i] * y[2*i];

z[i] = x[2*i + 1] * y[2*i + 1];

}

```

cutting the execution time in half.

If instead we unroll the loop completely, we end up with the following code:

```

#Completely unrolled Loop:

z[0] = x[0] * y[0];

z[1] = x[1] * y[1];

z[2] = x[2] * y[2];

z[3] = x[3] * y[3];

```

This would complete all the operations in a single clock cycle, at the expense of four times the hardware. It should be noted that memory accesses are also multiplied by the same factor, so care should be taken when applying this technique: if too many operations in a loop require memory accesses, then the speed limitation will be given by the available memory channels, and in the case of accessing external DRAM, the benefits of unrolling the loop won't be perceivable. In contrast, if a loop is compute-intensive and not many memory accesses are required, the improvements can be quite substantial. In the case of FPGAs, it's possible to achieve sizable speed-ups even when memory accesses are numerous, since they contain distributed memory blocks all across the chip.

Alas, given the short time available for this project, a hardware block that transforms the detected loops into parallel versions was not be implemented, but some ideas were discussed. In particular, columns of execution units, each unit implementing some of the CPU instructions could be connected to the next column through reconfigurable steering logic and registers, while a reconfigurable control unit would implement the execution sequence and branching instructions. And so, after a loop is detected, the array would be populated with the instructions in the loop body, trying to parallelize as many instructions as possible, while complying with the data dependencies.

# Chapter 3

# Previous Work

As it was already mentioned, this project builds upon the work done for a previous project called *Deep Learning Based CPU Acceleration* [14], and therefore, in order to understand and write a self-contained Thesis, it is necessary to describe some of the work previously done. The main goal of that project was to generate training datasets along with the desired training targets (i.e., degree of parallelization, head and tail of the loop, trip count, etc.), as well as the design and training of an ANN able to detect these parameters. For this purpose, various tools were developed, which will be briefly described next.

### 3.1 Dataset Generation

### 3.1.1 LoopGen: A Parametric Assembly Loop Code Generator

In order to train an ANN capable of recognizing parallelizable loops, we first had to create a dataset on which we could train it. Given that the CPU we were (and still are) working with was an in-house development, there exists no C-compiler for it and we were therefore forced to come up with our own assembly programs. Since the number of training examples required is in the order of hundreds (if not thousands) we came up with the idea of generating parametrizable assembly loops, in which the kind of loop, registers used, number of memory arrays, number of iterations, etc., are completely parametrizable and so, by randomizing these parameters (within certain restrictions), we were able to come up with hundreds, or even thousands of different assembly programs. Making it possible to change the registers was deemed necessary since we didn't want the ANN to be biased by arbitrarily chosen registers which it could learn to associate with certain kinds of loops. This way of creating different assembly programs is, in fact, nothing more than a clever trick to perform *data augmentation* [12]: a machine learning technique which consists in artificially inflating the training set with label-preserving transformations.

LoopGen consisted of three C++ functions that will be briefly described in the following paragraphs.

The first function, called "instr\_str", simply takes the type of instruction and its parameters (such as destination register, source registers, labels, modes, etc.) and returns a string with the correct assembly syntax for the given instruction. This is necessary to make possible the parametrization described before while keeping the registers and labels consistent with the desired behaviour of the assembly program.

The second and third functions, called "loop\_independent" and "loop\_dependent" respectively, take a plethora of parameters, such as loop identifier, kind of loop, temporary registers, array registers, array names, etc., and returns a string containing fully working assembly code automatically generated with those parameters.

The function "loop\_independent" creates four different kinds of loops that were deemed to be fully parallelizable. The first kind, "add\_constant", generates a program that adds a random constant value between -128 and 127 to the elements of the given arrays. The second kind, "add\_arrays" generates code that adds two or more arrays and stores the result in the first of those arrays. The third kind of loop, "swap\_arrays", generates a program that, as the name suggests, swaps pairs of arrays. The fourth and last kind of parallelizable loop, "fir\_Filter" creates a parametric, fully functional FIR filter for a CPU that does not possess a multiply instruction; an idea inspired on the work by Y. C. Lim and B. Liu. In [15], they demonstrated that an FIR filter with very small frequency response ripple magnitude can be realized using two power-of-two terms for each coefficient value. This allowed us to implement a fast filter using shifting instructions instead of multiplications, by hard-coding each filter coefficient into the immediate values of the lsr (Logic Shift Right) instructions themselves.

Analogously, the function "loop\_dependent" creates four different kinds of loops that were deemed to be non-parallelizable. The first kind of iteration-dependent loop, "fibonacci" returns a program that calculates Fibonacci-like sequences, given by the recurrence formula:

$$f[n] = \sum_{i=1}^{N} f[n-i]$$

with f[0] = f[1] = ... = f[N] = 1. It writes the sequence in an array, and when N is equal to 2, it reduces back to the classic Fibonacci sequence. The second kind, "dep\_array\_sum", returns a program that calculates the sum of elements in one or many arrays, with each successive element being added or subtracted depending on whether the previous partial sum was positive or negative. The third kind, "binom\_coeffs", returns a program that calculates the binomial coefficients, which count the number of

ways of selecting k elements out of a set of n elements. This program actually returns a recursive algorithm, which is computed by a loop with variable bounds.

The last kind of iteration-dependent loop, "IIR\_filter" was implemented using the same ideas as the FIR filter, that is, performing divisions with shift-right instructions. It can be shown that that the output value at a certain point in time n depends on previous outputs, therefore generating a loop whose output depends on previous iterations.

In both cases, whether it's an iteration-independent or dependent loop, after the main program ends, there is an infinite loop that does nothing but jump back to itself; the arrays are defined and memory is allocated for them using assembly directives.

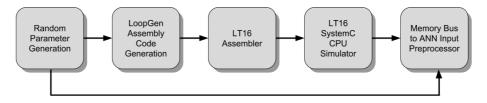

# **3.1.2** Generating the datasets with LoopSim: from LoopGen to CPU execution traces

Since we wanted the ANN to detect loops by inspecting the signals inside a CPU, we needed not only to create hundreds of assembly programs, but to compile them to machine code and produce the traces that would be found in the CPU-memory bus (in reality, this signal would be found in the instruction register's output). Additionally, we had to be able to do all of this in an automated way. Fortunately, the assembly compiler was already implemented, as were some parts of the CPU simulator; solving this was then a matter of adapting the existing code to our needs, and creating what needed creation. The flow of LoopSim can be visualized in figure 3.1.

Figure 3.1: LoopSim Data Flow

First, the parameters to be used with the functions in LoopGen were randomly generated, using uniform probability distributions, taking care of the restrictions imposed by each kind of loop. Some of these parameters also became the targets for the ANN: a Parallelizable loop (i.e., a loop created by the function loop\_independent) was associated with the target (1,0) and a Non-Parallelizable one (i.e., a loop created by the function loop\_dependent) with (0,1), that is, the classes we wanted the ANN to identify were (P, NP). Then, the assembly code generated by LoopGen was assembled into machine code using the compiler provided by the creators of the CPU, which was adapted and embedded into LoopSim. A SystemC CPU and its memory models were then instantiated, and the

string output from the compiler was then loaded to the RAM model.

The execution of any instruction was performed by calling the associated function in the processor class; some of these instructions had to be implemented since they were missing from the model. Given that we were provided only with a SystemC memory model that can hold machine code, and with a SystemC CPU model which only contains the register file and the functions associated with the instructions, it was necessary to implement a *decoder/execution unit* which implements the operation of the CPU. This was done as follows: after the CPU object is instantiated, it is set into the reset state: the register file, including the Program Counter are set to 0. Then, an instruction is fetched from the memory address given by the Program Counter and it is decoded according to its opcode; afterwards, the corresponding processor function is called with the corresponding parameters. The function call generates a new status with which the CPU state is updated (in particular, the Program Counter is incremented), and the process begins once again with a new instruction. In the case of a branching instruction, the branch delay slot and branching address are taken care of.

#### 3.1.3 ANN Input Pre-processor

After having generated the CPU execution traces, it was deemed convenient to represent this information using one-hot encoded vectors as data input for the ANN. Since the opcodes of the CPU instructions have no ordinal relationship, directly feeding the ANN with these 16-bits numbers and allowing the model to assume a natural ordering between instructions may have resulted in poor performance or unexpected results [3]. All instructions contain at least one of the following categories, each of which were encoded using one-hot vectors:

- Opcode

- Mode

- Condition

- Destination Register

- Source Register A

- Source Register B

- Immediate value

The first category, i.e., Opcode was encoded as follows:

(ADD, SUB, AND, OR, XOR, LSH, RSH, ADDI, CMP, LDIMM, LDPTR, STPTR, BIMM, BREG, CIMM, CREG, TRAP, RETI, BRT, TST)

Therefore, as an example, an "AND" instruction's opcode would be encoded as: (0, 0, 1, 0, .... 0). This vector has 20 dimensions, since all "load from pointer" instructions (LD08, LD16, LD32) are encoded to the same vector, and the same goes for the "store pointer instructions".

The remaining categories were encoded in a similar fashion.

In the previous project, the immediate value was also encoded with one-hot vectors; however, it was found that removing the immediate from the encoding did not result in any accuracy degradation of the new ANN's accuracy.

All these one-hot vectors were then concatenated and fed to the ANN in the following way:

```

(Opcode, Mode, Condition, Destination Register, Source

Register A, Source Register B)

```

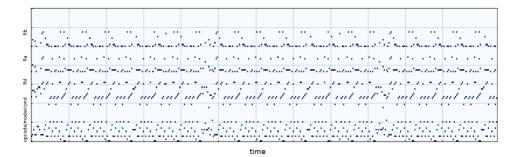

These vectorial time sequences were created and stored into a *comma separated values* (.csv) file as the CPU simulator executed each instruction. The execution of an IIR filter loop generates a sequence of vectors which can be visualized in figure 3.2:

Figure 3.2: Graphical representation of the first 400 vectorized instructions executed by an IIR filter

It was perhaps this way of visualizing the execution traces, that led us to the hypothesis that CNNs could perform well in this problem, since this is nothing more than a black and white 2D image, and CNNs are known for their excellent performance with them.

#### 3.1.4 LoopOracle v1: A Loop Classifier LSTM ANN

The ANN architecture implemented in our previous project consisted of an FC layer which takes the vectorized instruction sequences as inputs and creates an adequate encoding for an LSTM network. This input structure, given that it's fed with one-hot vectors, acts as a sort of embedding layer. The LSTM network consisted of two stacked LSTM layers with a hidden size of 256. At the output of this layer, a 256-to-2 FC layer classified the loop as either parallelizable or as non-parallelizable, i.e., the targets previously described (P, NP). Even though LSTMs seemed the obvious choice to pick, which were also recommended by experts on the field, the results achieved were quite underwhelming: an accuracy of around 80% in a problem where random chance would have a 50% success rate, was less than impressive.

The ANN was implemented using *PyTorch*, an open-source machine learning library for Python (based on Torch) which is used for applications such as natural language processing. Primarily developed by Facebook's artificial-intelligence research group, it provides a very high-level of abstraction for implementing deep ANNs and it's surprisingly easy to use.

# Software Architecture and Implementation

# 4.1 LoopOracle v2: Improving on the previous Loop Classifier ANN

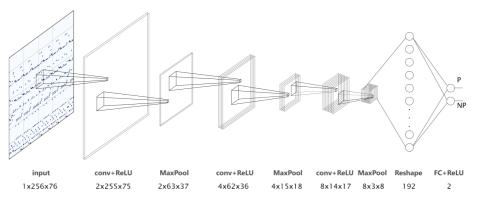

Our new ANN architecture consists of a pretty typical CNN: three convolutional layers followed by a fully connected classifier. It uses almost the same input data as our previous ANN, but the number of instructions was cut down from 512 to 256 (this is around the maximum number of instructions found in any loop body generated by LoopSim), and after removing the one-hot encoded immediate value, the instruction encoding ended up with a dimension of 76. The architecture can be visualized in figure 4.1:

Figure 4.1: Graphical representation of the CNN architecture

#### 4.1.1 Training a Pytorch CNN

As in our previous project, we started by developing the ANN in Python with the aid of the PyTorch library. Given that this allows for a very high-level design of ANNs, it's worth going through some of the most important lines of the code developed, starting with the definition of the model and forward pass:

```

class ConvolutionalLoopOracle(nn.Module):

def

init

(self)

super(ConvolutionalLoopOracle, self).__init__()

# Convolutional layers

self.conv1 = nn.Conv2d(in_channels=1, out_channels=2, kernel_size=2)

self.conv2 = nn.Conv2d(in_channels=2, out_channels=4, kernel_size=2)

self.conv3 = nn.Conv2d(in_channels=4, out_channels=8, kernel_size=2)

size=2)

self.pool2x4 = nn.MaxPool2d(kernel_size=[2, 4], stride=[2, 4])

# Output layer

self.fc = nn.Linear(8 * 8 * 3, 2)

def forward(self, x):

x = functional.relu(self.conv1(x))

x = self.pool2x4(x)

x = functional.relu(self.conv2(x))

x = self.pool2x4(x)

x = functional.relu(self.conv3(x))

x = self.pool2x4(x)

x = x.view(-1, 8 * 8 * 3)

x = set: post2x(x)

x = x.view(-1, 8 * 8 * 3)

x = functional.relu(self.fc(x))

return x

```

As shown in figure 4.1, the architecture consists of three convolutional + ReLU + MaxPooling layers, each layer duplicating the amount of channels of the previous one, while reducing the resolution of the feature space roughly by eight, since the MaxPooling operation has a kernel size of 2x4 and same stride. After these layers, only 192 activations make it to the end, which are then connected to an FC layer with this same number of inputs, and two outputs with a ReLU activation function, corresponding to the two classes previously discussed, (P, NP). After defining the CNN, we must define a function with an algorithm to train it:

```

def train model(model, learning rate, num epochs):

criterion = nn.SmoothL1Loss()

optimizer = torch.optim.Adam(model.parameters(), lr=learning_rate)

for i in range(num_epochs):

use 80% of dataset as training:

for j in range(int(0.8*data_len_()/5)):

x_t, y_t = data.get_batch(j*5, (j+1)*5)

optimizer.zero_grad()

y_hat = model(x_t)

loss = criterion(y_hat, y_t)

loss_backward()

optimizer.step()

# Validation:

with torch.no_grad():

optimizer.zero_grad()

# use 15% of dataset as validation:

x_t, y_t = data.get_batch(int(0.8 * data._len_()), int(0.95 * data._len_()))

y_hat = model(x_t)

val_loss = criterion(y_hat, y_t)

if val_loss < min_val:</pre>

min_val = val_loss

torch.save(model.state dict(), 'best model.pt')

```

As we said before, we won't go through the mathematical details of the back-propagation algorithm since this won't be done in hardware, but it's perhaps worth explaining some of the concepts involved in it. The first step of training an ANN consists of defining a *loss function*, that is, the function to be minimized. In our case, we have chosen the *Smooth L1 Loss*, defined as follows:

$$L_{1Smooth} = \begin{cases} |x| & \text{if } |x| > 1; \\ x^2 & \text{if } |x| \le 1 \end{cases}$$

This function is basically the classic L1 loss, but with a smooth, differentiable behaviour for values around zero. Although the L2 norm is more precise and better in minimizing prediction errors, the L1 norm produces sparser solutions, ignores more easily fine details and is less sensitive to outliers. Sparser solutions are good for feature selection in high dimensional spaces, as well for prediction speed [2].

The *Adam* (Adaptive Moment Estimation) optimization algorithm is an enhanced version of the stochastic gradient descent algorithm, which in contrast to the latter, computes individual adaptive learning rates for the different parameters of the network using the first and second derivatives of the loss function; it also takes into consideration how fast the weights were changing in the previous steps.

The training loop itself runs num\_epochs times, and it uses 80% of the whole dataset for the training of the ANN. The forward method is called with  $model(x_t)$  and the predicted results are stored in the variable y\_hat. After the forward pass, the difference (loss) between the target values y\_t and the predictions y\_hat is calculated by calling the function criterion (y\_hat, y\_t). When calling the forward function along the loss calculation, a computational graph of these operations is created, where each operation in this process is registered, allowing to perform the back-propagation pass by simply calling the function loss.backward(): this calculates all the gradients of the loss function respect to each parameter in the network. After the gradients are calculated, the Adam optimizer updates the values of the network's weights, and the network is ready to be trained again the next epoch. But before we do that, we first compute the loss in the validation set, which consists of 15% of the whole dataset (however, note that the network does not learn on this data). The idea behind this is having a measure of how well the ANN is performing on new, unseen data, so we can perform *early stopping* [11], which is another regularization technique used to avoid overfitting. For this reason, we keep track of the minimum value of the loss function on the validation set in each iteration, and in case this value decreases from the previous minimum, we store the model into a file that can be loaded in the future. Finally, after training the model num\_epochs times, we perform a final test using the remaining 5% of the dataset.

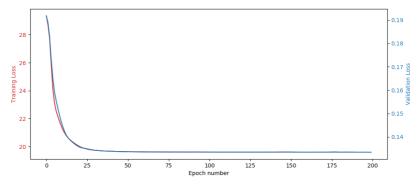

An initial learning rate of 0.001 is a fairly common practise, but we have to keep in mind that when using Adam's algorithm, this value will be accordingly adapted and it only makes a significant difference in the initial training steps. A number of epochs of 250 is much more than it was found to be necessary, with the validation loss reaching its minimum after around 50 epochs, as can be seen in figure 4.2.

Figure 4.2: Training and validation loss

A final test accuracy of around 99.8% was reached. A lot of testing with different network sizes was done, and even though more optimizations and size reductions may be possible, the final size was deemed reasonable. Given that one of our objectives is to investigate the hardware implementation of a CNN, a very simple architecture would lead to a very small design, which would not appropriately reflect the technological challenges that a typical hardware CNN implementation would entail. On the other hand, it is necessary to keep the architecture small enough so that it fits in a typical FPGA at a reasonable speed, and the sizes chosen for the CNN's layers provide a satisfactory balance between these opposing objectives.

# 4.2 Lowering the abstraction level: transforming a Py-Torch CNN to C++ code

After successfully developing and training the CNN in Python, the next step was to implement this architecture in a language that can be later synthesized by Vivado HLS. Using already developed C++ libraries was considered, but the complexity and generality of the code of the libraries found seemed excessive in comparison with our very limited needs, given that trying to understand these libraries would have taken considerable time and effort. As for the libraries and frameworks available for FPGA ANNs, they suffer a similar problem, with the addition that these libraries are developed with the intention of using the FPGA as an inference accelerator for the PC, much in the same way one would use a GPU. None of them, at least to the best of my knowledge, are tailored to be used as a standalone hardware block inside an SoC. Additionally, re-using an already developed library would have taken away all the experience and challenges that implementing a hardware neural network poses. And finally, the optimization possibilities and opportunities of an in-house developed neural network are significantly higher than what would be possible if an existing library was adapted.

Vivado HLS currently supports three high-level languages: C, C++ and SystemC. The initial choice was to use C as development language; however, it turned out that Vivado HLS does not support arbitrary fixed-point number representations in C, so the code was later ported from C to C++ instead of SystemC, since the syntax differences are minimal (though it must be said that both languages are quite finicky when passing an array to a function). Since the only thing we must implement in hardware is the forward pass, only the convolution, ReLU, max-pooling, reshape and affine functions had to be implemented.

If we recall equation 2.2, expanding the valid 2D cross-correlation operator, we obtain the following equation:

$$out(C_{out}, m, n) = b(C_{out}) + \sum_{C_{in}=0}^{N_{C_{in}}-1} \sum_{i=0}^{K_{r-1}} \sum_{j=0}^{K_{r-1}} in(C_{in}, m+i, n+j) \cdot w(C_{out}, C_{in}, i, j)$$

$$(4.1)$$

where:

- $out(C_{out}, m, n)$  is the output value of output channel  $C_{out}$  and coordinates m, n

- $b(C_{out})$  is the bias of channel  $C_{out}$

- $in(C_{in}, m+i, n+j)$  is the input value of input channel  $C_{in}$

- $w(C_{out}, C_{in}, i, j)$  is the weight of the corresponding kernel

- $N_{C_{in}}$  is the number of input channels

- Kr is the size of the kernel

Once this equation is fully understood, it's quite easy to implement in C++; so easy in fact that much to my amazement, the code written for the 2D convolution function worked on the first try after it had just been written!

As it can be seen, the lines in this code corresponds one to one with equation 4.1: the first three for loops correspond to traversing the coordinates of the output variable, while the remaining three for loops correspond each to one of the three summations.

Now that we have the code for the convolution operator, it is possible to calculate the amount of multiply-accumulate operations required by each layer, with a very simple equation:

$$#MulAcc = ch_{out} \cdot (x_{in_{dim}} - ker_{size} + 1) \cdot (y_{in_{dim}} - ker_{size} + 1) \cdot ker_{size}^2 \cdot ch_{in} \quad (4.2)$$

All layers have a kernel size of 2 (both in the horizontal and vertical dimensions), and the dimensions of each convolution operation are those shown in figure 4.1. Therefore, the number of multiply-accumulate operations for the first layer is 153000, 71424 for the second layer and 30464 for the third layer. A clever reader can already be thinking of ways to get rid of 153000 multiply operations, given the nature of our input data.

As for the implementation of the ReLU function, the code is pretty straight-forward, it just implements equation 2.3 for a 3D array.

An analogous function was implemented for the unidimensional case, which is needed at the output of the FC layer.

As for the MaxPooling function, this is again a straight-forward implementation of equation 2.4. The MaxPool function traverses the input array of every channel and outputs, for each channel, the maximum value found in a window of size  $[stride_x, stride_y]$ .

The function in charge of reshaping the output of the last convolutional layer, called view, traverses the 3D input array and writes those values into a 1D output array, as shown in the following code:

The last function implements an FC classification layer, which performs the affine transformation specified by equation 2.1:

It's easy to see that the FC layer requires 192x2 of multiply-accumulate operations; i.e., 384. The outputs of this FC layer are passed through the ReLU activation function which has been already described for the 3D case.

The forward function instantiates these functions as required, in order to implement the CNN architecture described before, as shown in the following code:

```

//..::First convolutional layer::..

// kernel size = 2x2, 1 input channel, 2 output channels

// kernel size D

Conv2d<in_x, in_y, data_in_CH, Cl_out_CH, kernel_size>(DataInTr, DataOutC1, C1W, C1B);

ReLU3d<C1_out_CH, C1_out_x, C1_out_y>(DataOutC1, DataOutC1);

MaxPool3d<C1_out_CH, C1_out_x, C1_out_y, stride_x, stride_y>(DataOutC1, DataOutMP1);

//..:Second convolutional layer::.

//.::Secona convolutional layer::..

//kernel size = 2x2, 2 input channels, 4 output channels

Conv2d:Rl_out_x, Rl_out_y, Cl_out_CH, C2_out_CH, kernel_size>(DataOutMP1, DataOutC2, C2W, C2B);

ReLU3d<C2_out_CH, C2_out_x, C2_out_y>(DataOutC2, DataOutC2);

MaxPool3d<C2_out_CH, C2_out_x, C2_out_y, stride_x, stride_y>(DataOutC2, DataOutMP2);

//..::Third convolutional layer::..

//kernel_size = 2x2, 4 input channels, 8 output channels

Conv2d<R2_out_x, R2_out_y, C2_out_CH, C3_out_CH, kernel_size>(DataOutMP2, DataOutC3, C3W, C3B);

ReLU3d<C3_out_CH, C3_out_x, C3_out_y>(DataOutC3, DataOutC3);

MaxPool3d<C3_out_CH, C3_out_x, C3_out_y, stride_x, stride_y>(DataOutC3, DataOutMP3);

.::Fully connected layer:

view<C3_out_CH, R3_out_x, R3_out_y>(DataOutMP3, dataOutView);

FullyConnected<FC_in, out_x>(dataOutView, dataOut, FCW, FCB);

ReLU1d<out_x>(dataOut, dataOut);

if (dataOut[0] < dataOut[1]){</pre>

CnnOut[0] = 0;

CnnOut[1] = 1;

} else {

CnnOut[0] = 1;

CnnOut[1] = 0;

}

```

Figure 4.3: Forward function

In contrast to PyTorch, all dimensions of every array must be calculated and defined beforehand; the values of the weights and biases were imported from the trained PyTorch model into floating-point arrays. All these details were left out from the code shown here, for the sake of clarity.

As anyone can intuit, this code is probably the most naive way to implement an ANN and does not contain any optimizations, but it is however quite readable. Even though it's not the final version of the C++ code used in Vivado HLS, it's necessary to show it here in order to better understand what ended up being implemented in Vivado, which is somewhat convoluted and nowhere near as readable.

# Chapter 5

# Hardware Architecture and Implementation

# 5.1 Vivado HLS implementation

Once we had a fully working C++ version of the CNN that produces identical results to the PyTorch golden model, we were able to start working on adapting the code so that it becomes synthetizable. The first step taken was to create specialized functions for each layer in order to be able to optimize each one of them. Inside each layer's convolutional function, loops were named with the number of layer and in accordance with the variables defined in equation 4.1, in order to make it easier to use pragmas and analyze the synthesis results. For example, in the case of the first convolutional loop, the code ends up looking like this:

Given that the number of instructions analyzed by the ANN is 256, we set this number of clock cycles as a goal, so that we can analyze loops as fast as they are executed by the CPU.

## 5.1.1 Unoptimized Solution

A first synthetizable solution with no directives or any kind of optimizations (simply the C++ code made synthetizable) achieves a latency of 4086734, a far cry from our original objective. The FPGA chip selected for the project was the Xilinx Zynq UltraScale+ MPSoC ZU3EG A484, given that it is the chip found in the Ultra96 board, which is reasonably priced and available for use in the university's electronics department. The clock frequency selected was 100MHz, which is the frequency in which the LT16x32 processor was originally being used.

The hardware utilization estimates are summarized in the following table:

|                | BRAM18K | DSP48E | FF   | LUT  |

|----------------|---------|--------|------|------|

| Total          | 112     | 5      | 2512 | 5340 |

| Utilization(%) | 25      | 1      | 1    | 7    |

Table 5.1: First solution hardware utilization

Looking more closely at the scheduling report, we can see that the first convolutional loop takes 1759804 clock cycles, while the second and third take 839528 and 331592 clock cycles respectively. These numbers are roughly 11 times higher than our first estimates for the number of operations that should be performed by these loops, so it might be a good idea to take a closer look at the scheduling of operations in the innermost loop:

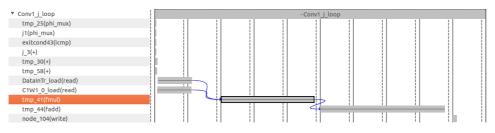

Figure 5.1: Scheduling of the first convolution innermost loop

As it can be appreciated in this figure, each multiply-accumulate operation in the loop takes ten clock cycles: two for reading the parameters, three for the floating point multiplication and strangely enough, four for the floating point addition. Therefore, given that each operation takes ten clock cycles, plus the initialization of the output with the bias and some additional overhead, we can see that these numbers are in agreement with our estimates. The remaining clock cycles correspond to the max pooling and ReLU operations, as well as the fully connected layer, etc.

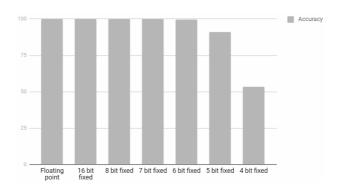

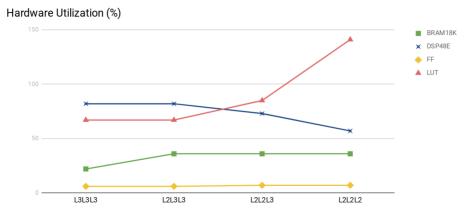

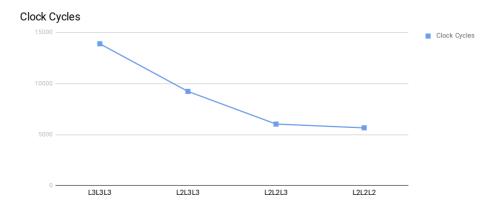

#### 5.1.2 Optimizing Data-types