Håvard Lefdal Hove

# Advanced gate drivers for next generation high power converters

Master's thesis in Energy and Environmental Engineering Supervisor: Dimosthenis Peftitsis June 2019

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Håvard Lefdal Hove

# Advanced gate drivers for next generation high power converters

Master's thesis in Energy and Environmental Engineering Supervisor: Dimosthenis Peftitsis June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

### Preface

This master thesis contains my final work as a master student at the Department of Electric Power Engineering at the Norwegian University of Science and Technology. The master thesis is written in collaboration with SINTEF Energy Research.

From I started my studies in August 2014, my passion for power engineering has grown. Especially within the field of power electronics I have found possibilities and challenges that motivates me. Therefore, power electronics have been my specialization field for the last two years of my studies. With the challenges we meet in the future in terms of greener energy systems and electrification, I am sure I have made the right decision.

The thesis builds on the specialization project that was delivered in December 2018 [1]. As it should be possible to read the master thesis without having read the specialization project, Chapter 2 and 3 that covers basic semiconductor theory and gate drivers have been re-used. However, both chapters have been modified to fit into the master thesis. In Chapter 2, some sections have been added or modified and figures have been redrawn to provide better explanations. In Chapter 3, the literature research have been updated to provide an even better overview of the state-of-the art than what was presented in the specialization project.

All the results that are presented in the master thesis are original. Even though some of the the presented figures show similar results as was presented in the specialization project, the laboratory work have been re-done, so that all results have been obtained with the same environmental conditions and thereby can be compared.

Through the work that is presented I have been given the opportunity to publish a paper and to submit an abstract. The paper have been presented at ECCE Asia 2019 in Busan, South Korea, May  $27^{th}$  2019. It can be found in Appendix A.1. The abstract is submitted to the ICSCRM 2019 conference which will be held in Kyoto, Japan, September  $29^{th}$  to October  $4^{th}$  2019. The abstract submission can be found in Appendix A.2.

> Trondheim, June 2019 Håvard Lefdal Hove

Harrind L. Hour

### Acknowledgment

I started working with gate drivers for silicon carbide MOSFETs during a summer internship at SINTEF Energy research. I would therefore like to thank SINTEF Energy Research with my two supervisors Giuseppe Guidi and Kjell Ljøkelsøy for giving me the opportunity to work with this interesting topic. The two have always been available to provide help and support with understanding, writing and lab work.

From NTNU my supervisors have been Associate Professor Dimosthenis Peftitsis and PhD candidate Ole Christian Spro. Their support and guiding have been vital in my work with this master thesis. Dimosthenis have always been available for quick questions and meeting, and have encouraged me and helped me with paper writing and abstract submission. Ole Christian have been my day-to-day supervisor. He have always been available for questions and have spent numerous of hours helping me with understanding and guiding me in lab. A massive thanks goes to both Dimosthenis and Ole Christian.

I would also like to thank my parents and my two sisters for supporting me and beliving in me through my five years of studies. It was my parents that opened the door for studies within a technical field at NTNU. Finally, I would like to thank my girlfriend for the support and for being patient with me through hectic months of master writing.

### Abstract

This master thesis investigates advanced gate driver topologies for new wide band-gap (WBG) semiconductor devices such as the silicon carbide (SiC) MOSFET. Compared to traditional semiconductor materials such as silicon (Si), WBG devices offer higher blocking voltages, lower on-state resistance, faster switching transients and operation under higher temperatures. This increases the requirement for the gate driver design as high precision and low parasitics are vital to be able to act on the fast switching transients.

Modeling and simulation is an important tool when designing power electronic converters employing WBG devices. Therefore, simulation models must provide accurate and reliable results and converge easily. However, the manufacturer of the SiC MOSFET that is used in this master thesis provides a non-continuous SPICE model for the device that often tends to run into convergence errors. Improvements are therefore suggested, and the reliability of the new model is verified through lab measurements on the actual device. The proposed model provides steady state simulation results that are as accurate as with the model provided by the manufacturer. Moreover, the simulation performance is improved and it converges easily.

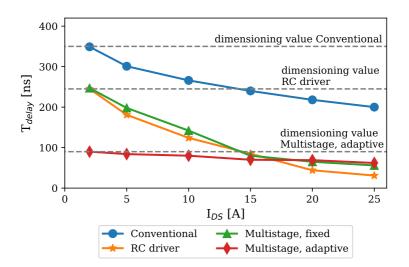

A new gate driver topology that aims for delay time minimization, termed the multistage driver, is proposed and validated through laboratory work. The multistage driver is voltage controlled, which is more robust than timing based gate drivers for fast switching devices. By making the multistage driver adaptive based on load current and junction temperature, the best possible reduction in delay time can be obtained. Compared to a conventional gate driver (CGD), the adaptive multistage driver reduces the turn-on delay time by 72 % and turn-off delay time by 74 %. A control circuit that realizes the adaptive multistage driver based on load current measurements for turn-off is proposed and validated through laboratory work as well. With the control circuit, the turn-off delay time is reduced by 71 %.

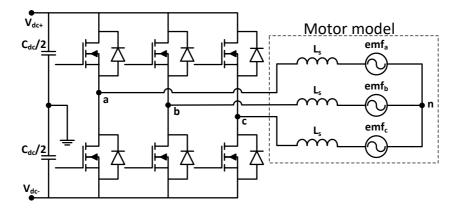

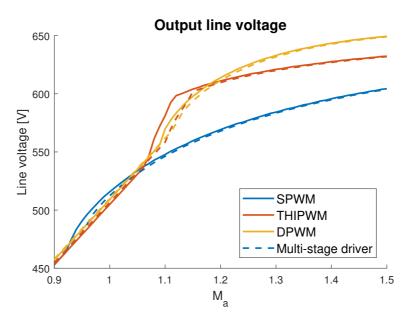

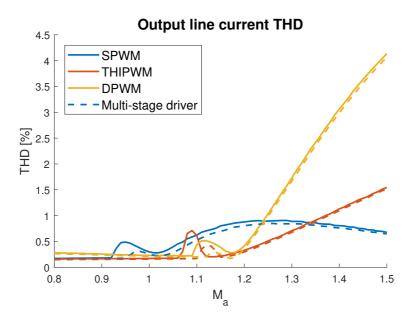

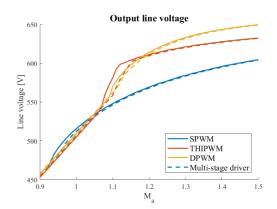

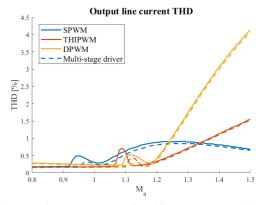

By using a delay time minimization gate driver in a converter bridge leg, the requirements for dead time and minimum pulse width can be reduced. A motor drive application was simulated. When using the multistage driver compared to the CGD, the simulation results suggests that the linear modulation region can be increased by up to 3.8 %, and the current THD in the linear region reduced by up to 7.7 % when switching at 15 kHz.

### Sammendrag

Denne masteroppgaven tar for seg avanserte driverkretser for halvleder komponenter med høy båndbredde (WBG) slik som de nye silisiumkarbid (SiC) MOSFETene. Sammenlignet med tradisjonelle halvleder materialer som silisium tilbyr WBG komponenter høyere blokkespenning, lavere ledemotstand, raskere svitsjetransienter og de kan opereres under høyere temperaturer. Dette øker kravene til driverkretsen side høy presisjon og lite parasittkomponenter er avgjørende for å kunne håndtere de raske svitsjetransientene.

Modellering og simulering er et viktig verktøy i design av kraftelektronikkomformere der WBG komponenter brukes. Simuleringsmodellene må derfor være presise, pålitelige og konvergere raskt. Produsenten av SiC MOSFETen som er brukt i denne masteroppgaven gir derimot en SPICE model som er ikke-kontinuerlig ofte gir konvergeringsproblemer i simuleringer. Forbedringer til denne modellen er derfor foreslått og troverdigheten til den nye modellen er verifisert gjennom labarbeid med en faktisk komponent. Resultatene viser at den foreslåtte modellen og den opprinnelige modellen fra produsenten er like presise for stasjonære forhold. Men, med den foreslåtte modellen er konvergeringsproblemene borte.

En ny driverkrets med formål om å minimere tidsforsinkelser er foreslått og verifisert gjennom labarbeid. Denne er referert til som en flertrinnsdriver. Flertrinnsdriveren er spenningskontrollert, noe som ansees som mer robust for raske svitsjetransienter enn tidsbaserte drivere. Den største reduksjonen i tidsforsinkelser oppnås når flertrinnsdriveren er gjort adaptiv basert på laststrøm og komponent temperatur. Sammenlignet med en konvensjonell driver (CGD) er den adaptive flertrinnsdriveren i stand til å kutte tidsforsinkelsen med 72 % ved påslag og 74 % ved avslag. En kontrollkrets som realiserer den adaptive flertrinnsdriveren ved avslag basert på laststrømsmåling er i tillegg foreslått og testet i lab. Med kontrollkretsen er tidsforsinkelsen kuttet med 71 %.

Ved å bruke en driverkrets som minimerer tidsforsinkelser i en omformerhalvbro kan kravene til dødtid og minimal pulsbredde reduseres. Et motordrifttilfelle ble simulert for å teste påvirkningen dette har. Sammenlignet med CGS viser simuleringsresultatene at ved å bruke flertrinnsdriveren så kan de lineære modulasjonsområdet økes med opptil 3.8 %, og strømmens THD i det lineære området reduseres med opptil 7.7 % når det svitsjes med en svitsjefrekvens på 15 kHz.

## Table of Contents

| Preface                           | i                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknow                            | vledgement iii                                                                                                                                                                                                                                                                                             |

| Abstra                            | v v                                                                                                                                                                                                                                                                                                        |

| Samme                             | ndrag vii                                                                                                                                                                                                                                                                                                  |

| Table o                           | f Contents xi                                                                                                                                                                                                                                                                                              |

| List of                           | Tables xiii                                                                                                                                                                                                                                                                                                |

| List of                           | Figures xvii                                                                                                                                                                                                                                                                                               |

| Abbrev                            | iations xviii                                                                                                                                                                                                                                                                                              |

| <b>1 Int</b><br>1.1<br>1.2<br>1.3 | oduction1Background and perspective1Objectives2Report Outline3                                                                                                                                                                                                                                             |

| 2 Sen<br>2.1<br>2.2<br>2.3        | iconductor device theory5Basics5Ideal switching characteristics82.2.1MOSFET capacitor model82.2.2Turn-on characteristics92.2.3Turn-off characteristics132.2.4Switching losses13Non-ideal switching characteristics142.3.1Ringing and overshoots142.3.2Current and temperature dependency152.3.3Dead time17 |

|   |                                                                                                | 2.3.4 Miller effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                                                                                                                             |

|---|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.4                                                                                            | WBG devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                                                             |

|   |                                                                                                | 2.4.1 Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                                                                                                                                                                                             |

|   |                                                                                                | 2.4.2 Si and SiC comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                                                                                                             |

|   |                                                                                                | 2.4.3 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                                                                                                             |

| - | ~                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 3 |                                                                                                | e drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                                                                                                                                             |

|   | 3.1                                                                                            | Conventional gate driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                                                                                                                                                                             |

|   | 3.2                                                                                            | RC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24                                                                                                                                                                                             |

|   | 3.3                                                                                            | State-of-the-art advanced gate drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26                                                                                                                                                                                             |

|   |                                                                                                | 3.3.1 Open loop gate drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                                                                                                                                                                                             |

|   |                                                                                                | 3.3.2 Closed-loop gate drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                                                                             |

|   | 3.4                                                                                            | Multistage driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                                                                             |

| 4 | T                                                                                              | Second CDICE model of C:C MOCFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                                                                                                                                             |

| 4 | <b>1mp</b><br>4.1                                                                              | proved SPICE model of SiC MOSFET         SPICE modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>37</b><br>37                                                                                                                                                                                |

|   | 4.1                                                                                            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                                                                                                                                             |

|   | 4.2                                                                                            | Initial model       4.2.1         Convergence error       4.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                                                             |

|   |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

|   | 4.2                                                                                            | 4.2.2 Initial SPICE model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39                                                                                                                                                                                             |

|   | 4.3                                                                                            | Proposed model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                                                                                                                                             |

|   | 4.4                                                                                            | Verification of proposed model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46                                                                                                                                                                                             |

|   |                                                                                                | 4.4.1 Experimental work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46<br>52                                                                                                                                                                                       |

|   |                                                                                                | 4.4.2 Simulations with proposed model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                                                                             |

|   |                                                                                                | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                |

| 5 | Exp                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                                                                                                                                                             |

| 5 | Exp<br>5.1                                                                                     | perimental validation of gate driver topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>57</b><br>57                                                                                                                                                                                |

| 5 | 5.1                                                                                            | erimental validation of gate driver topologies<br>Laboratory setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57                                                                                                                                                                                             |

| 5 | 5.1<br>5.2                                                                                     | perimental validation of gate driver topologies         Laboratory setup         Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                |

| 5 | 5.1                                                                                            | erimental validation of gate driver topologies         Laboratory setup         Method         Lab results                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57<br>59                                                                                                                                                                                       |

| 5 | 5.1<br>5.2                                                                                     | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57<br>59<br>60                                                                                                                                                                                 |

| 5 | 5.1<br>5.2                                                                                     | berimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57<br>59<br>60<br>61                                                                                                                                                                           |

| 5 | 5.1<br>5.2<br>5.3                                                                              | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         Sect of delay time minimization gate drivers                                                                                                                                                                                                                                                                                              | 57<br>59<br>60<br>61                                                                                                                                                                           |

|   | 5.1<br>5.2<br>5.3<br>Imp<br>6.1                                                                | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         Dead time minimization gate drivers         Dead time requirement                                                                                                                                                                                                                                                                         | 57<br>59<br>60<br>61<br>66                                                                                                                                                                     |

|   | 5.1<br>5.2<br>5.3                                                                              | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         Sect of delay time minimization gate drivers                                                                                                                                                                                                                                                                                              | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> </ul>                                                                                                             |

|   | 5.1<br>5.2<br>5.3<br>Imp<br>6.1                                                                | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         Dead time minimization gate drivers         Dead time requirement                                                                                                                                                                                                                                                                         | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>69</li> </ul>                                                                                                 |

|   | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2                                                  | Decimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         Dead time requirement         Motor model         PWM methods         Simulation model                                                                                                                                                                                                                                                    | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>69</li> <li>70</li> </ul>                                                                                     |

|   | 5.1<br>5.2<br>5.3<br>Imp<br>6.1<br>6.2<br>6.3                                                  | <b>Derimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients <b>bead time minimization gate drivers</b> Dead time requirement         Motor model         PWM methods                                                                                                                                                                                                                                           | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>70</li> <li>71</li> </ul>                                                                                     |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                             | <b>Derimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients <b>back of delay time minimization gate drivers</b> Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results                                                                                                                                                                              | 57<br>59<br>60<br>61<br>66<br><b>69</b><br>70<br>71<br>73<br>75                                                                                                                                |

|   | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b>               | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients <b>5.3.2</b> Turn-on switching transients <b>5.3.2</b> Turn-on switching transients <b>5.3.4 Dead time minimization gate drivers</b> Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Simulation results                                                                  | 57<br>59<br>60<br>61<br>66<br>69<br>70<br>71<br>73<br>75<br><b>77</b>                                                                                                                          |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1        | perimental validation of gate driver topologies         Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients         beact of delay time minimization gate drivers         Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Simulation results         Potive gate driving         Driver topology                                 | 57<br>59<br>60<br>61<br>66<br><b>69</b><br>69<br>70<br>71<br>73<br>75<br><b>77</b><br>77                                                                                                       |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1<br>7.2 | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients <b>beact of delay time minimization gate drivers</b> Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Driver topology         Adaptive boost voltage control circuit                                                   | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>70</li> <li>71</li> <li>73</li> <li>75</li> <li>77</li> <li>78</li> </ul>                                     |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1        | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients <b>bact of delay time minimization gate drivers</b> Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Driver topology         Adaptive boost voltage control circuit         PCB design                                 | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>70</li> <li>71</li> <li>73</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> </ul>                         |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1<br>7.2 | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients         Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Portive gate driving         Driver topology         Adaptive boost voltage control circuit         PCB design         7.3.1                                  | 57<br>59<br>60<br>61<br>66<br>69<br>70<br>71<br>73<br>75<br><b>77</b><br>77<br>78<br>79<br>80                                                                                                  |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1<br>7.2 | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients         Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Driver topology         Adaptive boost voltage control circuit         PCB design         7.3.1         Prototype         7.3.2         Design considerations | <ul> <li>57</li> <li>59</li> <li>60</li> <li>61</li> <li>66</li> <li>69</li> <li>70</li> <li>71</li> <li>73</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> <li>81</li> </ul> |

| 6 | 5.1<br>5.2<br>5.3<br><b>Imp</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Ada</b><br>7.1<br>7.2 | <b>Perimental validation of gate driver topologies</b> Laboratory setup         Method         Lab results         5.3.1         Turn-off switching transients         5.3.2         Turn-on switching transients         5.3.2         Turn-on switching transients         Dead time requirement         Motor model         PWM methods         Simulation model         Simulation results         Portive gate driving         Driver topology         Adaptive boost voltage control circuit         PCB design         7.3.1                                  | 57<br>59<br>60<br>61<br>66<br>69<br>70<br>71<br>73<br>75<br><b>77</b><br>77<br>78<br>79<br>80                                                                                                  |

|                 |      | 7.4.1<br>7.4.2<br>7.4.3 | Laboratory setup                           |             | 83<br>84<br>87 |

|-----------------|------|-------------------------|--------------------------------------------|-------------|----------------|

| 8               | Con  | clusion a               | and further work                           |             | 89             |

|                 | 8.1  | Conclu                  | sion                                       |             | 89             |

|                 | 8.2  | Further                 | work                                       |             | 91             |

| Bibliography 93 |      |                         | 93                                         |             |                |

| Ар              | pend | ix                      |                                            |             | 99             |

| Α               | Publ | lications               | 3                                          |             | 99             |

|                 | A.1  | ECCE                    | Asia 2019                                  |             | 99             |

|                 | A.2  | ICSCR                   | M 2019                                     |             | 108            |

| B               | Prop | osed SF                 | PICE model of SiC MOSFET                   |             | 111            |

| С               | Simu | ilation i               | model for delay time minimization gate dri | iver impact | 117            |

## List of Tables

| 4.1 | Key tolerances parameters in LTspice.                                   | 39 |

|-----|-------------------------------------------------------------------------|----|

| 5.1 | Equipment used in lab.                                                  | 58 |

| 5.2 | Test parameters used for the different drivers.                         | 59 |

| 5.3 | Test matrix.                                                            | 60 |

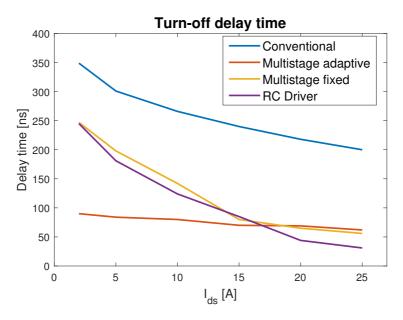

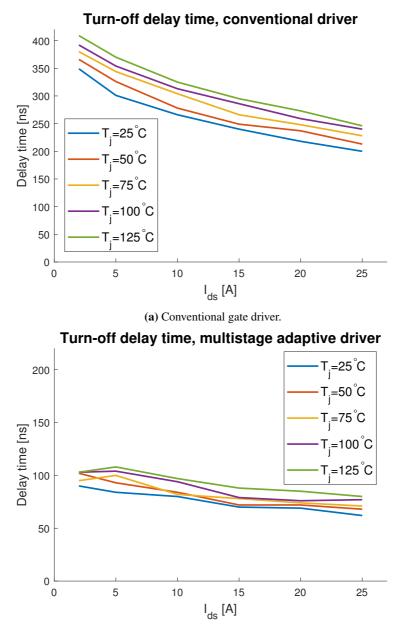

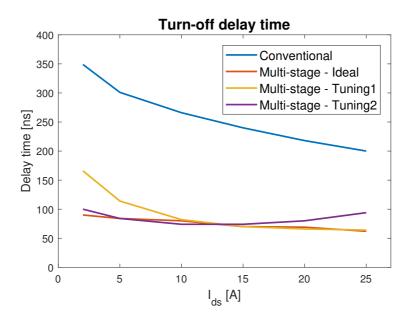

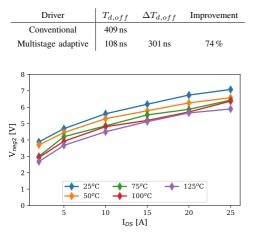

| 5.4 | Turn-off delay time improvements at 25°C for 2 A load current.          | 63 |

| 5.5 | Turn-off delay time improvements at 125°C                               | 66 |

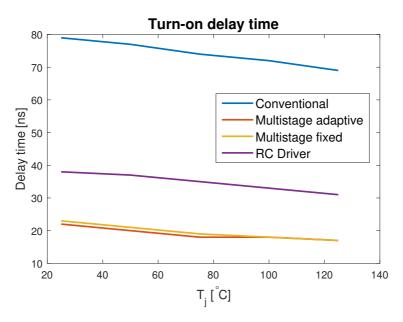

| 5.6 | Turn-on delay time improvements at 25°C.                                | 68 |

| 6.1 | Simulation parameters.                                                  | 70 |

| 6.2 | Maximum $M_a$ and current THD for linear regions for different PWM      |    |

|     | methods                                                                 | 75 |

| 7.1 | Component selection for the adaptive boost voltage control circuit.     | 81 |

| 7.2 | Capacitor inserted to suppress high frequency noise.                    | 82 |

| 7.3 | Test matrix.                                                            | 86 |

| 7.4 | Turn-off delay time improvements for the adaptive boost voltage control |    |

|     | circuit for 2 A load current.                                           | 88 |

# List of Figures

| 2.1  | Pn junction and critical electrical field for Si and SiC                   | 6      |

|------|----------------------------------------------------------------------------|--------|

| 2.2  | Semiconducture structures for MOSFET and IGBT                              | 7      |

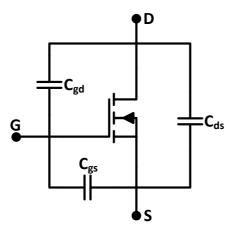

| 2.3  | MOSFET capacitor model                                                     | 8      |

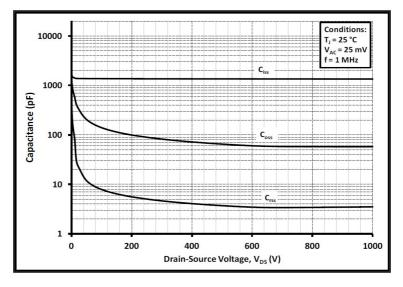

| 2.4  | MOSFET capacitors as function of drain-source voltage. Taken from C3M007   | 75120K |

|      | datasheet [2]                                                              | 9      |

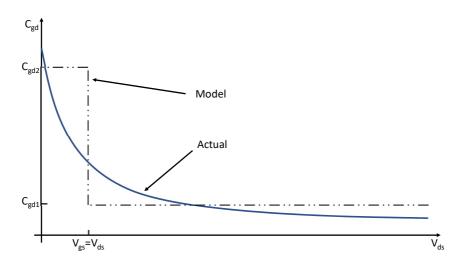

| 2.5  | Miller capacitor model, recreated from [3]                                 | 10     |

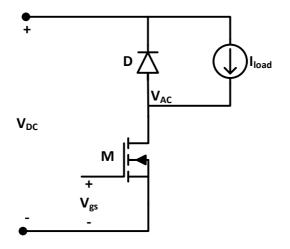

| 2.6  | Setup used to describe the switching characteristics                       | 10     |

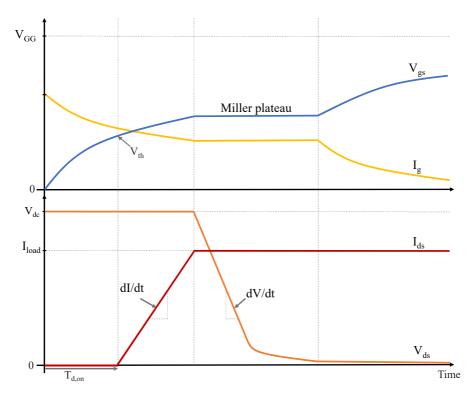

| 2.7  | Ideal turn-on switching waveforms as presented in [3]                      | 11     |

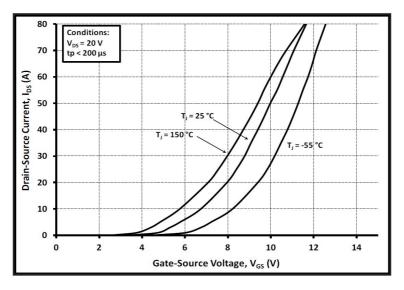

| 2.8  | MOSFET transfer curve. Taken from C3M0075120K datasheet [2]                | 12     |

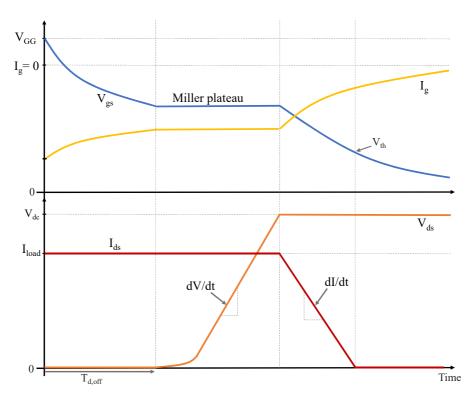

| 2.9  | Ideal turn-off switching waveforms as presented in [3]                     | 14     |

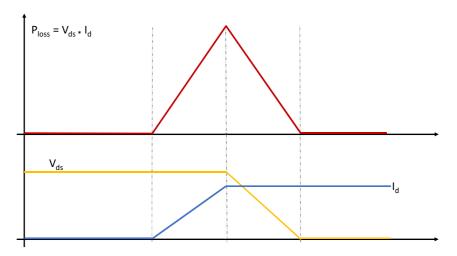

| 2.10 | Switching losses in a MOSFET with an inductive load.                       | 15     |

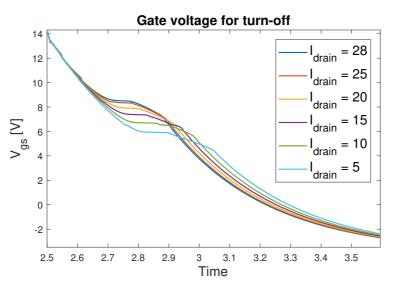

| 2.11 | Gate-source voltage at turn-off for different load currents                | 16     |

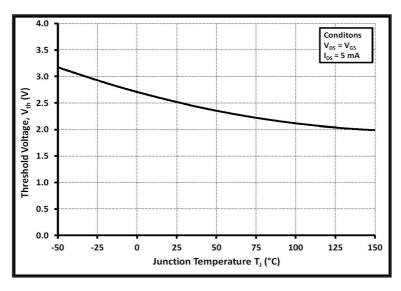

| 2.12 | Threshold voltage for different junction temperatures. Taken from C3M00751 | 20K    |

|      | datasheet [2]                                                              | 17     |

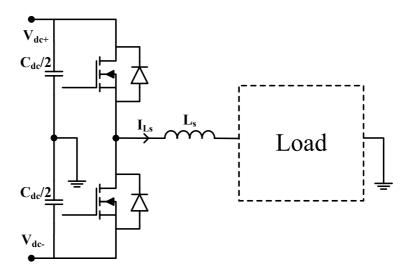

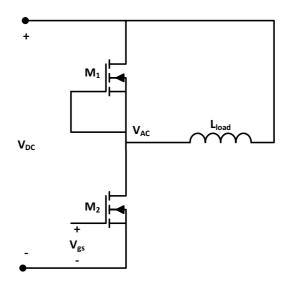

| 2.13 | Schematic diagram of a half-bridge with a load connected                   | 18     |

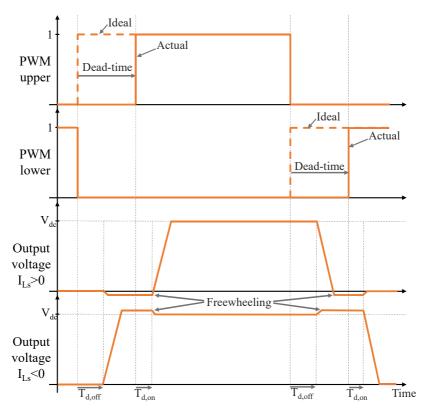

| 2.14 | Theoretical waveforms showing the impact of dead time in a bridge leg.     |        |

|      | First presented in [4].                                                    | 19     |

| 2.15 | Material properties for different semiconductors [5]                       | 20     |

|      |                                                                            |        |

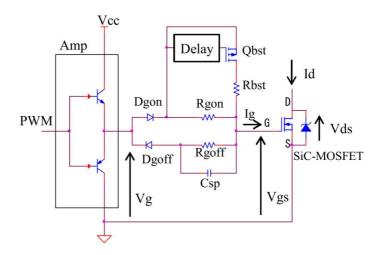

| 3.1  | Conventional gate driver (CGD) with separate turn-on and turn-off gate     | 22     |

| ~ ~  | resistor.                                                                  | 23     |

| 3.2  | The RC driver with separate current paths for turn-on and turn-off         | 24     |

| 3.3  | Delay time minimization (DTM) switching characteristics compared to        | 25     |

| 2.4  | CGD.                                                                       | 25     |

| 3.4  | The gate boost circuit, proposed in [6].                                   | 26     |

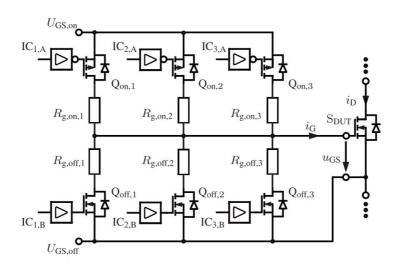

| 3.5  | The Stage-Wise Gate Driver, proposed in [7].                               | 27     |

| 3.6  | Active two stage gate driver.                                              | 28     |

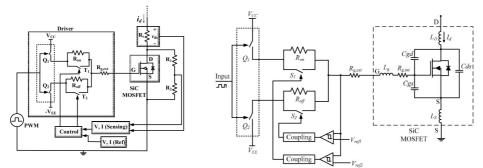

| 3.7  | Open-loop gate control, presented in [8]                                   | 29     |

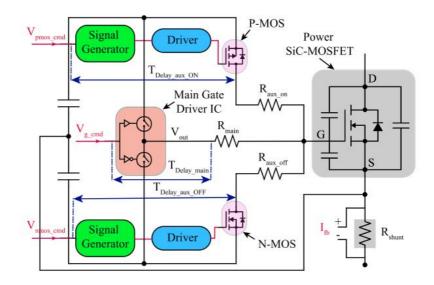

| 3.8  | Voltage controlled AGD, proposed in [9].                                   | 30     |

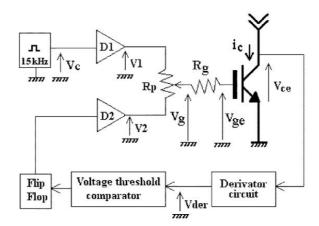

| 3.9  | Timing based active gate driver, proposed in [10]                          | 31     |

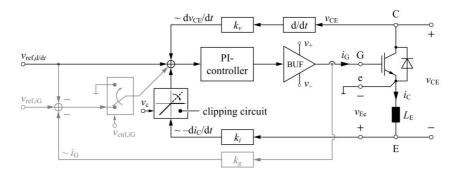

| 3.10  | Closed-loop dynamic gate driver, proposed in [11].                                  | 32 |

|-------|-------------------------------------------------------------------------------------|----|

|       | Closed-loop gate driver for SiC MOSFETs, presented in [12]                          | 32 |

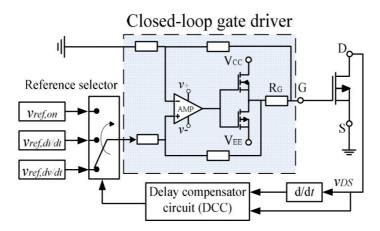

| 3.12  | Closed-loop gate driver for GaN HEMT, presented in [13].                            | 33 |

| 3.13  | Principle of gate current control. Taken from [14]                                  | 34 |

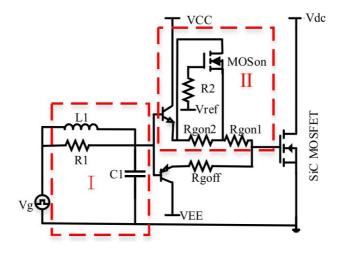

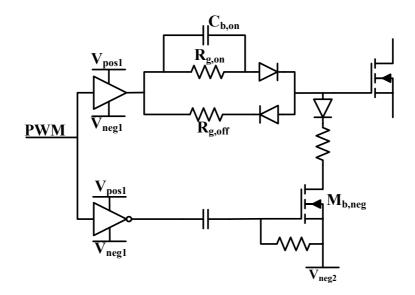

| 3.14  | Schmatic diagram of the multistage driver                                           | 35 |

| 4.1   | Power MOSFET model including parasitics, presented in [15]                          | 38 |

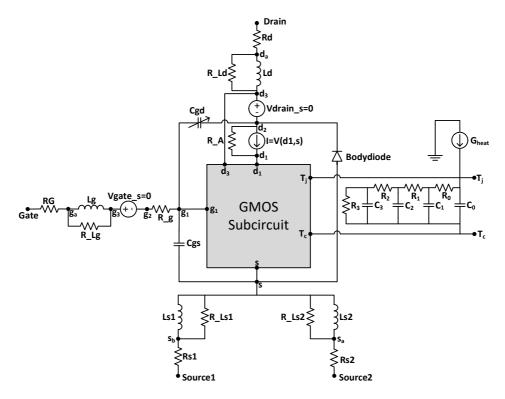

| 4.2   | Initial LTspice model.                                                              | 40 |

| 4.3   | LTspice MOSFET model visually represented.                                          | 41 |

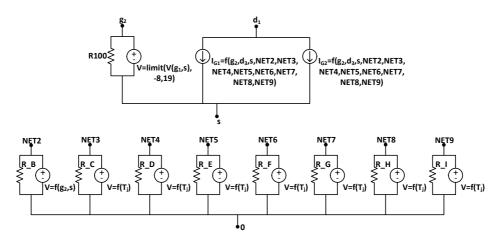

| 4.4   | Inner part of the LTspice MOSFET model (GMOS Subcircuit)                            | 42 |

| 4.5   | Voltage level in nodes NET5 to NET9 as function of gate-source voltage.             |    |

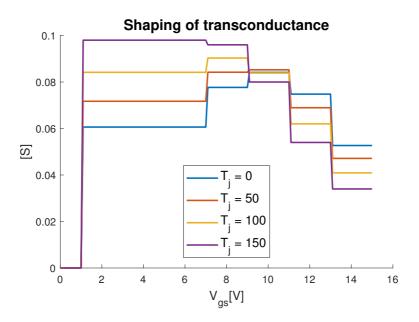

| 1.0   | The voltage levels are shaping the transconductance of the device                   | 44 |

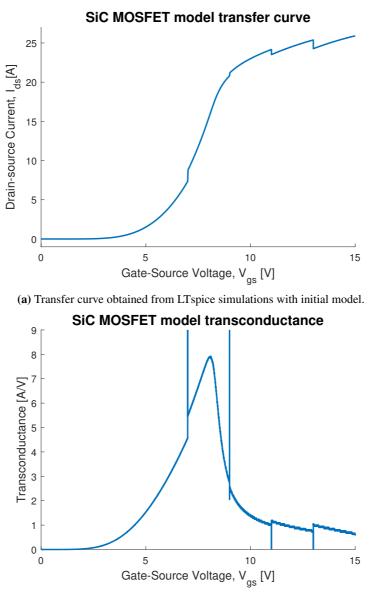

| 4.6   | Initial LTspice MOSFET model transfer curve.                                        | 44 |

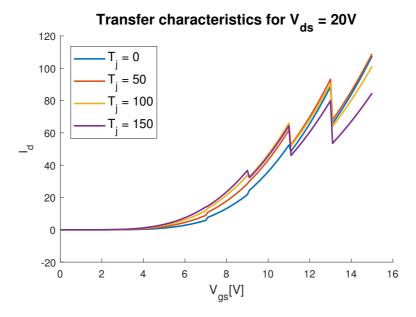

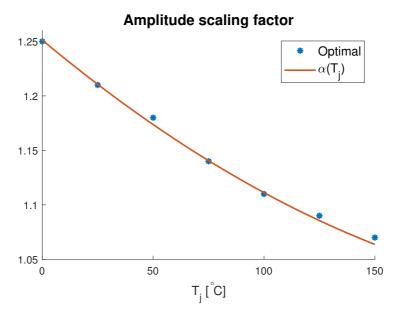

| 4.7   | Calculated, optimal, values for $\alpha$ and $\alpha(T_j)$                          | 46 |

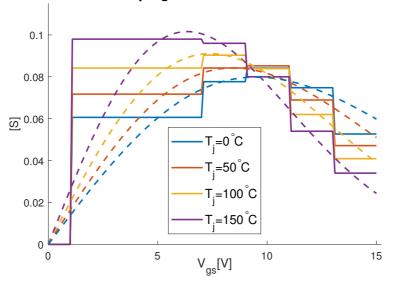

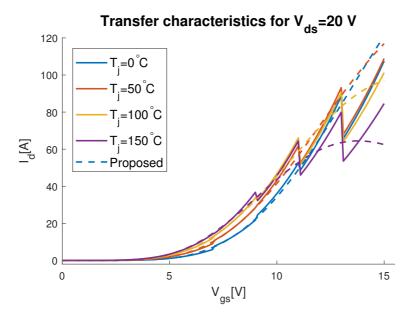

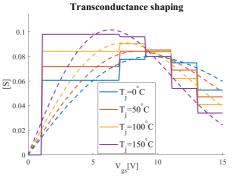

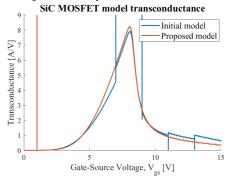

| 4.8   | LTspice MOSFET model transconductance shaping. Dotted lines are the proposed model. | 47 |

| 4.9   | LTspice MOSFET model transfer curve. Dotted lines are proposed model.               | 47 |

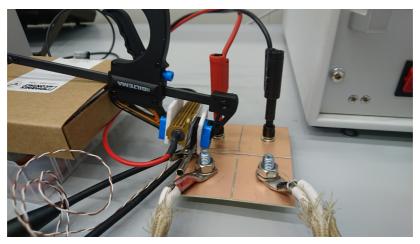

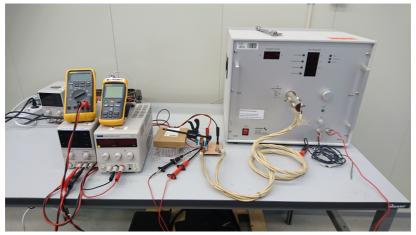

|       | Laboratory setup for output characteristics measurements.                           | 48 |

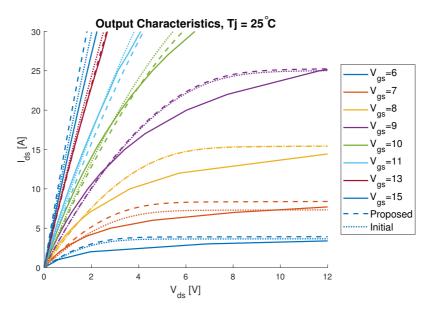

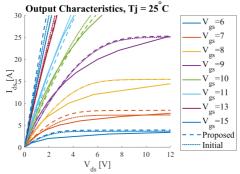

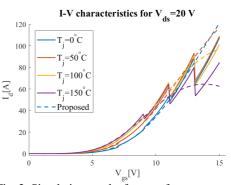

|       | Output characteristics from initial and proposed model compared with                |    |

|       | measurements from lab at junction temperature $25^{\circ}$ C                        | 49 |

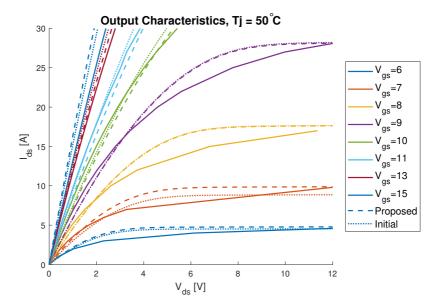

| 4.12  | Output characteristics from initial and proposed model compared with                |    |

|       | measurements from lab at junction temperature 50°C                                  | 50 |

| 4.13  | Output characteristics from initial and proposed model compared with                |    |

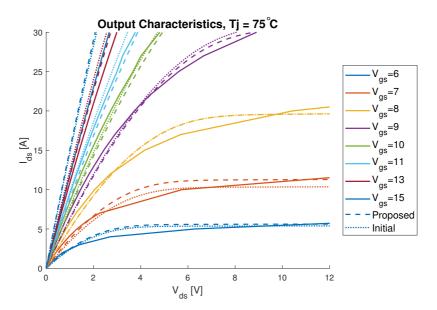

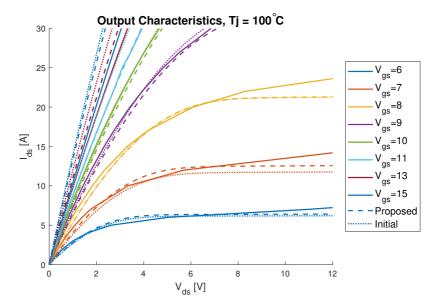

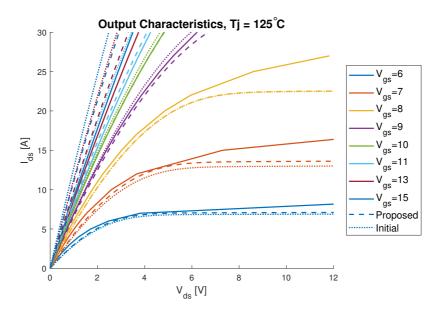

|       | measurements from lab at junction temperature 75°C                                  | 50 |

| 4.14  | Output characteristics from initial and proposed model compared with                |    |

|       | measurements from lab at junction temperature 100°C                                 | 51 |

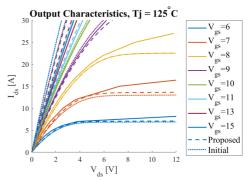

| 4.15  | Output characteristics from initial and proposed model compared with                |    |

|       | measurements from lab at junction temperature 125°C                                 | 51 |

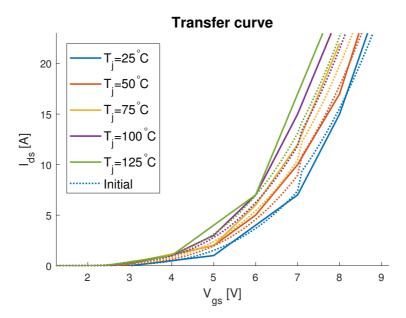

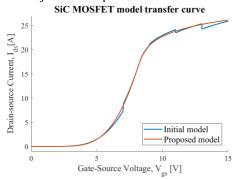

| 4.16  | Comparison between transfer curve from lab and the initial simulation               |    |

|       | model.                                                                              | 52 |

| 4.17  | Comparison between transfer curve from lab and the proposed simulation              | 50 |

| 4 1 0 | model.                                                                              | 53 |

|       | Initial and proposed LTspice model.                                                 | 54 |

| 4.19  | Comparison of dv/dt measurements from lab with initial and proposed model.          | 55 |

|       | model                                                                               | 55 |

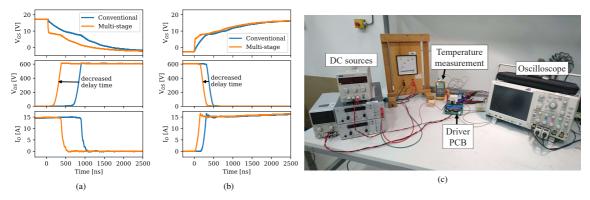

| 5.1   | Laboratory setup.                                                                   | 57 |

| 5.2   | Schematic diagram of the experimental setup.                                        | 58 |

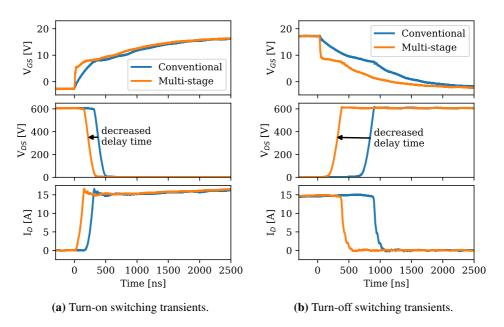

| 5.3   | Waveforms validating the operation principle of the multistage driver               | 61 |

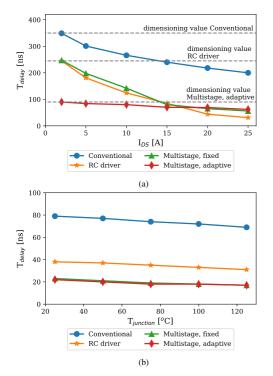

| 5.4   | Minimum turn-off delay times obtained with different gate drivers as func-          |    |

|       | tion of load current at junction temperature 25°C                                   | 62 |

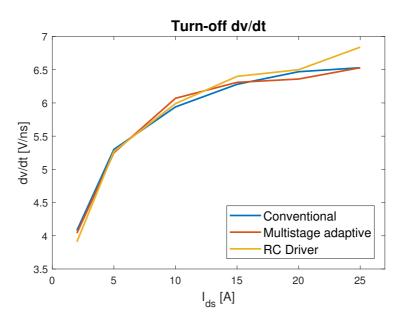

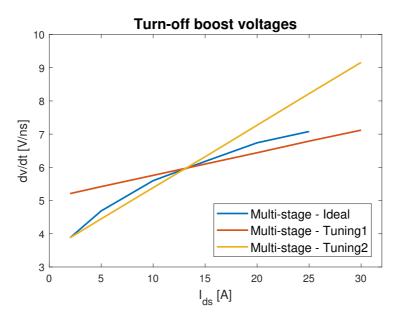

| 5.5   | Voltage commutation slopes as function of load current for three different          |    |

|       | driver topologies and junction temperature 25°C                                     | 63 |

| 5.6   | Turn-off boost voltages used in the adaptive multistage driver for different        |    |

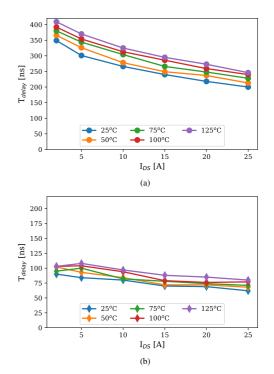

|       | load currents and junction temperatures                                             | 64 |

| 5.7        | Junction temperature dependency on turn-off delay times for the conven-       |    |

|------------|-------------------------------------------------------------------------------|----|

| <b>5</b> 0 | tional and the adaptive multistage gate driver.                               | 65 |

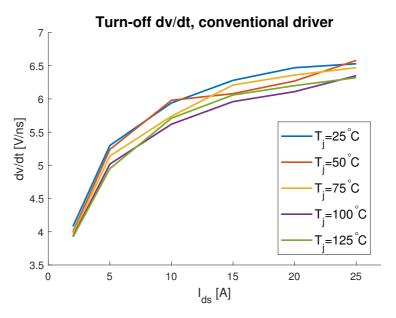

| 5.8        | Voltage commutation slopes for the conventional gate driver at different      | 66 |

| 5.9        | junction temperatures                                                         | 00 |

|            | gate driver topologies.                                                       | 67 |

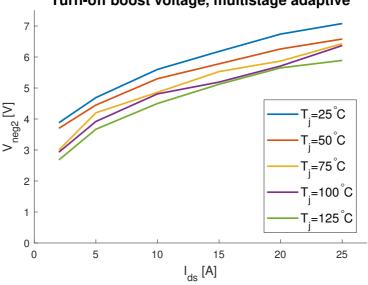

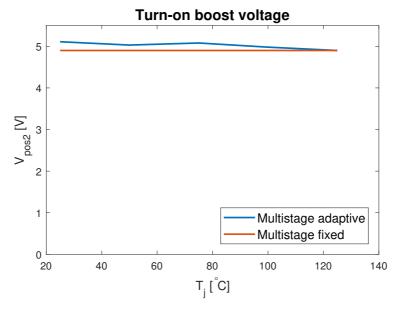

| 5.10       | Turn-on boost voltages used in the fixed and adaptive multistage driver.      | 68 |

| 6.1        | Dimensioning values for dead time requirement.                                | 70 |

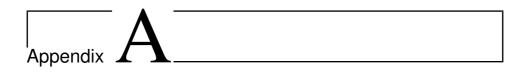

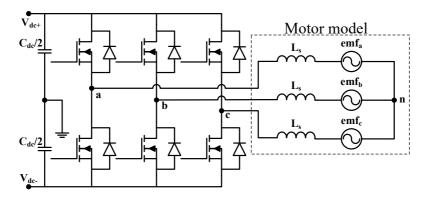

| 6.2        | Schematic diagram of a three phase inverter and the equivalent motor model.   | 71 |

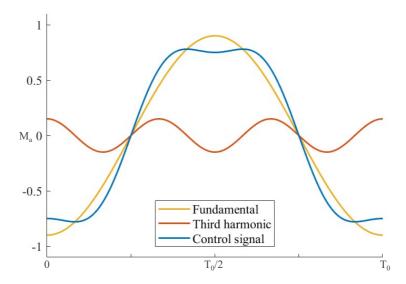

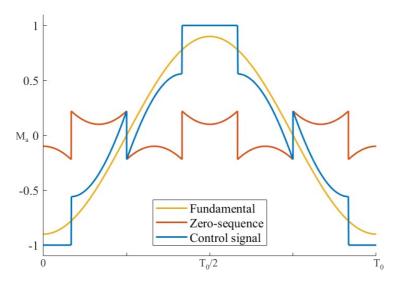

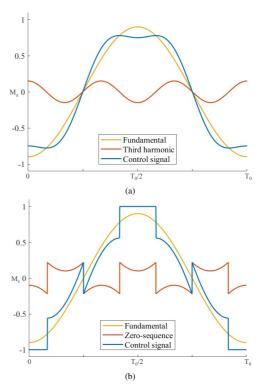

| 6.3        | Continuous control signal with third harmonic injection (THIPWM)              | 72 |

| 6.4        | Discontinuous control signal with zero-sequence injection (DPWM)              | 73 |

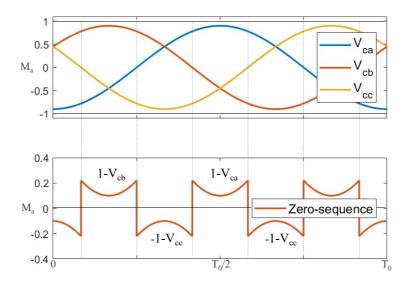

| 6.5        | Generation of the zero-sequence signal that is used in DPWM                   | 74 |

| 6.6        | Output line voltage magnitude as function of modulation index                 | 76 |

| 6.7        | Line current THD as function of modulation index.                             | 76 |

| 7.1        | Schematic diagram of the proposed adaptive gate driver.                       | 78 |

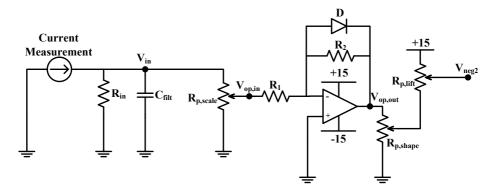

| 7.2        | Schematic diagram of the boost voltage control circuit.                       | 79 |

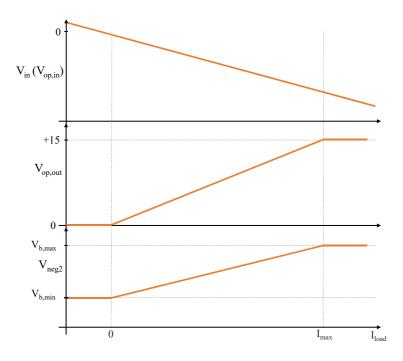

| 7.3        | Voltage levels in the control circuit.                                        | 80 |

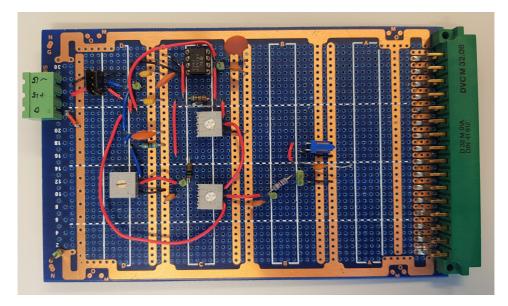

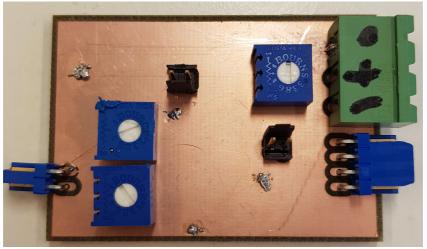

| 7.4        | Prototype of the boost voltage control circuit.                               | 81 |

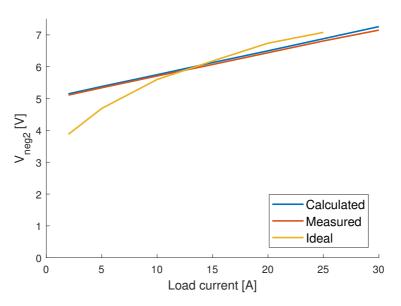

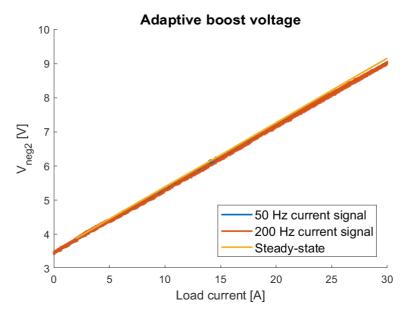

| 7.5        | Adaptive boost voltages at steady-state from prototype and the ideal boost    |    |

|            | voltages                                                                      | 82 |

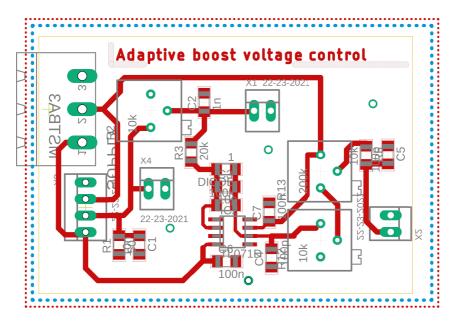

| 7.6        | Screenshot of the PCB design in Autodesk EAGLE.                               | 83 |

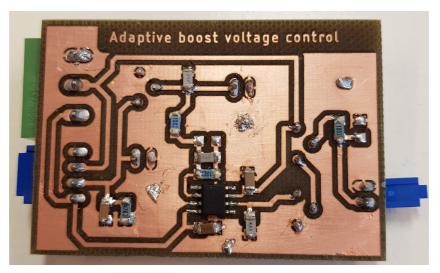

| 7.7        | The produced PCB after all components have been mounted                       | 84 |

| 7.8        | Laboratory setup used to evaluate the Adaptive boost voltage control circuit. | 85 |

| 7.9        | Steady-state turn-off boost voltages used for tuning strategy 1 and 2 com-    |    |

|            | pared with the ideal boost voltage values found in Chapter 5                  | 86 |

| 7.10       | Turn-off boost voltage measured on the PCB when a 50 Hz signal and a          |    |

|            | 200 Hz signal is applied on the adaptive boost voltage circuit.               | 87 |

| 7.11       | Turn-off delay times obtained with the two tuning strategies for the adap-    |    |

|            | tive boost voltage circuit compared to the conventional driver and the ideal  |    |

|            | tuning of the multistage driver.                                              | 88 |

# Abbreviations

| AGC    | = | Active Gate Driver                                  |

|--------|---|-----------------------------------------------------|

| CGD    | = | Conventional Gate Driver                            |

| DTM    | = | Delay Time Minimization                             |

| EMI    | = | Electromagnetic Interference                        |

| FACTS  | = | Flexible Alternating Current Transmission System    |

| FPGA   | = | Field Programmable Gate Array                       |

| GND    | = | Ground                                              |

| HV     | = | High Voltage                                        |

| HVDC   | = | High Voltage Direct Current                         |

| IC     | = | Integrated Circuit                                  |

| IGBT   | = | Insulated Gate Bipolar Transistor                   |

| MOSFET | = | Metal Oxide Semiconductor Field Effect Transistor   |

| MPW    | = | Minimum Pulse Width                                 |

| OV     | = | Over-voltage                                        |

| PCB    | = | Printed Circuit Board                               |

| PV     | = | Photovoltaic                                        |

| PWM    | = | Pulse Width Modulation                              |

| SPICE  | = | Simulation Program with Integrated Circuit Emphasis |

| VSI    | = | Voltage Source Inverter                             |

| WBG    | = | Wide Band-gap                                       |

|        |   |                                                     |

# Chapter

### Introduction

### **1.1 Background and perspective**

The worlds energy demand is increasing. According to UN, around one billion people lacks access to electricity [16]. Even though there are a lot of ongoing projects aiming to give more people access, it is still a long way to go. Through the Paris Agreement, almost every country have committed to cut their pollution of climate gasses [17]. Still, to cover the increasing energy demand by use of renewable energy sources is challenging and the  $CO_2$  emissions have continued to increase [18].

Fulfilling the goals in the Paris Agreement depends on the technology development. Evolving the energy systems from fossil fuel to energy carriers such as electricity have been pointed out as important, especially when the electricity comes from renewable energy sources. Equipment that allows renewable energy sources to be introduced to the energy system in an efficient and cost effective way must be developed. In addition, clean technologies that can substitute traditional fossil fuel technologies such as vehicles and airplanes must be further developed. This includes electric vehicles and energy sources are increasing [19]. In 2017 25% of all electricity worldwide was produced by renewables [20]. However, to keep up with the Paris Agreement the expansion of renewable energy sources must increase. In that development, power electronics will play a key role.

Power electronic components are today used in many electric applications and the integration level is increasing [21]. Typical examples are converters for power supplies, rectifiers for data centers or in HVDC power systems, motor drives in electric vehicles or ships, FACTS in HV transmission systems, or converters for renewable energy integration [22]. The possibilities are many, but further improvement of costs, reliability and efficiency is needed.

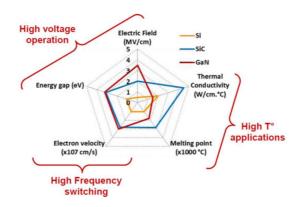

In the recent years, a new family of devices within power electronics have been introduced to the market, known as wide band-gap (WBG) devices [5]. They offer higher breakdown voltage, lower on-state resistance, operation under higher temperatures and faster switching transients [23]. Their capabilities opens for new possibilities in power electronic applications and designs. Currently, the two most promising WBG materials are galium nitride (GaN) and silicon carbide (SiC) [22]. The development show great potential, and the devices are suitable for many different applications [24, 25, 26]. However, since the component price is higher than for conventional semiconductor devices, the benefits of the new technology must be exploited with resulting benefit for the total system. One such benefit could be that the size of passive elements such as filters decrease with increasing switching frequency. Moreover, as the devices can operate under higher temperatures, the requirement for heatsink design can be lowered. This allows for converters with higher power density.

The gate driver is the circuitry that controls the turn-on and turn-off switching transient of semiconductor switching devices. To fully utilize the potential of WBG devices, such as the SiC MOSFET, proper gate drivers must be designed. For traditional semiconductor devices, all parts of the switching transient can be controlled separately by the gate driver. However, due to the increased switching speed of WBG devices, time delays and accuracy makes the control strategies challenging. New gate driver topologies that are able to control the fast switching transients of WBG are therefore vital to push the performance of the devices to the limit.

This master thesis continues the work that was done in the specialization project [1]. In the specialization project, a new gate driver topology was presented and evaluated through laboratory work and simulations. Results in terms of delay time as a function of load current was presented for turn-on and turn-off both from lab work and simulations. In the master thesis, the gate driver performance is further investigated in terms of junction temperature dependency, the SPICE simulation model that was used in the specialization project have been improved to avoid convergence errors, and the impact time delay minimization has on the output voltage and load current quality is investigated.

### 1.2 Objectives

In this master thesis the main objectives are to:

- Present the development of WBG devices and discuss the areas where they are useful.

- Present and discuss gate drivers in general and to give an overview of the state-of-the-art.

- Propose and discuss a new gate driver topology aiming for delay time minimization.

- Evaluate the performance of the new gate driver through laboratory work.

- Investigate and improve the non-continuous behaviour of the SiC MOSFET SPICE model that is provided by the manufacturer.

- Investigate the impact delay time minimization gate drivers have on the output voltage and line current quality.

- Propose functionality to realize adaptive gate driving based on load current measurements.

### **1.3 Report Outline**

The thesis is divided into 8 chapters to cover the objectives. The first chapter is the introduction. Then, in Chapter 2, an overview of semiconductor basics are provided. The chapter presents the basics in semiconductor physics and uses it to describe the operation principle of the MOSFET including switching transients. In the last part of the chapter, WBG devices are presented and compared to traditional semiconductor materials.

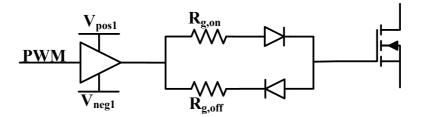

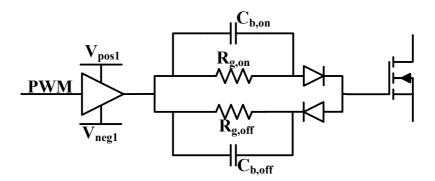

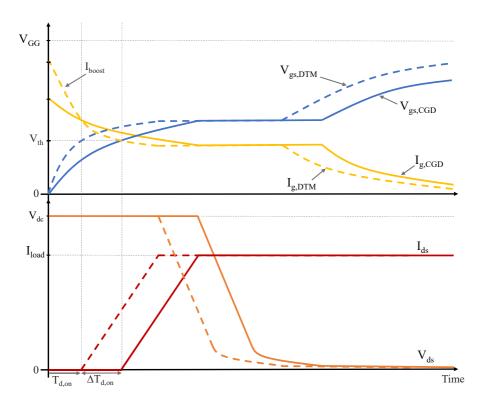

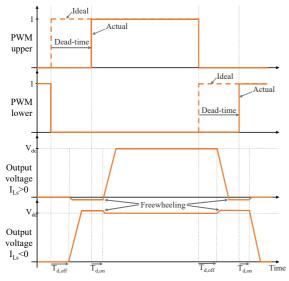

Chapter 3 presents gate drivers. First, a conventional gate driver is presented as it makes the benchmark for the other gate driver topologies in this thesis. Then, state-of-the-art gate drivers from literature are presented and discussed. Finally, a new gate driver topology, termed the multistage driver, is proposed.

In Chapter 4, the SPICE model that is provided by the manufacturer for the chosen SiC MOSFET is investigated. The model tended to run into convergence errors in the specialization project. Therefore, the model structure is investigated and improvements are proposed. The work have resulted in an Abstract submission for the ICSCRM 2019 conference in Kyoto, Japan in September 2019 which can be found in Appendix A.2.

Chapter 5 and 6 presents the work and results that was done for the paper that was presented at ECCE Asia in Busan in May 2019. The paper is found in Appendix A.1. In Chapter 5, the experimental work is presented. Here, the multistage driver is evaluated both for load current and junction temperature dependency. In Chapter 6, the impact delay time minimization gate drivers have on the output voltage and line current quality is investigated through simulations.

In Chapter 7 the multistage driver is made adaptive based on load current measurements. The chapter presents a control circuit that takes in current measurements and provides a voltage reference to the existing PCB. The performance is evaluated through experimental work and compared to the conventional gate driver and the results from Chapter 5.

Finally, in Chapter 8, the conclusions from the master thesis is drawn. In addition, further work is suggested based on the findings in the thesis.

# Chapter 2

### Semiconductor device theory

Silicon (Si) technology is dominating as the most used semiconductor in power electronic components. However, as the components are reaching their performance limit, the industry is looking for new semiconductor materials. The goal is to make new components with the right characteristics to allow the ongoing development of power electronics in terms of efficiency, increasing switching frequency and higher temperature operation. The result is the introduction of the wide band-gap (WBG) semiconductors. In this chapter, the basics for understanding semiconductors are presented.

### 2.1 Basics

For a current to flow in a material, charge carriers must be available and free to flow when an electric field is applied. For good conductors, such as metals, the free carrier density (electrons) is high, which gives low resistance. The free carrier density in a metal is a material constant and cannot be changed. For semiconductors such as silicon on the other hand, the carrier density can be changed if impurities are introduced or high electric fields are applied. For impurities, either atoms with fewer or more valence electrons can be introduced to the semiconductor material. If an introduced atom have fewer valence electrons, it will absorb one of the free electrons from another semiconductor atom giving an apparent positive charge that is free to move. This is referred to as a hole, and the semiconductor is said to be p-doped as the majority carrier is a positive charge. If an atom with more valence electrons are introduced, the extra electrons will be free to move in the semiconductor. This gives a higher free electron density and the semiconductor is said to be n-doped [3].

When a p-doped and an n-doped layer is created in the same semiconductor crystal, a pn junction is formed. In the junction, majority carriers will diffuse to the other side. At equilibrium this creates ionized, immobile impurities on each side of the junction. The width of this area is referred to as the depletion layer. On the p-doped side of the junction, but within the depletion layer, there will then be a negative space charge. For the n-doped side it will be opposite with a positive space charge. The charges will create an electric

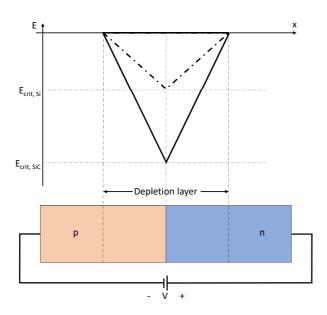

Figure 2.1: Pn junction and critical electrical field for Si and SiC.

field as shown in Figure (2.1). The slope of the electric field is proportional to the space charges in the depletion layer, which is depending on the doping level [3]. The space charges in the depletion layer is assumed to be evenly distributed in Figure (2.1), giving a linear electric field. The pn junction with the solid line must then have a higher doping level than the one with the dotted line. If the peak electric field is higher than the critical field of the semiconductor  $E_{crit}$ , the junction will start to conduct current in the reverse direction. This is termed reverse breakdown or avalanche breakdown and must be avoided as the high voltage and current leads to a large heat dissipation that can destroy the device if it is not reduced. Different semiconductors have different critical electric fields, for instance do silicon carbide (SiC) have a higher critical field than Si.

When a voltage is applied in the reverse bias direction of the pn junction (positive voltage on the n-doped side), more charge will diffuse over the junction. This will create a wider depletion layer which results in a higher peak electric field, as the slope of the electric field will have the same characteristic as before. The relationship between the applied voltage and the electric field in the semiconductor is given by Equation (2.1), where DL indicates the depletion layer.

$$V = -\int_{DL} E(x)dx \tag{2.1}$$

The breakdown voltage can be found by evaluating the expression when the peak electric field reaches the critical value. For two semiconductors with the same critical electric field, but with different doping level, the one with the highest doping level will have the lowest breakdown voltage. However, as previously mentioned, the one with the higher doping level will have a lower resistance.

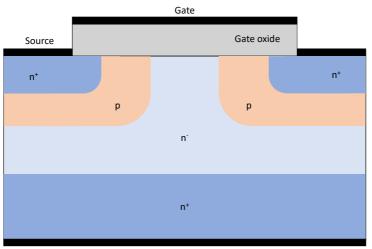

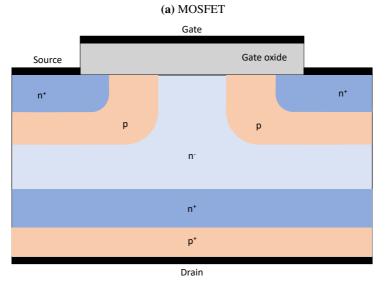

Drain

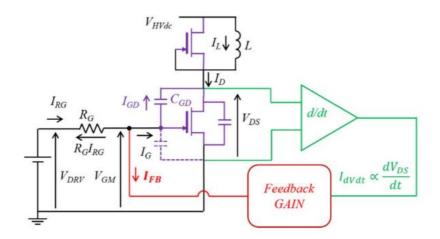

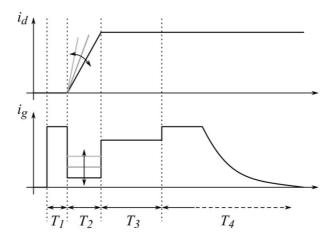

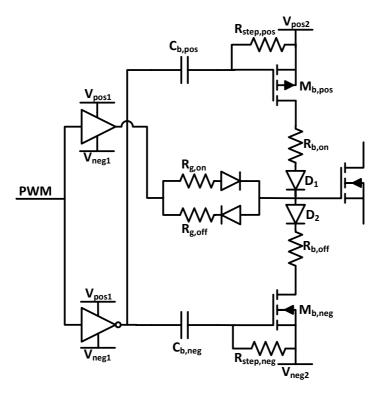

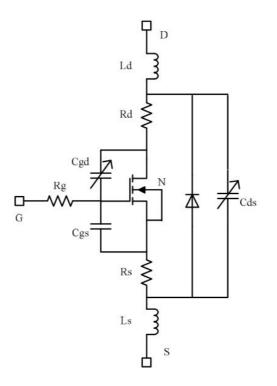

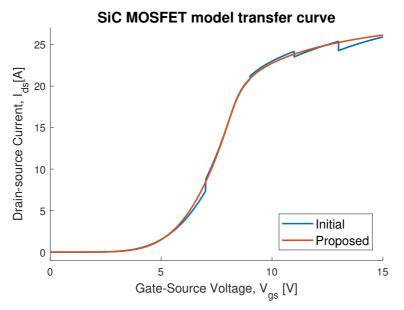

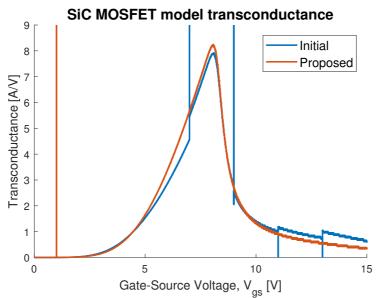

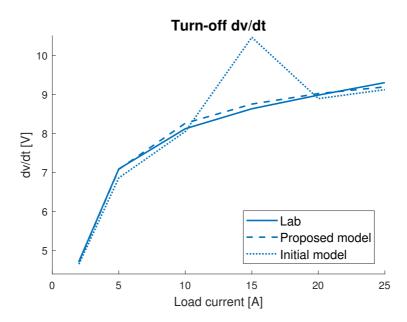

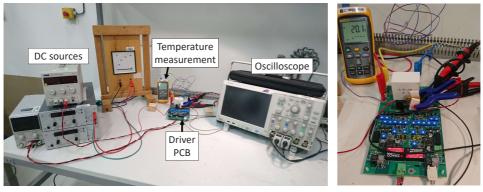

Figure 2.2: Semiconducture structures for MOSFET and IGBT.