Lyder Rumohr Blingsmo

# Comparison between Si MOSFETs and GaN HEMTs with special emphasis on low load problems occuring in the LLC resonant converter

Master's thesis in Energi og miljø Supervisor: Roy Nilsen, Tore Marvin Undeland, Ole Christian Spro

June 2019

Master's thesis

NDrwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Lyder Rumohr Blingsmo

# Comparison between Si MOSFETs and GaN HEMTs with special emphasis on low load problems occuring in the LLC resonant converter

Master's thesis in Energi og miljø Supervisor: Roy Nilsen, Tore Marvin Undeland, Ole Christian Spro June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

# Preface and acknowledgements

This thesis is written at Norwegian University of Science and Technology(NTNU) during the spring of 2019. It entails 30 credits (ECTS) and represents the final requirement for a degree in Master of Technology with the program Energy and Environmental Engineering with specialization in Electrical Energy Engineering.

The thesis is written in cooperation with Eltek AS in Drammen. Thank you to Erik Myhre, Ibrahim Abuishmais, Morten Hostvedt and Thomas Olsen at Eltek for helping me when I had questions. Thank you also to my supervisors at NTNU, Tore Marvin Undeland and Ole Christian Spro for helpful feedback and valuable input during the semester.

Lyder Rumohr Blingsmo, Trondheim, June 2019

Lyder Rought Blingsuc

# Summary

Rectifiers for supplying data center with power from the grid are subject to many requirements, one of which is very high efficiency. One of the most common converter architectures consists of a PFC rectifier stage, used for achieving sinusoidal mains current, followed by a DC-link and a LLC resonant converter for the DC-DC conversion. This topology is already quite efficient. However, one possible solution to increasing the efficiency further is lowering the on-state resistance of the transistors used. Regular silicon(Si) metal-oxide-semiconductor field-effect transistors(MOSFET) however are quickly approaching their theoretical limit in terms of tradeoff between die size and on-state resistance. To reduce on-state resistance further, the die size must then be increased. An increased die size comes with the disadvantage of large terminal capacitances, which can lead to problems.

One of the main enabling technologies for increased efficiency is therefore gallium nitride(GaN) high electron mobility transistors(HEMT). This is because they have smaller terminal capacitances for the same on-state resistance, owing to superior material properties. It is expected that replacing the Si MOSFETs in the LLC converter with GaN HEMTs could improve efficiency, while also avoiding the some of the problems that could occur with excessively large output capacitances. Especially low load regulation problems is considered in this regard.

In this report, only the LLC converter will be considered. The PFC converter will not be discussed. More specifically the LLC topology with a half-bridge structure at the input will be considered. On the secondary side a full-bridge diode-rectifier is used. Design methods, transfer functions, zero-voltage switching, operation modes and low load problems are discussed. Other broad topics such as control is only briefly mentioned. Si MOSFETs and GaN HEMTs are the only transistor types considered.

This report starts with a literature study on GaN devices, more specifically GaN HEMT. In the second part the LLC series resonant topology is discussed. Possible implementation of new GaN-switches in the LLC converter is researched. A direct comparison between GaN HEMTs and silicon MOSFETS is done. Special emphasis is put on considerations that are important to soft-switching topologies such as the LLC converter. Simulations in LTSPICE are done to validate some of the discussed concepts, especially the derived transfer function from the fundamental harmonic approximation(FHA), which shows good results. Lab measurements are also done, and it is seen that the GaN HEMT can improve upon the low load problems occurring in the LLC converter when using Si MOSFETs. The results show that this is achieved with the same degree of efficiency, and using GaN HEMTs the efficiency might even be increased.

What is written here is based on a project report previously done by the same author [1].

# Sammendrag

Det stilles store krav til likerettere brukt til å forsyne datasentere med kraft. Et av kravene er høy virkningsgrad. En av de vanligste topologiene brukt til dette formålet består av en PFC-likeretter, for å få sinusformet strøm fra nettet, etterfulgt av en DC-link og en LLC-konverter for DC-DC omforming. Disse strømforsyningene har allerede høy virkningsgrad. En mulighet for å øke virkningsgraden ytterligere er allikevel å redusere motstanden til transistorene når de er skrudd på. Men vanlige silisium(Si) 'metal-oxide-semiconductor field-effect transistorer'(MOSFET) nærmer seg raskt sin teoretiske grense for sammenhengen mellom on-state motstand og fysisk størrelse. For å redusere motstanden til en gitt silisium MOSFET enda mer, er da eneste mulig å øke størrelsen. Økt størrelse betyr større parasittiske kapasitanser, noe som kan gi problemer.

En av de viktigste teknologiene for økt virkningsgrad er derfor galliumnitrid(GaN) 'high electron mobility transistor' (HEMT). GaN har overlegne materialegenskaper, og kan derfor gi transistorerer med bedre egenskaper. Dette inkluderer blant annet mindre parasittiske kapasitanser for den samme on-state motstanden. Det forventes derfor at å erstatte Si MOSFET med GaN HEMT i LLComformeren kan bedre virkningsgraden, samtidig som man unngår problemene som oppstår ved alt for store utgangskapasitanser. Spesielt lavlast-reguleringsproblemer forventes å kunne bli bedre.

I denne rapporten vil bare LLC-omformeren bli vurdert. PFC-leddet diskuteres ikke. Mer spesifikt er det LLC-topologien med en halvbro-struktur på inngangen, og fullbro diodelikeretter som blir brukt. Designmetodikk, transferfunksjoner, nullspennings-svitsjing, driftmoduser og lavlastproblemer diskuteres. Andre store tema slik som for eksempel kontroll av omformeren nevnes bare kort. Si MOSFET og GaN HEMT er de eneste transistortypene som blir vurdert.

Rapporten begynner med et litteraturstudie på GaN transistor, og da spesielt GaN HEMT. Dette er etterfulgt av det litteraturstudie på LLC-serie-resonansomformeren. Mulig implementering av GaN HEMT i LLC-omformeren blir undersøkt. GaN HEMT og silisium MOSFETer sammenlignes direkte ved hjelp av 'figure of merit'(FOM). Spesiell vekt legges på hensyn som er viktig for 'softswitching'-topologier slik som LLC-konverteren. Gjennom simulering i LTspice valideres noen av de diskuterte konseptene, spesielt FHA-antagelsen i utledningen av transferfunksjonen. Transferfunksjon blir også målt i lab. Resultatene viser god overensstemmelse mellom teori og simulering og lab. En LLC-modul med GaN HEMT og en annen LLC-modul med Si MOSFETer sammenlignes også gjennom labmålinger. Her vises det at GaN HEMT kan forbedre lavlastproblemene samtidig som virkningsgraden forblir den samme, og kan til og med økes noe.

Det som er skrevet her er basert på et tidligere prosjekt av samme forfatter [1].

# Contents

|          | List | le of Contents                                                                                                                                                 | i |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1        | Intr | roduction 1                                                                                                                                                    | L |

|          | 1.1  | Motivation                                                                                                                                                     | L |

|          | 1.2  | Scope of report                                                                                                                                                | 2 |

|          | 1.3  | Project outline                                                                                                                                                | 3 |

| <b>2</b> | Gal  | N-transistors 5                                                                                                                                                | 5 |

|          | 2.1  | Material parameters                                                                                                                                            | 3 |

|          |      | 2.1.1 The band-gap                                                                                                                                             | 3 |

|          |      | 2.1.2 Critical field                                                                                                                                           | 3 |

|          |      | 2.1.3 Electron mobility $\ldots \ldots \ldots$ | 3 |

|          |      | 2.1.4 Relative permittivity                                                                                                                                    | 7 |

|          |      | 2.1.5 Thermal conductivity                                                                                                                                     | 7 |

|          | 2.2  | Transistor parameters                                                                                                                                          | 7 |

|          |      | 2.2.1 Breakdown voltage                                                                                                                                        | 7 |

|          |      | 2.2.2 On-state resistance                                                                                                                                      | 3 |

|          |      | 2.2.3 Stored output charge                                                                                                                                     | 3 |

|          |      | 2.2.4 Gate charge                                                                                                                                              | 3 |

|          | 2.3  | Types of GaN HEMT                                                                                                                                              | ) |

|          |      | 2.3.1 Cascode structure $\ldots \ldots \ldots$ | ) |

|          |      | 2.3.2 Altering the gate structure                                                                                                                              | ) |

|          | 2.4  | Nonlinearities                                                                                                                                                 | L |

|          | 2.5  | Comparison of a Si MOSFET and GaN transistor of similar rating . 12                                                                                            | 2 |

|          | 2.6  | Figure of merit(FOM) 14                                                                                                                                        | 1 |

|          | 2.7  | Challenges and design considerations                                                                                                                           | 5 |

| 3        | LLC  | C resonant converter 17                                                                                                                                        | 7 |

|          | 3.1  | Fourier transform of input voltage                                                                                                                             | 3 |

|          | 3.2  | Transfer functions                                                                                                                                             | 3 |

|          | 3.3  | Operating areas                                                                                                                                                | ) |

|          |      | 3.3.1 Gain                                                                                                                                                     | ) |

|          |      | $3.3.2$ Phase shift $\ldots \ldots 23$                                                   | 3 |

|          | 3.4            | Zero voltage and zero current switching                     |                                                | 24        |

|----------|----------------|-------------------------------------------------------------|------------------------------------------------|-----------|

|          | 3.5            | Deadtime  .  .  .  .  .  .  .  .  .                         |                                                | 27        |

|          | 3.6            | Operation modes $\ldots \ldots \ldots \ldots \ldots \ldots$ |                                                | 28        |

|          | 3.7            | Optimal design considerations                               |                                                | 30        |

|          | 3.8            | Snubbers                                                    |                                                | 32        |

|          | 3.9            | Other topology variations                                   |                                                | 33        |

|          |                | 3.9.1 Full bridge on input side                             |                                                | 33        |

|          |                | 3.9.2 Split capacitor and clamping diodes                   |                                                | 33        |

|          |                | 3.9.3 Inluding the magnetic components in                   | the transformer $\ . \ . \ .$                  | 33        |

|          |                | 3.9.4 Choice of rectifier at output                         |                                                | 34        |

|          | 3.10           | ) Low load problems                                         |                                                | 35        |

|          |                | 3.10.1 Control problems                                     |                                                | 36        |

|          |                | 3.10.2 Effect of parasitics                                 |                                                | 36        |

|          |                | 3.10.3 Time domain analysis of effect of $C_{jn}$           | and $C_{oss}$                                  | 39        |

|          |                | 3.10.4 Long deadtime                                        |                                                | 41        |

|          |                | 0                                                           |                                                |           |

| <b>4</b> | $\mathbf{Sim}$ | nulation                                                    |                                                | <b>45</b> |

|          | 4.1            | Comparison of gain characteristics                          |                                                | 46        |

|          |                |                                                             |                                                |           |

| <b>5</b> | Lab            | b measurements                                              |                                                | 49        |

|          | 5.1            | About the modules and lab setup                             |                                                | 49        |

|          | 5.2            | Preliminary test                                            |                                                | 55        |

|          | 5.3            | Changing $R_{ds,on}$                                        |                                                | 55        |

|          | 5.4            | Deadtime                                                    |                                                | 57        |

|          |                | 5.4.1 Delay time at low loads $\ldots$ $\ldots$ $\ldots$    |                                                | 57        |

|          |                | 5.4.2 Delay time as a function of current .                 |                                                | 60        |

|          |                | 5.4.3 Improving efficiency by taking adva                   | ntage of GaN HEMTs                             |           |

|          |                | shorter delay time                                          |                                                | 62        |

|          | 5.5            | Other measures for increasing the efficiency                |                                                | 66        |

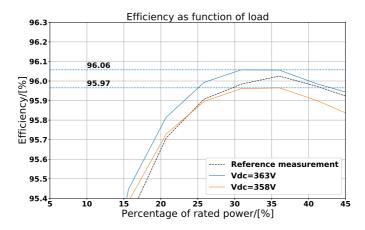

|          |                | 5.5.1 Changing the DC-link voltage at input                 | 1t                                             | 67        |

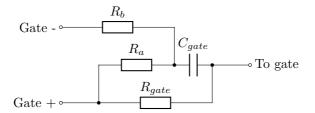

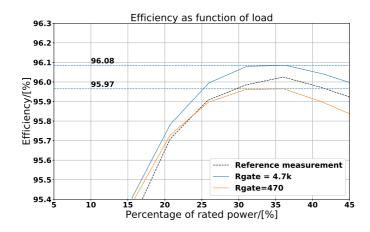

|          |                | 5.5.2 Changing $R_{gate}$                                   |                                                | 67        |

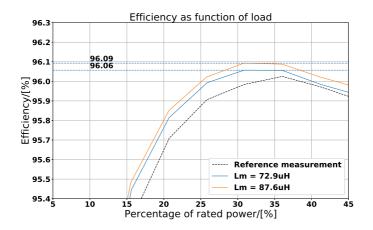

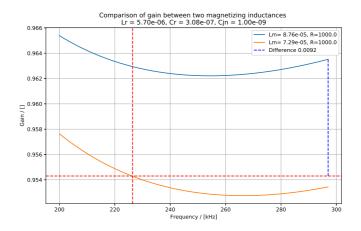

|          |                | 5.5.3 Changing magnetizing inductance, $L$                  | М                                              | 70        |

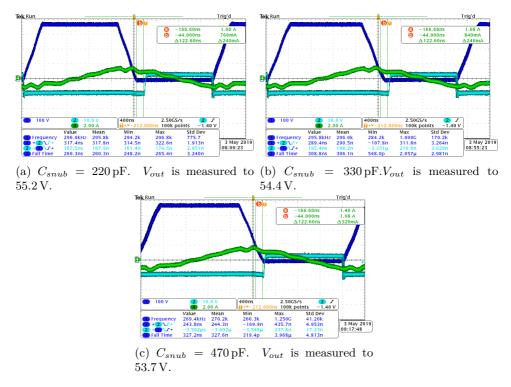

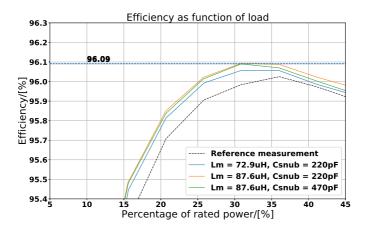

|          |                | 5.5.4 Changing snubber capacitances, $C_{snu}$              | <i>b</i> • • • • • • • • • • • • • • • • • • • | 72        |

|          |                | 5.5.5 Extra cable                                           |                                                | 74        |

|          | 5.6            | Transfer function                                           |                                                | 76        |

|          | 5.7            | Tolerances                                                  |                                                | 78        |

|          |                | 5.7.1 Yokogawa WT3000 precision power a                     | nalyzer                                        | 78        |

|          |                | 5.7.2 Tektronix oscilloscope and probes                     |                                                | 78        |

|          |                | 5.7.3 Flir ONE thermocamera                                 |                                                | 79        |

| 6        | Con            | nclusion and further work                                   |                                                | 81        |

| 5        | 6.1            | Conclusion                                                  |                                                | 81        |

|          | 6.2            | Further work                                                |                                                | 83        |

|          |                |                                                             |                                                |           |

| A        | ppen           | ndices                                                      |                                                | 85        |

| Α | Simulation model | 87 |

|---|------------------|----|

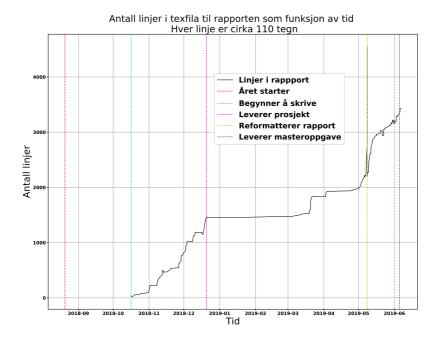

| в | Report progress  | 89 |

# List of Tables

| 2.1        | Silicon and gallium nitride comparison of important material properties for transistors. [11]                                                                     | 6        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

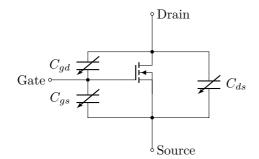

| 2.2        | Parasitic capacitances in a Si MOSFET. The same model holds for GaN HEMT.                                                                                         | 8        |

| 2.3        | Transistor properties comparison between Si MOSFET and GaN HEMT $70 \mathrm{m}\Omega$ from Infineon.                                                              | 12       |

| 2.4        | Figure of merit for Si MOSFET and GaN HEMT $70\mathrm{m}\Omega$ from Infine<br>on.                                                                                | 15       |

| 3.1        | Equivalent capacitance seen at the secondary side of the transformer caused by junction capacitances of the diodes for different rectifier solutions [41].        | 39       |

| 4.1        | Component parameters chosen for simulation of transfer function.<br>Upper part gives chosen parameters. Lower part is the variables<br>introduced in section 3.3. | 45       |

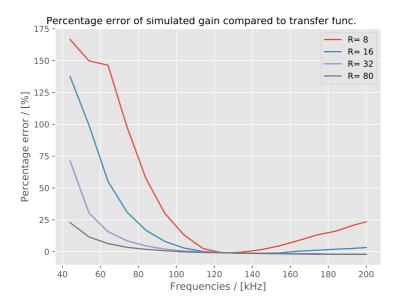

| 4.2        | Validity range of the transfer function if 25% is the accepted error margin.                                                                                      | 48       |

| 5.1        | Component values used in the LLC converter during lab measurements. Resonant frequencies, $m$ and $Q$ are calculated as explained                                 |          |

|            | in section 3.3                                                                                                                                                    | 49       |

| 5.2<br>5.3 | Equipment used in lab measurements                                                                                                                                | 52<br>56 |

| 5.4        | Measured peak efficiencies with two different on-state resistances for<br>both Si MOSFET and GaN HEMT.                                                            | 57       |

| 5.5        | Measured delay times at no load with two different on-state resis-<br>tances for both Si MOSFET and GaN HEMT.                                                     | 59       |

| 5.6        | Measured delay times for the Si MOSFET $31 \text{ m}\Omega$ and GaN HEMT $31 \text{ m}\Omega$ when setting the output voltage reference to $48 \text{ V}$         | 60       |

| 5.7  | Measured turn-on delay times with old and new deadtime curves                              |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | used in the DSP                                                                            | 63 |

| 5.8  | Measured drain-source voltage fall time for GaN HEMT $31\mathrm{m}\Omega$ with             |    |

|      | the new deadtime curve and $L_M = 87.6 \mu\text{H}$ for three different snub-              |    |

|      | ber capacitances. Also $V_{dc} = 363 \text{ V}, R_{gate} = 470 \Omega \dots \dots \dots$   | 73 |

| 5.9  | Measured output voltages for GaN HEMT $31 \text{ m}\Omega$ with the new dead-              |    |

|      | time curve and $L_M = 87.6 \mu\text{H}$ for three different snubber capaci-                |    |

|      | tances. Also $V_{dc} = 363 \text{ V}, R_{gate} = 470 \Omega \dots \dots \dots \dots \dots$ | 74 |

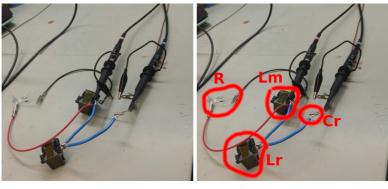

| 5.10 | Components used in measurement of transfer function                                        | 77 |

|      |                                                                                            |    |

| 6.1  | Summary of all efficiency improvements made with the GaN module.                           | 82 |

# List of Figures

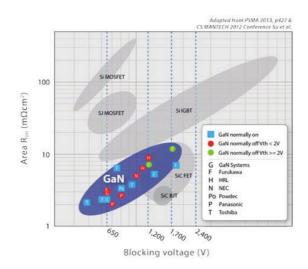

| 1.1 | The great promise of wide band-gap semiconductors. Obtained from [5]                                                                                                                                                | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

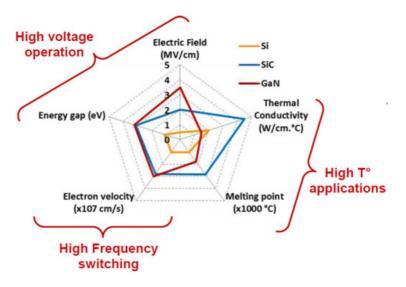

| 2.1 | Material properties of gallium nitride(GaN), silicon(Si) and silicon carbide(SiC) Obtained from [14].                                                                                                               | 7  |

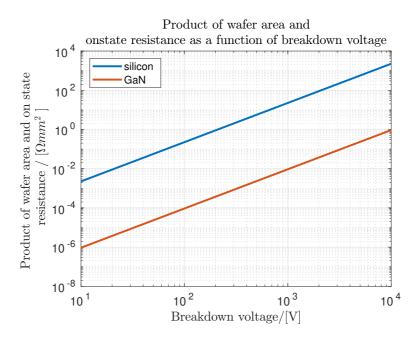

| 2.2 | Theoretical limit of the product of area and on-state resistance as a function of breakdown voltage for silicon and GaN.                                                                                            | 9  |

| 2.3 | Parasitic capacitances of a Si MOSFET. The same model is valid for<br>GaN HEMT. The capacitances are nonlinear and vary as a function                                                                               |    |

| 9.4 | of the applied drain-source voltage                                                                                                                                                                                 | 9  |

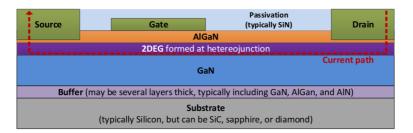

| 2.4 | Structure of depletion-mode GaN HEMT. Layers are not to scale.<br>Obtained from [13]                                                                                                                                | 10 |

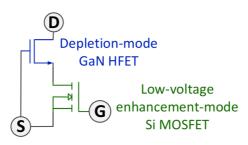

| 2.5 | Cascode structure for the GaN HEMT. This makes it a normally-off device. Obtained from [13]                                                                                                                         | 10 |

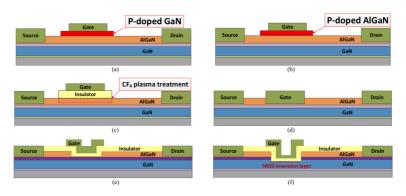

| 2.6 | Different structure alternatives to make the GaN HEMT normally-<br>off. a) p-doped GaN. b) p-doped AlGaN. c) Plasma treatment. d)<br>Recessed gate. e) Insulated recessed gate. f) Hybrid MIS-HFET.                 |    |

|     | Obtained from [12]                                                                                                                                                                                                  | 11 |

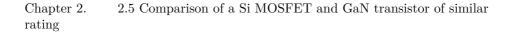

| 2.7 | Comparison of the capacitances as a function of the drain-to-source voltage. Figures are taken from the respective datasheets [18] [19].                                                                            | 13 |

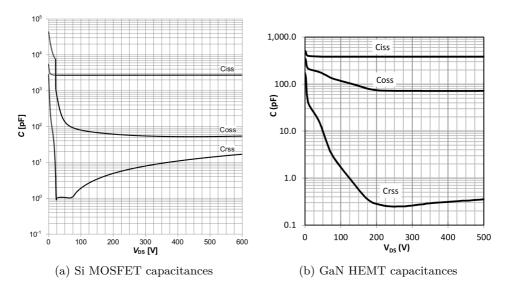

| 2.8 | Comparison of the stored energy as a function of the drain-to-source voltage. Figures are taken from the respective datasheets [18] [19].                                                                           | 13 |

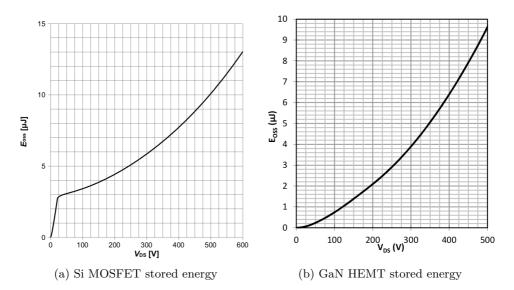

| 2.9 | Comparison of the reverse conduction characteristics. Figures are taken from the respective datasheets [18] [19]                                                                                                    | 14 |

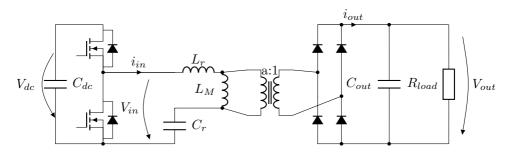

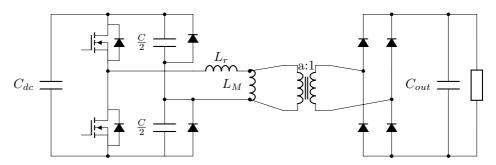

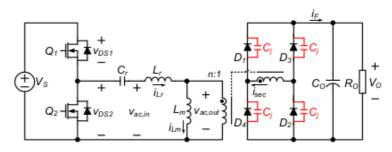

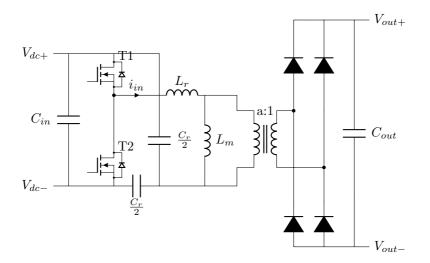

| 3.1 | LLC converter with a half bridge structure at the input and full-<br>bridge diode rectifier at the output.                                                                                                          | 17 |

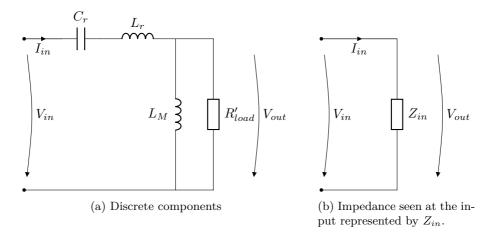

| 3.2 | Equivalent circuit of the LLC converter using the fundamental har-                                                                                                                                                  |    |

| 3.3 | monic approximation (FHA). Used for obtaining the transfer function.                                                                                                                                                | 19 |

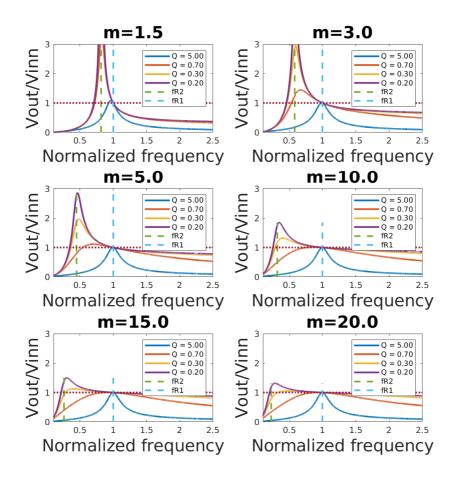

|     | Gain curves of the transfer function $\frac{V_{out}}{V_{in}}$ for different component parameters.                                                                                                                   | 22 |

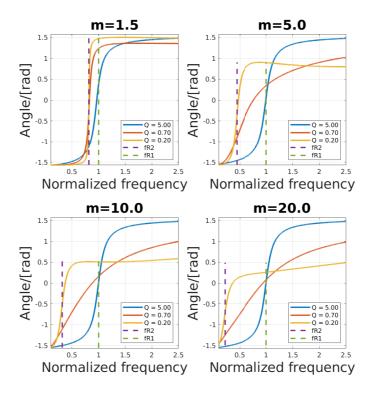

| 3.4 | Phase shift between voltage and current as seen from the midpoint<br>of the half-bridge at the input of the LLC resonant tank. Shows the<br>different operating areas and whether they are inductive or capacitive. | 24 |

|     |                                                                                                                                                                                                                     |    |

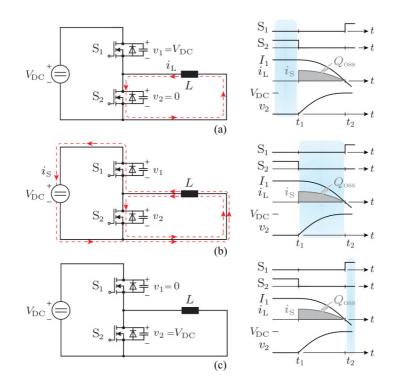

| 3.5  | A zero voltage switching transition. a) The lower switch is on, and<br>the upper is off. b) The lower switch is turned off, since the in-                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | ductance clamps the current, it starts to commutate from the lower                                                                                                   |     |

|      | switch to the upper. c) The voltage across the upper switch reaches                                                                                                  |     |

|      | zero, and it can be turned on with ZVS. The current still flows in the                                                                                               |     |

|      | same direction or is zero depending on operating point. Obtained                                                                                                     |     |

|      | from [17]                                                                                                                                                            | 25  |

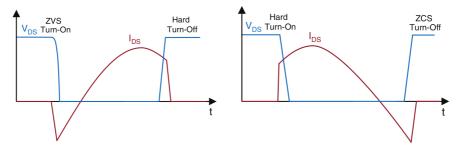

| 3.6  | Switching waveforms for a transistor in a resonant converter. Ob-                                                                                                    |     |

|      | tained from [11]                                                                                                                                                     | 26  |

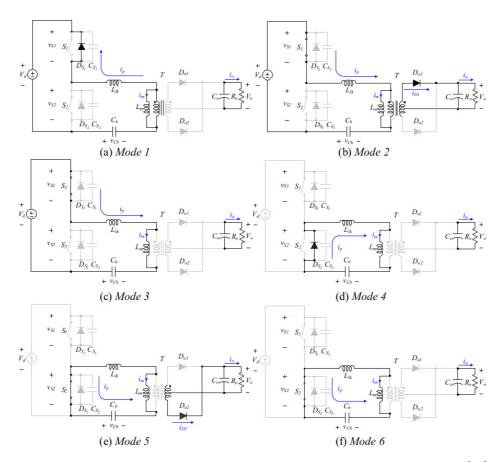

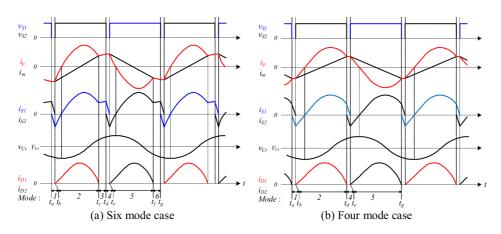

| 3.7  | Six different operating modes for a LLC converter. Obtained from                                                                                                     |     |

|      | [24]                                                                                                                                                                 | 29  |

| 3.8  | Analytical waveforms for the LLC resonant converter. $V_{Cr}$ is the                                                                                                 |     |

|      | same is $V_{Cb}$ in fig. 3.7. Obtained from [24].                                                                                                                    | 30  |

| 3.9  | Gain curves as a function of Q and m.                                                                                                                                | 31  |

| 3.10 |                                                                                                                                                                      |     |

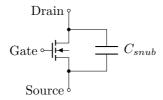

|      | capacitances of the transistor is not included in the figure                                                                                                         | 32  |

| 3.11 | LLC converter with split capacitor and clamping diodes to limit                                                                                                      |     |

|      | overcurrent and reduce current ripple.                                                                                                                               | 34  |

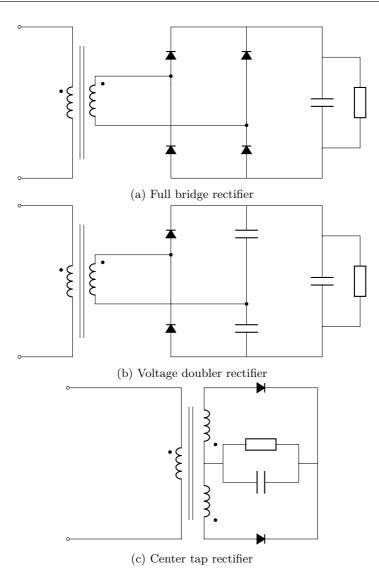

| 3.12 | Three possible rectifier solutions.                                                                                                                                  | 35  |

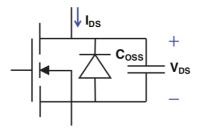

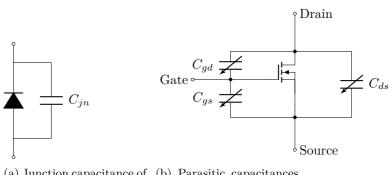

|      | Diode parasitic capacitance $C_{jn}$ , and Si MOSFET parasitic capac-                                                                                                |     |

|      | itances, $C_{gs}$ , $C_{ds}$ and $C_{gd}$ . $C_{oss} = C_{gd} + C_{ds}$ . The Si MOSFET                                                                              |     |

|      | model is also valid for GaN HEMT                                                                                                                                     | 37  |

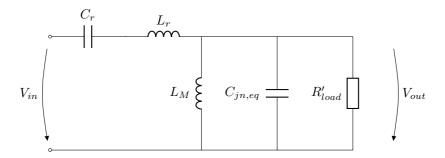

| 3.14 | Equivalent circuit for the LLC converter from the fundamental har-                                                                                                   |     |

|      | monic approximation (FHA) analysis with the junction capacitances                                                                                                    |     |

|      | included                                                                                                                                                             | 37  |

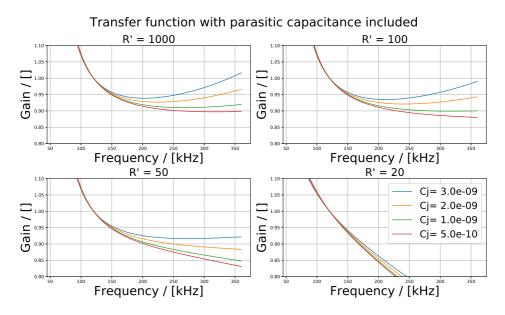

| 3.15 | Gain of the transfer function $\frac{V_{out}}{V_{in}}$ with the effect of parasitic junction capacitance of the rectifier diodes included. The legend given is valid |     |

|      |                                                                                                                                                                      |     |

|      | for all figures                                                                                                                                                      | 38  |

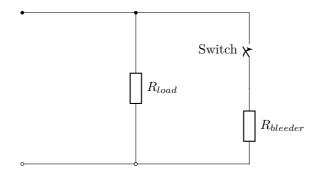

| 3.16 | Dummy load as possible solution to low load problems. Sometimes                                                                                                      |     |

|      | also called a bleeder resistance. It is connected in parallel with the                                                                                               |     |

|      | load resistance, and connected when needed by closing the switch.                                                                                                    | 39  |

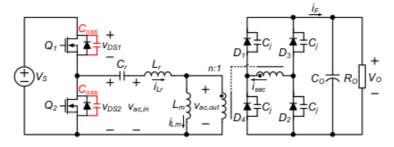

| 3.17 | Equivalent circuits of the LLC converter with different parasitic ef-                                                                                                | 10  |

| 0.10 | fects included. Figures obtained from [43]                                                                                                                           | 40  |

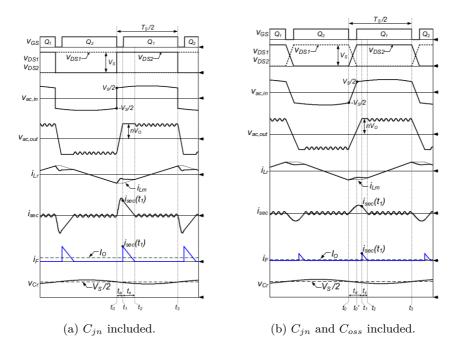

| 3.18 | Waveforms for the LLC converter for two different cases. One where                                                                                                   |     |

|      | only the parasitic effect of the output diodes junction capacitance<br>effect $C_{i}$ is included. And one where both $C_{i}$ and parasitie as                       |     |

|      | effect $C_{jn}$ is included. And one where both $C_{jn}$ and parasitic capacitances of the transistors, $C_{oss}$ is included. Obtained from [43].                   | 41  |

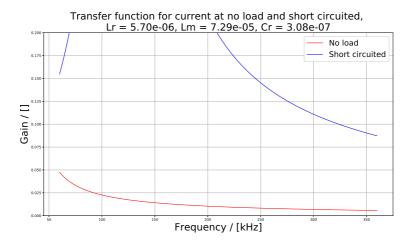

| 3 10 | Current into the resonant tank at no load and short circuit condition                                                                                                | -11 |

| 5.19 | for different frequencies. Calculated from the transfer function $\frac{I_{in}}{V_{in}}$ .                                                                           | 42  |

|      | for universe requestions. Conclusive norm the statistic function $V_{in}$                                                                                            | 12  |

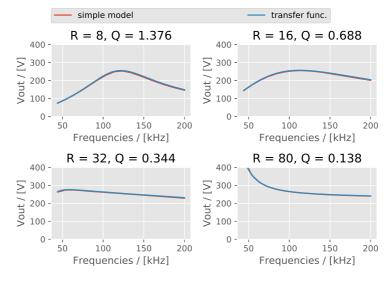

| 4.1  | Comparison of gain curves for the simulated simple model, complete                                                                                                   |     |

|      | model and theoretical transfer function from the fundamental har-                                                                                                    |     |

|      | monic approximation with <b>sinusoidal</b> input voltage. Resistances                                                                                                |     |

|      | are given in $\Omega$                                                                                                                                                | 46  |

|      |                                                                                                                                                                      |     |

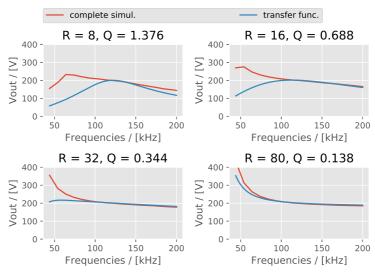

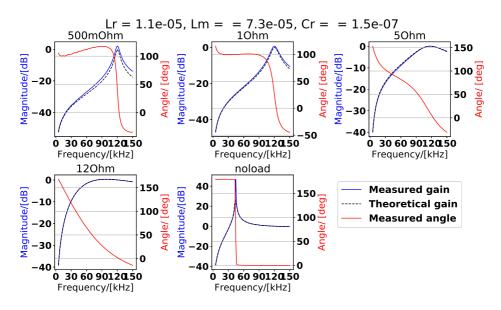

| <ul> <li>4.3 Deviation of simulated gains for the complete model compared to calculated transfer function with square wave input voltage. Resistances are given in Ω</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2  | Comparison of gain curves for the complete model and theoreti-<br>cal transfer function from the fundamental harmonic approximation<br>with square wave input voltage. Resistances are given in $\Omega$ | 47 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

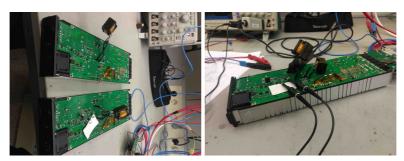

| <ul> <li>5.1 The two modules used, shown side by side from the bottom side. The resonant inductor L<sub>r</sub> is what sticks out. It is desoldered to be able to attach a current probe. The rest of the resonant tank and the transistors is inside the module</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.3  | Deviation of simulated gains for the complete model compared to calculated transfer function with <b>square wave</b> input voltage. Re-                                                                  |    |

| The resonant inductor $L_r$ is what sticks out. It is desoldered to be<br>able to attach a current probe. The rest of the resonant tank and<br>the transistors is inside the module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                                                                                                                                                                                          | 40 |

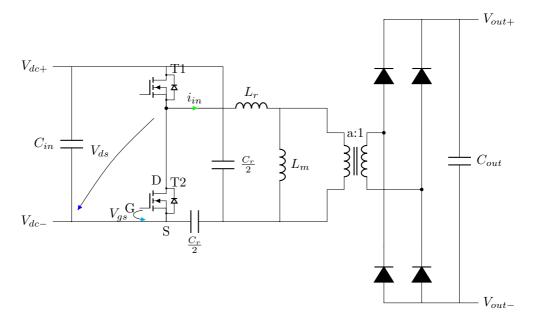

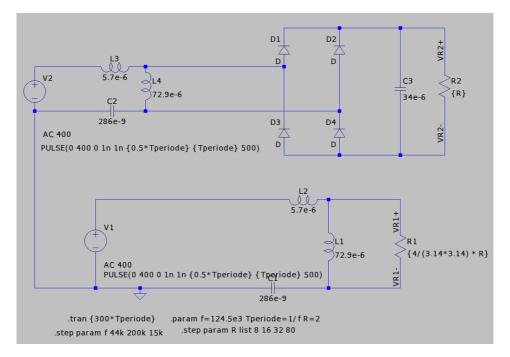

| 5.2 Simplified schematic of the LLC converter used. Snubber and junction capacitances are not shown. Also auxillary circuits such as gate drivers, fan etc. are not shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.1  | The resonant inductor $L_r$ is what sticks out. It is desoldered to be<br>able to attach a current probe. The rest of the resonant tank and                                                              | 50 |

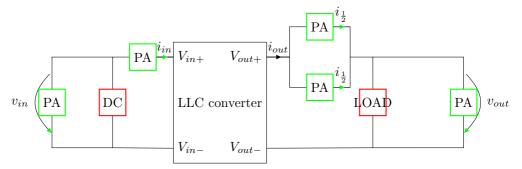

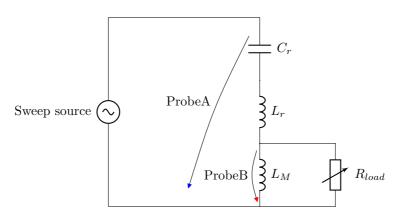

| 5.3       Schematic and picture of the lab setup.       54         5.4       The two modules used for lab measurements compared by an efficiency test to make sure they are comparable before further testing.       55         5.5       Measured peak efficiency for Si MOSFET and GaN HEMT with two different on-state resistances.       56         5.6       Explanation schematic with colors of the labeling of the oscilloscope curves from measurements.       58         5.7       Delay time at no load for Si MOSFET and GaN HEMT at both 70 mΩ and 31 mΩ.       59         5.8       Delay time for both Si MOSFET and GaN HEMT 31 mΩ when trying to regulate the output voltage to 48V.       61         5.9       Theoretical and measured delay times as a function of current into the resonant tank.       61         5.10       Typical channel reverse characteristics of GaN HEMT 70 mΩ taken from the respective datasheet [19]. The voltage given on the curves is the gate-source voltage bias.       64         5.11       New and old deadtime curves used for controlling the switching in the DSP.       64         5.13       Measured peak efficiency for GaN HEMT 31 mΩ.       65         5.14       Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.       66         5.14       Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.       66         5.16       Me                                   | 5.2  | Simplified schematic of the LLC converter used. Snubber and junction capacitances are not shown. Also auxillary circuits such as gate                                                                    | 53 |

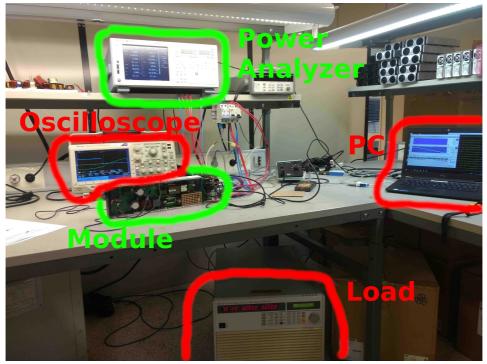

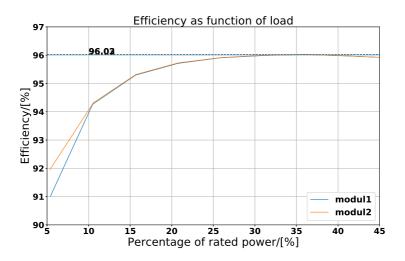

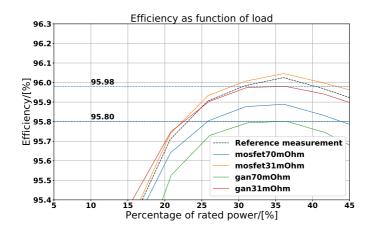

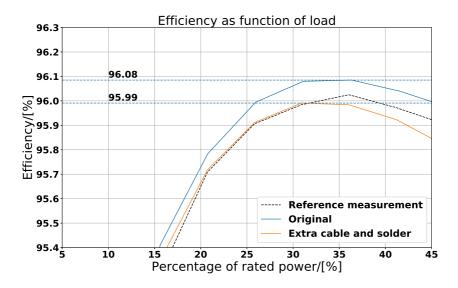

| ciency test to make sure they are comparable before further testing. 55<br>Measured peak efficiency for Si MOSFET and GaN HEMT with two<br>different on-state resistances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.3  |                                                                                                                                                                                                          | 54 |

| 5.5 Measured peak efficiency for Si MOSFET and GaN HEMT with two<br>different on-state resistances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.4  |                                                                                                                                                                                                          |    |

| 5.6Explanation schematic with colors of the labeling of the oscilloscope<br>curves from measurements.585.7Delay time at no load for Si MOSFET and GaN HEMT at both<br>70 mΩ and 31 mΩ.595.8Delay time for both Si MOSFET and GaN HEMT 31 mΩ when<br>trying to regulate the output voltage to 48V.615.9Theoretical and measured delay times as a function of current into<br>the resonant tank.615.10Typical channel reverse characteristics of GaN HEMT 70 mΩ taken<br>from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias.635.11New and old deadtime curves used for controlling the switching in<br>the DSP.645.12Turn on delay time for both new and old deadtime curve at no load<br>and peak efficiency load with the GaN HEMT 31 mΩ.655.13Measured peak efficiency for GaN HEMT 31 mΩ for two different<br>deadtime curves in the DSP.665.15Oscilloscope waveforms for three different dc-link voltages at the<br>input of the LLC converter.685.16Measured peak efficiencies for GaN HEMT 31 mΩ with the new<br>deadtime curve for two different input voltages and $R_{gate} = 470 \Omega$ .685.17Typical output characteristics for GaN HEMT 70 mΩ.68                                                                                                                                                                                                                                                                                                                                                      | 5.5  | Measured peak efficiency for Si MOSFET and GaN HEMT with two                                                                                                                                             | 55 |

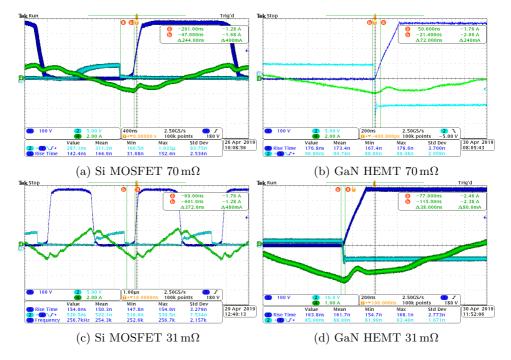

| curves from measurements.       58         5.7       Delay time at no load for Si MOSFET and GaN HEMT at both<br>70 mΩ and 31 mΩ.       59         5.8       Delay time for both Si MOSFET and GaN HEMT 31 mΩ when<br>trying to regulate the output voltage to 48V.       61         5.9       Theoretical and measured delay times as a function of current into<br>the resonant tank.       61         5.10       Typical channel reverse characteristics of GaN HEMT 70 mΩ taken<br>from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias.       63         5.11       New and old deadtime curves used for controlling the switching in<br>the DSP.       64         5.12       Turn on delay time for both new and old deadtime curve at no load<br>and peak efficiency load with the GaN HEMT 31 mΩ.       65         5.13       Measured peak efficiency for GaN HEMT 31 mΩ for two different<br>deadtime curves in the DSP.       66         5.14       Thermal photos of the diodes in antiparallel to the transistors for<br>two different deadtime curves used in the DSP.       66         5.15       Oscilloscope waveforms for three different dc-link voltages at the<br>input of the LLC converter.       68         5.16       Measured peak efficiencies for GaN HEMT 31 mΩ with the new<br>deadtime curve for two different input voltages and $R_{gate} = 470 \Omega$ .       68         5.17       Typical output characteristics for GaN HEMT 70 mΩ.       68 <td>50</td> <td></td> <td>56</td> | 50   |                                                                                                                                                                                                          | 56 |

| 5.7Delay time at no load for Si MOSFET and GaN HEMT at both<br>70 mΩ and 31 mΩ.595.8Delay time for both Si MOSFET and GaN HEMT 31 mΩ when<br>trying to regulate the output voltage to 48V.615.9Theoretical and measured delay times as a function of current into<br>the resonant tank.615.10Typical channel reverse characteristics of GaN HEMT 70 mΩ taken<br>from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias.625.11New and old deadtime curves used for controlling the switching in<br>the DSP.645.12Turn on delay time for both new and old deadtime curve at no load<br>and peak efficiency load with the GaN HEMT 31 mΩ.655.13Measured peak efficiency for GaN HEMT 31 mΩ for two different<br>deadtime curves in the DSP.665.14Thermal photos of the diodes in antiparallel to the transistors for<br>two different deadtime curves used in the DSP.665.15Oscilloscope waveforms for three different dc-link voltages at the<br>input of the LLC converter.685.16Measured peak efficiencies for GaN HEMT 31 mΩ with the new<br>deadtime curve for two different input voltages and $R_{gate} = 470 \Omega$ .685.17Typical output characteristics for GaN HEMT 70 mΩ.64                                                                                                                                                                                                                                                                                                                                  | 5.0  |                                                                                                                                                                                                          | 58 |

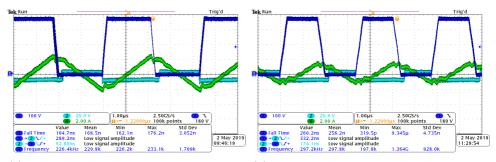

| $70 \ {\rm m}\Omega$ and $31 \ {\rm m}\Omega$ 595.8Delay time for both Si MOSFET and GaN HEMT $31 \ {\rm m}\Omega$ when<br>trying to regulate the output voltage to $48V$ .615.9Theoretical and measured delay times as a function of current into<br>the resonant tank.615.10Typical channel reverse characteristics of GaN HEMT $70 \ {\rm m}\Omega$ taken<br>from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias.635.11New and old deadtime curves used for controlling the switching in<br>the DSP.645.12Turn on delay time for both new and old deadtime curve at no load<br>and peak efficiency load with the GaN HEMT $31 \ {\rm m}\Omega$ for two different<br>deadtime curves in the DSP.665.14Thermal photos of the diodes in antiparallel to the transistors for<br>two different deadtime curves used in the DSP.665.15Oscilloscope waveforms for three different dc-link voltages at the<br>input of the LLC converter.685.16Measured peak efficiencies for GaN HEMT $31 \ {\rm m}\Omega$ with the new<br>deadtime curve for two different input voltages and $R_{gate} = 470 \ {\Omega}$ .685.17Typical output characteristics for GaN HEMT $70 \ {\rm m}\Omega$ .685.17Typical output characteristics for GaN HEMT $70 \ {\rm m}\Omega$ .68                                                                                                                                                                                                                                                          | 5.7  |                                                                                                                                                                                                          | 00 |

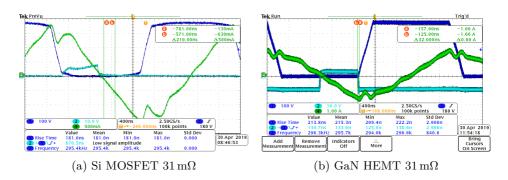

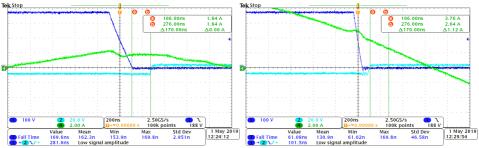

| 5.8Delay time for both Si MOSFET and GaN HEMT 31 mΩ when<br>trying to regulate the output voltage to 48V.615.9Theoretical and measured delay times as a function of current into<br>the resonant tank.615.10Typical channel reverse characteristics of GaN HEMT 70 mΩ taken<br>from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias.635.11New and old deadtime curves used for controlling the switching in<br>the DSP.645.12Turn on delay time for both new and old deadtime curve at no load<br>and peak efficiency load with the GaN HEMT 31 mΩ.655.13Measured peak efficiency for GaN HEMT 31 mΩ for two different<br>deadtime curves in the DSP.665.14Thermal photos of the diodes in antiparallel to the transistors for<br>two different deadtime curves used in the DSP.665.16Measured peak efficiencies for GaN HEMT 31 mΩ with the new<br>deadtime curve for two different input voltages and $R_{gate} = 470 \Omega$ .685.17Typical output characteristics for GaN HEMT 70 mΩ.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | •                                                                                                                                                                                                        | 59 |

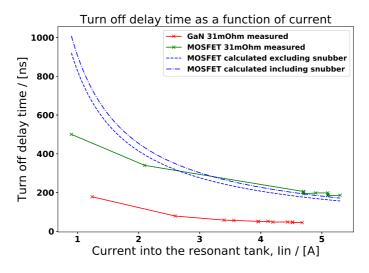

| <ul> <li>5.9 Theoretical and measured delay times as a function of current into the resonant tank</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.8  | Delay time for both Si MOSFET and GaN HEMT $31\mathrm{m}\Omega$ when                                                                                                                                     | 61 |

| <ul> <li>5.10 Typical channel reverse characteristics of GaN HEMT 70 mΩ taken from the respective datasheet [19]. The voltage given on the curves is the gate-source voltage bias.</li> <li>5.11 New and old deadtime curves used for controlling the switching in the DSP.</li> <li>5.12 Turn on delay time for both new and old deadtime curve at no load and peak efficiency load with the GaN HEMT 31 mΩ.</li> <li>5.13 Measured peak efficiency for GaN HEMT 31 mΩ for two different deadtime curves in the DSP.</li> <li>5.14 Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.</li> <li>5.15 Oscilloscope waveforms for three different dc-link voltages at the input of the LLC converter.</li> <li>5.16 Measured peak efficiencies for GaN HEMT 31 mΩ with the new deadtime curve for two different input voltages and R<sub>gate</sub> = 470 Ω.</li> <li>5.17 Typical output characteristics for GaN HEMT 70 mΩ. Obtained from datasheet [19].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.9  | Theoretical and measured delay times as a function of current into                                                                                                                                       |    |

| from the respective datasheet [19]. The voltage given on the curves<br>is the gate-source voltage bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                                                                                                                                                                                          | 61 |

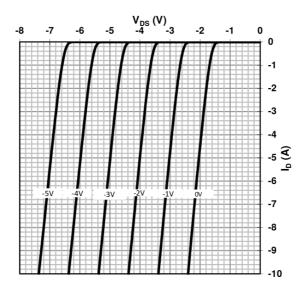

| <ul> <li>5.11 New and old deadtime curves used for controlling the switching in the DSP.</li> <li>5.12 Turn on delay time for both new and old deadtime curve at no load and peak efficiency load with the GaN HEMT 31 mΩ.</li> <li>5.13 Measured peak efficiency for GaN HEMT 31 mΩ for two different deadtime curves in the DSP.</li> <li>5.14 Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.</li> <li>5.15 Oscilloscope waveforms for three different dc-link voltages at the input of the LLC converter.</li> <li>5.16 Measured peak efficiencies for GaN HEMT 31 mΩ with the new deadtime curve for two different input voltages and R<sub>gate</sub> = 470 Ω.</li> <li>5.17 Typical output characteristics for GaN HEMT 70 mΩ. Obtained from datasheet [19].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.10 | from the respective datasheet [19]. The voltage given on the curves                                                                                                                                      |    |

| the DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F 11 |                                                                                                                                                                                                          | 63 |

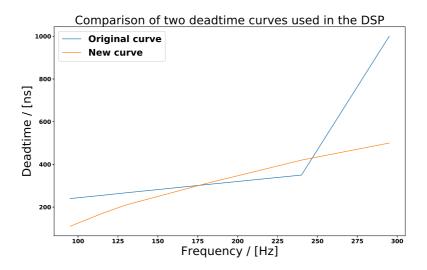

| <ul> <li>5.12 Turn on delay time for both new and old deadtime curve at no load and peak efficiency load with the GaN HEMT 31 mΩ.</li> <li>5.13 Measured peak efficiency for GaN HEMT 31 mΩ for two different deadtime curves in the DSP.</li> <li>5.14 Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.</li> <li>5.15 Oscilloscope waveforms for three different dc-link voltages at the input of the LLC converter.</li> <li>5.16 Measured peak efficiencies for GaN HEMT 31 mΩ with the new deadtime curve for two different input voltages and R<sub>gate</sub> = 470 Ω.</li> <li>5.17 Typical output characteristics for GaN HEMT 70 mΩ. Obtained from datasheet [19].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.11 | · · · · ·                                                                                                                                                                                                | 64 |

| and peak efficiency load with the GaN HEMT $31 \text{ m}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.12 |                                                                                                                                                                                                          | 01 |

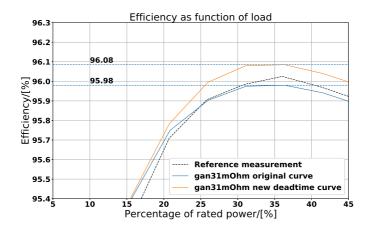

| deadtime curves in the DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                          | 65 |

| <ul> <li>5.14 Thermal photos of the diodes in antiparallel to the transistors for two different deadtime curves used in the DSP.</li> <li>5.15 Oscilloscope waveforms for three different dc-link voltages at the input of the LLC converter.</li> <li>5.16 Measured peak efficiencies for GaN HEMT 31 mΩ with the new deadtime curve for two different input voltages and R<sub>gate</sub> = 470 Ω.</li> <li>5.17 Typical output characteristics for GaN HEMT 70 mΩ. Obtained from datasheet [19].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.13 | 1 0                                                                                                                                                                                                      |    |

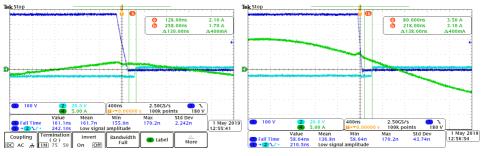

| two different deadtime curves used in the DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                                                                                                                                                          | 66 |

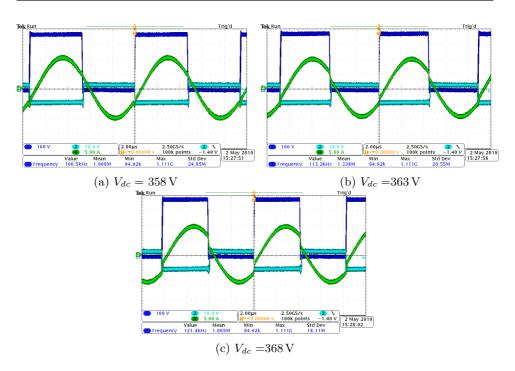

| <ul> <li>5.15 Oscilloscope waveforms for three different dc-link voltages at the input of the LLC converter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.14 |                                                                                                                                                                                                          | 66 |