# Asbjørn Engmark Espe

# Real-Time Ray Tracing of Animated Sparse Voxel Octrees on FPGA

Master's thesis in Cybernetics and Robotics June 2019

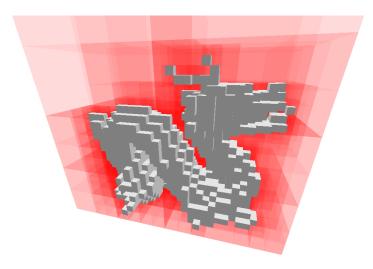

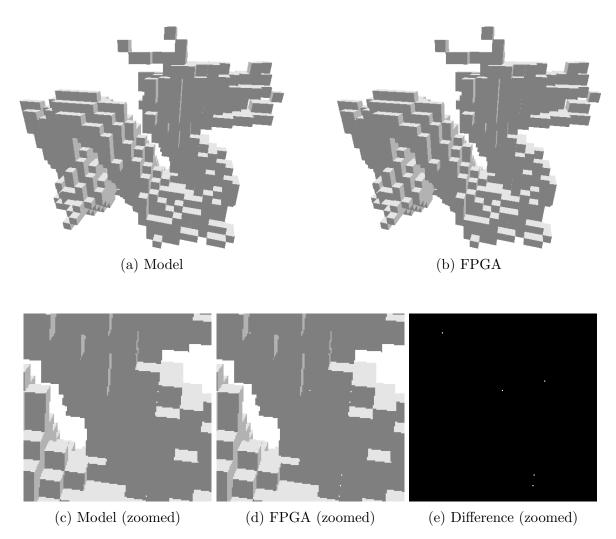

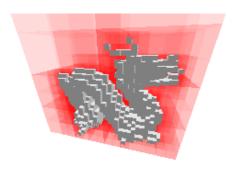

# Real-Time Ray Tracing of Animated Sparse Voxel Octrees on FPGA

Asbjørn Engmark Espe

Master of Science in Embedded Systems

Submission date: June 2019

Supervisors: Sverre Hendseth, ITK

$\hbox{\it Øystein Gjermundnes, IES}$

Norwegian University of Science and Technology Department of Engineering Cybernetics

# Problem statement

Ray tracing is a rendering technique in which rays are cast from a viewpoint into a scene in order to generate images. Briefly stated, it entails tracing in reverse the paths that physical light particles would take. The technique is viewed as an alternative to rasterisation rendering, which is the *de facto* standard in computer graphics today. The latter is based on the rasterisation of primitives—most commonly triangles.

As a consequence of the technique's physical nature, ray tracing implementations will often produce more realistic images, and will generally result in a more visually and physically correct rendition of a given scene, when compared to rasterisation rendering. Caused in part by the fact that the objects to be rendered may be modelled perfectly in a geometric sense, but also because physical effects such as reflection, refraction, and transparency are much easier to model and implement than for rasterisation rendering.

An octree is a space partitioning scheme that divides three-dimensional space into a tree structure. It is analogous to a binary tree in three dimensions, meaning that each node in the tree may have up to eight children. A sparse voxel octree—abbreviated SVO—is a specific flavour of octree often used in conjunction with ray tracing. What sets an SVO apart from the generalised octree is that the data structure itself is employed to natively represent volumetric data. Physical objects may be approximated by treating the SVO leaf nodes as either filled or empty (void) voxels. Several solutions have been proposed in the relevant literature for efficient real-time rendering of SVOs using ray tracing.

A drawback of using SVOs to store and render volumetric data is that the data is inherently static; SVOs by themselves do not support any form of animation or efficient data mutation. In order to use this data structure in the rendering of realistic real-time graphics, there is a need for animation—most notably rotation, translation, but also general affine transformations. This is necessary if ray tracing is to be used to render realistic, animated worlds, and not just static scenes.

In the project thesis, the student explored animation of SVO data from a theoretical standpoint, and formulated a general technique suitable for hardware implementation to achieve this. In the master's thesis, the student will continue within the same field of research, and:

- Review existing literature on the subject of hardware ray tracing.

- Investigate whether a hardware implementation for real-time ray tracing of SVO data is feasible, and formulate the specification and design of such a system.

- If feasible, demonstrate hardware ray tracing of SVO data. Explore the possibility of extending such a hardware implementation to support animation of SVO data.

# Abstract

Ray tracing is a technique used in computer graphics to render virtual scenes consisting of three-dimensional volumetric models. These volumetric models may be formulated as geometric primitives, or as data structures such as the optimised voxel-based model known as the sparse voxel octree (SVO). One of the main limitations today when using ray tracing to render SVOs is that the octree data structure is inherently static. In other words, efficient animation of a scene to be rendered is challenging to achieve. In the project thesis, a general method for animation of such SVO models was derived.

In this master's thesis, a hardware accelerator for ray tracing of animated sparse voxel octrees is designed and largely implemented. The hardware implementation runs on an FPGA, and its design employs the method from the project thesis in in order to facilitate animation. The proposed solution also makes use of two additional established algorithms as foundation: an efficient method for traversal of octrees, and a memory-efficient data structure scheme for storing SVO data.

Initially, an analysis of requirements is conducted and a specification of the desired system is introduced. The system design is then derived, in which the functionality of the system and its constituent modules are determined and discussed. Ultimately, an implementation of this design is presented and examined. Certain parts of the design were not fully implemented due to time constraints, such as the modules that provide the arithmetic operations necessary for animation. The overall result is the system design of a fully-fledged hardware accelerator for real-time ray tracing of animated SVO models, and a partial implementation of this design.

A number of implementation configurations are tested. Running at 100 MHz with 16 SVO traversal cores, the implementation is shown to be capable of rendering static SVO models with a frame rate of  $26.91\,\mathrm{Hz}$  at  $1280\times720$  resolution. With a sufficient number of traversal cores, the implementation appears to be limited by external factors—namely the IO performance of the development board. It is concluded that real-time performance rendering animated SVO models is achievable.

# Sammendrag

Ray tracing—eller *strålesporing*—er en teknikk benyttet i datagrafikk med det mål å tegne en virtuell verden bestående av tredimensjonale volumetriske modeller. Disse modellene kan være uttrykt som geometriske objekter, eller som abstrakte datastrukturer slik som den optimaliserte voxel-baserte modelltypen kalt sparse voxel octree (SVO). En av hovedbegrensningene forbundet med strålesporing av slike SVO-modeller i dag er at datastrukturen i utgangspunktet ikke har noen støtte for animasjon. I prosjektoppgaven ble det utviklet en generell metode for animering av slike SVO-modeller.

I denne masteroppgaven blir en hardwareakselerator for strålesporing av animerte SVO-modeller spesifisert, utviklet og, i stor grad, implementert. Implementasjonen kjøres på en FPGA, og spesifikasjonen benytter metoden utviklet i prosjektoppgaven for å legge til rette for animasjon. Som grunnlag benyttes ytterligere to etablerte algoritmer: en effektiv metode for traversering av octree-strukturer, og en minne-effektiv datastruktur for lagring av SVO-data.

I første omgang utføres en analyse av systemets krav, og en spesifikasjon av den ønskede løsningen presenteres. Systemets utforming utledes deretter, hvor dets funksjonalitet og interne moduler diskuteres og bestemmes. Til slutt presenteres en implementasjon av dette systemet. Visse deler av systemets implementasjon ble ikke ferdigstilt grunnet tidsbegrensninger, inkludert deler av funksjonaliteten knyttet til animasjon. Resultatet er en komplett spesifikasjon og utforming av et system for hardwareakselerert strålesporing av animerte SVO-modeller i sanntid, og en delvis implementasjon av denne spesifikasjonen.

En rekke ulike konfigurasjoner av implementasjonen testes. Ved en klokkefrekvens på  $100\,\mathrm{MHz}$  og med 16 kjerner for SVO-traversering, viser systemet seg i stand til å tegne statiske SVO-modeller med en bildefrekvens på  $26.91\,\mathrm{Hz}$  og en oppløsning på  $1280\times720$ . Dersom et tilstrekkelig antall kjerner for SVO-traversering implementeres, blir det demonstrert at systemet begrenses av eksterne faktorer—nemlig ytelsen forbundet med IO på utviklingskortet. Det konkluderes at sanntidsytelse under tegning av animerte SVO-modeller er oppnåelig.

# **Preface**

This master's thesis shares the subject of research—and in some sense builds upon—the work done in the project thesis [1]. Its approach to the subject at hand, however, differs, and the thesis should therefore be regarded as its own work separate from the project thesis. Moreover, while much of the background matter is shared between the theses, the actual work done and the results presented are thoroughly different in nature. The idea behind the project and master's thesis was conceived in the autumn of 2017 during a conversation after class with my lecturer at the time, Øystein Gjermundnes. I presented my idea to him, and he enthusiastically encouraged me to pursue it as a subject for a project and master's thesis. He also agreed to take the role as my cosupervisor when the time came. I formulated the general gist of the problem statements for both theses around this time.

Much thought has been put into determining how the workload should be divided between the project thesis and the master's thesis. After hearing some horror stories of students putting too much work into the project thesis, and leaving too little for the master's thesis, I ended up partitioning the subject matter into two distinct segments. The project thesis was to be an almost purely theoretical venture, in which some general method or technique would be derived. The master's thesis would be of a much more practical nature, and its work would be comprised of a distinctly different set of problems related to implementation of a system which may incorporate the work done in the project thesis in some way. This distribution of work ensures that both the project thesis and master's thesis may be treated as independent works.

The reason that ray tracing has been chosen as the subject matter for both theses is that I have had a fascination for the technique for many years. Ray tracing appeals to me because of the elegance and simplicity of its implementations—qualities that seem to go missing from traditional rasterisation rendering implementations. This thesis has a particular focus on hardware design of a ray tracing system. The process of designing a digital hardware system of substantial size is very different from the software design flow I'm used to. A considerably larger chunk of the time must be set aside for planning and verification of the system, since the turnaround time for trying and failing is significantly longer. Digital hardware design is challenging, but at the same time highly rewarding; it is immensely satisfying to see the module you have been designing for the last week actually working as intended.

My principal supervisor for this thesis, Sverre Hendseth, has assumed a more supplementary role during the design work than he had in the project thesis. This is mostly due to the fact that his field of expertise is not directly relevant to the work. The occasional meetings I have had with him have been jovial check-ups and geared towards how I am doing with the report work. It should be noted, however, that the

tips he has given me regarding general work planning and organisation have helped considerably during the planning phase of the project.

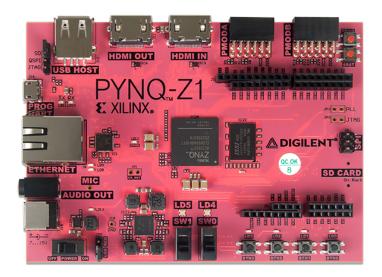

In his capacity as my co-supervisor, Øystein Gjermundnes has had a much more prominent part advising me over the course of this thesis than he had in the project thesis. He has given me many hardware design tips that have helped me along the way. Moreover, he arranged for me to borrow the development board employed for the design implementation, so that a time-consuming application process could be avoided.

To sum up, I feel I have been very independent during both the design and implementation work, and the writing of the thesis itself. That said, whenever I have been stuck—either technically or motivationally—my supervisors have helped me out with good advice and encouraging words. They have also passionately encouraged me to pursue a PhD degree after this thesis, which I very much look forward to. I therefore want to extend my gratitude to my supervisors, Sverre and Øystein. As was the case for the project thesis, I have had the privilege of doing most of the design work on a personal workstation the offices of Arm Norway, with access to unlimited amounts of caffeine. I wish to thank the wonderful people at Arm who have given me this opportunity. Lastly, I would like to highlight my appreciation for my family and friends. Especially my girlfriend, Rachel, who has consistently kept my spirits up for the duration of the project.

# Contents

| P            | roble | m stat            | sement                                    | iii          |

|--------------|-------|-------------------|-------------------------------------------|--------------|

| $\mathbf{A}$ | bstra | ct                |                                           | $\mathbf{v}$ |

| Sa           | amme  | $\mathbf{endrag}$ |                                           | vii          |

| P            | refac | e                 |                                           | ix           |

| 1            | Intr  | oducti            | ion                                       | 1            |

| 2            | Bac   | kgroui            | $\mathbf{ad}$                             | 3            |

|              | 2.1   | A brie            | ef history of real-time computer graphics | 3            |

|              | 2.2   | Funda             | mental concepts                           | 4            |

|              |       | 2.2.1             | 3D models                                 | 5            |

|              |       | 2.2.2             | Spaces and transforms                     | 6            |

|              |       | 2.2.3             | Computer animation                        | 8            |

|              |       | 2.2.4             | Number representation                     | 10           |

|              |       | 2.2.5             | Task scheduling                           | 13           |

|              |       | 2.2.6             | Memory caching                            | 15           |

|              | 2.3   | Rende             | ering techniques                          | 17           |

|              |       | 2.3.1             | Rasterisation                             | 17           |

|              |       | 2.3.2             | Ray tracing                               | 18           |

|              | 2.4   | Space             | partitioning                              | 20           |

|              |       | 2.4.1             | Octree                                    | 20           |

|              |       | 2.4.2             | Sparse voxel octree                       | 21           |

|              | 2.5   | Digita            | l hardware design                         | 25           |

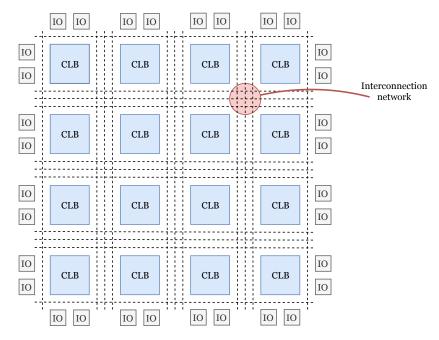

|              |       | 2.5.1             | FPGA                                      | 25           |

|              |       | 2.5.2             | HDL modelling                             | 28           |

|              |       | 2.5.3             | Verification                              | 29           |

|              |       | 2.5.4             | Logic synthesis                           | 30           |

|              |       | 2.5.5             | Communication protocols                   | 31           |

| 3            | Res   | earch (           | $\operatorname{context}$                  | 33           |

|              | 3.1   | Algori            | thms for octree traversal                 | 33           |

|              | 3.2   | Anima             | ation of sparse voxel octrees             | 34           |

|              | 3.3   | Hardw             | vare ray tracing                          | 35           |

|              | 3.4   |                   | works of significance                     | 35           |

| 4 | Esta | ablishe               | ed algorithms chosen as foundation 3                 | 37             |

|---|------|-----------------------|------------------------------------------------------|----------------|

|   | 4.1  | An eff                | icient parametric algorithm for octree traversal     | 37             |

|   |      | 4.1.1                 | Simplified algorithm for the 2D case                 | 38             |

|   |      | 4.1.2                 | Extending the algorithm to octrees                   | 41             |

|   |      | 4.1.3                 | Supporting arbitrary ray directions                  | 43             |

|   | 4.2  | Efficie               | nt sparse voxel octrees                              | 14             |

|   |      | 4.2.1                 | Scheme overview                                      | 14             |

|   | 4.3  | A met                 | hod for rigid-body animation of sparse voxel octrees | 17             |

|   |      | 4.3.1                 | Method overview                                      | 17             |

|   |      | 4.3.2                 | Mathematical formulation                             | 18             |

|   |      | 4.3.3                 | Extending the method to allow anisotropic scaling    | 49             |

|   |      | 4.3.4                 | Optimisations                                        | 50             |

| 5 | Req  | quirem                | ent analysis 5                                       | 53             |

|   | 5.1  | Interp                | retation of the problem statement                    | 53             |

|   | 5.2  | Prima                 | ry functional and non-functional requirements        | 54             |

|   | 5.3  | Furthe                | er requirement specification                         | 55             |

|   |      | 5.3.1                 | System scalability                                   | 55             |

|   |      | 5.3.2                 |                                                      | 56             |

|   |      | 5.3.3                 |                                                      | 58             |

|   |      | 5.3.4                 |                                                      | 60             |

|   |      | 5.3.5                 | Memory latency                                       | 32             |

| 6 | Sys  | $	ext{tem d}\epsilon$ | esign 6                                              | 3              |

|   | 6.1  |                       |                                                      | <sub>3</sub> 3 |

|   |      | 6.1.1                 |                                                      | 34             |

|   | 6.2  | Modul                 | · · · · · · · · · · · · · · · · · · ·                | <sub>35</sub>  |

|   |      | 6.2.1                 |                                                      | 66             |

|   |      | 6.2.2                 |                                                      | 71             |

|   |      | 6.2.3                 |                                                      | 73             |

|   |      | 6.2.4                 |                                                      | 76             |

|   |      | 6.2.5                 |                                                      | 77             |

| 7 | Svs  | tem in                | pplementation 7                                      | <b>7</b> 9     |

|   | 7.1  |                       | •                                                    | 79             |

|   | 7.2  | _                     |                                                      | 31             |

|   |      | 7.2.1                 |                                                      | 31             |

|   | 7.3  | Modul                 | •                                                    | 33             |

|   |      | 7.3.1                 | 1                                                    | 33             |

|   |      | 7.3.2                 | 9                                                    | 35             |

|   |      | 7.3.3                 |                                                      | 36             |

|   |      | 7.3.4                 |                                                      | 37             |

|   |      | 7.3.5                 | O .                                                  | 38             |

|   | 7.4  |                       |                                                      | 38             |

|   |      | 7.4.1                 |                                                      | 39             |

|   |      | 7.4.2                 |                                                      | 90             |

|   | 7.5  | -                     |                                                      | 91             |

|              |            | 7.5.1            | Software modelling                              |   |   |       |   |   |   |   | 91  |

|--------------|------------|------------------|-------------------------------------------------|---|---|-------|---|---|---|---|-----|

|              |            | 7.5.2            | Simulation                                      |   |   | <br>  |   |   |   |   | 91  |

|              |            | 7.5.3            | FPGA prototyping                                |   |   |       |   |   |   |   | 92  |

| 8            | Res        | ults an          | nd discussion                                   |   |   |       |   |   |   |   | 95  |

|              | 8.1        | Timing           | g                                               |   |   | <br>  |   |   |   |   | 95  |

|              |            | 8.1.1            | Critical path and maximum frequency             |   |   | <br>  |   |   |   |   | 96  |

|              | 8.2        | Resour           | rce utilisation                                 |   |   |       |   |   |   |   | 97  |

|              |            | 8.2.1            | Per-module utilisation                          |   |   | <br>  |   |   |   |   | 97  |

|              | 8.3        | Perform          | mance                                           |   |   | <br>  |   |   |   |   | 98  |

|              |            | 8.3.1            | Render times                                    |   |   | <br>  |   |   |   |   | 99  |

|              |            | 8.3.2            | Identifying bottlenecks                         |   |   |       |   |   |   |   | 100 |

|              |            | 8.3.3            | Extrapolating the data                          |   |   |       |   |   |   |   | 102 |

|              | 8.4        |                  | results                                         |   |   |       |   |   |   |   | 102 |

|              | 8.5        |                  | er discussion                                   |   |   |       |   |   |   |   | 104 |

|              | 0.0        | 8.5.1            | Validation with respect to primary requirements |   |   |       |   |   |   |   | 104 |

|              |            | 8.5.2            | Animation                                       |   |   |       |   |   |   |   | 104 |

|              |            | 8.5.3            | Memory                                          |   |   |       |   |   |   |   | 105 |

|              |            | 8.5.4            | Tracing complex scenes                          |   |   |       |   |   |   |   | 106 |

|              |            | 8.5.5            | Algorithmic optimisations                       |   |   |       |   |   |   |   | 107 |

|              |            | 0.0.0            | rigoriumine optimisations                       | • | • | <br>• | • | • | • | • | 101 |

| 9            | Con        | clusio           | ns                                              |   |   |       |   |   |   |   | 109 |

|              | 9.1        | Limita           | ations                                          |   |   |       |   |   |   |   | 110 |

|              | 9.2        | Future           | e work                                          |   | • | <br>  |   | ٠ |   | • | 111 |

| Bi           | bliog      | graphy           |                                                 |   |   |       |   |   |   |   | 113 |

| A            | Atta       | ached 2          | ZIP file contents                               |   |   |       |   |   |   |   | 121 |

|              |            |                  |                                                 |   |   |       |   |   |   |   | 100 |

| В            | Acr        | onyms            | and abbreviations                               |   |   |       |   |   |   |   | 123 |

| $\mathbf{C}$ | Har        | $\mathbf{dware}$ | modules                                         |   |   |       |   |   |   |   | 125 |

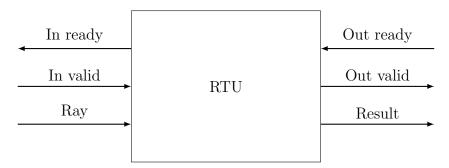

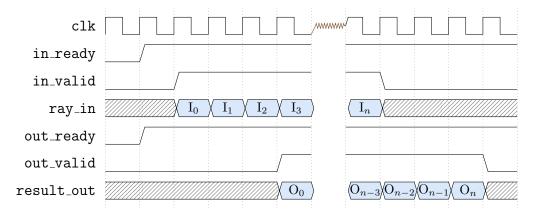

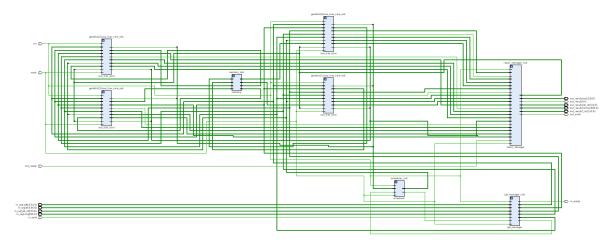

|              | C.1        | RTU t            | op module                                       |   |   |       |   |   |   |   | 125 |

|              | C.2        | Job m            | anager                                          |   |   |       |   |   |   |   | 127 |

|              |            | C.2.1            | Floating-point to fixed-point conversion        |   |   | <br>  |   |   |   |   | 128 |

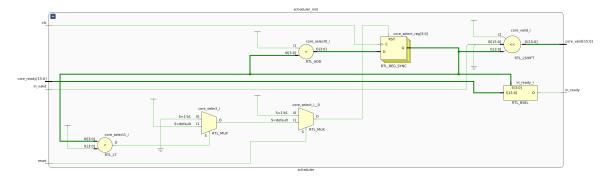

|              | C.3        |                  | ıler                                            |   |   |       |   |   |   |   | 130 |

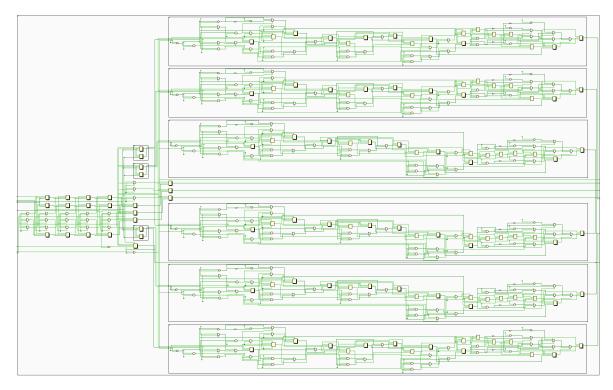

|              | C.4        | SVO t            | raversal core                                   |   |   | <br>  |   |   |   |   | 131 |

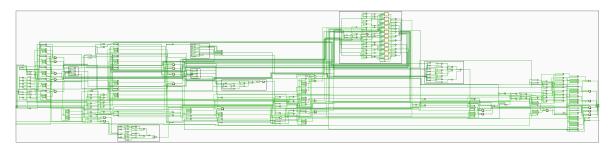

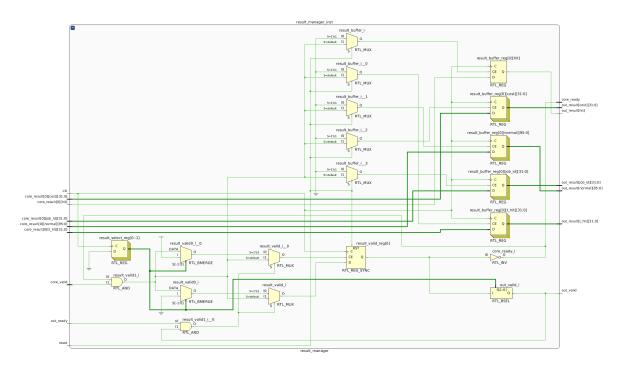

|              | C.5        | Result           | manager                                         |   |   | <br>  |   |   |   |   | 139 |

|              | C.6        |                  | ypes                                            |   |   |       |   |   |   |   | 141 |

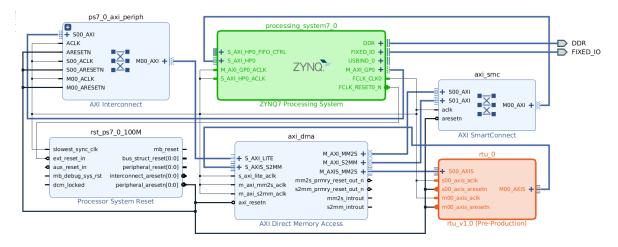

| D            | AX         | [ hardy          | ware modules                                    |   |   |       |   |   |   |   | 143 |

|              |            |                  | op module                                       |   |   |       | _ | - |   |   | 143 |

|              |            |                  | Stream slave module                             |   |   |       |   |   |   |   | 145 |

|              |            |                  | Stream master module                            |   |   |       |   |   |   |   | 146 |

| F            | <b>1/:</b> | ado av           | nthesis reports                                 |   |   |       |   |   |   |   | 149 |

| ت            |            | v                | -                                               |   |   |       |   |   |   |   | 149 |

|              |            |                  | tion report                                     |   |   |       |   |   |   |   |     |

|              | E.2        | $_{\rm 11ming}$  | g summary report                                |   |   |       |   |   |   |   | 153 |

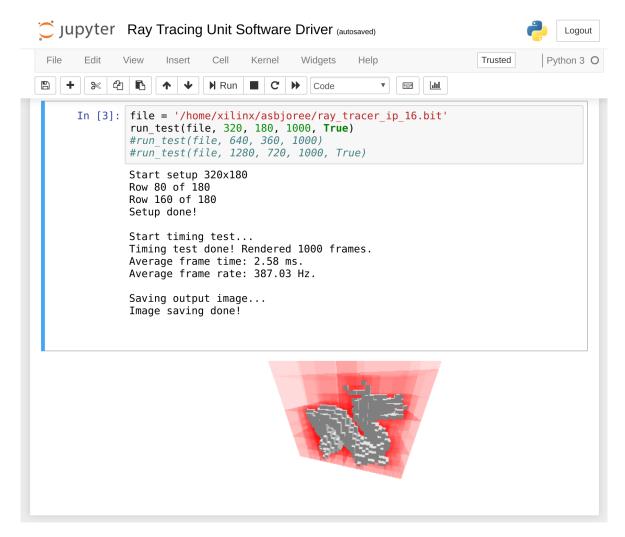

| ${f F}$      | Soft | sware driver          | 157 |

|--------------|------|-----------------------|-----|

|              | F.1  | Driver core functions | 157 |

|              | F.2  | Example driver usage  | 162 |

|              |      | F.2.1 Example output  | 163 |

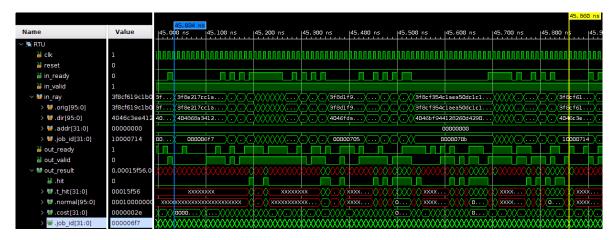

| $\mathbf{G}$ |      | , W 612 C 1110 G 61   | 165 |

|              | G.1  | Ray tracer core       | 165 |

|              | G.2  | Data types            | 169 |

|              | G.3  | Test bench            | 171 |

# Chapter 1

# Introduction

I do think that some form of ray tracing—forward tracing or reversed tracing—rather than forward rendering will eventually win because there's so many things that just get magically better there. (...) And there's a lot of work, lots of smart people, lots of effort, and lots of great results coming out of it. Eventually ray tracing will win, but it's not clear exactly when it's gonna be.

— John Carmack, 2011 [2]

The idea of real-time hardware-accelerated ray tracing has by many been described as the *holy grail* of computer graphics [3][4]. In the autumn of 2018, Nvidia threw a curve ball and confounded an entire field with the launch of its newest series of graphics cards which featured this elusive technology [5]. The hype surrounding these latest developments in the field seems to have somewhat diminished in the latest months, and many have even outright dismissed ray tracing as a useless "gimmick" [6][7]. It is understandable that from a video game enthusiast's standpoint, the features may not have borne much fruit. They have remained largely unexercised by the many video games that have been released in the meantime.

Nonetheless, the fact that Nvidia has gone all-in on this technology is nothing but exciting for someone who has been following the ray tracing scene closely for many years. In fact, the new and shiny Vulkan graphics API—which may be regarded as the spiritual successor to OpenGL in many respects—actually contains extensions that expose support for ray tracing [8]. This means that any graphics accelerator vendors that wish to fully support the Vulkan API and its applications are required to also support ray tracing. Moreover, in the context of these recent developments, ray tracing should not be regarded as a replacement for rasterisation rendering. Rather, it ought to be viewed as a complementary technology that may be employed in conjunction with rasterisation rendering to improve visual fidelity.

Of course, no one should expect such paradigm shifts of established technology to happen overnight. It may take many years before the rest of the industry decide to follow Nvidia's new direction—it might not even happen at all. But the fact that one of the major players in the industry have put so much on the line for this technology is intriguing. In any case it shall be very exciting to follow the many breakthroughs

that may happen in the field if the technology gains a foothold. Will the other vendors follow in Nvidia's footsteps or reject the technology entirely?

## About this work, and its relation to the project thesis

This master's thesis is inspired by—and, to some extent, builds upon—the work done in the specialisation project during the autumn of 2018. It may be viewed as a continuation of this work, although the reader should keep in mind that its approach to the subject of study varies, and thus the nature of the results and their implications will be entirely different. In the project thesis, a general technique for animation of sparse voxel octrees was introduced. In this master's thesis, the method will be treated as previous work, and employed in a fully-fledged hardware ray tracing system. The project thesis report is included in the attached ZIP file, as described in Appendix A.

Another point worth noting is that there does not appear to be an established and universally agreed-upon name for the specialisation project that is completed in the first half of the fifth year of study at NTNU. In this thesis, however, it will consistently be referred to as the *project thesis*. The project thesis [1] will also be explicitly cited in the text if deemed necessary.

Much of the background matter, as well as the research context and chosen algorithms are useful and relevant for both the project thesis and this thesis. It would be a wasted effort to rewrite all these relevant sections for this thesis. Therefore, certain relevant sections of text have been extracted, copied, or paraphrased from from project thesis and presented here. Whenever this occurs, it will be clearly stated either directly in the section or in an introductory section.

#### Thesis outline

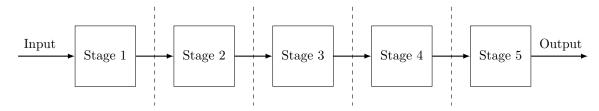

This thesis consists of nine chapters and a set of appendices. Chapters 1 to 4 are background and theory chapters. These contain no results, but serve to bring the reader up to speed on the concepts and theory that is required to understand the results. Chapter 2 contains general background theory, while Chapter 3 presents the general fields of research that this thesis is a part of. In Chapter 4, the algorithms upon which the solutions and results are built are presented in detail.

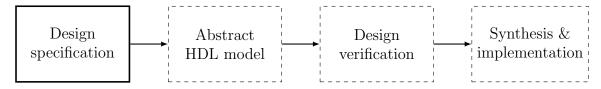

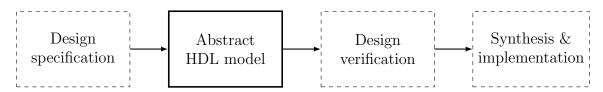

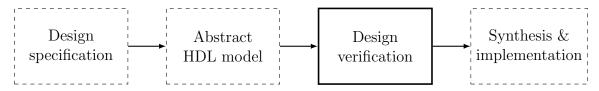

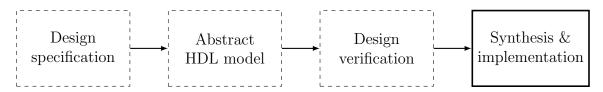

Chapters 5 to 8 are the result chapters, in which the work done as part of this project and its results are presented and discussed. The development methodology in this master's thesis is loosely based on the waterfall model, and these four chapters each represent one or more stages of the model. In Chapter 5, a high-level requirement analysis of the desired features of the system is presented. Chapter 6 introduces the system design and a specification of its modules is formulated and discussed. The hardware implementation of this system is presented in Chapter 7. The results, and a discussion of these, are presented in Chapter 8.

## A small note about figures

Unless otherwise specified, all figures presented in this text are designed and created by the author. It is not an insignificant workload that has been laid down in their creation, and as such, they should be regarded as original (or, in some cases, improved derivative) works and hopefully contribute to the credit of this thesis.

# Chapter 2

# Background

Images generated by computers permeate the lives of humans today in ways one could not imagine merely half a century ago. In the current age of information, there are numerous areas of which computer graphics is a central part, for instance the fields of numerical computing visualisations [9][10][11], video games [12][13][14], computer-aided design (CAD) [15][16][17], graphical user interfaces (GUIs) [18][19], and special effects for motion pictures (SFX) [20][21].

In this chapter, relevant background information will be presented, starting with a short account of the eventful history of real-time computer graphics. The chapter is partly derived from its counterpart in the project thesis by Espe [1], with some sections taken directly from it. Sourced from the project thesis are Sections 2.1, 2.3 and 2.4, as well as Sections 2.2.1 to 2.2.3. These selected sections have been evaluated as very relevant for this master's thesis, and have such been copied and slightly adapted to be a part of this background chapter.

# 2.1 A brief history of real-time computer graphics

Computer graphics as a field has only existed for about 60 years. The term first appeared around 1960, and was used to describe early works such as Ivan Sutherland's groundbreaking computer program *Sketchpad* [22]. Sutherland's program is considered the antecedent to modern computer graphics in that it was the first graphical solution enabling *human-computer interaction* (HCI).

The history of real-time computer graphics is defined by breakthroughs. The rendering capabilities at a given point in time was generally constrained by capacity of the underlying hardware. For instance, once transistor-based memory was available in the 1970s, the creation of efficient *frame buffers* was possible. Frame buffers are to this day central, as the technology simplifies and speeds up computation by allowing the decoupling of rendering logic from display logic [23][24].

By the late 1970s, three-dimensional computer graphics had left its infancy. And as the field matured, it became apparent that two main methods of real-time rendering were to dominate the scene. The earliest attempts had used rasterisation, a technique which gained popularity after the introduction of the Z-buffer in 1974, developed and proposed by both Edward Catmull [25] and Wolfgang Straßer [26], independently. The alternative to rasterisation was ray tracing, an image synthesis technique that was

first proposed by Arthur Appel in 1968 [27], but popularised after a paper by Turner Whitted in 1980 [28].

It would become clear, through the conception of dedicated graphics processing hardware in the 1980s and early 1990s, that rasterisation was to be the main-stream technique for real-time computer rendering. One of the earliest single-chip display controllers was the *NEC 7220*, released in 1982 [29]. By incorporating this chip in their designs, manufacturers could construct dedicated graphics processing units (GPUs), such as a range of products released by Number Nine Visual Technology through the 1980s. In these early GPUs, rasterisation of primitives—rather than ray tracing—was employed to produce output, further consolidating the position of rasterisation as the preferred method for image synthesis [30].

While rasterisation as a technique may have been more popular, there were attempts at hardware acceleration of ray tracing as well. In the late 1980s, a series of ray tracing demonstrations was run on a parallel processing architecture developed by the British semiconductor company Inmos [31]. The microprocessor architecture on which these demonstrations were run was known as the *transputer*. The main purpose of the transputer architecture was to allow for the construction of scalable concurrent systems, and the parallel nature of most ray tracing algorithms made ray tracing a prime candidate for the showcase of their technology.

Through the 1990s and 2000s, real-time computer graphics would continue to increase in popularity, as new graphics acceleration hardware would be released on a regular basis. Once the *personal computer* (PC) became a household item, high performance computing, and with it real-time computer graphics, was no longer reserved for the specialist user. In the early 2010s, a new field of research emerged—embedded computer graphics, or mobile graphics. While the main constraints in desktop hardware are performance and price, mobile devices introduce an additional concern: as a consequence of their battery-powered nature, there is a desire to deliver real-time computer graphics while simultaneously maintaining power efficiency [32].

Even though rasterisation is currently the title-holder of the real-time computer graphics race, ray tracing continues to be relevant. In 2018, the popularity of ray tracing experienced a revival after Nvidia unveiled its newest range of GPUs—the GeForce RTX series [5]. It should be interesting to see to which degree this recent surge of main-stream attention will impact the future of computer graphics.

# 2.2 Fundamental concepts

The overarching goal of computer graphics is to utilise a computer to deterministically render an image based on a specification of some form. The images generated may be stored for later consumption, or they may be presented in real-time on a display as part of a graphics pipeline. Regardless of what the end goal of the rendering process is, and which techniques were employed to reach this goal, there are some fundamental concepts that are used almost universally. These fundamental concepts are presented in this section.

## 2.2.1 3D models

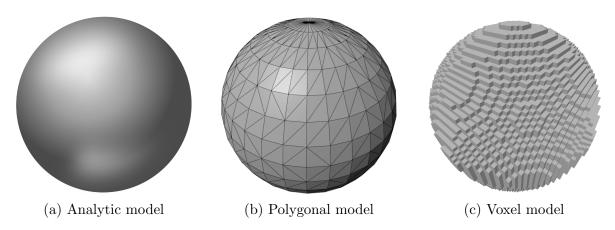

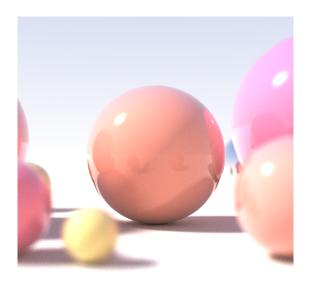

In three-dimensional computer graphics, the *model* can be viewed as a digital description of what is to be rendered. Models are a central part of most computer rendering pipelines and contain the data that is to be interpreted by the rendering process when generating a scene. Ordinarily, a model is a digital representation of a single, distinct object; a scene is a collection of models in some configuration. A model may be sorted into one of three main categories based on way it represents physical objects digitally. Each category has its drawbacks and advantages, which will be outlined in the following. Illustrations of the different categories are shown in Figure 2.1.

Figure 2.1: Three types of models.

#### Analytic models

Models that can be completely described by some mathematical equation are known as analytic models. Such models are often constructed from analytic, geometric primitives, for instance cubes, spheres, curves, and lines. These models have the advantage of supporting arbitrary accuracy [33, pp. 66, 70][34, p. 176]. For instance, a sphere of radius 1, centred at the origin may be modelled perfectly by its analytical formulation as all the points  $\mathbf{x}$  that satisfy Equation (2.1).

$$||\mathbf{x}|| = 1 \tag{2.1}$$

A drawback of analytic models is that they are in general more computationally expensive to render compared to alternative methods. Another shortcoming is that it may be very difficult to model complex shapes mathematically. Fortunately, for a given level of detail, one hardly ever needs the fidelity of mathematically perfect models. As such, they are rarely used in real-time three-dimensional computer graphics. The main use of this category of models is in the technique called *constructive solid geometry* (CSG), where multiple geometric primitives are combined with Boolean logic to produce more complex models [34, pp. 555–559]. An illustration of a sphere modelled analytically is shown in Figure 2.1a.

## Polygonal models

A more common approach in computer graphics is to describe the object as a polygonal surface mesh. These models, known as polygonal models, only store the boundary or shell of the object, and are therefore a type of surface representation [34, p. 176]. A polygonal model, such as the sphere shown in Figure 2.1b, can be regarded as a vector graphics representation of an object, in the sense that a series of points are employed to define the vertices of a surface. The points are connected by a mesh comprised of polygons—in almost all practical cases, triangles [14, p. 426][34, p. 177]. As a consequence of their vector graphics nature, polygonal models are particularly well suited for representing large, flat surfaces. A flat plane, for instance, can be modelled by only four vertices describing two triangles. A drawback is that polygonal models cannot accurately represent curved surfaces [33, p. 4]. High-fidelity models quickly become computationally expensive to render, since the level of detail is dependent on the number of polygons.

#### Voxel models

Where polygonal models can be considered a form of vector graphics representation of objects, voxel models may be regarded as a pixel or raster graphics representation. A voxel model, exemplified by Figure 2.1c, is a model consisting of a set of voxels. The word voxel, short for volumetric element, describes an object that can be thought of as the three-dimensional analogue of the two-dimensional pixel. In other words, a voxel represents a single data sample in a three-dimensional grid. As a consequence of their volumetric nature, voxel models are a type of volume representation, therefore contrasting polygonal models [34, p. 177]. However, certain optimisations of the model data structure can be made so that the model appears as a type of surface representation, for instance by employing tree-based structures [35].

# 2.2.2 Spaces and transforms

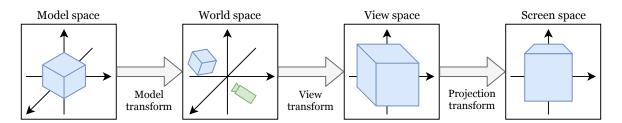

After being sculpted and exported from some form of graphics modelling software, a model will usually be stored in a normalised, axis-aligned format, with all co-ordinates being relative to a single point called the model's origin [14, p. 428]. In the other end of the rendering process, the final image produced is in most cases going to be displayed on a digital screen. Specifically, the end result of the graphics pipeline is a set of pixels positioned in an ordered two-dimensional grid.

Figure 2.2: The rendering process as a black box.

The rendering process itself is often thought of as a black box process, as shown in Figure 2.2. However, in order to properly understand the different spatial representations, as well as the process of converting between them, there is a need to take a look under the bonnet in search for a more rigorous definition.

## Vector spaces

By introducing the concept of spaces, the process can be simplified quite extensively. As it turns out, all the different co-ordinate systems normally encountered in computer graphics may be represented mathematically as vector spaces.

The first of the co-ordinate systems mentioned in the introduction to this section—the one which is local to the model—is termed the *model space*, or alternatively *local space* [33, p. 7] or *object space* [14, p. 428]. As for the screen, each individual pixel in this grid will have a unique set of co-ordinates that describes its position. The pixels are said to reside in *screen space* [33, p. 10].

Since the screen on which to display the final image is two-dimensional, while the models are (in most cases) three-dimensional, there is a need to convert between the two spaces. Further, it is desirable in almost all cases to rotate, scale, or move the model around in the scene. To facilitate these requirements, two new vector spaces are introduced: world space and view space. World space is the global space in which all models are positioned, rotated, and scaled as desired. It is the space that describes the larger world, and is what one usually thinks of as the scene in computer graphics [14, p. 428][33, p. 7]. All models to be rendered must be placed somewhere in the world space. View space, which is sometimes named camera space [33, p. 7], is the space that places the camera (or eye) in the origin, looking down the negative z-axis, and orients all objects in the scene such that they are placed correctly relative to the camera's point of view. This space is an intermediate step that is needed to correctly perform the final conversion to screen space.

As shown in Figure 2.3, there are four main spaces in the rendering pipeline. For illustration purposes, the camera is shown as an entity in world space. Some method for deterministically transforming co-ordinates in one space to another space is desired. Luckily, since the spaces can be mathematically defined as vector spaces, the transformations between each space can be represented as mathematical transformations.

Figure 2.3: Main spaces in rendering. The camera itself is shown in world space.

#### Transforms and transformations

In mathematics, a transformation, also known as a map, is a generic function that maps one space to another. The mathematical formulation of a map  $\mathbf{T}$  from  $\mathbb{R}^n$  to  $\mathbb{R}^m$  is shown in Equation (2.2).

$$\mathbf{T}: \mathbb{R}^n \to \mathbb{R}^m \tag{2.2}$$

Many mathematical maps, and all linear maps, can be written on matrix form. The map function T may be written as shown in Equation (2.3), where A is a matrix of

size  $m \times n$  and **x** is a column vector with n elements.

$$\mathbf{T}(\mathbf{x}) = \mathbf{A}\mathbf{x} , \qquad \mathbf{x} \in \mathbb{R}^n, \mathbf{A}\mathbf{x} \in \mathbb{R}^m$$

(2.3)

As it turns out, all the transformations needed in the graphics pipeline, except one, are *affine transformations*, which means that each of them may be represented as a homogeneous matrix. In computer graphics, such a matrix is called a *transform*, and the function it provides is called a *transformation*.

Since there are four spaces of concern, it stands to reason that there are three main transforms that are needed to convert between the spaces. These transforms and their names are shown in Table 2.1. The transform which converts from model space to world space is aptly known as the *model transform*, and the transform from world space to view space is called the *view transform*. The last transform, converting view space to screen space, is unique in that it is not a general affine transform. It is known as the *projection transform*, since it serves the function of projecting a three-dimensional world onto a two-dimensional plane (the pixel grid).

Table 2.1: The main transforms of the computer graphics pipeline.

| Initial space | Result space | Transform name       |

|---------------|--------------|----------------------|

| Model space   | World space  | Model transform      |

| World space   | View space   | View transform       |

| View space    | Screen space | Projection transform |

In practice, the three transforms are represented by four-dimensional matrices. A complete transformation of a point from model space to screen space can be written mathematically as shown in Equation (2.4).

$$\mathbf{q}' = \mathbf{PVMp} \qquad \mathbf{q} = \frac{\mathbf{q}'}{q'_w}$$

(2.4)

Where the vectors **p** and **q** are the initial and final positions, respectively. The matrices **M**, **V**, and **P** are the model, view, and projection transforms. Notice that in order to obtain the final point, the result of the matrix transformations has to be divided by its own fourth co-ordinate, the *homogeneous co-ordinate*. This is called the *perspective division* and is a consequence of the fact that the projection transform is not an affine homogeneous transform [34, p. 122]. The perspective division is the step responsible for the perspective effect that results in objects farther away appearing smaller than objects closer to the observer.

# 2.2.3 Computer animation

It is usually desirable to render not only static scenes, but also dynamic worlds containing movement, rotation, and deformation of models. The way this is achieved in computer graphics is usually through the stepwise alteration of 3D models, either by changing their associated model transforms, or by changing the model data itself. The

models are in most cases altered slightly between each successive rendered frame, so that their movements may be perceived as smooth motion. This practice of presenting a series of still, computer generated images in rapid succession with the goal of giving the appearance of motion is termed *computer animation* [34, p. 615].

The computer generated frames must be presented at a certain frequency in order to properly provide the visual continuity required for the human eye to perceive them as motion. The exact threshold frequency is a topic of much debate, but most studies appear to agree that it lies in the region of 12 to 16 frames per second [34, p. 615][36, p. 24]. If a rendering process is able to synthesise and present a series of images at or above this threshold rate, it is known as a real-time rendering process. It is worth noting that the usage of the term real-time in the field of computer graphics differs somewhat from the precise definition of real-time processes found in the field of embedded systems.

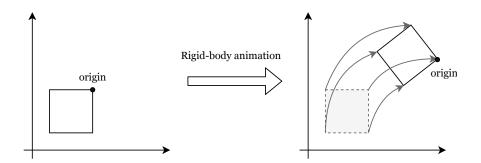

## Rigid-body animation

This thesis is chiefly concerned with a certain type of animation termed *rigid-body* animation. The term finds its roots in physics, where a *rigid body* is defined to be a stiff body for which deformation may be disregarded. By directly adopting this definition to the field of computer animation, one ends up with the definition of rigid-body animation—an animated rigid body. In other words, a model animated by rigid-body animation is an animated model which does not support deformation [34, p. 632].

Rigid-body animation can be regarded as a simple form of animation that does not alter the internal data of the model. The case of a polygon model is considered in the following to serve as an example. By treating the polygon model as a rigid body, the model as a whole must be regarded as a stiff, undeformable body. This means, in turn, that any animation applied to the model must be applied equally to all the model's internal vertices. And during the animation sequence, the positions of all the vertices in model space must remain unchanged. This does not mean, however, that every vertex will always be translated by the same amount in world co-ordinates. For instance when a model is rotated, each vertex is rotated around the model's origin, and their paths in world space may not be equal. An illustration highlighting this distinction is shown in Figure 2.4.

Figure 2.4: Example of rigid-body animation. After rotation and translation of the model, the vertices of the square remain unchanged in model space. In world space, however, their paths are different.

A consequence of this definition of rigid-body animation is that only certain affine transformations are permitted to be applied to models. It turns out that the only allowed transformations are rotation and translation—both representable by simple affine matrices [34, p. 632]. The simplifications that are possible as a result of this fact laid the foundation for the work done in the project thesis [1].

# 2.2.4 Number representation

While integers may be sufficient for many applications in computer science, in computer graphics it is often necessary to perform calculations involving real numbers. Indeed, simply observing the linear algebra equations derived in Section 2.2.2, makes it apparent that non-integral numbers are central to the mathematical calculations that facilitate the rendering of three-dimensional scenes.

Representing real numbers accurately in hardware, however, is a complicated endeavour. With a limited number of bits available for number storage, there is a perpetual trade-off between accuracy and size. A larger number of bits set aside for number storage would increase the accuracy, but in turn also increase the size of the number in memory. For some numbers, such as irrational real numbers, total accuracy is not possible regardless of the number of bits employed in representation. This means that the application in which the numbers are used should be considered carefully before determining how numbers are to be represented.

In modern practice there exist two fundamentally different approaches to representing real numbers in computers—fixed-point and floating-point. Both of these representations are used extensively in hardware applications, and each one has its advantages and drawbacks. A brief introduction of the two representations is laid out in the following, and a comparison between them is presented subsequently.

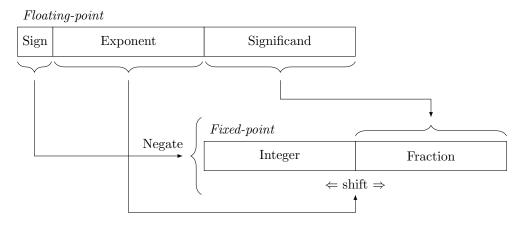

#### Fixed-point number representation

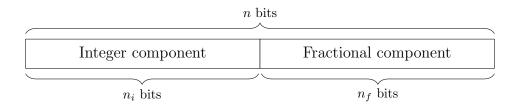

The first and simplest of the two is the fixed-point number representation. Real numbers are stored in fixed-point by splitting the number into two parts—an integer part and a fractional part. In other words, an n-bit fixed-point representation allocates a fixed number of bits,  $n_i$ , to represent the integer part, and employs the rest of the bits,  $n_f$ , to hold the fractional part [14, p. 216]. This structure is illustrated in Figure 2.5.

Figure 2.5: An n-bit fixed-point number. The representation uses  $n_i$  bits to hold the integer component, and  $n_f$  bits to hold the fractional component. In order to support negative numbers, two's complement representation is often used.

The number of bits chosen to represent each of the two components in an n-bit fixed-point number varies from application to application. In some cases, there is a

need for great precision in terms of the fractional part, which requires that a relatively large number of bits must be set aside to represent this part of the number. In other cases, fractional accuracy is not as important as the need to represent large absolute values. The integer part of the number could then be favoured in terms of allocated number of bits. Making a choice in this regard is up to the designer of the given system. A number of examples of different bit partitions are given in Table 2.2.

Table 2.2: Examples of different subdivisions of a fixed-point number. The numbers shown are in two's complement form in order to support negative values.

|       | Bit widt | hs       | Integer range         | Fractional precision  |  |  |  |  |

|-------|----------|----------|-----------------------|-----------------------|--|--|--|--|

| Total | Integer  | Fraction | 21100001 201100       |                       |  |  |  |  |

| 8     | 4        | 4        | -8 to 7               | $6.25 \times 10^{-2}$ |  |  |  |  |

| 16    | 4        | 12       | -8 to $7$             | $2.4 \times 10^{-4}$  |  |  |  |  |

| 16    | 8        | 8        | -128  to  127         | $3.9 \times 10^{-3}$  |  |  |  |  |

| 16    | 12       | 4        | -2048 to $2047$       | $6.25\times10^{-2}$   |  |  |  |  |

| 32    | 8        | 24       | -128 to 127           | $5.96\times10^{-8}$   |  |  |  |  |

| 32    | 16       | 16       | -32768 to $32767$     | $1.5 \times 10^{-5}$  |  |  |  |  |

| 32    | 24       | 8        | -8388608 to $8388607$ | $3.9 \times 10^{-3}$  |  |  |  |  |

### Floating-point number representation

The second approach, and the most widespread method for binary representation of real numbers today, is the floating-point number representation [37, p. J-13]. Unlike the fixed-point representation, this number format is standardised. It is governed by the IEEE-754 standard, more verbosely known as the *IEEE Standard for Floating-Point Arithmetic* [38]. The original standard dates back to 1985, but the specification upon which this thesis is based is the newer and revised version that was published in 2008.

The floating-point format employs exponential notation of numbers. This means that it utilises the concept that any real number x can be written on the exponential form shown in Equation (2.5), where s is a real number in the range  $[1,2\rangle$  and e is an integral number.

$$x = s \times 2^e \tag{2.5}$$

In other words, as long as the base of the exponentiation is agreed upon, the number x can be represented by only storing the significand s and exponent e. Moreover, as mentioned above, the significand only needs to hold values in the range  $[1,2\rangle$ . This is a consequence of the exponentiation base being 2—if the significand were outside this range, the exponent could be adjusted to bring it back within the range. In binary form, this means that the leading number of the significand will always be 1, and need not be stored explicitly [39, p. 12].

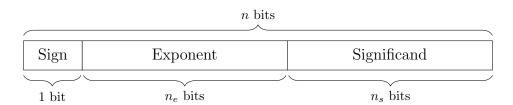

This simplification does, however, raise the question of how to store negative numbers. Two's complement would not really work in this case. The IEEE-754 standard defines the structural layout of a floating-point number as shown in Figure 2.6. The illustration shows that one bit of the number has been reserved to store the sign. The rest of the bits are used to store the exponent and significand.

Figure 2.6: An n-bit floating-point number. The representation uses 1 bit to signify the sign of the number,  $n_e$  bits to store the exponent, and  $n_s$  bits to hold the significand.

The floating-point specification additionally defines two special values that may be encoded as a floating-point number. These values are signalled by setting all bits of the exponent e to one. The first of the two special values is the not-a-number value, referred to as NaN. The NaN value is used to represent uninitialised variables or for signalling invalid operations. The second value is the infinity value, which is used to represent results that are numerically unbounded. The specification states that if the significand s is zero, the floating-point number signifies  $\pm \infty$ —where the sign bit determines sign. If the significand is not equal to zero, the number represent a NaN.

In Table 2.3, the most common floating-point formats are listed along with their specifications and range. Most relevant for this thesis is the *single-precision floating-point specification*, which has the standardised name binary32.

Table 2.3: The most common of the IEEE-754 formats. Numbers are taken from the *IEEE Standard for Floating-Point Arithmetic* [38, p. 13].

| Common name         | Standard name | n   | $n_s$ | $n_e$            | Magnitude range |             |  |  |

|---------------------|---------------|-----|-------|------------------|-----------------|-------------|--|--|

|                     | Standard Hame | 70  | 108   | r <sup>i</sup> e | Min             | Max         |  |  |

| Half-precision      | binary16      | 16  | 10    | 5                | $2^{-14}$       | $2^{15}$    |  |  |

| Single-precision    | binary32      | 32  | 23    | 8                | $2^{-126}$      | $2^{127}$   |  |  |

| Double-precision    | binary64      | 64  | 52    | 11               | $2^{-1022}$     | $2^{1023}$  |  |  |

| Quadruple-precision | binary128     | 128 | 112   | 15               | $2^{-16382}$    | $2^{16383}$ |  |  |

#### Comparison of fixed-point and floating-point

While the floating-point number representation is the most widely used in computers today, the fixed-point representation does have a few conveniences that makes it

preferable in certain contexts. As will be further detailed in Chapters 5 to 8, both number formats are to be used in the solution in order to circumnavigate their individual weaknesses.

The main drawback of floating-point numbers when compared to fixed-point numbers, is that the former is a much more expensive and complex format to implement in hardware. Quite a bit of chip area is required in order to efficiently facilitate operations such as addition and multiplication of floating-point numbers. Fixed-point numbers, however, do not present a significant overhead in implementation. In fact, in hardware one may almost exclusively treat fixed-point numbers as integer numbers. This means that operations such as addition and multiplication of fixed-point numbers can be implemented at a much lower cost than for the floating-point representation. The differences in area can be seen in Table 2.4.

Table 2.4: Differences in chip area requirements between fixed-point and floating-point implementations. Numbers are in  $\mu m^2$ , and taken from [37, p. 29].

| Type           | 16-bit addition | 32-bit addition | 32-bit multiplication |

|----------------|-----------------|-----------------|-----------------------|

| Fixed-point    | 67              | 137             | 3495                  |

| Floating-point | 1360            | 4184            | 7700                  |

On the other hand, an advantage of floating-point numbers is that they have an enormous range compared to fixed-point numbers of the same bit width. This fact is evident by inspecting and comparing Tables 2.2 and 2.3, and is a huge contributing factor to their widespread use. In addition, the exponential nature of floating-point numbers makes them well-suited for many numerical applications. As an example, it is rare that one needs the precision of millionths when dealing with numbers in the order of a billion. There are, however, some situations in which these precisions are needed, and employing floating-point numbers may then lead to rounding errors.

# 2.2.5 Task scheduling

In computer graphics, parallelised systems are commonplace. Whenever a parallelised system is encountered, either in hardware or software, a question is raised concerning how one might best utilise this parallelisation. And a decision regarding the method by which tasks should be ordered and distributed in the parallelised system must be made. The study of how tasks should be ordered, and in which manner they should be distributed among execution units is often termed *task scheduling*.

Normally, the term refers to a collection of methods used to determine the order of execution of tasks on a single or multiple execution units, as well as the analysis of such methods—for instance the study of which methods that yield the highest utilisation. In this thesis, the term is used to mean a slightly different concept. As will be further detailed in the later chapters—specifically Chapters 6 and 7—the system in this thesis is made up of several duplicated execution cores that perform a similar function on a set of data. The term scheduling is then used to describe the process of selecting which

cores that should be assigned new tasks. This distinction is subtle, but should become apparent through the examples presented in the following sections.

Another point to note is that the field of scheduling is very broad, and there exists a host of different scheduling algorithms. Most are not relevant to this thesis, so only a few algorithms will be presented and discussed. Introduced in the following are the round-robin algorithm and the first-available algorithm.

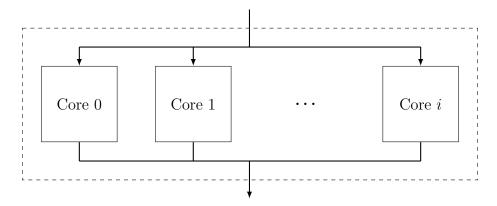

#### Round-robin

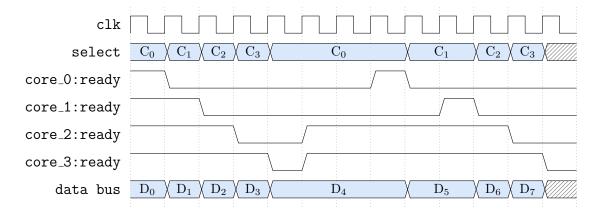

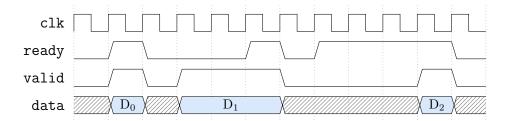

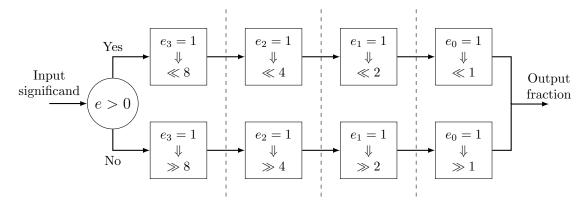

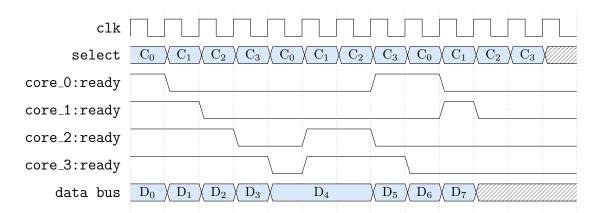

The simplest form of scheduling is to order all execution units, and simply wait for the next execution unit in line to be ready before assigning the next task. This approach is called *round-robin* scheduling, and is illustrated in Figure 2.7. In the figure, the **select** signal cycles which core is selected in a predetermined order. If the currently selected core is ready, it is assigned a task—here represented by sending it a data packet on the data bus.

Figure 2.7: Example of round-robin scheduling.

Round-robin scheduling has the advantage that it is exceptionally simple to implement into a system. The select signal may be realised as a counter that is incremented for each job, and reset to 0 whenever it reaches the maximum index. A drawback of this method is that a single execution unit may hold up the entire system if it is busy with a job while next in line. The issue is highlighted by the diagram above, where the system has to wait for core  $C_0$  to be ready for several clock cycles before continuing.

#### First-available

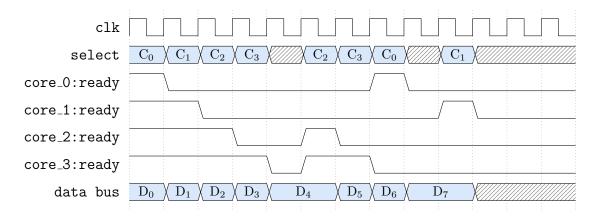

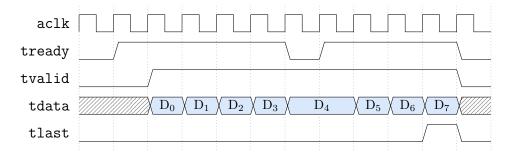

Another method of scheduling tasks among execution units is to assign the next task to the first execution unit that becomes available. This method is demonstrated in Figure 2.8, where it is shown that the **select** signal always selects the first core that is ready and assigns the next data packet to it.

The scheme is a bit more involved to implement efficiently, especially in hardware. However, it solves the issue raised by round-robin scheduling, where a single execution unit may impede the rest of the system. This is substantiated by the diagram, where the next task is assigned to core  $C_2$  when it becomes ready before  $C_0$  and  $C_1$ . In a comparison of the two diagrams, one can see that the first-available scheduling method

Figure 2.8: Example of first-available scheduling.

is finished two clock cycles before the round-robin method in the same setting—evidence to the claim that it is more efficient and leads to higher utilisation.

# 2.2.6 Memory caching

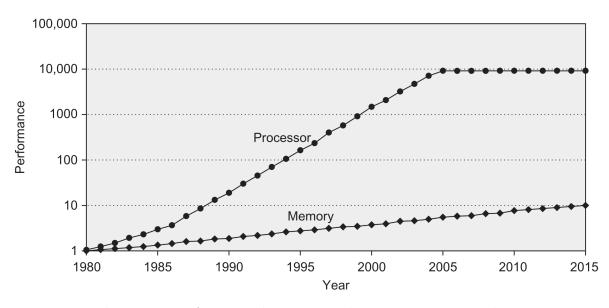

In the early years of digital hardware design, computation cores and memory performance increased in lockstep; clock speeds of both processors and memories were improved by a significant figure each generation. As the field matured, it became apparent that memory clock speed could not be increased indefinitely, and that further improvements would not match the performance increase of the computation cores. In later years, a considerable gap has been established between processor core speed and main memory speed [37, p. 78]. This gap, illustrated in Figure 2.9, leads to many situations where the computation cores of a hardware design will have to await data from memory before computations requiring such data can continue [40, p. 82].

Figure 2.9: The gap in performance between single-core processors and main memory. Image taken from [37, p. 80].

In computer graphics, performance is of the essence. It is therefore crucial that

memory is implemented as efficiently as possible, and that the effects of this performance gap are minimised. The *memory cache* is a digital circuit designed to this end. In essence, the cache module will try to predict which memory addresses that may be used in the future, and subsequently store these addresses in a smaller, faster memory. The processor may then fetch the data from the cache instead of the main memory, which in turn leads to an overall reduction of latency. The selection of which memory addresses that are to be kept in the cache has spawned a whole field of study in itself. However, since the processor will often reuse the same memory addresses multiple times in short order, most policies entail keeping track of addresses that have been recently used [40, p. 83].

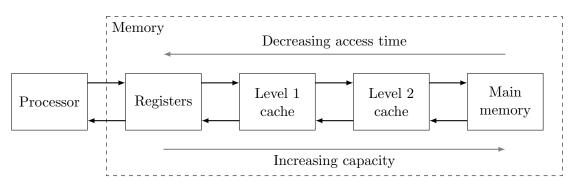

There is a trade-off between cache size and cache speed; the access latency of a cache generally increases with its size. A small and fast cache will often result in many cache misses, while a larger albeit slower cache will result in a higher degree of cache hits. Since the desired behaviour is a fast cache with as many cache hits as possible, many systems have multiple levels of caches between the main memory and the processor, where each tier is smaller and faster than the previous. This tiered organisation of caches is termed the cache hierarchy, and the general idea is shown in Figure 2.10.

Figure 2.10: An example of a cache hierarchy. Level n caches may be abbreviated Ln.

One may divide caches into three main categories on the basis of their operation. These categories and their advantages and drawbacks are detailed in the following.

#### Direct-mapped cache

A direct-mapped cache is a cache in which every memory address may only be placed at a specific position [37, p. 81][40, p. 306]. In other words, the processor will only have to check a single position in the cache in order to determine if the word it is trying to access is available, or if it must be fetched from a higher level memory. This has the advantage that the processor very quickly can determine if the cache has the memory it is requesting. A downside is the fact that multiple words share the same position in the cache, and that a cache line may be prematurely exchanged with another.

### Fully-associative cache

In contrast to the direct-mapped cache, a *fully-associative* cache lets any memory address reside in any location in the cache [37, p. 81]. This reduces the issue of multiple cache lines contesting for the same location in the cache substantially. However, since the processor now has to search through the entire cache in order to determine if the

data it requests is available, this scheme does make the overhead for retrieving words from the cache a bit larger.

#### Set-associative cache

The most popular scheme today is a combination of two extremes detailed above—the *set-associative* cache [37, p. 81][40, p. 308]. Caches belonging to this category are divided in to a number of *sets*, and each memory address is associated with a single set. When a newly fetched cache line from memory is to be placed in the cache, it may reside anywhere within its associated set.

This cache type improves upon the fully-associative cache since the processor only has to search through a single set in order to determine whether the requested memory resides in the cache. Another advantage is that the contesting issue associated with the direct-mapped cache is reduced. On a cache miss, a newly fetched cache line may be exchanged with a number of different cache lines. As such, an appropriate replacement policy should be implemented [37, p. J-9][40, p. 309].

# 2.3 Rendering techniques

The final space encountered in the computer graphics pipeline is the screen space. In this space, the objects to be rendered are projected onto a two-dimensional plane. However, the screen is a discrete grid of values, while the mathematically defined screen space is continuous. This raises the question of how one would go about sampling the continuous screen space in order to render the discrete frame. There are two main methods one may use to this end: rasterisation and ray tracing. In the following sections these two methods will be presented in more detail.

## 2.3.1 Rasterisation

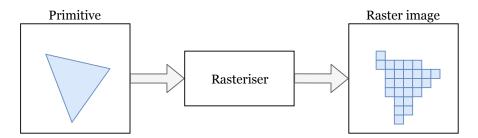

Rasterisation is a general technique for transforming data specified in vector graphics format into a grid of pixels—a raster image. Most graphics pipelines in use today employ some form of rasterisation [34, p. 8]. Shown in Figure 2.11 is the general idea behind the scheme.

Figure 2.11: Rasterisation used for sampling a primitive.

Specifically, rasterisation concerns itself with taking a set of primitives, for each primitive calculating which set of pixels the primitive is projected onto, and lastly, sampling the primitives to determine which colour the resulting pixel should have.

Most implementations of rasterisation additionally use some form of depth sorting in order to determine which primitive is in front of the other in the case of overlap [14, pp. 467–468][33, p. 19][34, p. 27].

The type of models used in rasterisation is, almost exclusively, polygonal models. This is because the models are natively in vector graphics format, which alleviates the need for translating the model into such a format before rendering [34, pp. 176–177].

#### Scan line rendering

The most popular method facilitating the implementation of rasterisation is by using the technique known as *scan line rendering*. The method works by inverting the problem; instead of working on each polygon, it works on each row of the raster image. By posing the problem this way, the implementation may take advantage of certain properties—such as scan line and edge coherence—in order to reduce the workload [34, p. 42].

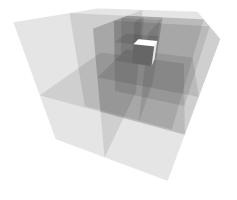

# 2.3.2 Ray tracing

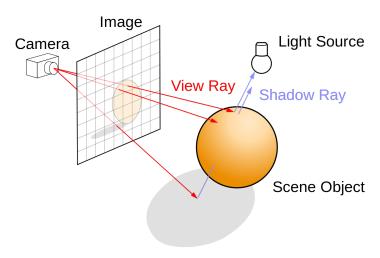

As an alternative to rasterisation, ray tracing is a method of sampling volumetric models, such as voxel models or analytic models. The method of ray tracing is based on modelling the physical properties of light. The idea is to trace the path light would take in reverse, starting from the camera, or eye, into the scene. If the ray hits an object, the colour of this object determines the colour of the pixel the ray passes through on its way [27]. In order to simulate the effects of lighting—such as shadows, reflections, and refractions—secondary rays may be spawned whenever the primary rays hit an object [34, p. 548][33, p. 220]. The basic concept is illustrated in Figure 2.12.

Figure 2.12: Ray tracing process. Image taken from [41].

Since effects of light can be simulated with relative ease, images produced by ray tracing often have a higher degree of realism than those resulting from traditional rasterisation-based methods. However, without introducing heavy optimisations, this improved visual fidelity generally also comes at a higher computational cost. As a result, ray tracing is widely used in applications which do not require real-time rendering, such as special effects for motion pictures [42].

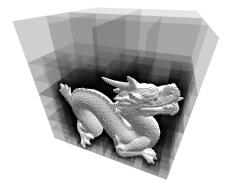

## Recursive ray tracing

Ray tracing as a concept easily lends itself to recursive implementations. One such implementation is termed *recursive ray tracing*. This method—or some derivative of it—is usually central in the generation of the hyper-realistic images one often associates with ray tracing. Examples of such images can be seen in Figure 2.13.

Figure 2.13: Examples of recursive ray tracing. The scenes are rendered with shadow, reflection, and refraction effects. Images taken from [43] and [44].

The general principle behind recursive ray tracing was pioneered by Whitted [28], and consists of recursively generating new rays whenever a ray is terminated by hitting a surface. For every primary ray hit, one or more secondary rays of the following types may be spawned: shadow rays, reflection rays, or refraction rays. Each of these types of rays are responsible for modelling a single effect of lighting.

- The first type, **shadow rays**, consists of rays that have the purpose of simulating the effects of shadows. The rays are traced from the hit point of the primary ray in the direction towards light sources. If a shadow ray hits an object on its way, the primary hit point is occluded from the light source in question, and hence lies in its shadow.

- Secondly, **reflection rays** are, as the name states, rays traced from the hit point on reflective surfaces. Such rays are traced with the direction reflected as calculated by some law of reflection, and allow the rendering of the mirror effect that appears on reflective objects in the scene.

- Finally, **refraction rays** are rays that follow the laws of refraction. Whenever a primary ray hits a (partially or fully) transparent object, a new ray is traced entering into the object. The direction of this ray is often calculated using Snell's law, which is dependent on the refractive indices of the materials it exits and enters [28].

# 2.4 Space partitioning

In the field of mathematics, *space partitioning* is the study of methods and techniques for efficient subdivision of space into partitions. As a branch of geometry, it is most often concerned with Euclidean space. There are several areas of application for the concept—chief among them, perhaps, is computer graphics. In computer graphics, performance is critical; being able to sort or organise objects in a scene by utilising space partitioning, means that certain optimisations are possible. For instance, hidden surface elimination or ray-object intersection can be greatly sped up by maintaining a sorted scene.

A great deal of research has been conducted into the field space partitioning over the years, but some proposed structures are more relevant than others in the context of this project. These partitioning schemes are based on a common form of partitioning termed binary space partitioning (BSP). It is a general style of space partitioning in the form of a tree structure, where each node in the tree may have zero or more children. Every node in the tree can be said to describe a portion of space, but policy of how space is divided among the nodes is dependent on the scheme used [14, p. 436]. In this thesis, two BSP-derived structures will be presented. The octree will be discussed initially, and subsequently, the sparse voxel octree.

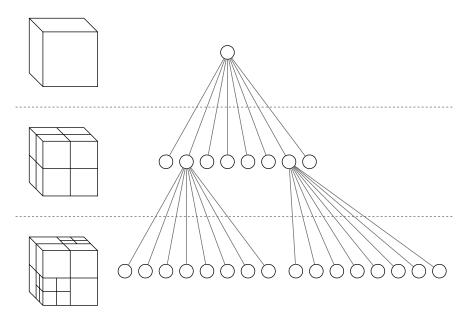

## 2.4.1 Octree

The *octree* is a type of BSP that was first introduced in a 1980 technical paper by Donald Meagher [45]. In it, he describes how binary trees and, especially, quadtrees (two-dimensional binary trees) are established data structures with many areas of applications. He continues by proposing the octree as a data structure which makes use of an N-dimensional binary tree in the representation of N-dimensional objects. In most cases, and especially in this thesis, three-dimensional space is used, so N = 3.

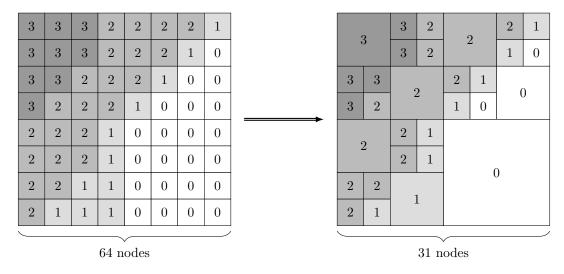

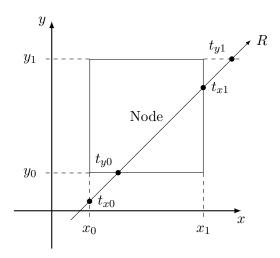

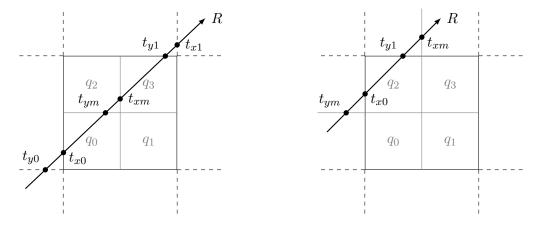

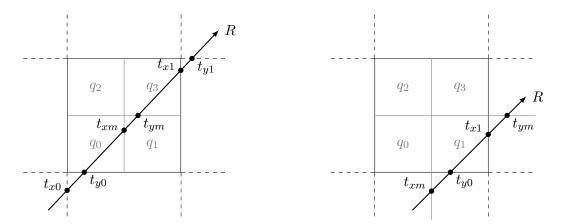

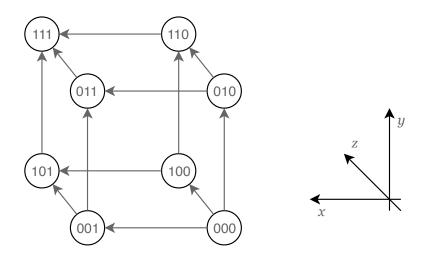

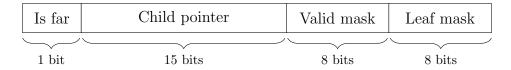

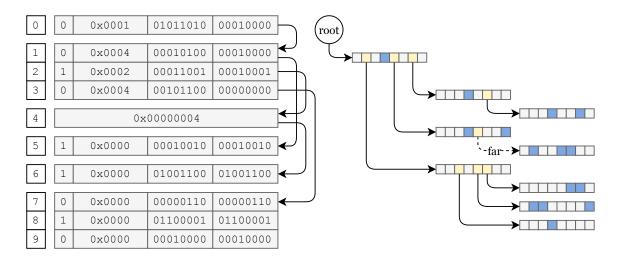

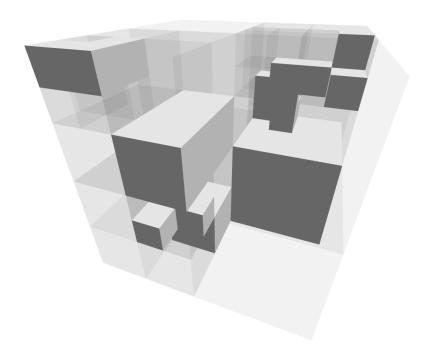

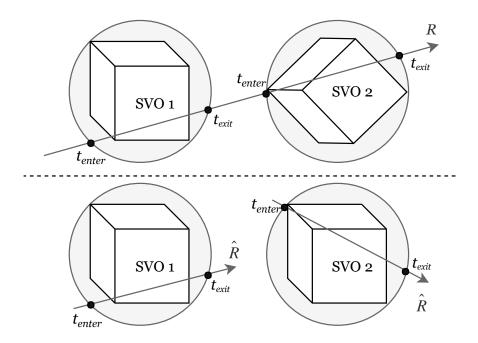

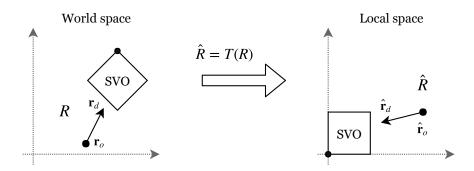

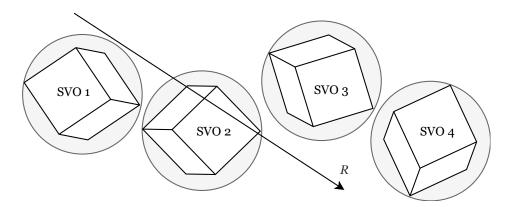

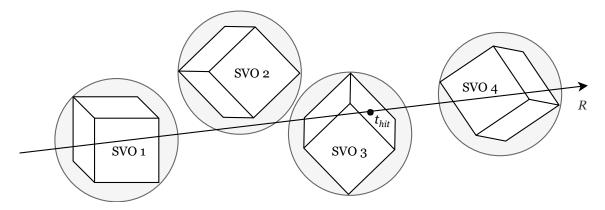

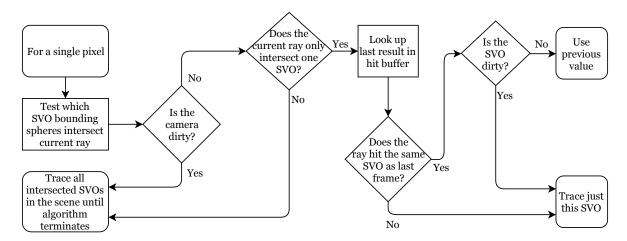

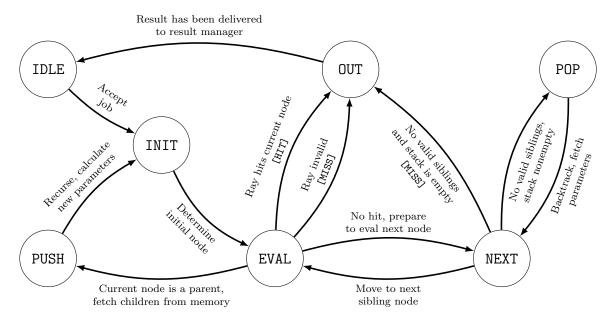

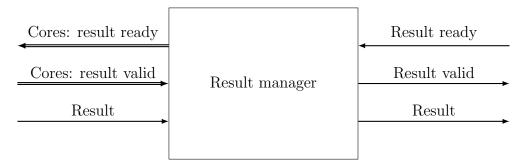

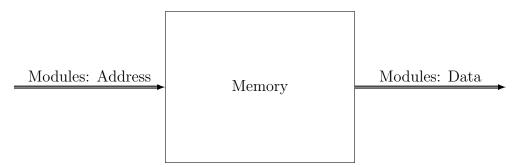

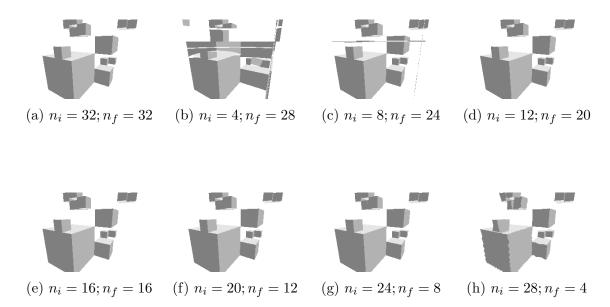

Figure 2.14: An illustration of the hierarchical structure of an octree.