# Abdelrahman Mohamed

# High-Performance Embedded Systems for Stereoscopic Vision

Master's thesis in Embedded Computing Systems Supervisor: Prof. Geir Mathisen, Dr. Kristoffer Nyborg Gregertsen June 2019

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

Abdelrahman Mohamed

# High-Performance Embedded Systems for Stereoscopic Vision

Master's thesis in Embedded Computing Systems Supervisor: Prof. Geir Mathisen, Dr. Kristoffer Nyborg Gregertsen June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

# Preface

This thesis "High-Performance Embedded Systems for Stereo Vision" has been written as a part of the European Master's Course in Embedded Computing Systems (EMECS), fulfilling a master's degree in Embedded Computing Systems at the Norwegian University of Science and Technology (NTNU).

I would like to thank my supervisors Prof. Geir Mathisen and Dr Kristoffer Nyborg Gregertsen for their excellent guidance and support during this challenging project, and providing me with all the tools required for this thesis, Finally I would like to thank my family and friends for being helpful and supportive during the time of my studies.

The stereo system developed for this project is built for Zynq Ultrascale+, and Nvidia Jetson boards, and it utilizes the libraries OpenCV, CUDA and XFopenCV, more details can be found in the methods and tools section 4.

The project was undertaken at Sintef Digital, where I had previously worked on my specialization project, however the contents of this thesis are original, independent work by the author, Abdelrahman Mohamed.

> Abdelrahman Mohamed Trondheim, 7 July 2019

# Abstract

This thesis aims to extract real-time 3D information about the environment using stereoscopic vision in space; it was developed for the Integrated 3D Sensors project I3DS (Integrated 3D sensors).

Stereo vision presents two significant challenges first is the correspondence problem; finding for every pixel it's corresponding pixel in the other image, two approaches for solving this problem are explored in this thesis local-based approach and semi-global based approach. The second challenge is the high throughput of data, making it challenging to implement a system that provides high frame rates with low power consumption, different embedded architectures are explored in this thesis; embedded CPU, embedded GPU, and FPGA to mitigate that problem.

The use of hardware accelerators (FPGA and GPU) provides better performance but at a significantly higher development costs, and time, so this project exploits modern software tools to accelerate the embedded development, OpenCV on the embedded CPU, CUDA implementation of OpenCV and libsgm on the embedded GPU, and the new library by Xilinx XFopenCV synthesized for the FPGA.

Finally, local block stereo matching and semi-global stereo matching are implemented on CPU, GPU and FPGA, providing six different implementations, benchmarked for stereo matching accuracy, processing time/frame rates and power consumption.

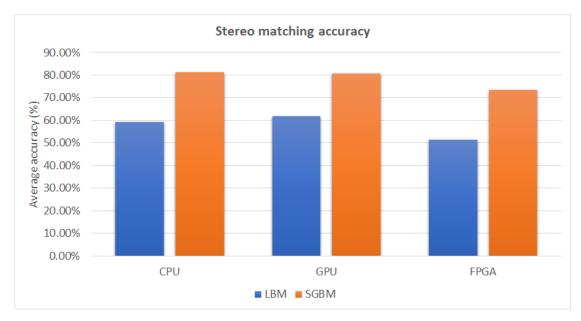

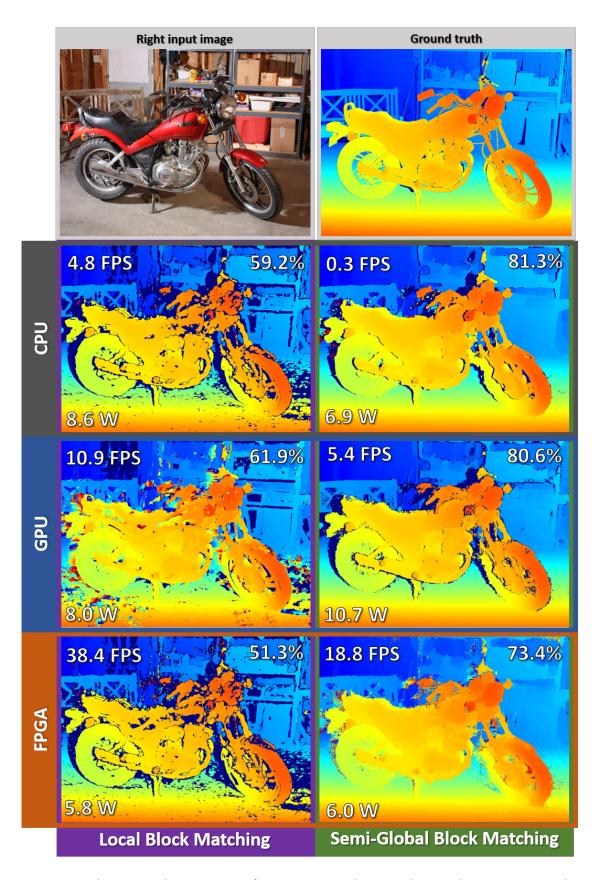

It is shown that the CPU implementation provides the highest accuracy, but lowest frame rates, and highest power consumption, the FPGA implementation provided lowest accuracy, but highest frame rates and lowest power consumption, while the GPU scored mid-way in all of its benchmarks.

This thesis starts with an introduction and then provides the theoretical background behind the implementations in the High-Performance Embedded Computing and Stereo Vision chapters, afterwards the implementations, and their optimizations are documented in the Stereo system calibration and the embedded stereo system implementation chapters, finally the benchmarks and results chapter followed by the conclusion and discussion.

# Contents

| Pre | eface  | i                                                            |

|-----|--------|--------------------------------------------------------------|

| Ab  | strac  | t iii                                                        |

| Co  | ntent  | ts                                                           |

| Lis | t of F | Figures                                                      |

| 1   | Intro  | oduction                                                     |

| 2   | High   | n-Performance Embedded Computing 3                           |

|     | 2.1    | Graphical Processing Units                                   |

|     |        | 2.1.1 Streaming multiprocessors                              |

|     |        | 2.1.2 CUDA                                                   |

|     | 2.2    | Field Programmable Gate Array    5                           |

|     | 2.3    | Comparison of architectures for vision applications in space |

|     | 2.4    | Heterogeneous computing                                      |

| 3   | Ster   | eo Vision                                                    |

|     | 3.1    | Stereo system geometry         12                            |

|     |        | 3.1.1 Pinhole camera model         12                        |

|     |        | 3.1.2 Depth computation         12                           |

|     |        | 3.1.3 Epipolar geometry 13                                   |

|     | 3.2    | Stereo camera model                                          |

|     |        | 3.2.1 Intrinsic parameters                                   |

|     |        | 3.2.2 Extrinsic parameters                                   |

|     |        | 3.2.3 Distortion                                             |

|     | 3.3    | Image rectification         15                               |

|     | 3.4    | Stereo matching                                              |

|     |        | 3.4.1         The correspondence Problem         16          |

|     |        | 3.4.2 Matching Cost Computation                              |

|     |        | 3.4.3 Parametric Matching Cost Functions 17                  |

|     |        | 3.4.4 Non-parametric Matching Cost Functions 18              |

|     |        | 3.4.5 Cost aggregation                                       |

|     |        | 3.4.6 Disparity Selection/Optimization                       |

| 4   | Meth   | hods and Tools                                               |

|     | 4.1    | Presentation of the hardware         21                      |

|     |        | 4.1.1 Ultrazed-EG Starter kit                                |

|     |        | 4.1.2 TE0808-04-09-2IE-S Starter Kit                         |

|     |        | 4.1.3 Jetson TX2 developer kit                               |

|     | 4.2    | Software tools                                               |

|     |        | 4.2.1 Vivado Design Suite                                    |

|   |      | 4.2.2 PetaLinux tools                      |

|---|------|--------------------------------------------|

|   |      | 4.2.3 SDx/SDSoC                            |

|   | 4.3  | Libraries                                  |

|   |      | 4.3.1 OpenCV                               |

|   |      | 4.3.2 CUDA                                 |

|   |      | 4.3.3 libsgm                               |

|   |      | 4.3.4 XFopenCV                             |

|   |      | 4.3.5 Benchmark                            |

| 5 | Ster | eo System Calibration                      |

|   | 5.1  | Calibration                                |

|   |      | 5.1.1 Camera Parameters                    |

|   | 5.2  | Rectification                              |

|   |      | 5.2.1 cv::InitUndistortRectify()           |

|   |      | 5.2.2 cv::Remap()                          |

| 6 | Emb  | bedded Stereo System Implementation        |

|   | 6.1  | Specification                              |

|   | 6.2  | FPGA development environment35             |

|   | 6.3  | FPGA accelerated functions    36           |

|   |      | 6.3.1 xf::InitUndistortRectifyMapInverse   |

|   |      | 6.3.2 xf::remap                            |

|   |      | 6.3.3 xf::stereoBM 36                      |

|   |      | 6.3.4 xf::SemiGlobalBM 36                  |

|   | 6.4  | FPGA optimizations    36                   |

|   |      | 6.4.1 Stereo matching parallel units       |

|   |      | 6.4.2 The default stereo system            |

|   |      | 6.4.3 Remap matrices storage 38            |

|   |      | 6.4.4 Parallel remapping                   |

|   |      | 6.4.5 Pipelining                           |

|   | 6.5  | GPU accelerated stereo system              |

|   |      | 6.5.1 The implementation                   |

|   | 6.6  | GPU optimizations                          |

| 7 | Ben  | chmarks and Results                        |

|   | 7.1  | Test parameters         43                 |

|   | 7.2  | The I3DS dataset         43                |

|   | 7.3  | Middlebury dataset                         |

|   | 7.4  | Stereo matching accuracy 44                |

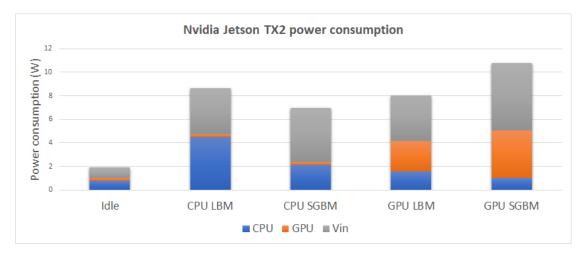

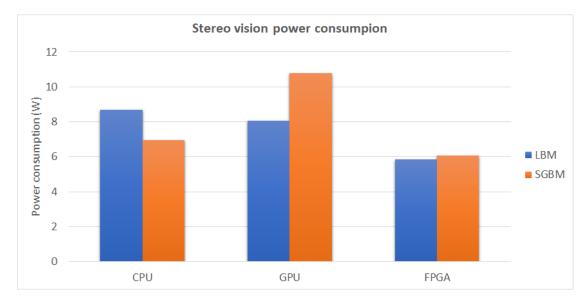

|   | 7.5  | Power consumption                          |

|   |      | 7.5.1         Nvidia Jetson TX2         46 |

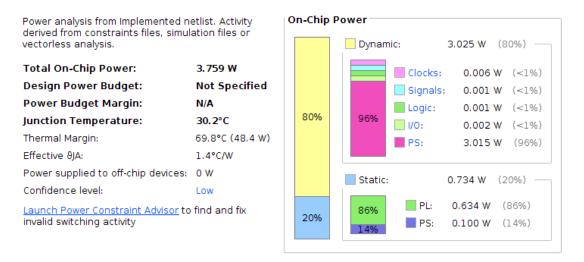

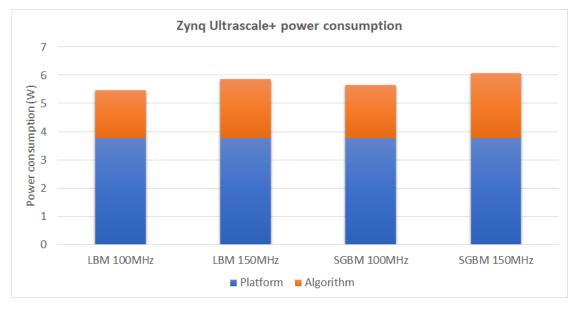

|   |      | 7.5.2 FPGA power consumption         46    |

|   | 7.6  | Processing time / Frames per second 48     |

| 8 | Disc | cussion                                    |

|   |      | 8.0.1 Developement costs                   |

|    |            | 8.0.2 Stereo matching accuracy              |

|----|------------|---------------------------------------------|

|    |            | 8.0.3 Frame rates                           |

|    |            | 8.0.4 Power consumption                     |

|    | 8.1        | Limitations                                 |

| 9  | Con        | clusion                                     |

|    | 9.1        | Further work                                |

| Ap | pend       | lices                                       |

| Α  | Buil       | ding the hardware platform                  |

|    |            | Hardware block design                       |

|    | A.2        | Configure platform and interface properties |

|    | A.3        | Synthesizing the hardware design            |

|    |            | A.3.1 Generating the DSA file               |

|    |            | A.3.2 Note: System format bug               |

| В  | Buil       | ding the operating system                   |

|    | B.1        | Petalinux tools                             |

|    | B.2        | Building the PetaLinux Image                |

|    | B.3        | Petalinux hardware description file         |

|    | B.4        | PetaLinux kernel                            |

|    | B.5        | Configure petalinux rootfs                  |

|    | <b>B.6</b> | Add device tree fragment for APF driver     |

|    | B.7        | Building the PetaLinux image                |

|    | B.8        | Generate boot files                         |

|    | B.9        | Building the SYSROOT folder                 |

|    | B.10       | The petalinux image                         |

| Bi |            | raphy                                       |

# List of Figures

| 1  | Image on the left Curiousity Mars Rover [Credit:NASA/JPL-Caltech/MSSS] Image         |    |

|----|--------------------------------------------------------------------------------------|----|

|    | on the right active debris removal in low earth orbit [Credit: ESA]                  | 1  |

| 2  | Stereo image pair from the planetary I3DS data-set, figure on the right is the       |    |

|    | disparity map generated using a semi-global block matching algorithm                 | 2  |

| 3  | Block diagram of the Mali GPU microarchitecture [1]                                  | 3  |

| 4  | Block diagram of a streaming multiprocessor unit in the Pascal architecture [2] .    | 4  |

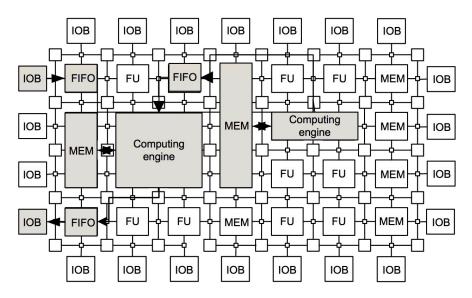

| 6  | Example architecture of reconfigurable hardware [1]                                  | 5  |

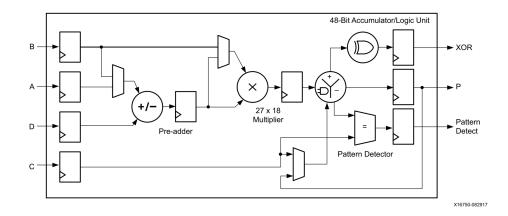

| 7  | The built-in components in the XtremeDSP DSP48 slices that are in the Zynq Ul-       |    |

|    | trascale+ architecture [3]                                                           | 6  |

| 8  | Example accelerator implemented on reconfigurable hardware [1]                       | 6  |

| 9  | Comparison of different processing platforms [4]                                     | 7  |

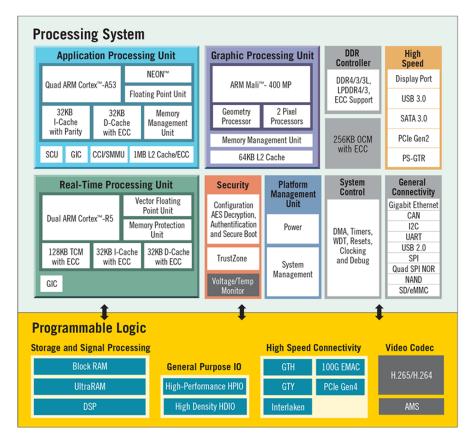

| 10 | Zynq Ultrascale+ EG architecture                                                     | 8  |

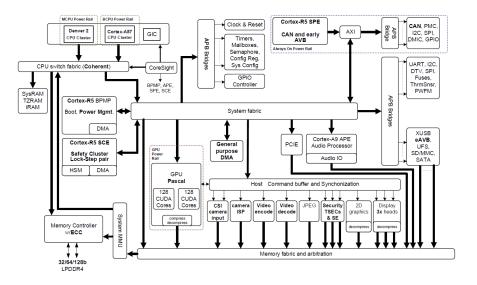

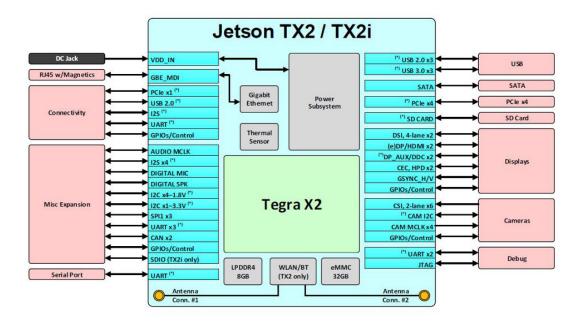

| 11 | Tegra X2 architecture                                                                | 9  |

| 12 | The pinhole camera model. The camera has an origin point $C$ and the image forms     |    |

|    | as pixel $p$ as projection of points $P$ at an offset $f$ [5]                        | 11 |

| 13 | Depth calculation from two perfectly aligned pinhole cameras                         | 12 |

| 14 | Illustration of the epipolar geometry [6]                                            | 13 |

| 15 | A checkerboard pattern demonstrated with no distortion, positive radial distortion   |    |

|    | and negative radial distortion respectively                                          | 14 |

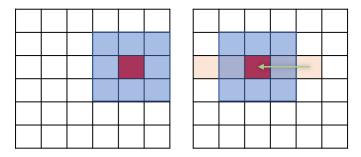

| 16 | Matching cost computation of two pixels $p$ (marked in red), with a position differ- |    |

|    | ence of disparity $d$ (green arrow) in a local block matching algorithm assessed by  |    |

|    | checking the neighbourhood pixels $N$ (marked in blue)                               | 16 |

| 17 | Illumination difference in the planetary I3DS dataset, showing a bias with the       |    |

|    | right image being darker than the left image                                         | 17 |

| 18 | Given a pixel window census transform produces a bit array where every pixel         |    |

|    | represents if the neighbourhood pixel is smaller or larger                           | 19 |

| 19 | Given two bit arrays produced from a stereo image pair their matching cost is        |    |

|    | calculated using hamming distance by using an XOR operator and summing the bits      | 20 |

| 20 | The Ultrazed-EG IO carrier card on the left and the Ultrazed-EG system on module     |    |

|    | on the right featuring an XCZU3EG chip [7]                                           | 21 |

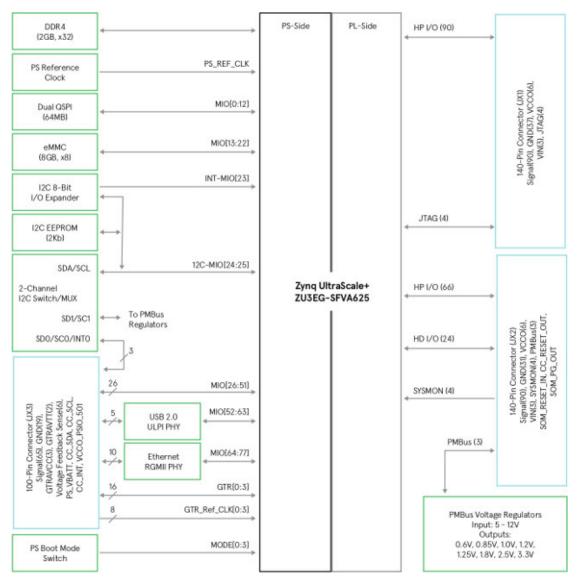

| 21 | The Ultrazed-EG SoM block diagram[7]                                                 | 22 |

| 22 | TE0808-04 carrier board on the left and the TE0808-04-09EG-2IE system on mod-        |    |

|    | ule on the right featuring an XCZU9EG chip [8]                                       | 23 |

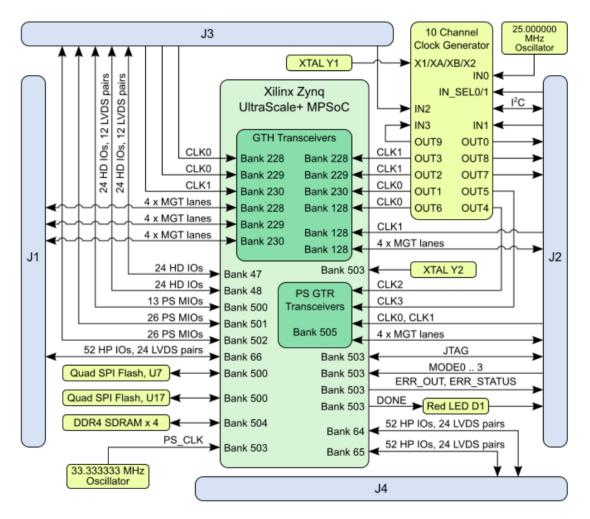

| 23 | The TE0808-04-09 block diagram [8]                                                   | 24 |

| 24 | The Jetson TX2 development kit on the left and the Jetson TX2 system on module       |    |

|    | on the right [9]                                                                     | 25 |

| 25 | The Jetson TX2 block diagram [9]                                                     | 26 |

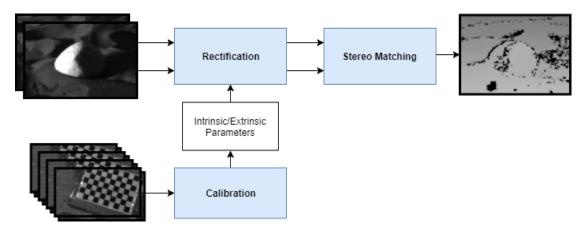

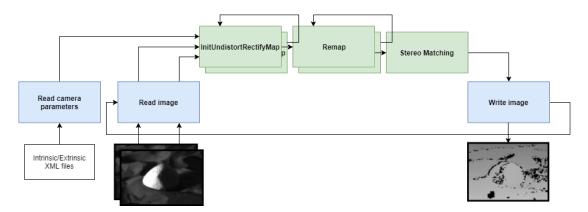

| 26 | High-level view of the overall stereo system; consisting of calibration, rectification<br>and stereo matching blocks                                                                                                                                                                                                                                       | 29 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

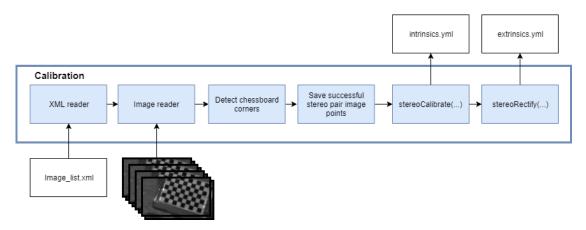

| 27 | The block design of the stereo calibrator C++ app                                                                                                                                                                                                                                                                                                          | 30 |

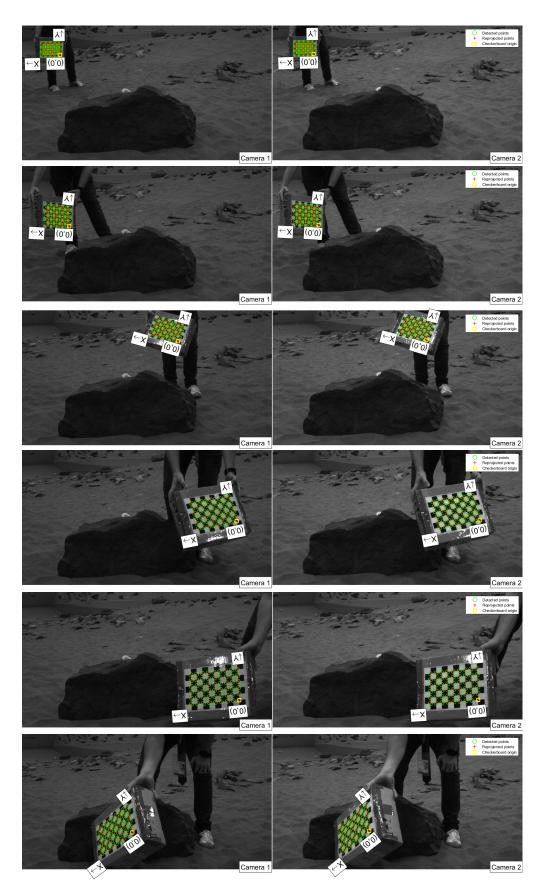

| 28 | Sample set of stereo image calibration pairs taken during I3DS planetary use-case validation in the Airbus artificial Mars landscape in Stevenage.                                                                                                                                                                                                         | 31 |

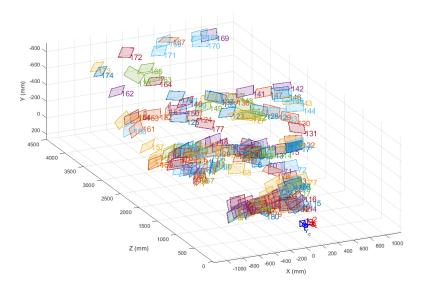

| 29 | Figure generated from matlab showing the relative position and orientation of every checkerboard snap to the cameras                                                                                                                                                                                                                                       | 32 |

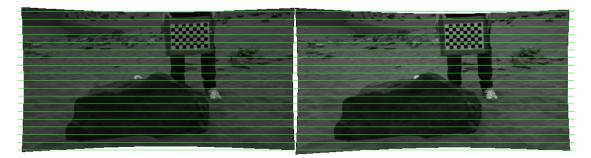

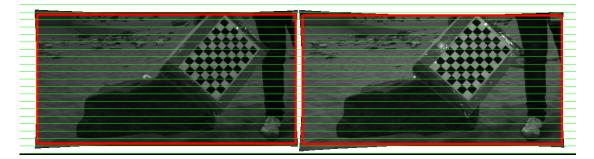

| 30 | Rectification of the stereo pair from the I3DS dataset                                                                                                                                                                                                                                                                                                     | 33 |

| 31 | Rectification and taking a region of interest of a stereo pair from the I3DS for correct disparity map generation                                                                                                                                                                                                                                          | 34 |

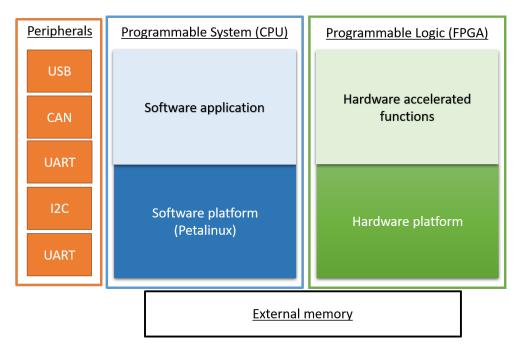

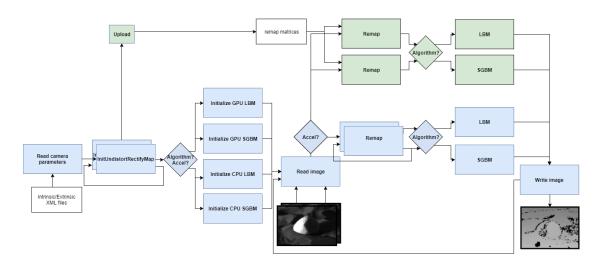

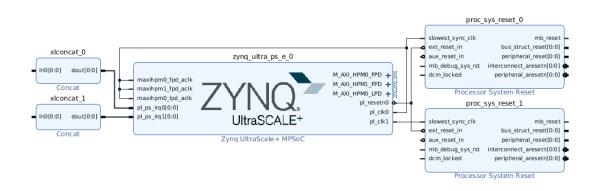

| 32 | High-level view of the software system implemented on the Ultrascale+ architecture                                                                                                                                                                                                                                                                         | 35 |

| 33 | Resource usage of a stereo system using 16, 32 and 80 parallel computational units respectively                                                                                                                                                                                                                                                            | 37 |

| 34 | The default stereo system implementation, with the functions implemented on the CPU side marked in blue and the functions implemented on the FPGA side marked                                                                                                                                                                                              |    |

|    | in green                                                                                                                                                                                                                                                                                                                                                   | 38 |

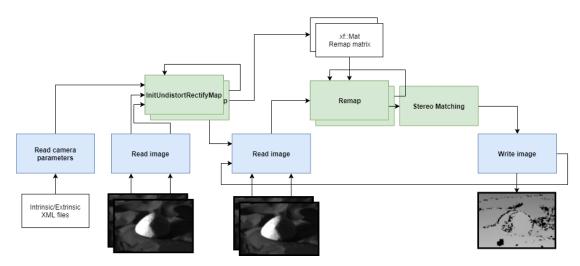

| 35 | Block design of the stereo system with the InitUndistortRectifyMapInverse func-<br>tion moved to the initialization phase                                                                                                                                                                                                                                  | 39 |

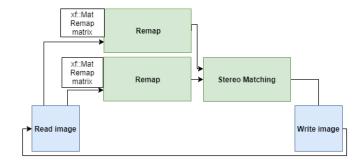

| 36 | Block design of the stereo system with parallel remap, with the functions implemented on the CPU side marked in blue and the functions implemented on the FPGA side marked in green                                                                                                                                                                        | 40 |

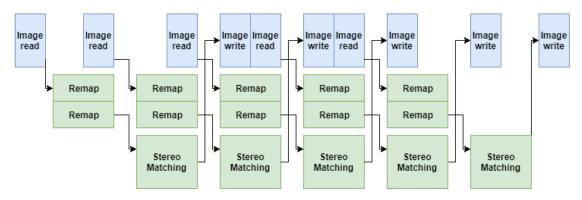

| 37 | Final block design the pipelined stereo system, with the functions implemented on the CPU side marked in blue and the functions accelerated in hardware marked in green                                                                                                                                                                                    | 41 |

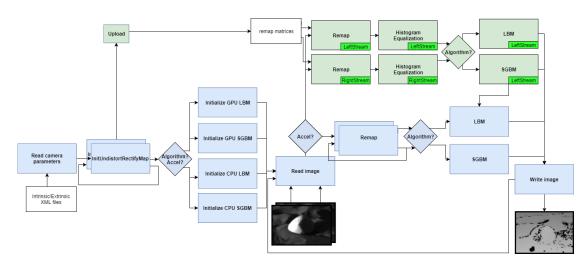

| 38 | The implementation of the GPU accelerated stereo system, with the functions im-<br>plemented on the CPU side marked in blue and the functions implemented on the<br>GPU side, marked in green, accel? checks if the function is marked for accelera-<br>tion in GPU, and Algorithm? checks if to run Local block matching or Semi-global<br>block matching | 41 |

| 39 | The implementation of the GPU accelerated stereo system with asynchronous ex-                                                                                                                                                                                                                                                                              | 42 |

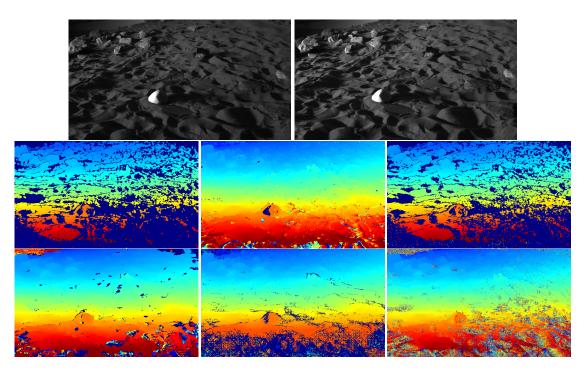

| 40 | The first row shows a stereo pair left and right images respectively, the second row shows the disparity maps from local block matching implementations on CPU, GPU and FPGA respectively, the third row shows the disparity maps from semi-global                                                                                                         |    |

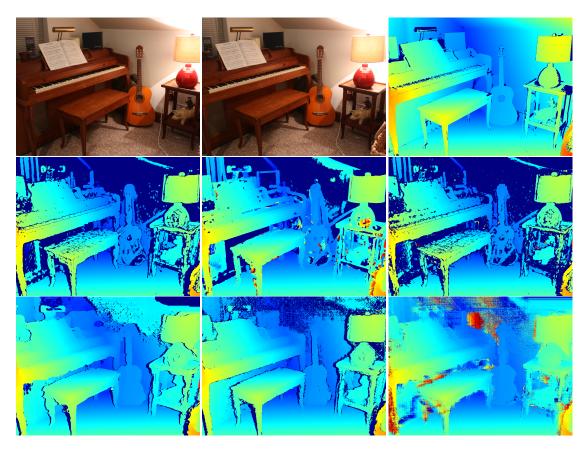

| 41 | The first row shows a stereo pair left and right images, and the ground truth dis-<br>parity map respectively from the Middlebury dataset, second row shows the dis-<br>parity maps from local block matching implementations on CPU, GPU and FPGA<br>respectively, the third row shows the disparity maps from semi-global block match-                   | 44 |

|    |                                                                                                                                                                                                                                                                                                                                                            |    |

| 42       | The average accuracy of the implementation of local block matching and semi global block matching tested with the 2014 Middlebury dataset implemented on CPU, GPU and FPGA architectures                                           | 46       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 43       | The average power consumption for the stereo pipeline implementations on a 1920x1080p stereo pair image stream, showing the CPU power consumption (blue) GPU power consumption (orange) and the grey area shows the power consump- |          |

|          | tion from all the modules in the SoC such as the DDR power consumption                                                                                                                                                             | 47       |

| 44       |                                                                                                                                                                                                                                    | 47       |

| 45       | Power consumed by the FPGA implementation of the stereo pipeline on a 1920x1080                                                                                                                                                    | 17       |

| 10       | stereo pair image stream using both local block matching and semi-global block                                                                                                                                                     |          |

|          | matching, running at a frequency of 100 MHz and 150 MHz                                                                                                                                                                            | 48       |

| 46       | Power consumed for the stereo pipeline implementations LBM and SGBM on a                                                                                                                                                           |          |

|          | 1920x1080 stereo pair image stream, using CPU, GPU and FPGA architectures                                                                                                                                                          | 49       |

| 47       | Google benchmark report with integrated TX2 power measurements                                                                                                                                                                     | 49       |

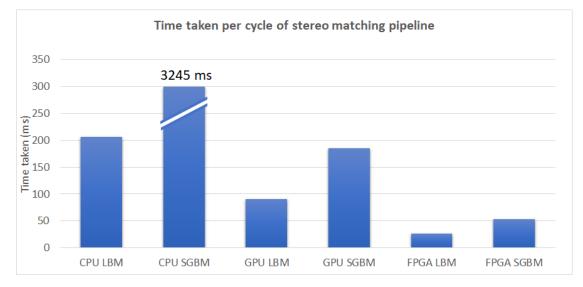

| 48       | Chart showing the average processing time for every implementation with CPU                                                                                                                                                        |          |

|          | LBM at 206ms, CPU SGBM at 3245 ms, GPU LBM at 91 ms, GPU SGBM at 185 ms,                                                                                                                                                           |          |

|          | FPGA LBM at 26 ms and FPGA SGBM at 53 ms                                                                                                                                                                                           | 51       |

| 49       | The output disparity maps from stereo matching pipeline implementations on the                                                                                                                                                     |          |

|          | 2014 Middlebury dataset, 1920x1080 images, 160 max disparity, using local and                                                                                                                                                      |          |

|          | semi-global block matching, implemented on an embedded CPU (ARM Cortex-                                                                                                                                                            |          |

|          | A57), embedded GPU (NVIDIA Pascal) and FPGA (Xilinx XCZU9EG). For every                                                                                                                                                            |          |

|          | output disparity map the average frames per second are shown on the top left                                                                                                                                                       |          |

|          | corner, the average accuracy on the top right and the average system on chip                                                                                                                                                       |          |

|          | power consumption on the bottom left                                                                                                                                                                                               | 54       |

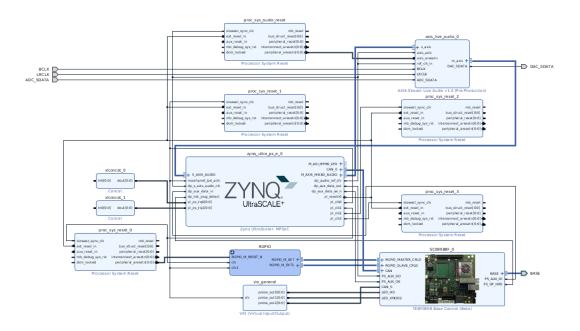

| 50       | Minimal hardware platform block design for SDSoC development                                                                                                                                                                       | 59       |

| 51       | High-level system view with all the active peripherals highlighted                                                                                                                                                                 | 60       |

| 52<br>53 | SK0808 board hardware platform block design                                                                                                                                                                                        | 60<br>61 |

| 33       | Interface properties for an SDSoC hardware platform                                                                                                                                                                                | 01       |

# 1 Introduction

Space robotics is an exciting field with many applications both in low-earth orbit and planetary exploration, such as active debris removal [10] and Mars exploration [11] simultaneous localization and mapping. However, many challenges are faced with the ability to map the environment and localize objects of interests, the "robot" not only needs to be able to understand the contents of 2D images, but also be able to perceive the depth information. There are many sensors that provide 3D information of the environment, one of the most commonly used are stereo cameras.

Figure 1: Image on the left Curiousity Mars Rover [Credit:NASA/JPL-Caltech/MSSS] Image on the right active debris removal in low earth orbit [Credit: ESA]

Stereo cameras, as inspired from nature, takes two images from two different viewpoints at the same time instance, from these images the 3D information of the environment can be extrapolated, it has multiple applications in embedded systems from autonomous cars [12], space [13] and robotics [14] [15]. Stereo vision remains an active area of research, especially with finding how every pixel in a left image correspond to which pixel in the right image; the stereo correspondence is the most challenging aspect [16] within the stereo pipeline, and this project explores different methods to solve this problem.

The use of a typical embedded microprocessor architecture fails to meet the high data throughput demands of stereo-vision algorithms while keeping power consumption to a minimum. Conventional space-grade processors such as LEON3 and RAD750 perform significantly worse than the commercial off the shelf devices [13], which gives the need for high-performance embedded computing [1], employing different architectures to solve different parts within the problem (Heterogeneous Computing Architecture) [17], and using hardware accelerators such as Field

1

Programmable Gate Arrays (FPGAs) [18] and Graphical Processing Units (GPUs) [19].

Figure 2: Stereo image pair from the planetary I3DS data-set, figure on the right is the disparity map generated using a semi-global block matching algorithm

Stereo vision is an "embarrassingly parallel" problem which means the problem requires little to no effort, to be separated into smaller parallel problems which make hardware accelerators (FPGAs and GPUs) work exceptionally well for accelerating the stereo pipeline, due to their highly parallel architecture

This thesis considers the use of high performance embedded systems, for stereoscopic vision in space, it was developed for the Integrated 3D Sensors project I3DS (Integrated 3D sensors) which is funded under Horizon 2020 EU research and development program and is part of the Strategic Research Cluster on Space Robotics Technologies. The I3DS project is developing a generic modular sensors suite, which includes various sensors which are to be used for nearfuture space exploration missions, and solving the challenges of integrated pre-processing and integrating it with the electrical, thermal and mechanical interfaces of the vehicle.

# 2 High-Performance Embedded Computing

For as long as embedded systems have existed, there has been a need for high performance and lower energy consumption; Over the last three decades, embedded systems performance has been improving almost exponentially.

One of the main drivers for such developments was frequency scaling up until the mid-2000s; afterwards multiple technologies have been employed to meet the need for higher performance and lower energy consumption, such as pipelining and multicore architectures. However, now one of the main techniques used when the non-functional requirements are not met and more code optimizations is no longer feasible, Sections of the code can be moved to hardware accelerators to achieve the performance needs, such as embedded graphical processing units (GPU) and field programmable gate array (FPGA).

# 2.1 Graphical Processing Units

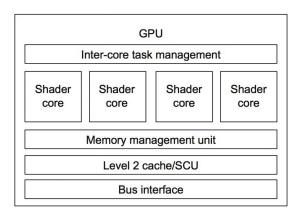

Graphical Processing Units primary purpose was to accelerate the graphical pipeline. However, it can now be used to accelerate many computationally intensive tasks. GPUs offer a massively parallel architecture, with the use of Single Instruction Multiple Data (SIMD) it offers a massive boost for the acceleration of "embarrassingly parallel tasks" such as the stereo block matching algorithm. Embedded GPUs are optimized to run with low power, figure 3 shows the architecture of a Mali GPU with multiple cores accessing shared internal memory.

Figure 3: Block diagram of the Mali GPU microarchitecture [1]

GPUs offer some advantages over other types of hardware accelerators most significant advantage is that it runs multiple floating-point operations in parallel, for example; the Nvidia Jetson TX2 offers 256 cores allowing up to 256 floating-point operations to be running in parallel. Another advantage is that the algorithm is developed in software, incurring lower development costs and time, better backwards compatibility and upgradability. However, this comes at a cost; instructions have to be fetched and cued up, math operations have to be performed, and results have to be sent to memory.

# 2.1.1 Streaming multiprocessors

The GPU is built around an array of streaming multiprocessors, figure 4 shows the Pascal architecture with multiple cores; 64 floating point single precision cores and 32 floating point double precision cores, LD/ST are load/store units they enable overlapping load/store instructions, and SFU is a special function unit.

Figure 4: Block diagram of a streaming multiprocessor unit in the Pascal architecture [2]

# 2.1.2 CUDA

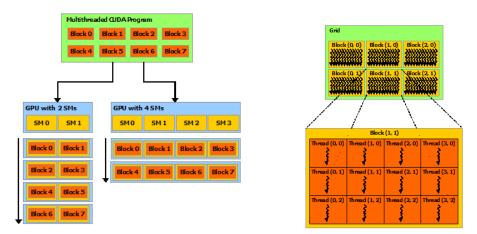

CUDA (Compute Unified Device Architecture) is a parallel computing platfrom developed by NVIDA, it enables the development of applications that leverages the GPU's high levels of parallelism, and was designed to be automatically scalable with the number of streaming multiprocessors and memory partitions as shown in figure 5a.

The functions set to run on hardware invoke a kernel, creating a thread hierarchy that can be grouped into thread blocks as shown in figure 5b, for the image processing application; these blocks are configured into a 2-dimensional grid of blocks, which is also configured into a 2-dimensional grid of threads. The grid size depends on the image size, and can be configured so that there are as many threads as there are pixels.

The GPU employs shared memory to accelerate synchronization for the image processing application, The blocks can store multiple pixels data in the shared memory, giving each thread the ability to access the surrounding pixels of it's pixel.

4

(a) Automatic scalability in a CUDA program (b) Typical CUDA grid of blocks (Reference:[20]) (Reference:[20])

# 2.2 Field Programmable Gate Array

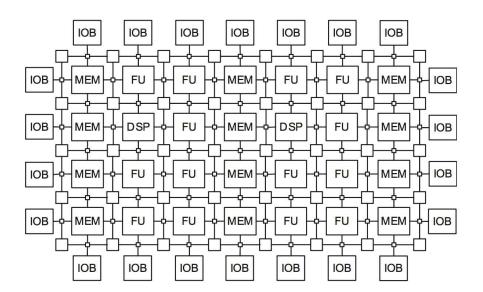

Field programmable gate arrays (FPGA) are inherently highly flexible and reconfigurable allowing the implementation of customized hardware including customized memory, control units and datapath, thus the developer can design efficient hardware to match the application, for example, applications such as image processing, parallel pixel level operations can be employed to providing a system well suited for real-time applications.

Figure 6: Example architecture of reconfigurable hardware [1]

The figure 13 illustrates example hardware within the FPGA, the programmable logic consists of input output blocks (IOB), configurable logic blocks (CLB), digital signal processing components (DSP), Memory components (MEM) and interconnect.

Figure 7: The built-in components in the XtremeDSP DSP48 slices that are in the Zynq Ultrascale+ architecture [3]

When a function is chosen to be accelerated on hardware, it can be configured as in figure 8 with multiple computing engines, a suitable communication structure is chosen (e.g. RAM, FIFO), taking advantage of such flexiblity allows for designs higher performance and lower power consumption.

Figure 8: Example accelerator implemented on reconfigurable hardware [1]

It's difficult to deliver a hard real-time system on multicores running software, due to pro-

|                               | And | Contraction of the second seco | Control Contro | the Constraints | die<br>server<br>of of of of of other | R. C. F. | entropy of the second s |

|-------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughput                    | 0.2 - 1.7                               | 0.5 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20-100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 - 150        | 50-240                                | 300-1460 | 200-2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Power (W)                     | 1 - 18                                  | 1 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 - 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6 - 10          | 1 - 10                                | 2 - 10   | 70 - 195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $\mathbf{Perf}/\mathbf{Watt}$ | $0.1 {-} 0.6$                           | 0.25 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.5 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 - 15          | 12 - 50                               | 60 - 250 | 5 - 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Figure 9: Comparison of different processing platforms [4]

cesses interrupting each other, worst-case execution time, constraints for the criticality of the process and safety. In comparison, FPGAs software analysis for FPGAs is less complex but require increased development time. SoC approach is the most promising for high-performance embedded computing, combining acceleration resources with general purpose processors and peripherals lead to architectures with single-device, low-power, small size/weight and fast intrachip communication to support efficient co-processing.

## 2.3 Comparison of architectures for vision applications in space

High-performance embedded systems have become increasingly important for applications in space such as planetary exploration and active debris removal. High-performance embedded systems are with multiple challenges such as performance to able to process a high throughput of data in real-time, As the system is mainly powered through solar energy, energy efficiency is critical, mass and volume also pose a challenge as they induce high costs.

However, a unique challenge that comes to light for space applications is the radiation tolerance, which is covered by rad-hard and rad-tolerant devices that guarantee reliability but offer much lower performance compared to the commercial off the shelf devices.

The use of high-performance embedded systems in space would provide significant improvement for vision applications in space, as shown by Lentaris et al. [4]. The mobile GPU shows an order of magnitude higher performance per watt, while the FPGA shows two orders of magnitude higher performance per watt than the rad-hard CPU and the embedded CPU.

# 2.4 Heterogeneous computing

Computer vision algorithms can be quite complex, different functions can run more efficiently on different architectures, if the system was designed to run on a single target, it often doesn't meet the performance, and power budget constraints, so heterogeneous architectures pair up different architectures on the same chip providing the ability to exploit every architecture. However, it comes with challenges.

- Choosing which functional blocks to run on which hardware

- The data flow between different processing systems need to be synchronized while satisfying the timing constraints

- Different architectures can have different programming environments and languages

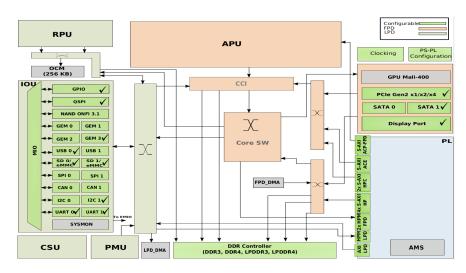

Employing multiple architectures within a single chipset has become more common in recent years, the two architectures that are used for this thesis are good examples for that. First one produced by Xilinx; the Zynq Ultrascale+ EG architecture 10 which includes an application processing unity (ARM Cortex A53), realtime processing unit (ARM Cortex R5), graphics processing unit (ARM Mali 400) and the programmable logic. The second architecture produced by NVIDIA, The tegra X2 architecture 11 used in the Nvidia Jetson TX2, which has Pascal architecture GPU with 256 CUDA cores, Denver 2 dual core CPU and Cortex A57 quad core CPU.

Figure 10: Zynq Ultrascale+ EG architecture

Figure 11: Tegra X2 architecture

# 3 Stereo Vision

Stereo vision is a sensing technique that uses multiple cameras to estimate the 3D position of objects from two cameras in two different positions. The object is detected in both cameras in different positions within the image, the difference between the positions is called disparity, from the disparity, the depth information is calculated.

Stereo vision has been researched heavily over the past 3 decades, with applications spanning from self-driving cars, space exploration to medical imaging. However, it is still faced with many challenges.

The correspondence problem is a difficult challenge [16] and there are multiple algorithms designed to solve it [21] finding which pixel in an image correlates with which pixels in the other image. Another challenge is the real-time performance of the stereo system; stereo vision handles a high throughput of data coming from two cameras. Due to the embedded CPU architecture, it fails to deliver real-time performance in a power constrained application. Architectures such as embedded GPUs and FPGAs can solve this problem, but an algorithm that takes full advantage of the highly parallel nature of both processing systems need to be implemented.

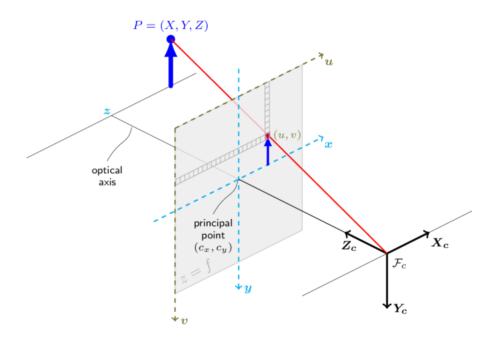

Figure 12: The pinhole camera model. The camera has an origin point C and the image forms as pixel p as projection of points P at an offset f [5]

## 3.1 Stereo system geometry

Estimating the depth information of the scene requires full knowledge of the stereo vision system, each camera's optical characteristics and position/orientation need to be modelled to provide accurate results.

## 3.1.1 Pinhole camera model

The pinhole camera model 12 provides a relationship of a three-dimensional point P = (X, Y, Z) with a pixel position p = (x, y); however, this model assumes no distortion from a lens and assumes the aperture as a point. The pixel p = (x, y) is the projection of the 3D point P = (X, Y, Z) on an image plane that is at an offset f focal length from the camera origin C resulting in the relationship 3.1.

$$x = f \frac{X}{Z} \qquad y = f \frac{Y}{Z} \tag{3.1}$$

Every 3D point P uniquely corresponds to a pixel p, however, for every pixel the corresponding point can lie anywhere along the red line, so to retrieve depth information from pixel positions a second camera is required.

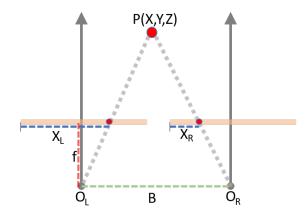

#### 3.1.2 Depth computation

depth data can be calculated to produce a depth map of a scene from the positions of the corresponding pixels in each image by using triangulation.

Figure 13: Depth calculation from two perfectly aligned pinhole cameras

The difference between the corrosponding pixels in both images is called disparity d, and in the case of perfectly aligned pinhole cameras lies on the x axis of the image, so we can calculate the disparity by simply subtracting the x position of each pixel  $X_L$  and  $X_R$

$$d = X_L - X_R \tag{3.2}$$

Once the disparity information is calculated, the depth information can be extracted from the disparity d, focal length f and the distance between both cameras (Baseline b).

$$Z = f \frac{b}{d}$$

(3.3)

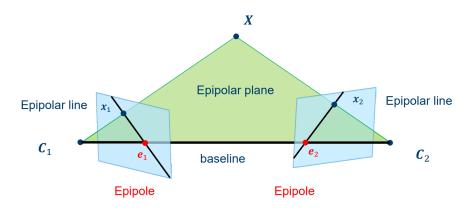

#### 3.1.3 Epipolar geometry

The epipolar geometry describes the relationship between both cameras in the stereo camera and can be used to build it's model.

Figure 14: Illustration of the epipolar geometry [6]

The epipolar plane is the plane containing X, and the two camera centres  $C_1$  and  $C_2$ , the baseline is the line joining the two camera centres, the epipolar lines are where the epipolar plane intersects the image planes, the epipoles are where the baseline intersects the two image planes.

#### **Epipolar constraint**

With knowledge about the epipolar geometry, the stereo matching algorithm can be made more efficient, by constraining the search for correlating pixels along one dimension; the epipolar line.

# 3.2 Stereo camera model

The stereo image is said to be fully rectified, if the epipolar lines lie horizontaly within the images, effictively making the search for the corresponding pixels, on pixels with the same y position. To making rectification possible, the stereo pair need to be rectified in real-time, this is achieved by modeling the camera's optical parameters (intrinsic parameters), and their position/orientation (extrinsic parameters).

## 3.2.1 Intrinsic parameters

The previous relationship is expressed in homogeneous coordinates 3.4.

$$\lambda \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} f & 0 & 0 & 0 \\ 0 & f & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix} = \begin{bmatrix} f & 0 & 0 \\ 0 & f & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix} = \mathbf{A} \begin{bmatrix} \mathbf{I}_{3\mathbf{x}\mathbf{3}} | \mathbf{0}_{3\mathbf{x}\mathbf{1}} \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix}$$

(3.4)

Where  $\lambda$  is a scaling term used to keep the third term normalized to 1, (x, y) is the pixel position, of the 3D point (X, Y, Z), the intrinsic parameters of the camera are represented in the camera

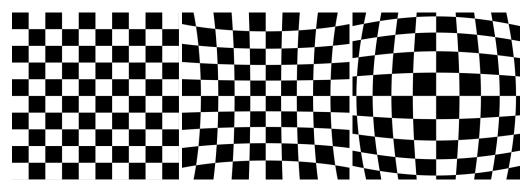

Figure 15: A checkerboard pattern demonstrated with no distortion, positive radial distortion and negative radial distortion respectively

matrix A.

$$\mathbf{A} = \begin{bmatrix} f_x & s & c_x \\ 0 & f_y & c_y \\ 0 & 0 & 1 \end{bmatrix}$$

(3.5)

The focal length f is split into two components  $f_x$  and  $f_y$ ,  $c_x$  and  $c_y$  are the principal point's position relative to the reference frame, and the pixel skew effect s which can usually be ignored for modern cameras, saving up computation time in a resource constraint system.

#### 3.2.2 Extrinsic parameters

The camera itself can move around if it is attached to a dynamic object (robot), so describing the position of the camera can be achieved by moving from the camera coordinate system to the world coordinate system.

The position and orientation of each camera relative to each other and to the world coordinate system are defined in the extrinsic parameters as transformation matrices 3.6.

$$\begin{bmatrix} \mathbf{R}_{3x3} | \mathbf{T}_{3x1} \end{bmatrix} = \begin{bmatrix} r_{11} & r_{12} & r_{13} & t_x \\ r_{21} & r_{22} & r_{23} & t_y \\ r_{31} & r_{32} & r_{33} & t_z \end{bmatrix}$$

(3.6)

Finally, the pixel positions in terms of the 3D point can be calculated 3.7, while taking into consideration the intrinsic and extrinsic parameters.

$$\lambda \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} f_x & s & c_x \\ 0 & f_y & c_y \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} r_{11} & r_{12} & r_{13} & t_x \\ r_{21} & r_{22} & r_{23} & t_y \\ r_{31} & r_{32} & r_{33} & t_z \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \\ 1 \end{bmatrix}$$

(3.7)

#### 3.2.3 Distortion

The biggest source of distortion, however, comes from the lens of the camera, which applies radial distortions 15 and some tangential distortion, which makes the image appear more warped. Taking into consideration the distortion coming from the lenses; the camera model can be extended using the extrinsic parameters from 3.6.

$$\lambda \begin{bmatrix} x'\\ y'\\ 1 \end{bmatrix} = \begin{bmatrix} \mathbf{R}_{3x3} | \mathbf{T}_{3x1} \end{bmatrix} \begin{bmatrix} X\\ Y\\ Z\\ 1 \end{bmatrix}$$

(3.8)

$$r^2 = x'^2 + y'^2 \tag{3.9}$$

$$x'' = x'(1 + k_1r^2 + k_2r^4 + k_3r^6) + 2p_1x'y' + p_2(r^2 + 2x'^2)$$

$$y'' = y'(1 + k_1r^2 + k_2r^4 + k_3r^6) + 2p_2x'y' + p_1(r^2 + 2y'^2)$$

(3.10)

where  $k_1, k_2$  and  $k_3$  are the radial distortion coefficients and  $p_1, p_2$  are the tangential coefficients

### 3.3 Image rectification

The calibration process will extract the intrinsic, extrinsic and distortion parameters. The images from the camera will then need be rectified in real-time using these parameters, proving fully rectified images to the stereo matching algorithm.

There are many rectification algorithms each having it's own advantage, since the thesis is concerned with the implementation on power constrained highly-parallel embedded system architectecture, a well suited algorithm from Zicari et al. [22] can be used to rectify and undistort the images, highlighted in the following series of equations.

$$a_1 = 2.x.y$$

$a_2 = r_2 + 2.x^2$   $a_3 = r_2 + 2.y_2$  (3.11)

$$r_2 = x^2 + y^2$$

$r_4 = r_2^2$   $r_6 = r_2^3$  (3.12)

$$\begin{bmatrix} x_d \\ y_d \end{bmatrix} = (1+k(1).r_2+k(2).r_4+k(5).r_6).\begin{bmatrix} x \\ y \end{bmatrix} + \begin{bmatrix} k(3).a_1+k(4).a_2 \\ k(3).a_3+k(4).a_1 \end{bmatrix}$$

(3.13)

$$\begin{bmatrix} x_{raw} \\ y_{raw} \\ 1 \end{bmatrix} = \mathbf{A} \times \begin{bmatrix} x_d \\ y_d \\ 1 \end{bmatrix}$$

(3.14)

Where A is the camera matrix 3.5, extended with the extrinsic transformations 3.7 and K is the distortion vector.

These equations taken in a pixel location p(x, y) and output a raw rectified and undistorted new raw pixel values  $p_{raw}(x_{raw}, y_{raw})$  which is non integer.

In order to calculate the new rectified pixel position  $p_{rect}$  interpolation is employed;  $x_{raw}$  can be split into it's integer component  $x_i$  and it's non integer component  $x_f$  which leads to  $P_{rect} = (x_{rect}, y_{rect})$  can be computed by interpolating the four surrounding pixels.

$$p_{rect} = (1 - x_f)(1 - y_f)p(x_i, y_i) + (1 - x_f)y_f p(x_i, y_{i+1}) + x_f(1 - y_f)p(x_{i+1}, y_i) + x_f y_f p(x_{i+1}, y_{i+1})$$

(3.15)

From 3.15 the rectified pixel value of every pixel in the image can be calculated, producing a rectified image will be used as input for the stereo matching block.

## 3.4 Stereo matching

The process of taking two images from different views, and outputting the depth information for every pixel is called stereo matching, The three dimensional position of every pixel can be known from the position difference between corresponding pixels (Disparity), which is inversely proportional to the depth position.

#### 3.4.1 The correspondence Problem

Finding which pixel within the other image corresponds to every pixel in an image has proven to be the most challenging step. However this process can be made less computationally demanding by reducing the search area of the corresponding pixels, one method is that if the input images at this stage are fully rectified, the corresponding pixel will have the same Y position, so the search can be limited along the x-axis and up to a maximum disparity.

The stereo matching methods that are considered in this thesis can be split into two categories, local based approaches and global based approaches, where local approaches mainly find the best fit disparity value by choosing the minimal aggregated cost of a window of pixels, while the global-based approaches into these steps [16]

- Matching cost computation SSD, SAD, NCC

- Cost aggregation

- Disparity computation/optimization

- Disparity refinement (post processing)

# 3.4.2 Matching Cost Computation

There are multiple ways to calculate the matching cost of a pixel pair [23]. The best pixel match will be assessed with a cost function, and the matching cost will be assessed by checking the Neighborhood pixels N for each pixel with a disparity value d, the matching cost will be computed, and then the most suited candidate will be used for the next stage.

Figure 16: Matching cost computation of two pixels p (marked in red), with a position difference of disparity d (green arrow) in a local block matching algorithm assessed by checking the neighbourhood pixels N (marked in blue)

There are two methods used to determine the matching cost; first is a **parametric matching cost** which calculates cost based on the intensity values within the neighbourhood window, and the second is a **non-parametric matching cost** which uses only the local ordering of intensity

#### 3.4. STEREO MATCHING

values within the neighborhood pixels, which is more robust against illumination changes.

#### 3.4.3 Parametric Matching Cost Functions

Parametric matching cost functions provides a score for the pixel pair's dissimilarity, and it does that by directly comparing the pixel's intensity values, this provides the advantage of not needing to perform any computation before calculating the cost. However, it makes it particularly vulnerable to changes in illumination.

Illumination can be different between the image pair. Two common challenges that are common are the bias and the vignetting effect. The bias indicates that one image is brighter than the other 17, it usually occurs due to the sensors of the camera reacting differently to the illumination, while the vignetting effect occurs when the pixels at the centre of the image are brighter than the edges.

Figure 17: Illumination difference in the planetary I3DS dataset, showing a bias with the right image being darker than the left image

Different types of parametric matching cost functions have been proposed throughout literature [23] each with its advantages and disadvantages.

#### The Sum of Squared Difference (SSD)

The sum of squared difference is commonly used matching cost function; it is computationally efficient and provides a simple way to get the matching cost. However, it doesn't account for any of the illumination difference; it assumes brightness constancy thus doesn't account for bias and doesn't deal with the aperture problem and thus doesn't account for offset.