NTNU

Norwegian University of Science and Technology

Faculty of Information Technology and Electrical

Engineering

Department of Electronic Systems

Thomas Stenseth

# FPGA based video scaling for broadcast systems

Master's thesis in Electronics Systems Design and Innovation Supervisor: Kjetil Svarstad

June 2019

### Thomas Stenseth

# FPGA based video scaling for broadcast systems

Master's thesis in Electronics Systems Design and Innovation Supervisor: Kjetil Svarstad June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

# **Problem Description**

Assignment title: FPGA based video scaling for broadcast systems

Implement FPGA based video scaler with support for upscaling and downscaling. The scaler should be build-time configurable for scaling between any video resolution. It should also support switching between preconfigured scaling modes during runtime.

Example of preconfigured video scaling modes:

- 720p to 1080p @ 60fps

- 1080p to 720p @ 60fps

- 1080p to 2160p @ 60fps

- 2160p to 1080p @ 60fps

Analyze the performance of the different scaling methods with focus on resource usage, latency and maximum frequency. Find a recommendation for the optimal solution for broadcast video systems, by comparing the different scaling filter implementations. Where the optimal solution offers the best tradeoff between scaled video quality and FPGA resource usage.

The finished system should be verified and documented using best practice methods.

Assignment given: 15. January 2019

Supervisor: Professor Kjetil Svarstad, IES NTNU

Co-Supervisor: Lars Erik Songe Paulsen, Appear TV

# **Summary**

Video scaling is a process used to change the resolution of a video. This is widely used in broadcast systems to be able to support multiple devices using different resolution. Since broadcast systems relies on a continuous non-faulty operation, a hardware-based implementation is preferred over a software-based one, as this often has better performance and stability. The focus on this thesis is to implement a hardware-based video scaler, with a focus on resource usage, latency and maximum frequency, and to verify the implemented design using best practice methods.

A scaler with support for nearest-neighbor and bilinear interpolation was implemented in this thesis. The results from the synthesis test shows that the design meets its performance requirements. Both interpolation methods were able to operate at a maximum frequency above 300 MHz, while only using 1% of the resources of an Intel Arria 10 FPGA, and with a 4-line framebuffer the latency is four lines of pixels.

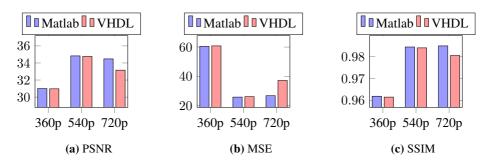

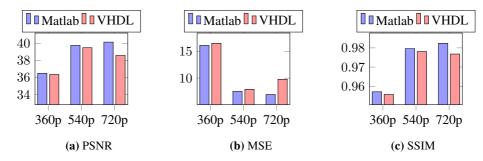

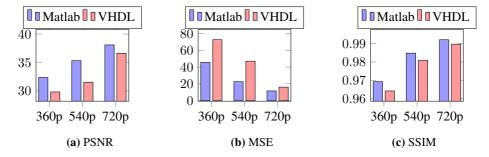

The objective image quality test shows lower performance of the implemented scaler algorithms compared to the reference algorithms, however the subjective test shows little or no difference, raising the suspicion that the lower objective results are a result of shifting in pixel positions, not incorrect pixel color values.

UVVM was used to verify the sub-modules of the design, and an Avalon-ST VIP was implemented for this purpose. Unfortunately, due to time limitations, the top level of the design were not completed, preventing the use of the Avalon-ST VIP for verification of the scaler algorithms.

With completion of the top level of the design, this video scaler would be able to handle scaling of video up to a resolution of 4k with a 30Hz framerate.

# Sammendrag

Video skalering er en prosess brukt for å endre oppløsningen på en video. Dette er mye brukt i profesjonelle kringkastningssystem som skal støtte mange forskjellige typer brukerutstyr med ulik oppløsning. Siden profesjonelt kringkastningsutstyr krever å kunne operere med en kontinuerlig driftstid uten feil på systemet, er en maskinvare-basert løsning å foretrekke over en programvare-basert, da denne ofte har en høyere ytelse og bedre stabilitet. Denne masteroppgaven fokuserer på å designe og implementere en maskinvare-basert video skaleringskrets, og verifisere denne. Designmålet er å kunne kjøre kretsen på så høy frekvens med så lav forsinkelse som mulig, mens samtidig å kunne ha et lavt ressursbruk.

I denne masteroppgaven har en skalererkrets som støtter nærmeste-nabo og bi-lineær interpolasjon blitt designet og implementert. Resultatene fra syntesetestingen viste at skaleringskretsen oppfylte spesifikasjonene som var satt. Den opererte med en maksimumsfrekvens på over 300 MHz for begge interpolasjonsalgoritmene, mens den kun brukte 1% av ressursene som var tilgjengelig på en Intel Arria 10 FPGA. Med et 4-linjers bufferminne er forsinkelsen gjennom kretsen fire piksellinjer.

Den objektive bildekvalitetstesten ga et lavere resultat for den maskinvare-baserte skalereren sammenlignet med referansealgoritmene. Derimot kunne man fra de subjektive testene ikke se noen tydelig forskjell på resultatene sammenlignet med referansen. Dette hinter til en mulighet for at de dårlige objektive resultatene kom fra at pikslene ble flyttet på i posisjon, og ikke at pikslene i seg selv hadde feil fargeverdi.

UVVM ble brukt til å verifisere under-modulene i designet, og en Avalon-ST VIP ble implementert for dette formålet. Dessverre på grunn av tidsmangel, ble ikke toppnivået av designet fullført, noe som gjorde at man ikke kunne bruke UVVM til å verifisere skaleringsalgoritmene.

Ut ifra resultatene kunne man konkludere med at hadde toppnivået på skaleringskretsen blitt fullført, så kunne dette designet ha skalert video med opp til 4k oppløsning og 30Hz bildefrekvens.

### **Preface**

This report is the result of a Master's thesis conducted during the spring of 2019. It is the conclusion of a five year study in Electronics Engineering at the Department of Electronic Systems at the Norwegian University of Science and Technology.

A lot of work has been put down into this thesis, and it has given me a lot of experience in digital design and VHDL coding techniques. The implementation of the Avalon-ST VIP for UVVM were a big challenge, but it gave me good insight into verification methods for VHDL designs.

I would like to thank my supervisor Professor Kjetil Svarstad at NTNU, and my cosupervisor Lars Erik Sogne Paulsen at Appear TV for their help and guidance during this project. I would also like to thank Appear TV for providing me with the necessary software needed to implement, test and verify this design.

June 10, 2019

Thomas Stenseth

# **Table of Contents**

| Pr  | obien   | Description                    | 1    |

|-----|---------|--------------------------------|------|

| Su  | mma     | ry                             | iii  |

| Sa  | mmei    | ndrag                          | v    |

| Pr  | eface   |                                | vii  |

| Ta  | ble of  | Contents                       | xi   |

| Lis | st of I | ligures                        | xiii |

| Lis | st of T | ables                          | xv   |

| 1   | Intro   | oduction                       | 1    |

|     | 1.1     | Background                     | 1    |

|     | 1.2     | Objectives                     | 2    |

|     | 1.3     | Approach and limitations       | 2    |

|     | 1.4     | Features and contributions     | 3    |

|     | 1.5     | Report Outline                 | 3    |

| 2   | Vide    | o Scaling                      | 5    |

|     | 2.1     | Basics of Video Scaling        | 5    |

|     | 2.2     | Nearest-Neighbor Interpolation | 6    |

|     | 2.3     | Bilinear Interpolation         | 7    |

|     | 2.4     | Bicubic Interpolation          | 9    |

| 3   | Inte    | rpolation on an FPGA           | 11   |

|     | 3.1     | Reverse Mapping                | 11   |

|     | 3.2     | Framebuffer                    | 12   |

|     | 3.3     | Nearest-Neighbor Interpolation | 14   |

|     | 3.4     | Bilinear Interpolation         | 15   |

| 4   | Har     | dware Implementation           | 17   |

|     | 4.1     | Fixed-Point Numbers            | 17   |

| 8 | Con   | clusion and Future Work                        | 53       |

|---|-------|------------------------------------------------|----------|

|   | 7.3   | Synthesis test                                 | 49       |

|   | 7 2   | 7.2.5 Subjective image quality                 |          |

|   |       | 8 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6        | 46<br>47 |

|   |       |                                                |          |

|   |       | 7.2.3 Bilinear Functional Verification         | 45       |

|   |       | 7.2.2 Nearest-Neighbor Image Quality           | 43       |

|   | 1.4   | 7.2.1 Nearest-Neighbor Functional Verification | 43       |

|   | 7.2   | Scaler Verification and Image Quality          | 42       |

|   | , . 1 | 7.1.1 Controller                               | 41       |

| • | 7.1   | Verification of Sub-Modules                    | 41       |

| 7 | Resi  | ults and Discussion                            | 41       |

|   | 0.5   | Syndrosis test                                 | 70       |

|   | 6.3   | Synthesis test                                 | 40       |

|   |       | 6.2.3 Test Images                              | 39       |

|   |       | 6.2.2 Objective image quality models           | 38       |

|   |       | 6.2.1 Matlab binary conversion                 | 38       |

|   | 6.2   | Scaler Verification and Image Quality          | 37       |

|   | 6.1   | Verifying VHDL Modules                         | 37       |

| 6 | Testi | ing and Verification Strategy                  | 37       |

|   |       | •                                              |          |

|   |       | 5.2.3 Memory Concerns                          | 35       |

|   |       | 5.2.2 Avalon-ST VVC                            | 34       |

|   |       | 5.2.1 Avalon-ST BFM                            | 33       |

|   | 5.2   | Avalon-ST VIP                                  | 33       |

|   |       | 5.1.3 VVC (VHDL Verification Component)        | 32       |

|   |       | 5.1.2 BFM (Bus Functional Model)               | 32       |

|   |       | 5.1.1 Utility Library                          | 31       |

|   | 5.1   | UVVM                                           | 31       |

| 5 |       | fication IP Implementation                     | 31       |

| _ |       |                                                | _        |

|   | 4.7   | FIFOs                                          | 29       |

|   |       | 4.6.4 Bilinear Interpolation                   | 2        |

|   |       | 4.6.3 Nearest-Neighbor Interpolation           | 26       |

|   |       | 4.6.2 Reverse Mapping                          | 25       |

|   |       | 4.6.1 Scaler FSM                               | 24       |

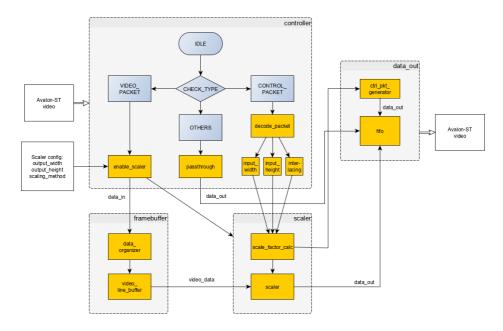

|   | 4.6   | Scaler                                         | 24       |

|   |       | 4.5.3 An Improved Memory Configuration         | 23       |

|   |       | 4.5.2 Multi-port RAM                           | 22       |

|   |       | 4.5.1 Simple dual-port RAM                     | 21       |

|   | 4.5   | Frame buffer                                   | 21       |

|   | 15    | 4.4.1 Controller FSM                           | 20       |

|   | 4.4   | Controller                                     | 20       |

|   | 4.4   |                                                |          |

|   | 4.3   | Interface                                      | 19       |

|   | 4.3   |                                                | 18       |

|   | 4.2   | Top Level Design                               | 17       |

|    | 8.1    | Video Scaler                            | 53  |

|----|--------|-----------------------------------------|-----|

|    | 8.2    | Avalon-ST VIP                           | 54  |

|    | 8.3    | Future Work                             | 54  |

| Bi | bliogr | raphy                                   | 55  |

| Aŗ | pend   | ix                                      | 57  |

| A  | VHI    | OL source code                          | 57  |

| 4. | A.1    | FIFO                                    | 57  |

|    | A.2    | Simple Dual-Port RAM                    | 60  |

|    | A.3    | Multiport RAM                           | 61  |

|    | A.4    | My Fixed Package                        | 63  |

|    | A.5    | Nearest-Neighbor Scaling                | 64  |

|    | A.6    | Bilinear Scaling 4-line Framebuffer     | 69  |

|    | A.7    | Bilinear Scaling Full Size Framebuffer  | 77  |

|    | A.8    | Scaler Controller                       | 83  |

|    | A.9    | Scaler Top Level                        | 85  |

| В  | VHI    | DL Testbenches                          | 89  |

|    | B.1    | FIFO Testbench                          | 89  |

|    | B.2    | Simple Dual-Port RAM Testbench          | 92  |

|    | B.3    | Multiport RAM Testbench                 | 94  |

|    | B.4    | Scaler Algorithm Testbench With File IO | 97  |

|    | B.5    | 1                                       | 100 |

|    | B.6    | Scaler Top Level Testharness With UVVM  | 104 |

| C  | Aval   | on-ST Verification IP source code       | 107 |

|    | C.1    | Avalon-ST BFM                           | 107 |

|    | C.2    | Avalon-ST VVC Testbench                 | 117 |

|    | C.3    | Avalon-ST VVC Testharness               | 119 |

| D  | MA     | ΓLAB source code                        | 121 |

|    | D.1    | Image to Binary Function                | 121 |

|    | D.2    | Binary to Image Function                | 122 |

| E  | Con    | aplete test results                     | 123 |

|    | E.1    | -                                       | 123 |

|    | E 2    |                                         | 125 |

# **List of Figures**

| Reverse mapping                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nearest neighbor interpolation                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

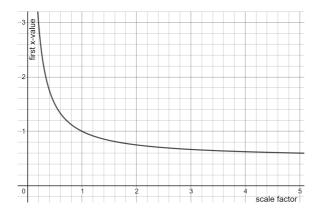

| First x-value as the function of scale factor                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

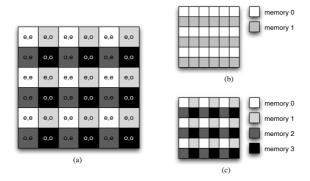

| Mapping pixels in source image to memories [1]                     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

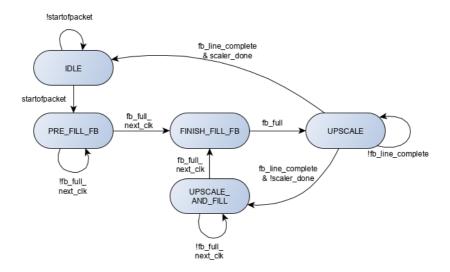

| Upscaler FSM                                                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

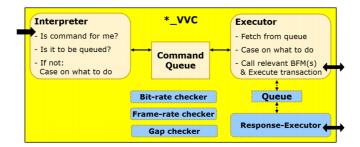

| Structured VVC architecture [2]                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

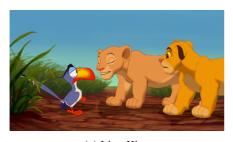

| Natural content used for testing. Taken from Planet Earth II [3] 4 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Bilinear upscaling to 1080p using natural content                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MATLAB vs VHDL bilinear upscaling from 360p to 1080p using ani-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| mated content                                                      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MATLAB vs VHDL bilinear upscaling from 360p to 1080p using natural |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| content                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

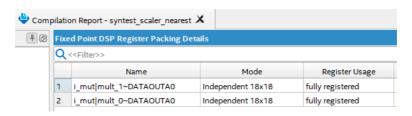

|                                                                    | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Synthesis test bilinear DSP pipeline                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | Nearest neighbor interpolation Bilinear interpolation Bicubic interpolation Bicubic interpolation  Serial video data First x-value as the function of scale factor  Scaler top level Timing diagram of packet transmission Controller FSM Simple dual-port RAM Mapping pixels in source image to memories [1]. Upscaler FSM  Structured VVC architecture [2]  Animated content used for testing Natural content used for testing. Taken from Planet Earth II [3]  Animated content used for testing. Taken from Planet Earth II [3]  Output image from nearest-neighbor upscaling from 720p to 1080p  Nearest neighbor upscaling to 1080p using animated content Vearest neighbor upscaling from 720p to 1080p  Hearest neighbor upscaling to 1080p using natural content Unutu image from bilinear upscaling from 720p to 1080p  Hearest neighbor upscaling to 1080p using natural content  ANEAREST NEW TO THE MATLAB US WHDL bilinear upscaling from 360p to 1080p using animated content  MATLAB vs VHDL bilinear upscaling from 360p to 1080p using natural content  MATLAB vs VHDL bilinear upscaling from 360p to 1080p using natural content  MATLAB vs VHDL bilinear upscaling from 360p to 1080p using natural content  MATLAB vs VHDL bilinear upscaling from 360p to 1080p using natural content  Synthesis test nearest neighbor DSP pipeline |

# **List of Tables**

| 5.1 | Writing data to FIFO from testbench using BFM | 32 |

|-----|-----------------------------------------------|----|

| 7.1 | Synthesis test of sub modules                 | 19 |

| 7.2 |                                               | 50 |

| 7.3 | Performance on Intel Arria 10 GX 1150         | 50 |

| 7.4 | Resource usage on Intel Arria 10 GX 1150      | 52 |

| E.1 | MATLAB nearest-neighbor, animated content     | 23 |

|     | VHDL nearest-neighbor, animated content       |    |

| E.3 | MATLAB nearest-neighbor, natural content      | 24 |

| E.4 | VHDL nearest-neighbor, natural content        | 24 |

| E.5 | MATLAB bilinear, animated content             | 25 |

| E.6 | VHDL bilinear, animated content               | 25 |

| E.7 | MATLAB bilinear, natural content              | 25 |

| E.8 | VHDL bilinear, natural content                | 26 |

# **Chapter 1**

### Introduction

This master thesis builds upon an earlier project thesis conducted at NTNU in the fall of 2018 [4]. In the project thesis, the most common algorithms used for scaling video were explored, and an implementation of these were done in MATLAB. They were compared with each other with respect to ease of implementation, complexity of the algorithm, and their respective performance in image quality after scaling. This master thesis is thus the final step in implementing these algorithms in hardware, and building a working system that performs video scaling.

As this thesis heavily explores hardware implementation of mathematical algorithms, the reader is expected to have knowledge in mathematics, FPGA programming, hardware design and verification methods. Preferably the reader should also have some knowledge about digital video, and be familiar with the concept of color spaces, data streams, and how digital video is being presented to the user.

### 1.1 Background

As current video formats are evolving and people are moving away from watching linear TV to watching content on multiple devices, broadcast equipment that supports these new formats is required. One property of these new devices is that they have displays with many different resolutions and aspect ratios. It is therefore necessary to scale video to support these new formats.

Scaling of video requires scaling algorithms which reconstruct data that is not present in the original material. This is a computational heavy workload, and the design and implementation of the scaling algorithm is key for the end result. Using pure software-based scalers to perform the scaling operation is heavily dependent on the underlying hardware, and the other tasks performed by this hardware simultaneously. Because of this, software-based solutions is not the most reliable and best performing solutions in professional broadcast equipment.

A hardware implementation is preferred over a software-based one in broadcasting systems that require stable 24/7 operation. This way the system is guaranteed to meet its specifications, and the performance is stable over longer periods without the concerns for which other tasks that are running simultaneously. Given that new standards for video delivery are continuously being developed as well, it is often desirable to be able to update the current systems to support these new features. A hardware implementation on an FPGA is therefore a good choice, as this both guarantees the performance demands to be met, as well as having the possibility to be updated with newer video standards as these are being released.

### 1.2 Objectives

This report will focus on the two most used scaling algorithms, and implement these on an FPGA using VHDL. These two algorithms will be compared with regards to how much resources they use on an FPGA, how well they perform in terms of speed, and the image quality of the output produced. To verify the correctness of the system, UVVM (Universal VHDL Verification Methodology) will be used, and a Verification IP that complies with the Avalon-ST Video interface will be implemented for this purpose.

In summary this project aims to:

- Implement a video scaler in VHDL supporting upscaling between resolutions commonly used in broadcast systems.

- Implement a VIP (Verification IP) for the Avalon-ST Video interface compliant with the open-source UVVM (Universal VHDL Verification Methodology) library.

- Test and verify the implemented modules with a focus on meeting the quality and performance requirements set for the system.

### 1.3 Approach and limitations

Video scaling can be performed either as an up- or downscaling process. In the down-scaling process the output consists of less data than the original input, and thus this is a reduction of information. For the upscaling process the opposite is true, and the system has to generate more information than what was present in the original source material. This is a much more heavy computational workload, and in many cases this will be the limitation for how well the system performs. This thesis will therefore focus on the upscaling process in regards of the implementation and testing.

In order to properly test the design, the testing strategy was split into two parts. The first part focuses on functional verification of the signaling and state machines using UVVM and the Avalon-ST Verification IP implemented for this. The other part focuses on correctness of the video output generated by the scaler. This was tested by creating a MATLAB

script that read the output data from the scaler, and compared this to the built-in scaler in MATLAB which served as a reference.

The Avalon-ST Video interface specification was chosen for this project because this design target the Intel Arria 10 FPGA family, and Avalon-ST Video is the interface used by Intels own proprietary IP cores. This makes the Avalon-ST Video interface well documented through Intels own user guides, see [5] and [6], and we can expect this interface to be well suited for implementation of a video scaler on an Intel Arria 10 FPGA.

#### 1.4 Features and contributions

A major contribution of this project is the Avalon-ST VIP implemented for verification with UVVM. This VIP is non-existing amongst the included VIPs in UVVM, or withing the open-source UVVM community, and it will therefore be uploaded to the UVVM community with a MIT licence for public use. It can then serve as a foundation for other users who need UVVM verification of modules utilizing the Avalon-ST interface.

The main contribution will be the implemented scaling algorithm together with the sub-modules created for this project. These will also be published in a public repository on GitHub with a MIT licence for others to use. A lot of groundwork has been made to optimize these algorithms to utilize built-in DSPs on the FPGA, so these designs can be used as a basis for other video scaling implementations.

### 1.5 Report Outline

This report first presents the basics of video scaling together with a detailed explanation of the inner workings of the different scaling algorithms in Chapter 2. Chapter 3 then examines these algorithms further, and provide a possible manner to which these algorithms can be implemented on an FPGA. The actual hardware implementation details is discussed in Chapter 4, where the implementation details for each of the sub-modules making up this design is discussed separately. Chapter 5 gives a brief introduction to UVVM and its components, before discussing the implementation details of the Avalon-ST VIP. The testing and verification strategy is discussed in Chapter 6, and the test images used for this project are presented here. Finally the results are presented in Chapter 7 together with discussions around these, and the final conclusion is drawn in Chapter 8.

# **Chapter 2**

# **Video Scaling**

### 2.1 Basics of Video Scaling

Video scaling is the process of changing the resolution of the frames making up the video. If the resolution is reduced from its original size, a process know as downscaling, the amount of information in each frame will be reduced. This happens since the number of pixels in each frame is reduced. Upscaling, on the other hand, is the process of increasing the amount of pixels in each frame, which also increases the amount of information in each frame. Construction of new pixels in a scaling process from the pixels in the original frames is known as interpolation.

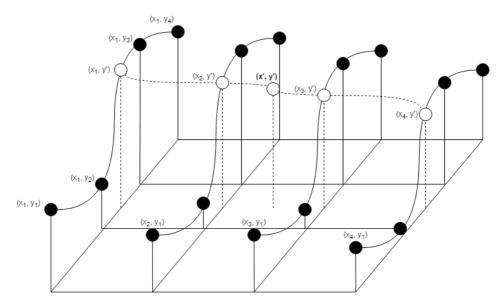

When a video frame is scaled using an interpolation algorithm, the pixels in the new frame has to be mapped to the original frame by a mapping function. This mapping function defines which pixels in the original frame that should be used by the interpolation algorithm to create the new pixel. There are two directions the mapping function could operate, and these are known as *source-to-target* and *target-to-source* mapping, or *forward-* and *reverse mapping* respectively.

In the forward mapping function, each pixel in the source frame is used as a basis and the corresponding pixel in the target frame is calculated from these. This can be described as the mathematical function

$$(x', y') = T(x, y)$$

(2.1)

where x' and y' is the target pixels. This is a hard way to compute the new pixel values, since the mapping function might not have all the necessary information about the target frame to produce a correct result. A result of this is the possibility of introducing holes in the target pixels when one or more pixels are forgotten [7]. A more natural way is therefore to use reverse mapping.

The reverse mapping function uses the new pixels as a basis, and calculate their respective position in the source frame. This can be seen in Figure 2.1.

Figure 2.1: Reverse mapping

The mathematical expression of reverse mapping can be expressed as

$$(x,y) = T^{-1}(x',y') (2.2)$$

and by using this mapping function, it is easier to determine which pixels in the source frame the interpolation algorithm should utilize to generate the new pixel in the target frame. By using reverse mapping you also ensure that all the pixels in the target frame are given values. In the forward mapping method there is a possibility of generating "holes" which are pixels without intensity values. This is not the case with reverse mapping.

### 2.2 Nearest-Neighbor Interpolation

The most basic interpolation algorithm is the nearest-neighbor interpolation algorithm. After the reverse mapping function has calculated the new pixels relative position in the source frame, nearest-neighbor algorithm simply chooses the value of the pixel in the source frame that is closest to the new pixel. This can be described mathematically with a kernel using the weighting coefficients

$$W_{nn}(x,y) = \begin{cases} 1 & \text{for } -0.5 \le x, y < 0.5\\ 0 & \text{otherwise} \end{cases}$$

(2.3)

The function for calculating each pixel's intensity value is thereby given as

$$f(x', y') = f(x, y) \cdot W_{nn}(x' - x, y' - y)$$

(2.4)

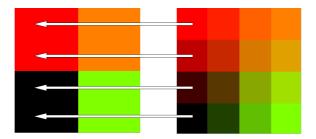

An illustration of nearest-neighbor interpolation in a single dimension can be seen in Figure 2.2, where the black dots represent the original pixels in the source frame.

Figure 2.2: Nearest neighbor interpolation

Since nearest-neighbor interpolation simply takes the values of the nearest pixel, the end result is a very pixelated image. This is generally not a desired result, unless the source material is pixel art. However, nearest-neighbor interpolation has a very low computational requirement, and can easily be done in real-time as it is basically a copy-paste operation.

### 2.3 Bilinear Interpolation

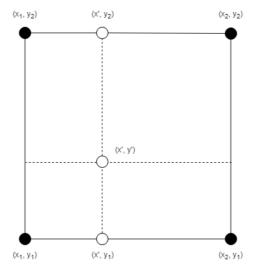

Bilinear interpolation uses a  $2 \times 2$  neighborhood of pixels, as a basis to assign appropriate intensity values to new pixels. It takes the 4 surrounding pixels of the position in the source frame calculated by the reverse mapping function, and calculate a weighted average of these to determine the new pixel intensity. Figure 2.3 demonstrates the concept of bilinear interpolation with (x',y') representing the position calculated by the reverse mapping function.

Figure 2.3: Bilinear interpolation

As the name suggest, bilinear interpolation uses a linear kernel to calculate the weight of

each pixel [8], and the weighting coefficients are given by

$$W_{lin}(x) = \begin{cases} 1 - x & \text{for } |x| < 1\\ 0 & \text{for } |x| \ge 1 \end{cases}$$

$$W_{lin}(y) = \begin{cases} 1 - y & \text{for } |y| < 1\\ 0 & \text{for } |y| \ge 1 \end{cases}$$

$$(2.5)$$

where each weighting coefficient determines intensity in one direction. The kernel for bilinear interpolation would then use the combined weighting coefficient

$$W_{bil}(x,y) = W_{lin}(x) \cdot W_{lin}(y) \tag{2.6}$$

Using the kernel with the weighting coefficients shown in Equation 2.5, we can develop a practical implementation-friendly algorithm for calculating the new pixel intensities. By first performing interpolation in the x-direction, we could generate two new pixel points, shown as  $(x', y_2)$  and  $(x', y_1)$  in Figure 2.3. These new points would then be used to calculate the final pixel intensity, shown as (x', y') in Figure 2.3.

By using the x-direction as the first interpolation direction, we get the two intermediate values  $(x', y_2)$  and  $(x', y_1)$  as given by Equation 2.7 and 2.8.

$$f(x', y_1) \approx \frac{x_2 - x'}{x_2 - x_1} f(x_1, y_1) + \frac{x' - x_1}{x_2 - x_1} f(x_2, y_1)$$

(2.7)

$$f(x', y_2) \approx \frac{x_2 - x'}{x_2 - x_1} f(x_1, y_2) + \frac{x' - x_1}{x_2 - x_1} f(x_2, y_2)$$

(2.8)

From Equation 2.7 and 2.8 we see that each of the four neighbouring pixels are counted towards the two new intermediate intensity values based on the distance they reside from the point given by the reverse mapping algorithm. These two intermediate values is then used to calculate the final value of the pixel. The two values are interpolated in the y-direction as shown in Equation 2.9

$$f(x',y') \approx \frac{y_2 - y'}{y_2 - y_1} f(x',y_1) + \frac{y' - y_1}{y_2 - y_1} f(x',y_2)$$

(2.9)

which yield the final intensity of the new pixel in the target frame.

By using a  $2 \times 2$  neighborhood of pixels and taking a weighted sum of these, the end result of bilinear interpolation is a more correct result than nearest-neighbor interpolation. This way several pixels determine the value of the new pixel, and we avoid situations where the end result is very pixelated. This is especially favourable for natural content where sharp changes from pixel to pixel is scarce. However, bilinear interpolation is more computational demanding than nearest-neighbor as it requires several operations per pixel for the interpolation process.

### 2.4 Bicubic Interpolation

As with bilinear interpolation, bicubic interpolation uses a neighborhood of pixels as a basis to calculate the value of the new pixel. The neighborhood consist of  $4 \times 4$  pixels, and an illustration of this can be seen in Figure 2.4.

Figure 2.4: Bicubic interpolation

Bicubic interpolation utilizes a more advanced convolution algorithm to calculate the weight of the pixels from the source frame [9]. The weight of each pixel is calculated from the following kernel

$$W_{cub}(x) = \begin{cases} (a+2)|x|^3 - (a+3)|x|^2 + 1 & \text{for } |x| \le 1\\ a|x|^3 - 5a|x|^2 + 8a|x| - 4a & \text{if } 1 < |x| < 2\\ 0 & \text{otherwise} \end{cases}$$

(2.10)

In this kernel the value of a is usually set to -0.5, as this is the only value that will achieve third-order precision [9]. Using a=-0.5 and having |x|<2, which is the case for a  $4\times 4$  neighborhood,  $W_{cub}(x)$  simplifies to

$$W_{cub}(x) = \begin{cases} 1.5|x|^3 - 2.5|x|^2 + 1 & \text{for } |x| \le 1\\ -0.5|x|^3 + 2.5|x|^2 - 4|x| + 2 & \text{if } 1 < |x| < 2 \end{cases}$$

(2.11)

The complete kernel for bicubic interpolation in two dimensions is given by multiplying the cubic kernel in both x- and y-direction:

$$W_{bic}(x,y) = W_{cub}(x) \cdot W_{cub}(y) \tag{2.12}$$

Using Figure 2.4 as a basis, and the kernel for bicubic interpolation to calculate the weight of each pixel in the  $4\times 4$  neighborhood, the formula for bicubic interpolation becomes the sum

$$f(x',y') = \sum_{x=\lfloor x'\rfloor-1}^{\lfloor x'\rfloor+2} \left[ \sum_{y=\lfloor y'\rfloor-1}^{\lfloor y'\rfloor+2} f(x,y) \cdot W_{bic}(x'-x,y'-y) \right]$$

(2.13)

This operation is much more computational intensive than bilinear interpolation, but it can also easily be done in parallel. Because of the larger number of source pixels used to determine the value of the new pixel, and the third-order kernel, the end result of bicubic interpolation is usually more accurate and correct than for nearest-neighbor and bilinear interpolation [9].

# **Chapter 3**

# Interpolation on an FPGA

### 3.1 Reverse Mapping

Reverse mapping takes each pixel position in the output frame and calculates the corresponding pixel position in the input frame. This makes reverse mapping well suited for applications where the input can be buffered, and a streamed output is required, see chapter 9.2 in [7]. With reverse mapping you also ensure that there is no holes in the output frame, since the output frame is being generated based on the number of pixels in the output frame itself, not on the input frame.

In the previous project thesis [4], the reverse mapping function was handled by iterating though each pixel in the output frame, and calculate each pixels relative position in the input frame. This was done using the same method for coordinate orientation and interval calculation as was used by [8], and the equation is given as

$$x = \frac{x'}{scalefactor} + 0.5 * \left(1 - \frac{1}{scalefactor}\right)$$

$$y = \frac{y'}{scalefactor} + 0.5 * \left(1 - \frac{1}{scalefactor}\right)$$

(3.1)

where (x, y) is the pixel position in the input frame and (x', y') is the pixel position in the output frame, with x and y being the column and row position respectively in a 2D matrix. The scale factor component is the number of pixels in one direction of the output frame compared to the input frame, so an upscaling from 1280x720 to 1920x1080 would give a scale factor of 1080/720 = 1.5 in the x-direction. This would also be equal for the y-direction as the aspect ratio is preserved after scaling.

We can see from Equation 3.1 that this calculation has one multiplication and two division operations. Division operations on an FPGA is hard, especially when using non-integer

values as is the case with a scale factor of 1.5. Multiplication can be handled more easily with the use of built in DSPs on an FPGA. A more suited equation for calculating (x, y) on an FPGA would therefore be to rewrite Equation 3.1 to only have multiplications. This can be done by first separating out the scale factor division, which is a constant, as

$$c_1 = \frac{1}{scale factor} \tag{3.2}$$

and then use this result to rewrite Equation 3.1 as

$$x = x' * c_1 + 0.5 * (1 - c_1)$$

$$y = y' * c_1 + 0.5 * (1 - c_1)$$

(3.3)

Investigating Equation 3.3 we see that this can be further optimized. The final part of the equation is also always constant, and thus it is only the first part of the equation that needs to be calculated for each new (x', y') value. We could therefore separate the last part as

$$c_2 = 0.5 * (1 - c_1) \tag{3.4}$$

which would yield the final two equations to be performed on an FPGA for each pixel as

$$x = x' * c_1 + c_2 y = y' * c_1 + c_2$$

(3.5)

Equation 3.5 only consist of one multiplication and one addition, this is something that can be well optimized on an FPGA by using DSPs and pipelining.

#### 3.2 Framebuffer

To be able to use reverse mapping on an FPGA, the input video frame has to be buffered in a framebuffer. This is especially true for any interpolation algorithm that requires a neighborhood of pixels in an input frame to calculate the new pixel in the output frame. If the frame is not buffered, pixel values might be lost before the interpolation algorithm gets to use them for the calculation of the new pixel values.

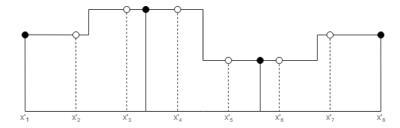

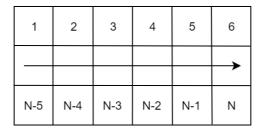

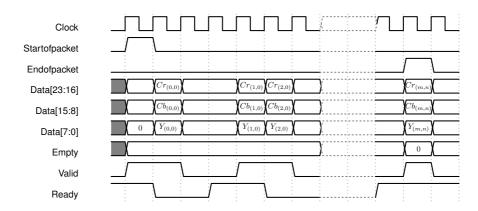

In many cases a digital video signal is being delivered as a stream of serial data with one pixel being sent at a time, staring from the upper left-hand pixel of a video frame, and finishing with the lower right-hand pixel. Because of this, each pixel is only available for one clock cycle on the data bus, and thus is it very important that the pixel data is buffered in a framebuffer. An illustration of the serial video data transfer can be seen in Figure 3.1

Figure 3.1: Serial video data

A complete frame of a video contains a lot of data. Given an input video with the resolution 1920x1080, each frame holds  $\sim 2 \cdot 10^6$  pixels. If each pixel contains 24-bit of data, 8-bit per colour component, a complete frame consist of  $\sim 50$  Mbit of data. This is a very large amount of data that needs to be stored in a framebuffer. Luckily we can exploit the fact that video data often is being transmitted in a series. This way, we only need to store some of the lines in the video frame at any given time.

Given that we use bilinear interpolation as our scaling algorithm, we need a neighborhood of  $2\times 2$  pixels to generate a new pixel for our output data. This way we only need two lines of video data in our framebuffer to do the interpolation. By using reverse mapping and starting the interpolation with the upper left-hand pixel in the output image, the scaling algorithm will flow naturally through the buffered lines in the framebuffer, at the same time generating output data in the same serial fashion as the input data. When the interpolation algorithm is done with these two lines, they are no longer needed, and their memory addresses in the framebuffer can be reused.

While the interpolation is taking place, new data will arrive on the input, and this data would need to be buffered in the framebuffer. If the scaler implementation produces one new video output line at the same rate as one input line is being received, the framebuffer will be emptied at the same rate as it is being filled. This way you would need a framebuffer that is twice the size of the minimum requirement of the pixel-neighborhood of the interpolation algorithm used.

Using bilinear interpolation as an example, this would require a 4-line framebuffer. When two lines have been processed, two new lines would have been filled in the framebuffer. When the interpolation algorithm starts working on these two new lines, the memory addresses of the two old ones are free, and they can be refilled by the incoming video data.

Theoretically, bilinear interpolation could also be performed using a 3-line framebuffer, or even a 2-line framebuffer where the new data is being written to the memory address just emptied by the scaler. However, this could lead to unwanted situations where data is overwritten before it is being read by the scaler if the scaler stalls for a couple of clock periods, or vice versa in a situation where the input data is being stalled while the scaler keeps on going. Using a framebuffer twice the size of the required neighborhood-pixels always put at least one line between the read and write process to the framebuffer. This way the design would have several clock cycles headroom to halt if for instance the input

data is interrupted for a couple of cycles.