## Asbjørn Steensland

# Universal Programmable State Machine

Master's thesis in Electronic Systems Design and Innovation Supervisor: Per Gunnar Kjeldsberg June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Master's thesis

Asbjørn Steensland

# Universal Programmable State Machine

Master's thesis in Electronic Systems Design and Innovation Supervisor: Per Gunnar Kjeldsberg June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Assignment text

#### Candidate name: Asbjørn Steensland

Assignment title: Universal Programmable State Machine

#### Assignment text:

Currently, it is standard design practice to have individual custom made finite state machines (FSMs) that control use of each Mixed Mode IPs (like regulators, PLLs ...) in a design. The assingment will investigate the possibility of having an universal programmable FSM that can be used for all these, and possibly other IPs. Details:

- List advantages and disadvantages for an FSM vs a Microprocessor

- Investigate how such an FSM can be implemented

- Investigate how such an FSM can be programmed

- Investigate how such an FSM can be verified

- Investigate how such an FSM can be hooked up with the overall system

- Investigate how such an FSM can be configured

- Implement an example design based on the investigations outlined above

Assignment proposer/Co-supervisors: Anja Dekens and Conrad Foik, Nordic Semiconductor ASA

Supervisor: Per Gunnar Kjeldsberg, Department of Electronic Systems, NTNU

## Abstract

FSMs are used extensively in digital hardware designs. As the market for ICs and SoCs is increasing rapidly, the designs must follow. FSMs are often custom made and hardwired for each implementation. Thus, their behavior cannot be changed after manufacturing, and it takes time to design each FSM. This thesis investigates a Universal Programmable FSM (UPFSM), which can replace existing FSMs.

An FSM has a state set, a number of inputs and outputs, a state transition function, and an output function. The state transition function finds the next state based on the current state and the input signals. A Moore machine FSM calculates the output based on the current state, while a Mealy machine FSM also uses the input signals.

Two solutions for the UPFSM has been prototyped and investigated:

The LFSM is a LUT based solution which is similar to microprogrammed control. It stores the next state and the output in a LUT which is indexed using the current state and the inputs. The LUT is connected to a bus, allowing a microprocessor to write a new program to LFSM.

The SWFSM is a software-based solution. The input and output signals for the "FSM" are routed to registers accessible by a microprocessor. The microprocessor runs a program in software that read the input register, computes the next state and outputs, and write to the output register.

Both these solutions are used to replace an existing FSM in TD, an existing test-design. TD is part of a larger test-chip, TC, which has a microprocessor.

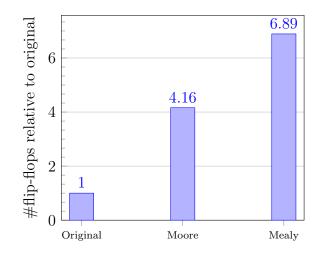

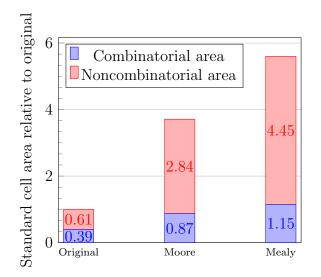

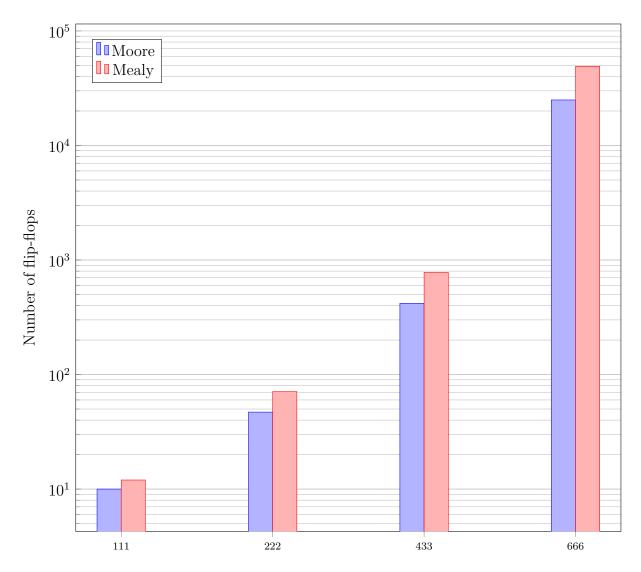

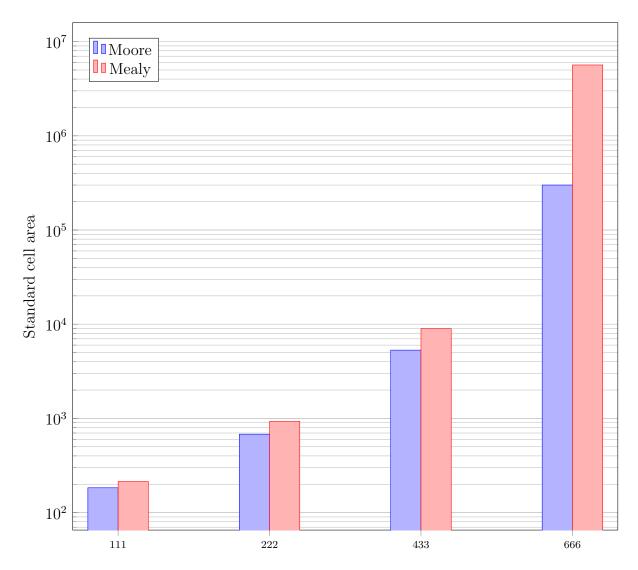

A comparison between the original hardwired FSM, the LFSM, and the SWFSM has been carried out. The original hardwired FSM is not programmable, but easy to use, has a small area, and provide an output every clock cycle. The LFSM is equally fast as the hardwired FSM but not easy to program and require more area. For the FSM in TD, the LFSM is 3.71 times (Moore) or 5.6 times (Mealy) larger than the original hardwired FSM in area. The LFSM area increases exponentially with FSM size. A "666" {#input bits, #state bits, #output bits} Moore LFSM is 441 times larger than a "222" Moore LFSM. The SWFSM require little area when the microprocessor is not considered, and it is easier to program. It is, however, very slow compared to the others, using 992 microprocessor clock cycles to read the input and write the output.

A UPFSM will always be a compromise between area, speed, ease of use, and complexity. However, the programmability can be very useful in certain designs, and this thesis has shown some possible ways to implement it.

# Sammendrag

Tilstandsmaskiner (FSM-er) blir utstrakt brukt i digital maskinvaredesign. Ettersom markedet for integrerte kretser og brikke-systemer er økende må designene følge etter. FSM-er blir ofte spesiallaget og hardkodet for hver enkelt implementasjon. Følgende kan ikke oppførselen endres etter at brikken er produsert. I tillegg tar det tid å designe hver FSM. Denne oppgaven undersøker en Universell Programmerbar FSM (UPFSM) som kan erstatte eksisterende FSM-er.

En FSM har et sett med tilstander, et antall inn- og utganger, en overgangs- og en utgangsfunksjon. Overgangsfunksjonen returnerer neste tilstand basert på nå-tilstanden og inngangsverdiene. Utgangsfunksjonen returnerer utgangsverdiene. For en Moore-maskin er denne kun avhengig av nå-tilstanden, mens en Mealy-maskin i tillegg er avhengig av inngangsverdiene.

To løsninger for en UPFSM er blitt prototypet og undersøkt:

LFSM-en er basert på en oppslagstabell (LUT), og minner om mikroprogrammert kontroll. Den holder neste-tilstanden og utgangsverdiene i en oppslagstabell som blir indeksert av nå-tilstanden og inngangsverdiene. LFSM-en er koblet til en buss, slik at en mikroprosessor kan skrive et nytt program til oppslagsen.

SWFSM-en er basert på programvare. Inn- og utgangssignalene til FSM-en er forlenget til registre som kan leses og skrives til av en mikroprosessor. Mikroprosessoren kjører et program som leser inngangsverdiene, regner ut neste tilstand og skriver utgangsverdiene til registerne.

Begge disse løsningene er brukt til å erstatte en eksisterende FSM i TD, et eksisterende test-design. TD er en del av en større test-brikke, TC, som har en mikroprosessor.

Den originale hardkodede FSM-en, LFSM-en og SWFSM-en er sammenlignet. Den originale FSM-en er ikke programmerbar, men er lett å bruke, krever lite areal og genererer utgangsverdier hver klokkesykel. LFSM-en er like rask, men er vanskelig å programmere og krever mye areal. For FSM-en i TD, bruker LFSM-en 3.71 ganger (Moore) eller 5.6 ganger (Mealy) mer areal enn den originale FSM-en. Arealet øker eksponensielt med størrelsen til FSM-en. En Moore LFSM med "666" {#inngangssignaler, #tilstandsbits, #utgangssignaler} er 441 ganger større enn en "222" Moore LFSM. SWFSM-en bruker mindre areal (sett bort i fra mikroprosessoren), er er enklere å programmere, men den er veldig treg siden den bruker 992 klokkesykler til å lese inngangen og skrive til utgangen.

En UPFSM vil alltid være et kompromiss mellom areal, ytelse, brukervennlighet og kompleksitet. Men, programmerbarhet kan i visse design være veldg nyttig, og denne oppgaven har vist noen mulige måte å implementere dette på.

# Preface

This master thesis is the final assignment for me as a student at Electronics Systems Design and Innovation an NTNU. Doing a thesis of this scope is not something I have done before, and it has been challenging and professionally rewarding. The experiences from a project assignment I did the previous semester has been useful for structuring the work and grasping the task, even though this is a different subject.

I want to thank all persons involved in helping me carry out this thesis; supervisor Per Gunnar Kjeldsberg at Department of Electronic Systems, NTNU, and supervisors Anja Dekens and Conrad Foik from Nordic Semiconductor. Also, thank you to Nordic Semiconductor engineers Knut Austbø, Vinodh Gunasekaren and Berend Dekens for taking your time to help me even though you had no official supervisor role. Nordic Semiconductor, as a company, also have my gratitude for providing working place, tools, and great support.

> Trondheim 09.06.2019 Asbjørn Steensland

# Contents

|          | $\mathbf{Ass}$ | gnment text                                                                                          | i  |  |  |  |

|----------|----------------|------------------------------------------------------------------------------------------------------|----|--|--|--|

|          | Abs            | tract                                                                                                | ii |  |  |  |

|          | San            | mendrag                                                                                              | v  |  |  |  |

|          | Pre            | čace v                                                                                               | ii |  |  |  |

|          | Cor            | tents                                                                                                | ix |  |  |  |

|          | List           | of figures                                                                                           | xi |  |  |  |

|          | List           | of tables xi                                                                                         | ii |  |  |  |

|          | Abl            | reviations x                                                                                         | v  |  |  |  |

| 1        | Intr           | oduction                                                                                             | 1  |  |  |  |

|          | 1.1            | Motivation                                                                                           | 1  |  |  |  |

|          | 1.2            | Project description and limitations                                                                  | 2  |  |  |  |

|          | 1.3            | Objectives and main contributions                                                                    | 2  |  |  |  |

|          | 1.4            | Report outline                                                                                       | 2  |  |  |  |

| <b>2</b> | Theory 5       |                                                                                                      |    |  |  |  |

|          | 2.1            | Automata theory                                                                                      | 5  |  |  |  |

|          | 2.2            | Finite State Machines                                                                                | 6  |  |  |  |

|          |                | 2.2.1 FSM versus Turing machine                                                                      | 8  |  |  |  |

|          |                | 2.2.2 Mealy and Moore FSM                                                                            | 9  |  |  |  |

|          |                | 2.2.3 Implementation of FSM in hardware                                                              | 9  |  |  |  |

|          | 2.3            | Microprocessors                                                                                      | 10 |  |  |  |

|          | 2.4            | Microprogrammed Control                                                                              | 1  |  |  |  |

|          | 2.5            | Lookup table                                                                                         | 12 |  |  |  |

| 3        | $\mathbf{Des}$ | gn tools, previous work and related work 1                                                           | .3 |  |  |  |

|          | 3.1            | Design tools                                                                                         | 13 |  |  |  |

|          |                | 3.1.1 SystemVerilog $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 13 |  |  |  |

|          |                | 3.1.2 Mentor Graphics QuestaSim <sup><math>\widehat{\mathbb{R}}</math></sup>                         | 4  |  |  |  |

|          |                | 3.1.3 Industry standard synthesis tool                                                               | 4  |  |  |  |

|          | 3.2            | Previous work at Nordic Semiconductor                                                                | 4  |  |  |  |

|          |                | 3.2.1 Test Design (TD)                                                                               | 4  |  |  |  |

|          |                | 3.2.2 Test Chip (TC)                                                                                 | 15 |  |  |  |

|          | 3.3            | Related work                                                                                         | 16 |  |  |  |

|              |        | 3.3.1 Software based FSMs on microprocessors                 | 16        |

|--------------|--------|--------------------------------------------------------------|-----------|

|              |        | 3.3.2 Programmable FSMs using custom processor architectures | 18        |

| 4            | UP     | FSM development and design                                   | <b>21</b> |

|              | 4.1    | Hardware-based UPFSM                                         | 22        |

|              |        | 4.1.1 Development                                            | 22        |

|              |        | 4.1.2 LFSM design                                            | 24        |

|              | 4.2    | Software based UPFSM                                         | 30        |

|              |        | 4.2.1 Development                                            | 31        |

|              |        | 4.2.2 Design                                                 | 31        |

| <b>5</b>     | Tes    | ting, results, and discussion for the UPFSM                  | 35        |

|              | 5.1    | LFSM                                                         | 35        |

|              |        | 5.1.1 Results from synthesis                                 | 35        |

|              | 5.2    | SWFSM                                                        | 38        |

| 6            | Eva    | luation and discussion                                       | 41        |

|              | 6.1    | Area                                                         | 41        |

|              | 6.2    | Throughput and speed                                         | 41        |

|              | 6.3    | Power consumption                                            | 42        |

|              | 6.4    | Complexity and ease of use                                   | 43        |

|              | 6.5    | Summary and future work                                      | 44        |

| 7            | Cor    | nclusion                                                     | 47        |

| Bi           | ibliog | graphy                                                       | 49        |

| $\mathbf{A}$ | ppen   | dices                                                        | 51        |

|              | А      | LFSM source code                                             | 51        |

|              | В      | Spreadsheet for USB-FSM                                      | 53        |

|              | С      | Python txt-file parser script                                | 55        |

# List of Figures

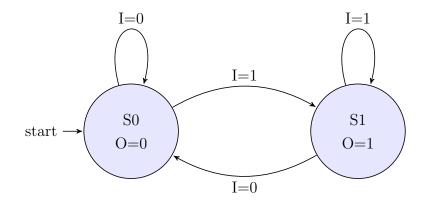

| 2.1 | Simple state diagram                                                                                  | 7  |

|-----|-------------------------------------------------------------------------------------------------------|----|

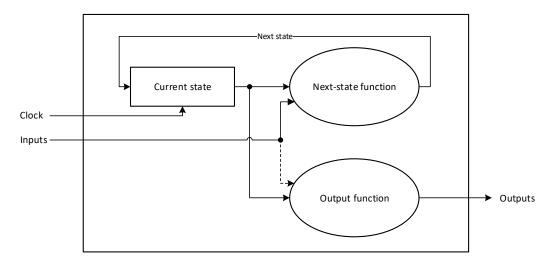

| 2.2 | Model of the functions in a FSM. The dashed line only applies to Mealy                                |    |

|     | machines.                                                                                             | 9  |

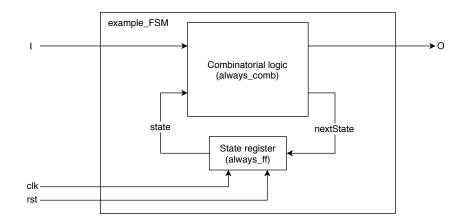

| 2.3 | HDL implementation of the example FSM                                                                 | 11 |

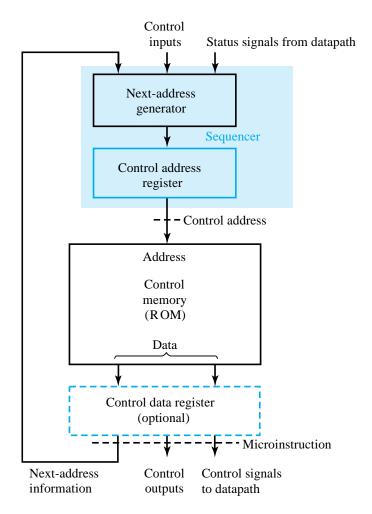

| 2.4 | Microprogrammed control unit organization [18]                                                        | 12 |

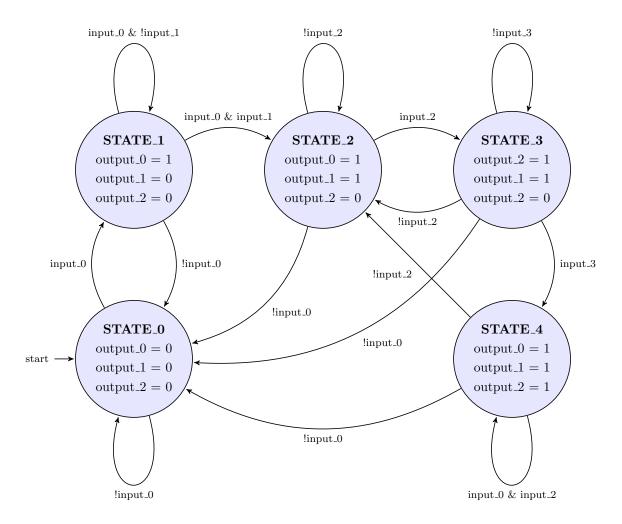

| 3.1 | State diagram of TD                                                                                   | 15 |

| 3.2 | Timeline showing the flexibility of a software based FSM during the design                            |    |

|     | stages [5]. $\ldots$ | 17 |

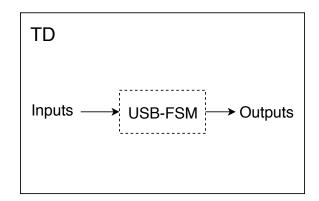

| 4.1 | The existing TD with the hardwired USB-FSM. The dashed lines indicates                                |    |

|     | that the USB-FSM is not an IP, but is hardwired in TD                                                 | 21 |

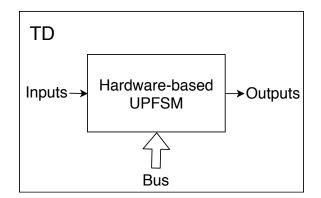

| 4.2 | TD with the hardware-based UPFSM                                                                      | 22 |

| 4.3 | Overview of the LFSM and its three main parts                                                         | 24 |

| 4.4 | The layout of the LUT. The size in this figure correspond to the USB-FSM.                             | 25 |

| 4.5 | Simplified overview of how the SWFSM works with TD and TC. The USB-                                   |    |

|     | FSM is gray to illustrate how the signals are re-routed                                               | 30 |

| 4.6 | Overview of the SWFSM and its connections                                                             | 31 |

| 5.1 | Number of flip-flops relative to original TD                                                          | 36 |

| 5.2 | Area relative to original TD                                                                          | 36 |

| 5.3 | Number of flip-flops for different LUT sizes of LFSM. X-axis numbers are                              |    |

|     | ${\#input width, \#state-bits, \#output witdth}, Y-axis is logarithmic with}$                         |    |

|     | base 10. $\ldots$    | 37 |

| 5.4 | Area of LFSM. X-axis numbers are {#inputs, #states, #outputs}, Y-axis                                 |    |

|     | is logarithmic with base 10                                                                           | 38 |

# List of Tables

| 2.1 | State transition table for a simple FSM                                           | 7  |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | State transition function $\delta$ . The next state is based on the current state |    |

|     | and the input signal.                                                             | 8  |

| 2.3 | Output function $W$ . The output signal is determined by the current state        |    |

|     | only                                                                              | 8  |

| 6.1 | Summary and comparison of the three types of FSMs considered                      | 45 |

# Abbreviations

| ALU            | - Arithmetic Logic Unit             |  |  |

|----------------|-------------------------------------|--|--|

| CAR            | - Control Adress Register           |  |  |

| CPU            | - Central Processing Unit           |  |  |

| $\mathbf{FSM}$ | - Finite State Machine              |  |  |

| HDL            | - Hardware Description Language     |  |  |

| IC             | - Integrated circuit                |  |  |

| IoT            | - Internet of Things                |  |  |

| IP             | - Intellectual Property             |  |  |

| LFSM           | - Lookup table Finite State Machine |  |  |

| $\mathbf{LUT}$ | - Lookup table                      |  |  |

| MMI            | - Mixed Mode Intellectual Property  |  |  |

| RTL            | - Register Transfer Level           |  |  |

| ROM            | - Read Only Memory                  |  |  |

| SWFSM          | - Software Finite State Machine     |  |  |

| SoC            | - System on Chip                    |  |  |

| $\mathbf{TC}$  | - Test Chip                         |  |  |

| TD             | - Test Design                       |  |  |

|                |                                     |  |  |

${\bf UPFSM}~$  - Universal Programmable State Machine

## 1 Introduction

#### 1.1 Motivation

Our daily lives today are depending on digital electronics and integrated circuits (ICs). In the future, the demand for ICs will continue to increase. Internet of Things (IoT), where electronic devices are connected to the internet, will fuel this demand for the foreseeable future. In 2018, 7 billion IoT devices were connected, and this is predicted to increase to 22 billion devices in 2025 [1], [2]. Innovation and smart design are critical factors in order to fulfill the demands. Since Moores law is ending [3], smart design is even more critical. Moores law used to be a driving element in the industry, and designers must now find other means to develop the technology further. Another aspect is the increased complexity of the designs. In order to be competitive and meet time to market demands, it is beneficial to reduce the design time. This thesis aims at both provide innovations into the field of state machines and help reduce design time.

Digital logic can be classified as sequential or combinatorial. In a sequential system, the behavior is determined by the inputs to the system and the current state of the system. This indicates that the system uses the previous events to determine the current state and thus the behavior. Such systems cannot be described with a truth table and are instead described as a finite-state machine (FSM) [4].

In this thesis, the focus will be on different implementations of FSMs used to control other circuits or components of an IC. Usually, such FSMs are hardwired and custom made to each application and implementation. Designing a custom FSM each time it is needed is time-consuming and inflexible. The lack of flexibility arises from the fact that the workings and behavior of the FSM cannot be changed after manufacturing of circuit. Being able to change the FSM behavior can be useful if the circuit is not working as expected. The central concept in this thesis is thus to present a Universal Programmable FSM (UPFSM), which can be reprogrammed after manufacturing and can be used to replace hardwired FSM. The FSM does not have to be programmable in run-time and programmability at reset or power-up is sufficient.

Such a UPFSM can be implemented in software and use microprocessors to execute the software [5], [6]. This kind of implementation has the advantage of being flexible, relatively easy to use, and can do other tasks than just the FSM tasks. However, microprocessors are slow and costly in terms of area, complexity, and power consumption, so hardware FSMs are typically used. Instead of using a full microprocessor, it is possible to create something in between a microprocessor and a custom hardwired FSM, which can remedy a microprocessor's drawbacks of cost and speed.

### **1.2** Project description and limitations

This thesis describes the development and design of two possible solutions for a UPFSM. The two are a hardware-based solution and a software-based solution. These solutions are made to replace an existing FSM in a current IP-design, but they are designed with the ability to replace other FSMs as well. Furthermore, these solutions will be compared to each other and a hardwired FSM. The evaluation is based on area, throughput and speed, power consumption, and complexity and ease of use.

The hardware-based design, is implemented as an intellectual property core (IP) [7] for use in existing designs. It is not fully verified but is used to replace an existing hardwired FSM in an analog mixed-mode IP (MMI) which has a testbench for verification.

The software-based design, is based on forwarding the input and output signals to a microprocessor in a System-On-Chip (SoC). This microprocessor runs a software program that acts like an FSM. The software-based FSM is also used to replace the same hardwired FSM.

The assignment is proposed by semiconductor company Nordic Semiconductor, and existing designs and frameworks by Nordic semiconductor are used in this thesis.

### 1.3 Objectives and main contributions

The objectives in this thesis are:

- Compare state machines and microprocessors.

- Replace FSMs in an existing IP with a UPFSM.

- Evaluate and compare the different UPFSM solutions with the existing hardwired FSM implementation. The evaluation criteria are area, speed and throughput, power consumption, and ease of use.

The work and evaluation will contribute to an understanding of different ways to implement FSMs and use of them in digital circuits. This includes the compromises between area and speed, and how the compromises are affected by the FSM size. Besides, it may provide more ideas of FSM implementations and open up for other optimizations.

### 1.4 Report outline

The report is divided into the following chapters:

Section 2: Theory presenting relevant background theory on automata theory, FSMs,

microprocessors, microprogrammed control, and look-up-tables (LUT).

Section 3: Design tools, previous work, and related work describing the design tools and language used in this project and presents the previous work used for the UPFSM. In addition, an overview of work related to this project is presented.

Section 4: UPFSM development and design presenting the development and design of the hardware-based and software-based designs.

Section 5: Testing, results, and discussion for the UPFSM presenting the testing, results obtained, and a discussion for each of the two designs.

Section 6: Evaluation and discussion presenting an evaluation and comparison of the different ways to implement FSMs and suggesting topics for future work.

Section 7: Conclusion summarizing the findings in the thesis.

**References** list the references used in this thesis.

Additional information, such as source code are attached in the Appendices A to C.

## 2 Theory

This chapter presents and describes relevant background theory used in this report.

### 2.1 Automata theory

Automata Theory is a theoretical branch of computer science. In the 20th century, mathematicians began developing machines, both theoretically and physically, which completed calculations faster and more reliably than humans [8]. The word *automaton* means performing certain processes automatically and is closely related to the word "automation". An *automata* is a simple machine which can be used to perform the logic computations in such processes. Automata give computer scientists an understanding of how machines compute functions and solve problems. More importantly, they provide insight into what it means for a function to be *computable* or for a question to be *decidable* [8].

Abstract models of machines that perform computations on input signal changes by moving through a series of states or configurations are called automatons. A transition function determines the next configuration or state on the basis of a finite portion of the present configuration. This transition function is used in each state of the computation. The Turing machine is the most general and powerful automata [8].

The primary objective of automata theory is to develop methods which help to describe and analyze the dynamic behavior of discrete systems where signals are periodically sampled. The construction of the system in terms of storage and combinatorial elements determines the behavior. The characteristics typically include [8]:

- Inputs: sequences of input symbols from a finite set I of input signals.  $I = \{x_1, x_2, x_3...x_k\}$ , where k is the number of input signals.

- Outputs: sequences of symbols from a finite set Z of output signals.  $Z = \{y_1, y_2, y_3...y_m\},\$ where m is the number of output signals.

- States: a finite set Q, which is defined by the type of automaton

There are four major families of automatons:

- Finite-state machine (FSM)

- Pushdown automata

- Linear-bounded automata

- Turing machine

The above families can be seen as a hierarchy, where the simplest automaton is the FSM, and the most complex is the Turing machine [8]. Besides, it can be said that the Turing machine is an FSM, while the FSM is not a Turing machine. The Turing machine will be briefly described in Section 2.2.1.

#### 2.2 Finite State Machines

Sometimes, the inputs to a system do not contain enough information to describe the system behavior. Modeling such systems require an internal state. If the number of states in a system is finite, it is a finite state system [9]. A finite state machine (FSM) is an automaton in which the state set Q contains a finite number of elements. FSMs are abstract machines, and consists of a set of states (Q), a set of input signals (I), a set of output signals (Z), a state transition function, and an output function. The state transition function returns the next state and a new set of output events by using the current state and an input event. In the most general form, the state transition function can be seen as a function which maps an ordered sequence of input signals (I) into a corresponding sequence of output signals (Z):

$$I \to Z$$

(1)

A finite state machine is a sequential system which provides an output based on the following five components, which can be described by the following definition [8]:

$$M = (Q, I, Z, \delta, W) \tag{2}$$

where

Q: Finite set of states.

*I*: Finite set of input signals.

Z: Finite set of output signals.

$\delta$ : State transition function,  $\delta : Q \times I \to Q$ .

W: Output function,  $W: Q \times I \to Z$ .

As mentioned, an FSM contains a finite number of states. Each state accepts a finite number of inputs, and each state has a state transition mapping function that describes what actions to perform for a change in the input signals. Thus, a change in the input signals may cause the machine to change states and change the output signals.

In order to explain some more concepts used in FSMs, consider an example of an FSM. It should have two states, S1 and S2, and one input signal (I) and one output signal (0).

If I=0, the FSM should go to state S0, and if I=1, the FSM should go to S1. In S0, O=0 and in S1, O=1. Since the outputs only depend on the current state, it would be a Moore machine. Moore machines and the counterpart, Mealy machines, is elaborated further in Section 2.2.2. This FSM could, for example, describe a door, where S0 is an open door, and S1 is a closed door. The input could resemble the door handle, and the output is the actual door position; closed or open. This can be described using a *state transition table*, which is presented in Table 2.1.

| Input | Current State | Output | Next State |

|-------|---------------|--------|------------|

| 0     | SO            | 0      | S0         |

| 1     | S0            | 0      | S1         |

| 0     | S1            | 1      | S0         |

| 1     | S1            | 1      | S1         |

Table 2.1: State transition table for a simple FSM

The state transition table contains all necessary information to describe an FSM. The state transition table shows all the states, the transitions between the states, and what the output is in each state. Such a table is still not a formal description, but it is intuitive and easy to grasp. A state diagram illustrates the state transition table. The state diagram does not formally describe the FSM, but contains the same information as a formal description [10]. Figure 2.1 shows the state diagram for the example FSM.

Figure 2.1: Simple state diagram

Using formal definition from Equation (2), the example FSM will be described as

$$M_1 = (\{S0, S1\}, \{I\}, \{O\}, \delta, \{W\})$$

(3)

In Equation (3), the example state machine is called  $M_1$ , and it has the state set  $Q = \{S0, S1\}$ , the input signal  $I = \{I\}$  and the output signal  $Z = \{O\}$ . The state transition function  $\delta$  is described using Table 2.2, and the output function is described using Table 2.3.

**Table 2.2:** State transition function  $\delta$ . The next state is based on the current state and the input signal.

|    | 0  | 1  |

|----|----|----|

| S0 | S0 | S1 |

| S1 | S0 | S1 |

Table 2.3: Output function W. The output signal is determined by the current state only.

|    | 0 | 1 |

|----|---|---|

| S0 | 0 | 0 |

| S1 | 1 | 1 |

#### 2.2.1 FSM versus Turing machine

As previously described, the FSM is the simplest automaton, e.g., the simplest way to describe a computational system. It is, therefore, not an adequate computation model for all types of systems. A Turing machine, on the other hand, is a lot more powerful.

A theoretical computer has two states for each bit, but within the computer, there is no theoretical limit of the number of components the computer interacts with. This means an FSM will not be sufficient to model a computer. However, more powerful automata, such as a Turing machine can be capable enough.

A Turing machine is an abstract machine essentially consisting of a "control unit", a "tape" and a "read-write device" [11]. The control unit, which essentially is an FSM, contains a set of instructions and is at any time in a certain state. The state set is finite. The tape is divided into squares, and each square can contain a symbol. The read-write device can operate on exactly one square of the tape. It can read an existing symbol on the tape, or overwrite what is on the square. The read-write device can move left or right on the tape. The tape can be infinitely long, giving the Turing machine infinite memory. [8]. Formally, the Turing machine is defined as a 7-tuple [12]:

$$M = (Q, \Sigma, \Gamma, \delta, q_0, B, F) \tag{4}$$

where

- Q: The finite set of states of the control unit.

- $\Sigma$ : The finite set of input symbols.

- $\Gamma$ : The complete set of tape symbols, which always is a subset of  $\Sigma$ .

- $\delta$ : The transition function  $\delta(q, X)$ , with the arguments state q and tape symbol X.

- $q_0$ : The start state, which is a member of Q.

- B: The blank symbol. This is in  $\Gamma$ , but not in  $\Sigma$ .

F: The set of accepting states, a subset of Q.

The Turing machine differs from an FSM in the fact that the Turing machine is capable of changing symbols on its infinitely long tape. The FSM's only memory is its current state, while the Turing machine has memory on the tape, which can be infinitely long. The reading and writing of the tape simulates the execution and storage used in computers and means the Turing machine can model all computations that can be calculated in modern computers [12].

#### 2.2.2 Mealy and Moore FSM

Figure 2.2: Model of the functions in a FSM. The dashed line only applies to Mealy machines.

The output from an FSM can be determined by the current state only, or a combination of the current state and the inputs. The first one is called a Moore machine, named after Edward Moore, who presented the concepts in a paper [13] in 1956. The latter machine is called a Mealy machine and is named after George H. Mealy [14]. In a Mealy machine, the outputs are determined by both the inputs and the current state. It follows that the output function uses both the current state and inputs as parameters. Figure 2.2 depicts the functions and components of an FSM and the difference between Mealy and Moore. The output function only depends on the current state for a Moore machine, while it also depends on the inputs for a Mealy machine.

#### 2.2.3 Implementation of FSM in hardware

In a digital circuit, a state register holds the current state, and two logic functions compute the output and the next state which is to be fed to the state register. In a hardwaredescription language (HDL) such as SystemVerilog, the example FSM could be written using enumerated types for the states [15]. A way to create the example FSM in SystemVerilog is presented in Listing 1. The SystemVerilog language is further elaborated in Section 3.1.1.

```

module example_FSM

1

^{2}

(

input logic clk,

3

input logic rst,

input logic I,

4

5

6

7

output logic O

);

typedef enum logic {S0, S1} stateType;

8

9

stateType state, nextState;

10

11

12

always_ff @(posedge clk or posedge rst) begin

if (rst) state <= S0;</pre>

13

else

state <= nextState;</pre>

14

end

15

16

always_comb begin

17

18

case (state)

S0: begin

19

'0;

0 =

20

if (!I) nextState = S0;

21

nextState = S1;

else

22

end

\frac{23}{24}

25

26

if (I)

nextState = S1;

27

nextState = S0;

else

28

end

29

endcase

30

end

31

endmodule

32

```

Listing 1: HDL code for a simple FSM

In this code, one can see that the nextState function and output functions are combinatorial logic and is declared inside an *always\_comb* block. The *always\_ff* block contain the state register. A register is sequential logic and needs a clock for synchronization. This code will result in a circuit almost similar to the Moore machine version in Figure 2.2, but with some generalizations, as can be seen in Figure 2.3.

There are many more ways to create and optimize hardware implementations of FSMs. Many computer-aided design (CAD) programs can use either a graphical or textual representation of an FSM and produce an optimized implementation automatically [4].

#### 2.3 Microprocessors

As presented in Section 2.1, it is possible to argue that a microprocessor can be modeled as an FSM automaton. In the real world, however, microprocessors are more general and capable than hardware FSMs. A microprocessor is an IC containing a central processing unit (CPU) [16]. The microprocessor is a register-based, clock driven digital IC

Figure 2.3: HDL implementation of the example FSM.

that accepts binary input data. The input data is processed according to instructions found in the memory and provides results as outputs. Depending on the instructions, the processing can be performed differently.

The logic circuitry of a microprocessor can be divided into two parts: the datapath and the control unit [17]. The datapath performs the actual executions of the data, such as adding numbers or writing to registers. The datapath thus contains the pipeline with its functional units, such as the arithmetic logic unit (ALU) and registers for the temporary storage of data. The control unit is responsible for controlling the datapath by setting control signals to the functional units and the peripheral units such as memory.

#### 2.4 Microprogrammed Control

A control unit with its binary control values stored as words in memory is called microprogrammed control [18]. Each word contains a microinstruction that specifies one or more microoperations for the system. A sequence of such microinstructions is called a microprogram. Usually, this microprogram is fixed at design time and stored in ROM. However, it can be stored in RAM and loaded at system startup from non-volatile storage. A RAM solution is called writable control memory and would require read/write functionality [18].

Figure 2.4 show the general configuration of microprogrammed control. The "control address register" (CAR) specifies the address of the microinstruction in the ROM. One part of the microinstruction word is used to determine the address of the next microinstruction. The rest of the microinstruction is used for various control signals. The next-address information may be combined with various input signals in the "next-address generator", which generates the next address. The CAR and the next-address generator is often called a sequencer.

Figure 2.4: Microprogrammed control unit organization [18]

### 2.5 Lookup table

A lookup table (LUT) is a group of memory cells which, given a set of input values, contain all possible results of a given function [19]. The values of the function must be stored so that the output values correspond to the input values. A LUT with n inputs will have  $2^n$  single bit memory cells. LUTs are often used to encode logic functions in field-programmable gate arrays (FPGAs).

## 3 Design tools, previous work and related work

#### 3.1 Design tools

This chapter presents an overview and a brief description of the design language and tools used in the work for this thesis.

#### 3.1.1 SystemVerilog

SystemVerilog is a hardware-description language (HDL) [20]. It is used to model, simulate, and verify the functionality of digital circuits at levels of abstraction ranging from system level down to gate and switch level, including RTL. The following paragraphs present some important constructs and features used in this thesis.

**Module** is a basic unit of hierarchy in SystemVerilog. Modules contain declarations and functional descriptions and represent hardware components. They can be nested, meaning a module can be instantiated inside another module.

SystemVerilog Interface (SVI) is used to encapsulate communication between blocks, for example, between modules. This makes it useful for design reuse, increases code readability, and ease the maintenance of IPs [20]. In its purest form, an SVI is a bundle of nets and variables but can contain tasks and functions to model bus functionality.

**Assertions** are used for functional verification. Two types exist, immediate and concurrent assertions. Immediate assertions are used to test the value of an expression. Concurrent assertions are used to test properties. Properties are built from sequences, which describe behavior over time, and thus with respect to a clock. If an assertion is violated, an error is generated. Assertions are typically checked dynamically during simulations [20].

*always\_comb* and *always\_ff* are the two main SystemVerilog constructs used in this thesis. They are used for combinatorial and sequential logic, respectively. [20]

*logic*, *enum* and *parameter* are the most prevalent types used. *logic* is the same as *reg*, and has a user-defined size. *logic* is preferred in SystemVerilog [20]. *Enum* is used to compact the code and make it more readable. *Typedef* is used in combination with *enum* to define user-defined types. *Parameter* is used to giving names to constant values.

This can be used to define bus widths etc., which makes simulating different sizes and modifying the design easier.

#### 3.1.2 Mentor Graphics QuestaSim<sup>®</sup>

QuestaSim<sup>®</sup> is a simulation tool provided by Mentor Graphics. It is used to simulate RTL designs and netlists, running testbenches, and help in verification of designs [21]. The waveform generator is used extensively in the design work in this thesis. The waveform can be used to measure the time between signals are set and see how the signals behave. It supports SystemVerilog assertions and coverage for verification. For full-chip simulations, version  $10.7c_{-3}$  was used.

#### 3.1.3 Industry standard synthesis tool

For synthesis of the different designs in order to get results for area, power consumption and throughput, an industry standard synthesis tool is used.

#### 3.2 Previous work at Nordic Semiconductor

Both following sections describe work done by Nordic Semiconductor. This work is used as a foundation for development, design, and testing the different UPFSM implementations.

#### 3.2.1 Test Design (TD)

TD is an IP from Nordic Semiconductor written in SystemVerilog. It is a mixed-mode IP (MMI) used to control an analog power regulator using digital logic. It is a part of a larger system for power supply to an SoC called Test Chip (TC). In this thesis, an FSM inside TD is used for experimentation and evaluation purposes.

TD is connected to the main bus structure on the SoC and can thus be enabled or disabled from software. If TD is enabled and a USB cable is connected, TD will initiate a startup sequence using the aforementioned FSM for the analog logic and notify the microprocessor when the USB power supply is ready and stable. The USB cable is in this context only regarded as a power source.

The FSM in question has 4 input signals, 3 output signals, and 5 states. The state transition diagram is seen in Figure 3.1. Only the input signals indicated at the transition arrows are used for that transition. All other input signals are don't care bits and not used.

Figure 3.1: State diagram of TD.

The exact mechanisms controlled by this FSM are not crucial for this thesis. However, TD and its FSM was relevant for experimentation for programmable FSMs, as the physical, manufactured analog circuits may behave differently than the models used in the design work. Being able to change the FSM behavior would allow for optimizing the circuit for the analog circuits. The original FSM in TD is created similarly to the method presented in Section 2.2.3.

#### 3.2.2 Test Chip (TC)

TC is an SoC from Nordic Semiconductor, in which TD is included. TC is a wireless communications SoC, with several peripherals and microprocessors. It is designed for low power operation. The microprocessor used in this thesis is from ARM<sup>®</sup>. The microprocessor is connected to a bus structure, which enables the microprocessor to access TD and other components of TC. The physical TC was not used; only a model was used to simulate the behavior of TC. The model of TC has an existing framework and toolchains for running simulations and programs.

### 3.3 Related work

This chapter presents work which is related to this thesis. Some of this work is directly relevant for this thesis, as it has been the basis of the experimentation and evaluations. Some of the work is not directly relevant for this thesis, but it can suggest other ways of implementing FSMs and invoke other possible solutions.

#### 3.3.1 Software based FSMs on microprocessors

Work in the field of software-based FSMs on microprocessors is relevant for programmable FSMs. In this thesis, the work done by the microprocessor architecture company ARM [5] and by Comer [6] is used. ARMs white paper is the most recent and relevant for this thesis, but the work of Comer is, albeit old, relevant as it presents parameters and what to consider when comparing conventional state machines to microprocessor-based state machines.

**ARM** proposed in a white paper that the microprocessor architectures developed by ARM can be used to replace hardware FSMs [5]. The paper presents several reasons to use software-based FSMs in SoC designs and how they can be implemented. The advantages of using software-based FSMs are:

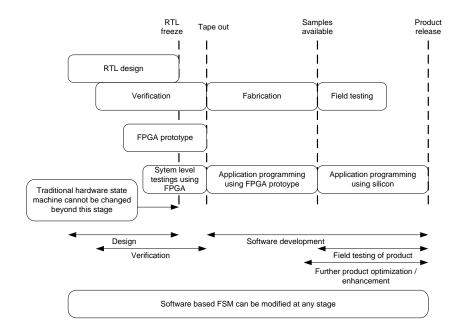

- Increased flexibility: As the software-based FSMs reduce the risk of the project by allowing the FSM to be changed at any time in the project cycle. A hardware FSM cannot easily, if at all, be changed after production. Figure 3.2 shows how this flexibility compares to the other methods of designing FSMs.

- Debug methodology: Since the software-based FSMs use a program, conventional debug tools can be used to, for example, set breakpoints and halt the processor. This helps in optimizing the design.

- Combine software control capability to FSM design: Sequential operations are easier to handle, and functions/subroutine calls can be used to implement repetitive tasks. Also, assembly code can be used to optimize parts of the FSM operations, and the rest can be programmed in C.

The white paper then presents some design examples and what to consider for implementing an FSM on the different ARM Cortex-M architectures. It is challenging to meet the speed and time-critical requirements, and the paper also mentions workarounds and

Figure 3.2: Timeline showing the flexibility of a software based FSM during the design stages [5].

propose methods to help with such challenges. However, many of these methods require high clock frequencies.

**Comer** considers the use of a microprocessor as a controller for digital systems [6]. The paper, published in 1987, suggests that a microprocessor can be considered as an FSM with each state being defined in terms of possible machine instructions. The approach is based on the following premises:

- 1. The state machine approach is used for the microprocessor controller. This means that the functionality of the controller is partitioned into states, which are implemented in software running on the microprocessor.

- 2. Since the same approach is used for both a controller running in a microprocessor and a controller in a hardware state machine, it allows for partitioning the functionality into software and hardware.

- 3. After all refinement has been done, a comparison between a conventional state machine and a microprocessor state machine can be carried out. A choice between them can thus be based on criteria such as cost, area, or performance.

Some key differences between them are presented. A conventional state machine computes the next state directly when the input changes, while a microprocessor must add the inputs to an accumulator which is used to branch to the next state. The addition to the accumulator involves at least one data transfer. Another difference is the timing, where a conventional state machine remains in a given state for one clock cycle, and then moves to a new state or remains in the same. In a microprocessor, some states may only be for timing purposes, and others consider the inputs. A third difference is in the data manipulation or processing capabilities of the microprocessor, which opens up possibilities for storing data and use it for branching later and so on. A conventional state machine will require additional circuitry to do this.

The strengths of microprocessors are versatility, the possibility of more states without increasing system complexity, and the fact that they are programmable. The main weaknesses are speed and cost. The cost includes both the hardware and also the fact that microprocessors require programming, which in 1987 involved paying a manufacturer to program the ROM or buying an expensive ROM burner.

The concluding remarks are that a microprocessor controller is limited to lower frequency operations and are more expensive for smaller systems. For large systems with many states or that require flexibility in terms of changing the sequence of control signals, using a microprocessor controller might be reasonable.

#### 3.3.2 Programmable FSMs using custom processor architectures

Using a custom processor architecture to implement a programmable state machine has been done in the past. Wangyang et al. [22] and Hatta et al. [23] has done this, and their work is briefly presented below.

Wangyang et al. created a programmable state machine for packet processing [22]. It is called a PSM and is intended to bridge the gap between a hardware FSM and a full processor. The PSM is a 4 stage pipeline with 18 instructions which are classified as register type, immediate type, and branch types. The application example is for packet processing. The PSM replace an FSM which is used for parsing packet headers. The main drawback with the PSM instead of a hardware FSM is speed, but it is less complicated and costly than a full processor and retains the advantages of programmability.

Hatta et al. also created a programmable FSM which they call the P-FSM [23]. It is designed to minimize both the logic and memory area using a specific architecture for state management of communication protocols. The P-FSM is a state processor capable of handling various types of state diagrams. The instruction memory can be changed and used to implement additional state management. A sequencer is used to index the instruction memory. The P-FSM is used as a hardware accelerator on a communications SoC, where it placed between the embedded processor and *dynamically reconfigurable*

*hardware for protocol processing* (DRHPP). It must be programmable in order to handle various communication protocols.

The P-FSM contains a sequencer used to address the instruction memory. The sequencer is also used as a step counter to control activation of an instruction processor. The instruction memory contains several FSM programs, and the sequencer thus indexes the correct FSM instructions. The instruction processor consists of an instruction decoder, calculation block, forwarding block, register-comparison block, event-comparison block, and two MUXes.

According to the article, it is, for a network communications application, 90 times faster than an ARM processor and from RTL synthesis only 1.5% of the area of a conventional communications SoC.

# 4 UPFSM development and design

The goal of this thesis is to make a Universal Programmable State Machine (UPFSM) which can replace FSMs in existing IP designs and is possible to reprogram after the SoC has been manufactured. The thesis will also include an evaluation of possible ways to implement a UPFSM and compare it to a hardwired FSM, in terms of area, speed, power consumption, and ease of use.

An existing IP, TD, and SoC, TC, is used to develop and test the UPFSM. TD and TC are presented in Section 3.3. TD contains a hardwired FSM from before which is used to control an analog MMI (mixed mode IP). This analog MMI is a power regulator which gets its power supply from a USB cable. The existing FSM is therefore called the "USB-FSM". A simplified overview of TD and the USB-FSM can be seen in Figure 4.1. A realistic aim in making the UPFSM is to be able to replace the USB-FSM and to be able to program it. The USB-FSM is only an example of an FSM which can be replaced, meaning the UPFSM should be able to replace most other FSMs as well.

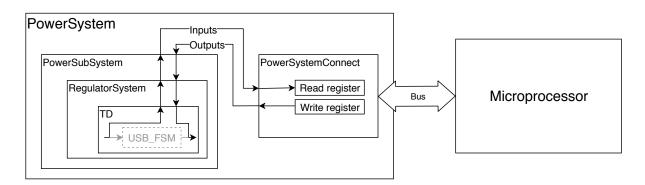

Figure 4.1: The existing TD with the hardwired USB-FSM. The dashed lines indicates that the USB-FSM is not an IP, but is hardwired in TD.

A UPFSM can be implemented in many ways. Two possible starting points are using a hardware-based design or a software-based design. A hardware-based design involves developing a system that is programmable, flexible, and can replace existing design. A software-based design means implementing the UPFSM in software that is running on a microprocessor. The microprocessor can be hooked up to the existing FSM connections. Investigating both of these solution spaces would allow for interesting evaluation and comparison. Therefore, two prototype designs for replacing the USB-FSM are implemented. The development of the two methods are presented in Section 4.1 and Section 4.2.

## 4.1 Hardware-based UPFSM

A hardware-based design can be inserted in the place of the original FSM. In the case of TD, this will involve inserting a system to replace the original hardwired USB-FSM with a UPFSM. To be programmable, the UPFSM must most likely have a bus interface which is used for programming. The idea is illustrated in Figure 4.2.

Figure 4.2: TD with the hardware-based UPFSM.

The inputs and outputs from the original FSM are connected to the hardware system. It would, therefore, be useful for the system to be parameterized in such a way that it can be used to replace different sizes of FSMs. Section 4.1.1 describes how the hardware-based system was investigated and developed, and Section 4.1.2 describes the system that was implemented based on the findings in the investigation.

#### 4.1.1 Development

For learning and realizing what goes into an FSM in general, Python was used to model the USB-FSM. The goal for this modeling was to determine what functionality should be made programmable and to aid in making the UPFSM in hardware. This includes how to read the inputs and write to the outputs, as well as how to implement the next-state and output functions. However, it proved to be challenging to use Python for this task. One problem is that Python does not contain switch-statements, which are useful for describing the FSM. Instead, a bundle of "if-else" statements had to be used, and this made the code more confusing and did not help much in terms of making the USB-FSM more understandable. A lower level language such as C would probably have been a better choice since switch-statements can be used and the language provides more control to what data types are used.

As the Python modeling was not as fruitful as one could have hoped, prototyping in SystemVerilog was done instead. A common approach, as mentioned in Section 2.2.3, was used in the beginning. This approach utilizes an enumerated variable for the different states and a switch-case statement with some if-else statements to compute the next state and outputs. Firstly, a simple FSM was made, similar to the example FSM in Section 2.2.3. This was done in order to get a better understanding of how this way to write an FSM worked in SystemVerilog and how it can be made programmable. More research was, however, needed to find ways to make a programmable system. Two main possibilities were discovered; a custom instruction set processor or a microprogrammed control system.

A processor is programmable by nature, as described in Section 2.3. As mentioned in Section 2.2.1, a microprocessor can be modeled as a Turing machine, which is a more powerful automaton than the FSM. Therefore, having a custom instruction set processor architecture was considered, as it would be programmable, and flexible. Instead of a general microprocessor, a processor reduced to the components and instruction set needed to run a programmable FSM could be used. Such a system had been implemented by Wangyang et al. [22] and Hatta et al. [23]. Their solutions are presented in Section 3.3. However, designing a custom instruction set architecture is complicated, and due to limited time for this thesis, it was decided to find other solutions to make a hardware-based UPFSM.

Microprogrammed control was the other possibility that was discovered. Since the USB-FSM is used to control another system, this inspired to research other ways to implement control circuits. In [4], it was discovered that hardwired FSMs can be used to control microprocessors. [4] also presented microprogrammed control as a an alternative way to control microprocessors. Microprogrammed control is presented in Section 2.4.

Microprogrammed control works on the principle of a memory with control words stored as microinstructions. This memory is typically a ROM. A sequencer finds the address of the next microinstruction based on information from the following microinstruction and some input signals to the control unit. Microprogrammed control is, in fact, an FSM, with each microinstruction containing the output values and the next state information. However, it was considered not to be particularly universal, as an interface with the sequencer is needed, and the next state is not only generated by the ROM but also linked to the program running in the processor itself. Also, the ROM is by definition, not writable, so it is not possible to reprogram or reconfigure the ROM. As mentioned in Section 2.4, RAM can also be used in writable microprogrammed control. Using this would make it more programmable and flexible. However, implementing a RAM with functionality for reading and writing seemed slow and unnecessarily complicated. Using registers instead would make likely make for a faster and simpler design.

Using registers to store functionality was further researched. The motivation was to use general ideas from microprogrammed control and simplify it. Therefore, the concept of a LUT was discovered. LUT is presented in Section 2.5. A LUT is a way to map an input to an output. This would be beneficial since it avoids the addressing and sequencing needed for a microprogrammed control solution with RAM. A LUT-based design would also be less complicated than a custom processor architecture. Therefore, it was decided to move on with designing a LUT-based UPFSM called the LFSM, as in "LUT-FSM".

#### 4.1.2 LFSM design

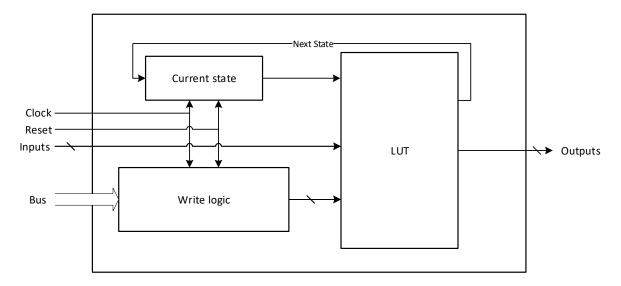

As mentioned, the LFSM is a variation of writable microprogrammed control. Figure 4.3 show an overview of the LFSM. As the figure depicts, it consists of three main parts; a LUT, write logic, and a state register. Each part and how the LFSM is programmed is described in the following paragraphs.

Figure 4.3: Overview of the LFSM and its three main parts.

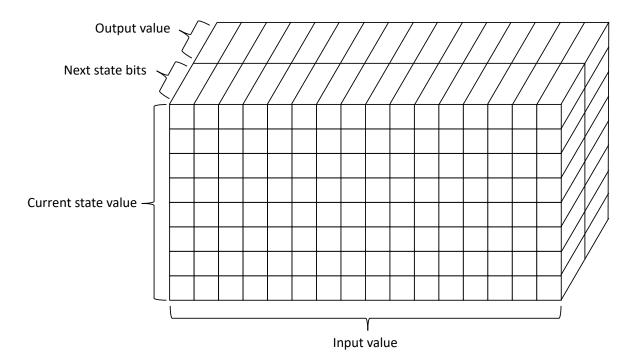

**LUT** From Section 2.2, it is clear that an FSM has a transition function which returns the next state based on the current state and the input. In addition, the output is returned by an output function, which, depending on if it is a Moore or Mealy machine, is based on the current state and the inputs. A state transition table can describe this dependency. In the LFSM, the state transition table is implemented in a three-dimensional LUT. The LUT thus replace the state transition and output functions.

Figure 4.4 illustrates the layout of the LUT. At each position in the LUT, there is a word containing the next state bits and the output value. Indexing the LUT with the combination of the value of the current state bits and the value of the input signals, the position returns the corresponding output value and the next state. The LFSM with a LUT resembles microprogrammed control, except instead of using an address generator, the LUT uses current state and the inputs directly. The LUT size is decided by the number of input signals, output signals, and states needed for the desired FSM.

Figure 4.4: The layout of the LUT. The size in this figure correspond to the USB-FSM.

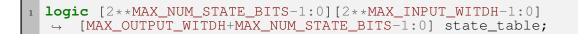

Listing 2: Declaration of LUT.

Listing 2 show how the LUT named "state\_table" is declared in SystemVerilog. As one can see, there are three parameters to specify the size of the LUT. Equation (5) shows how the size of the LUT is determined by the number of inputs signals, output signals, and state bits.

$$Size = 2^{(I+Q)} * (Z+Q)$$

(5)

where:

- Q = MAX\_NUM\_STATE\_BITS which specifies the number of bits needed to represent the state set.

- $I = MAX_INPUT_WITDH$  which specifies the number of input bits.

- $Z = MAX_OUTPUT_WIDTH$  which specifies the number of output bits.

The LUT must be sized to this in order to accommodate all possible combinations of input signal values and state bit values, and to store a word with next state bits and output signals for each position. Figure 4.4 corresponds to the USB-FSM, which has Q=3, I=4, and Z=3. This gives 16 possible input signal values and 8 possible state

values. Each combination of an input value and a state value holds a 6 bit word (Q+Z). The USB-FSM would, therefore, need a LUT size of 768 bits.

Since the LUT is generated in hardware, it must be sized large enough to accommodate all possible FSM sizes that might be needed for the UPFSM in the future. It is not possible to resize the LUT after the design is manufactured. However, it is possible to use fewer states, input signals, and output signals than specified by the parameters. This would, of course, lead to an area penalty, which can be very high for large FSMs with many states, inputs, and outputs. Besides, the LUT size is determined by the number of bits needed to represent the state set. For the USB-FSM, which has 5 states, Q=3 bits is must still be used to represent the state set in the LUT. 3 bits is enough for 8 states, and this means the LUT is excessively large.

Write logic The LUT is writeable and can be programmed. The programming is done by connecting a bus interface to the LFSM and use logic to write to the LUT. Using this bus interface, an FSM configuration can be loaded into the LUT, which obviously will change the contents in the LUT. The new content in the LUT results in a different state transition and output functions, and the FSM will react to the inputs differently. The bus is connected to the main bus structure of the chip, and the on-chip microprocessor can load the FSM configuration from non-volatile memory by software at startup.

The bus interface has both read and write capabilities, but only the write functionality is used in the LFSM. The bus has an addressing scheme which is used to write and read from other IPs. The bus data width is 32 bits, which for this design of the LFSM means each word in the LUT only can be 32 bits wide. Due to this, the maximum number of output bits and state bits combined cannot exceed 32 bits. However, the word length issue can most likely be solved by, for example, using a two-stage write process which loads each position with two bus transfers. This was not implemented for in the LFSM due to limited time and since it is not required for the USB-FSM.

Listing 3 show the SystemVerilog code for how the LFSM configures the LUT from the bus. Since it must be synchronized with the bus, the write logic is in a sequential *always\_ff* block. The writing must be done by a bus master, such as a microprocessor, which uses a software program to write the LUT at chip startup or reset. Due to limited time in the work for this thesis, a bus driver in a testbench has been used for writing to the LFSM. Writing starts by writing 32'hFFFFFFF to address 32'hFFC in the LFSM. This toggles a register which tells the LFSM that it is in programming mode. While it is in programming mode, it will not function as an FSM, and all the outputs will be zero. Then, at each clock tick, a new word is written to the LUT from the bus, and the counters increment and writing to the next position is performed. This iteration continues until the entire FSM configuration has been written. After the FSM configuration writing finishes,

```

Used for iterating through LUT

logic [MAX_NUM_STATES-1:0] i;

2

logic [MAX_NUM_INPUTS-1:0]

3

j;

4

' Write LUT

5

always_ff @(posedge clk or posedge arst) begin

6

LUT set to zero on reset, and index variables are set to

\overline{7}

zero

if

(arst) begin

8

state_table <= '0;

i <= '0;</pre>

9

i <= '0;

j <= '0;

10

11

end

12

else begin

13

case(busAddr)

32'hFFC : begin //Set FSM in programming mode by sending

14

15

FFFFFFFF to address FFC

if (busWe && busDo == 32'hFFFFFFF) begin

16

if (programming_mode) programming_mode <= '0; //Toggle</pre>

17

programming mode

else programming_mode <= '1;</pre>

18

end

19

end

20

//For every entry in state table to be indexable using

21

inputs and state bits, the below musbe done:

LFSM_BASE : begin

22

if (busWe) begin

23

if(programming_mode) state_table[i][j] <=</pre>

24

busDo[MAX NUM OUTPUTS + MAX NUM STATES - 1 : 0];

Incrementing indexes

25

j <= j + 1;

if(j >= 2**MAX_NUM_INPUTS - 1) begin

26

27

i <= i + 1;

28

i <= '0;

if(i >= 2**MAX_NUM_STATES - 1) begin

i <= '0;</pre>

29

30

31

end

32

end

33

end

34

35

end

36

endcase

end

37

end

38

```

Listing 3: Writing process.

32'hFFFFFFF must be written to address 32'hFFC to toggle the programming mode off and return the LFSM into FSM operating mode.

A reset signal will zero all the bits in the LUT, and also set the counters **i** and **j** to zero. Therefore, the LUT must be rewritten when a reset has occurred.

Having the correct word at the corresponding position in the LUT is crucial for correct behavior of the FSM. This poses a challenge in the writing process. The writing must start at position (current state value 0, input value 0) and iterate using the counters **i** and **j** in Listing 3. Each word written is a line from the state transition table. Thus, care must be taken so that the state transition table is correct and will correspond to the correct position in the LUT. The transition table must have a word for every position, even if the position (a combination of state and inputs) is an unreachable state or not used at all. Having to write all positions can be seen in relation to the LUT size issue. Having more clever indexing and writing by the bus may open possibilities to reduce the LUT size, which should be considered for future work.

**State register and reading the LUT** The state register in the LFSM is not different from what a was presented in Section 2.2.3. It holds the current state. The state register is declared as an *always\_ff* block as shown in Listing 4. At each clock cycle, the state register will either remain in the current state or get a new state from the LUT. If the reset signal goes high, the state register will be set to zero.

```

always_ff @(posedge clk or posedge arst) begin

Default state is 0 on reset (arst) begin

2

//

if

3

state <= '0;</pre>

4

5

end

6

else begin

\overline{7}

<= nextState;

state

8

end

9

end

```

**Listing 4:** State register in LFSM.

Finding the correct output values and the next state is relatively straight forward once the writing of the configuration is finished. Listing 5 show how the LFSM finds the next state and the outputs. Since it is a combinatorial process, it is declared as an *always\_comb*. As mentioned in Section 2.2.2, a Moore machine only need the current state to determine the outputs, while a Mealy machine needs both the state and the inputs. Thus, a parameter can be set when instantiating the LFSM whether or not it should be a Mealy or Moore machine.

As seen in Listing 5, the programming mode register is checked, which means the LFSM only sets output and next state when it is not in programming mode. In a Moore machine, input value zero is used constantly for finding the output. The use of input value zero is arbitrary. For a Mealy machine, the actual input value instead of zero. Using a Moore machine should make possibilities for reducing the area of the LUT after synthesis, while a Mealy machine opens possibilities for more advanced state machines.

How to program the LFSM As mentioned, making sure the right word is at the right position is crucial for correct behavior by the LFSM. The LFSM use a state transition table in the LUT. State transition tables is presented Section 2.2. For the current LFSM design, the user of the LFSM must manually create the state transition table for the FSM which is to be used. The state transition table must be binary coded. The state transition table is, as mentioned, written to the LUT using a bus interface.

```

if (MEALY == 1) begin : la_Mealy

always_comb begin

2

if (!programming_mode) begin //Only provide output and

3

nextState while not in programming mode

outputs = state_table [state] [inputs] [MAX_NUM_OUTPUTS +

4

MAX_NUM_STATES - 1 : MAX_NUM_STATES]; //Only the

outputs from LUT word

nextState = state_table [state] [inputs] [MAX_NUM_STATES

\mathbf{5}

: 0]; //Only the nextState bits

end

6

else begin

\overline{7}

'0; //all outputs are zero when there is no

outputs =

8

valid program in the FSM

State = '0; //nextState is default zero when no valid

nextState =

9

program

\hookrightarrow

end

10

11

end

end

12

else begin : la_Moore

13

always comb begin

14

if(!programming_mode) begin

15

outputs = state_table [state] [0] [MAX_NUM_OUTPUTS

16

MAX_NUM_STATES - 1 : MAX_NUM_STATES]; //Outputs only

\rightarrow

determined by state. The use of input 0 is arbitrary.

nextState = state_table [state] [inputs] [MAX_NUM_STATES

17

1 : 0];

\rightarrow

end

18

else begin

19

outputs = '0;

nextState = '0;

20

21

22

end

end

23

end

24

```

Listing 5: Finding the next state and the outputs.

Creating the state transition table for the format for writing over the bus has so far been done by using a spreadsheet program like Microsoft Excel. The spreadsheet of the state transition table for the USB-FSM can be seen in Appendix B. In Microsoft Excel, it is possible to copy columns. So, the columns for the next state and the outputs are copied into a .txt-file and all spaces are removed. A simple Python script is used to parse this .txt-file into the format needed for the software or bus driver to write to the LUT. The script is added in Appendix C.

This way of programming the LFSM is not particularly user-friendly and mistakes can easily happen. Especially, creating the binary encoded state transition table is prone to mistakes. It is also difficult to find mistakes and debug the program. The amount of work to create the tables is also very dependent on the number of inputs, outputs, and states. During the work of this thesis, more emphasis was put into creating a functional LFSM rather than the programming interface, and it is left for future work to create a more user-friendly interface. Some ideas for refinement are for example to create a C-program for the FSM and then have a script parse the C-file and automatically create the format required for the LUT. An even more advanced solution which might be more user-friendly would be a graphical user interface where the FSM can be drawn as a state diagram and a program can interpret the drawing and generate the format for the LUT.

#### 4.2 Software based UPFSM

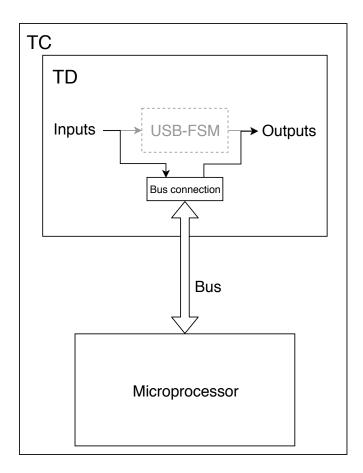

Using a microprocessor as an FSM is not a new idea. As presented in Section 3.3, it was considered already in 1987 [6], and ARM has a white paper [5] on the subject. The main inspiration for the software-based design is from the ARM white paper. Besides, implementing an FSM in software for running on a microprocessor opens possibilities for comparison and evaluation to the LFSM. The software-based UPFSM is for simplicity's sake called the SWFSM. Figure 4.5 show a simplified overview of the SWFSM design.

Figure 4.5: Simplified overview of how the SWFSM works with TD and TC. The USB-FSM is gray to illustrate how the signals are re-routed.

The SWFSM should have a microprocessor connected to the inputs and outputs from the original FSM. Since the microprocessor has multiple connections, a bus infrastructure is needed to communicate to all the various units connected to the microprocessor. Section 4.2.1 describes how the SWFSM was investigated an developed, and Section 4.2.2 describes the design that was implemented.

#### 4.2.1 Development

The ARM white paper [5] was used as a starting point. As the existing TC was used in this thesis, a natural starting point. TC has a bus structure and a microprocessor, as well as frameworks for testing and developing software. From the ARM white paper, it was clear that some registers for reading and writing the FSM inputs and outputs were needed. These registers had to be connected to the main bus structure of TC so that the microprocessor could access them from software. It was decided to use one register for the inputs to the FSM and one register for the outputs.

As TC is an existing SoC from Nordic Semiconductor, and the SWFSM is in the crosssection of hardware and software design, cooperation with engineers from Nordic Semiconductor was necessary for the implementation. The development started at two ends, with one end being the software side, and the other end the hardware side. Engineers with knowledge of the software and hardware sides assisted in their respective fields. Eventually, the ends were tied together, and the design of the actual SWFSM could be carried out.

#### 4.2.2 Design

Figure 4.6 shows a simplified overview of the SWFSM and how it is placed in TD. It can be divided into two major parts, the hardware side with signals and registers, and the software side which runs in the microprocessor. Each side will be presented in the following paragraphs.

Figure 4.6: Overview of the SWFSM and its connections.

Hardware side The SWFSM is using registers and signals which are added to the hardware of TC. The existing USB-FSM in TD is removed, but the signals going in and out of the USB-FSM are routed to registers accessible to the microprocessor. TD is instantiated inside several layers of other IPs and subsystems. Thus, the input and

output signals had to be routed through all the layers to the module which is connected to the bus infrastructure.

As shown in Figure 4.6, TD is a part of a larger IP named PowerSystem. PowerSystem contains submodules PowerSubSystem and RegulatorSystem, which contains TD. However, PowerSystem is connected to the bus infrastructure via the submodule PowerSystemConnect. This means that the signals from TD must be routed to the top module, PowerSystem, and then into the PowerSystemConnect. PowerSystemConnect contains all the registers for all the modules in PowerSystem. The PowerSystem has a base address in the bus structure, and offsets are used to access the internal modules. The registers used for the USB-FSM did not exist in TC from before, so they had to be added with help from hardware-engineers from Nordic Semiconductor. The register for the input signals is made as a read-only register since these signals originate from logic in TD and the microprocessor does not need to write to them. The register for the output signals is made as a write-only register, as these signals used to be the outputs of the original USB-FSM. An existing testbench for TC was used to verify that the signals were added correctly.

**Software side** With help from software engineers at Nordic Semiconductor, the registers implemented in hardware is added to the firmware for TC. The framework is built up around software header-files containing structs. These structs are used to break down the address which is used on the bus. As mentioned, each module has a base address and an offset. The base address is used to find the correct struct, and the offset is specified in the struct.