Karine Avagian

# An FPGA-oriented Hardware Implementation of Richardson-Lucy Deconvolution Algorithm for Hyperspectral Images

Masteroppgave i Elektronisk Systemdesign og Innovasjon Veileder: Kjetil Svarstad, Milica Orlandic Juni 2019

## Karine Avagian

# An FPGA-oriented Hardware Implementation of Richardson-Lucy Deconvolution Algorithm for Hyperspectral Images

Masteroppgave i Elektronisk Systemdesign og Innovasjon Veileder: Kjetil Svarstad, Milica Orlandic Juni 2019

Norges teknisk-naturvitenskapelige universitet Fakultet for informasjonsteknologi og elektroteknikk Institutt for elektroniske systemer

## Abstract

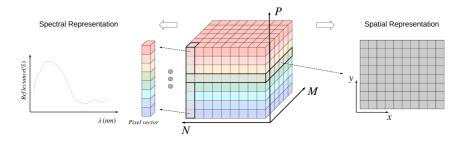

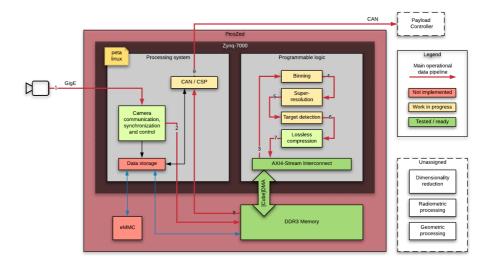

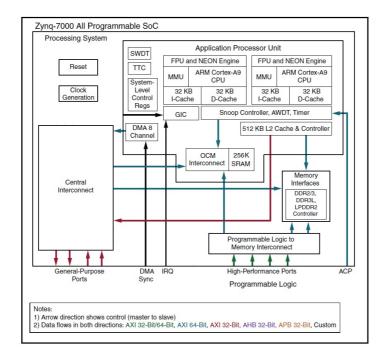

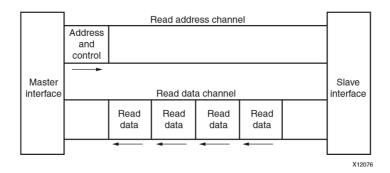

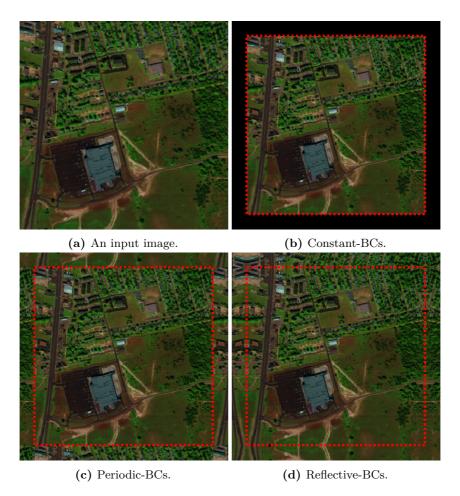

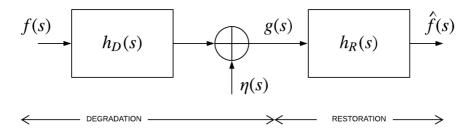

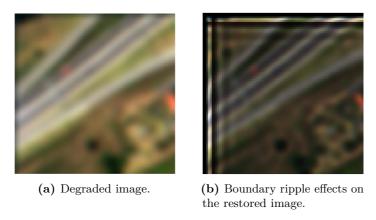

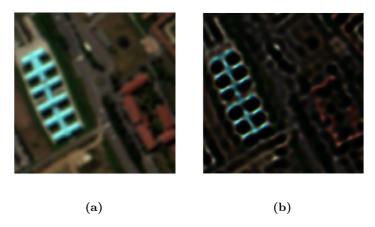

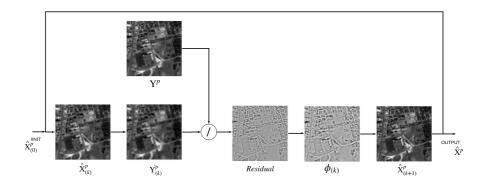

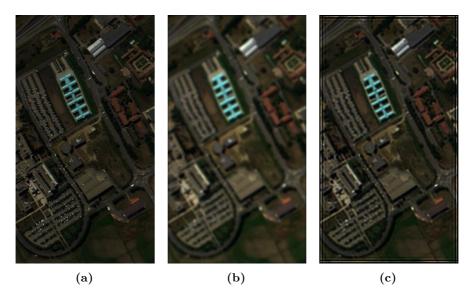

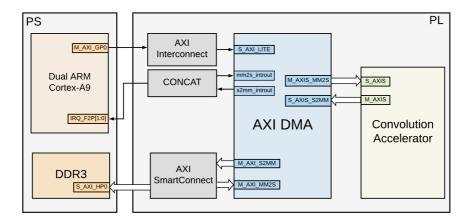

This work presents a method to reduce the spatial degradation in hyperspectral images caused during the image acquisition process. The degradation is modeled by a convolution with a *Point Spread Function* (PSF), which in this work, is assumed to be known. The three-dimensional hyperspectral images are modeled as a composition of two-dimensional independent images. Degradation is reduced by applying an accelerated Richardson-Lucy (RL) deconvolution algorithm on each individual image. Boundary conditions are introduced in order to keep a constant image size without distorting the estimated image boundaries. An algorithm is implemented in C in both the floating-point and fixed-point representations. The quantization error between the two representations is negligible. The RLdeconvolution algorithm is fully ported on an FPGA-based platform (i.e., Xilinx Zynq-7020) using the hardware description language VHDL. Two architectures are designed and called Architecture-1 and Architecture-2. The former is optimized with respect to the communication time with an external memory and the latter is optimized for limited storage. Both architectures are parameterized with respect to the image size and run-time configurable with respect to the number of iterations. In addition, Architecture-2 is run-time configurable with respect to the kernel size with a maximum kernel size equal to  $9 \times 9$ . The execution time of implemented architectures is compared to a software only implementation of the algorithm running on the same Xilinx Zynq platform. A speed-up by a factor of 31 is achieved for Architecture-1 and a speed-up by a factor of 61 is achieved for Architecture-2. The execution time is also compared to a HW/SW implementation of the RL-deconvolution and a speed-up by a factor of 13 is achieved for Architecture-1 and a speed-up by a factor of 26 is achieved for Architecture-2. Compared to a state-of-the-art solution, a speed-up by a factor of 1.8 is achieved for the Architecture-2 when running a standard RL-deconvolution.

## SAMMENDRAG

Denne masteroppgaven presenterer en metode for å forbedre romlig oppløsning i hyperspektrale bilder. Uskarpheter i bilder modelleres ved hjelp av foldning (convolution) med en Point Spread Function (PSF), som antas å være kjent. Et tre-dimensjonalt hyperspektralbilde modelleres som en komposisjon av flere to-dimensjonale bilder. Uklarhet i bildene reduseres ved hjelp av en akselererert Richardon-Lucy (RL) dekonvolusjon. Original bildestørrelse bevares ved hjelp av "boundary conditions". Algoritmen er implementert i C, med både "floating-point" og "fixed-point" representasjoner. Kvantiseringsfeilen mellom representasjonene er neglisjerbar. Algoritmen er derreter beskrevet i VHDL og kjørt på an FPGAbasert plattform (Xilinx Zynq-7020). To arkitekturer har blitt designet, den første, Architecture-1, optimalisert med hensyn til kommunikasjonstid med ekternt minne, og den andre, Architecture-2, optimalisert med hensyn til intern FPGA lagringsplass. Begge arkitekturene er parametrisert med hensyn til bildestørrelse og konfigurerbar i kjøretid med hensyn til antall iterasjoner i algoritmen. I tillegg er Architecture-2 konfigurerbar ved kjøretid med hensyn til kernel størrelse, der maksimal kernel størrelse er  $9 \times 9$ . Kjøretid til Architecture-2 er to ganger raskere en for Architecture-1. Kjøretid for de implementerte arkitekturene er sammenlignet med en software-basert implementasjon som kjøres på samme platform, der akselerasjonen er lik 61 for Architecture-2. Kjøretid er også sammenlignet med en HW/SW implementasjon av RL-dekonvolusjon or en akselerasjon lik 26 er oppnådd for Architecture-2. Sammelignet med en state-ofthe-art implementasjon, akselerasjon lik 1.8 for Architecture-2.

# ACKNOWLEDGMENTS

I would love to thank my co-supervisor Milica Orlandić for her support throughout the entire year and that extra time spent re-reading and editing my first conference paper. This was a small accomplishment I am happy to have. Furthermore, I would like to thank all the guys and girls at the HYPSO project, and a special thanks to Dordje Bošković for sharing the ideas, driving carefully and being as stressed as I am. Lastly, I would like to thank my dearest Steinar, for all his love and care, and my family, for their encouragement and patience.

Now, I can finally pass the torch to my dearest Gabi, enjoy the coming years at NTNU!

# Contents

| Abstract                                                                                                             |                |

|----------------------------------------------------------------------------------------------------------------------|----------------|

| Sammendrag                                                                                                           | ii             |

| Acknowledgments                                                                                                      | •              |

| Table of Contents                                                                                                    | iz             |

| List of Tables                                                                                                       | xi             |

| List of Figures                                                                                                      | xvii           |

| Abbreviations                                                                                                        | xix            |

| Introduction         1.1       Remote Sensing                                                                        |                |

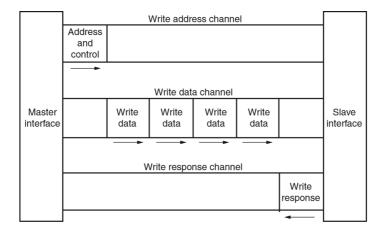

| 1.2.2 On-Board Computer          1.2.3 AXI4 interfaces          1.3 Main contributions          1.4 Thesis structure |                |

| 2 Background         2.1 Image Degradation                                                                           | 15 14 18 18 18 |

|   | 2.3         | Image Quality Assessment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21              |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   | 2.4         | State-of-The-Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23              |

|   |             | 2.4.1 3-D Richarsdon-Lucy Deconvolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23              |

|   |             | 2.4.2 Specialization project overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24              |

|   |             | 2.4.3 State-of-The-Art hardware implementations of RL-Deconvolu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-              |

|   |             | tion algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27              |

| _ |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ••              |

| 3 | Anal<br>3.1 | y and a second s | <b>29</b><br>29 |

|   | 3.2         | Restoration and Degradation Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{23}{31}$ |

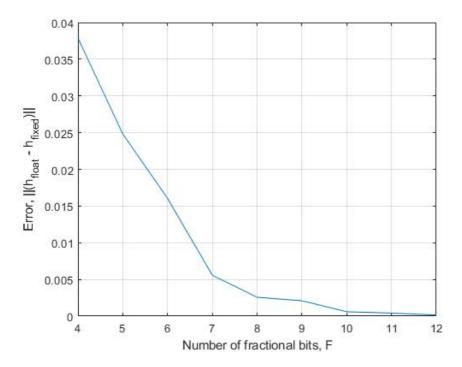

|   | 3.4         | 3.2.1 Kernel Size and Quantization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31              |

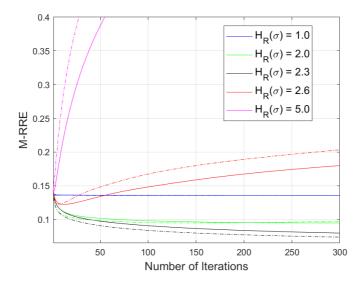

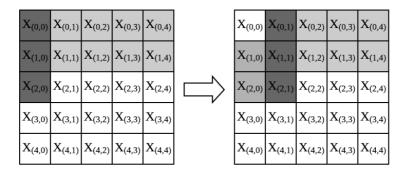

|   | 3.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33              |

|   | 0.0         | V 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34              |

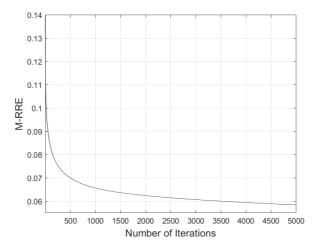

|   |             | v e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39              |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>43        |

|   | 2.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

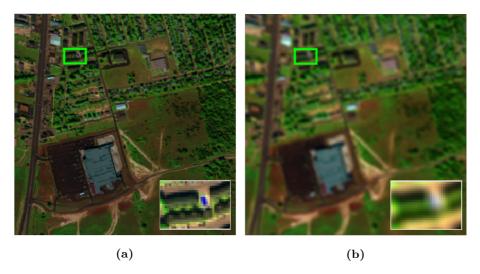

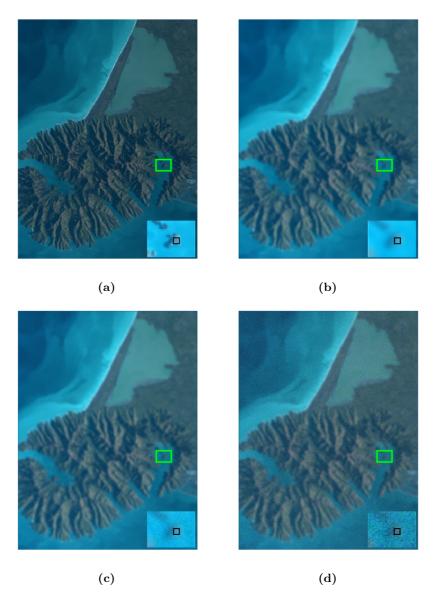

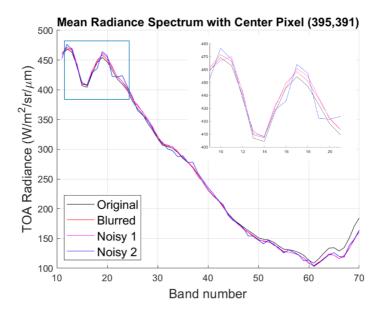

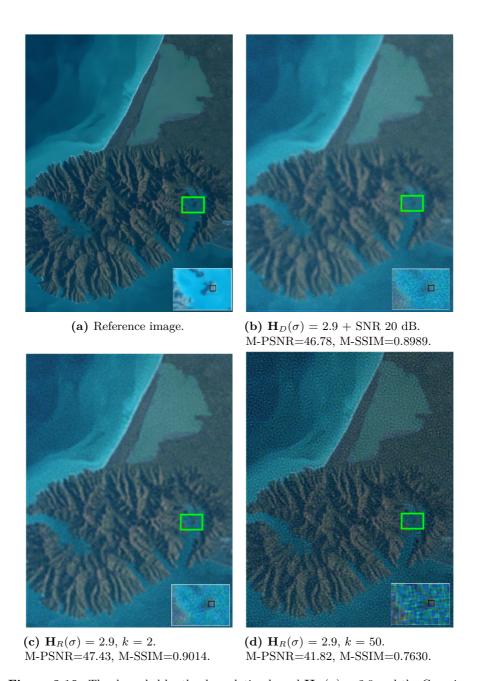

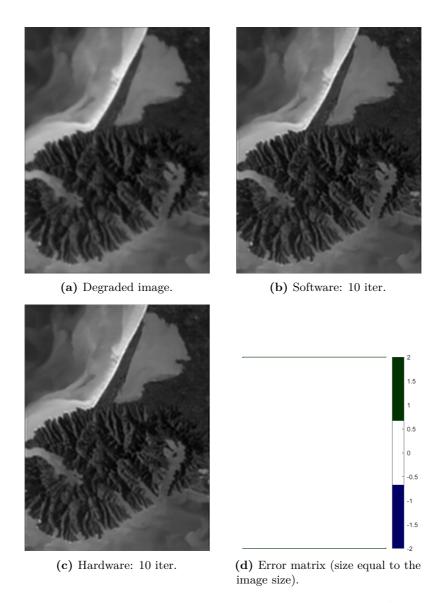

|   | 3.4         | Hyperspectral Data - Coastal Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45              |

| 4 | Hard        | lware Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>53</b>       |

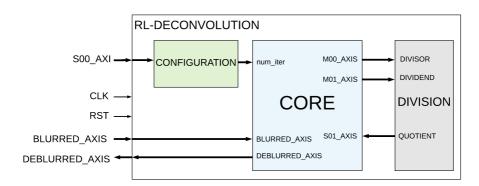

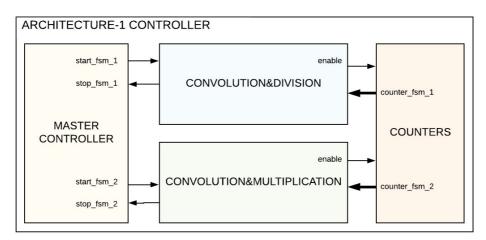

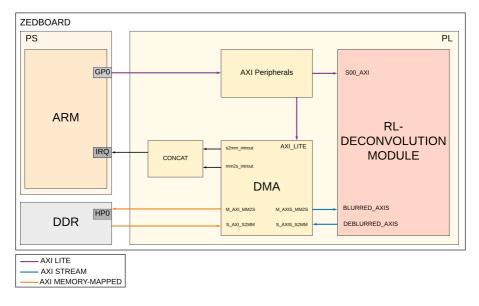

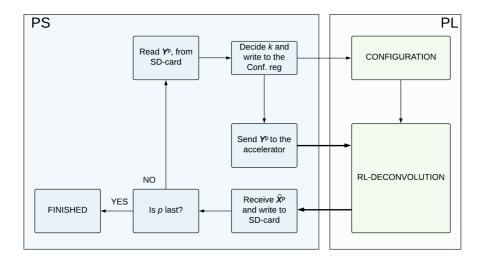

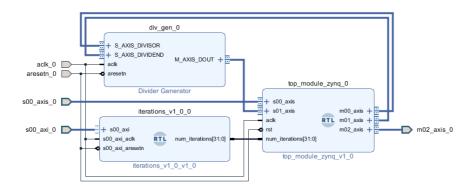

|   | 4.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53              |

|   | 4.2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55              |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56              |

|   |             | 4.2.2 Data Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57              |

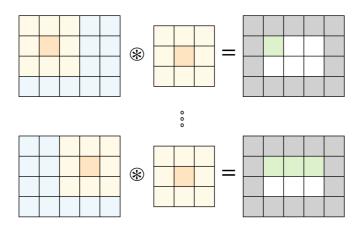

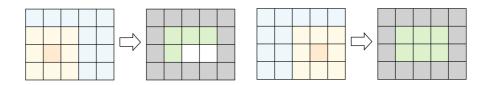

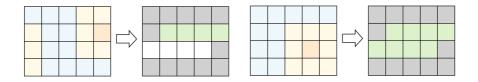

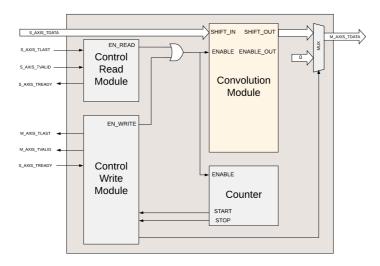

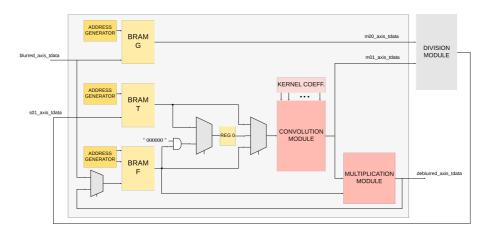

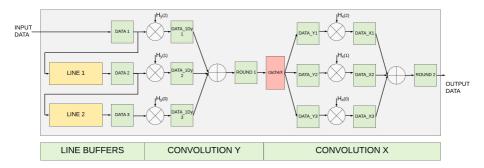

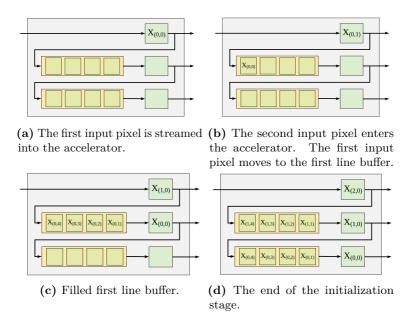

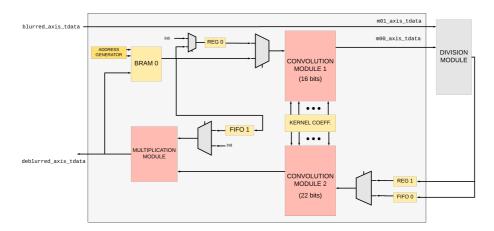

|   |             | 4.2.3 Convolution Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58              |

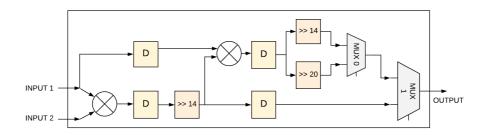

|   |             | 4.2.4 Multiplication Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60              |

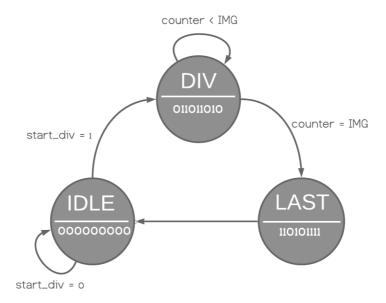

|   |             | 4.2.5 Division Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61              |

|   |             | 4.2.6 Configuration Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62              |

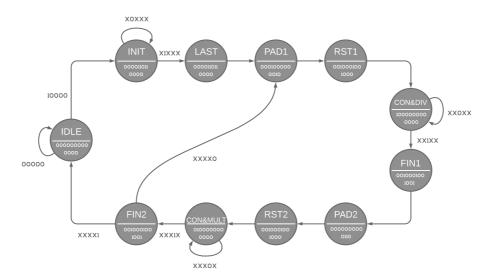

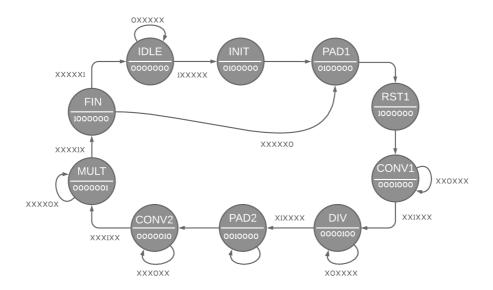

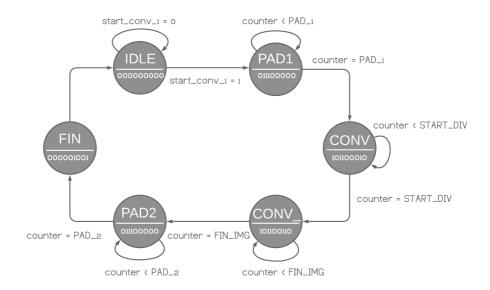

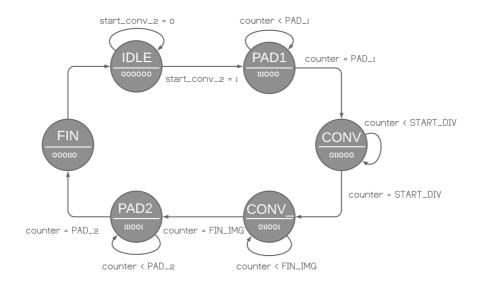

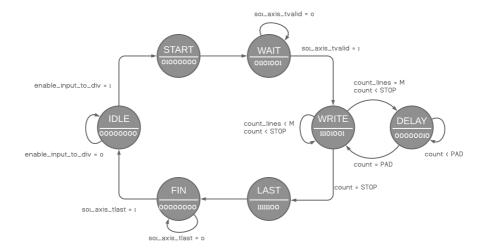

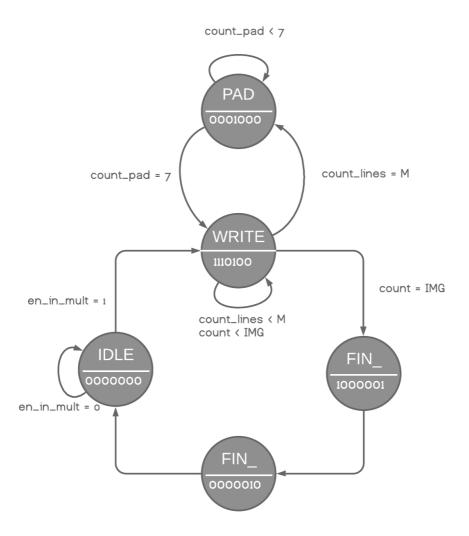

|   |             | 4.2.7 Control Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63              |

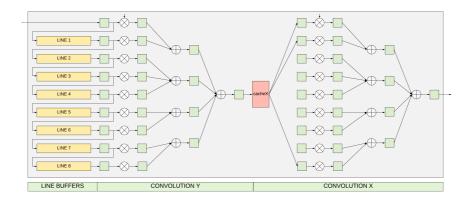

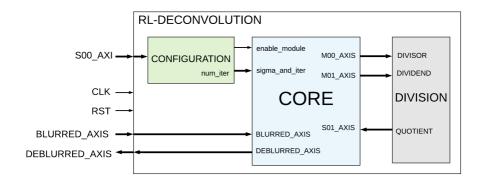

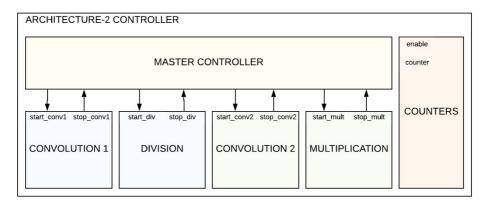

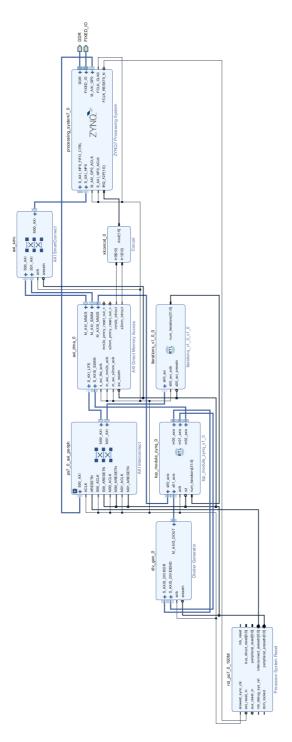

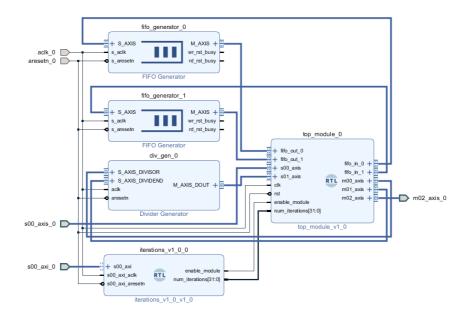

|   | 4.3         | Architecture-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66              |

|   |             | 4.3.1 Core IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66              |

|   |             | O Company of the comp | 67              |

|   |             | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67              |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67              |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68              |

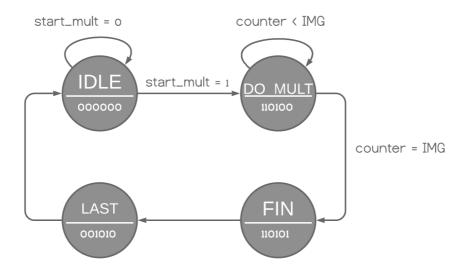

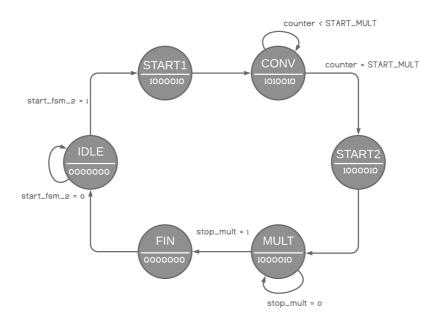

|   |             | 4.3.6 Control Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69              |

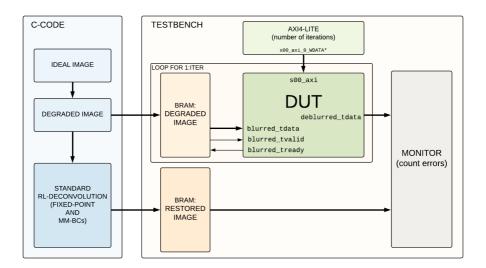

| 5 | Vorif       | fication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77              |

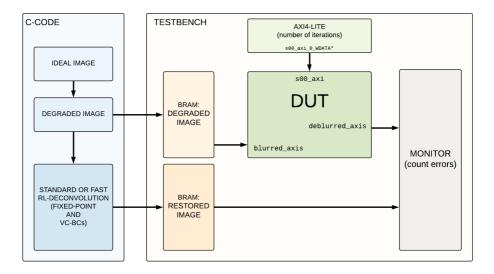

| J |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78              |