ISBN 978-82-326- 4072-0 (printed ver.) ISBN 978-82-326- 4073-7 (electronic ver.) ISSN 1503-8181

O NTNU

SiC MOSFETs and Diodes: Characterization, Applications and Low-Inductive Converter

Subhadra Tiwari

## SiC MOSFETs and Diodes: Characterization, Applications and Low-Inductive Converter Design Considerations

Thesis for the Degree of Philosophiae Doctor

Trondheim, April 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

© Subhadra Tiwari

ISBN 978-82-326- 4072-0 (printed ver.) ISBN 978-82-326- 4073-7 (electronic ver.) ISSN 1503-8181

Doctoral theses at NTNU, 2019:238

Printed by NTNU Grafisk senter

To my parents

### Preface

This thesis is submitted to the Norwegian University of Science and Technology (NTNU) in partial fulfillment of the requirements for the degree of philosophiae doctor (PhD).

The research is carried out at the Department of Electric Power Engineering, Faculty of Information Technology and Electrical Engineering, NTNU, Norway. The PhD work is sponsored by The Research Council of Norway, and six industry partners: EFD Induction, Siemens, Eltek, Norwegian Electric Systems, and Vacon.

Trondheim, April 2019 Subhadra Tiwari

### Acknowledgments

I would like to express my sincere gratitude to my main supervisor Prof. Ole-Morten Midtgård for providing me with this great opportunity, and for his supervision, continuous encouragement and support. My sincere thanks to my co-supervisor Prof. em. Tore Marvin Undeland for his supervision, invaluable insight, helpful feedback and intriguing questions throughout this research work.

I would also like to thank EFD Induction AS, which is one of the industry partners financing this PhD project, for providing me the opportunity to work in their laboratory. Special thanks goes to John Kåre Langelid, from EFD Induction AS, for sharing his experience, knowledge and providing valuable comments, and suggestions throughout this PhD work. I also wish to acknowledge Prof. Roy Nilsen, Dr. Supratim Basu, Dr. Richard Lund, and Dr. Ibrahim Abed Abuishmais for their valuable inputs and suggestions. I would also like to thank Terje Rogne from The Switch Marine Drive AS, and Kjell Ljøkelsøy from SINTEF Energy Research for providing technical feedbacks for some of my papers. My thanks to Ali Rabiei from Chalmers University of Technology for technical discussions during his visit to NTNU.

I would like to thank Prof. Rik W. De Doncker for providing me the opportunity to work at E. ON Energy Research Center for six months as a guest PhD researcher at RWTH Aachen University. Moreover, I had the opportunity to visit CPES lab at Virginia Polytechnic Institute for two weeks in 2016. Both of these international exposures enhanced my knowledge of the laboratory and simulation tools that were central for my PhD project.

The Department of Electric Power Engineering at NTNU has provided good laboratory facilities and great administrative support. My thanks to the members of staff at the department for help regarding various practical matters. Additionally, the social environment among the fellow PhD students has been of great value. I would also like to thank my office mates, Ole Christian Spro and Andreas Giannakis for their friendly chats.

Finally, I would like to thank my family. They have always supported and believed in me, and words cannot express how truly appreciative I am for all of their love and encouragement. Last but not least, my husband Raghbendra deserves my deepest gratitude for his support and love during my years as a PhD student. Thanks also for your help in reading the draft of my dissertation. Moreover, it is impossible not to mention my beloved son, Ayan. He is the true source of motivation and energy for me.

> Trondheim, April 2019 Subhadra Tiwari

### Abstract

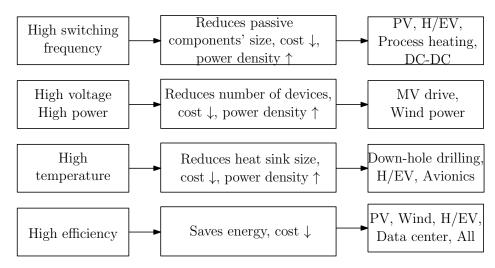

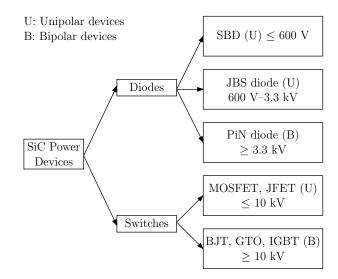

The future power electronic system trends are: higher efficiency, higher power density, higher operating temperature and lower operation cost of power electronic converters. The emerging wide-bandgap (WBG) semiconductor material, especially silicon carbide (SiC), exhibits outstanding inherent properties that promise the potential to meet the subsequent growing demands. SiC enables the development of power devices capable of switching efficiently even at higher voltages and temperatures compared to the matured and wellestablished Si technology of today. Nonetheless, parasitic inductance and capacitance in the switching circuit are limitations for fully unleashing the fast-switching potential of these devices. The objective of this research is to evaluate what the state-of-the-art SiC devices, particularly SiC MOSFETs, offer at present and what can be done for better realizing their high switching-speed capability.

First, to assess the fast dynamic characteristics of SiC devices with a high degree of accuracy, measurement probes and oscilloscope with adequate bandwidth along with low-inductive connections are adopted. Switching characterization was conducted via double-pulse test in hard-switched as well as in resonant topology. Based on the measurement results, it is recommended to use a realistic topology for the precise assessment of switching losses in SiC devices.

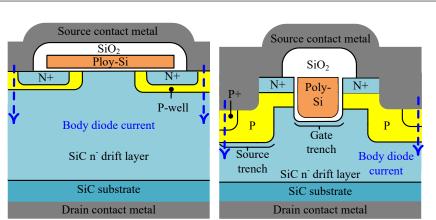

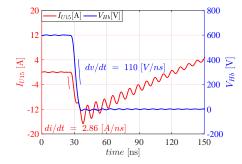

Second, the state-of-the-art SiC MOSFET modules are examined to determine how fast they switch compared to the class-leading IGBT modules, given that they are packaged in the standard plastic housing. Measurement results revealed that the maximum dv/dt and di/dt rates that SiC MOSFET achieves are: 20 V/ns and 11 A/ns at 600 V bus voltage and 120 A load current. Si IGBT, on the other hand, achieved 17 V/ns and 12 A/ns when switched at similar conditions. According to this result, it can be inferred that dv/dt and di/dt rates that SiC MOSFET reaches are not as revolutionary as its intrinsic properties can potentially offer. In fact, this outcome can be attributed to the higher internal gate resistance that manufacturers use for avoiding oscillation during turn-off and the higher package inductance. In order to know what else can be achieved using SiC MOSFET, the body-diodes of the state-of-the-art SiC MOSFETs (both planar and trench technologies) were inspected. A particular focus was put on di/dt during the second-half of the recovery, keeping di/dt on the first-half of the recovery constant for all the devices being tested. Experimental outcomes revealed that the body-diodes in new generation SiC MOSFETs are as good as SiC junction barrier Schottky (JBS) diodes from the switching point of view. Nonetheless, the forward voltage drop is higher approximately by a factor of 3 compared to unipolar SiC Schottky diodes. Based on this information and the research conducted by another team, which confirmed that the body-diodes in new SiC MOSFETs do not create reliability issues anymore like those seen in the initial generation SiC MOSFETs, it is concluded that the body-diodes in SiC MOSFETs work effectively as freewheeling diodes.

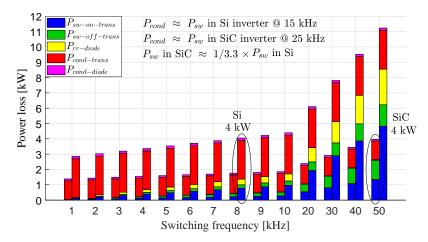

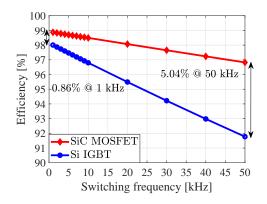

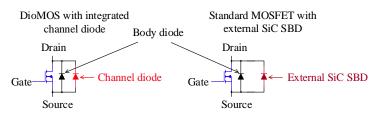

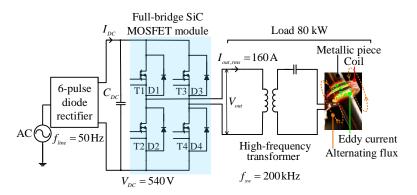

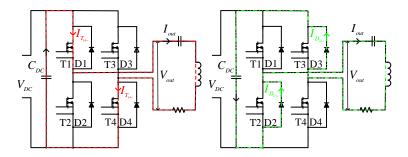

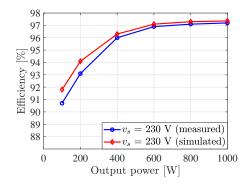

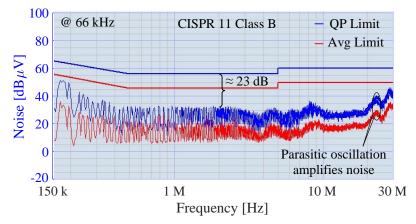

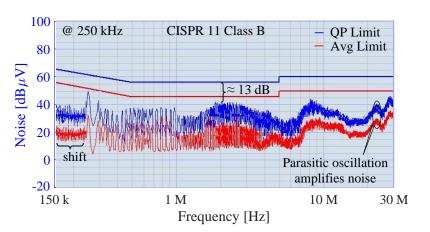

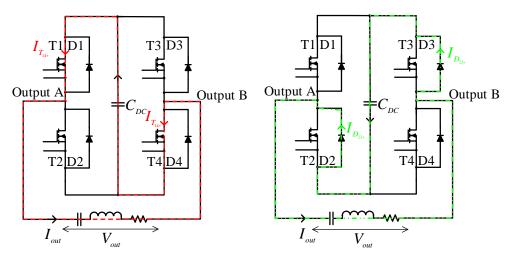

Third, SiC MOSFETs are evaluated in three different key applications. One of those applications is a 240 kW back-to-back connected three-phase, two-level voltage source converter for motor drive, which disclosed that, for the same converter power loss, the switching frequency in an all-SiC-based converter can be increased by six times compared to that of an all-Si-based converter. Another application is an 80 kW single-phase, fullbridge inverter for induction heating applications, which proved an efficiency of 99.3%when switched at 200 kHz. SiC DioMOS, where MOSFET and diode are fabricated in a single chip, was the device under test and the inverter loss was measured via calorimetric method in this case. Finally, a 1 kW power factor correction rectifier is evaluated employing SiC MOSFET and SiC JBS diode in boost stage. A peak efficiency of 97.2% was achieved when switched at 250 kHz satisfying the 80 PLUS regulation throughout the entire load range. Moreover, EMI measurements revealed that the rectifier satisfies CISPR 11 Class B limits. Furthermore, when the switching frequency was increased from 66 to 250 kHz, the size of boost inductor was reduced drastically, while the emissions were increased by roughly 10 dB throughout the entire conducted spectra for the identical size of EMI filter.

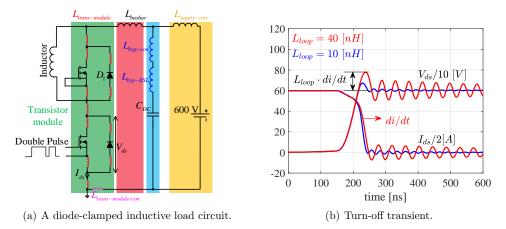

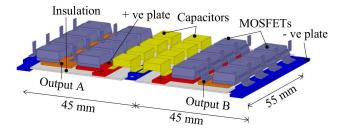

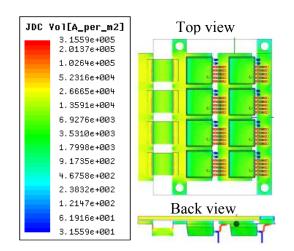

To further unlock the fast switching potential of SiC devices, low-inductive converter design guidelines are proposed, such as the selection of DC-clamping capacitors with low internal inductance and their appropriate orientation and stripline layouts whenever possible maintaining width to length ratio larger than unity. Two design examples for further achieving low switching loop inductance with SiC modules and discrete SiC devices are provided. For the SiC modules, multiple DC-source busbars for multiple screw hole modules are recommended. As internal inductance of the standard module is larger, an example of layout employing seven-pin discrete SiC MOSFETs and Ceralink capacitors is designed, the switching loop inductance of which is estimated to be 5 nH via 3D FEM simulations.

**Keywords:** Silicon Carbide (SiC), Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET), Junction Barrier Schottky (JBS) diodes, High-Efficiency Converters, Low inductance designs.

### Contents

| Pr | reface                                                    | e                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                                      | i                                                                                       |

|----|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------|

| A  | cknov                                                     | vledgn                                                                                                     | nents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                      | iii                                                                                     |

| A۱ | ostra                                                     | $\mathbf{ct}$                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                                      | $\mathbf{v}$                                                                            |

| Ta | ble c                                                     | of Cont                                                                                                    | tents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                                      | vii                                                                                     |

| Li | st of                                                     | Tables                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                      | xii                                                                                     |

| Li | st of                                                     | Figure                                                                                                     | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |                                      | xiii                                                                                    |

| Li | st of                                                     | $\mathbf{Symbol}$                                                                                          | bls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |                                      | xxv                                                                                     |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6            | Scope<br>Struct<br>Metho<br>Main s<br>Overvi<br>1.6.1                                                      | on         cound and motivation         of the work         ure of the thesis         ure of the thesis         dology         ceientific contributions         ew of publications         List of journal papers         List of conference papers         List of tutorial presentations                                                                                                                                                                                                                         | · · ·                            |                                      | $2 \\ 3 \\ 3 \\ 4 \\ 6 \\ 6 \\ 6 \\ 6$                                                  |

| 2  | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | Materi<br>Funda<br>2.2.1<br>2.2.2<br>Overvi<br>2.3.1<br>2.3.2<br>Compa<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4 | bide power devices and key advantages and challenges         al properties         mentals and potential advantages of SiC         Fundamental properties of SiC         Potential advantages of SiC         ew of SiC power devices         SiC power diodes         SiC switches         arison of SiC MOSFETs/SiC diodes with Si MOSFETs/Si diodes         Structures of MOSFET         Comparison of SiC MOSFETs with Si MOSFETs         Structures of diode         Structures of SiC MOSFETs with Si MOSFETs | · · ·<br>· · ·<br>· · ·<br>· · · | ·<br>·<br>·<br>·<br>·<br>·<br>·<br>· | $ \begin{array}{c} 10\\ 10\\ 12\\ 12\\ 14\\ 17\\ 17\\ 17\\ 19\\ 19\\ 19\\ \end{array} $ |

|    | 2.5                                                       | Packag                                                                                                     | $\operatorname{ging}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                |                                      | 20                                                                                      |

|   | $2.6 \\ 2.7$                           | Critical thinking or challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

|---|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 |                                        | requisites for accurate assessment of switching loss by electrical thod         Introduction         Prerequisites for accurate measurement of high-speed switching signals         3.2.1       Bandwidth of measuring probes and oscilloscope         3.2.2       Low-inductive measurement connections         3.2.3       Load inductor characteristics         3.2.4       Post processing of measured data         mportance of realistic circuits for loss evaluation         3.3.1       Hard-switched topology         3.3.2       Resonant inverter topology         3.3.3       Experimental results for hard versus resonant topology         Summary | <ul> <li>23</li> <li>24</li> <li>24</li> <li>25</li> <li>26</li> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>29</li> <li>31</li> </ul> |

| 4 | <b>Cha</b><br>4.1<br>4.2<br>4.3<br>4.4 | aracterization of state-of-the-art SiC MOSFET modules         Introduction         Comparison of SiC MOSFET modules         4.2.1         Modules with different stray inductance         4.2.2         Modules with different stray capacitance         Comparison of SiC MOSFET and Si IGBT         4.3.1         SiC MOSFET vs. Si non-punch-through IGBT modules         4.3.2         SiC MOSFET versus Si soft-punch-through IGBT         Summary                                                                                                                                                                                                          | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>39</li> <li>42</li> <li>42</li> <li>46</li> <li>51</li> </ul>                         |

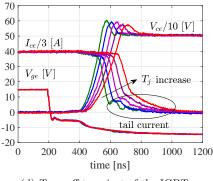

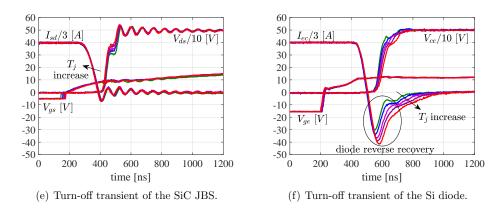

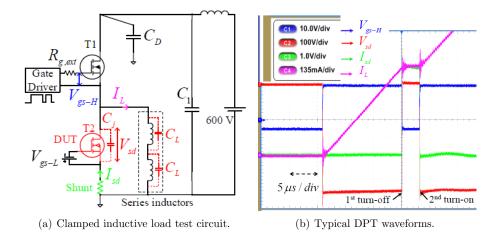

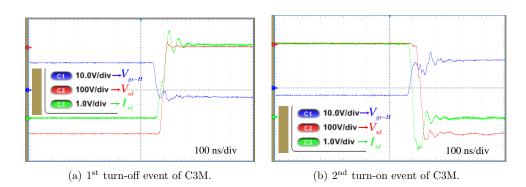

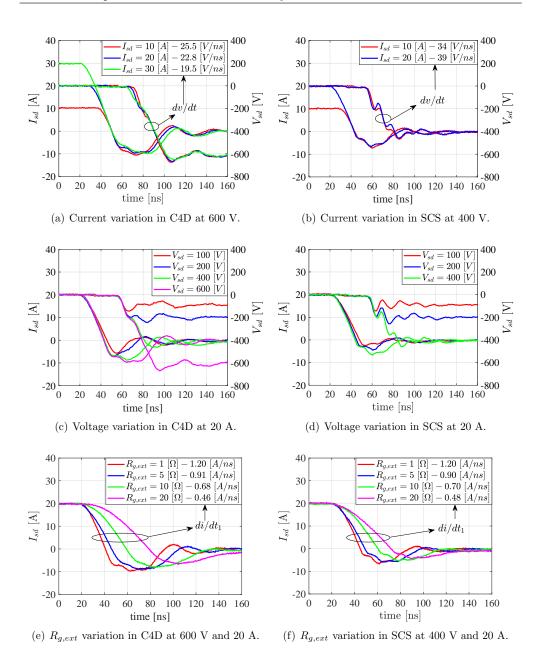

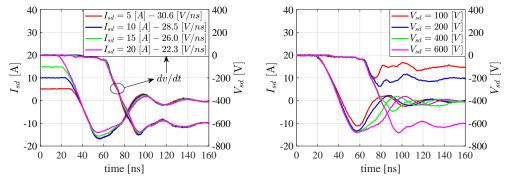

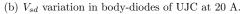

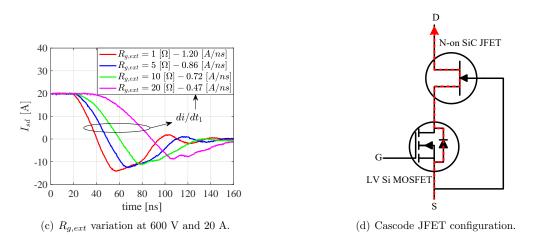

| 5 | Cha<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | aracterization of body-diodes in state-of-the-art SiC MOSFETsIntroductionDevice under testMethodologyHardware setup and measurement considerationsExperimental results5.5.1Planar versus double-trench MOSFETs5.5.2Planar Schottky diodes with different chip areas5.5.3Trench cascode JFET5.5.4Comparison of DUTs at 400 and 600VConclusion                                                                                                                                                                                                                                                                                                                     | <ul> <li><b>53</b></li> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>60</li> <li>61</li> <li>63</li> </ul>      |

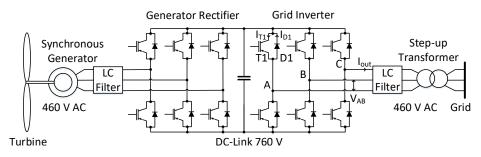

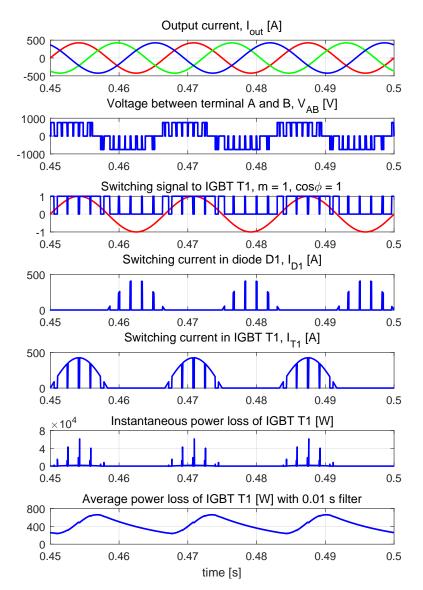

| 6 | <b>Apj</b><br>6.1                      | plications of SiC power devices         Wind power applications         6.1.1         Methodology and measurement results         6.1.2         Topology selection and simulation of losses         6.1.3         Simulation results         6.1.4         Evaluation of inverter power loss at different switching frequencies         6.1.5         Evaluation of back-to-back converter efficiency at different switching frequencies         6.1.6         Discussion and summary                                                                                                                                                                            | <ul> <li>65</li> <li>66</li> <li>66</li> <li>67</li> <li>68</li> <li>71</li> <li>72</li> <li>72</li> <li>72</li> </ul>                         |

|   | 6.2        | Induction heating applications                                           | . 74         |

|---|------------|--------------------------------------------------------------------------|--------------|

|   |            | 6.2.1 Device under study                                                 | . 75         |

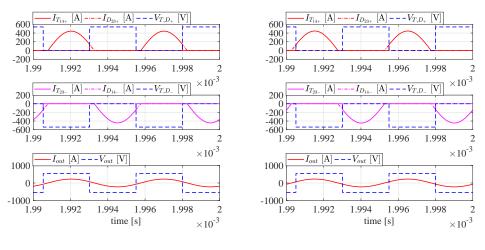

|   |            | 6.2.2 Calorimetric loss measurement in a full-bridge resonant inverter . |              |

|   |            | 6.2.3 Accuracy analysis of calorimetric efficiency measurement           | . 81         |

|   |            | 6.2.4 Discussion and summary                                             |              |

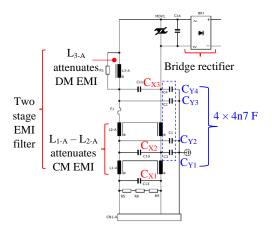

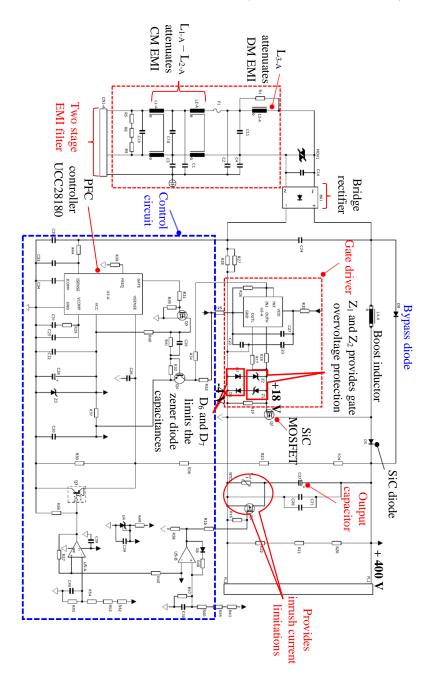

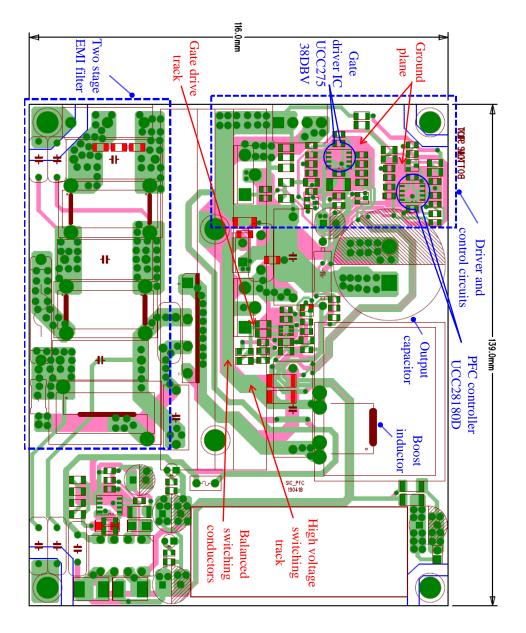

|   | 6.3        | Power factor correction applications                                     |              |

|   |            | 6.3.1 Converter description and specification                            |              |

|   |            | 6.3.2 PFC converter loss evaluation via circuit simulation               |              |

|   |            | 6.3.3 Circuit design and layout considerations of PFC rectifier          |              |

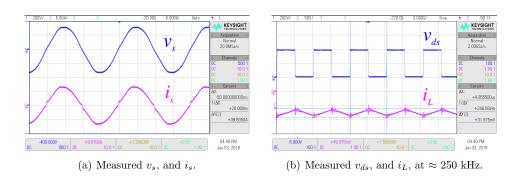

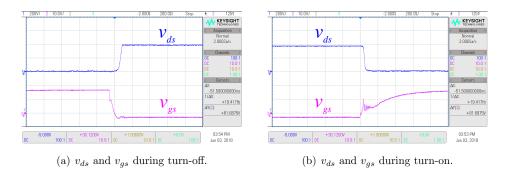

|   |            | 6.3.4 Experimental results                                               |              |

|   |            | 6.3.5 Summary and conclusion                                             |              |

| 7 | Low        | v-inductive converter design considerations                              | 97           |

|   | 7.1        | Introduction                                                             | . 97         |

|   | 7.2        | Theoretical background for the selection of dielectric material          | . 99         |

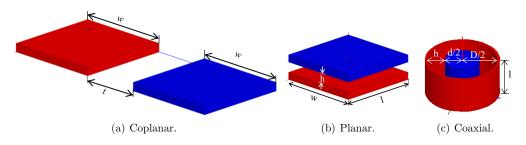

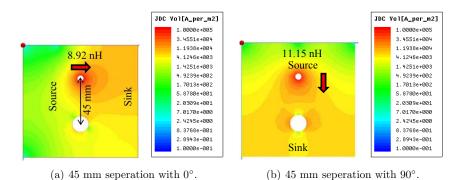

|   | 7.3        | Impact of geometry on stray inductance and capacitance                   | . 100        |

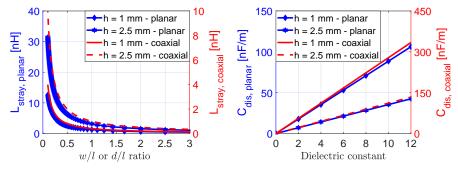

|   | 7.4        | Selection of low inductance DC-link capacitors                           | . 101        |

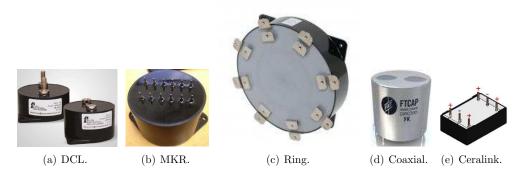

|   | 7.5        | Impact of capacitor orientation on inductance                            |              |

|   |            | 7.5.1 Axial terminated capacitors                                        | . 103        |

|   |            | 7.5.2 Circular terminated capacitors                                     | . 106        |

|   | 7.6        | Design of DC-link for AC-DC-AC converter                                 | . 108        |

|   |            | 7.6.1 Sizing the DC-link capacitor                                       | . 108        |

|   |            | 7.6.2 Comparison of stray inductance shared by various parts             |              |

|   |            | 7.6.3 Exemplifying a DC-link busbar design with coaxial capacitor        |              |

|   | 7.7        | Example of a low-inductive busbar design for SiC MOSFET modules          |              |

|   |            | 7.7.1 Busbar for single screw hole module                                |              |

|   |            | 7.7.2 Busbar for multiple screw holes module                             |              |

|   | 7.8        | Example of a low-inductive busbar design using discrete SiC MOSFETs .    |              |

|   | 7.9        | Conclusion                                                               |              |

| 8 | Cor        | nclusions and Future work                                                | 117          |

|   | 8.1        | Summary and conclusions                                                  | . 117        |

|   | 8.2        | Suggested future work                                                    | . 121        |

| A |            | dix A LTSpice Simulation for analyzing the impact of parasitics i        |              |

|   |            | switching                                                                | 123          |

|   | A.1        | Impact of stray inductance                                               |              |

|   |            | A.1.1 Impact of switching-loop inductance                                |              |

|   |            | A.1.2 Impact of gate-loop inductance                                     |              |

|   | A.2        | 1 0 1                                                                    |              |

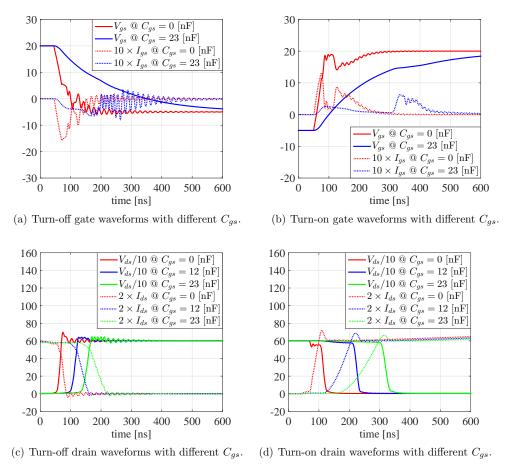

|   |            | A.2.1 Impact of gate-source capacitance                                  |              |

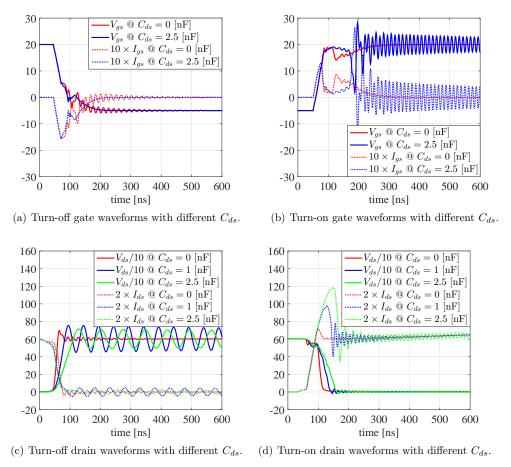

|   |            | A.2.2 Impact of drain-source capacitance                                 |              |

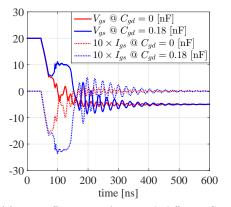

|   |            | A.2.3 Impact of gate-drain capacitance                                   | . 127        |

| A |            | dix B 3D FEM simulation for low inductive circuit designs                | 129<br>120   |

|   | B.1<br>B.2 | Modelling of busbar in Ansys Q3D extractor                               | . 129<br>132 |

|   | D.2        | Estimation of stray inductance via measurement and analytical expression | 197          |

| Appen   | dix C   | Fundamental information for Chapter 6                               | 133 |

|---------|---------|---------------------------------------------------------------------|-----|

| C.1     | Equati  | ons for passive component sizing                                    | 133 |

| C.2     | Equati  | ons for conduction loss calculation                                 | 133 |

| C.3     | A com   | plete schematic diagram and component layout of PFC rectifier (two- |     |

|         | layer b | $\operatorname{poard}$                                              | 134 |

| Appen   | dix D   | An insight into close-to-lossless switching enabled by SiC          | 2   |

| MO      | SFET    |                                                                     | 137 |

| D.1     | Introd  | uction                                                              | 137 |

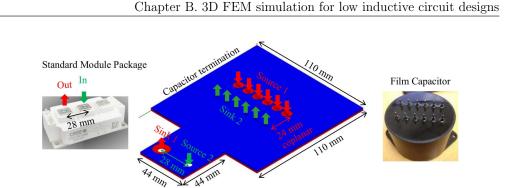

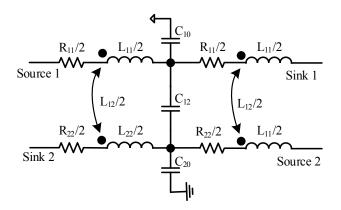

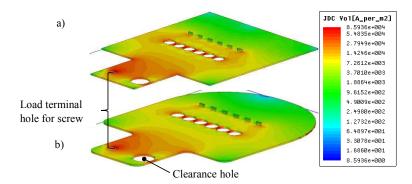

| D.2     | Design  | of low inductive layout via 3D FEM simulation in Ansys Q3D $$       | 138 |

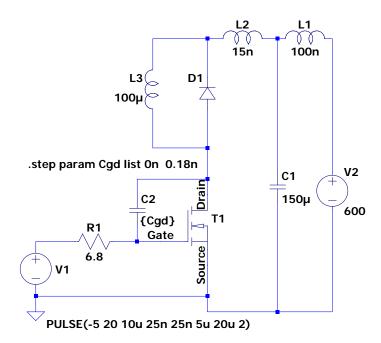

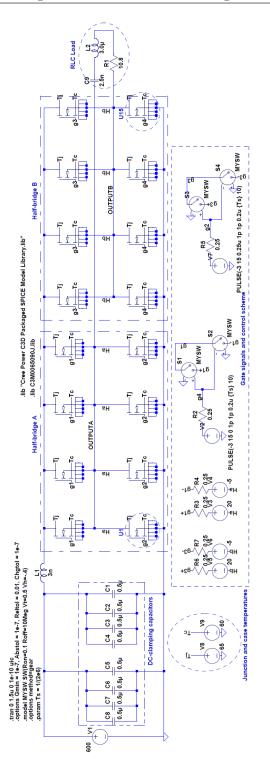

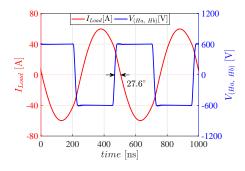

| D.3     | Evalua  | tion of inverter via LTSpice simulations                            | 141 |

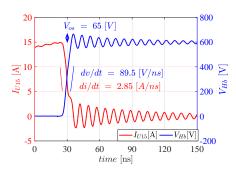

|         | D.3.1   | Analysis of voltage overshoot when switched at 8 A                  | 142 |

|         | D.3.2   | Analysis of voltage overshoot when switched at 15 A                 | 143 |

|         | D.3.3   | Conclusion                                                          | 144 |

| Bibliog | raphy   |                                                                     | 145 |

## List of Tables

| 2.1          | Key material properties of Si, GaAs, SiC and GaN [14,31].                                                                                                                                    | 9          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2          | A list of reported SiC BJTs.                                                                                                                                                                 | 16         |

| 2.3          | A list of reported SiC IGBTs.                                                                                                                                                                | 17         |

| $2.4 \\ 2.5$ | Comparison of key parameters for Si versus SiC MOSFETs in TO247 package.<br>Comparison of key parameters for Si- versus SiC Schottky diodes in TO247                                         | 18         |

| 2.0          | package                                                                                                                                                                                      | 20         |

| 2.6          | Commercially available SiC modules and their package inductance.                                                                                                                             | $20 \\ 21$ |

| 3.1          | Data sheet readings of voltage measurement probes used in the thesis                                                                                                                         | 25         |

| 3.2          | Current measurement techniques and their specifications as per data sheet.                                                                                                                   | 25         |

| 4.1          | $O_{1}$ state assistance total discrime $C_{1}$ and $C_{2}$ of the module and $C_{2}$                                                                                                        |            |

| 4.1          | On-state resistance, total die size, $C_{iss}$ , and $C_{oss}$ of the modules under study.                                                                                                   | 35         |

| 4.2          | Summary of laboratory measurements for CAS120M12BM2 (Wolfspeed,                                                                                                                              | 55         |

| 4.2          | MOSFET).                                                                                                                                                                                     | 36         |

| 4.3          | Summary of laboratory measurements for BSM120D12P2C005 (Rohm,                                                                                                                                | 00         |

|              | MOSFET).                                                                                                                                                                                     | 36         |

| 4.4          | Data sheet readings of SiC MOSFET dies with different voltage ratings                                                                                                                        | 39         |

| 4.5          | Data sheet readings of SiC MOSFET modules with same voltage ratings                                                                                                                          | 39         |

| 4.6          | Key electrical parameters of SiC MOSFET versus Si NPT IGBT modules.                                                                                                                          | 43         |

| 4.7          | Summary of laboratory measurements for CAS300M12BM2 (Wolfspeed,                                                                                                                              |            |

|              | MOSFET).                                                                                                                                                                                     | 43         |

| 4.8          | Summary of laboratory measurements for SKM400GB125D (Semikron,                                                                                                                               |            |

|              | IGBT)                                                                                                                                                                                        | 44         |

| 4.9          | Specific loss of SiC MOSFET versus Si IGBT for the selected $R_{g,on}$ and                                                                                                                   |            |

| 4.10         | $R_{g,off}$                                                                                                                                                                                  | 45         |

|              | Key electrical parameters of SiC MOSFET versus Si SPT IGBT modules.                                                                                                                          | 47         |

| 4.11         | Key measurements of SiC MOSFET vs Si IGBT module. $V_{ds} = 500 \text{ V}, I_{ds} = 120 \text{ A}$ , two different junction temperatures: $T_i = 25 \text{ °C}$ and $T_i = 125 \text{ °C}$ , |            |

|              | and two different gate resistances for each modules. $\dots \dots \dots \dots \dots$                                                                                                         | 50         |

|              | and two different gave resistances for each modules                                                                                                                                          | 00         |

| 5.1          | Key parameters of the investigated device under test                                                                                                                                         | 54         |

| 5.2          | $dv/dt$ , $di/dt_2$ , $I_{rrm}$ , and $t_{rr}$ of C4D and SCS at 20 A and two different                                                                                                      |            |

|              | voltages: 100 and 400 V.                                                                                                                                                                     | 60         |

| 5.3          | $dv/dt$ , $di/dt_2$ , $I_{rrm}$ , and $t_{rr}$ of the investigated DUTs at 400 V and 600 V                                                                                                   |            |

|              | while keeping a constant $di/dt_1$ of 1.2 A/ns. Compared to 400 V, $dv/dt$ ,                                                                                                                 | co         |

|              | $I_{rrm}$ , and $t_{rr}$ are measured to be higher at 600 V                                                                                                                                  | 62         |

| 6.1          | Key electrical parameters of half-bridge SiC MOSFET module versus half-                                                                                          |      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|              | bridge Si NPT IGBT module.                                                                                                                                       | 66   |

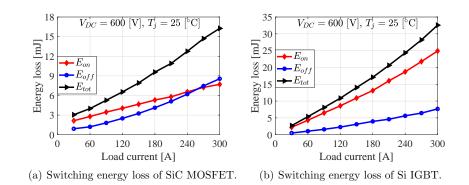

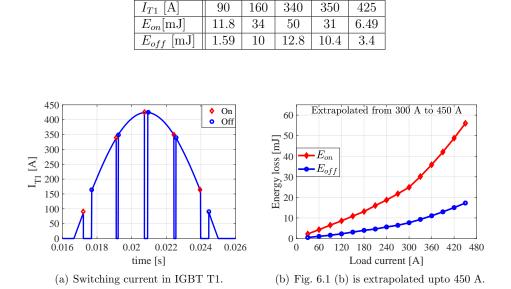

| 6.2          | Reading of currents and energy losses (refer Fig. 6.4 (a) and (b)                                                                                                | 69   |

| 6.3          | A comparison of simulated and numerically calculated power loss of tran-                                                                                         |      |

|              | sistor T1.                                                                                                                                                       | 70   |

| 6.4          | Definition of symbols used in $(6.1)$ - $(6.3)$ .                                                                                                                |      |

| 6.5          | Key electrical parameters of the six-pack SiC MOSFET module versus the                                                                                           |      |

| 0.0          | six-pack Si SPT IGBT module.                                                                                                                                     | 73   |

| 6.6          | Conduction losses of SiC MOSFET versus Si IGBT modules (six-packs)                                                                                               |      |

| 0.0          | in a two-level VSC during motoring versus generating operations at two                                                                                           |      |

|              | different junction temperatures                                                                                                                                  | 73   |

| 6.7          | Conduction losses of SiC MOSFET versus Si IGBT modules (half-bridges)                                                                                            | 10   |

| 0.1          | in a two-level VSC during motoring versus generating operations at two                                                                                           |      |

|              | different junction temperatures                                                                                                                                  | 74   |

| 6.8          | Major differences between a SiC DioMOS and a standard SiC MOSFET                                                                                                 | 14   |

| 0.8          |                                                                                                                                                                  | 75   |

| 6.9          | Summary of the measured parameters at 78 kW input power.                                                                                                         |      |

|              |                                                                                                                                                                  | 80   |

| 6.10         | Summary of the calculated parameters for approximately 78 kW of input                                                                                            | 01   |

| C 11         | power                                                                                                                                                            | 81   |

| 0.11         | Summary of the specific turn-off loss measurements in three different                                                                                            |      |

|              | topologies and normalization with regard to electrically measured loss in a                                                                                      | 0.0  |

| 0.10         | half-bridge resonant inverter.                                                                                                                                   | . 82 |

|              | Specifications of PFC boost converter.                                                                                                                           | 85   |

| 6.13         | Chosen components with their part numbers and specifications. The on-                                                                                            |      |

|              | state parameters associated with the diode, $V_{FO}$ and $R_d$ , and MOSFET,                                                                                     |      |

|              | $R_{DS,on}$ , are taken at 125 °C [82,86]                                                                                                                        |      |

| 6.14         | EMI filter specifications.                                                                                                                                       | 92   |

| 7.1          | List of insulating materials with breakdown voltage, dielectric constant and                                                                                     |      |

| 1.1          | continuous temperature.                                                                                                                                          | 99   |

| 7.2          | Electrical specification of low inductance DC-link capacitors.                                                                                                   |      |

| 7.3          | Parameters normalized to capacitance of Ring capacitor.                                                                                                          |      |

| 7.4          | Parameters normalized to ripple current of Ring capacitor.                                                                                                       |      |

| 7.5          | Summary of inductances for axial terminated capacitors.                                                                                                          |      |

| 7.6          | Summary of inductances for circular terminated capacitors                                                                                                        |      |

| $7.0 \\ 7.7$ | Summary of switching loop inductance                                                                                                                             |      |

| 7.1<br>7.8   | Summary of switching loop inductance. $\ldots$ $\ldots$ $\ldots$ $\ldots$ Summary of $L_{stray,ext}$ in different designs from Q3D simulation. $\ldots$ $\ldots$ |      |

| 1.0          | Summary of $L_{stray,ext}$ in different designs from Q5D simulation                                                                                              | 113  |

## List of Figures

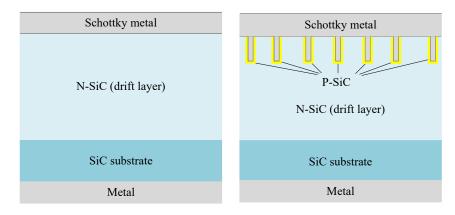

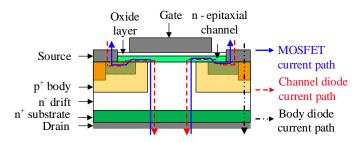

| <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | Key applications benefiting from SiC power devices                                                                                                                                                                                                                                                                                                                                                          | 11<br>13<br>18<br>19 |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

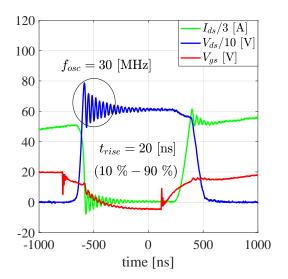

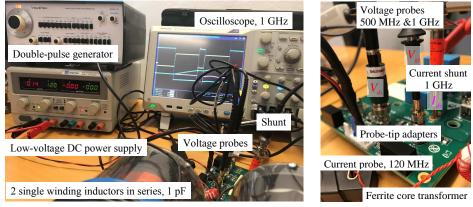

| 3.1<br>3.2                                                | For $R_{g,ext} = 0 \Omega$ , the $t_{rise}$ and $t_{fall}$ are in the range of 20 ns and the ringing<br>frequency $(f_{osc})$ is 30 MHz, thus the probes and oscilloscope bandwidth<br>of $\geq 150$ MHz are adequate for tracking these switching transients. The<br>legends used in Fig. 3.1 are: $V_{ds}$ , drain-source voltage; $I_{ds}$ , drain-source<br>current; and $V_{gs}$ , gate-source voltage | 24                   |

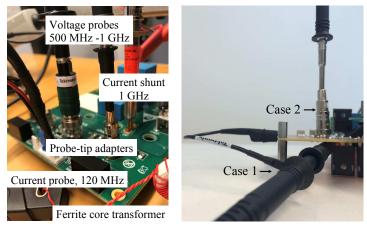

| 3.3                                                       | Load current is measured by a dc/ac current probe out of a 40-turn ferrite<br>core transformer                                                                                                                                                                                                                                                                                                              | 26                   |

| 3.4                                                       | to select the end of the integration time                                                                                                                                                                                                                                                                                                                                                                   | 27<br>28             |

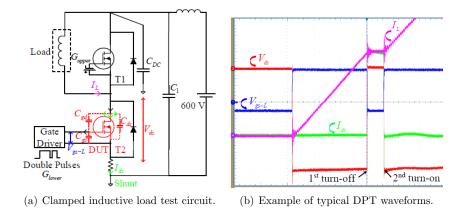

| 3.5<br>3.6                                                | Illustration of a circuit diagram for hard-switching loss measurement, and<br>an example of a typical double-pulse test waveform                                                                                                                                                                                                                                                                            | 28                   |

|                                                           | inductor and capacitor in (a), and an example of a typical output waveform, where the turn-off instant is the key point of interest and is annotated by a rectangle in (b).                                                                                                                                                                                                                                 | 29                   |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

xiii

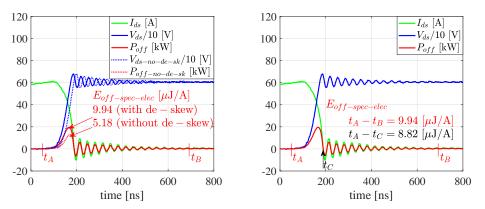

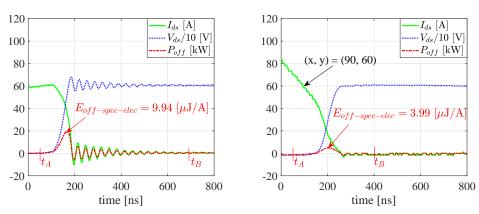

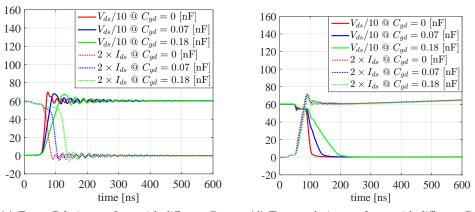

| 3.7 | (a) Illustration of turn-off transients under hard versus resonant topology<br>at the same load current. The former exhibits oscillations, while oscilla-<br>tions are absent in the latter. Specifically, the turn-off energy loss is 2.5<br>times lower for resonant topology than that of the hard-switched inverter,<br>showing the ample benefit of the latter topology                                                                                                      | 30 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

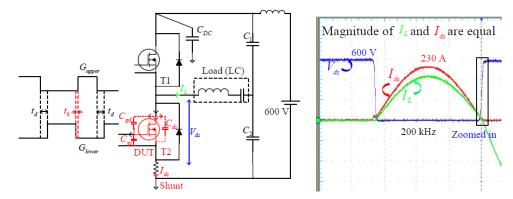

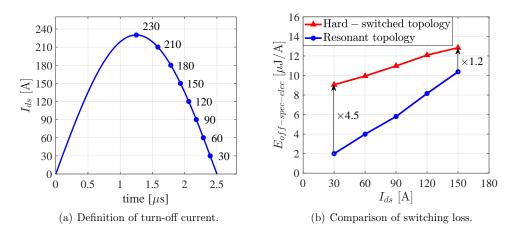

| 3.8 | (a) Illustration of the turn-off current in the resonant switching case. The peak value of the load current is set at 230 A, and the turn-off instants are varied. (b) Comparison of the switching loss between the hard (square wave current) and soft/resonant (sine wave current) switching. Switching with square wave current leads to higher turn-off losses, a factor of 1.2 (150 A) to 4.5 (30 A) depending on the load current, compared to that with sine wave current. | 30 |

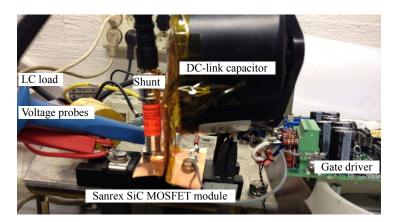

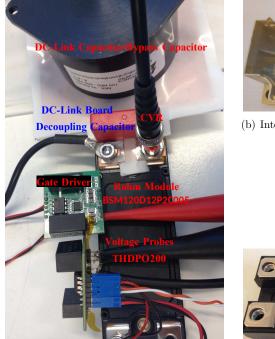

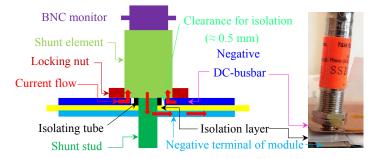

| 4.1 | (a) Hardware setup showing a planar busbar, placement of current viewing resistor (CVR) instead of a screw, several parallel capacitors in the DC-link to reduce stray inductance associated with bypass capacitor and their connections $(L_{byp})$ , and to realize an overall low stray inductance $(L_{stray})$ in the switching loop. (b) and (c) Pictures showing the internal layouts of two different modules under study.                                                | 34 |

| 4.2 | Detailed sketch of CVR insertion between the busbar and the module. A clearance of 0.5 mm is provided for shunt voltage drop on the DC-busbar.                                                                                                                                                                                                                                                                                                                                    | 35 |

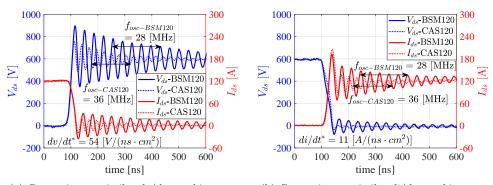

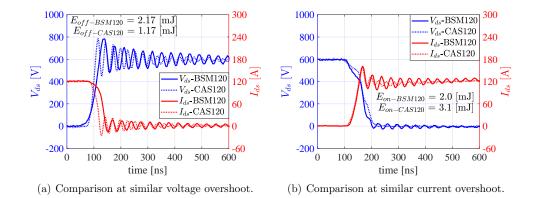

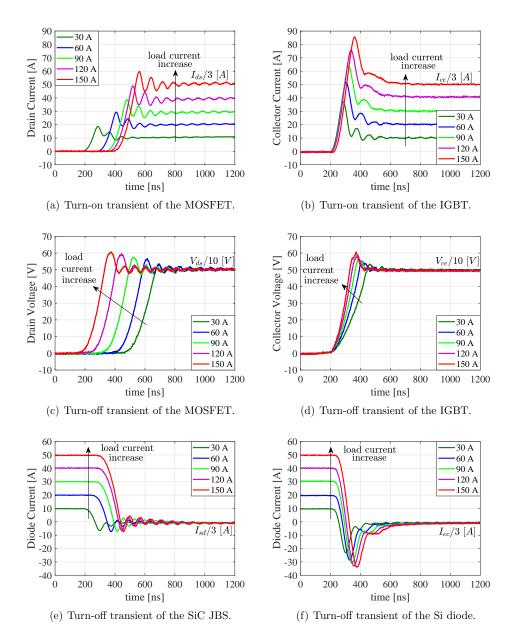

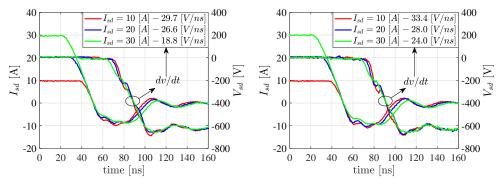

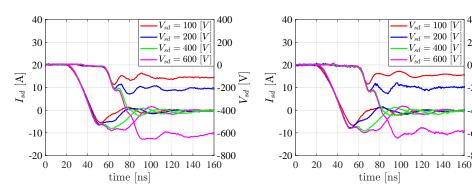

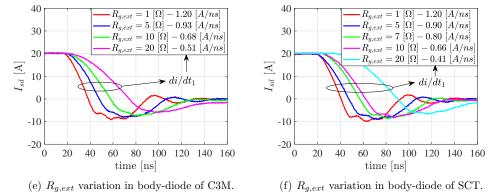

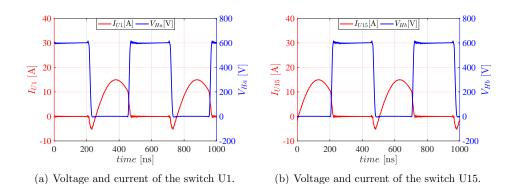

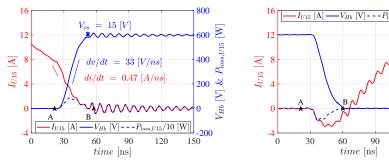

| 4.3 | Measurement of switching transients of two different SiC MOSFET mod-<br>ules at similar $dv/dt$ per chip area during turn-off and similar $di/dt$ per<br>chip area during turn-on.                                                                                                                                                                                                                                                                                                | 37 |

| 4.4 | Measurement of switching transients of two different SiC MOSFET mod-<br>ules at similar voltage overshoot during turn-off and similar current over-<br>shoot during turn-on.                                                                                                                                                                                                                                                                                                      | 37 |

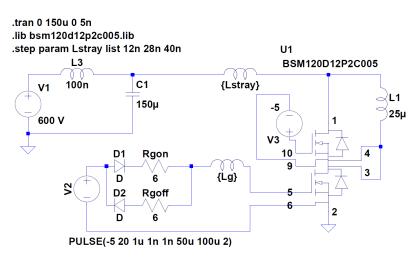

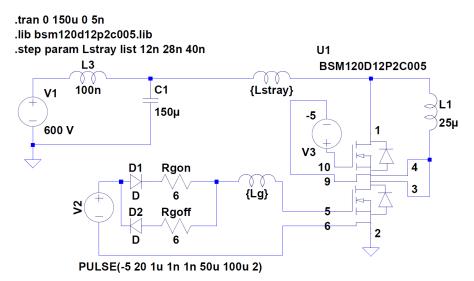

| 4.5 | Simulation model in LTSpice for the study of impact of stray inductances.                                                                                                                                                                                                                                                                                                                                                                                                         | 38 |

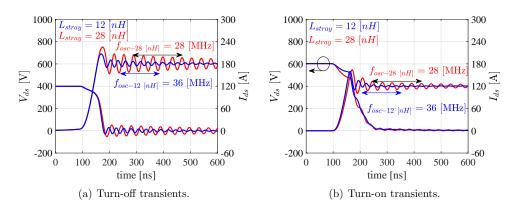

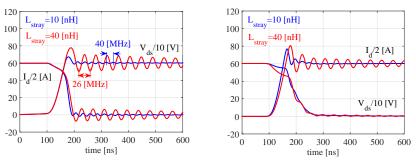

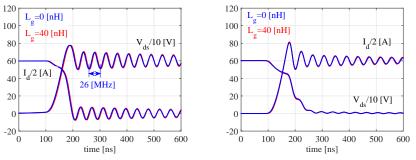

| 4.6 | LTSpice simulation of turn-off and turn-on switching transients with two different values of $L_{stray}$ , provided $R_{g,ext} = 6 \ \Omega$ . Note that an LTSpice model of a half-bridge SiC MOSFET module, BSM120D12P2C005, is considered to investigate the effect of parasitic inductance. Clearly, the higher the $L_{stray}$ , the higher the overshoot and the larger and longer the oscillations.                                                                        | 38 |

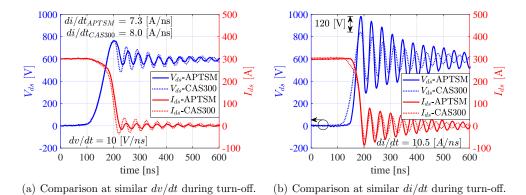

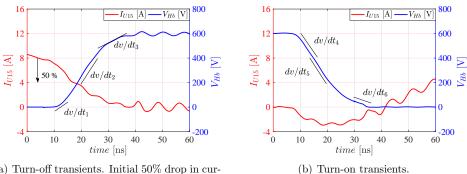

| 4.7 | (a) APTSM has slightly lower $di/dt$ compared to CAS300, indicating the presence of higher $L_{module}$ in it. (b) At similar $di/dt$ during turn-off, the APTSM shows noticeably higher overshoot than the CAS300, further clarifying the fact that it has higher $L_{module}$ .                                                                                                                                                                                                 | 40 |

| 4.8 | Measured turn-on transients of two modules at similar $di/dt$ in the turn-<br>on. Simulation results with different $C_{gs}$ and $C_{ds}$ , as presented in the<br>Appendix, further confirm that the lower current overshoot in APTSM is<br>due to smaller $Q_c$ , smaller $C_{ds}$ and larger $C_{gs}$ in it compared to CAS300.                                                                                                                                                | 41 |

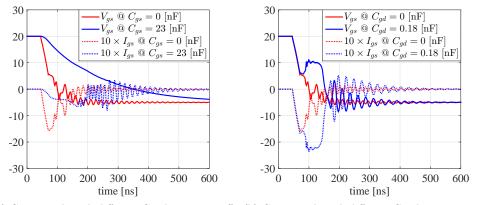

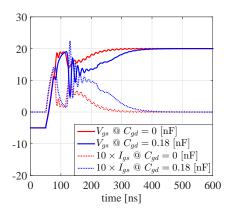

| 4.9 | (a) Impact of different $C_{gs}$ and $C_{gd}$ on $V_{gs}$ and $I_{gs}$ . Higher $C_{gs}$ leads to cleaner gate signals; whereas, higher $C_{gd}$ results in noisier ones. Hence, higher ratio of $C_{gs}/C_{gd}$ is preferable to avoid possible device malfunction.                                                                                                                                                                                                              | 41 |

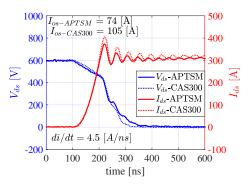

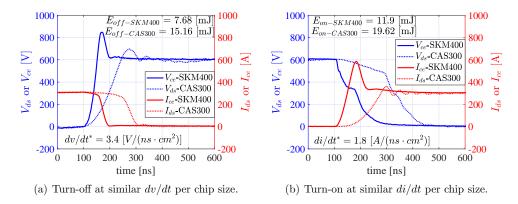

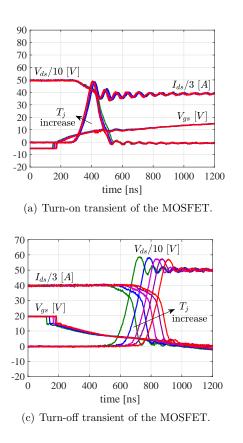

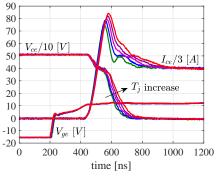

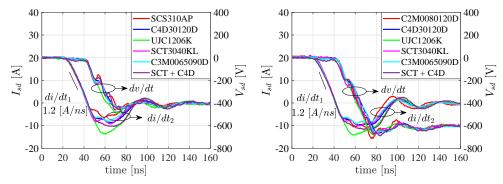

| 4.10  | Measurement of switching transients of SiC MOSFET module versus Si<br>IGBT module at similar $dv/dt$ per chip area during turn-off and similar<br>di/dt per chip area during turn-on. Provided the same chip area, SiC<br>MOSFET incurs higher losses compared to Si IGBT, indicating the possible<br>higher junction temperature in the chip of the former module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

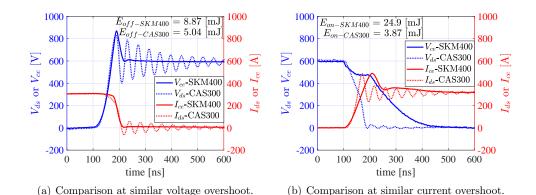

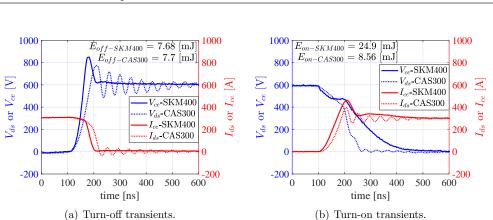

| 4.11  | Measurement of switching transients of SiC MOSFET versus Si IGBT mod-<br>ules at similar voltage overshoot during turn-off and similar current over-<br>shoot during turn-on. Given the similar overshoot, SiC MOSFET shows<br>better performance than Si IGBT from an efficiency viewpoint, but the<br>amount of parasitic ringing is noticeably higher in SiC MOSFET. Note<br>that turn-on losses are higher in Si IGBT which is primarily because of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11  |

| 1.10  | higher recovery charge of Si pn diode associated with it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45  |

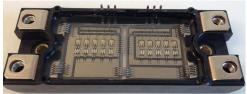

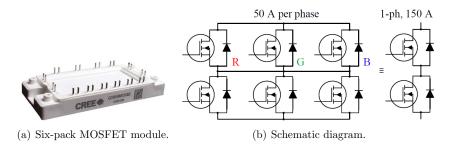

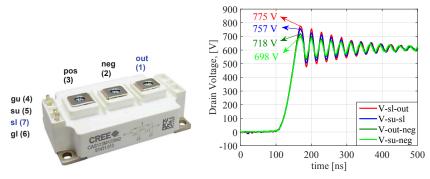

|       | Comparison of switching events for the chosen optimal case (a) Photograph of a six-pack SiC MOSFET module from Wolfspeed. (b) Schematic diagram showing the parallel connection of three phases in a six-pack SiC MOSFET module forming an equivalent single phase (1-ph),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46  |

| 4 1 4 | 150 A, half-bridge configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46  |

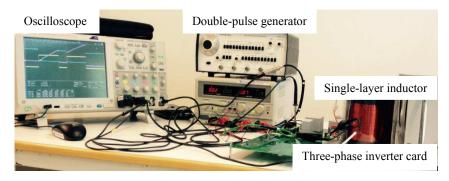

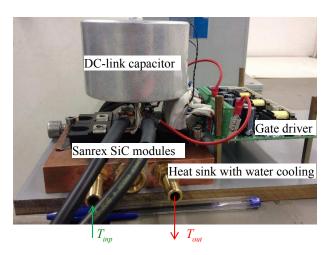

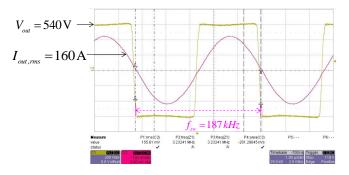

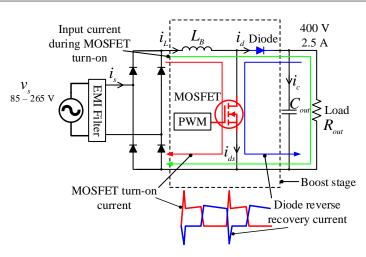

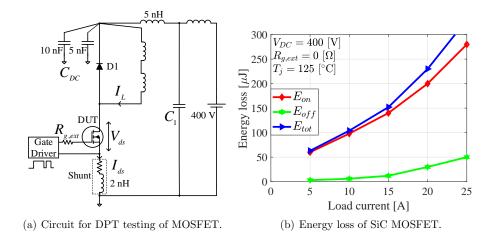

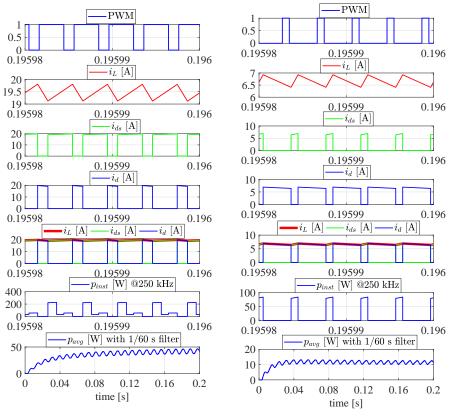

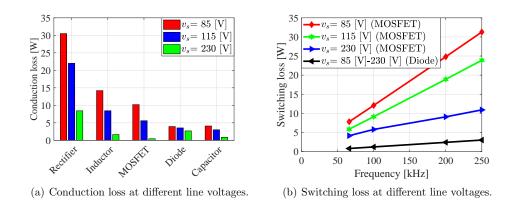

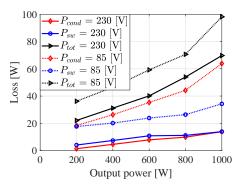

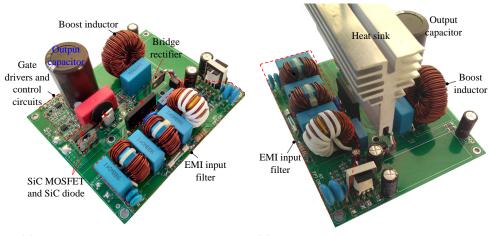

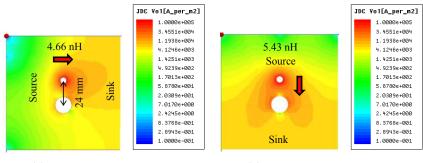

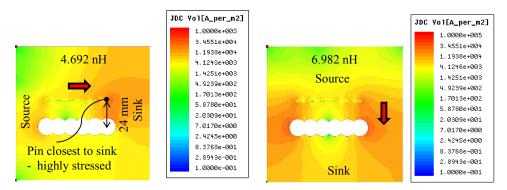

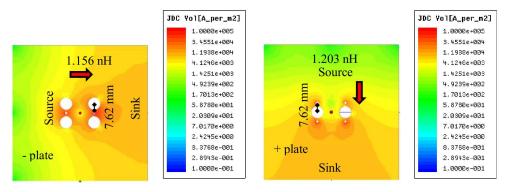

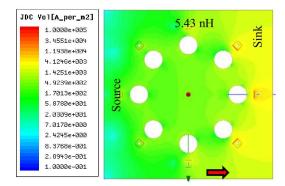

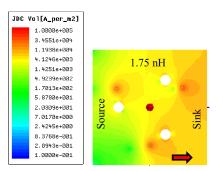

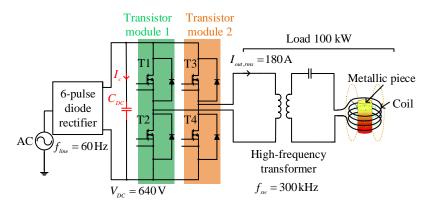

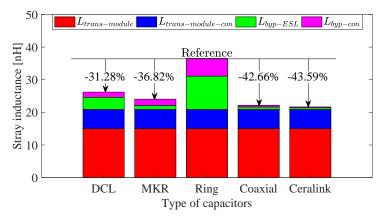

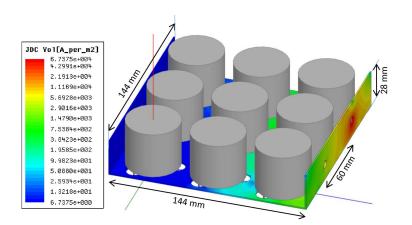

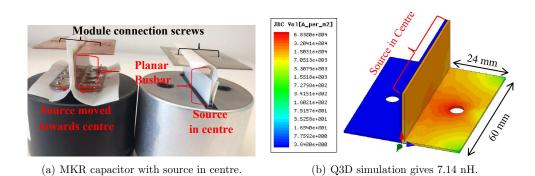

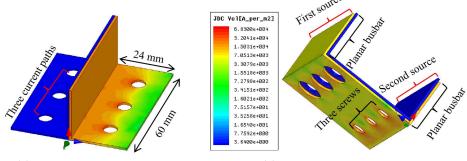

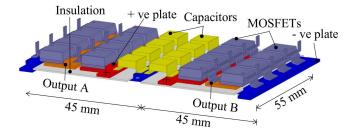

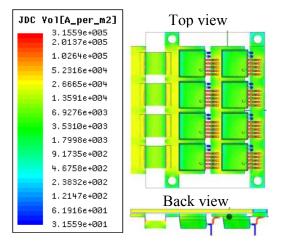

| 4.14  | Hardware setup showing the double pulse test arrangement. Switching<br>energy loss is measured using a three-phase inverter power circuit board in<br>order to emulate a stray inductance of a real application circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47  |