# Development of an Embedded Test Platform

A Real-Time Programmers Perspective

# Henrik Finnland Foss

Master of Science in Cybernetics and Robotics Submission date: June 2014 Supervisor: Amund Skavhaug, ITK

Norwegian University of Science and Technology Department of Engineering Cybernetics

# MASTER THESIS

# **Development of an Embedded Test Platform**

A Real-Time Programmers Perspective

*Author:* Henrik Finnland Foss Supervisor: Amund Skavhaug

June 9, 2014

# Preface

This thesis is a report of my master thesis project in Engineering Cybernetics at the Norwegian University of Science and Technology (NTNU). It is a study into different topics concerning embedded and real-time systems. The goals were twofold, one part concerned with hardware and creating a platform for testing such topics, and the other studying real-time behaviour of a complex operating system patched to be fully preemptible.

The project started in January 2014, and has presented me with the opportunity to work with both familiar and unfamiliar subjects. The project was specified as a set of goals instead of a tight problem description. This meant that I was able to shape my own path and could thus investigate deeper into topics which presented themselves as challenging.

I would like to give a special thanks to my supervisor, Amund Skavhaug, for excellent guidance.

Henrik Finnland Foss Trondheim, June 9, 2014

## Summary

As the embedded world grows day by day, more complex operations are carried out in this environment. The embedded market is no longer dominated by the 8-bit segment, and future embedded and real-time programmers will thus need a wider range of knowledge and skills. This project is a study into several aspects of embedded real-time systems. The first goal was to create a versatile test platform for future programmers to learn real-time and embedded programming principles. The second goal was to study GNU/Linux in an embedded real-time environment. The purpose of the first goal was to create an improved alternative to the course assignment in TTK4147, Real-Time Systems, where today's exercises are either outdated or run on virtual machines. The purpose of the second goal was to investigate the potential for a complex operating system to offer hard real-time characteristics.

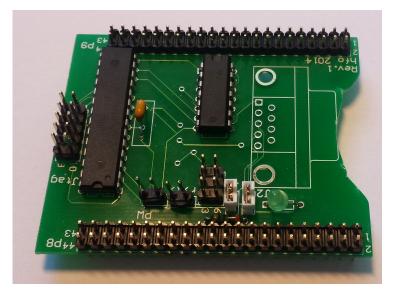

This project has created an embedded platform for testing embedded and real-time principles. The platform consists of a single-board computer together with a stackable cape by own design, containing a 8-bit microcontroller circuit. The cape, called the External Response Tester, was programmed to perform testing on the responsiveness of the connected hardware, and it was shown that it did so with precision. We also expanded on the operating systems catalogue for the single-board computer as we ported a fully preemptible Linux kernel, as well as the real-time operating system FreeRTOS to work on the board. This complete educational platform was found to be capable of unifying and replacing most of the TTK4147 course assignments.

The operating system GNU/Linux, more importantly the fully preemptible PREEMPT\_RT version, was evaluated in terms of usage in hard real-time systems. An analysis that compared results from the ordinary Linux kernel, the PREEMPT\_RT patched Linux kernel, and FreeRTOS was carried out. We concluded that the fully preemptible Linux version is not "definitely unsuitable", and its applicability depends on the requirements of a given real-time application.

## Sammendrag

Innebygde datasystemer finnes i dag i mange ulike applikasjoner, og antallet øker sterkt. Videre utfører slike datasystemer stadig mer komplekse operasjoner. Tidligere var dette markedet dominert av 8-bit mikrokontrollere, i dag benyttes stadig mer komplekse prosessorer. Dette fører til at utviklere av innebygde datasystemer og sanntidssystemer trenger et bredere spekter av kunnskap og ferdigheter. Det første målet med denne oppgaven var å lage en allsidig og moderne test-plattform som programmerere kan bruke for å lære seg viktige prinsipper innenfor fagområdene. Det andre målet var å studere operativsystemet GNU/Linux for bruk i innebygde sanntidsapplikasjoner. Bakgrunnen for at vi satte oss det første målet var at dagens øvingsopplegg i TTK4147 Sanntidssystemer, er enten utdatert eller kjøres på virtuelle maskiner. En ny og moderne plattform ville kunne forbedre store deler av dette øvingsopplegget. Bakgrunnen for at vi satte oss det andre målet var at vi ville undersøke potensialet for å ha et komplekst operativsystem som GNU/Linux til å levere harde sanntidsegenskaper.

Dette prosjektet har utviklet en plattform som muliggjør testing av prinsipper fra innebygde datasystemer og sanntidssystemer. Plattformen består av en enkelt-brett datamaskin sammen med en 8-bit mikrokontroller-krets designet på et PCB brett. Denne mikrokontroller-kretsen har muligheten til å stables oppå enkelt-brett datamaskinen, eller fungere for seg selv. Den er programmert til å utføre tester som undersøker reaksjonsevnen til programvare kjørende på ekstern maskinvare. Dette viste vi at den utførte med god nøyaktighet. Vi utvidet også operativsystem katalogen for enkelt-brett datamaskinen med en fullt avbrytbar GNU/Linux versjon, og implementerte sanntids-operativsystemet FreeRTOS. Vi viste at denne komplette plattformen hadde alle egenskapene som skal til for å samle øvingsopplegget i TTK4147 til og utføres på en enkelt plattform.

Den fullt avbrytbare versjonen av GNU/Linux ble evaluert i forhold til sine sanntids-karakteristikker. En analyse sammenlignet resultater fra den ordinære GNU/Linux versjon, den full avbrytbare versjonen og FreeRTOS. Vi konkluderte med at den avbrytbare versjonen av Linux har et potensiale til å benyttes i sanntidsapplikasjonener, men det avhenger av applikasjonen.

iv

# Contents

|   | Pref | ace                                      | i   |

|---|------|------------------------------------------|-----|

|   | Sum  | nmary                                    | ii  |

|   | Sam  | nmendrag                                 | iii |

| 1 | Intr | oduction                                 | 1   |

|   | 1.1  | Background                               | 1   |

|   | 1.2  | Project goals                            | 2   |

|   | 1.3  | Main contributions                       | 2   |

|   | 1.4  | Report layout                            | 3   |

|   | 1.5  | Literature and Related Work              | 3   |

| 2 | Rea  | 1-time Systems                           | 5   |

|   | 2.1  | Interrupts                               | 5   |

|   | 2.2  | Latency                                  | 8   |

|   |      | 2.2.1 Worst case latency and boundedness | 9   |

|   |      | 2.2.2 Latency vs throughput              | 9   |

|   | 2.3  | Scheduling                               | 9   |

|   |      | 2.3.1 Priorities                         | 10  |

| 3 | Har  | dware                                    | 15  |

|   | 3.1  | ARM                                      | 15  |

|   |      | 3.1.1 ARM vs x86                         | 16  |

|   |      | 3.1.2 Other architectures                | 16  |

|   | 3.2  | BeagleBone Black                         | 16  |

|   |      | 3.2.1 The AM3358 processor               | 18  |

|   |      | 3.2.1.1 The exception vector             | 18  |

|   |      | 3.2.2 Programmable Realtime Unit         | 18  |

|   |     | 3.2.3   | The AM3358 Pin Multiplexer (Pinmux)  | 19 |

|---|-----|---------|--------------------------------------|----|

|   | 3.3 | Atmel   | 8-bit AVR                            | 20 |

|   |     | 3.3.1   | Modified Harvard Architecture        | 20 |

|   |     | 3.3.2   | Atmel Studio and the JTAG ICE        | 21 |

|   | 3.4 | Salea   | e Logic                              | 22 |

| 4 | Ope | erating | Systems                              | 23 |

|   | 4.1 | GNU/    | /Linux                               | 23 |

|   |     | 4.1.1   | Naming                               | 24 |

|   |     | 4.1.2   | Kernel Architecture                  | 24 |

|   |     | 4.1.3   | Kernel and User space                | 25 |

|   |     | 4.1.4   | Microkernel vs Monolithic kernel     | 26 |

|   |     | 4.1.5   | Linux Standard Base                  | 27 |

|   |     | 4.1.6   | Preemption and real-time viability   | 28 |

|   |     | 4.1.7   | Scheduling                           | 28 |

|   |     |         | 4.1.7.1 Priorities                   | 28 |

|   |     | 4.1.8   | Device Tree                          | 29 |

|   |     | 4.1.9   | General-purpose input/output Control | 29 |

|   |     |         | 4.1.9.1 Sysfs                        | 30 |

|   |     |         | 4.1.9.2 Memory mapping               | 31 |

|   |     |         | 4.1.9.3 Kernel module                | 31 |

|   |     |         | 4.1.9.4 Polling                      | 31 |

|   |     | 4.1.10  | Distributions                        | 32 |

|   | 4.2 | QNX     |                                      | 34 |

|   |     | 4.2.1   | Neutrino microkernel                 | 34 |

|   |     | 4.2.2   | Threads and processes                | 35 |

|   |     | 4.2.3   | Thread lifecycle                     | 35 |

|   |     | 4.2.4   | Scheduler                            | 36 |

|   | 4.3 | FreeR   | TOS                                  | 38 |

|   |     | 4.3.1   | Tasks in FreeRTOS                    | 38 |

|   |     | 4.3.2   | Lifecycle                            | 38 |

|   |     | 4.3.3   | FreeRTOS scheduler                   | 38 |

### CONTENTS

| 5                             | Har | dware                                                               | solution                         | 41 |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------|-----|---------------------------------------------------------------------|----------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

|                               | 5.1 | Propo                                                               | osed solution                    | 41 |  |  |  |  |  |  |  |  |  |  |  |

|                               | 5.2 | Extern                                                              | nal Response Tester              | 42 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 5.2.1                                                               | AVR butterfly                    | 42 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 5.2.2                                                               | BeagleBone Cape                  | 42 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 5.2.3                                                               | Prototyping                      | 43 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.2.3.1 Schematics               | 45 |  |  |  |  |  |  |  |  |  |  |  |

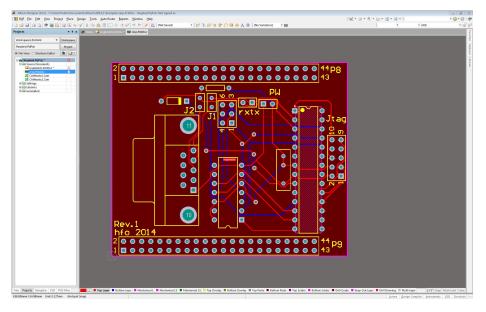

|                               |     | 5.2.4                                                               | PCB design                       | 48 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.2.4.1 Altium designer          | 48 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.2.4.2 Manufacturing files      | 48 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.2.4.3 Final pinout description | 49 |  |  |  |  |  |  |  |  |  |  |  |

|                               | 5.3 | ERT a                                                               | pplication                       | 51 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 5.3.1                                                               | How to use                       | 51 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 5.3.2                                                               | Code explanation                 | 53 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.1 Defines and globals      | 53 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.2 UART setup               | 53 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.3 Timer 1 and ICP setup    | 54 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.4 Timer 0 setup            | 54 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.5 Input/Output setup       | 54 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     |                                                                     | 5.3.2.6 The main loop            | 55 |  |  |  |  |  |  |  |  |  |  |  |

|                               | 5.4 | 4 Discussion on the creation of the External Response Tester cape 5 |                                  |    |  |  |  |  |  |  |  |  |  |  |  |

| 6 GNU/Linux on the BeagleBone |     |                                                                     |                                  |    |  |  |  |  |  |  |  |  |  |  |  |

|                               | 6.1 | Boot                                                                | process                          | 57 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.1.1                                                               | Bootloader                       | 57 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.1.2                                                               | SD card                          | 58 |  |  |  |  |  |  |  |  |  |  |  |

|                               | 6.2 | Debia                                                               | bian GNU/Linux                   |    |  |  |  |  |  |  |  |  |  |  |  |

|                               | 6.3 | Comp                                                                | ompiling the Linux kernel        |    |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.3.1                                                               | Configure pinmux driver          | 61 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.3.2                                                               | Device Tree setup                | 62 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.3.3                                                               | General configuration settings   | 65 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.3.4                                                               | Further optimizations            | 66 |  |  |  |  |  |  |  |  |  |  |  |

|                               | 6.4 | Devel                                                               | oping on the BeagleBone Black    | 67 |  |  |  |  |  |  |  |  |  |  |  |

|                               |     | 6.4.1                                                               | Cross-compilation with Eclipse   | 67 |  |  |  |  |  |  |  |  |  |  |  |

vii

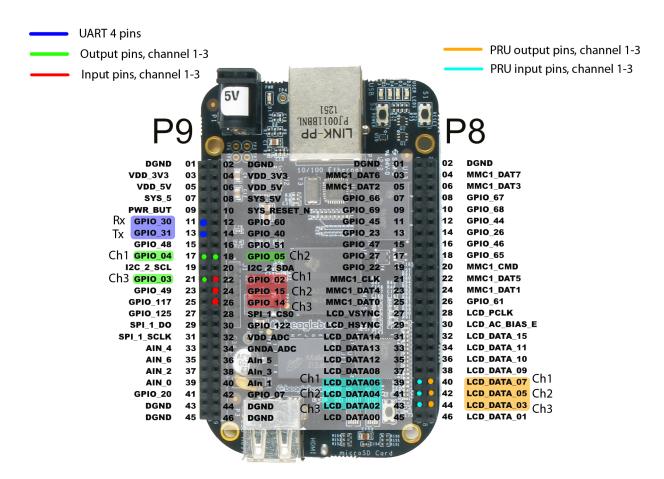

|   |      | 6.4.2   | BeagleBone pinout for interracting with the ERT cape | 68 |

|---|------|---------|------------------------------------------------------|----|

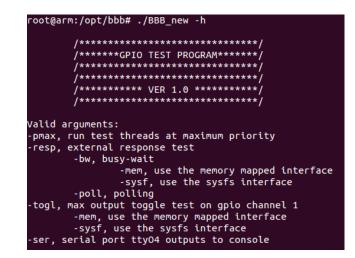

|   |      | 6.4.3   | GPIO test application                                | 68 |

|   |      |         | 6.4.3.1 The response test                            | 68 |

|   |      |         | 6.4.3.2 The maximum single pin toggle test           | 69 |

|   |      |         | 6.4.3.3 The code                                     | 70 |

|   |      | 6.4.4   | Developing for the PRU subsystem                     | 71 |

|   |      |         | 6.4.4.1 Starting and loading programs to the PRU     | 71 |

|   |      |         | 6.4.4.2 The PRU single pin maximum toggle test       | 72 |

|   |      |         | 6.4.4.3 PRU busy-wait test                           | 72 |

|   | 6.5  | Bench   | hmarking tools                                       | 72 |

|   |      | 6.5.1   | Cyclictest                                           | 73 |

|   |      | 6.5.2   | Stress                                               | 73 |

|   |      | 6.5.3   | Hackbench                                            | 73 |

|   | 6.6  | Discu   | ssion on the implementation of GNU/Linux             | 73 |

| 7 | Free | eRTOS   | and additional OS support                            | 75 |

|   | 7.1  |         |                                                      | 75 |

|   | 7.2  | -       | TOS                                                  | 75 |

|   |      | 7.2.1   |                                                      | 76 |

|   |      |         | 7.2.1.1 Configuring the tick interrupt               | 76 |

|   |      |         | 7.2.1.2 ARM exception vector                         | 77 |

|   | 7.3  | FreeR   | TOS test application                                 | 78 |

|   |      | 7.3.1   | GPIO interrupt                                       | 78 |

|   |      | 7.3.2   | Initialization of output GPIO and UART0              | 79 |

|   |      | 7.3.3   | Tasks                                                | 80 |

|   | 7.4  | Discu   | ssion on the implementation of additional OS support | 80 |

| 8 | Test | t setun | and results                                          | 83 |

| Ŭ | 8.1  | · · ·   | naximum single pin toggle test                       | 83 |

|   | 0.1  | 8.1.1   | Setup                                                | 83 |

|   |      | 8.1.2   | Testing                                              | 83 |

|   |      | 8.1.3   | Results                                              | 84 |

|   | 8.2  |         | ctest                                                | 86 |

|   |      | 8.2.1   | Setup                                                | 86 |

|   |      | 8.2.2   | Testing                                              | 86 |

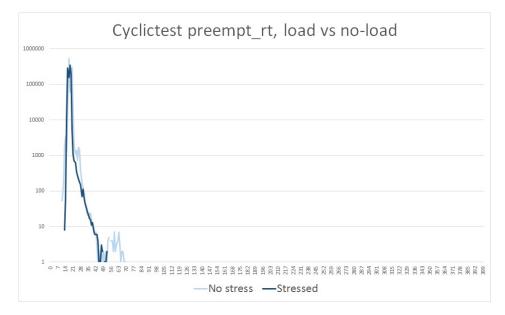

|    |            |         |            |                                                 | 87  |

|----|------------|---------|------------|-------------------------------------------------|-----|

|    | 8.3        | Cape    | response   | testing                                         | 92  |

|    |            | 8.3.1   | Setup .    |                                                 | 92  |

|    |            | 8.3.2   | Testing    |                                                 | 92  |

|    |            | 8.3.3   | Results    |                                                 | 93  |

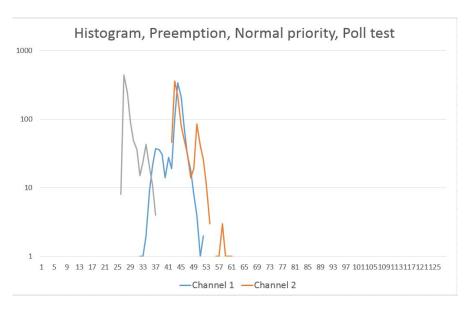

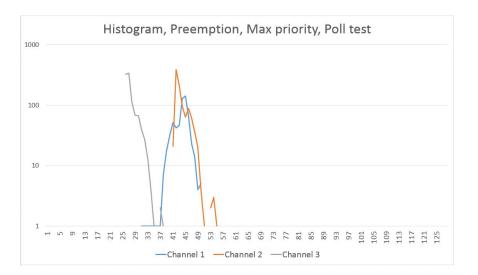

|    |            |         | 8.3.3.1    | Basic preemption Linux kernel                   | 93  |

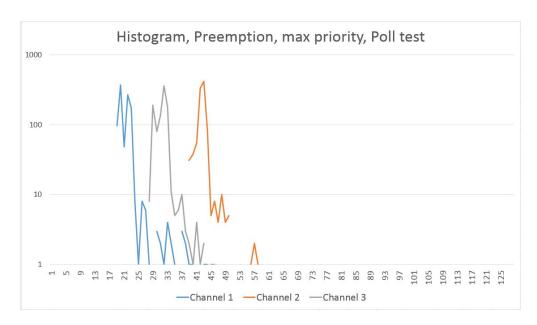

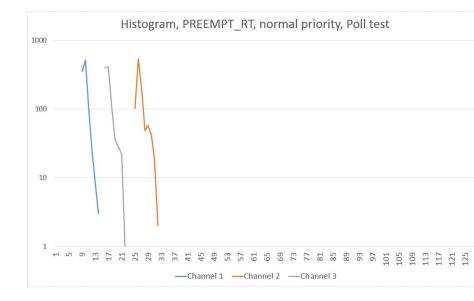

|    |            |         | 8.3.3.2    | PREEMPT_RT patched Linux kernel                 | 95  |

|    |            |         | 8.3.3.3    | FreeRTOS                                        | 97  |

|    |            |         | 8.3.3.4    | PRU                                             | 98  |

| 9  | Disc       | cussion | L          |                                                 | 99  |

|    | 9.1        | I/O la  | tency in ( | GNU/Linux                                       | 99  |

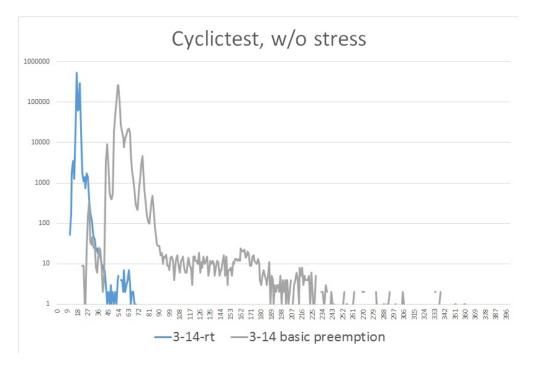

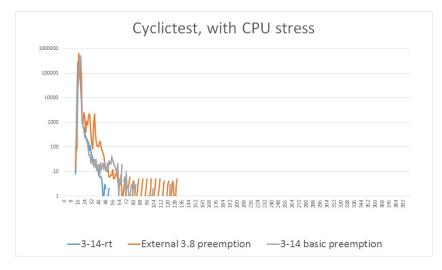

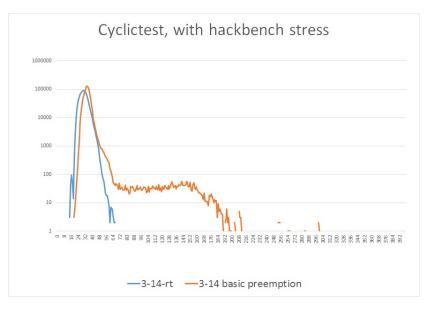

|    | 9.2        | Syster  | n latency  | y in GNU/Linux, PREEMPT_RT vs basic low-latency |     |

|    |            | preen   | nptable k  | ernel                                           | 100 |

|    | 9.3        | Worki   | ng with t  | he BeagleBone Black and ERT cape                | 102 |

| 10 | ) Con      | clusio  | ns and re  | commendations                                   | 105 |

|    | 10.1       | Concl   | usions .   |                                                 | 105 |

|    | 10.2       | Recon   | nmendat    | ions for future work                            | 105 |

| A  | Acro       | onyms   |            |                                                 | 107 |

| B  | Арр        | endix   |            |                                                 | 109 |

|    | <b>B.1</b> | Apper   | nded exte  | rnal storage                                    | 109 |

|    | B.2        | How t   | o boot th  | e different OS on BeagleBone Black              | 110 |

|    |            | B.2.1   | Booting    | Linux                                           | 110 |

|    |            |         | B.2.1.1    | Swapping the kernel                             | 110 |

|    |            |         | B.2.1.2    | Log in                                          | 110 |

|    |            | B.2.2   | Booting    | QNX and FreeRTOS                                | 110 |

|    |            |         | B.2.2.1    | QNX                                             | 111 |

|    |            |         | B.2.2.2    | FreeRTOS                                        | 111 |

|    | <b>B.3</b> | ERT c   | ode files  |                                                 | 112 |

|    |            | B.3.1   | defines.   | h and globals                                   | 112 |

|    |            | B.3.2   | main.c     |                                                 | 115 |

|    |            | B.3.3   | io.c       |                                                 | 122 |

### CONTENTS

| Bibliography |         |       |     |     |     |   |     |   |     |   |   |    |   |    |   |   |   |     |   |   |   |   |     | 129 |

|--------------|---------|-------|-----|-----|-----|---|-----|---|-----|---|---|----|---|----|---|---|---|-----|---|---|---|---|-----|-----|

| B.3.5        | timer.c | <br>• | ••• | ••• | ••• | • | ••• | • | ••• | • | • | •• | • | •• | • | • | • | ••• | • | • | • | • | ••• | 127 |

| B.3.4        | usart.c | <br>• | ••• |     |     | • |     | • |     |   | • |    | • |    | • | • | • |     | • | • | • | • | ••• | 124 |

# 1 Introduction

The definition of a real-time system is, "the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced"<sup>1</sup>. This area in computer science originated from a growing usage of computer systems in control applications. Until the 2000s most real-time systems were implemented through homebrew Operating Systems(OS) tailored to each specific problem. Today the popular solution is to use supported commercial or/and open source OS, and thus, reducing lead time in product development. However, the high quantity of both different hardware platforms and OS makes it necessary for designers to have good knowledge of real-time systems. The main purpose of this thesis will be to create an embedded test platform, which future students can use as a basis for their education into embedded and real-time systems.

## 1.1 Background

TTK4147 Real-Time Systems is a course lectured at NTNU. The purpose of the course is to educate the students in how to analyse and evaluate runtime requirements for embedded real-time systems. There are 11 exercises and one miniproject, which counts towards the final grade in the subject, these are practical tasks which often consists of coding for specific operation systems and platforms. However, several of these platforms are either outdated or run on virtual machines, and will thus, not necessarily represent what the students will experience in the outside the university.

<sup>&</sup>lt;sup>1</sup>Real-Time Systems[17]

## 1.2 Project goals

This thesis will create an embedded test platform compatible with several OS. We will through both examples and quantifiable test results present how the platform can be used by students. It will hopefully be as an education to for how to program for modern 32-bit embedded architectures, both in general and in terms of real-time principles. We will also take a closer look into one of the OS that will run on the platform, GNU/Linux, and especially the state of its kernel for use in hard real-time systems.

To achieve our goals the problem will be separated into several parts:

- Draw inspiration from similar work done in the past.

- Acquire and review the necessary background material.

- As far as the time permits, implement a solution.

- Evaluate the result and the choices made throughout the process.

## 1.3 Main contributions

The main contributions of this thesis are:

- The first openly available fully functional port of FreeRTOS to the BeagleBone Black single-board computer<sup>2</sup>.

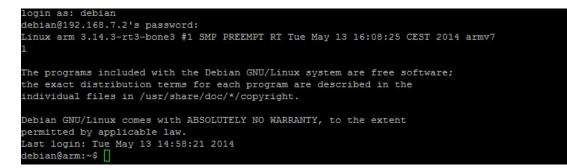

- A fully functional real-time patched Linux kernel version 3.14 for the BeagleBone Black.

- Created a new basis for the exercises in the course TTK4147 Real-Time Systems, for the Department of Engineering Cybernetics at NTNU.

2

<sup>&</sup>lt;sup>2</sup>Github repository: https://github.com/henfos/BBBFreeRTOS

## **1.4 Report layout**

This report contains 10 chapters, including this introductory chapter, acronyms and an appendix.

Chapters 2, 3 and 4 are chapters which will focus on theory. First, we will present real-time system topics, followed by theory concerning the hardware we chose to work with, before an OS chapter will explain topics specific to each OS, which are relevant to the software implementation. Chapter 5, 6 and 7 will then focus on the practical implementation carried out in this thesis. The hardware solution with the creation of the External Response Tester is shown first. Then we will show how GNU/Linux was set up and used, before we dedicate a chapter to showing the setup and usage of additional supported OS. Each of these chapters will end with a section discussing the implementation. Chapter 8 contains all the quantifiable results obtained during this thesis. The chapter also includes a description of how each experiment was set up, its testing process and results. We finish with a discussion of the results in chapter 9, which is followed by conclusions and recommendations in chapter 10.

The thesis is written with the expectation that the reader has basic knowledge of operating systems, programming and hardware. Thus, not all terms and topics will be fully elaborated and the reader is therefore encouraged to look up any unknowns. All figures are, unless otherwise noted, made by the author.

All the resources referenced in the thesis are located in the appended CD/USB drive, as well as a PDF version of the thesis. The structure of this appended drive can be found in Appendix B.1.

## **1.5 Literature and Related Work**

There has been no similar work done in the past at this campus, which we have used. Most of the theory on real-time systems topics was gathered from the TTK4147, Real-Time Systems, course material [27], [2]. Apart from these books information was gathered through various Internet sources and communities.

# 2 Real-time Systems

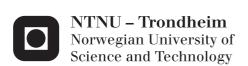

The introductory chapter stated that the correctness of a real-time system not only on the logical results of the computations, but also on the physical instant at which these results are produced. The study of real-time systems is important because many time critical operations has an inherent need for guaranteed performance. Examples of such operations include air traffic control systems and car safety features. These systems have computational deadlines that must be met, regardless of system load. Hence, predictability is the most important feature in these systems. When we are talking about real-time systems there are two different versions, soft and hard. Soft real-time systems are those which continue even if deadlines are not met, however the system's quality of service is degraded. Hard real-time are those systems where a failure to meet deadlines leads to catastrophic system failures. This thesis will have a focus on the latter systems, and real-time will carry the meaning of hard real-time unless otherwise specified. This chapter will present important topics concerning real-time systems, which will be relevant later on in the thesis. Topics that are presented in this chapter are for the most part covered by the curriculum of TTK4147, [27] and [2].

## 2.1 Interrupts

Creating a device that fulfills some real-time requirements would be easy if it never relied on any external information. Then all operations would be completely deterministic, and thus it would be straightforward to guarantee performance. However, most systems will work with one or more external resources, and this fact complicates matters significantly. There are several methods for communicating with external sources, a processor can for instance continuously poll for information.

Figure 2.1: Validity of system depending on response time in question to its deadline.

Polling is the process of continuously checking the external resources for some state change. However, this means that the processor will not be able to do anything else as it might miss an event. Instead of polling, we will therefore for the most part use interrupts.

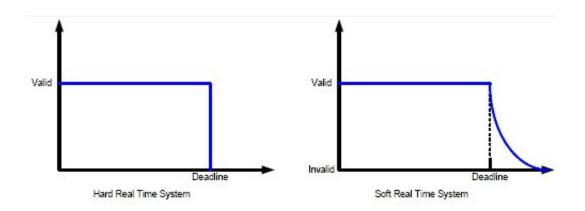

An interrupt is a signal (emitted by hardware or software), which is handled by the processor in a different way than an ordinary signal. Its purpose is to reduce wasting valuable time polling for a resource. Interrupts enables the processor to perform other tasks until an interrupt occurs. It is able to free the processor because it has the ability to break off normal code execution to run some specialized handler code. These specialized handlers are called Interrupt Service Routines (ISR). An example of is when waiting for some data on a bus. Instead of polling continuously to check if there is some new data, we will add an extra line on the bus, which the external resource will trigger when it posts data on the bus. This enables us, by connecting this line to a processors interrupt controller, to use all the processing power for whatever purpose, because at the instance the interrupt line triggers, the code will break normal code execution to run a handler, which receives the data. The break from normal code execution will create some overhead, however, this technique does by far still outweigh polling techniques. The programmer will ,however, have to be aware of high interrupt loads, as this can cause serious performance issues.

The use of interrupts does, as stated above, free the processor to perform other operations while waiting for some external device. However, it will affect the real-time capabilities based on the number of interrupts sources, as well as the already stated context switching overhead and the size of the interrupt handler. This makes it difficult for complex systems to meet the requirement of guaranteed performance. For example, it may be impossible for a complex operating system to specify any worst case latencies.

Figure 2.2: Processor handling of different interrupt sources. Courtesy of [1]

7

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/File:Interrupt\_Process.PNG

## 2.2 Latency

Latency is the time interval between a request is made, until it is serviced.

#### **Interrupt latency**

Interrupt latency is the time from when an interrupt is generated to when the source of the interrupt is serviced. The minimum interrupt latency depends on the hardware in use, more importantly the interrupt controller circuit. The maximum interrupt latency depends on software, and in a non-RTOS it can be difficult to gain any knowledge on this time interval. There is also the factor that most processors will allow interrupts to be turned off, this is to protect certain critical code sections. However, with the use of a RTOS we can guarantee that the interrupt latency will never exceed a predefined maximum.

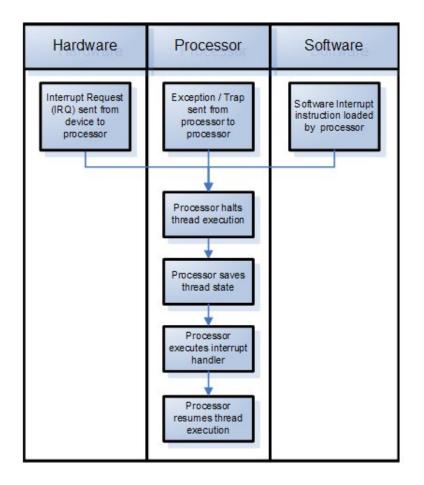

*Figure 2.3: Interrupt latency is only one of the factors in the cost of handling an interrupt. Courtesy of* [1]

The interrupt latency ( $T_n$  in Figure 2.3) and the interrupt termination time ( $T_{iret}$  in Figure 2.3) are the two factors which are determined by hardware and the OS. The interrupt processing time ( $T_{int}$  in Figure 2.3) is the time it takes to run the code in the interrupt service routine (ISR). This code will often set some flag such that the

<sup>&</sup>lt;sup>1</sup>http://www.qnx.com/developers/docs/qnx\_4.25\_docs/qnx4/sysarch/microkernel. html

#### 2.3. SCHEDULING

operations requested by the interrupt can be done in normal code execution. Other times, however, this code can be rather heavy, and thus, significantly increase the overall interrupt cost.

#### I/O latency

I/O latency is the full time from a process asks to do some I/O operation, until it is actually conducted. When barebone programming on 8-bit microcontrollers (MCUs), like the Atmel AVR, the programmer will mostly have direct control over I/O. Thus, there will only be bound, deterministic, hardware latency. However, when introducing a complex OS like GNU/Linux then I/O control can be hidden through several layers, thus, these systems are prone to more significant I/O latency.

#### 2.2.1 Worst case latency and boundedness

The total worst case latency for a task is a key property when evaluating real-time characteristics of a system. Further, it is important that if the worst case latency can not be mathematically proven, that the empirical results can indicate an upper bound on latency.

#### 2.2.2 Latency vs throughput

Throughput is the amount of data transferred or processed in a specified amount of time. Latency and throughput are two terms that are often confused and sometimes used interchangeably. The reality is that low latency often comes at the cost of less throughput. Low latency requires the OS to frequently break normal code execution to check if there is a request, from either software or hardware, that needs to handled. Breaking from normal code execution creates overhead, and this overhead subtracts of the systems total throughput. To clarify, a responsive system is not the same as a high performance system.

# 2.3 Scheduling

In the event of one single task with given processing time, it is straightforward to evaluate if it meets real-time requirements. However, often we have several tasks running concurrently. The processor then has to context switch between the differents tasks. Scheduling is the method by which a task is given access to system resources. The choice of scheduler is both an important and difficult one. For example, a advanced scheduler may enable a lot different lower priority tasks to run, and still keep requirements for the higher priority tasks. This may however cause larger overhead, which reduces system throughput capabilities.

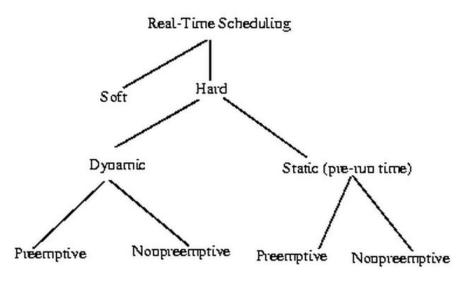

Figure 2.4 shows the different categories of schedulers. This thesis is as earlier stated focused on hard real-time problems. Static schedulers are schedulers with priorities which are fixed pre-run time, while dynamic has the ability of changing the priorities of each task during run-time. Non-preemptive (or co-operative) schedulers are schedulers where once a task is given processing time, it will run until itself decides to yield, or uses its time-slice. Preemptive schedulers, on the other hand, allow a task to force a context switch whenever it is ready to run, and there is a lower priority task which currently is running.

Figure 2.4: Different groups of schedulers. Courtesy of [1]

#### 2.3.1 Priorities

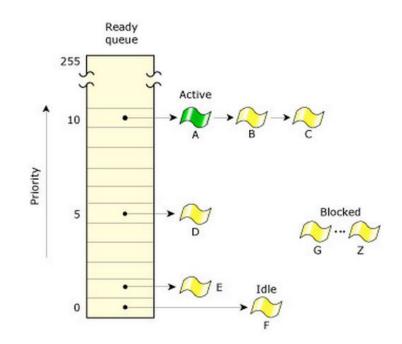

Real-time systems these have multiple threads or tasks. Some may perform display and housekeeping operations, others are tasked with crucial control operations. With the use of priorities we can make sure that the lesser important operations do not interfere with the crucial ones. Priorities are often a simple number which tells the scheduler which position in the ready queue it should take, se Figure 2.5. They can also be static or dynamic. Static priorities are set pre-runtime and can not be changed. Dynamic priorities however, give the system the possibility to change the priority in runtime, which often can be very useful.

<sup>&</sup>lt;sup>1</sup>http://users.ece.cmu.edu/~koopman/des\_s99/real\_time/

<sup>&</sup>lt;sup>2</sup>http://www.qnx.com/developers/docs/6.3.0SP3/neutrino/prog/images/readyq.jpg

*Figure 2.5: Tasks waiting in different ready queues depending on priority, while other tasks are blocked. Courtesy of [2].*

#### **Priority inversion**

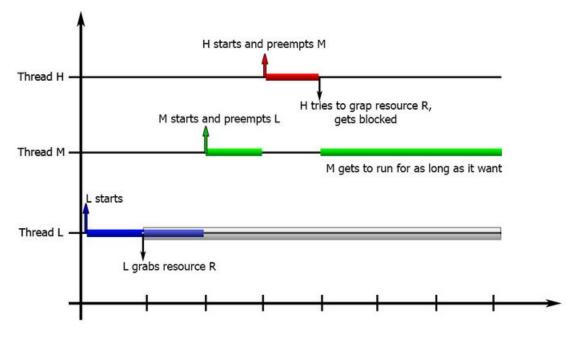

Priority inversion is a scenario where a high priority task is not able to run due to involvement by a lower priority task. Take the scenario with three threads, one with high (H), medium (M), and low (L) priority. There exists also a resource (R) used by the H and L threads. Figure 2.6 shows a scenario where thread H is not able to run due to thread L controlling the needed resource R. Further, since there is a thread M running, thread L is not able to finish its operations with R. This makes it impossible to say when thread H will be able to run again, something that should not happen since H has the highest priority. This is an example of priority inversion.

This is a classic problematic scenario in real-time system, and there are several ways to solve this problem. However, there have been several cases where this have been forgotten and lead to serious errors through starvation of higher priority tasks. Most famous is the Mars lander "Mars Pathfinder" incident <sup>1</sup>. When the rover started to gather meteorological data it did so through a low priority task, its data was then published on an information bus. Another high priority task, which ran bus management also frequently accessed this information bus. The low priority task

<sup>&</sup>lt;sup>1</sup>What really happened on Mars? [16]

Figure 2.6: Example of priority inversion.

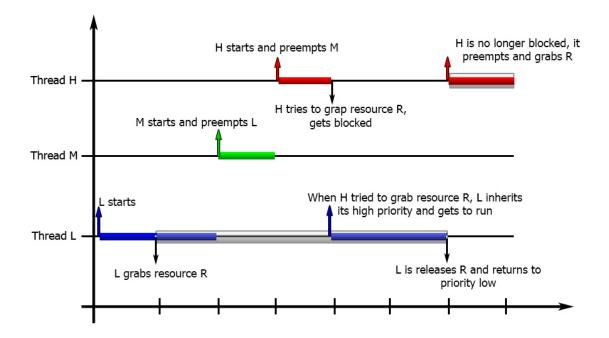

would then control the bus resource like in Figure 2.6, and a medium priority task would preempt it with the consequence of keeping the high priority task blocked when it needed the bus. A watchdog timer would then go off, which caused a system wide reset. The rover ran a version of VxWorks, a RTOS which is created by Wind River. A VxWorks mutex object, like the one used to lock access to the information bus, accepts a boolean parameter that indicates whether priority inheritance should be performed by the mutex. Priority inheritance causes the low priority task to temporarily be assigned the priority of the highest waiting priority task while holding the resource. Thus, the medium priority task can not preempt and prevent the low priority task from finishing. Once the low priority task releases the resource it returns to its original low priority and the high priority task waiting preempts it, see Figure 2.7. By uploading a small program, which changed this boolean parameter of the information bus mutex, no further system resets occurred.

There are several other solutions to this problem, but the important thing is to know about the scenario since there is no foolproof method to predict the situation.

Figure 2.7: Solution to problem by using priority inheritance.

# 3 | Hardware

The main criteria for choosing the hardware platform was that it would be both modern, and versatile. This was based on problem formulation 1.2, which states that the test platform would be used in education for learning embedded and real-time principle. Thus, it was important for the architecture to support multiple OS, such that all the OS already used in the course TTK4147 exercise program, would be supported by this new platform. Thus the choice fell, on using the popular ARM architecture. This basis would be complemented by a preprogrammed external unit, this would be used as a benchmarking and analysis tool. This interacting unit was chosen to be built around an 8-bit Atmel AVR MCU, due to previous experience with such units.

This chapter will present the different architectures and hardware, which are relevant for this thesis.

## **3.1** ARM

The ARM architecture was first introduced in the mid 1980s. In 1985, VLSI produced the first ARM silicon, known as ARM1. ARM is an IP company, which does no manufacturing. Their primary business is selling IP cores, in particular chip layout designs. The licensees then base their MCUs and CPUs on these ARM cores. ARM designs are based on reduced instruction set computing (RISC) architecture, as opposed to a complex instruction set computing (CISC) architecture. The difference will be presented in the next subchapter. The ARM architecture had a 60% market share, as of 2012 in the embedded processor market<sup>1</sup>, a number which is expected to grow to 68% in 2016. ARM offers a powerful ecosystem, where their cores range from

<sup>&</sup>lt;sup>1</sup>ICD: ARM market share [12]

costly high-end 64-bit cores to cheap low-powered cores. These low-powered cores have in later years been steadily attracting more traditionally 8/16-bit projects over to ARM. They also offer a full range of development tools and software.

#### 3.1.1 ARM vs x86

The best known computer architecture today is the x86, the x86 has since 2006 been the de facto processors in desktop and laptop computers. In 2006 Apple moved, as the last of the large personal computer companies, from PowerPC to the x86 architecture. The x86 is in contrary to ARM based on CISC architecture. CISC enables a single instruction to execute several low-level operations. CISC attempts to minimize the number of instructions per program, while RISC reduces cycles per instruction at the cost of the number of instructions per program. The x86 has historically had greater emphasis on speed and performance than power consumption, and therefore not been a serious contender in the embedded market. The higher power consumption comes in part from the large overhead needed to maintain the large ROMs needed for CISC. However, Intel is making strides to gain a foothold inside this market. Their latest Atom low power architecture<sup>2</sup> looks to be ARM's first serious contender in the mobile embedded market<sup>3</sup>. This could be the first push to create very low powered x86 processors, ARM does as it stands today, have a much larger ecosystem when it comes to the embedded market.

#### 3.1.2 Other architectures

There are several other architectures available for the embedded market, including the Atmel AVR, the Microchip PIC, the Texas Instrument MSP430, and several others. Most of these are 8 or 16-bit specialists, and their 32/64-bit architectures are not as popular as their less advanced counterparts.

## 3.2 BeagleBone Black

We needed a versatile base to enable the running of several OS on the same testing solution. As explained at the start of this Chapter, the ARM architecture was selected

<sup>&</sup>lt;sup>2</sup>Bay Trail, launched Q3 2013

<sup>&</sup>lt;sup>3</sup>The Bay Trail tested [26].

#### 3.2. BEAGLEBONE BLACK

to create this platform. The choice of hardware therefore fell on the BeagleBone Black single-board computer, seen in Figure 3.1. This board has a 1GHz ARM Cortex-A8 processor produced by Texas Instruments. It is a popular open-source community supported development platform, which provides a lot of resources to support development. This board features:

- AM3358 1GHz ARM Cortex-A8

- 512MB DDR3 RAM

- 2GB 8-bit eMMC on-board flash storage

- 3D graphics accelerator

- NEON floating-point accelerator

- 2x PRU 32-bit microcontrollers

- USB, Ethernet, HDMI, 2 x 46 pin headers

Figure 3.1: The BeagleBone Black. Courtesy of [1].

<sup>&</sup>lt;sup>1</sup>http://beagleboard.org/Products/BeagleBone+Black

#### 3.2.1 The AM3358 processor

The BeagleBone Black has a AM3358 Sitara ARM Cortex-A8 processor. The ARM Cortex-A8 is a processor core implementing the ARMv7-A 32-bit instruction set architecture, and it runs at 1GHz. The Cortex-A8 is one of the most widely used cores in mobile devices, and Texas Instruments recommends it as "Ideal for home automation, industrial automation, enterprise/educational tablets, portable navigation devices and networking".

#### 3.2.1.1 The exception vector

ARM microprocessors are able to respond to an interrupt with a context switch, this breaks normal code execution to run some special handler routine. All these interrupts are on ARM processors called exceptions (including hardware reset). When an exception occurs, the processor saves the context and then jumps to a vector table in memory, which contains addresses to where the exceptions should be handled. This is the Exception Vector Table (EVT), and it includes Reset, Data Abort, Prefetch Abort, Undefined Instruction, Normal Interrupt (IRQ), and Software Interrupt (SWI) exceptions.

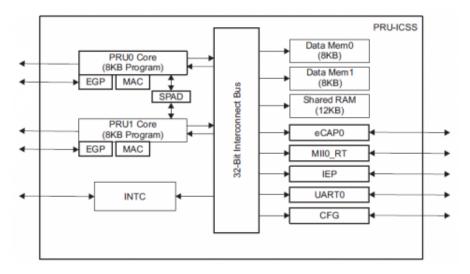

#### 3.2.2 Programmable Realtime Unit

The MCU chip comes with a second generation Programmable Realtime Unit (PRU) subsystem, which features a dual 32-bit RISC core, 8KB data memory, 8KB instruction memory and 12KB shared RAM, see Figure 3.2. Its instruction set is small and deterministic, which means all instructions are executed in a single cycle, except accessing external memory. This is a subsystem integrated separately from the ARM core, allowing independent operation. The PRU can be set up by the main Cortex core, and the BeagleBone community has written a package which creates PRU support for GNU/Linux systems. The package includes the PRU assembly complier, *pasm*, and its source code. It also provides a userspace driver to load applications. Documentation and example applications are also included. The package can be found on github  $^4$ .

<sup>&</sup>lt;sup>4</sup>Am335x\_pru\_package, [18]

<sup>&</sup>lt;sup>1</sup>The PRU reference guide, http://mythopoeic.org/BBB-PRU/am335xPruReferenceGuide.pdf

Figure 3.2: The PRUSSv2. Courtesy of [1].

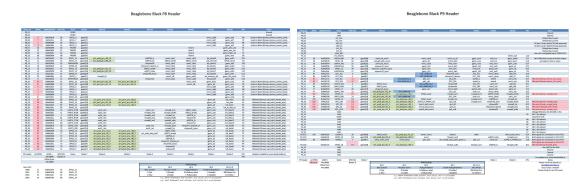

#### 3.2.3 The AM3358 Pin Multiplexer (Pinmux)

The AM3358 chip has fewer pins on its package than the internal logic provides functionality. The chip therefore provides a configurable pin multiplexer, which gives the user a choice to what logic should be available. Each pin can be set to one out of eight modes. Some pins have to be set in some predetermined mode to initialize the board, however, a lot of pins have a range of modes providing the developer with flexibility. Figure 3.3 is included to illustrate the vast number of different modes, which are choosable for the BeagleBone Black headers. The pinmux can be configured at boot, and at normal runtime.

*Figure 3.3: The different possible modes for the BeagleBone black header pins. Courtesy of Derek Molloy* [1].

## 3.3 Atmel 8-bit AVR

The Atmel AVR architecture was developed by two students<sup>5</sup> at the Norwegian Institute of Technology (now Norwegian University of Science and Technology - NTNU)<sup>6</sup>. These students further developed the architecture when the technology was acquired by Atmel. Their 8-bit MCUs deliver high speed (1 MIPS/MHz), a large range of pins (6-100), and a large range of peripheral set options. Combined with free and inexpensive development tools the AVR has gained a large user base in the 8-bit MCU market.

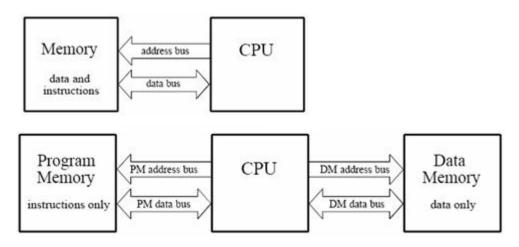

### 3.3.1 Modified Harvard Architecture

The Atmel AVR MCU is a harvard architecture machine<sup>7</sup>. This is one of two main types of digital computer architectures. The characteristic of the Harvard Architecture is that it maintains a distinct separation between code and data spaces. The alternative architecture is the von Neumann architecture, which has shared signals and memory for code and data. The difference between these are that the harvard architecture is able to access memory and data simultaneously, enabling the possibility of completing an instruction in a single cycle. However, the code memory of the harvard architecture is typically read-only memory, which makes it impossible for program contents to be modified by the program itself. This is something easily done by the von Neumann Architecture where all the memory is read-write, as seen in Figure 3.4.

Modified harvard architectures allows for the contents of its instruction memory to be accessed just as if it was data. This enables the architecture to support high performance concurrent data and instruction memory access, while also supporting tasks like loading a program from disk storage as data and then executing it. The AVR adopts such a modified version of the harvard architectures through special instructions.

<sup>&</sup>lt;sup>1</sup>GPIO Programming on ARM Embedded Linux, http://derekmolloy.ie/beaglebone/ beaglebone-gpio-programming-on-arm-embedded-linux/

<sup>&</sup>lt;sup>5</sup>Alf-Egil Bogen and Vegard Wollan

<sup>&</sup>lt;sup>6</sup>The Story of AVR [1]

<sup>&</sup>lt;sup>7</sup>Data in Program Space [21]

*Figure 3.4: The main difference between the Harvard (bottom) and von Neumann (top) arcitecture.*

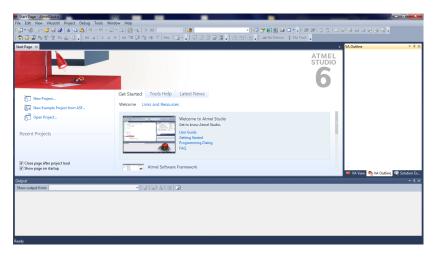

### 3.3.2 Atmel Studio and the JTAG ICE

Atmel Studio (seen in Figure 3.5) and the JTAG ICE (seen in Figure 3.6 are development tools enabling programming of the Atmel AVR MCUs. The Atmel Studio is a Integrated Development Environment (IDE) created by Atmel for developing and debugging assembly or C/C++ applications for Atmel MCUs. It is free of charge and is integrated with the Atmel Software Framework (ASF). ASF provides a large collection of embedded software to keep developers from reinventing the wheel.

Figure 3.5: The graphical user interface of Atmel Studio.

The JTAGICE3 is a development tool for debugging and programming Atmel MCUs. It supports JTAG, aWire, SPI and PDI interfaces, has hardware and software programmable breakpoints, and is powered by and interfaces with the host computer via USB.

Figure 3.6: The JTAGICE3.

## 3.4 Saleae Logic

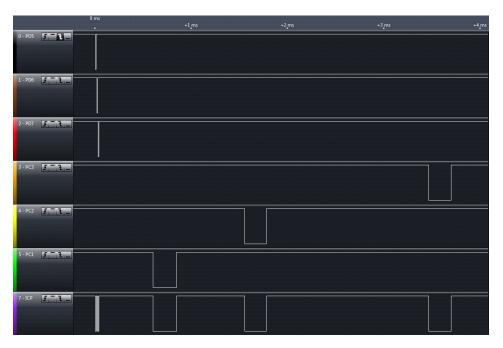

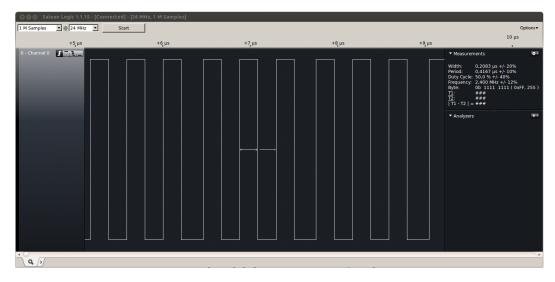

Saleae Logic (seen in Figure 3.7) is a logic analyser used to record, view, measure and interpret digital signals, featuring 8 channels and 9 probes, and with a sampling frequency up to 24MHz. It supports both newer GNU/Linux distributions and Windows, which makes it highly flexible. It is a handy tool in both prototyping and to document results, and is used throughout this thesis.

Figure 3.7: The logic analyzer used throughout this thesis.

# 4 **Operating Systems**

As stated in the introduction of Chapter 3, the ARM platform was chosen for its modernity and versatility. These are also the reasons for focusing mostly on the GNU/Linux OS. FreeRTOS and QNX will, however, also be presented as alternatives to GNU/Linux, albeit as more specialized Real-Time OS (RTOS). The exercise program of the course TTK4147 utilizes all three OS in some manner, either through virtual computers or different hardware platforms. By enabling support of these on a single target we will streamline the educational resources.

This chapter will present the three OS which will be compatible with the hardware platform, and are relevant for this thesis.

# 4.1 GNU/Linux

The presentation of the Unix/GNU/Linux is based on <sup>1</sup>. The first production of Unix was installed in early 1972 and was by the start of the 1980s a leading force in commercial startups. It had achieved its market position through its popularity in academic circles. However, since Unix was a commercial product they wanted to prohibit illegal copying and redistribution. Therefore, as most manufacturers, they stopped distributing source code and began using copyright and restrictive licenses. This caused free software activist and Harvard graduate Richard Stallman to launch the GNU Project in 1983. GNU is a recursive acronym meaning "GNU's Not Unix", and its aim was to create a completely free Unix compatible "Unix-like" OS. By 1991 they had completed most mid-level portions of the OS. However, the team struggled to make progress with their kernel, GNU Hurd. Due to an ambitious design there were severe implementation problems. Then, in 1991 Linus Torvalds used the GNU's

<sup>&</sup>lt;sup>1</sup>2.1. History of Unix, Linux, and Open Source / Free Software[31]

development tools to produce his Linux kernel, originally only intended to work on the Intel 386(486) processors. However, Linux quickly became a popular community driven project with Torvalds as chief architect. The existing programs from the GNU project where then ported, resulting in a complete computer OS composed entirely of free software.

Today, there are several GNU/Linux distributions, were an OS is built on top of the Linux kernel. These range from distributions for the most powerful supercomputers, to the smallest embedded systems.

# 4.1.1 Naming

There is some naming controversy regarding Linux; should it refer to the kernel only, or to the entire operating system? "Linux" has become a far more widespread name than its partner, GNU, and this even though popular distributions like Ubuntu uses almost equal amounts of code from both (8-9% of total LOC<sup>2</sup>). This thesis will however use the term GNU/Linux as a general term to all OS based of the Linux kernel, quoting Richard Stallman "*people tend to think it's all Linux, that it was all started by Mr. Torvalds in 1991, and they think it all comes from his vision of life, and that's the really bad problem*".

# 4.1.2 Kernel Architecture

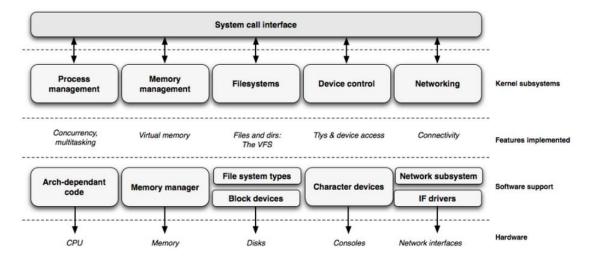

Linux is a monolithic kernel, this can be observed in Figure 4.1, and will be elaborated on later. The GNU/Linux OS is therefore somewhat more complex than other OS that will be used in this thesis project. Device drivers and kernel extensions run in kernel space with full access to the hardware. The kernel does support the loading of kernel modules in runtime. Device drivers can thus be loaded or unloaded while running the system. As the Linux kernel is also a file based system, user applications can interact with hardware through files. Device drivers are mapped to the */dev* and/or */sys* directories, while processes are mapped to the */proc* directory. The Linux kernel supports:

- True preemptive multitasking

- Virtual memory

24

<sup>&</sup>lt;sup>2</sup>How much GNU in GNU/Linux [6]

#### 4.1. GNU/LINUX

- Shared libraries

- Demand loading

- Memory management

- TCP/IP

- Threading

Figure 4.1: Functions of the Linux kernel. Courtesy of [1].

# 4.1.3 Kernel and User space

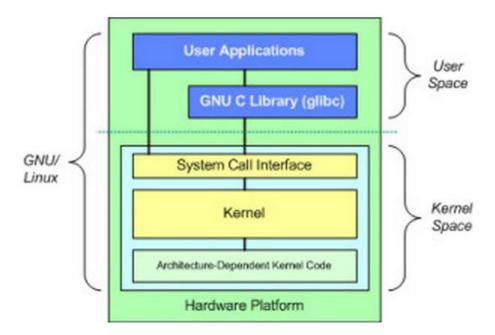

A GNU/Linux OS can be divided into two levels - User space and Kernel space, as illustrated in Figure 4.2. The OS divides the virtual memory between these two modes, thus protecting data and functionality from faults. The purpose of the kernel space is to run the kernel and most device drivers. Device drivers are programs which interacts with some device attached to the processor. The kernel space creates a stable foundation for the user space, which runs the normal user processes. The user space processes can only access a small part of the kernel via the system interface.

<sup>&</sup>lt;sup>1</sup>http://knowstuffs.wordpress.com/tag/kernel-architecture/

Figure 4.2: Kernel and user space and the different levels of each. Courtesy of [1].

# 4.1.4 Microkernel vs Monolithic kernel

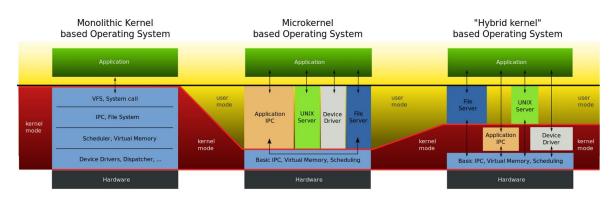

A microkernel differs from a monolithic kernel in that it only the most basic functions are available from system calls, the kernel is broken down into separate processes, known as servers. This structure is implemented in many real-time operating systems. The practical purpose of using a microkernel is to sacrifice some performance for reliability. In a monolithic structure, a service is obtained by a single system call. In a microkernel structure a service is obtained through Interprocess Communication (IPC), this causes overhead due to the required context switch. However, since the microkernel is divided into different servers, if one fails, the other servers will work efficiently. In critical operations as control systems often are, this is an extremely important feature.

The idea of microkernels did not breakthrough until the end of the 1980's. Windows and GNU/Linux (and most UNIX like) OS are therefore in essence monolithic. Since the introduction of microkernels, most monolithic kernels have become more of a hybrid solution, see Figure 4.3. However, since they are in their core still a monolithic kernel the problem with this structure remains. These kernels needs to be completely foolproof or else the user will experience complete system crashes, an experience

#### 4.1. GNU/LINUX

made famous by the infamous Windows bluescreen.

*Figure 4.3: Figure showing how a microkernel differs from the standard monolithic kernel. Courtesy of [1].*

## 4.1.5 Linux Standard Base

Linux Standard Base (LSB) is a standardized method for creating software system structure. LSB is a superset of the Portable Operating System Interface (POSIX). POSIX is an IEEE standard<sup>3</sup> first released in 1988, with the latest revision in 2008. The standard contains specifications for Unix-like operating system environments. It is implemented as an extra layer between the OS and applications, thus creating code compatibility between OS. It includes specifications for the command line, scripting, user-level programs, services, program-level I/O services and threading. LSB extends this specification with its stated goal being: *"to develop and promote a set of open standards that will increase compatibility among Linux distributions and enable software applications to run on any compliant system even in binary form. In addition, the LSB will help coordinate efforts to recruit software vendors to port and write products for Linux Operating Systems.<sup>4</sup>"*

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/File:OS-structure2.svg

<sup>&</sup>lt;sup>3</sup>1003.1-2008 - Portable Operating System Interface (POSIX(R))[13]

<sup>&</sup>lt;sup>1</sup>http://knowstuffs.wordpress.com/tag/kernel-architecture/

<sup>&</sup>lt;sup>4</sup>The Linux foundation, Linux Standard Base[7]

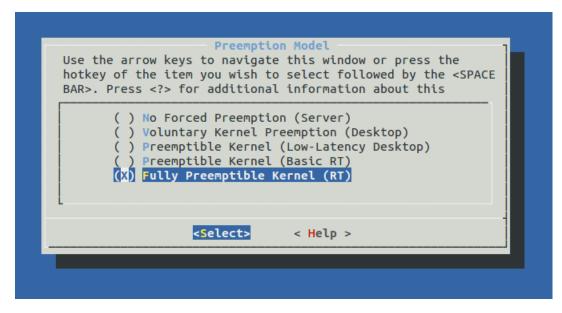

### 4.1.6 Preemption and real-time viability

This thesis investigates themes relevant to real-time systems, for GNU/Linux to be fully relevant in this category implies that preemption is a necessity. Towards Linux kernel version 2.6 preemption had moved from availability only in user space to the possibility of interruption of kernel code. However, there were still sections in the kernel code, which could not be preempted. The PREEMPT\_RT patch may be a solution. This patch supports full preemption of critical sections, by making in-kernel locking-primitives spinlock and rwlock pre-emptible. The drawback is that some device drivers can stop functioning because they are dependent on non-pre-emptible sections, which now are not possible. The creation of non-pre-emptible sections is still possible, but only thrugh using raw spinlocks. However, this should only be used in bounded situations, as Steven Rostedt, maintainer of the stable version of the PREEMPT\_RT patch explains: "If there's an unbounded latency that's in PREEMPT\_RT, we consider that a bug, and work hard to fix it.<sup>5</sup>.". Rostedt also specifies that the patch is to provide GNU/Linux with something very close to a hard real-time OS: "I will be the first to tell you that I wouldn't want the PREEMPT\_RT kernel to be controlling whether or not the plane I'm flying on crashes. But it's good enough for robotics, stock exchanges, and for computers that have to interface with hard real-time software. PREEMPT RT has been used on computers that have gone into space." The complexity of Linux makes PREEMPT\_RT a hardening of Linux real-time capabilities, but it's far from mathematically provable.

## 4.1.7 Scheduling

To support real-time scheduling the kernel contains three scheduling classes named SCHED\_FIFO (first-in-first-out), SCHED\_RR (round-robin) and SCHED\_DEADLINE, which implements earliest deadline first.

#### 4.1.7.1 Priorities

The PREEMPT\_RT patch makes several changes to interrupt handling, locking mechanism, and also the scheduler. As mentioned in the last section, the kernel implements the scheduling classes, and these implement a strict priority order. The

<sup>&</sup>lt;sup>5</sup>Steven Rostedt, interview [3]

#### 4.1. GNU/LINUX

priorities vary from 0 to 99, with inverted priority values, i.e. 0 is the highest priority. While in the standard Linux kernel, process priorities are dynamic. The scheduler keeps track and adjusts a process priority periodically.

## 4.1.8 Device Tree

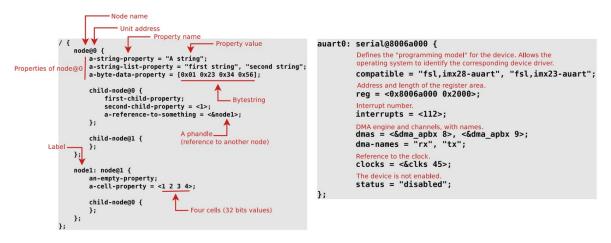

The growing popularity of SoCs and Linux for ARM devices created some problems in the early 2010s. Each SoC or board had its own hardware-specific code, this caused major problems as drivers, which could be shared with other SoC families, had been put under board-specific code. The duplication of code spawned a famous Linus Torvalds quote: "Gaah. Guys, this whole ARM thing is a f\*cking pain in the ass. " in 2011<sup>6</sup>. This spawned a project to build a single Linux kernel, which would boot on different ARM SoCs. The project made use of device trees for describing hardware to solve this problem. A device tree is a data structure (seen in Figure 4.4), which enables the description of most board design aspects, thus enabling hardware specification to be read at boot time and dynamically configure the device drivers. The Device Tree description includes:

- The number and type of CPUs.

- Base addresses and size of RAM.

- Busses and bridges.

- Peripheral device connections and GPIO set up.

- Interrupt controllers and IRQ line connections.

# 4.1.9 General-purpose input/output Control

The move from 8-bit architecture to a more advanced 32-bit architecture will almost always also induce a move to a more advanced OS like GNU/Linux. I/O operations will then be hidden from barebone programming. There are basically two ways to control a General-Purpose Input/Output (GPIO) pin from userspace in GNU/Linux: memory mapping or sysfs. And if we want to use a GPIO pin as an interrupt source,

<sup>&</sup>lt;sup>6</sup>Linus Torvalds, Linux kernel mailing list [29]

#### CHAPTER 4. OPERATING SYSTEMS

Figure 4.4: General device tree structure and an example of implementation.

we also have to options. Either use polling combined with sysfs files in userspace or by writing a kernel module.

#### 4.1.9.1 Sysfs

Sysfs is a virtual file system provided by Linux. It describes the devices known to the system and is by default mounted on */sys*. The purpose of each file is to pass on information to the kernel so that it can perform a specific command. Platforms which implement the abstraction layer *gpiolib* provides files mounted on */sys/class/gpio* for interacting with the GPIOs in userspace. Linux provides a program called echo for displaying a line of text<sup>7</sup>, it can also push be used to push a line of text into a file. Echoing a pin number to */sys/class/gpio/export* or *..unexport* will expose or remove a pin from userspace. For example, *echo 10 > export* will export the control of pin 10 to userspace and create a file */sys/class/gpio/gpio10* which can be given commands to. Available commands are:

- *direction*, with arguments in or out. For if the pin should be input or output.

- *value*, with arguments 0 or 1. Low or high output.

- *edge*, with arguments none, rising, falling or both. These are arguments for selecting the signal edge for using a gpio pin with the polling function poll.

<sup>&</sup>lt;sup>7</sup>http://linux.about.com/library/cmd/blcmdl1\_echo.htm

#### 4.1. GNU/LINUX

• *active\_low*, with arguments 0 or 1. Nonzero value will invert the value attribute for both reading and writing.

#### 4.1.9.2 Memory mapping

Memory mapping associates a range of user-space addresses to device memory. Using the POSIX-compliant  $mmap()^8$  we can open /dev/mem and map a device's physical address space into a process's virtual address space. Thus, by reading or writing to that assigned address range, we are actually accessing the device. Memory mapping can therefore provide quick and easy access to a device for performance-critical application. It does, however, require the application to run as superuser, which can cause trouble if the programmer makes a mistake in the addressing. There are no possible interrupt handling, and no protection against simultaneous access.

#### 4.1.9.3 Kernel module

When trying to use a GPIO as an interrupt source, the most direct way is to do it through the kernel and implement a kernel module. Modules are pieces of code that can be loaded and unloaded into the kernel upon demand, and are often device drivers<sup>9</sup>. This makes it is possible to extend the features of the kernel without the need to reboot or recompile. The code running in the kernel can map I/O to interrupts, and register handlers to those interrupts, among a lot of other features.

#### 4.1.9.4 Polling

Most interrupt handling gets carried out in the kernel. However, by using a kernel driver in combination with the sysfs interface and poll, we can also do I/O event driven operations in user space.

The *poll()* system call can block a process until any of a given set of file descriptors becomes available for reading or writing. As we earlier presented 4.1.9.1 we mentioned how it GPIOs could be controlled through such file descriptors. We can then create an event driven GPIO driver in user space by, exporting pins, setting them to be edge triggered, opening their files and passing the file descriptors to a *poll()* call.

<sup>&</sup>lt;sup>8</sup>Linux Device Drivers, chapter 13 [25]

<sup>&</sup>lt;sup>9</sup>The Linux Kernel Module Programming Guide, Chapter 1 [25]

## 4.1.10 Distributions

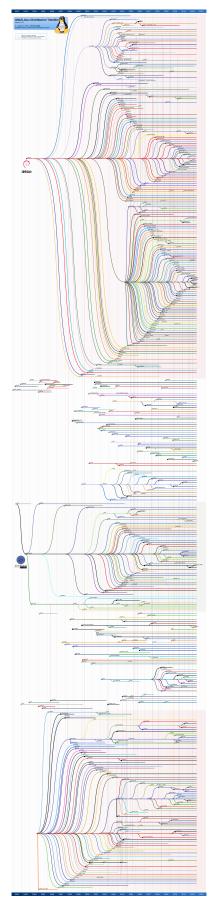

As previously stated a GNU/Linux distribution is an operating system built on top of the Linux kernel. Distributions often include some Package Management System (PMS), where each package contains a specific application or service. They include compiled code, with installations and removal handled by the PMS, thus packages which are dependent of other packages will be detected, thereby easing the installation process. The PMS will also handle upgrading packages and continually check that all the dependencies are fulfilled. The distributions typically contain a range of packages, and the system administrator can also add packages not included in the distribution. There is a huge number of distributions fitting most imaginable applications. There are commercially backed distributions like Fedora and Ubuntu, and entirely community-driven distributions, such as Debian and Arch Linux. Figure 4.5 shows the distribution timeline from 1993 until today. Each line represents its own distribution of GNU/Linux. The figure is not meant to be closely studied, but instead provide an illustration to the vast size of the GNU/Linux community.

# 4.1. GNU/LINUX

Figure 4.5: General Device Tree structure and a example of implementation.

# 4.2 QNX

QNX Neutrino <sup>10</sup> is a real-time operating system (OS), and its primary market target is embedded systems. QNX was developed in the early 1980s as a commercial Unix-like OS. However, instead of an monolithic kernel, QNX implements a microkernel. The OS can be used in a large variety of platforms including x86, PowerPC, ARM and many others.

# 4.2.1 Neutrino microkernel

The microkernel implements core POSIX features along with an IPC message-passing service. As the implementation is a microkernel, then the file system, networking and similar functions are provided by optional servers which can be configured at compilation. The kernel is primarily coded in C, and according to QNX, performance goals are achieved by: *"successively refined algorithms and data structures, rather than via assembly-level peep-hole optimizations"*. QNX Neutrino is a fully preemptible OS, and the entire OS is based upon kernel calls to support<sup>11</sup>:

- Threads

- Message passing

- Signals

- Clocks

- Timers

- Interrupt handlers

- Semaphores

- Mutual exclusion locks (mutexes)

- Condition variables (condvars)

- Barriers

<sup>&</sup>lt;sup>10</sup>http://www.qnx.com/products/neutrino-rtos/neutrino-rtos.html <sup>11</sup>The QNX microkernel [22]

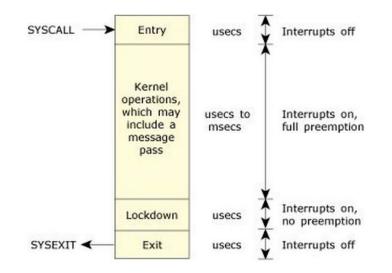

Fully preemptible means that even kernel operations as message passing can be preempted and resumed with no harm done. However, within a system call there are some minor critical sections, which turns off interrupts (see Figure 4.6). The minimal complexity of the kernel helps as it makes it possible to place an upper bound on the longest non-preemptible code path. Interrupts and preemption are disabled in very brief intervals (hundreds of nanoseconds).

*Figure 4.6: Example that show when a system call is preemptible, and when interrupts are on/off. Courtesy of [22].*

## 4.2.2 Threads and processes

Any given process always contains at least one thread, and can be thought of a "container" for threads through defining an address space, which all of the threads share. It is noteworthy to mention that even though all threads in a process share address space, thus each thread are allowed private data. This private data can for instance be the thread ID protected within the kernel, or that each thread has a stack for its own use.

#### 4.2.3 Thread lifecycle

An executing thread can be described as either "running", "ready" or "blocked". There are however a lot of different states within "blocked", as shown in Figure 4.7. Except

for the "running" state in which a thread has processing power, and "ready" where the thread is waiting to acquire time by the scheduler, the rest are other "blocked" states. In these cases the threads are waiting for some other factors like sleep, semaphores or resources, before they are able to return to the ready queue.

Figure 4.7: Possible thread states. Courtesy of [22].

# 4.2.4 Scheduler

The scheduler is invoked whenever a decision on which thread is to be given processing time next. This happens whenever the running thread is blocked, preempted, yields or uses its allocated time-slice. There are 0-255 priority queues, with 255 being the highest priority. When several threads are ready, QNX provides three scheduling algorithms:

- First in, first out (FIFO) scheduling

- Round-robin scheduling

- Sporadic scheduling

#### 4.2. QNX

These algorithms can be changed by within each thread, this way different threads can use the scheduling that fits its purpose best.

In FIFO scheduling the first thread entering the ready state will be the first to execute at the given priority. It will execute until it either blocks, yields or is preempted by a higher-priority thread.

This holds also for the round-robin scheme, however, in this case the threads are also given a time-slice. If they do not relinquish control within this set timeslice they will be forced back into the ready queue, giving the next thread access.

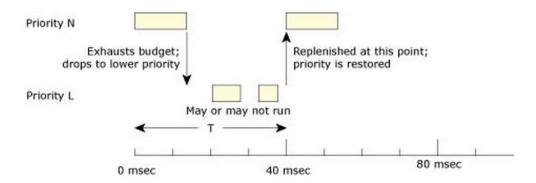

The sporadic scheduling algorithm is more complicated. It is used to provide a capped limit on the execution time of a thread, within a given period of time. The threads priority can dynamically change between a normal (foreground) priority and a low (background) priority. As in FIFO scheduling a thread runs until it is blocks, yields or preempted. The difference is that the a thread is allocated a fixed amount of time it is allowed to run at normal priority (N) before dropping to low priority (L). By also controlling the replenishment period for normal priority execution, and the value of the low priority, sporadic scheduling can be a powerful tool for handling aperiodic events, without missing hard deadlines of other threads. An example is illustrated in Figure **??**.

Figure 4.8: Thread drops in priority until its budget is replenished. Courtesy of [22].

# 4.3 FreeRTOS

FreeRTOS<sup>12</sup> is a real-time operating system and its primary market target is again embedded systems. However, FreeRTOS is as its name indicates a free, open sourced OS. It implements a simpler microkernel then QNX were its features include, preemptive tasks, support for 34 hardware architectures, a small footprint, and it is written in C. The basic non-commercial version does however, not include support for network communication, external hardware drivers, or a file system.

# 4.3.1 Tasks in FreeRTOS

There are no software restrictions to the number of tasks that can be created in FreeRTOS, though the practical number of maximum tasks will be limited by hardware and memory. Tasks are created before the a call starts the scheduler. Any created task shall always be wrapped in an infinite loop, or to invoke vTaskDelete, which free all allocated memory to this task by kernel.

## 4.3.2 Lifecycle

In FreeRTOS a task is either running or not, and only one task can run at any given time. When not running a task will be in one of three states, as depicted in Figure 4.9. When a task is delayed or waiting for another task (through semaphores or mutexes) it is said to be "Blocked". A task can also be suspended, when a task gets suspended it will stay in that state until it gets resumed, by either a task or the kernel. The last state in the "Not running" superstate is the ready state. This is where all the tasks which are not waiting for any events, but there is a equally or higher prioritized task running at that time. If a task with higher priority than the one currently running enters the ready state, and preemption is enabled, then the schedular will force a context switch.

## 4.3.3 FreeRTOS scheduler

The scheduler has the responsibility of choosing which task in "Ready" states is to be given processor time. The FreeRTOS scheduler operates as an ISR at a given tick

38

<sup>&</sup>lt;sup>12</sup>http://www.freertos.org/

Figure 4.9: Lifecycle of FreeRTOS tasks. Courtesy of [19].

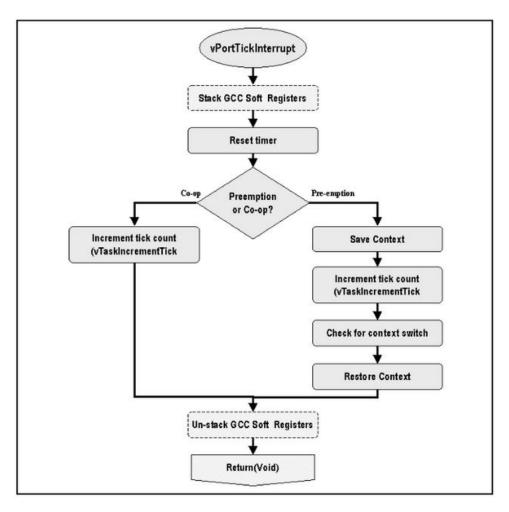

period. This tick period is defined in the kernel header files. Figure 4.10 shows the scheduler algorithm run in the ISR. The first operation is to reset the counter timer, this is to initialize the next tick period. If the scheduler is co-operative, then the only action is to increment the tick count. However, if the scheduler is preemptive then the scheduler can force a context switch. Therefore the context of the current task is saved before the tick count is incremented. The scheduler then checks if the tick incrementation caused any higher priority blocked tasks to unblock. If so, then a context switch is executed before context is restored, and the ISR returns.

The scheduler is started through a call to the vTaskStartScheduler() function. This should be the last function called in main, after all the required tasks have been created. It then creates the IDLE task, this is the task running with at lowest priority. Further, it sets up the time interrupt to invoke the scheduler. Since this is hardware dependent, the configuring occurs in the Hardware Abstraction Layer (HAL), this is the part which requires porting when compiling FreeRTOS for new platforms. After this is done, context is restored and the tasks will begin to run.

Figure 4.10: ISR scheduler algorithm for FreeRTOS. Courtesy of [19].

# 5 Hardware solution

# 5.1 Proposed solution

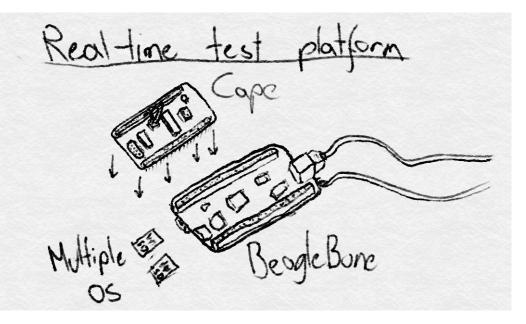

The problem formulation 1.2 states that this thesis show create an embedded test platform. Figure 5.1, which is based on the hardware and software choices made in Chapters 3 and 4, shows a sketch of the proposed hardware solution to this problem. It depicts the BeagleBone Black, together with SD cards representing the possibility for multiple OS, and the boards expansion, the External Response Tester (ERT) cape. This chapter will present how the ERT was made and programmed.

Figure 5.1: Sketch of hardware solution.

# 5.2 External Response Tester

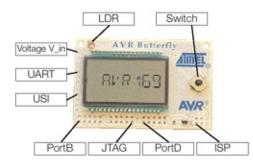

As mentioned in the introduction of Chapter 3, the Beaglebone platform was chosen for being a modern embedded development platform with a range of compatible OS. However, there was need to create an equally versatile device, which could be used to simulate external sources that the BeagleBone applications could interact with. Presently the exercises in the course TTK4147 Real-time systems use the AVR butterfly evalution tool to enable these kind of tests.

# 5.2.1 AVR butterfly

The AVR butterfly is a ATmega169 MCU with a small LCD screen and a four-direction joystick, shown in Figure 5.2.

Figure 5.2: The AVR butterfly. Courtesy of [1].

In the course assignments the butterfly is programmed to be a real-time response tester. It transmits out a signal on 1 to 3 output pins, and then waits for, and times the response on 1 to 3 (other) input pins. Each test runs either 10, 100 or 1000 such timed responses on each pin. The results of such a response test is then be placed on the butterfly UART.

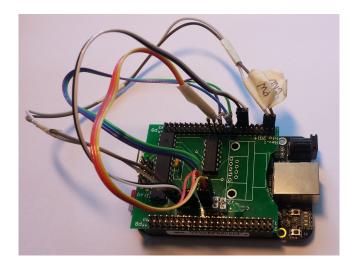

## 5.2.2 BeagleBone Cape

This project set out to create some device with similar, but extended features compared to the AVR butterfly. A BeagleBone cape is a device which can be plugged into the board headers extending its features. Many different capes exist through

42

<sup>&</sup>lt;sup>1</sup>http://www.atmel.com/tools/avrbutterfly.aspx?tab=overview

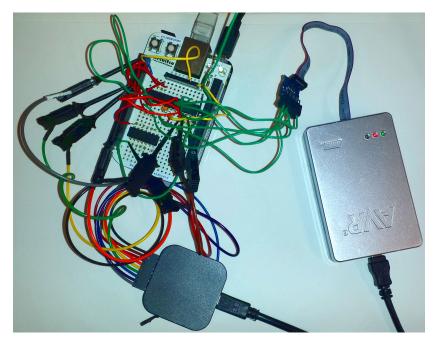

the BeagleBone community, these range from LCD screens to motor control. Thus, to enable cape prototyping we took advantage of such a community cape, the BeagleBone Breadboard shown in Figure 5.3. This was used to ensure that the design performed according to our expectations, before creating and ordering a Printed Circuit Board (PCB).

Figure 5.3: The BeagleBone Breadbord. Courtesy of [1]

# 5.2.3 Prototyping

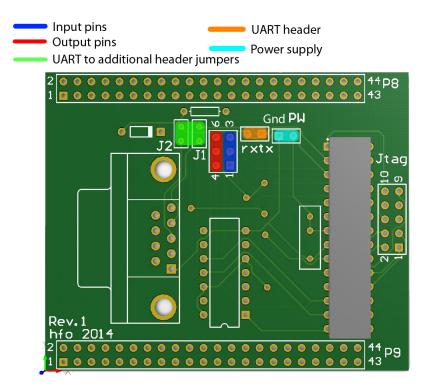

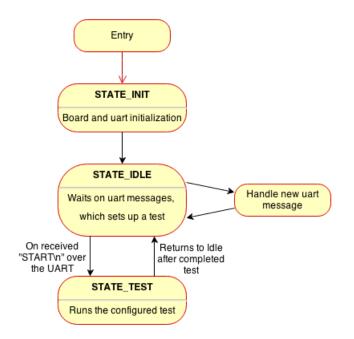

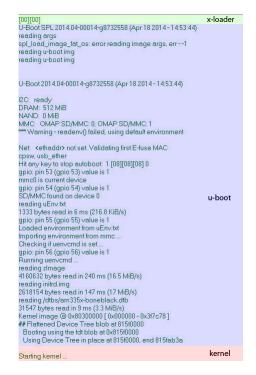

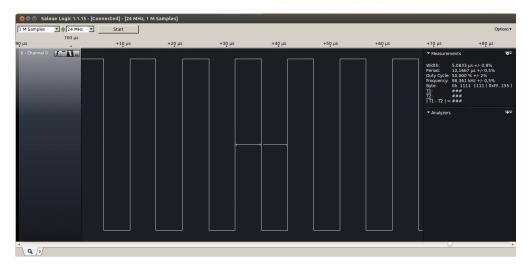

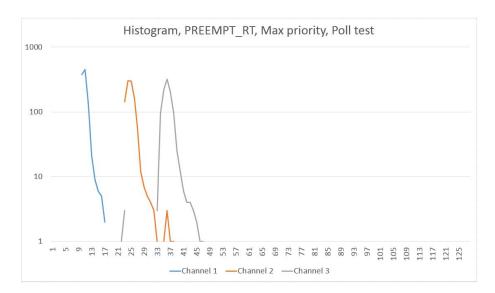

The ERT cape features can be summarized as follows: