# Autonomous environmental monitoring probe for aquaculture sites

alireza ramezaniakhmareh

Embedded Computing Systems Submission date: December 2012 Supervisor: Jo Arve Alfredsen, ITK

Norwegian University of Science and Technology Department of Engineering Cybernetics

# Norwegian University of Science and Technology Department of Engineering Cybernetics

Master of Science in Electronic Engineering Embedded Systems

# MS Thesis Report

Alireza Ramezani

Version : 0.1 rev3

Build Date : November 30, 2012

#### Abstract

Proper knowledge of the composition and quality of the local underwater environment is very important for the management of sea-based aquaculture farms. This project aims to develop an instrument that is capable of moving vertically in a controlled manner along a taut string from the sea surface to a predetermined depth while measuring pertinent seawater parameters. The main focus will be to specify, design and implement an embedded computer system that realizes the instrument.

### Contents

| 1        | Pro   | ject Sp | ecification                                                                                                                            | 4     |

|----------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

|          | 1.1   | Basics  | about water analysis                                                                                                                   | . 4   |

|          | 1.2   | Enviro  | nmental Parameters Measurement Requirements                                                                                            | . 6   |

|          | 1.3   | Deploy  | yment time and power consumption                                                                                                       | . 6   |

| <b>2</b> | Syst  | tem Le  | vel Design                                                                                                                             | 7     |

|          | 2.1   | System  | s Main Functional Modules                                                                                                              | . 7   |

|          |       | 2.1.1   | Microcontroller                                                                                                                        |       |

|          |       | 2.1.2   | Stepper Motor                                                                                                                          | . 7   |

|          |       | 2.1.3   | Power-on indicator                                                                                                                     |       |

|          |       | 2.1.4   | GSM/GPRS Module                                                                                                                        | . 7   |

|          |       | 2.1.5   | External Non Volatile Memory                                                                                                           | . 8   |

|          |       | 2.1.6   | Power Supply                                                                                                                           | . 8   |

|          |       | 2.1.7   | Digital Sensor Module                                                                                                                  | . 8   |

|          | 2.2   | Requi   | red Communication Interfaces                                                                                                           |       |

| 3        | Mo    | dule Le | evel Design                                                                                                                            | 10    |

|          | 3.1   |         | ontroller's Peripherials                                                                                                               | . 10  |

|          |       | 3.1.1   | General-Purpose Input/Output Controller(GPIO)                                                                                          |       |

|          |       | 3.1.2   | Interrupt Controller(INTC)                                                                                                             |       |

|          |       | 3.1.3   | Power Manager(PM)                                                                                                                      |       |

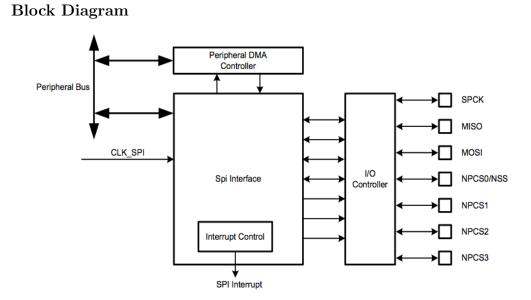

|          |       | 3.1.4   | Serial peripheral Interface(SPI)                                                                                                       |       |

|          |       | 3.1.5   | Universal synchronous and Asynchronous Receiver and                                                                                    |       |

|          |       |         | $Transmitter(USART) \dots \dots$ | . 55  |

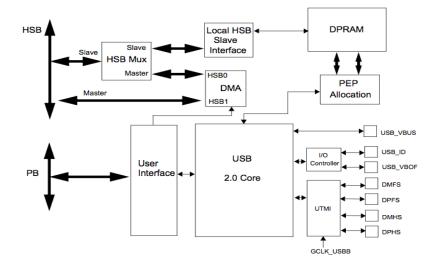

|          |       | 3.1.6   | Hi-Speed USB Interface (USBB)                                                                                                          | . 65  |

|          | 3.2   | GSM/G   | GPRS Module Specifications                                                                                                             | . 96  |

| 4        | Pro   | totypin | lg                                                                                                                                     | 102   |

|          | 4.1   | FreeRT  | COS                                                                                                                                    | . 102 |

|          |       | 4.1.1   | FreeRTOS Modules                                                                                                                       | . 102 |

|          |       | 4.1.2   | FreeRTOS Implementation Modules                                                                                                        | . 115 |

|          | 4.2   | Target  | Application Development                                                                                                                | . 119 |

|          |       |         | Embedded System Block Diagram                                                                                                          |       |

| 5        | Con   | clusion | and Future Work                                                                                                                        | 131   |

| Bi       | bliog | graphy  |                                                                                                                                        | 132   |

|          |       |         |                                                                                                                                        |       |

# List of Figures

| 1  | GPIO Block Diagram                                                                                           |

|----|--------------------------------------------------------------------------------------------------------------|

| 2  | Overview of the GPIO Pad Connections 12                                                                      |

| 3  | Output Line Timings                                                                                          |

| 4  | Interrupt Timing With Glitch Filter Disabled 16                                                              |

| 5  | Interrupt Timing With Glitch Filter Enabled                                                                  |

| 6  | Overall Mermory Map                                                                                          |

| 7  | INTC Block Diagram                                                                                           |

| 8  | Power Manager Block Diagram                                                                                  |

| 9  | Oscillator Connections                                                                                       |

| 10 | PLL with Control Logic and Filters                                                                           |

| 11 | Synchronous Clock Generation                                                                                 |

| 12 | Generic Clock Generation                                                                                     |

| 13 | Reset Controller Block Diagram                                                                               |

| 14 | SPI Block Diagram                                                                                            |

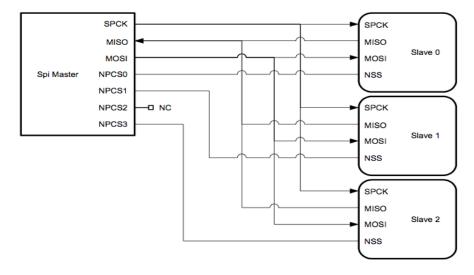

| 15 | Application Block Diagram: Single Master/Multiple Slave Im-                                                  |

|    | plementation $\ldots \ldots 42$ |

| 16 | Application Block Diagram: Single Master/Multiple Slave Im-                                                  |

|    | plementation                                                                                                 |

| 17 | Application Block Diagram: Single Master/Multiple Slave Im-                                                  |

|    | plementation                                                                                                 |

| 18 | Master Mode Block Diagram                                                                                    |

| 19 | Master Mode Flow Diagram                                                                                     |

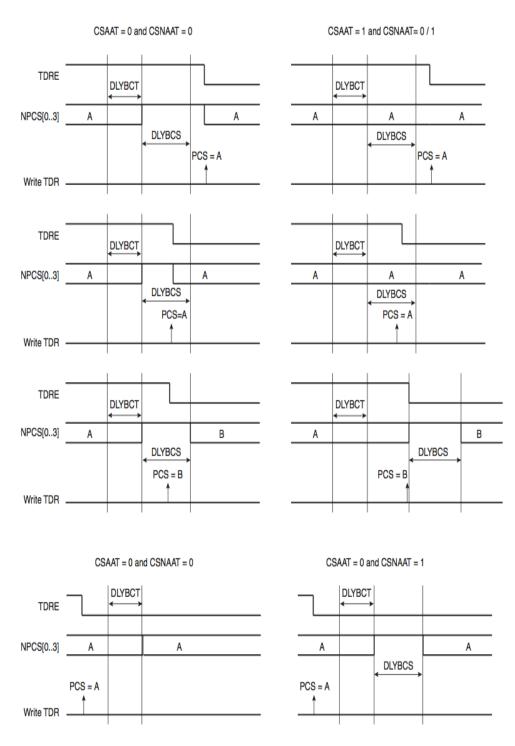

| 20 | Programmable Delays                                                                                          |

| 21 | Peripheral Deselection                                                                                       |

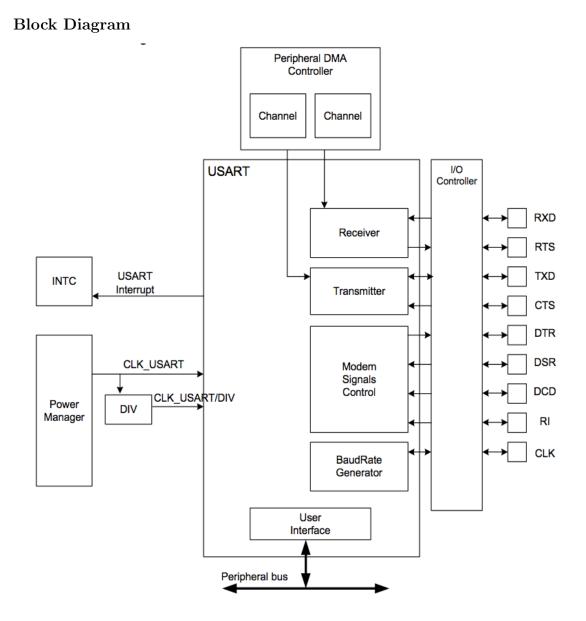

| 22 | USART Block Diagram                                                                                          |

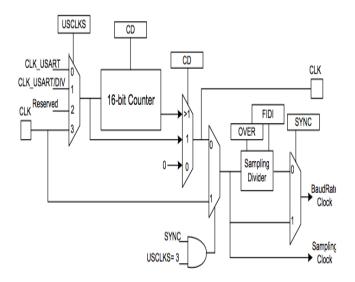

| 23 | Baud Rate Generator                                                                                          |

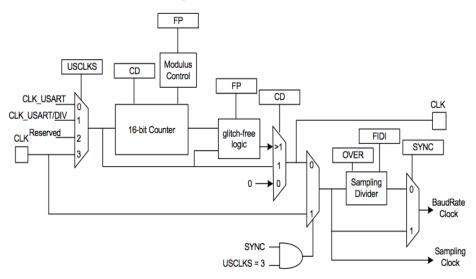

| 24 | Fractional Baud Rate Generator) 61                                                                           |

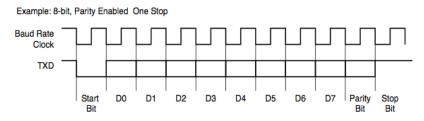

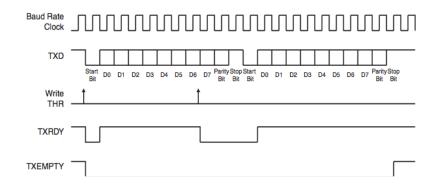

| 25 | Character Transmit                                                                                           |

| 26 | Transmitter Status                                                                                           |

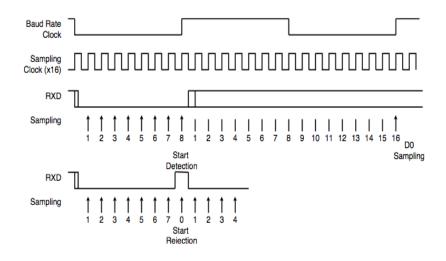

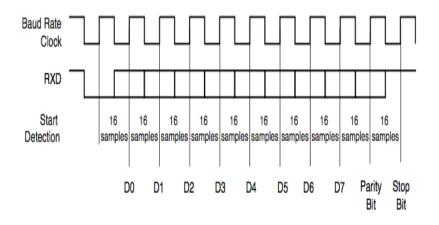

| 27 | Asynchronous Start Bit Detection                                                                             |

| 28 | Asynchronous Character Reception                                                                             |

| 29 | USBB Block Diagram                                                                                           |

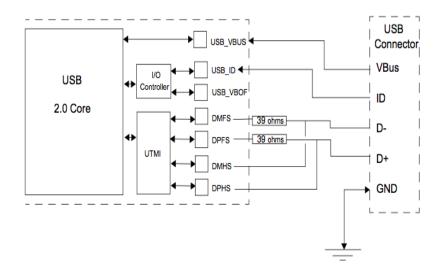

| 30 | Self-powered Device Application Block Diagram                                                                |

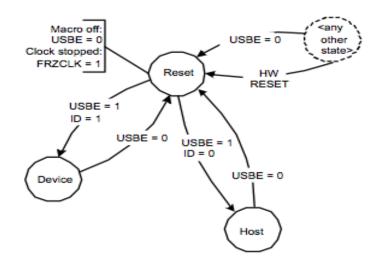

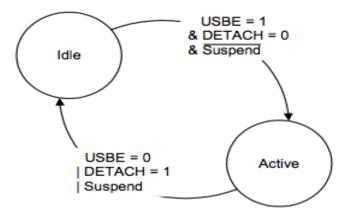

| 31 | General States                                                                                               |

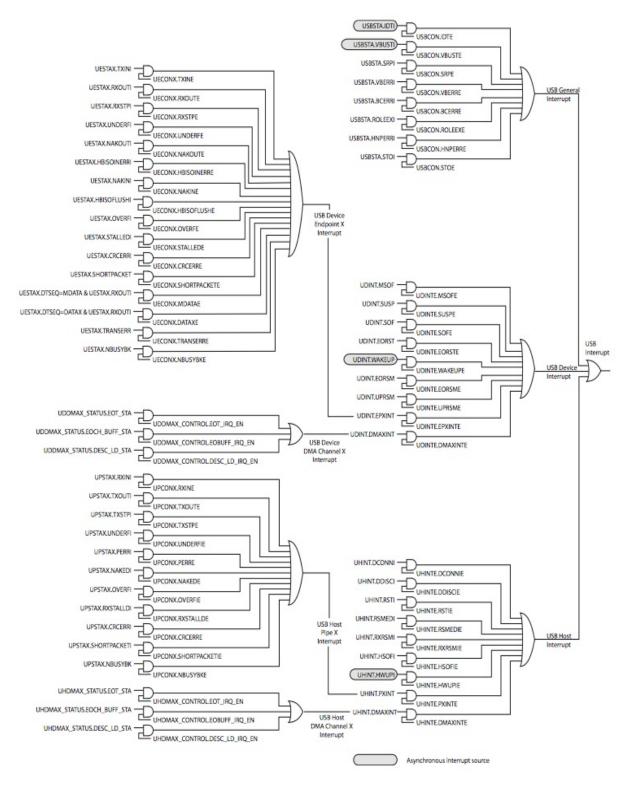

| 32 | Interrupt System                                                                                             |

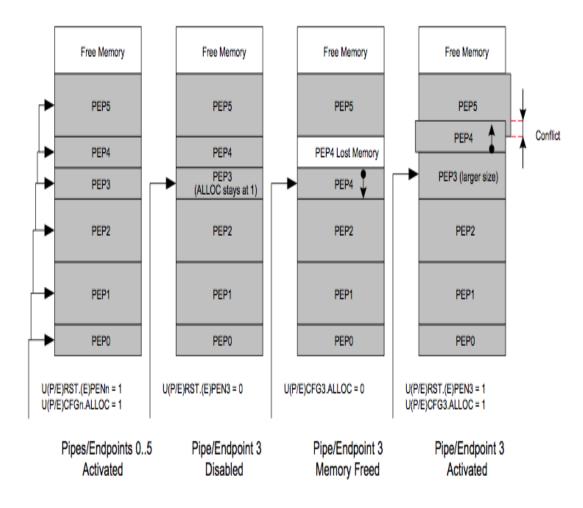

| 33 | Allocation and Reorganization of the DPRAM                                                                   |

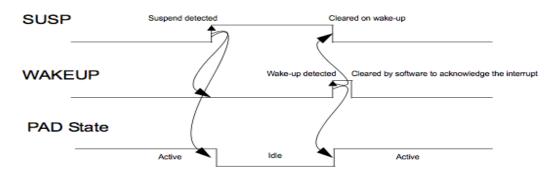

| 34 | Pad Behavior                                                                                                 |

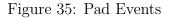

| 35 | Pad Events                                                                                                   |

|    |                                                                                                              |

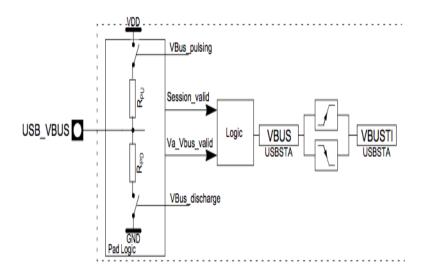

| 36 | Plug-In Detection Input Block Diagram             |

|----|---------------------------------------------------|

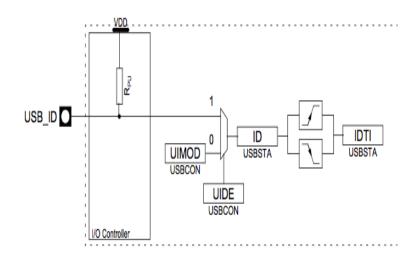

| 37 | Pad Events         80                             |

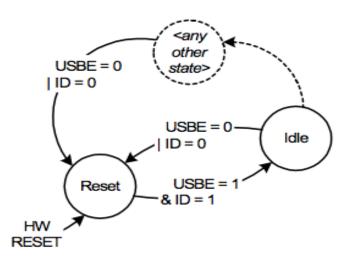

| 38 | Device Mode States                                |

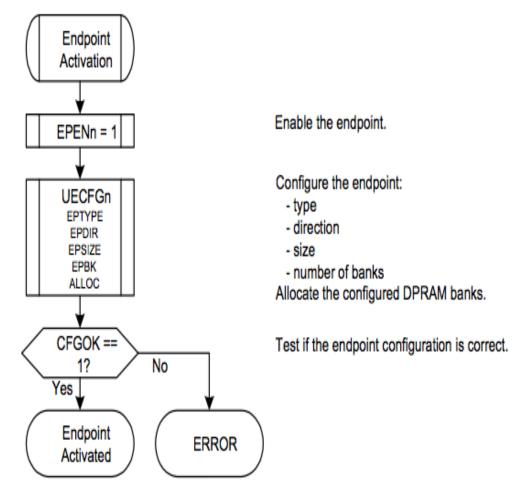

| 39 | Endpoint Activation Algorithm                     |

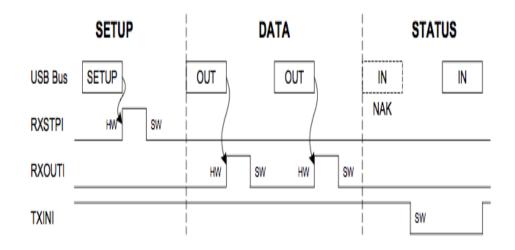

| 40 | Control Write                                     |

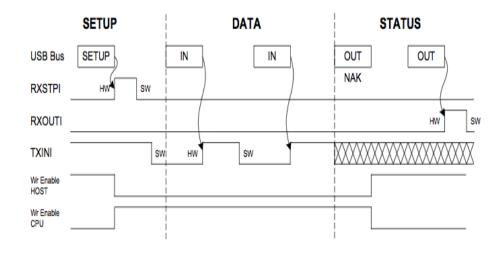

| 41 | Control Read                                      |

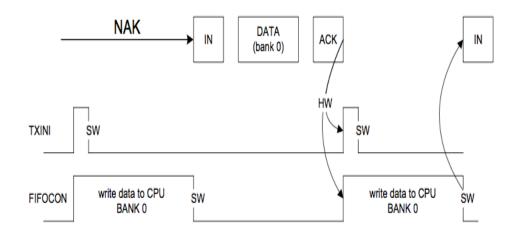

| 42 | Example of an IN Endpoint with 1 Data Bank        |

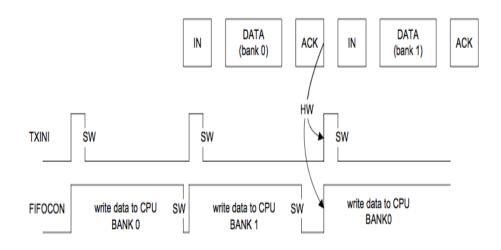

| 43 | Example of an IN Endpoint with 2 Data Banks       |

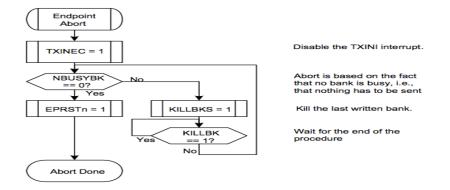

| 44 | Abort Algorithm                                   |

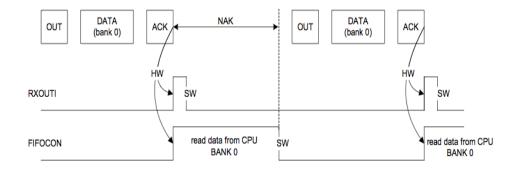

| 45 | Example of an OUT Endpoint with one Data Bank 92  |

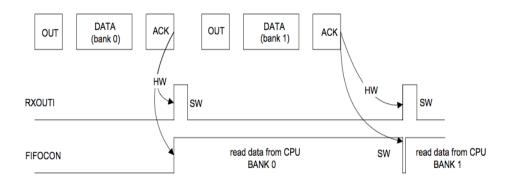

| 46 | Example of an OUT Endpoint with two Data Banks 92 |

| 47 | GC 864-QUAD V2 Compact                            |

| 48 | actual size GC864-QUAD                            |

| 49 | GC864-QUAD with SIM holder                        |

| 50 | Application Block Diagram                         |

## List of Tables

| 1  | GPIO Register Memory Map                                    | 8 |

|----|-------------------------------------------------------------|---|

| 2  | INTC Register Memory Map                                    | 3 |

| 3  | Sleep Modes                                                 | 3 |

| 4  | Generic Clock Allocation                                    | 5 |

| 5  | Reset Description                                           | 7 |

| 6  | Effect of the Different Reset Events                        | 7 |

| 7  | VDDIO pin monitored by BOD33                                | 8 |

| 8  | PM Register Memory Map                                      | 0 |

| 9  | I/O Lines Description                                       | 3 |

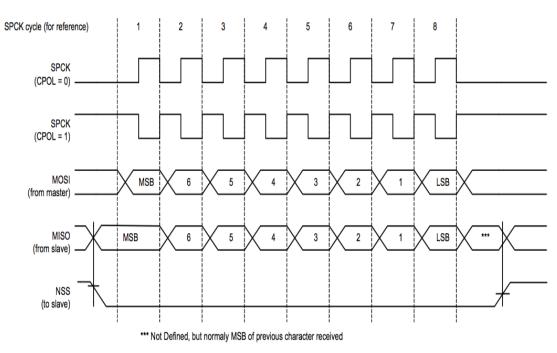

| 10 | SPI modes                                                   | 5 |

| 11 | SPI Register Memory Map                                     | 5 |

| 12 | I/O Lines Description                                       | 7 |

| 13 | Baud Rate Example (OVER=0) 6                                | 0 |

| 14 | USART Register Memory Map                                   | 5 |

| 15 | Description of USB Pipes/Endpoints                          | 6 |

| 16 | Example of Configuration of Pipes/Endpoints Using the Whole |   |

|    | DPRAM                                                       | 6 |

| 17 | Example of Configuration of Pipes/Endpoints Using the Whole |   |

|    | DPRAM                                                       | 6 |

| 18 | I/O Lines Description                                       | 9 |

#### **1** Project Specification

#### 1.1 Basics about water analysis

Salinity - is a measure of the total concentration of all ions found in water. Seven ions make up the bulk of a salinity reading. These are sodium, potassium, calcium, magnesium, chloride, sulfate, and bicarbonate. Salinity is typically measured in parts per thousand (ppt). Full-strength seawater is typically around 35 ppt. Estuarine water is classified as having 3 ppt while freshwater has less than 0.3 ppt. Any water having more than 1 ppt salinity can be expected to have a salty taste. Penaeid shrimp generally exhibit ideal growth at salinity values between 15-25 ppt, but it is a highly adaptable species and has been grown in commercial settings at salinities ranging from 2-38 ppt. Tilapias show varying degrees of salinity tolerance depending on species but all can tolerate salinities lower than 5 ppt.

Potassium - concentrations in water tend to be highly variable and tend to vary with salinity. The concentration of potassium in seawater is normally around 380 ppm.

pH - values between 7.0 and 8.0 are generally considered ideal for a quaculture.

Temperature - the ideal water temperature for the culture of tropical fishes and shrimps is between 82F to 86F.

Total Hardness, Calcium & Magnesium - total hardness is the concentration of calcium and magnesium in water expressed in milligrams per liter (mg/l) of equivalent calcium carbonate (CaCO3). Water having total hardness values of 0-75 mg/l is generally classified as soft water, while values above 150 mg/l is categorized as hard water. Full strength seawater has a total hardness of 6,600 mg/l. Hardness is important to crustaceans because they have heavily mineralized exoskeletons and it is often thought that low hardness levels may limit their growth (Greenway, 1974). The lower limit for total hardness for the proper development of crustacean's exoskeletons is believed to be 50 mg/l (Boyd, 1990).

Phosphorous - is perhaps the most important nutrient influencing the natural productivity of aquatic systems. Phosphorous is critical for proper development of phytoplankton and phytoplankton is one of the basic building blocks of aquatic productivity. Estuarine areas typically have much higher concentrations of phosphorous in the water and this is why they are so productive. Open ocean environments typically have very low concentrations of phosphorous and productivity is generally low. Concentration of phosphorous in pure seawater is usually around 0.07 mg/l.

Total Ammonia Nitrogen (TAN) - TAN consists of two fractions, un-ionized ammonia (NH3) and ionized ammonia (NH4+) and is the by-product of protein metabolism. TAN is excreted from the gills of fish as they assimilate feed and is produced when bacteria decompose organic waste solids within the culture system. The un-ionized form of ammonia-nitrogen is extremely toxic to fish. The fraction of TAN in the un-ionized form is dependent upon the pH and temperature of the water. At a pH of 7.0, most of the TAN is in the ionized form, while at a pH of 8.0 the majority is in the un-ionized form, While the lethal concentration of ammonia-nitrogen for many species has been established, the sublethal effects of ammonia-nitrogen have not been well defined. Reduction in growth rates may be the most important sublethal effect. In general, the concentration of unionized ammonia-nitrogen should not exceed 0.05 mg/1. Nitrite-nitrogen (N02-) - is a product of the oxidation of ammonia-nitrogen. Vitrifying bacteria (Nitosomonas) in the production system utilize ammonia-nitrogen as an energy source for growth and produce nitrite-nitrogen as a by-product. These bacteria are the basis for biological filtration. The vitrifying bacteria grow on the surface of the biofilter substrate and to some extent on all production system components including pipes, valves, tank walls, etc. While nitrite-nitrogen is not as toxic as ammonia-nitrogen, it is harmful to aquatic species and must be removed from the system. Concentrations of nitrite-nitrogen should not exceed 0.5 mg/l for long periods of time.

Nitrate-nitrogen (NO3) - fortunately, Nitrobacter bacteria, which are also present in most biological filters, utilize nitrite-nitrogen as an energy source and produce nitrate as a by-product. Nitrates are not generally of great concern to the aquaculturist. Studies have shown that aquatic species can tolerate extremely high levels (greater than 100 mg/l) of nitrate-nitrogen in production systems. Nitrate-nitrogen is either flushed from a system during system maintenance operations (such as settled solids removal or filter backwashing) or denitrification occurs within a treatment system component such as a settling tank. Denitrification is mainly due to the metabolism of nitrate-nitrogen by anaerobic bacteria producing nitrogen gas that is released to the atmosphere during aeration processes.

Sulfate - the most common form of sulfur in seawater is sulfate. Concentrations can vary with the nature of the geological materials in the watershed and with hydrological conditions. Pure seawater normally contains around 885 mg/l sulfate.

Heavy Metals - according to the recommendations of the United States Environmental Protection Agency (EPA), safe levels of cadmium, chromium, copper, lead, and zinc are 10, 100, 25, 100, and 100 micrograms/liter (ug/L) respectively. Most of these metals form a dietary requirement at very low levels (less than 10 ug/L) while being toxic at high concentrations.

#### 1.2 Environmental Parameters Measurement Requirements

Temperature: the Probe should be able to measure the temperature range from  $-2^{\circ}$  to  $+30^{\circ}$  C. Because, water temperature usually ranges from  $1^{\circ}$  to  $30^{\circ}$ C, during the year in the Trondheim fjord. Also, the required accuracy for mentioned measurement is about  $\pm 0.1^{\circ}$ C.

Salinity: Salinity usually ranges from 0.5ppt to 35ppt( case study ). As a result, the sensor which is used in the probe should be capable of measuring this range of salinity and accurate enough for a valid data to be obtained. And, the resolution acceptable for this experiment would be 1ppt.

Depth: It should be measured continuously (non stopping measurement-free running) to calculate at which depth the probe is at each time instant. And, requested Resolution shall be 0.1m with the accuracy of  $\pm 0.1$ m. Worth mentioning that the maximum depth would be around 50 meters.

#### 1.3 Deployment time and power consumption

The power consumption of the system should be as low as possible, because the device is powered with the batteries which cannot persist much operation time if the power consumption is not regulated properly. And, because of difficulty in accessing the probe for battery replacement, it would be designed to work for at least 3 months without the need for battery recharge or replacement.

#### 2 System Level Design

The main goal of this phase is to identify the systems main functional modules (modularization) and define the logical interfaces between them.

#### 2.1 Systems Main Functional Modules

#### 2.1.1 Microcontroller

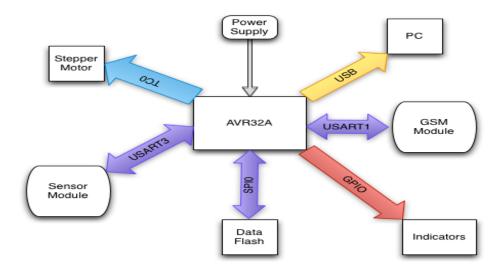

As the main controller of our system, we have considered a 32-bit AVR microcontroller which has some good features such low power consumption, high performance, and low cost that are three important characteristics of Embedded Systems. By using an 32-bit family of AVRs, we could have a system capable of running a realtime operating system (such as Embedded linux). For this project, we have implemented an embedded system based on FreeRTOS which has a realtime kernel and a small code size suitable for embedded applications.

#### 2.1.2 Stepper Motor

As we should have a strategy for making the probe to move along a taut string, we have made use of a stepper motor which task is controlling the vertical motion. Its worth mentioning that implementing the task for motor control would be out of this project focus.

#### 2.1.3 Power-on indicator

Our probe needs to signal the power-on state to the user. For this purpose, we have considered a LED as a power-on indicator.

#### 2.1.4 GSM/GPRS Module

There should be a module through which the Microcontroller communicates and sends the data to GSM network. So, we have assigned this task to a GSM/GPRS module. This module should have the capability to send the gathered data as a text message to a predefined GSM network.

#### 2.1.5 External Non Volatile Memory

By considering the internal memory of microcontrollers usually is not sufficient for storing large amount of data (maximum few hundred Kb), we have to think about having another high capacity external memory for storing our samples which are crucial for future data analysis.

#### 2.1.6 Power Supply

One of main characteristics of Embedded systems is being low power. As a result, we have considered some facilities to reduce the power consumption, and make use of a number of normal AA batteries as our system's power supply.

#### 2.1.7 Digital Sensor Module

In this project we have considered using a digital sensor module with RS232 interface, with which the microcontroller could communicate and receive the sensor acquired data fast and efficient. This sensor measures water quality factors such as temperature, depth, and salinity which are the main characteristics of water quality measurement.

#### 2.2 Required Communication Interfaces

RS232 communication port: the microcontroller needs a port for communication with both sensor module and GSM module. RS232 is a simple and user-friendly communication port through which we send and receive data to and from sensor module easily and fast. By considering this fact that both AVR controller and GSM module have the same working voltage range, but AVR controller and sensor module have different voltage levels, we need a voltage convertor between AVR and sensor module. By having so, we have the proper communication interface between main system modules.

Debug Interface: for the testing and debug purposes, there should be a J-tag interface through which the maintenance staff could test the system while required. And, if it is necessary, upgrade the firmware of the MCU through J-Tag interface.

GSM/GPRS Network Connection: By having the monitoring probe connected to a GSM network, we could send the gathered data to devices which are connected to that network either(a cell phone, for example).

USB communication port: Taking into account that the GSM network connection might fail because of whichever reason, there should be an alternative way for monitoring the environment which would be through a USB interface. By making available a USB communication port, we could guarantee the constant observation with a PC having minimum hardware and software requirements.

#### 3 Module Level Design

The main goal of this section is to make Further modularization and detailed specification of each hardware and software component providing the required basis/documentation for implementation.

#### 3.1 Microcontroller's Peripherials

Here we list the peripherals that have been used for this project, and their related specific characteristics.

#### 3.1.1 General-Purpose Input/Output Controller(GPIO)

Features Each I/O line of the GPIO features:

• Configurable pin-change, rising-edge or falling-edge interrupt on any I/O line

- A glitch filter providing rejection of pulses shorter than one clock cycle

- Input visibility and output control

- Multiplexing of up to four peripheral functions per I/O line

- Programmable internal pull-up resistor

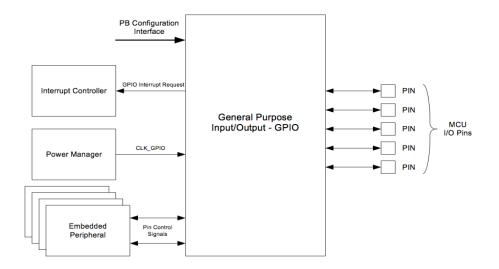

**Overview** The General Purpose Input/Output Controller manages the I/O pins of the microcontroller. Each I/O line may be dedicated as a general-purpose I/O or be assigned to a function of an embedded peripheral. This assures effective optimization of the pins of a product.

Block Diagram Here is the block diagram of GPIO controller:

Figure 1: GPIO Block Diagram

**Product Dependencies** In order to use this module, other parts of the system must be configured correctly, as described below.

**Module Configuration** Most of the features of the GPIO are configurable for each product.

Product specific settings includes:

- Number of I/O pins.

- Functions implemented on each pin

- Peripheral function(s) multiplexed on each I/O pin

- Reset value of registers

**Clocks** The clock for the GPIO bus interface (CLK\_GPIO) is generated by the Power Manager. This clock is enabled at reset, and can be disabled in the Power Manager.

The CLK\_GPIO must be enabled in order to access the configuration registers of the GPIO or to use the GPIO interrupts. After configuring the GPIO, the CLK\_GPIO can be disabled if interrupts are not used.

**Interrupts** The GPIO interrupt lines are connected to the interrupt controller. Using the GPIO interrupt requires the interrupt controller to be configured first.

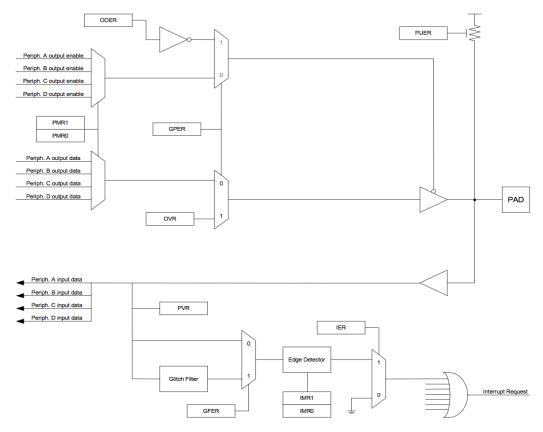

**Functional Description** The GPIO controls the I/O lines of the microcontroller. The control logic associated with each pin is represented in the figure below:

Figure 2: Overview of the GPIO Pad Connections

#### **Basic Operation**

I/O Line or peripheral function selection When a pin is multiplexed with one or more peripheral functions, the selection is controlled with the GPIO Enable Register (GPER). If a bit in GPER is written to one, the corresponding pin is controlled by the GPIO. If a bit is written to zero, the corresponding pin is controlled by a peripheral function. **Peripheral selection** The GPIO provides multiplexing of up to four peripheral functions on a single pin. The selection is performed by accessing Peripheral Mux Register 0 (PMR0) and Peripheral Mux Register 1 (PMR1).

**Output control** When the I/O line is assigned to a peripheral function, i.e. the corresponding bit in GPER is written to zero, the drive of the I/O line is controlled by the peripheral. The peripheral, depending on the value in PMR0 and PMR1, determines whether the pin is driven or not.

When the I/O line is controlled by the GPIO, the value of the Output Driver Enable Register (ODER) determines if the pin is driven or not. When a bit in this register is written to one, the corresponding I/O line is driven by the GPIO. When the bit is written to zero, the GPIO does not drive the line.

The level driven on an I/O line can be determined by writing to the Output Value Register (OVR).

**Inputs** The level on each I/O line can be read through the Pin Value Register (PVR). This register indicates the level of the I/O lines regardless of whether the lines are driven by the GPIO or by an external component. Note that due to power saving measures, the PVR register can only be read when GPER is written to one for the corresponding pin or if interrupt is enabled for the pin.

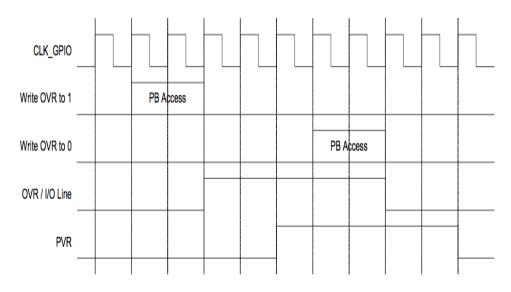

**Output line timings** The figure below shows the timing of the I/O line when writing a one and a zero to OVR. The same timing applies when performing a 'set' or 'clear' access, i.e., writing a one to the Output Value Set Register (OVRS) or the Output Value Clear Register (OVRC). The timing of PVR is also shown.

Figure 3: Output Line Timings

#### **Advanced Operation**

**Pull-up resistor control** Each I/O line is designed with an embedded pull-up resistor. The pull-up resistor can be enabled or disabled by writing a one or a zero to the corresponding bit in the Pull-up Enable Register (PUER). Control of the pull-up resistor is possible whether an I/O line is controlled by a peripheral or the GPIO.

**Input glitch filter** Optional input glitch filters can be enabled on each I/O line. When the glitch filter is enabled, a glitch with duration of less than 1 clock cycle is automatically rejected, while a pulse with duration of 2 clock cycles or more is accepted. For pulse durations between 1 clock cycle and 2 clock cycles, the pulse may or may not be taken into account, depending on the precise timing of its occurrence. Thus for a pulse to be guaranteed visible it must exceed 2 clock cycles, whereas for a glitch to be reliably filtered out, its duration must not exceed 1 clock cycle. The filter introduces 2 clock cycles of latency.

The glitch filters are controlled by the Glitch Filter Enable Register (GFER). When a bit is written to one in GFER, the glitch filter on the corresponding pin is enabled. The glitch filter affects only interrupt inputs. Inputs to peripherals or the value read through PVR are not affected by the glitch filters.

**Interrupts** The GPIO can be configured to generate an interrupt when it detects an input change on an I/O line. The module can be configured to signal an interrupt whenever a pin changes value or only to trigger on rising edges or falling edges. Interrupts are enabled on a pin by writing a one to the corresponding bit in the Interrupt Enable Register (IER). The interrupt mode is set by writing to the Interrupt Mode Register 0 (IMR0) and the Interrupt Mode Register 1(IMR1). Interrupts can be enabled on a pin, regardless of the configuration of the I/O line, i.e. whether it is controlled by the GPIO or assigned to a peripheral function.

In every port there are four interrupt lines connected to the interrupt controller. Groups of eight interrupts in the port are ORed together to form an interrupt line.

When an interrupt event is detected on an I/O line, and the corresponding bit in IER is written to one, the GPIO interrupt request line is asserted. A number of interrupt signals are ORed-wired together to generate a single interrupt signal to the interrupt controller.

The Interrupt Flag Register (IFR) can by read to determine which pin(s) caused the interrupt. The interrupt bit must be cleared by writing a one to the Interrupt Flag Clear Register (IFRC). To take effect, the clear operation must be performed when the interrupt line is enabled in IER. Otherwise, it will be ignored.

GPIO interrupts can only be triggered when the CLK\_GPIO is enabled.

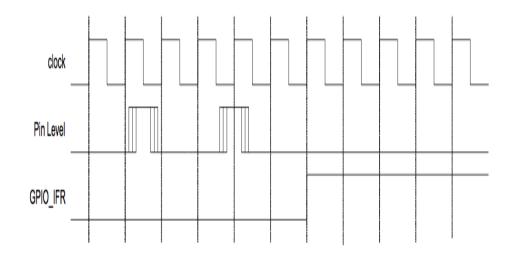

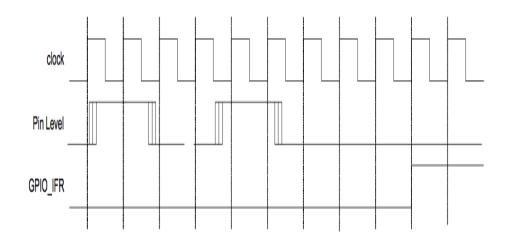

**Interrupt Timings** The figure below shows the timing for rising edge (or pin-change) interrupts when the glitch filter is disabled. For the pulse to be registered, it must be sampled at the rising edge of the clock. In this example, this is not the case for the first pulse. The second pulse is however sampled on a rising edge and will trigger an interrupt request.

Figure 4: Interrupt Timing With Glitch Filter Disabled

The figure below shows the timing for rising edge (or pin-change) interrupts when the glitch filter is enabled. For the pulse to be registered, it must be sampled on two subsequent rising edges. In the example, the first pulse is rejected while the second pulse is accepted and causes an interrupt request.

Figure 5: Interrupt Timing With Glitch Filter Enabled

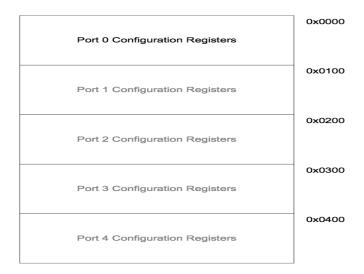

**User Interface** The GPIO controls all the I/O pins on the AVR32 microcontroller. The pins are managed as 32- bit ports that are configurable

through a PB interface. Each port has a set of configuration registers. The overall memory map of the GPIO is shown below. The number of pins and hence the number of ports are product specific.

Figure 6: Overall Mermory Map

In the GPIO Controller Function Multiplexingtable in the Package and Pinout chapter, each GPIO line has a unique number. Note that the PA, PB, PC and PX ports do not directly correspond to the GPIO ports. To find the corresponding port and pin the following formula can be used:

GPIO port = floor((GPIO number) / 32), example: floor((36)/32) = 1

GPIO pin = GPIO number mod 32, example:  $36 \mod 32 = 4$

The table below shows the configuration registers for one port. Addresses shown are relative to the port address offset. The specific address of a configuration register is found by adding the register offset and the port offset to the GPIO start address. One bit in each of the configuration registers corresponds to an I/O pin.

| Offset | Register                      | Function   | Name  | Access     | Reset value |

|--------|-------------------------------|------------|-------|------------|-------------|

| 0x00   | GPIO Enable Register          | Read/Write | GPER  | Read/Write | (1)         |

| 0x04   | GPIO Enable Register          | Set        | GPERS | Write-Only |             |

| 0x08   | GPIO Enable Register          | Clear      | GPERC | Write-Only |             |

| 0x0C   | GPIO Enable Register          | Toggle     | GPERT | Write-Only |             |

| 0x10   | Peripheral Mux Register 0     | Read/Write | PMR0  | Read/Write | (1)         |

| 0x14   | Peripheral Mux Register 0     | Set        | PMR0S | Write-Only |             |

| 0x18   | Peripheral Mux Register 0     | Clear      | PMR0C | Write-Only |             |

| 0x1C   | Peripheral Mux Register 0     | Toggle     | PMR0T | Write-Only |             |

| 0x20   | Peripheral Mux Register 1     | Read/Write | PMR1  | Read/Write | (1)         |

| 0x24   | Peripheral Mux Register 1     | Set        | PMR1S | Write-Only |             |

| 0x28   | Peripheral Mux Register 1     | Clear      | PMR1C | Write-Only |             |

| 0x2C   | Peripheral Mux Register 1     | Toggle     | PMR1T | Write-Only |             |

| 0x40   | Output Driver Enable Register | Read/Write | ODER  | Read/Write | (1)         |

| 0x44   | Output Driver Enable Register | Set        | ODERS | Write-Only |             |

| 0x48   | Output Driver Enable Register | Clear      | ODERC | Write-Only |             |

| 0x4C   | Output Driver Enable Register | Toggle     | ODERT | Write-Only |             |

| 0x50   | Output Value Register         | Read/Write | OVR   | Read/Write | (1)         |

| 0x54   | Output Value Register         | Set        | OVRS  | Write-Only |             |

| 0x58   | Output Value Register         | Clear      | OVRC  | Write-Only |             |

| 0x5c   | Output Value Register         | Toggle     | OVRT  | Write-Only |             |

| 0x60   | Pin Value Register            | Read       | PVR   | Read-Only  | (2)         |

| 0x70   | Pull-up Enable Register       | Read/Write | PUER  | Read/Write | (1)         |

| 0x74   | Pull-up Enable Register       | Set        | PUERS | Write-Only |             |

| 0x78   | Pull-up Enable Register       | Clear      | PUERC | Write-Only |             |

| 0x7C   | Pull-up Enable Register       | Toggle     | PUERT | Write-Only |             |

| 0x90   | Interrupt Enable Register     | Read/Write | IER   | Read/Write | (1)         |

| 0x94   | Interrupt Enable Register     | Set        | IERS  | Write-Only |             |

| 0x98   | Interrupt Enable Register     | Clear      | IERC  | Write-Only |             |

| 0x9C   | Interrupt Enable Register     | Toggle     | IERT  | Write-Only |             |

| 0xA0   | Interrupt Mode Register 0     | Read/Write | IMR0  | Read/Write | (1)         |

| 0xA4   | Interrupt Mode Register 0     | Set        | IMR0S | Write-Only |             |

| 0xA8   | Interrupt Mode Register 0     | Clear      | IMR0C | Write-Only |             |

| 0xAC   | Interrupt Mode Register 0     | Toggle     | IMR0T | Write-Only |             |

| 0xB0   | Interrupt Mode Register 1     | Read/Write | IMR1  | Read/Write | (1)         |

| Table 1: GPIO Register Memory M | [ap |

|---------------------------------|-----|

|---------------------------------|-----|

| Offset | Register                      | Function   | Name  | Access     | Reset value |

|--------|-------------------------------|------------|-------|------------|-------------|

| 0xB4   | Interrupt Mode Register 1     | Set        | IMR1S | Write-Only |             |

| 0xB8   | Interrupt Mode Register 1     | Clear      | IMR1C | Write-Only |             |

| 0xBC   | Interrupt Mode Register 1     | Toggle     | IMR1T | Write-Only |             |

| 0xC0   | Glitch Filter Enable Register | Read/Write | GFER  | Read/Write | (1)         |

| 0xC4   | Glitch Filter Enable Register | Set        | GFERS | Write-Only |             |

| 0xC8   | Glitch Filter Enable Register | Clear      | GFERC | Write-Only |             |

| 0xCC   | Glitch Filter Enable Register | Toggle     | GFERT | Write-Only |             |

| 0xD0   | Interrupt Flag Register       | Read       | IFR   | Read-Only  | (1)         |

| 0xD4   | Interrupt Flag Register       | -          | -     | -          |             |

| 0xD8   | Interrupt Flag Register       | Clear      | IFRC  | Write-Only |             |

| 0xDC   | Interrupt Flag Register       | -          | -     | -          |             |

Access Types Each configuration register can be accessed in four different ways. The first address location can be used to write the register directly. This address can also be used to read the register value. The following addresses facilitate three different types of write access to the register. Performing a "set" access, all bits written to one will be set. Bits written to

zero will be unchanged by the operation. Performing a "clear" access, all bits written to one will be cleared. Bits written to zero will be unchanged by the operation. Finally, a toggle access will toggle the value of all bits written to one. Again all bits written to zero remain unchanged. Note that for some registers (e.g. IFR), not all access methods are permitted.

Note that for ports with less than 32 bits, the corresponding control registers will have unused bits. This is also the case for features that are not implemented for a specific pin. Writing to an unused bit will have no effect. Reading unused bits will always return 0.

#### 3.1.2 Interrupt Controller(INTC)

#### Features

- Autovectored low latency interrupt service with programmable priority

- 4 priority levels for regular, maskable interrupts

- One Non-Maskable Interrupt

- Up to 64 groups of interrupts with up to 32 interrupt requests in each group

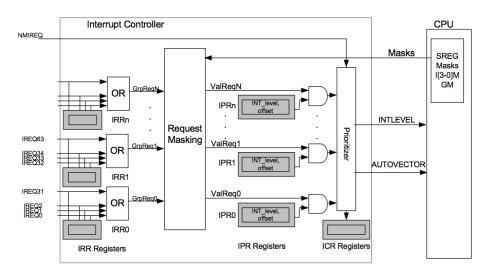

**Overview** The INTC collects interrupt requests from the peripherals, prioritizes them, and delivers an interrupt request and an autovector to the CPU. The AVR32 architecture supports 4 priority levels for regular, maskable interrupts, and a Non-Maskable Interrupt (NMI).

The INTC supports up to 64 groups of interrupts. Each group can have up to 32 interrupt request lines, these lines are connected to the peripherals. Each group has an Interrupt Priority Register (IPR) and an Interrupt Request Register (IRR). The IPRs are used to assign a priority level and an autovector to each group, and the IRRs are used to identify the active interrupt request within each group. If a group has only one interrupt request line, an active interrupt group uniquely identifies the active interrupt request line, and the corresponding IRR is not needed. The INTC also provides one Interrupt Cause Register (ICR) per priority level. These registers identify the group that has a pending interrupt of the corresponding priority level. If several groups have a pending interrupt of the same level, the group with the lowest number takes priority.

**Block Diagram** Figure 12 gives an overview of the INTC. The grey boxes represent registers that can be accessed via the user interface. The interrupt requests from the peripherals (IREQn) and the NMI are input on the left side of the figure. Signals to and from the CPU are on the right side of the figure.

Figure 7: INTC Block Diagram

**Product Dependencies** In order to use this module, other parts of the system must be configured correctly, as described below.

**Power Management** If the CPU enters a sleep mode that disables CLK\_SYNC, the INTC will stop functioning and resume operation after the system wakes up from sleep mode.

**Clocks** The clock for the INTC bus interface (CLK\_INTC) is generated by the Power Manager. This clock is enabled at reset, and can be disabled in the Power Manager. The INTC sampling logic runs on a clock which is stopped in any of the sleep modes where the system RC oscillator is not running. This clock is referred to as CLK\_SYNC. This clock is enabled at reset, and only turned off in sleep modes where the system RC oscillator is stopped. **Debug Operation** When an external debugger forces the CPU into debug mode, the INTC continues normal operation.

**Functional Description** All of the incoming interrupt requests (IREQs) are sampled into the corresponding Interrupt Request Register (IRR). The IRRs must be accessed to identify which IREQ within a group that is active. If several IREQs within the same group are active, the interrupt service routine must prioritize between them. All of the input lines in each group are logically ORed together to form the GrpReqN lines, indicating if there is a pending interrupt in the corresponding group.

The Request Masking hardware maps each of the GrpReq lines to a priority level from INT0 to INT3 by associating each group with the Interrupt Level (INTLEVEL) field in the corresponding Interrupt Priority Register (IPR). The GrpReq inputs are then masked by the mask bits from the CPU status register. Any interrupt group that has a pending interrupt of a priority level that is not masked by the CPU status register, gets its corresponding ValReq line asserted.

Masking of the interrupt requests is done based on five interrupt mask bits of the CPU status register, namely Interrupt Level 3 Mask (I3M) to Interrupt Level 0 Mask (I0M), and Global Interrupt Mask (GM). An interrupt request is masked if either the GM or the corresponding interrupt level mask bit is set.

The Prioritizer hardware uses the ValReq lines and the INTLEVEL field in the IPRs to select the pending interrupt of the highest priority. If an NMI interrupt request is pending, it automatically gets the highest priority of any pending interrupt. If several interrupt groups of the highest pending interrupt level have pending interrupts, the interrupt group with the lowest number is selected.

The INTLEVEL and handler autovector offset (AUTOVECTOR) of the selected interrupt are transmitted to the CPU for interrupt handling and context switching. The CPU does not need to know which interrupt is requesting handling, but only the level and the offset of the handler address. The IRR registers contain the interrupt request lines of the groups and can be read via user interface registers for checking which interrupts of the group are actually active.

The delay through the INTC from the peripheral interrupt request is set until the interrupt request to the CPU is set is three cycles of CLK\_SYNC.

**Non-Maskable Interrupts** A NMI request has priority over all other interrupt requests. NMI has a dedicated exception vector address defined by the AVR32 architecture, so AUTOVECTOR is undefined when INTLEVEL indicates that an NMI is pending.

**CPU Response** When the CPU receives an interrupt request it checks if any other exceptions are pending. If no exceptions of higher priority are pending, interrupt handling is initiated. When initiating interrupt handling, the corresponding interrupt mask bit is set automatically for this and lower levels in status register. E.g, if an interrupt of level 3 is approved for handling, the interrupt mask bits I3M, I2M, I1M, and I0M are set in status register. If an interrupt of level 1 is approved, the masking bits I1M and I0M are set in status register. The handler address is calculated by logical OR of the AUTOVECTOR to the CPU system register Exception Vector Base Address (EVBA). The CPU will then jump to the calculated address and start executing the interrupt handler.

Setting the interrupt mask bits prevents the interrupts from the same and lower levels to be passed through the interrupt controller. Setting of the same level mask bit prevents also multiple requests of the same interrupt to happen.

It is the responsibility of the handler software to clear the interrupt request that caused the interrupt before returning from the interrupt handler. If the conditions that caused the interrupt are not cleared, the interrupt request remains active.

**Clearing an Interrupt Request** Clearing of the interrupt request is done by writing to registers in the corresponding peripheral module, which then clears the corresponding NMIREQ/IREQ signal.

The recommended way of clearing an interrupt request is a store operation to the controlling peripheral register, followed by a dummy load operation from the same register. This causes a pipeline stall, which prevents the interrupt from accidentally re-triggering in case the handler is exited and the interrupt mask is cleared before the interrupt request is cleared.

**User Interface** Here are the registers accessible by the user:

| Offset | Register                       | Register Name | Access     | Reset      |

|--------|--------------------------------|---------------|------------|------------|

| 0x000  | Interrupt Priority Register 0  | IPR0          | Read/Write | 0x00000000 |

| 0x004  | Interrupt Priority Register 1  | IPR1          | Read/Write | 0x00000000 |

|        |                                |               |            |            |

| x0FC   | Interrupt Priority Register 63 | IPR63         | Read/Write | 0x00000000 |

| 0x100  | Interrupt Request Register 0   | IRR0          | Read-only  | N/A        |

| 0x104  | Interrupt Request Register 1   | IRR1          | Read-only  | N/A        |

|        |                                |               |            |            |

| x1FC   | Interrupt Request Register 63  | IRR63         | Read-only  | N/A        |

| 0x200  | Interrupt Cause Register 3     | ICR3          | Read-only  | N/A        |

| )x204  | Interrupt Cause Register 2     | ICR2          | Read-only  | N/A        |

| x208   | Interrupt Cause Register 1     | ICR1          | Read-only  | N/A        |

| x20C   | Interrupt Cause Register 0     | ICR0          | Read-only  | N/A        |

Table 2: INTC Register Memory Map

#### 3.1.3 Power Manager(PM)

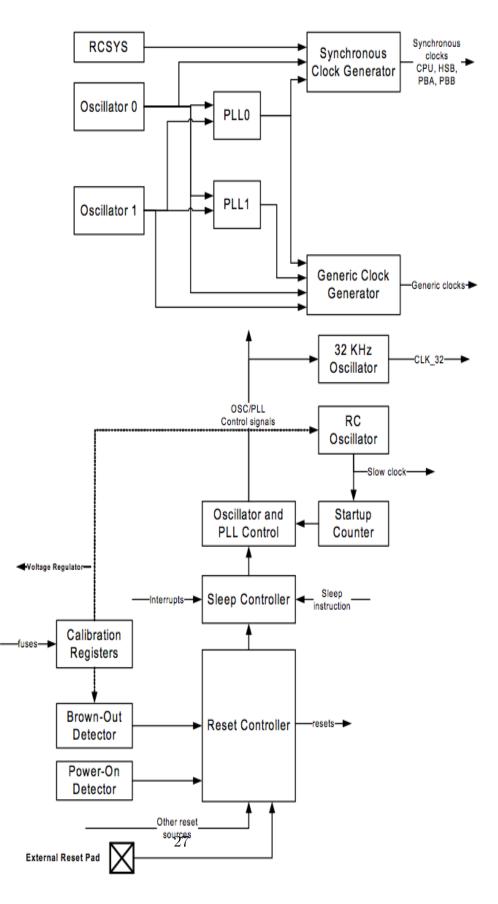

**Overview** The Power Manager (PM) controls the oscillators and PLLs, and generates the clocks and resets in the device. The PM controls two fast crystal oscillators, as well as two PLLs, which can multiply the clock from either oscillator to provide higher frequencies. Additionally, a low-power 32KHz oscillator is used to generate the real-time counter clock for high accuracy real-time measurements. The PM also contains a low-power RC oscillator with fast start-up time, which can be used to clock the digital logic.

The provided clocks are divided into synchronous and generic clocks. The synchronous clocks are used to clock the main digital logic in the device, namely the CPU, and the modules and peripherals connected to the HSB, PBA, and PBB buses. The generic clocks are asynchronous clocks, which can be tuned precisely within a wide frequency range, which makes them suitable for peripherals that require specific frequencies, such as timers and communication modules.

The PM also contains advanced power-saving features, allowing the user to optimize the power consumption for an application. The synchronous clocks are divided into three clock domains, one for the CPU and HSB, one for modules on the PBA bus, and one for modules on the PBB bus. The three clocks can run at different speeds, so the user can save power by running peripherals at a relatively low clock, while maintaining a high CPU performance. Additionally, the clocks can be independently changed on-the-fly, without halting any peripherals. This enables the user to adjust the speed of the CPU and memories to the dynamic load of the application, without disturbing or re-configuring active peripherals.

Each module also has a separate clock, enabling the user to switch off the clock for inactive modules, to save further power. Additionally, clocks and oscillators can be automatically switched off during idle periods by using the sleep instruction on the CPU. The system will return to normal on occurrence of interrupts.

The Power Manager also contains a Reset Controller, which collects all possible reset sources, generates hard and soft resets, and allows the reset source to be identified by software.

**Block Diagram**

Figure 8: Power Manager Block Diagram

#### **Product Dependencies**

I/O Lines The PM provides a number of generic clock outputs, which can be connected to output pins, multiplexed with I/O lines. The user must first program the I/O controller to assign these pins to their peripheral function. If the I/O pins of the PM are not used by the application, they can be used for other purposes by the I/O controller.

**Interrupt** The PM interrupt line is connected to one of the internal sources of the interrupt controller. Using the PM interrupt requires the interrupt controller to be programmed first.

#### **Functional Description**

**Slow Clock** The slow clock is generated from an internal RC oscillator which is always running, except in Static mode. The slow clock can be used for the main clock in the device. The slow clock is also used for the Watchdog Timer and measuring various delays in the Power Manager.

The RC oscillator has a 3 cycles startup time, and is always available when the CPU is running. The RC oscillator operates at approximately 115 kHz. Software can change RC oscillator calibration through the use of the RCCR register.

RC oscillator can also be used as the RTC clock when crystal accuracy is not required.

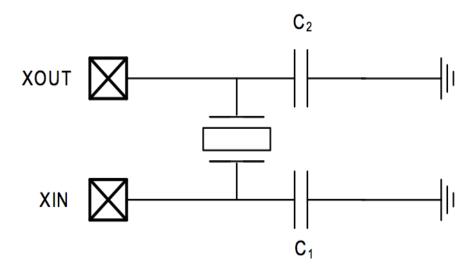

**Oscillator 0 and 1 Operation** The two main oscillators are designed to be used with an external crystal and two biasing capacitors, as shown in Figure 9. Oscillator 0 can be used for the main clock in the device. Both oscillators can be used as source for the generic clocks.

The oscillators are disabled by default after reset. When the oscillators are disabled, the XIN and XOUT pins can be used as general purpose I/Os. When the oscillators are configured to use an external clock, the clock must be applied to the XIN pin while the XOUT pin can be used as a general purpose I/O.

The oscillators can be enabled by writing to the OSCnEN bits in MCCTRL. Operation mode (external clock or crystal) is chosen by writing to the MODE field in OSCCTRLn. Oscillators are automatically switched off in certain sleep modes to reduce power consumption.

After a hard reset, or when waking up from a sleep mode that disabled the oscillators, the oscillators may need a certain amount of time to stabilize on the correct frequency. This start-up time can be set in the OSCCTRLn register.

The PM masks the oscillator outputs during the start-up time, to ensure that no unstable clocks propagate to the digital logic. The OSCnRDY bits in POSCSR are automatically set and cleared according to the status of the oscillators. A zero to one transition on these bits can also be configured to generate an interrupt.

Figure 9: Oscillator Connections

**32 KHz Oscillator Operation** The 32 KHz oscillator operates as described for Oscillator 0 and 1 above. The 32 KHz oscillator is used as source clock for the Real-Time Counter.

The oscillator is disabled by default, but can be enabled by writing OSC32EN in OSCCTRL32. The oscillator is an ultra-low power design and remains enabled in all sleep modes except Static mode.

While the 32 KHz oscillator is disabled, the XIN32 and XOUT32 pins are available as general purpose I/Os. When the oscillator is configured to work

with an external clock (MODE field in OSCCTRL32 register), the external clock must be connected to XIN32 while the XOUT32 pin can be used as a general purpose I/O.

The startup time of the 32 KHz oscillator can be set in the OSCCTRL32, after which OSC32RDY in POSCSR is set. An interrupt can be generated on a zero to one transition of OSC32RDY.

As a crystal oscillator usually requires a very long startup time (up to 1 second), the 32 KHz oscillator will keep running across resets, except Power-On-Reset.

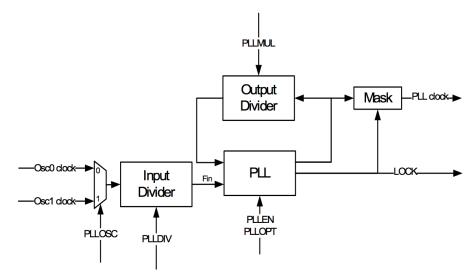

**PLL Operation** The device contains two PLLs, PLL0 and PLL1. These are disabled by default, but can be enabled to provide high frequency source clocks for synchronous or generic clocks. The PLLs can take either Oscillator 0 or 1 as reference clock. The PLL output is divided by a multiplication factor, and the PLL compares the resulting clock to the reference clock. The PLL will adjust its output frequency until the two compared clocks are equal, thus locking the output frequency to a multiple of the reference clock frequency.

When the PLL is switched on, or when changing the clock source or multiplication factor for the PLL, the PLL is unlocked and the output frequency is undefined. The PLL clock for the digital logic is automatically masked when the PLL is unlocked, to prevent connected digital logic from receiving a too high frequency and thus become unstable.

Figure 10: PLL with Control Logic and Filters

**Enabling the PLL:** PLLn is enabled by writing the PLLEN bit in the PLLn register. PLLOSC selects Oscillator 0 or 1 as clock source. The PLL-MUL and PLLDIV bitfields must be written with the multiplication and division factors, respectively, creating the voltage controlled oscillator frequency f\_VCO and the PLL frequency f\_PLL:

if

$$PLLDIV > 0$$

$f_{IN} = \frac{f_{OSC}}{2.PLL_{DIV}}$

$f_{VCO} = \frac{(PLLMUL+1)}{(PLLDIV).f_{OSC}}$

if  $PLLDIV = 0$

$f_{IN} = f_{OSC}$

$f_{VCO} = 2.(PLLMUL + 1).f_{OSC}$

Note: Refer to Electrical Characteristics section for  $F_{IN}$  and  $F_{VCO}$  frequency range.

if PLLOPT[1] field is set to 0:

$f_{PLL} = f_{VCO}$ if PLLOPT[1] field is set to 1:

$f_{PLL} = f_{VCO}/2$

The PLLn: PLLOPT field should be set to proper values according to the PLL operating frequency. The PLLOPT field can also be set to divide the output frequency of the PLLs by 2.

The lock signal for each PLL is available as a LOCKn flag in POSCSR. An interrupt can be generated on a 0 to 1 transition of these bits.

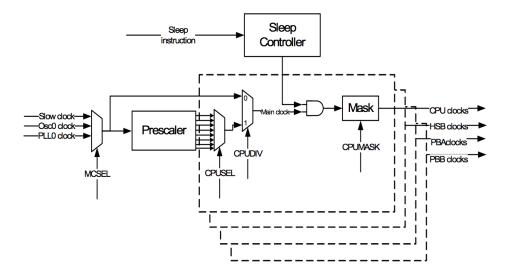

**Synchronous Clocks** The slow clock (default), Oscillator 0, or PLL0 provide the source for the main clock, which is the common root for the synchronous clocks for the CPU/HSB, PBA, and PBB modules. The main clock is divided by an 8-bit prescaler, and each of these four synchronous clocks can run from any tapping of this prescaler, or the undivided main clock, as long as  $f_{CPU} \geq f_{PBA,B}$ .

The synchronous clock source can be changed on-the fly, responding to varying load in the application. The clock domains can be shut down in sleep mode. Additionally, the clocks for each module in the four domains can be individually masked, to avoid power consumption in inactive modules.

Figure 11: Synchronous Clock Generation

Selecting PLL or oscillator for the main clock The common main clock can be connected to the slow clock, Oscillator 0, or PLL0. By default, the main clock will be connected to the slow clock. The user can connect the main clock to Oscillator 0 or PLL0 by writing the MCSEL field in the Main Clock Control Register (MCCTRL). This must only be done after that unit has been enabled, otherwise a deadlock will occur. Care should also be taken that the new frequency of the synchronous clocks does not exceed the maximum frequency for each clock domain.

Selecting synchronous clock division ratio The main clock feeds an 8-bit prescaler, which can be used to generate the synchronous clocks. By default, the synchronous clocks run on the undivided main clock. The user can select a prescaler division for the CPU clock by writing CKSEL.CPUDIV to 1 and CPUSEL to the prescaling value, resulting in a CPU clock frequency:

$f_{CPU} = f_{main}/2^{(CPUSEL+1)}$

Similarly, the clock for the PBA, and PBB can be divided by writing their respective fields. To ensure correct operation, frequencies must be selected so that  $f_{CPU} \geq f_{PBA,B}$ . Also, frequencies must never exceed the specified maximum frequency for each clock domain.

CKSEL can be written without halting or disabling peripheral modules. Writing CKSEL allows a new clock setting to be written to all synchronous clocks at the same time. It is possible to keep one or more clocks unchanged by writing the same value a before to the xxxDIV and xxxSEL fields. This way, it is possible to e.g. scale CPU and HSB speed according to the required performance, while keeping the PBA and PBB frequency constant.

For modules connected to the HSB bus, the PB clock frequency must be set to the same frequency than the CPU clock.

**Clock ready flag** There is a slight delay from CKSEL is written and the new clock setting becomes effective. During this interval, the Clock Ready (CKRDY) flag in ISR will read as 0. If IER.CKRDY is written to one, the Power Manager interrupt can be triggered when the new clock setting is effective. CKSEL must not be re-written while CKRDY is zero, or the system may become unstable or hang.

**Peripheral Clock Masking** By default, the clock for all modules are enabled, regardless of which modules are actually being used. It is possible to disable the clock for a module in the CPU, HSB, PBA, or PBB clock domain by writing the corresponding bit in the Clock Mask register (CPU/HSB/P-BA/PBB) to 0. When a module is not clocked, it will cease operation, and its registers cannot be read or written. The module can be re-enabled later by writing the corresponding mask bit to 1.

A module may be connected to several clock domains, in which case it will have several mask bits.

**Cautionary note** The OCD clock must never be switched off if the user wishes to debug the device with a JTAG debugger.

Note that clocks should only be switched off if it is certain that the module will not be used. Switching off the clock for the internal RAM will cause a problem if the stack is mapped there. Switching off the clock to the Power Manager (PM), which contains the mask registers, or the corresponding PBx bridge, will make it impossible to write the mask registers again. In this case, they can only be re-enabled by a system reset.

**Mask ready flag** Due to synchronisation in the clock generator, there is a slight delay from a mask register is written until the new mask setting goes into effect. When clearing mask bits, this delay can usually be ignored. However, when setting mask bits, the registers in the corresponding module must not be written until the clock has actually be re-enabled. The status flag MSKRDY in ISR pro- vides the required mask status information. When writing either mask register with any value, this bit is cleared. The bit is set when the clocks have been enabled and disabled according to the new mask setting. Optionally, the Power Manager interrupt can be enabled by writing the MSKRDY bit in IER.

**Sleep Modes** In normal operation, all clock domains are active, allowing software execution and peripheral operation. When the CPU is idle, it is possible to switch off the CPU clock and optionally other clock domains to save power. This is activated by the sleep instruction, which takes the sleep mode index number as argument.

**Entering and exiting sleep modes** The sleep instruction will halt the CPU and all modules belonging to the stopped clock domains. The modules will be halted regardless of the bit settings of the mask registers.

Oscillators and PLLs can also be switched off to save power. Some of these modules have a relatively long start-up time, and are only switched off when very low power consumption is required.

The CPU and affected modules are restarted when the sleep mode is exited. This occurs when an interrupt triggers. Note that even if an interrupt is enabled in sleep mode, it may not trigger if the source module is not clocked.

Supported sleep modes The following sleep modes are supported.

Idle: The CPU is stopped, the rest of the chip is operating. Wake-up sources are any interrupt.

Frozen: The CPU and HSB modules are stopped, peripherals are operating. Wake-up sources are any interrupt from PB modules.

Standby: All synchronous clocks are stopped, but oscillators and PLLs are running, allowing quick wake-up to normal mode. Wake-up sources are RTC or external interrupt.

Stop: As Standby, but Oscillator 0 and 1, and the PLLs are stopped. 32 KHz (if enabled) and RC oscillators and RTC/WDT still operate. Wake-up sources are RTC, external interrupt, or external reset pin.

DeepStop: All synchronous clocks, Oscillator 0 and 1 and PLL 0 and 1 are stopped. 32 KHz oscillator can run if enabled. RC oscillator still operates. Bandgap voltage reference, BOD and BOD33 are turned off. Wake-up sources are RTC, external interrupt (EIC) or external reset pin.

Static: All oscillators, including 32 KHz and RC oscillator are stopped. Bandgap voltage reference, BOD and BOD33 detectors are turned off. Wakeup sources are external interrupt (EIC) in asynchronous mode only or external reset pin.

| Index | Sleep Mode | CPU  | HSB  | PBA,B<br>GCLK | Osc0,1<br>PLL0,1,<br>SYSTIMER | Osc32 | RCSYS | BOD &<br>BOD33 &<br>Bandgap | Voltage<br>Regulator |

|-------|------------|------|------|---------------|-------------------------------|-------|-------|-----------------------------|----------------------|

| 0     | Idle       | Stop | Run  | Run           | Run                           | Run   | Run   | On                          | Full power           |

| 1     | Frozen     | Stop | Stop | Run           | Run                           | Run   | Run   | On                          | Full power           |

| 2     | Standby    | Stop | Stop | Stop          | Run                           | Run   | Run   | On                          | Full power           |

| 3     | Stop       | Stop | Stop | Stop          | Stop                          | Run   | Run   | On                          | Low power            |

| 4     | DeepStop   | Stop | Stop | Stop          | Stop                          | Run   | Run   | Off                         | Low power            |

| 5     | Static     | Stop | Stop | Stop          | Stop                          | Stop  | Stop  | Off                         | Low power            |

Table 3: Sleep Modes

The power level of the internal voltage regulator is also adjusted according to the sleep mode to reduce the internal regulator power consumption.

**Precautions when entering sleep mode** Modules communicating with external circuits should normally be disabled before entering a sleep mode that will stop the module operation. This prevents erratic behavior when entering or exiting sleep mode.

Communication between the synchronous clock domains is disturbed when entering and exiting sleep modes. This means that bus transactions are not allowed between clock domains affected by the sleep mode. The system may hang if the bus clocks are stopped in the middle of a bus transaction.

The CPU is automatically stopped in a safe state to ensure that all CPU bus operations are complete when the sleep mode goes into effect. Thus, when entering Idle mode, no further action is necessary.

When entering a sleep mode (except Idle mode), all HSB masters must be stopped before entering the sleep mode. Also, if there is a chance that any PB write operations are incomplete, the CPU should perform a read operation from any register on the PB bus before executing the sleep instruction. This will stall the CPU while waiting for any pending PB operations to complete.

When entering a sleep mode deeper or equal to DeepStop, the VBus asynchronous interrupt should be disabled (USBCON.VBUSTE = 0).

**Wake Up** The USB can be used to wake up the part from sleep modes through register AWEN of the Power Manager.

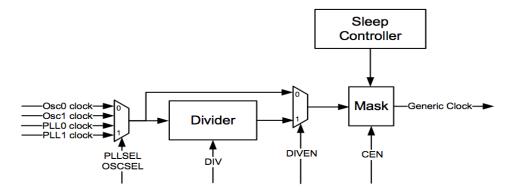

**Generic Clocks** Timers, communication modules, and other modules connected to external circuitry may require specific clock frequencies to operate correctly. The Power Manager contains an implementation defined number of generic clocks that can provide a wide range of accurate clock frequencies.

Each generic clock module runs from either Oscillator 0 or 1, or PLL0 or 1. The selected source can optionally be divided by any even integer up to 512. Each clock can be independently enabled and disabled, and is also automatically disabled along with peripheral clocks by the Sleep Controller.

Figure 12: Generic Clock Generation

**Enabling a generic clock** A generic clock is enabled by writing the CEN bit in GCCTRL to 1. Each generic clock can use either Oscillator 0 or 1 or PLL0 or 1 as source, as selected by the PLLSEL and OSCSEL bits. The source clock can optionally be divided by writing DIVEN to 1 and the division factor to DIV, resulting in the output frequency:

$f_{GCLK} = f_{SRC} / (2.(DIV + 1))$

**Disabling a generic clock** The generic clock can be disabled by writing CEN to zero or entering a sleep mode that disables the PB clocks. In either case, the generic clock will be switched off on the first falling edge after the disabling event, to ensure that no glitches occur. If CEN is written to 0, the bit will still read as 1 until the next falling edge occurs, and the clock is actually switched off. When writing CEN to 0, the other bits in GCCTRL should not be changed until CEN reads as 0, to avoid glitches on the generic clock.

When the clock is disabled, both the prescaler and output are reset.

**Changing clock frequency** When changing generic clock frequency by writing GCCTRL, the clock should be switched off by the procedure above, before being re-enabled with the new clock source or division setting. This prevents glitches during the transition.

**Generic clock implementation** The generic clocks are allocated to different functions as shown in Table 4.

| Clock number | Function   |

|--------------|------------|

| 0            | GCLK0 pin  |

| 1            | GCLK1 pin  |

| 2            | GCLK2 pin  |

| 3            | GCLK3 pin  |

| 4            | GCLK_USBB  |

| 5            | GCLK_ABDAC |

Table 4: Generic Clock Allocation

**Divided PB Clocks** The clock generator in the Power Manager provides divided PBA and PBB clocks for use by peripherals that require a prescaled PBx clock.

The divided clocks are not directly maskable, but are stopped in sleep modes where the PBx clocks are stopped.

**Debug Operation** The OCD clock must never be switched off if the user wishes to debug the device with a JTAG debugger.

During a debug session, the user may need to halt the system to inspect memory and CPU registers. The clocks normally keep running during this debug operation, but some peripherals may require the clocks to be stopped, e.g. to prevent timer overflow, which would cause the program to fail. For this reason, peripherals on the PBA and PBB buses may use "debug qualified" PBx clocks. The divided PBx clocks are always debug qualified clocks.

Debug qualified PBx clocks are stopped during debug operation. The debug system can optionally keep these clocks running during the debug operation.

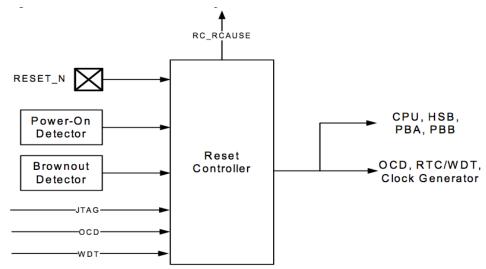

**Reset Controller** The Reset Controller collects the various reset sources in the system and generates hard and soft resets for the digital logic.

The device contains a Power-On Detector, which keeps the system reset until power is stable. This eliminates the need for external reset circuitry to guarantee stable operation when powering up the device.

It is also possible to reset the device by asserting the RESET\_N pin. This pin has an internal pullup, and does not need to be driven externally when negated. Table 5 lists these and other reset sources supported by the Reset Controller.

Figure 13: Reset Controller Block Diagram

In addition to the listed reset types, the JTAG can keep parts of the device

statically reset through the JTAG Reset Register.

| Reset source   | Description                                                                 |

|----------------|-----------------------------------------------------------------------------|

| Power-on Reset | Supply voltage below the power-on reset detector threshold voltage          |

| External Reset | RESET_N pin asserted                                                        |

| Brownout Reset | Supply voltage below the brownout reset detector threshold voltage          |

| CPU Error      | Caused by an illegal CPU access to external memory while in Supervisor mode |

| Watchdog Timer | See watchdog timer documentation.                                           |

| OCD            | See On-Chip Debug documentation                                             |

#### Table 5: Reset Description

When a reset occurs, some parts of the chip are not necessarily reset, depending on the reset source. Only the Power On Reset (POR) will force a reset of the whole chip.

|                                              | Power-On<br>Reset | External<br>Reset | Watchdog<br>Reset | BOD<br>Reset | BOD33<br>Reset | CPU<br>Error<br>Reset | OCD<br>Reset |

|----------------------------------------------|-------------------|-------------------|-------------------|--------------|----------------|-----------------------|--------------|

| CPU/HSB/PBA/PBB<br>(excluding Power Manager) | Y                 | Y                 | Y                 | Y            | Y              | Y                     | Y            |

| 32 KHz oscillator                            | Y                 | N                 | N                 | N            | N              | N                     | N            |

| RTC control register                         | Y                 | N                 | N                 | N            | N              | N                     | N            |

| GPLP registers                               | Y                 | N                 | N                 | N            | N              | N                     | N            |

| Watchdog control register                    | Y                 | Y                 | N                 | Y            | Y              | Y                     | Y            |

| Voltage calibration register                 | Y                 | N                 | N                 | N            | N              | N                     | N            |

| RCSYS Calibration register                   | Y                 | N                 | N                 | N            | N              | N                     | N            |

| BOD control register                         | Y                 | Y                 | N                 | N            | N              | N                     | N            |

| BOD33 control register                       | Y                 | Y                 | N                 | N            | N              | N                     | N            |

| Bandgap control register                     | Y                 | Y                 | N                 | N            | N              | N                     | N            |

| Clock control registers                      | Y                 | Y                 | Y                 | Y            | Y              | Y                     | Y            |

| Osc0/Osc1 and control registers              | Y                 | Y                 | Y                 | Y            | Y              | Y                     | Y            |

| PLL0/PLL1 and control registers              | Y                 | Y                 | Y                 | Y            | Y              | Y                     | Y            |

| OCD system and OCD registers                 | Y                 | Y                 | N                 | Y            | Y              | Y                     | N            |

Table 6: Effect of the Different Reset Events

The cause of the last reset can be read from the RCAUSE register. This register contains one bit for each reset source, and can be read during the boot sequence of an application to determine the proper action to be taken.

**Power-On detector** The Power-On Detector monitors the VDDCORE supply pin and generates a reset when the device is powered on. The reset is active until the supply voltage from the linear regulator is above the power-on threshold level. The reset will be re-activated if the voltage drops below the power-on threshold level.

**Brown-Out detector** The Brown-Out Detector (BOD) monitors the VD-DCORE supply pin and compares the supply voltage to the brown-out detection level, as set in BOD.LEVEL. The BOD is disabled by default, but can be enabled either by software or by flash fuses. The Brown-Out Detector can either generate an interrupt or a reset when the supply voltage is below the brown-out detection level. In any case, the BOD output is available in bit POSCSR.BODDET bit.

Note that any change to the BOD.LEVEL field of the BOD register should be done with the BOD deactivated to avoid spurious reset or interrupt.

**Brown-Out detector 3V3** The Brown-Out Detector 3V3 (BOD33) monitors one VDDIO supply pin and compares the supply voltage to the brownout detection 3V3 level, which is typically calibrated at 2V7. The BOD33 is enabled by default, but can be disabled by software. The Brown-Out Detector 3V3 can either generate an interrupt or a reset when the supply voltage is below the brown-out detection3V3 level. In any case, the BOD33 output is available in bit POSCSR.BOD33DET bit.

Note that any change to the BOD33.LEVEL field of the BOD33 register should be done with the BOD33 deactivated to avoid spurious reset or interrupt.

| TFBGA144 | QFP144 | VFBGA100 |

|----------|--------|----------|

| H5       | 81     | E5       |

The BOD33.LEVEL default value is calibrated to 2V7

Table 7: VDDIO pin monitored by BOD33

**External reset** The external reset detector monitors the state of the RE-SET\_N pin. By default, a low level on this pin will generate a reset.

**Calibration Registers** The Power Manager controls the calibration of the RC oscillator, voltage regulator, bandgap voltage reference through several calibrations registers.

Those calibration registers are loaded after a Power On Reset with default values stored in factory-programmed flash fuses.

Although it is not recommended to override default factory settings, it is still possible to override these default values by writing to those registers. To prevent unexpected writes due to software bugs, write access to these registers is protected by a "key". First, a write to the register must be made with the field "KEY" equal to 0x55 then a second write must be issued with the "KEY" field equal to 0xAA.

| Offset | Register                              | Register Name | Access     | Reset State                         |

|--------|---------------------------------------|---------------|------------|-------------------------------------|

| 0x000  | Main Clock Control                    | MCCTRL        | Read/Write | 0x00000000                          |

| 0x0004 | Clock Select                          | CKSEL         | Read/Write | 0x00000000                          |

| 0x008  | CPU Mask                              | CPUMASK       | Read/Write | 0x00000003                          |

| 0x00C  | HSB Mask                              | HSBMASK       | Read/Write | 0x00000FFF                          |

| 0x010  | PBA Mask                              | PBAMASK       | Read/Write | 0x001FFFFF                          |

| 0x014  | PBB Mask                              | PBBMASK       | Read/Write | 0x000003FF                          |

| 0x020  | PLL0 Control                          | PLLO          | Read/Write | 0x00000000                          |

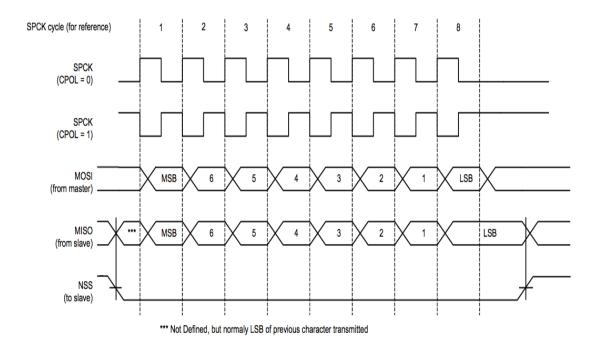

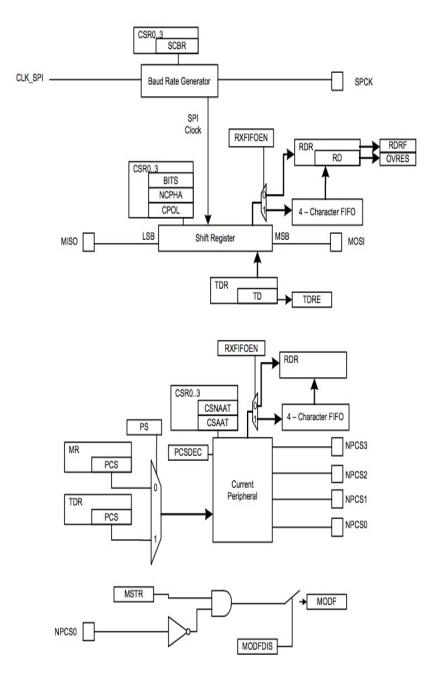

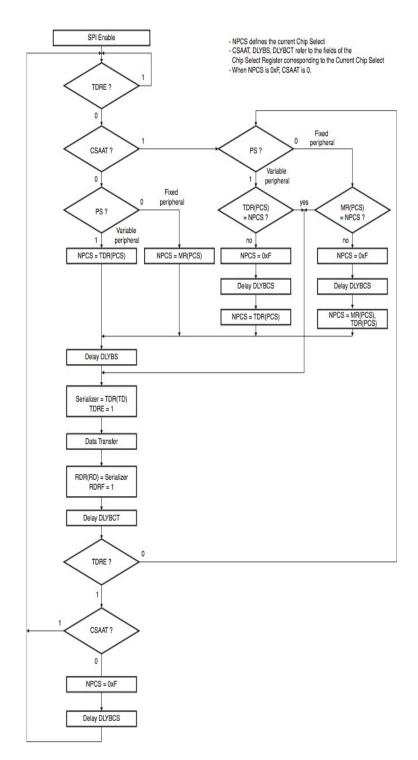

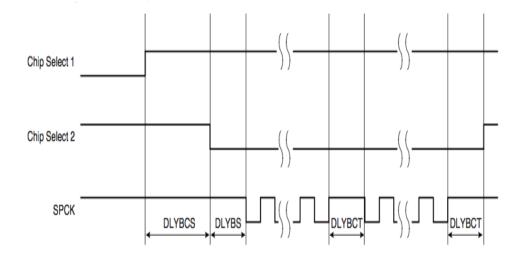

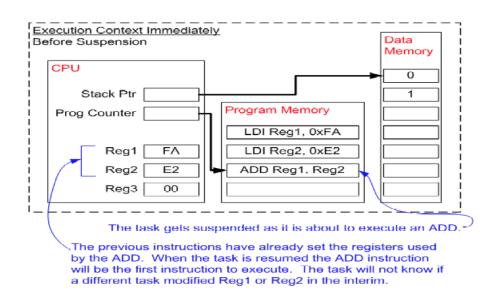

| 0x024  | PLL1 Control                          | PLL1          | Read/Write | 0x00000000                          |