| rsion)<br>rsion)<br>-8181 |                                                                              | Kristoffer Nyborg Gregertsen     | Doctoral theses at NTNU, 2012:78Kristoffer Nyborg GregertsenExecution time controlA hardware accelerated Ada<br>implementation with novel<br>support for interrupt handling                                         |

|---------------------------|------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | <b>NTNU – Trondheim</b><br>Norwegian University of<br>Science and Technology | Doctoral theses at NTNU, 2012:78 | Nruegian University of Science and Technology.<br>Mathematics and Electrical Engineering<br>Department of Engineering Cybernetics<br>Department of Engineering Cybernetics<br>Department of Engineering Cybernetics |

ISBN 978-82-471-3429-0 (printed ver ISBN 978-82-471-3430-6 (electronic ver ISSN 1503-

o ntnu

Kristoffer Nyborg Gregertsen

# Execution time control

A hardware accelerated Ada implementation with novel support for interrupt handling

Thesis for the degree of Philosophiae Doctor

Trondheim, April 2012

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Engineering Cybernetics

**NTNU – Trondheim** Norwegian University of Science and Technology

### NTNU

Norwegian University of Science and Technology

Thesis for the degree of Philosophiae Doctor

Faculty of Information Technology, Mathematics and Electrical Engineering Department of Engineering Cybernetics

© Kristoffer Nyborg Gregertsen

ISBN 978-82-471-3429-0 (printed version) ISBN 978-82-471-3430-6 (electronic version) ISSN 1503-8181

ITK Report 2012-2-W

Doctoral theses at NTNU, 2012:78

Printed by Skipnes Kommunikasjon as

Til Christine og Edvard.

# **Summary**

Execution time control is a technique that allows execution time budgets to be set and overruns to be handled dynamically to prevent deadline misses. This removes the need for the worst-case execution time (WCET) of tasks to be found by offline timing analysis – a problem that can be very hard to solve for modern computer architectures. Execution time control can also increase the processor utilization, as the WCET will often be much higher than the average execution time.

This thesis describes how the GNU Ada Compiler and a bare-board Ravenscar runtime environment were ported to the Atmel AVR® 32 UC3 microcontroller series making the Ada programming language available on this architecture for the first time, and an implementation of Ada execution time control for this system that supports full execution time control for interrupt handling. Usage patterns for this brand new feature are demonstrated in Ada by extending the object-oriented realtime framework with execution time servers for interrupt handling, allowing the system to be protected against unexpected bursts of interrupts that could otherwise result in deadline misses. Separate execution time measurement for interrupt handling also improves the accuracy of measurement for tasks. As a direct result of the work presented in this thesis separate execution time measurement for interrupts will be included in the forthcoming ISO-standard for Ada 2012.

While the implementation of execution time control is for the Ada programming language and the UC3 microcontroller series, the design and implementation should be portable to other architectures, and the principles of execution time control for interrupt handling applicable to other programming languages.

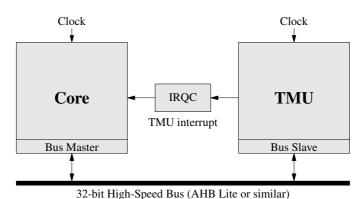

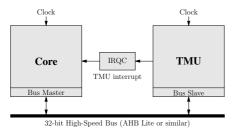

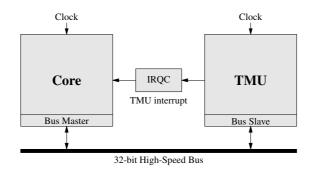

Low run-time overhead is important for execution time control to be useful for realtime systems. Therefore a hardware Time Management Unit (TMU) was designed to reduce the overhead of execution time control. This design has been implemented for the UC3 and performance tests with the developed run-time environment shows that it gives a significant reduction of overhead. The memory-mapped design of the TMU also allows it to be implemented on other architectures.

# Contents

| Su | Summary |                                                   |     |  |  |  |

|----|---------|---------------------------------------------------|-----|--|--|--|

| Co | onten   | ts                                                | vii |  |  |  |

| Pr | eface   |                                                   | ix  |  |  |  |

| 1  | Intr    | oduction                                          | 1   |  |  |  |

|    | 1.1     | Background and motivation                         | 1   |  |  |  |

|    | 1.2     | Research goals and methods                        | 5   |  |  |  |

|    | 1.3     | Related work                                      | 6   |  |  |  |

|    | 1.4     | Thesis organization                               | 8   |  |  |  |

| 2  | Bac     | kground theory                                    | 9   |  |  |  |

|    | 2.1     | Real-time systems and execution time control      | 9   |  |  |  |

|    | 2.2     | The Ada programming language                      | 15  |  |  |  |

|    | 2.3     | The GNU Ada Compiler (GNAT)                       | 22  |  |  |  |

|    | 2.4     | The Atmel AVR32 architecture                      | 25  |  |  |  |

| 3  | Mai     | n contributions                                   | 29  |  |  |  |

|    | 3.1     | GNAT for AVR32                                    | 29  |  |  |  |

|    | 3.2     | Implementation of Ada 2005 execution time control | 30  |  |  |  |

|    | 3.3     | Usage of execution time control in Ada            | 33  |  |  |  |

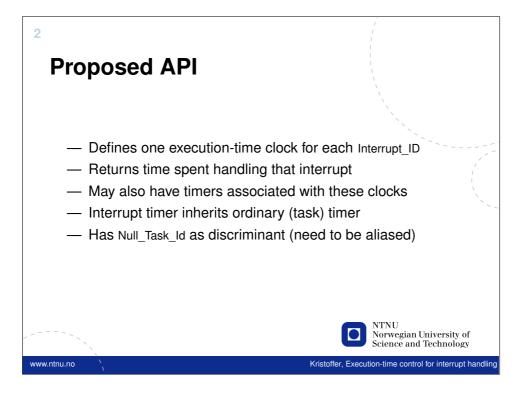

|    | 3.4     | IRTAW-14 and ISO standardization                  | 34  |  |  |  |

|    | 3.5     | Implementation of Ada 2012 execution time control | 36  |  |  |  |

|    | 3.6     | The hardware Time Management Unit (TMU)           | 41  |  |  |  |

|    | 3.7     | Ada 2012 execution time control using the TMU     | 44  |  |  |  |

| 4  | Con     | clusions and future work                          | 49  |  |  |  |

|    | 4.1     | Evaluation of contributions                       | 49  |  |  |  |

|    | 4.2     | Future work                                       | 51  |  |  |  |

| A | Publ                                       | ished material                                  | 61  |  |

|---|--------------------------------------------|-------------------------------------------------|-----|--|

|   | A.1                                        | Article No. 1                                   | 63  |  |

|   | A.2                                        | Article No. 2                                   | 69  |  |

|   | A.3                                        | Article No. 3                                   | 79  |  |

|   | A.4                                        | Article No. 4                                   | 93  |  |

|   | A.5                                        | Article No. 5                                   | 109 |  |

|   | A.6                                        | Article No. 6                                   | 115 |  |

|   | A.7                                        | Article No. 7                                   | 129 |  |

| B | Pres                                       | entations at IRTAW-14                           | 147 |  |

| С | GNA                                        | TforAVR32                                       | 157 |  |

|   | C.1                                        | Installing GNAT on the host machine             | 157 |  |

|   | C.2 Installing the GNU toolchain for AVR32 |                                                 |     |  |

|   | C.3                                        | Obtaining and building the cross compiler       |     |  |

|   | C.4                                        | Obtaining and building the run-time environment | 159 |  |

|   | C.5                                        | Debugging applications                          | 160 |  |

| D | Addi                                       | itional listings                                | 161 |  |

# Preface

The research work leading to this thesis was funded by a PhD grant given by the Faculty of Information Technology, Mathematics and Electrical Engineering at the Norwegian University of Technology and Science (NTNU). Getting this grant allowed me the great privilege of choosing a research topic after my own interest. This allowed me to continue my research on execution time control for the Ada programming language that I started with my master thesis. I wish to express my gratitude to the Norwegian taxpayers who in the end have financed my work, and believe my work is a contribution to more reliable embedded systems.

My research work has also been a journey through Norway. I started working on this thesis after finishing my master degree in 2008, when my spouse and I moved to the beautiful small town of Ålesund for a year. Luckily, Ålesund University College provided me with an office, and a stimulating work environment during this critical first phase of my research. After the year in Ålesund, we moved to the little village Ørsta. We lived there between the fjords and mountains for one and a half year. While it sometimes was hard to work in the solitude of my home office, living with the amazing nature literally right outside the door made up for it.

In 2011 we moved back to Trondheim and I could finally be with colleagues again. Shortly after we got our first child. Becoming a father also meant little sleep at night and lots of work, but I would not change it for anything in the world. In the fall the final pieces of the research work were put into place, and we also moved into our first house. This thesis was completed while I stayed home with my son which was quite challenging, having to write in stole moments while he slept at daytime, in evenings, and during weekends. Luckily, the thesis was mostly finished before this, and I could enjoy the time with my son without worrying to much about it.

### Acknowledgments

This thesis would never have been written without the support of my advisor, Amund Skavhaug. He recruited me already in the third year of my master study, and guided me in selecting relevant courses within real-time systems, computer architecture and electronics. It was also Amund who encouraged and helped me to apply for the PhD grant, and helped me select the research topic. During my PhD work he always supported me with my research, but also with more personal matters. He has reminded me that there are other things to life than just work. Amund often talks about his past as a badminton coach, and how he has adapted the coach attitude in guiding his students. One can really tell that this is true by the quality of his work. You are the best advisor I could ever hope for, Amund.

My gratitude also goes to the companies Atmel Norway and AdaCore, who have supported me in my research effort. Atmel Norway has provided hardware and open-source development tools, and allowed the TMU to be implemented and tested with the AVR32 UC3 microcontroller. Special thanks to Ronny Pedersen for supporting GCC for AVR32, master student Stian Søvik at NTNU for implementing the TMU, and Frode Sundal and Martin Olsson for helping me with the testing. Thanks to AdaCore for providing the open-source version of GNAT that has been used throughout this research. Special thanks to José F. Ruiz for helping porting the Ravenscar run-time to the AVR32.

I wish to thank Ålesund University College for providing me with an office for the year I stayed, and all the nice people there for being so welcoming and inspiring. You always made me feel like one of you.

Another bunch of kind people are those of the Ada real-time community, many of whom I met at IRTAW-14 in Portovenere. I felt welcomed and appreciated among you, and hope to meet you all again in the years that come. Special thanks to Alan Burns for encouraging me to participate at the workshop, and Juan de la Puente and Juan Zamorano for taking me to see "Cinque Terre".

I would like to thank my family who has always supported and believed in me. My mother and father have nourished my curiosity through my childhood, taking me to the museum of natural history in my home town Stavanger about every week. After walking that much among stuffed animals I probably should have become a zoologist, and I would therefore like to thank my uncle Knut for introducing me to computers. It may have been the turbo switch on your 486 that triggered the process leading to a PhD in real-time systems.

Many thanks to my good friends Henrik and Robin for proof-reading the thesis.

Finally, I would like to thank the love of my life Christine, without whom I could not have finished the PhD with my sanity intact. You have always encouraged me in my research work, while making sure that this work did not expand to fill my whole life. You have also provided good reality orientation when needed. We have also been blessed with a beautiful son Edvard, who has given my life a whole new perspective and provided yet another reason to get the PhD done.

# Chapter 1

# Introduction

## 1.1 Background and motivation

*Embedded systems* are everywhere in today's society – to such an extent that we take their functionality for granted. They are present in equipment such as mobile phones, washing machines and televisions that we use every day, and in automobiles, airplanes and rail-road systems upon which our lives depend when we use them. A sign of this omnipresence is that the sale of processors for embedded systems far outweigh that of processors used in personal computers and servers. Common for embedded systems is that they are an integral part of the larger system that depend on its functionality. Therefore, the malfunction of an embedded system may cause great economic losses, or in the worst case, even result in material damage and loss of life.

The term *dependability* describes the systems' ability to provide its functionality according to specification. The system experiences a *failure* when this functionality cannot be provided. A failure is caused by an *error* that is a manifestation of an underlying *fault* in the system. Faults may be physical like component wear-out; transient, like electromagnetic interference; intermittent that come and go for instance due to components overheating; or logical human-made faults in hardware, software or the interaction between these. To achieve the desired level of dependability one can apply techniques to prevent faults from being introduced in the design. This is known as *fault prevention*. However, as it is hubris to declare any system fault-free, it is equally important to make sure that errors does not cause failure. This is known as *fault tolerance*.

#### 1.1.1 Real-time systems

As embedded systems often interact with the physical world, they have temporal requirements to the produced output in addition to the value of the output itself. Thus, if the output is not produced on time it is an error in the timing domain. Such systems are commonly known as *real-time* systems.

A *task* is an entity that performs some work in the system, and is *released* either periodically or by some sporadic event. Each release is called an *instance* of the task. Real-time tasks also have an associated *deadline* relative to the release time for finishing their work and producing the output. Deadlines are commonly classified as *hard* if a deadline miss is an error which may result in system failure, *firm* if a missed deadline means that the result has no value but does not cause failure, and *soft* if the value of the result gradually drops after the deadline. In this work deadlines are considered hard unless explicitly stated otherwise.

For practical and economical reasons a set of tasks is usually executed on the same computer, sharing the processor cores and other resources such as data and hard-ware units among them. The resources, and in particular the processor execution time, are shared among the tasks according to some *scheduling policy*. A scheduling policy is *static* if the task priorities are always the same, and *dynamic* if it changes at run-time. *Scheduling analysis* is applied to make sure that system is *schedulable* which means that all tasks will be able to meet their deadlines.

### **1.1.2** Worst-case execution time (WCET)

Scheduling analysis requires the worst-case execution time (WCET) of tasks to be known. The WCET is computed by applying *timing analysis* on the task, either by static analysis of the source code and the compiled executable using an abstract model of the computer architecture, or by measuring the execution time of the task or parts of the task when executed on the targeted hardware [62]. Finding the WCET may be hard for all but the most trivial tasks as a large space of input data and initial conditions need to be considered. Furthermore, timing analysis is made magnitudes harder by performance enhancing techniques such as multi-level cache, deep pipelines with shared execution units, and more. These techniques introduce *timing anomalies* that can be counter-intuitive and hard to predict [62]. Timing analysis is even harder for multi-core computer architectures as the execution on the different cores will be affected by how the others use the coherent cache hierarchy and other shared resources.

The precision of the timing analysis is how close the computed WCET is to the

actual WCET, while the *safety* tells if the timing analysis provides a guaranteed bound for the actual WCET or just a prediction [62]. For hard real-time systems safety is paramount as deadline misses could be the result if the WCET used for scheduling analysis is less than the actual WCET. The overestimation of state-ofthe-art timing analysis tools is reported to be in the range of 30-50% [62]. Furthermore, even if a computed WCET is very precise, the actual WCET can be magnitudes higher than the average execution time, since it includes the unlikely event of several performance enhancing techniques failing at the same time. Therefore, using the WCET as the tasks execution time *budget* leads to waste of computational resources as the tasks usually will require much less execution time than budgeted for in the scheduling analysis. For some systems there may be soft tasks that can utilize the additional available execution time, but this may not always be the case.

A survey published as recently as 2008 describes several state-of-the-art methods and tools for timing analysis, both prototypes and commercial [62]. Out of the many tools listed, all but one assume uninterrupted task execution due to the effects interruption has on the state of the cache, and can therefore not be used with preemptive scheduling. Furthermore, none of the described tools work with multicore processors with a shared cache. The tools also require detailed descriptions of the hardware used, and are therefore limited to a handful of computer architectures used in embedded systems. For high-end architectures using performance enhancing techniques the timing analysis of a task can take as much as a day [62]. While the survey reports that the problem of finding safe bounds to WCET is solved, and that the described tools has found successful use, this use seems to be limited to high-integrity projects with large budgets and long development time, such as the aviation, automotive, defense and space industry.

Timing analysis has been subject of much research effort since the survey of 2008, and recent research does try to address the multi-core WCET problem [16, 35].

### **1.1.3** Execution time control

Execution time control allows dynamic control of the tasks execution time instead of solely relying on static guarantees, and thus provides fault tolerance in the timing domain instead of just fault prevention. This is done by setting an execution time budget for the tasks at release time and handling budget *overruns* according to some application-dependent *policy* to prevent deadlines being lost [60]. Note that execution time properties is needed to set reasonable task budgets. However, as safety is provided by execution time control, the requirements for the timing analysis.

lysis are less strict – guaranteed bounds on the WCET are no longer needed. This means that simpler measurement based techniques can be used to find a reasonable budget for the tasks.

Execution time control is also a prerequisite for execution time servers such as the deferrable and sporadic server that allows for soft sporadic tasks to have short average response time whilst guaranteeing for the deadlines of hard periodic tasks [14]. Furthermore, execution time control facilitates tasks executing algorithms where there is an increasing reward with increased service (IRIS) [36]. In this case, the algorithm is stopped when it has converged or its execution time budget is exhausted. If no acceptable result was computed in time a simpler algorithm may be executed.

The *mechanism* for execution time control is provided by the run-time environment and measures the time a task has been executing on the system by providing a high accuracy execution time clock that can either be explicit or implicitly defined in the system. Execution time monitoring allows applications to provide *handlers* for a clock that are called when the execution time of the clock reaches a specified timeout value. The mechanism for this is referred to as an execution time *timer*, and is a type of *alarm*. The run-time overhead incurred by the mechanisms should be as low as possible for execution time control to be acceptable for use in realtime systems.

### 1.1.4 Interrupts

*Interrupts* cause the normal execution of tasks to be paused and a *handler* to be executed, either as a result of an asynchronous hardware interrupt line being asserted or a synchronous software interrupt being triggered. An interrupt is said to *occur*, and an occurrence is *pending* in the time between its *generation* and its *delivery* to the system in the form of the appropriate handler being called. It depends on the hardware whether a generated interrupt occurrence is lost if another of the same type is already pending.

This work deals with *hardware* interrupts unless explicitly stated otherwise. These interrupts may be generated by components of the computer system such as peripheral units, or by external sources. Often the computer architecture has an interrupt controller that multiplexes and groups interrupt lines, and triggers the interrupt handling on the processor. There may also be several interrupt *levels*, where interrupts may be interrupted by others of a higher level. With the exception of non-maskable interrupts, the delivery of interrupts may be blocked by the use of *masks*. Whether a blocked interrupt remains pending or is lost depends on the

architecture and hardware.

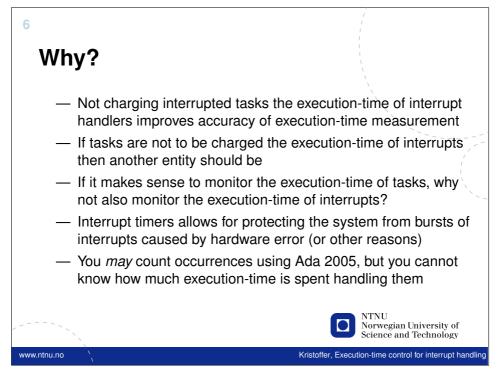

The execution time of interrupt handlers has usually been charged to the interrupted task. This causes inaccuracy in the execution time measurement of tasks, which again means that the budgets of all tasks have to be extended to allow for the additional execution time of interrupt handlers as it cannot be known in advance which tasks will be interrupted. Furthermore, as interrupt handling have higher priority than normal task execution, deadlines may be lost in the case of an unexpected high rate of interrupts, either due to a design or analysis fault, or an error in hardware generating more interrupts than the system can handle. While it is possible to count the number of occurrences and deduce the execution time from these, this is an inaccurate method and relies on the WCET of the interrupt handlers being known.

The lack of proper protection against unexpectedly high rates of interrupt occurrences motivates the development of execution time control for interrupt handling similar to that for tasks. The overhead to interrupt handling has to be very low for this new feature to be usable in real-time systems, and specialized hardware may therefore also be needed.

## 1.2 Research goals and methods

The primary goals of this research are:

- 1. To establish a research platform by porting the GNU Ada Compiler (GNAT) and a bare-board run-time environment to the Atmel AVR32 UC3 micro-controller series and implement execution time control for this system.

- 2. To design and implement execution time control for interrupt handling and demonstrate usage patterns for this new feature in the Ada programming language.

- 3. To design and implement a dedicated hardware Time Management Unit (TMU) for reducing the overhead of execution time control.

The Ada programming language was chosen for this research work as it is renowned within high-integrity systems, has built-in real-time tasking support, and has supported execution time control for tasks since Ada 2005 [32]. Also, there is a fairly small but active community researching on Ada for real-time systems, with the International Real-Time Ada Workshop (IRTAW) being an important meeting place for proposing and discussing new real-time features for the language.

GNAT is a front-end for the GNU Compiler Collection (GCC) maintained by Ada-Core. Both GCC and GNAT are open-source software available under the GNU Public License (GPL) [54] and the research can therefore be shared freely, benefiting the whole community. The GNAT bare-board Ravenscar run-time environment [47] was used as real-time kernel for the research. Due to the limited tasking support of the Ravenscar profile [10, 11], the run-time environment is small in code size and is therefore easy to understand and make changes to. The run-time environment is also of high quality and forms a solid base for the research.

Due to the close relation between NTNU and Atmel Norway, it was decided to use their new AVR32 architecture and the UC3 microcontroller series [3, 4, 57] as a hardware platform for the research. This allowed for the TMU to be implemented and tested with Atmel's proprietary synthesizable code for the UC3. Also, there is an open-source GCC back-end available for AVR32 so that GNAT can easily be ported to the architecture.

### **1.3 Related work**

Execution time control is supported in different ways by many systems. For decades mainframe computer systems have allowed setting execution time budgets for jobs and users in order to protect and share the valuable processing time. Often general purpose operating systems have a periodic scheduling tick in the frequency range 10 to 1000 Hz, and will find a statistical *approximation* of the execution time by counting which process is running when this tick handler is called. However, the coarse-grained precision and uncertainty of this execution time measurement method makes it unusable for real-time systems.

Real-time POSIX has supported execution time control since POSIX.1b standardized in 1993. It defines execution time clocks for processes and threads, and timers to signal overruns for these clocks [20,55]. Using these POSIX features Harbour et al. at the University of Cantabria implemented execution time control for Ada 95 and demonstrated usage patterns for real-time applications [21]. The same research group also implemented and demonstrated these features on the embedded MaRTE OS [45]. The execution time control features were proposed added to the Ada language standard and discussed at IRTAW-10 [44]. The proposal was later refined [41] and was forwarded by IRTAW-12 to the Ada Rapporteur Group (ARG) for the process of ISO-standardization [1].

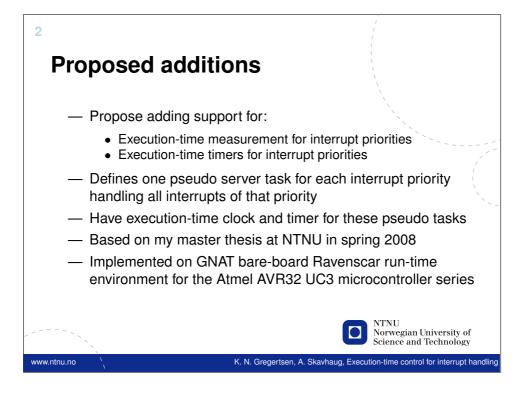

Execution time control was standardized together with other new real-time features in Ada 2005 [32]. However, the standard did not state which execution time budget, if any, that is to be charged the execution time of interrupt handlers. All implementations known to the candidate when this research work started, charged the running task [17,21,22,45,56]. This causes inaccuracy to execution time measurement and was pointed out as an issue when the new Ada 2005 real-time features were evaluated [59]. At IRTAW-14 where the candidate proposed adding full execution time control for interrupt handling [24], the developers of MaRTE OS also proposed adding a execution time clock for all interrupt handling combined, primarily to improve the accuracy of execution time measurement for tasks [46]. These two independent proposals were forwarded to ARG for the process of ISO-standardization [40] and are to be included in the forthcoming Ada 2012 standard [33].

Execution time control was also implemented for the Open Ravenscar Kernel (ORK) by de la Puente and Zamarano at the Polytechnical University of Madrid prior to standardization of the feature in Ada 2005, and execution time control policies within the limitations of the Ravenscar profile were demonstrated [17]. As the Ravenscar prohibits asynchronous task control and changes of priorities, most of the policies possible with the full Ada 95 tasking model [21] could not be used, leaving only overrun detection and system reconfiguration as options. However, it was concluded that execution time control indeed could be useful with the Ravenscar profile [17]. Yet, when execution time control was standardized with Ada 2005, execution time timers were explicitly prohibited with the profile [32] primarily because of the static nature of Ravenscar tasking and the lack of mechanisms to handle overruns. Still, ORK and the GNAT bare-board kernel based on it [47] have continued to support execution time control [56].

#### 1.3.1 Other languages and systems

The Real-Time Specification for Java  $(RTSJ)^1$  supports execution time control by an integrated approach referred to as *cost monitoring* [50]. In essence the RTSJ allows budgets, or the *cost*, to be set for periodic threads. This cost is the same for each release. In the case of a cost overrun the offending thread will only be allowed to continue executing if this will not cause lower priority threads to miss their deadlines, otherwise it will be immediately blocked until its next release. The cost monitoring scheme is intended to be independent of scheduling policy [50].

The QNX® Neutrino® RTOS<sup>2</sup> supports execution time control by allowing reservation of CPU time for *partitions* consisting of processes and tasks. The OS uses

<sup>&</sup>lt;sup>1</sup>Web: http://www.rtsj.org

<sup>&</sup>lt;sup>2</sup>Web: http://www.qnx.com/products/neutrino-rtos

an approach that is adaptive in that CPU time not used by one partition may be utilized by others. The limits on CPU time are only enforced when the system is overloaded in order to guarantee that the reserved CPU resources are available for specified processes. Partitions are configured, not programmed, and are therefore flexible in use, no recompilation is needed in order to change the allocation of CPU resources.

### **1.4** Thesis organization

The reminder of this thesis is organized as follows:

- **Chapter 2:** Theoretical background of the thesis, giving a brief introduction to real-time scheduling systems and execution time control; the Ada programming language and GNAT; and the Atmel AVR32 architecture.

- **Chapter 3:** Description of the main contributions of this PhD in the form of published and submitted material.

- **Chapter 4:** Conclusions on the main contributions of this PhD and a brief discussion of future work topics.

- **Appendix A:** The published and submitted material forming the basis of this thesis in chronological order.

- **Appendix B:** The presentations of interrupt execution time control by the candidate at IRTAW-14 that formed the basis for ISO standardization of this new feature.

- **Appendix C:** Description of how to obtain the sources for GNATforAVR32 and set up the development environment.

- Appendix D: Additional code listings.

# Chapter 2

# **Background theory**

### 2.1 Real-time systems and execution time control

#### 2.1.1 Scheduling policies

The scheduling policy decides which tasks that are to be executed and for how long by allocating the processors available in the system. The *runnable* tasks are placed in one or more *ready queues* waiting to be scheduled for execution. Tasks are removed from the ready queue when blocked by a system call or delayed until a specified relative or absolute time. Employing *preemptive* scheduling, a running task may be replaced by another runnable task and put back on the ready queue, while employing *non-preemptive* scheduling, tasks run until they are delayed, blocked by a system call or voluntarily *yield* the processor. This work only considers preemptive scheduling.

The most widely used policy is Fixed Priority Scheduling (FPS), where each task is given a fixed *priority* and resources are allocated to the task according to this priority. Usually tasks with the same priority are handled in first-in-first-out (FIFO) order, and the following rules apply:

- A blocked task that becomes ready is added at the tail of the ready queue for its active priority.

- When a task loses inherited priority, the task is added at the head of the ready queue for its new active priority.

- When a task executes a non-blocking delay statement or yield, it is added to the tail of the ready queue for its active priority.

• A running task is preempted whenever there is a nonempty ready queue with a higher priority and is then added at the head of the ready queue for its active priority.

Round-robin (RR) arbitration may be used instead of FIFO order to manage tasks with equal priorities. In this case the running task is moved to the end of the ready queue for its active priority after having been executed for a given time. Execution time clocks and timers may be used internally by the scheduler for an efficient and accurate implementation of this scheme [45]. While RR gives some degree of fairness between tasks of the same priority it does not improve schedulability, and also makes it harder to reason about the response time of tasks. Thus it is best suited for non-real-time tasks.

Another policy is Earliest Deadline First (EDF), where the processor is allocated to the task with least remaining time until its deadline. Thus EDF is a *dynamic* policy as priorities are decided and changed at run-time. EDF is optimal for uni-processor systems, allowing up to 100% utilization, but is more complex to implement and is also vulnerable to cascades of missed deadlines if tasks are allowed to continue executing after a deadline miss.

#### 2.1.2 Scheduling analysis

Rate monotonic analysis (RMA) may be used to assign priorities to tasks and check the schedulability with FPS under the assumption that the processor is the only shared resource, that all tasks are periodic, that the deadline equals the next release, and that there is zero overhead of context switch between tasks [37].

With RMA each task *i* is assigned a priority according to their period  $T_i$  – the task with the shortest period is given the highest priority and so on. Note that when using RMA the priority of a task does not say anything about the *importance* of the task. Also, the required amount of execution time needed by task *i* is assumed to be a known constant  $C_i$ . It is assumed without further evidence here, that the task set is schedulable also if the tasks use less than C, thus the WCET or execution time budget may be used as C.

The utilization-based test is sufficient but not necessary as it gives the least upper bound (LUB) of the total processor utilization U for a task set with N tasks:

$$\sum_{i=1}^{N} \frac{C_i}{T_i} \le N(2^{\frac{1}{N}} - 1) = \text{LUB}$$

(2.1)

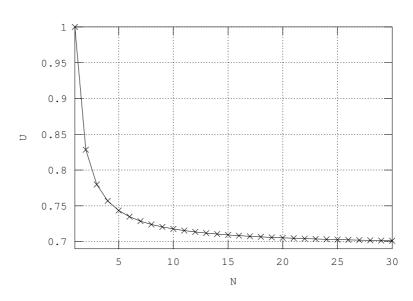

*Figure 2.1:* The least upper bound (LUB) of processor utilization with rate monotonic analysis (RMA) for N tasks.

As seen in Figure 2.1 the LUB asymptotically approaches 69.3% utilization when the number of tasks in the set increases towards infinity.

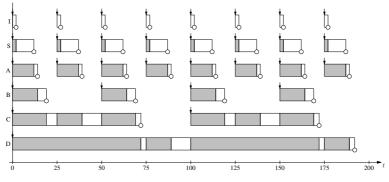

Response time analysis provides a sufficient *and necessary* test for schedulability. The test it will not be described formally here, and is instead performed by drawing Gantt charts. The test is done by releasing all tasks simultaneously at what is called the *critical instant*. If a task is schedulable when released at the critical instant it will also be schedulable at any other release configuration [37]. Only the time of the longest task period after the critical instance has to be considered. If all tasks reach their deadlines within this interval the system is schedulable.

| Task | Т  | С  |

|------|----|----|

| А    | 20 | 5  |

| В    | 40 | 10 |

| С    | 60 | 20 |

*Table 2.1:* Example periodic task set. Priorities are  $p_A > p_B > p_C$ .

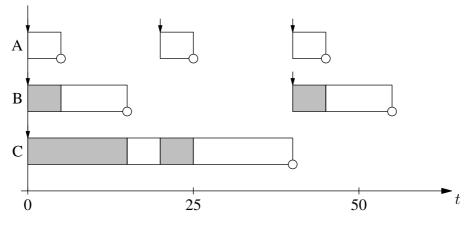

An example task set is shown in Table 2.1. The total utilization for the task set is 83.3% and thus the utilization-based test fails as the LUB for N = 3 is 78%. However, this does not necessarily mean that the task set is not schedulable – as seen from the Gantt chart in Figure 2.2 all tasks reach their deadlines, and the task

*Figure 2.2:* Gantt chart for the example task set in Table 2.1. Task release is shown by a black arrow. Tasks are drawn as a white rectangle when running, and gray when another task preempts it. Completion before deadline is indicated by a white circle.

set is indeed schedulable.

#### 2.1.3 Shared resources

When using preemptive scheduling, shared resources must be protected with mutual exclusion. This can be done using explicit *semaphores* and protected regions of the code, but this primitive method is prone to programming faults that may cause a *deadlock* – a situation where several tasks all are blocked waiting for each other to release the shared resources. A better approach is to use a *monitor* that contains the shared resources and automatically takes care of the mutual exclusion.

It is also important to avoid *unbounded priority inversion* – a situation where a task is waiting for a lower priority task to release a shared resource, while this task again is preempted by a third task preventing it from finishing with the resource. This can be avoided by using a *priority inheritance* protocol with shared resources, the most practical being the *ceiling protocol* where a shared resource is given a fixed priority ceiling equal to or higher than the priority of all tasks accessing it. When a task acquires the resource it inherits the ceiling priority and thus no *unbounded* priority inversion can occur – the worst-case time waiting for a task with lower priority to release the shared resource is the highest WCET of all its operations.

Response time analysis is also possible for monitors using different priority inheritance protocols.

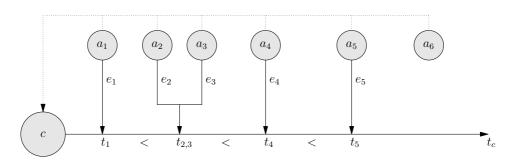

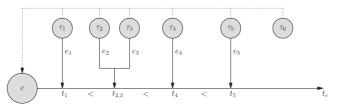

**Figure 2.3:** Six alarms associated with one clock. All alarms but  $a_6$  are set. Assuming that FIFO order is used and that  $a_2$  was set before  $a_3$  the events will be handled in the order  $e_1$ ,  $e_2$ ,  $e_3$ ,  $e_4$  and  $e_5$ .

#### 2.1.4 Timing services

A *clock* measures the passage of time using a physical process as reference, typically a crystal oscillator. Clocked time is discrete and represented by a count of ticks  $c \in \mathbb{N}_0$ . Each tick corresponds to a duration T, so the measured time is  $t = T \cdot c$ . Most clocks have inaccuracies caused by jitter and drift when compared to a reference clock. If the duration between the ticks is not a constant T but a stochastic function  $\hat{T}$  it is called jitter. If the expected duration  $E(\hat{T})$  between the ticks is not equal to T the clock will also drift compared to a reference clock. This drift will accumulate over time. Such inaccuracies are not considered in this work. Clocks are allowed to be stopped and resumed, but required to be monotonic. Therefore the following relation holds between samples where  $t_i$  denotes the i'th sample of a clock:

$$t_1 \le t_2 \le \ldots \le t_{i-1} \le t_i \quad \forall i \in \mathbb{N}$$

$$(2.2)$$

The real-time clock (RTC) is used for system operations such as task release and setting task deadlines. There is only one instance of this clock. The clock is activated at system start-up, also called its epoch, and is never stopped. Execution time clocks are used to measure the total time an executable entity has been running on the system. There is one clock for each entity. The clock is started when the entity is scheduled for execution and stopped when it is suspended, blocked, preempted by another entity, or terminated. In this work the executable entities considered are tasks and interrupt handlers.

An *alarm* is associated with a clock and is used to generate an *event* that occurs when the clock reaches a specified time  $t_e$ . An alarm is said to be *set* with a *handler* that is to be called when the event occurs, at a time  $t \ge t_e$ . Several alarms may

be associated with a single clock as seen in Figure 2.3. Event occurrences for one clock are required to be handled in order with earliest event first. The order for events occurring at the same time is not specified, but FIFO order will be used in this work unless stated otherwise.

### 2.1.5 Overrun handling

Different overrun handling policies exist to prevent deadline miss and system failure in the case of a task execution time overrun. Harbour et al. describes the following schemes [21]:

- *Handled*: The overrun is recorded and the task allowed to continue executing. This may be used for testing, for critical tasks that must be allowed to finish their work, or in cases where an occasional overrun is acceptable.

- *Stopped*: The task instance is stopped in the case of an overrun by the use of asynchronous control such as the abort statement in Ada, and is not repeated. The task starts executing normally the next time it is released.

- *Imprecise*: The task consists of a mandatory part that is usually short, and an optional part that refines the result. The optional part is aborted in case of an overrun. This scheme allows fixed priority for tasks executing algorithms where predicting the WCET is hard.

- *Lowered*: The task is lowered to background priority in the case of an overrun to avoid deadline miss for tasks with lower priority. The task may finish if there is sufficient CPU resources. The task priority is restored at the next release.

Another alternative is to reconfigure the system into a safe-state when an execution time overrun is detected. This is also possible when asynchronous task control is not available such as for the Ravenscar profile [17].

### 2.1.6 Execution time servers

Execution time servers allow a group of sporadic tasks with soft deadlines to be executed with higher priority than the periodic tasks with hard deadlines – thus giving low *average* response time for the sporadic tasks while guaranteeing a response time within the hard deadline for the periodic tasks. To set a budget for the sporadic tasks a *group budget* mechanism is needed.

The deferrable and sporadic server are the most used algorithms. Both allow the group of sporadic tasks to be modeled as a periodic task with period T when applying RMA. The deferrable server works by replenishing the group budget for the sporadic tasks registered with the server periodically with period T. If the budget is exhausted the tasks can either be halted by asynchronous task control, or given a priority below that of the periodic tasks to avoid further interference. When the budget is replenished the tasks are resumed or restored to the high priority. An appealing aspect of the deferrable server is that no knowledge of how the sporadic tasks execute is needed.

The sporadic server is quite similar to the deferrable server except that the consumed execution time for a sporadic task starting at time t is returned to the server at t + T. The sporadic server is much more complex than the deferrable, and the sporadic task must communicate with the server during execution. However, the benefit of the sporadic server is improved average response time.

# 2.2 The Ada programming language

In the 70s the U.S. Department of Defense ordered a programming language to replace the myriad of languages and dialects used for its different projects. A french team won the contract with the programming language Ada, named after Ada Lovelace – the daughter of the poet lord Byron and allegedly the world's first programmer, working on the mechanical Babbage machine.

The programming language was ISO-standardized in 1983 as Ada 83. There was a major revision of the language in 1995, known as Ada 95, bringing changes to tasking, added object-oriented programming (OOP) through *tagged types*, and more. The current revision is Ada 2005, which is an amendment to Ada 95, and brings Java-inspired improvements to the OOP-model such as supporting prefix method call notation and interfaces, more flexible access types, enhanced structure and visibility control for packages, extensions to the standard library, and new tasking and real-time features [8]. The coming Ada 2012 brings dynamic contracts, more flexible expressions, further extensions to the standard library, improved support for multi-processor system, and execution time measurement for interrupt hand-ling [9].

Since Ada was designed for use in large high-integrity systems it has many safeguards against common programming faults. The language also has excellent support for development and maintenance of large applications by its notation of packages. Furthermore, Ada has language support for tasking and a rich set of Listing 2.1: Task type example.

```

task type Worker

(P: System.Priority;

N : Character)

is

pragma Priority (P);

end Worker;

task body Worker is

Next : Time := Clock;

begin

loop

delay until Next;

Put Line ("Hello!, My, name, is, " & N & '.');

Next := Next + Seconds (1);

end loop:

end Worker:

A : Worker (Default Priority + 2, 'A');

B: Worker (Default Priority + 1, 'B');

```

synchronization primitives, making even multitasking applications portable.

### 2.2.1 Tasking features

Ada allows tasks to be specified either as a single instance, or as a task type with many possible instantiations that can be declared with *discriminants* as parameters. The body of the task defines the code that the task is to execute. An example defining a task type and two instances is shown in Listing 2.1. In this example the real-time package shown in Listing D.1 with its high-precision real-time clock is used for task delay.

Several real-time scheduling policies, or *dispatching policies*, are supported by Ada: FPS with FIFO within priorities or round-robin dispatching, EDF [13] and coherent mixes of these.

*Protected objects*, a type of monitors, provide mutual exclusive access to internal data through protected operations – procedures, functions and entries. Protected objects are also used for communication and synchronization between tasks, and

Listing 2.2: Protected type implementation of mutex.

```

protected type Mutex is

entry Lock;

procedure Unlock;

function Is_Open return Boolean;

private

Open : Boolean := True;

end Mutex:

protected body Mutex is

entry Lock when Open is

begin

Open := False;

end Lock:

procedure Unlock is

begin

Open := True;

end Unlock:

function Is Open return Boolean is

begin

return Open;

end Is_Open;

end Mutex:

```

as interrupt routine handlers. As with tasks, a single instance may be defined or a protected type with many instances. Entries are associated with a *guard* condition which will block entry callers until the guard evaluates to true. This allows task synchronization through protected objects. How protected objects achieve mutual exclusion and queue tasks blocked on an entry is implementation dependent. Ada defines the priority ceiling protocol, and FIFO and priority queuing policies for entries.

An example of a protected object type used as a mutex is shown in Listing 2.2. The mutex is only used as example as its functionality is well known, otherwise it is meaningless to use a high-level synchronization primitive such as the protected object to implement a low-level primitive such as the mutex.

Full Ada tasking supports more complex features than shown in the example, such

as task rendezvous with entries and the select statement, allowing tasks to communicate directly, with the possibility of timeout for the task waiting for others; asynchronous abortion of code blocks; and the requeue statement to move a task to the queue of another entry. Since these features are not supported by the Ravenscar run-time environment they are not described further. The reader is referred to the excellent books by John Barnes [7] and Alan Burns and Andy Wellings [12, 15].

### 2.2.2 The Ravenscar profile

While Ada is much used within high-integrity systems, the concurrent constructs of the language have often been excluded as being non-deterministic and inefficient [11]. Instead methods such as the cyclic executive [5, 12] has been used. Advances in static analysis have made it possible to check hard deadlines when using preemptive fixed priority scheduling. This has led to development of the Ravenscar profile [10], a sub-set of the Ada tasking model designed to provide the static and deterministic environment needed to perform static analysis [11]. The simplicity of the tasking model also allows efficient run-time environments. The sequential parts of Ada are not affected by the profile [11].

The Ravenscar profile is specified as a set of configuration pragmas defining restrictions to the Ada tasking model and the required dynamic semantics [10, 32]. The following features are supported [11]:

- Tasks types and objects defined at library level.

- Protected types and objects, defined at library level, limited to one entry having a simple guard and a queue length of one.

- FIFO within priorities dispatching policy for tasks.

- Ceiling locking protocol for protected objects.

- The Ada.Real\_Time package and the delay until statement.

- The Ada.Execution\_Time and Ada.Execution\_Time.Interrupts packages for execution time measurement of tasks and interrupt handling.

- Synchronous task control with suspension objects.

- Protected procedures as statically bounded interrupt handlers.

A static set of tasks and protected objects is achieved by only allowing such objects to be statically declared at library level and disallowing task termination. Dynamic attachment of interrupt handlers and dynamic change of task priorities

with the exception of changes caused by ceiling locking is also prohibited. Tasks may not have entries, thereby allowing task communication and synchronization only through protected objects or suspension objects. A protected object may have a single entry with a queue length of one using a simple barrier. The **requeue** statement and asynchronous control are disallowed. There can be no relative delay statements and the profile forces the use of the real-time package for timing purposes.

### 2.2.3 Timing events

Timing events allow protected procedures to be called at a specified time without the need for a task or delay statement to control their activation. The package used for timing events is defined as shown in Listing D.2.

A Timing\_Event object is said to be *set* if associated with a non-null handler and *cleared* otherwise. The type Timing\_Event\_Handler identifies a protected procedure that will be executed when the timing event *occurs*. There are two procedures for setting a timing event with a handler, both named Set\_Handler. One takes the absolute time of the event and the other uses relative time. If Set\_Handler is called for an already set event, the handler is replaced. If called with a null handler the event is cleared. Handlers may be cancelled using Cancel\_Handler which returns whether the handler was cancelled or not. The function Current\_Handler returns the current handler of the event, while the function Time\_Of\_Event returns the time when the event will occur.

Implementations are required to perform operations on a timing event object atomically, and are also required to document the upper bound on the overhead of the handler being called.

### 2.2.4 Execution time control

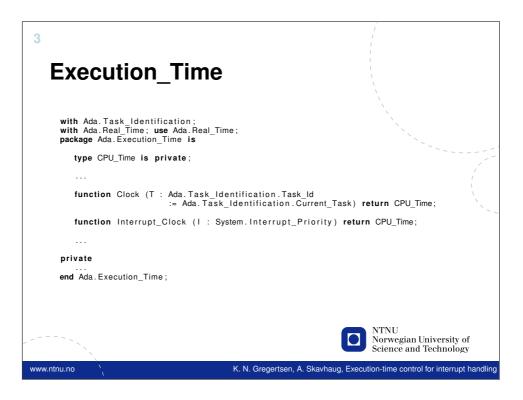

The package Ada.Execution\_Time shown in Listing D.3 defines the type CPU\_Time which represents the elapsed execution time and the function Clock to get the execution time of a task [33]. The execution time of a task is defined as the time spent by the system executing that task, including the time spent executing run-time or system services on its behalf [33].

With Ada 2005 it was implementation defined which task, if any, that was charged the execution time used by interrupt handlers. Ada 2012 has the ability to account for either the total or separate execution time of interrupts handlers. The constant

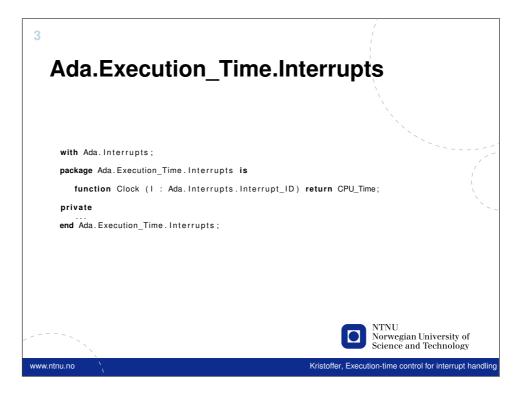

Interrupt\_Clocks\_Supported indicates if the system supports measuring the total execution time of interrupt handlers by the use of the function Clock\_For\_Interrupts. The function will raise a Program\_Error when called if this is not supported. The constant Separate\_Interrupt\_Clocks\_Supported indicates whether or not the system supports measuring the execution time of interrupt handlers separately. This functionality is provided by the child package Interrupts shown in Listing D.4. In this child package the function Clock returns the execution time for the handler of the given interrupt or raises Program\_Error if separate execution time for interrupts is not supported.

The child package Timers shown in Listing D.5 defines the tagged type Timer. An object of this type represents the source of an execution time event for a single task and is capable of detecting execution time overruns. As for timing events a timer is said to be set if associated with a non-null handler and cleared otherwise. All timers are initially cleared. The type Timer\_Handler identifies a protected procedure to be executed when the timer *expires*. Timers are set and cancelled as with timing events with the exception of the absolute time for Set\_Handler being given as CPU\_Time. The function Time\_Remaining replaces Time\_Of\_Event and returns the time remaining until the timer expires. Operations on a timer-object are required to be atomic. The number of timers possible for a single task is allowed to be limited by the implementation, and an exception Time\_Resource\_Error is to be raised if this number of timers is exceeded.

The child package Group\_Budgets shown in Listing D.6 allows execution time budgets to be set and replenished for a group of tasks. A user-provided handler is called when the budget has expired. Tasks may be added or removed from the group at any time, but a task can only belong one group at a time, and all tasks in a group has to be bound to the same CPU. Handlers are set and cancelled in the same way as timing events and timers.

### 2.2.5 The object-oriented real-time framework

The object-oriented real-time framework for Ada 2005 was initially designed and implemented by Andy Wellings and Alan Burns at the University of York [15, 60, 61], and has since become a de-facto standard within the real-time Ada research community. The framework has been extended with support for operating modes and mode changes [43], multi-processor systems using the coming Ada 2012 features [49], and execution time servers for interrupt handling using the non-standard interrupt execution time timers by the candidate [31].

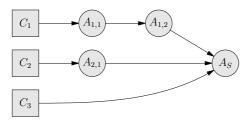

The original framework consists of four major components [60]:

task body Simple\_RT\_Task is

begin

S. Initialize ;

loop

R.Wait\_For\_Next\_Release;

S.Code;

end loop;

end Simple\_RT\_Task;

The package Real\_Time\_Task\_States defining the abstract tagged task state type that contains the task initialization code and the code to be executed at each release, the relative deadline, execution time budget, the priority of the task, and notification handlers for deadline miss and overruns. Child packages define periodic, sporadic and aperiodic abstract task states inheriting the abstract task state, each adding relevant parameters for the type of task.

Listing 2.3: The basic real-time task type of the framework.

- 2. The package Release\_Mechanisms defining the synchronized interface for releasing tasks either as a result of the passage of timer or some event. Extended interfaces with overrun detection and deadline miss detection are also defined. Child packages implement periodic release mechanisms and one sporadic mechanism triggered by a procedure call with a minimal interrelease time (MIT), both types with and without overrun and deadline miss detection; and aperiodic release triggered with execution time servers. The release mechanisms use the attributes of their corresponding task states.

- 3. The package Real\_Time\_Tasks defining the task types that perform the work by dispatching calls to the provided release mechanism and task state. The simplest of the types shown in Listing 2.3 first initializes the object, and then waits for release and executes the code in an infinite loop. The two more advanced task types use asynchronous control to abort the task code in the case of deadline miss or execution time overrun, and then inform the task state by calling the corresponding handlers.

- 4. The package Execution\_Servers defining the synchronized interface for execution time servers and generic parameters for this. Child packages implement the deferrable and sporadic server for use with aperiodic tasks.

Using this framework, the programmer needs only create a tagged task state type

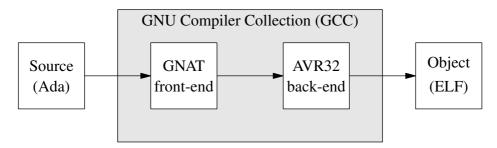

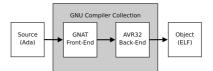

Figure 2.4: The GNU Compiler Collection with front- and back-ends.

inheriting the desired abstract type, and implement the abstract procedures for the tasks code and handlers. Objects of this task state can then be declared together with the appropriate release mechanism, real-time task type, and execution time server in the case of aperiodic tasks. Using the framework is easy as the boiler-plate parts are predefined, and also very flexible as the parts are interconnected through dispatching calls.

# 2.3 The GNU Ada Compiler (GNAT)

The GNU Compiler Collection (GCC) was released in 1987 by Richard M. Stallman, initially named the GNU C Compiler, and is the heart of the GNU Project maintained by the Free Software Foundation (FSF). Following the philosophy of FSF, GCC is open-source and "free as in liberty" – everyone can obtain the code, modify, compiler and redistribute it under the GNU Public License (GPL) as long as they do not deny this right to others [54].

GCC supports a great number of programming languages and computer architecture targets by a design as shown in Figure 2.4. It uses language *front-ends* that compile code into the internal tree representation, and target back-ends that create the assembler output from this and perform machine dependent optimization. The GNU Project also comes with assemblers, linkers and other tools in the GNU Tool-chain, the GNU Debugger (GDB) and more.

The GNU Ada Compiler (GNAT) is the GCC front-end for the Ada programming language. It was developed at the University of New York on contract with the U.S. Air Force and was originally called the GNU Ada Translator, hence the acronym GNAT. In a parallel project, the POSIX based real-time run-time library was developed at the University of Florida. After the completion of the project, the company AdaCore was established by project members to provide support for

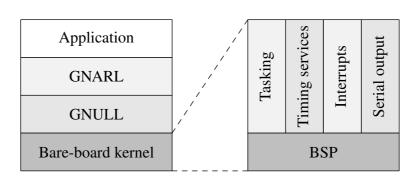

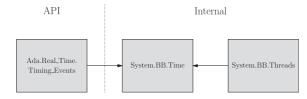

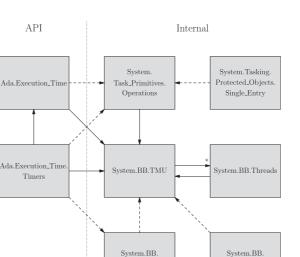

*Figure 2.5: The GNU Ada Library (GNARL). Here the GNU Low-level Library (GNULL) is implemented by the bare-board real-time kernel to the right.*

GNAT and further develop it into a full-featured industrial strength compiler [42]. AdaCore distributes GNAT both as the supported PRO version and the free/libre GPL version. The latest version is GNAT 2011 that brings supports for Ada 2012.

GNAT is more than just a language front-end; it also consists of the GNU Ada Run-time Library (GNARL), and Ada specific tools such as the binder, linker, builder with support for project files, and more, making it a complete development tool-chain for high-integrity systems.

### 2.3.1 Restricted GNARL

The GNU Ada Run-time Library (GNARL) seen in Figure 2.5 implements the features of Ada not directly supported by the compiler such as tasking, interrupt handling, standard libraries, distributed programming, system interfaces, and more. The routines of GNARL are called by the application either directly or indirectly by compiler generated code.

The restricted Ravenscar version of GNARL is carefully designed to take advantage of the simplifications allowed by the profile [47]. Task management is simplified since all tasks are defined at library level, cannot terminate, and have fixed base priority. All task data structures are statically allocated, thus memory requirements are determined at link time. Protected objects are simplified since there are no asynchronous operations, no time-out on entry calls and no varying queue length on entries. On single processor systems mutual exclusion is ensured by the ceiling priority protocol and scheduling policy. Evaluation of protected entries may be done by proxy, thereby improving performance by reducing the number of context switches [47].

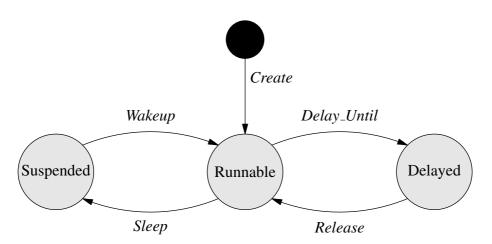

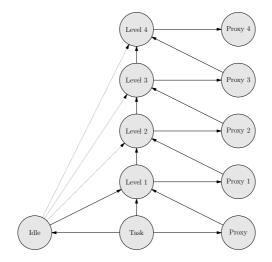

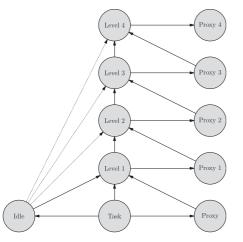

*Figure 2.6:* Thread states of the bare-board real-time core: Runnable when in the ready queue; Suspended when unconditionally blocked (on an entry); and Delayed when blocked until a specified absolute time.

#### 2.3.2 The bare-board Ravenscar run-time environment

For most systems the GNU Low-Level Library (GNULL) is a translation layer between generic and actual operating system calls, but for the bare-board run-time environment it fully implements the needed dynamic semantics of the Ravenscar profile as to the right of Figure 2.5. This is done by including a multi-tasking core based on the Open Ravenscar Kernel (ORK) [18, 48]. This kernel was developed at the Polytechnical University of Madrid (UPM) on contract with the European Space Agency (ESA) for use on the ERC32 and LEON space application processors, and was later integrated into GNARL by José F. Ruiz at AdaCore [47].

The core implements preemptive fixed priority scheduling with ceiling locking, having 256 priorities including the interrupt priorities. However, the total number of priorities can easily be changed if needed. To allow interrupt nesting whilst avoiding priority inversion, each interrupt priority has its own interrupt stack [47]. Interrupts are masked as long as the running task has higher or equal priority to the given interrupt. All interrupts are masked while modifying core data in order to ensure mutual exclusion.

The *thread* type used for tasking is very simple due to the limitations of the Ravenscar profile and only has three states as seen in Figure 2.6. All thread operations on runnable threads are done on the *running* thread first in the ready queue. The queue is only modified as a result of threads being inserted, removed, and when the priority of the running thread is changed according to the FIFO within priorities dispatching policy. Whenever the first thread in the queue is not equal to the running thread a *context switch* will take place before leaving the core. There is no idle thread in the run-time environment. Instead the thread that finds the ready queue empty when leaving the kernel is reinserted into the queue and enters an idle-loop waiting for any thread to be made runnable by an interrupt. The thread only leaves the idle-loop when itself or another thread is runnable again. Threads enter the idle-loop one at the time.

The timing services of the core provides as high precision as possible while supporting the 50 year time span required by the Ada standard [33]. This is done by using a 64-bit value for time divided into two parts. The least significant part is present in the system timer called the *clock*. The most significant part is stored in memory and is incremented every time the clock timer overflows. A second timer, the *alarm*, is used in one-shot mode to release delayed tasks with high-precision between the clock overflows.

The multitasking core builds on a device specific Board Support Package (BSP) consisting of peripheral drivers, CPU primitives and assembler files facilitating context switch, low-level interrupt handling and interrupt masking.

# 2.4 The Atmel AVR32 architecture

The Atmel AVR32 [3] was designed at Atmel Norway in close cooperation with NTNU, and is a 32-bit RISC architecture optimized for high code density and high computational throughput with low power consumption [57].

The architecture has a fairly small register file consisting of 13 general purpose registers (named R0 to R12), the link register (LR) used for storing the routine return address, the program counter (PC) and the system register (SR). Instructions are both 16- and 32-bit wide for higher code density. Being a RISC architecture, the AVR32 has a number of load / store operations, many with the possibility to increment or decrement the pointer register before or after memory access. There are also instructions to load or store multiple registers.

The AVR32 has four interrupt levels, and exceptions such as the Non-Maskable Interrupt (NMI) and illegal address exception. The entry point for each of the four levels is configurable, and registers R8 to R12, LR, SR and PC are automatically stored before entering the handler. For the AVR32A microarchitecture the registers are stored on the system stack, while for the high-performance AVR32B microarchitecture shadow register files are used.

Interrupts are managed by the *interrupt controller* that groups the interrupts of the specific part, and allows each such interrupt group to be assigned to any interrupt level.

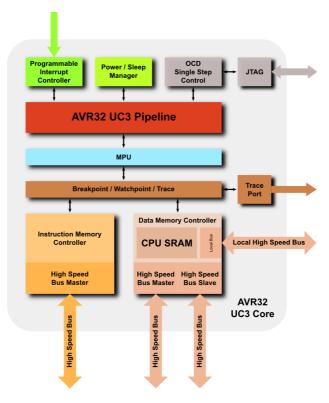

#### 2.4.1 The UC3 microcontroller series

The UC3 microcontroller series [4] is the second implementation of the AVR32 architecture, and the first of the AVR32A microarchitecture. It is primarily intended for embedded control applications where deterministic execution time is paramount. The UC3 implements the DSP instructions of the AVR32 architecture set such as several single-cycle multiply and accumulate instructions for both modular and saturated arithmetic.

The UC3 has a three-stage hazard-free pipeline consisting of:

- 1. The instruction fetch stage optimized for on-chip Flash memory.

- 2. The decode stage that decodes the instructions and sets up control signals.

- 3. The execution stage consisting of the ALU preforming arithmetic and logical operations, the multiplication unit preforming multiply and multiplyaccumulate operations, and the load / store unit accessing the SRAM and high-speed bus.

An important feature of the UC3 is the internal SRAM integrated with the CPU pipeline. The system bus is bypassed, allowing deterministic, single-cycle read/write memory access. A high-speed bus (HSB) slave interface to the SRAM allows DMA controllers or other HSB masters to directly write or read data from memory. Arbitration with a programmable priority scheme is performed if the CPU and a high speed slave request access simultaneously.

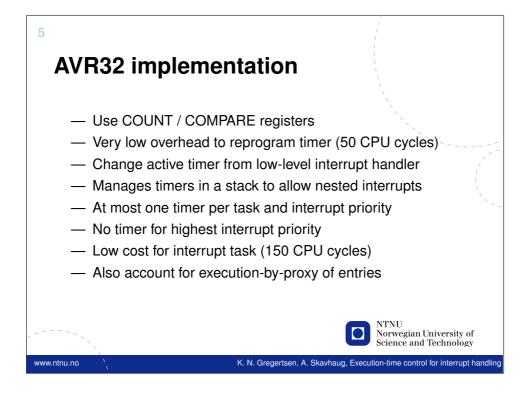

#### 2.4.2 Hardware timers

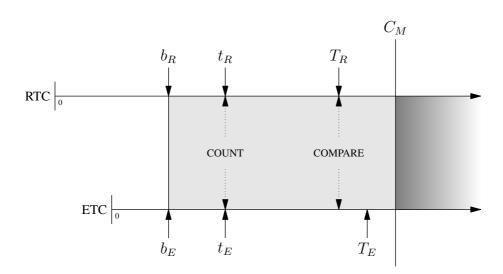

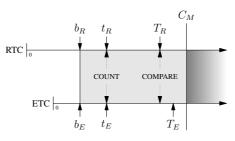

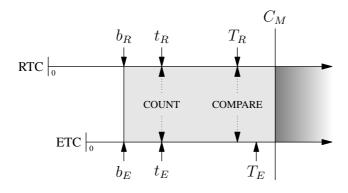

The 32-bit COUNT / COMPARE system registers of the Atmel AVR32 architecture are used to count the number of elapsed CPU cycles and allow an interrupt to be triggered. The COUNT register is reset to zero at system start-up and is incremented by one every CPU clock cycle. The COMPARE interrupt is triggered when COUNT equals COMPARE, cleared when COMPARE is written, and disabled when COMPARE is zero, which is also the reset value of the register. For newer UC3 revisions the COUNT register is reset on COMPARE match. It is however possible to disable this behavior in the CPU configuration register.

The Timer / Counter peripheral of the UC3 may be used for signal waveform generation and measurement, and as an one-shot or periodical timer generating interrupts. The peripheral has three 16-bit channels with selectable clock source and prescaling.

# Chapter 3

# **Main contributions**

## 3.1 GNAT for AVR32

Article A.1 is titled "An efficient and deterministic multi-tasking run-time environment for Ada and the Ravenscar profile on the Atmel AVR32 UC3 microcontroller" [26] and describes how the GNU Ada Compiler (GNAT) was ported to the Atmel AVR32 architecture and how the GNAT bare-board run-time environment was ported from the LEON architecture to the UC3 series of microcontrollers. This work made Ada available for the AVR32 for the first time, and provided a solid research platform for Ada real-time systems.

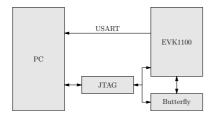

Refer to Appendix C for details about how the source code of the compiler and run-time environment is obtained, configured and build.

#### 3.1.1 Porting the GNAT front-end to the AVR32 GCC back-end

The GCC back-end for the AVR32 architecture was initially developed at NTNU and is now maintained by Atmel Norway. It is not yet in the official code distribution of GCC, but patches for GCC 4.3 are available at Atmels web-pages.

Since both the front-end and back-end are open source components of GCC, porting GNAT to the AVR32 was mainly a matter of applying the GNAT patches from AdaCore to the already patched GCC source code provided by Atmel. Due to changes to the source code by the AVR32 patches, some of the GNAT patches failed to apply and needed to be fixed manually. The ported compiler may also be used together with AVR32 Linux on the AVR32 AP7 series of application processors [2]. In this case the standard POSIX based run-time environment should be used. This work was not prioritized as Linux was not found suitable for the research and the AP7 has now become deprecated.

### 3.1.2 Porting the run-time environment

When porting the run-time environment to the UC3, the board support package (BSP) including the context switch routine, low-level interrupt handler and peripheral drivers needed to be rewritten due to differences in hardware.

The context switch routine for the UC3 could be written in as few as 15 instructions with no branches due to the small register file of the AVR32. This was a significant reduction compared to the LEON architecture that has a large register file with register windows which means that the execution time of the routine will vary depending on the current window size. The UC3 context switch has a constant execution time which eases execution time analysis of applications.

The AVR32 has a peripheral interrupt controller that groups interrupts. Each group is configured to one of the architectures four interrupt levels by software, and there is a low-level handler for each level. The interrupt ID is found by first reading the interrupt cause register of the level to find the interrupt group, and then the interrupt request register of that group to find the interrupt line.

The timing services uses two hardware timers named *clock* and *alarm*. On the AVR32 two channels of the 16-bit Timer / Counter peripheral are used for these timers. The clock timer keeps the least significant part (LSP) of the system clock. On overflow, the most significant part (MSP) of the clock that resides in system memory, is incremented by the clock interrupt handler. The alarm timer is used in one-shot allowing fine grained task release within the clock periods.

# 3.2 Implementation of Ada 2005 execution time control

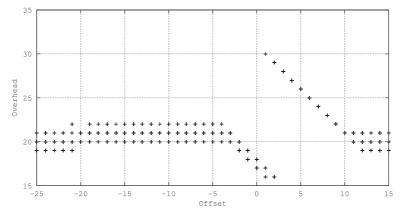

Article A.4 is titled "Implementing the new Ada 2005 timing event and execution time control features on the AVR32 architecture" [30] and describes how the new Ada 2005 timing event and execution time control features were implemented for the GNAT bare-board run-time environment on the Atmel AVR32 UC3. A novel feature of this implementation is that the execution time for interrupt levels are measured separately, and there is an interrupt timer for all levels except the highest

one. This increases the accuracy of execution time measurement for tasks and allows execution time control for interrupts for the first time.

### 3.2.1 Timing events

Prior to implementing Ada 2005 timing events the alarm timer was used exclusively for waking up delayed tasks. The functionality needed for this was spread over three kernel packages. When implementing timing events it was decided to use the same alarm mechanism both for waking up tasks and handling timing events and to gather all the functionality needed in System.BB.Time. By using the same mechanism both for timing events and waking up delayed tasks, a clean implementation was achieved. Furthermore, lower overhead may be achieved as a timing event and a task release occurring at the same time are handled by the same alarm interrupt.

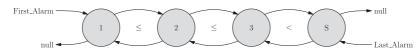

Internally, alarms are organized as a queue in ascending order by the timeout value of the events with a sentinel at the end. The queue is implemented as a doubly linked list in order for alarms to be quickly extracted if cancelled. The sentinel was added to simplify the code by removing the special case of having an empty queue. When inserting an alarm the queue is searched from the front to the end. The one-shot alarm timer is reprogrammed whenever the first alarm is changed. When the alarm timer interrupt is triggered, all alarms with timeout less than or equal to the current time are called and removed from the queue by the interrupt handler.

### 3.2.2 Execution time control

The execution time control features were implemented in a new package named System.BB.TMU where TMU stands for *Time Management Unit*. The package defines the type CPU\_Time representing elapsed execution time as a 64-bit modular integer, and the timer mechanism that is used for execution time control combining a clock and a single alarm in one type. This is done as implementations are allowed to limit the number of timers for tasks. As recommended for the Ravenscar profile [17], the implementation allows for at most one timer for each execution time clock.

The system measures execution time as the number of CPU clock cycles used by a task since its activation by using the COUNT / COMPARE registers of the AVR32 architecture. The Base\_Time of a timer is initially zero and is used for keeping track of absolute execution time. The execution time for an active timer is the sum

of the base time and the value of the COUNT system register. When a timer is deactivated its base time is incremented with the value of the COUNT register, thus the execution time of inactive tasks equals the base time. The correctness of the execution time measurement depends on the CPU counter never overflowing. To prevent this the value written to COMPARE is never greater than a constant  $C_{max}$  set to  $2^{31}-1$ . When COUNT equals this value a COMPARE interrupt will be pending causing the timer to be inactivated and its base time updated when handled.

Accuracy of task execution time measurement is improved by charging the execution time of interrupt handlers to the clock of a pseudo interrupt task for the corresponding interrupt level. This allows task budgets to be tighter and therefore allow for a higher utilization of the processor. Even more important, it allows the use of execution time timers for interrupt handling in order to set budgets and handle overruns. This allows protection against faults in interrupt generation or handling, for instance by blocking the handling of an interrupt when its budget is exceeded. Interrupt timers are not allowed for the highest interrupt priority since the kernel interrupts are of this level, and blocking these will result in system malfunction.

Execution by proxy improves system performance by reducing the number of context switches needed. When task  $\tau_a$  executes a protected operation releasing task  $\tau_b$  that is blocked on an entry,  $\tau_a$  will also execute the entry on behalf of  $\tau_b$ . By charging  $\tau_b$  the execution time spent on the entry this implementation improves the accuracy of the execution time measurement and the execution time of the entry does not have to be added to the budget of  $\tau_a$ . The usefulness of this feature is highly dependent on the implementation overhead for changing timers compared to the execution time of the entry. Testing of the implementation indicates that the overhead of changing clocks may be larger than the execution time of the entry. Still there is some usefulness in exchanging a variable overhead of entry-by-proxy execution with a constant.

#### 3.2.3 Modifications to Ada 2005 standard library

In order to support execution time control for interrupts, additions had to be made to Annex D of the Ada 2005 standard [32] as shown in Listing 3.1. These changes were made in the existing execution time control packages specified instead of adding new packages to the standard library. In Ada.Execution\_Time the function Interrupt\_Clock was added to support execution time measurement for interrupt priorities. It returns the total time spent by all interrupt handlers of the given interrupt priority since start-up.

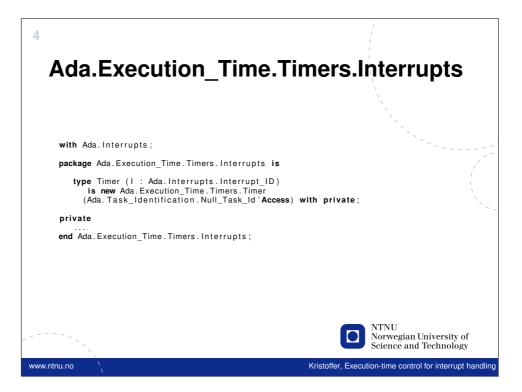

Also, the tagged type Interrupt\_Timer was added to Ada.Execution\_Time.Timers to

Listing 3.1: First API proposal for interrupt execution time control.

```

package Ada.Execution_Time is

...

function Interrupt_Clock ( Priority : System.Interrupt_Priority )

return CPU_Time;

...

end Ada.Execution_Time;

package Ada.Execution_Time.Timers is

...

Pseudo_Task_Id : aliased constant Ada.Task_Identification.Task_Id

:= Ada.Task_Identification.Null_Task_Id;

type Interrupt_Timer (I : System.Interrupt_Priority )

is new Timer (Pseudo_Task_Id'Access) with private;

end Ada.Execution_Time.Timers;

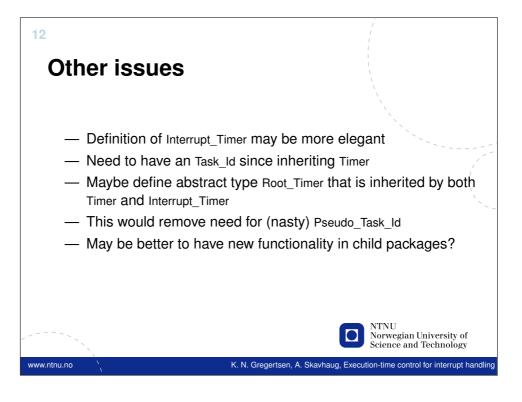

```