# Power Distribution and Conditioning for a Small Student Satellite

Design of the NUTS Backplane & EPS Module

Dewald De Bruyn

Master of Science in Engineering Cybernetics Submission date: June 2011 Supervisor: Amund Skavhaug, ITK Co-supervisor: Roger Birkeland, IET

Norwegian University of Science and Technology Department of Engineering Cybernetics

# **Problem Description**

The NUTS (NTNU Test Satellite) project was started in September 2010. The project is part of the Norwegian student satellite program run by NAROM (Norwegian Center for Space-related Education). The projects goal is to design, manufacture and launch a double CubeSat by 2014.

As part of the NUTS satellite design, there is a need for a system backplane, which different sub-modules can be plugged into. The backplane will form the basis of the satellite, and must provide distribution of power and communication buses to the rest of the system.

The Electrical Power System is a very important part of any satellite mission, and must handle power conversion and battery charging, as well as provide regulated supply to the rest of the system. Together with the system backplane, an EPS module has to be designed for the NUTS satellite.

The candidate will:

- Gain an overview of the project and outline the necessary requirements and constraints.

- Become familiar with previous work on the subject.

- Propose a solution for a system backplane and electrical power system.

- Implement and test prototypes of the solutions, as extensively as allowed by the project time frame.

- Evaluate the proposed design and the results obtained from testing.

Assignment given: 10. January 2011 Supervisor: Amund Skavhaug, ITK

## Summary & Conclusion

The NTNU Test Satellite project aims to launch a 10x10x20 cm nanosatellite, weighing less than 2.66 kg. The satellite, which follows the CubeSat standard, is a relatively low cost project, and explores the use of comercially available, low cost electronic components in space. This work is mainly concerned with power management and distribution for NUTS, but also describes the design of a system backplane.

The thesis is split into two parts. The first describes the design and evaluation of the backplane with main focus on power distribution, and the second part describes battery charging and power conversion in the Electrical Power System (EPS) unit.

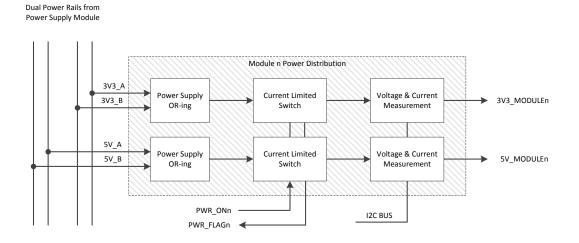

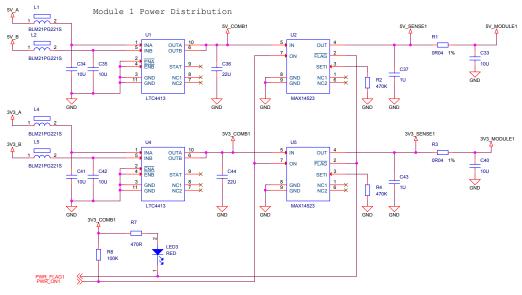

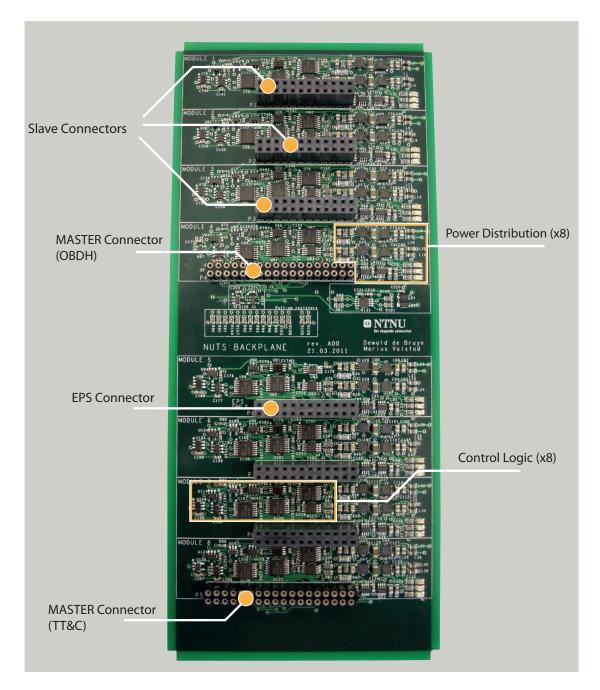

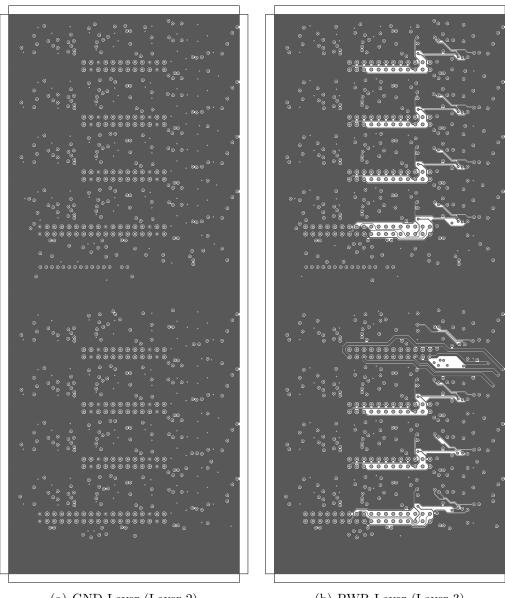

The backplane has been designed with flexibility, fault-tolerance and simplicity in mind. The design is based on a single  $I^2C$  bus with bus repeaters for each submodule, with the ability to isolate individual modules from the system in case of a malfunction. Power is distributed with dual 3.3 V and dual 5 V busses working in active redundancy, ensuring continued operation should a voltage converter fail. Power distribution for each module consists of three parts: power supply or-ing, current-limit switch and power monitor, and is integrated into the backplane. The state of the power switches and bus repeaters are controlled from two master modules, and a watchdog timer ensures return to a default state should both master modules be disabled.

The proposed solution integrates all the management logic and power distribution circuitry into the backplane itself, leaving the valuable PCB space on the submodules free for module implementations. The power distribution unit has been evaluated with a separate prototype, and displays good performance in terms of power losses and response to over-current conditions. A prototype implementation of the backplane has been produced.

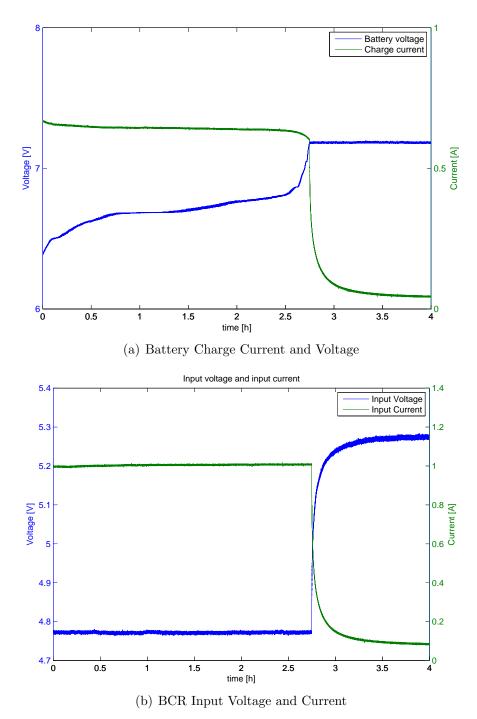

The electrical power system of the satellite consists of solar panels, batteries, and voltage converters. With very limited power available, the main focus of the design has been to reduce losses in power conversion. A battery charge regulator (BCR) has therefore been proposed, which charges the battery while keeping the solar panels at their maximum operating point. This integrates a *Maximum*  Power Point Tracking stage with a battery charger into a single converter, greatly increasing efficiency. Redundancy can be achieved by using separate converters for separate panels in parallel. A prototype BCR has been tested, and initial results show over 91% converter efficiency.

# Contents

| Ι        | 01            | verview                       | 1  |  |  |  |

|----------|---------------|-------------------------------|----|--|--|--|

| 1        | Intr          | roduction                     | 3  |  |  |  |

|          | 1.1           | NTNU Test Satellite Project   | 4  |  |  |  |

|          | 1.2           | Related Work                  | 5  |  |  |  |

|          | 1.3           | Scope & Disposition           | 9  |  |  |  |

| <b>2</b> | Background 11 |                               |    |  |  |  |

|          | 2.1           | The CubeSat Standard          | 11 |  |  |  |

|          | 2.2           | Satellite Power Systems       | 13 |  |  |  |

|          | 2.3           | Design Philosophy             | 21 |  |  |  |

|          | 2.4           | NUTS System Overview          | 23 |  |  |  |

| II       | N             | UTS Backplane                 | 27 |  |  |  |

| 3        | Bac           | kplane Introduction           | 29 |  |  |  |

|          | 3.1           | Purpose                       | 29 |  |  |  |

|          | 3.2           | Requirements                  | 30 |  |  |  |

|          | 3.3           | Specifications                | 34 |  |  |  |

| 4        | Bac           | kplane Implementation         | 37 |  |  |  |

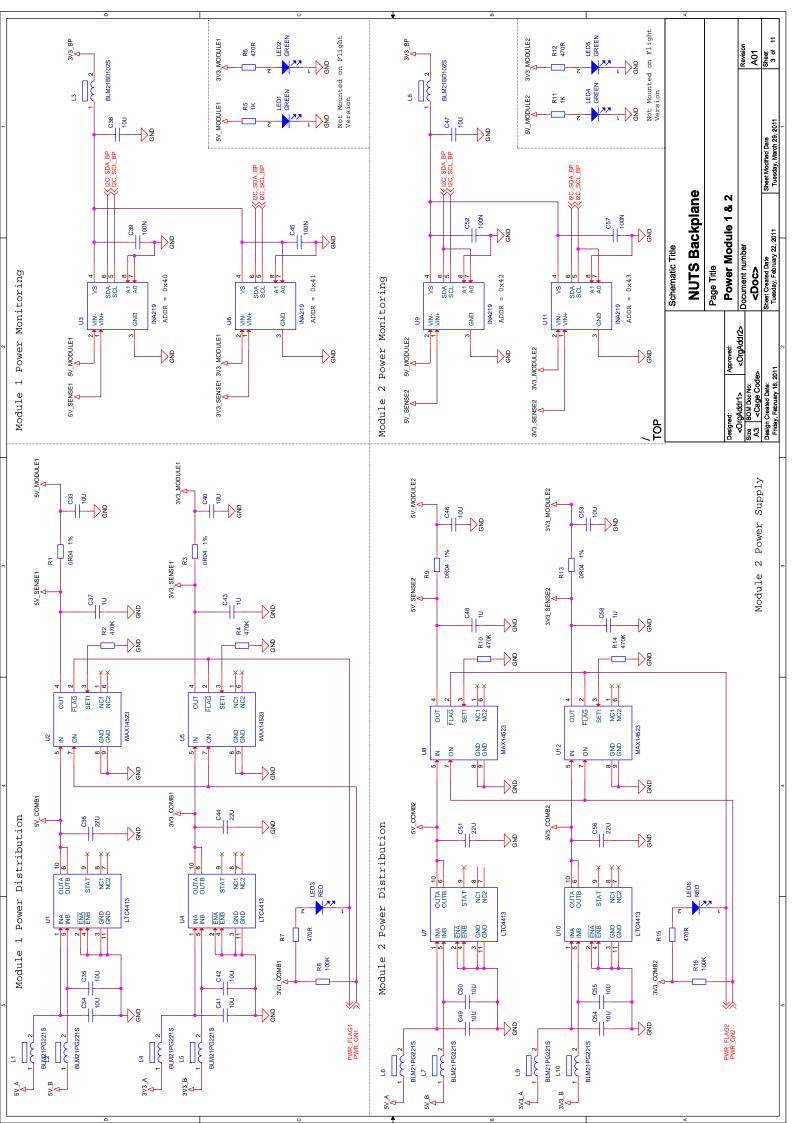

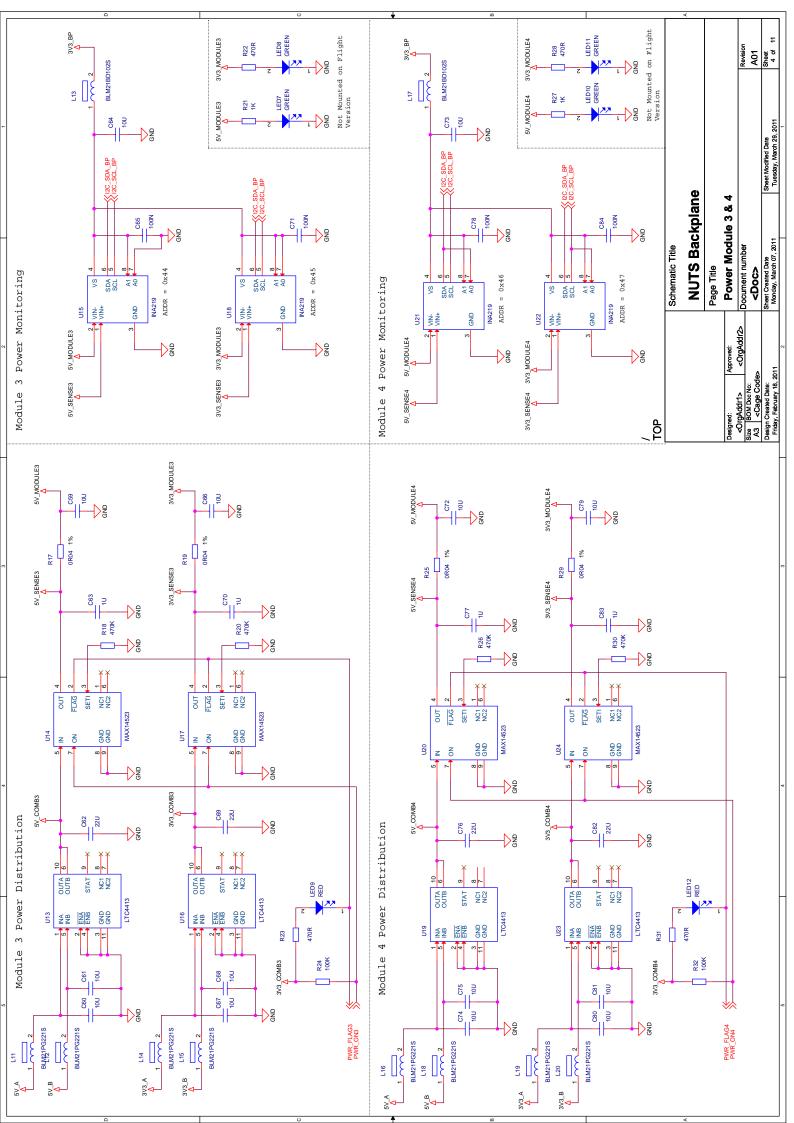

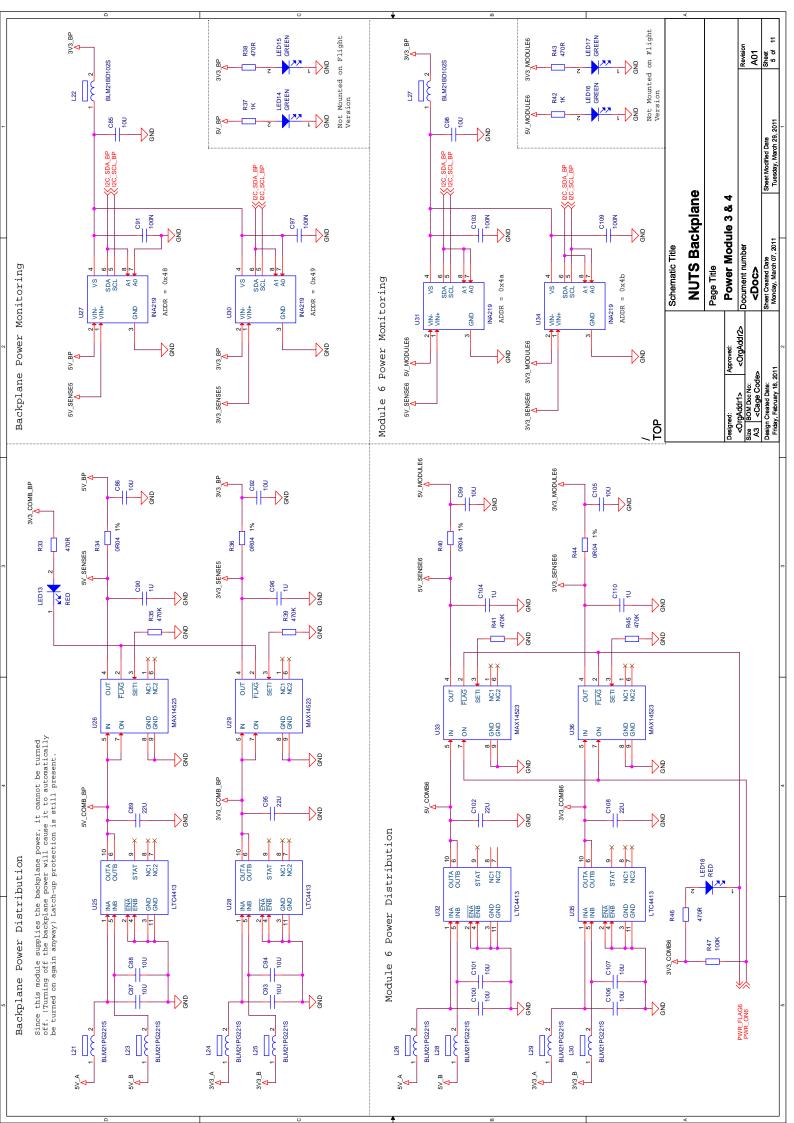

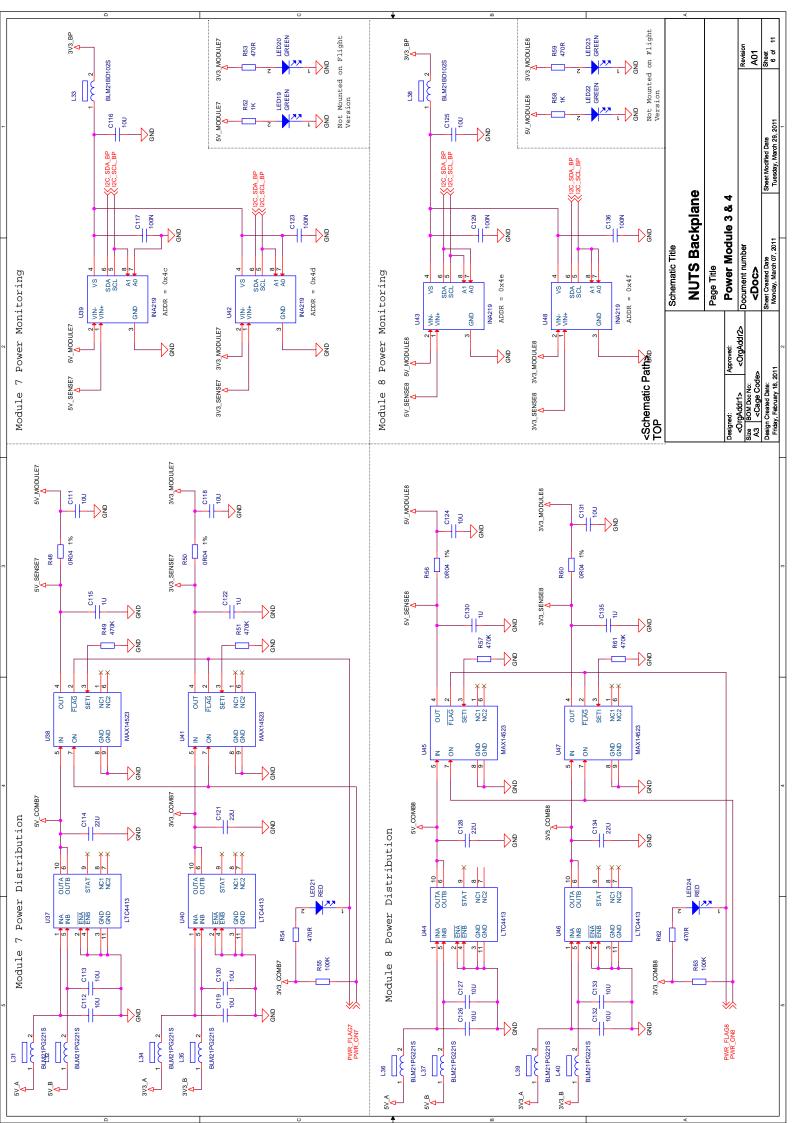

|          | 4.1           | Backplane Power Distribution  | 37 |  |  |  |

|          | 4.2           | Communication Bus             | 43 |  |  |  |

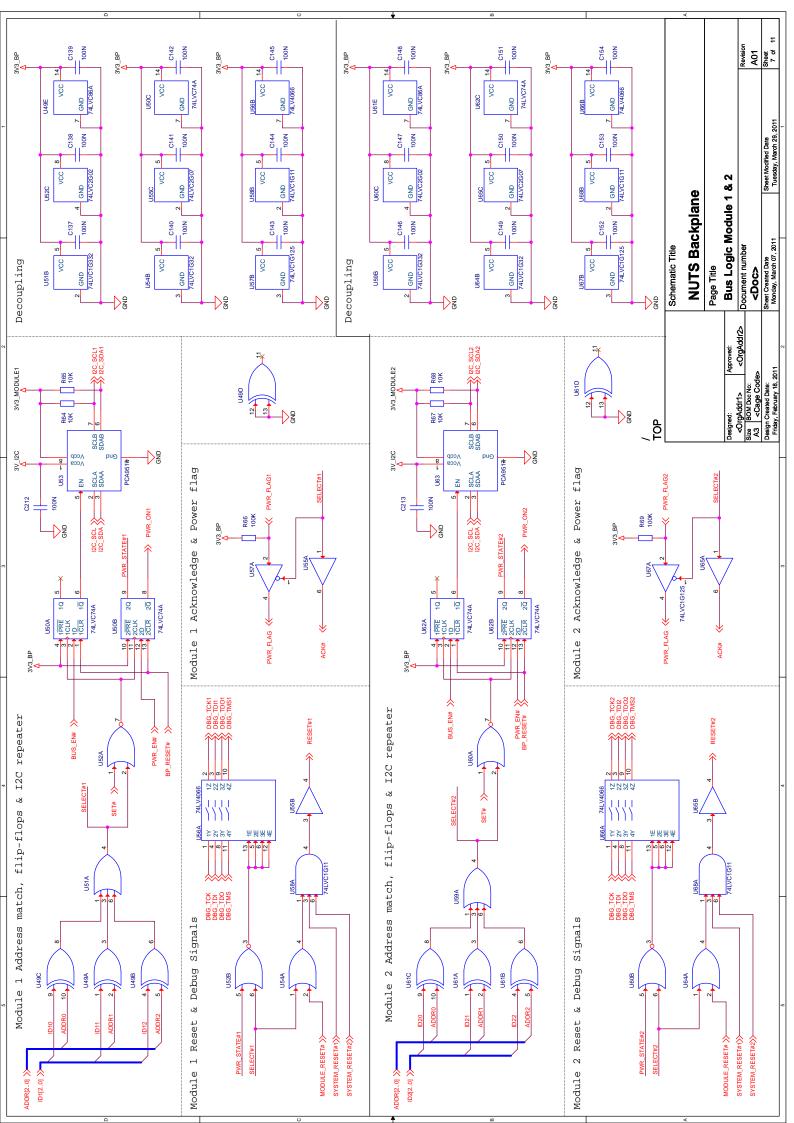

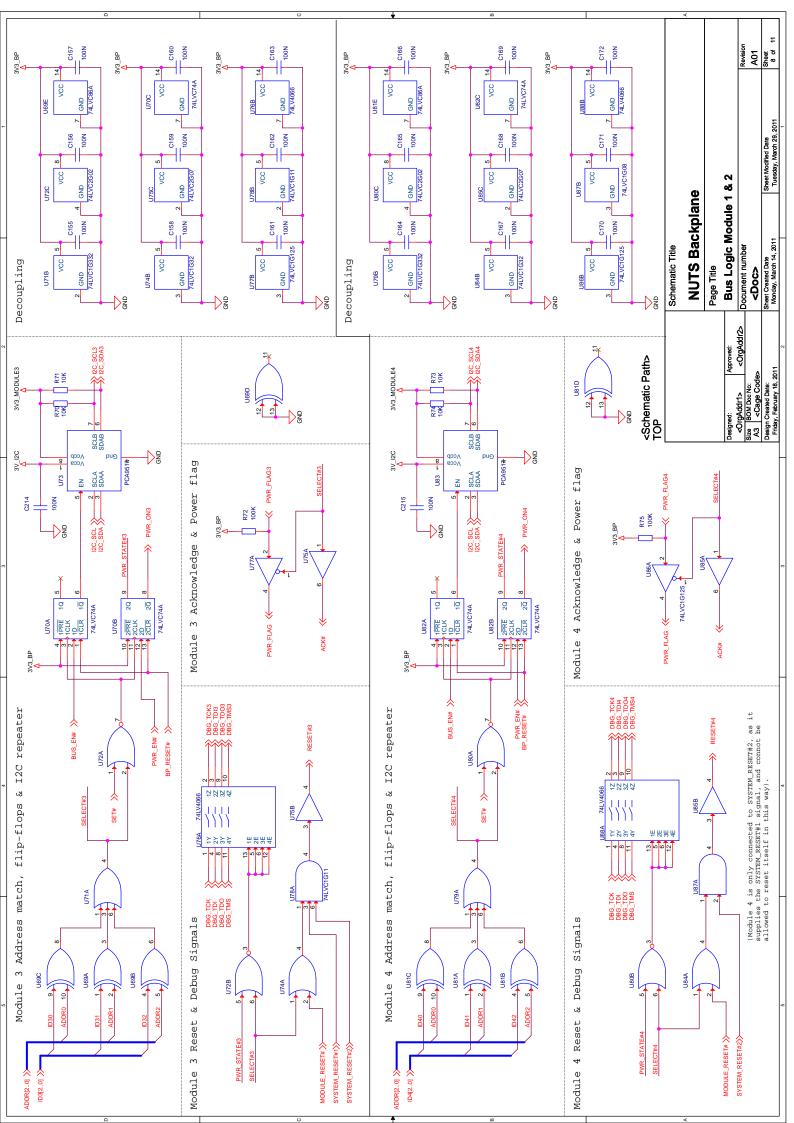

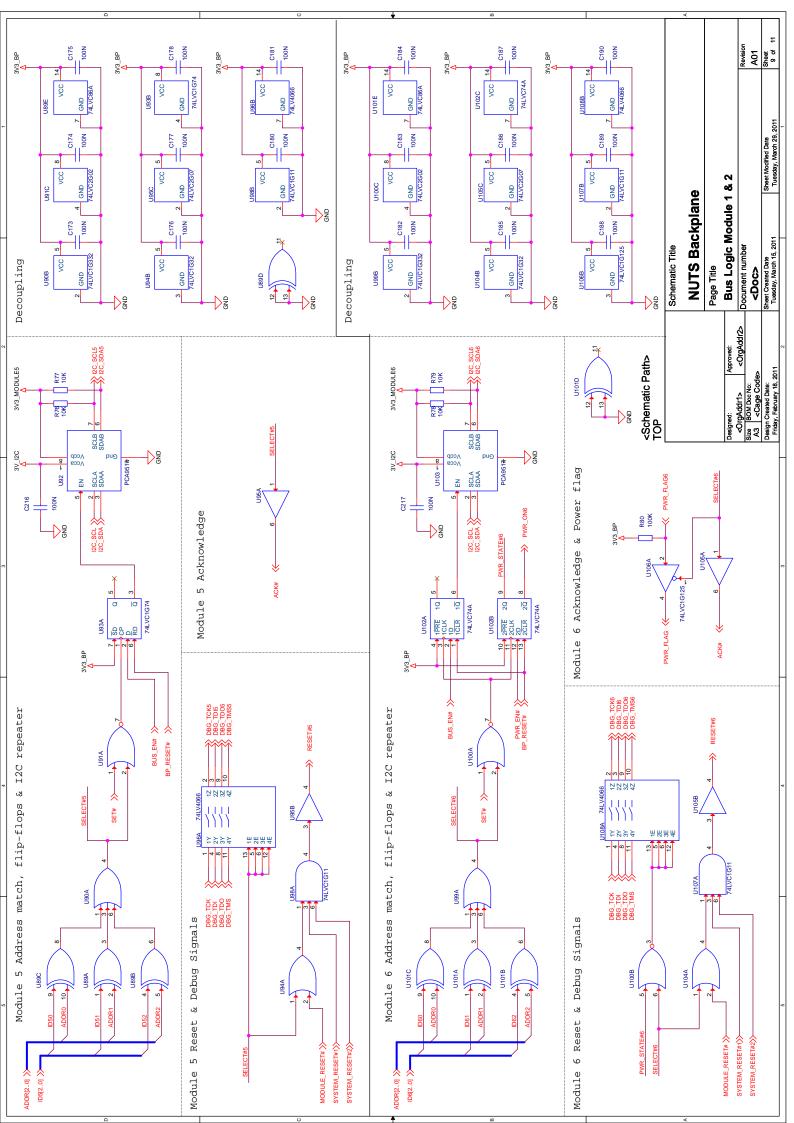

|          | 4.3           | Backplane Bus Logic           | 45 |  |  |  |

|          | 4.4           | EPS & Master Module Slots     | 48 |  |  |  |

|          | 4.5           | Backplane Reset Monitor       | 49 |  |  |  |

|          | 4.6           | Connectors                    | 50 |  |  |  |

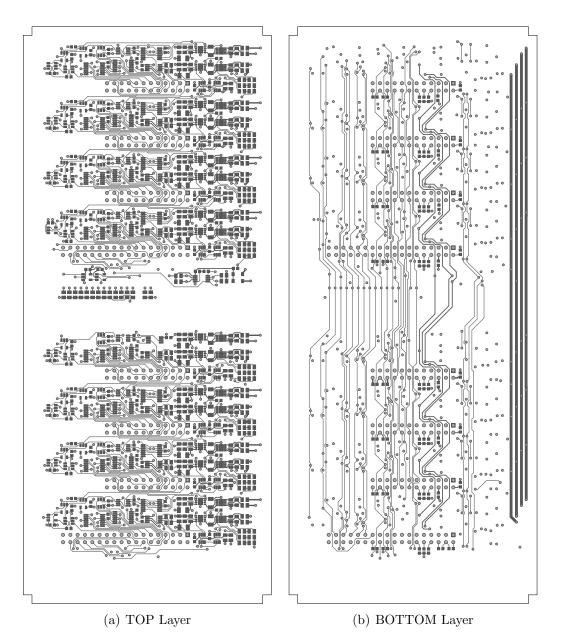

|          | 4.7           | Schematic Design & PCB Layout | 51 |  |  |  |

|          | 4.8           | Production                    | 52 |  |  |  |

| 5        | Backplane Testing & Verfication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | 5.1 Power Distribution Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|          | 5.2 Backplane Initial Hardware Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58  |

| 6        | Backplane Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61  |

| Ū        | 6.1 Power Distribution Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -   |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00  |

| <b>7</b> | Backplane Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67  |

|          | 7.1 Design Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67  |

|          | 7.2 Evaluation of Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70  |

|          | 7.3 Recommended Changes/Fixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71  |

| 8        | Backplane Conclusion & Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73  |

| Π        | I NUTS EPS Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75  |

| 9        | EPS Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77  |

| 9        | 9.1 Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|          | 9.1         I in pose         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I</thi<> |     |

|          | 9.3 EPS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80  |

| 10       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85  |

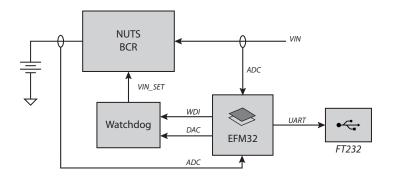

|          | 10.1 Battery Charge Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85  |

|          | 10.2 Analog Watchdog Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91  |

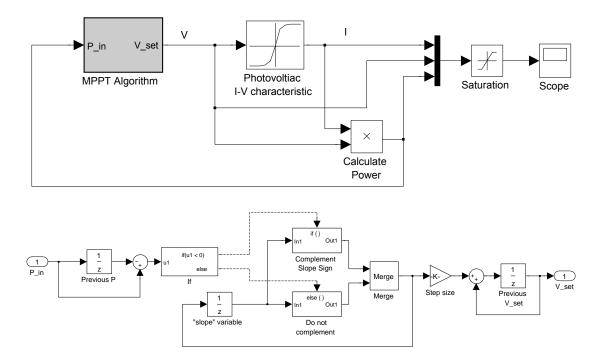

|          | 10.3 MPPT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94  |

| 11       | EPS Testing & Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99  |

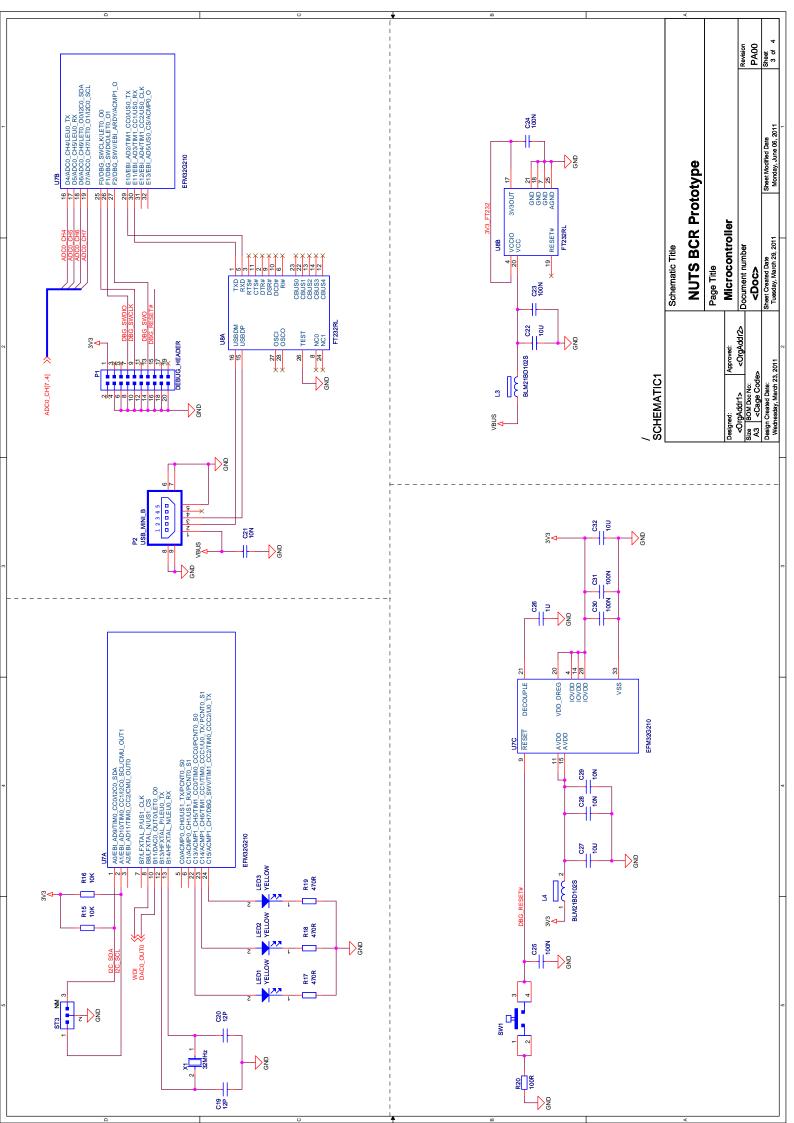

|          | 11.1 Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|          | 11.2 Batteries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|          | 11.3 Power Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

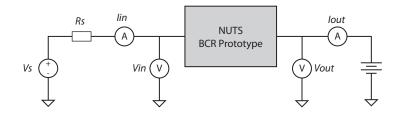

|          | 11.4 Efficiency Measurement Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 12       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .05 |

|          | 12.1 BCR Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105 |

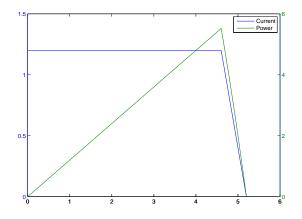

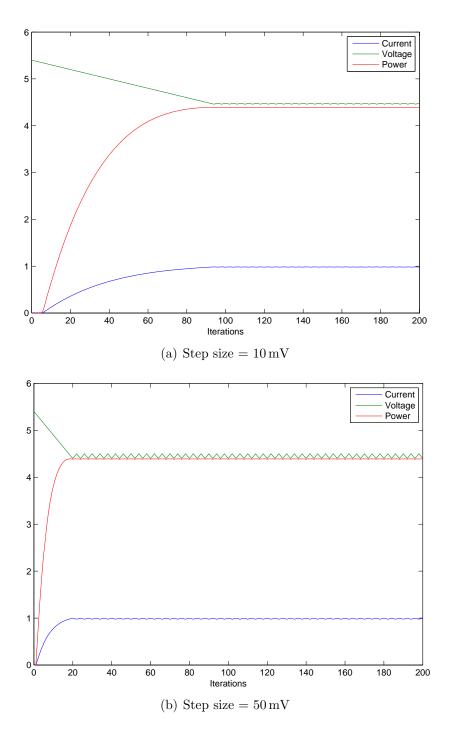

|          | 12.2 MPPT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

| 13       | EPS Discussion 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .11 |

|          | 13.1 Design Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111 |

|          | 13.2 Evaluation of Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|          | 13.3 Recommendations for Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113 |

| 14 EPS Conclusion |                                        | 115 |  |

|-------------------|----------------------------------------|-----|--|

| I۱                | Summary                                | 117 |  |

| 15                | Conclusion                             | 119 |  |

| $\mathbf{V}$      | Appendix                               | 123 |  |

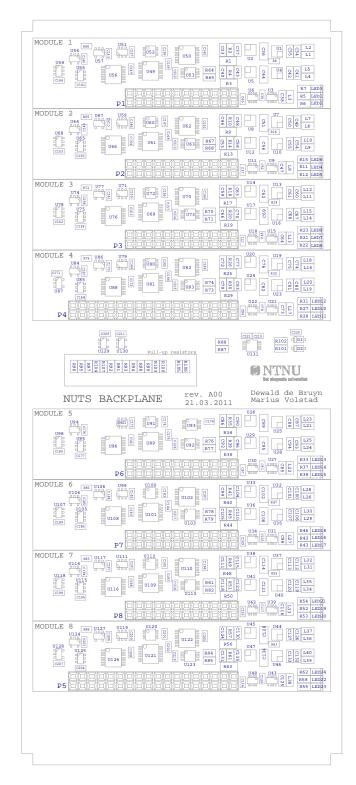

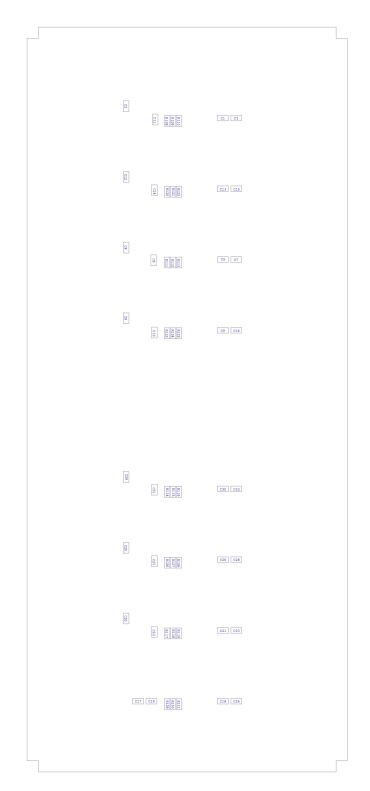

| $\mathbf{A}$      | NUTS Backplane PCB                     | 125 |  |

|                   | A.1 Assembly Drawing                   | 125 |  |

|                   | A.2 Bill of Materials                  | 128 |  |

|                   | A.3 Gerber Files                       | 130 |  |

| в                 | Schematics                             | 133 |  |

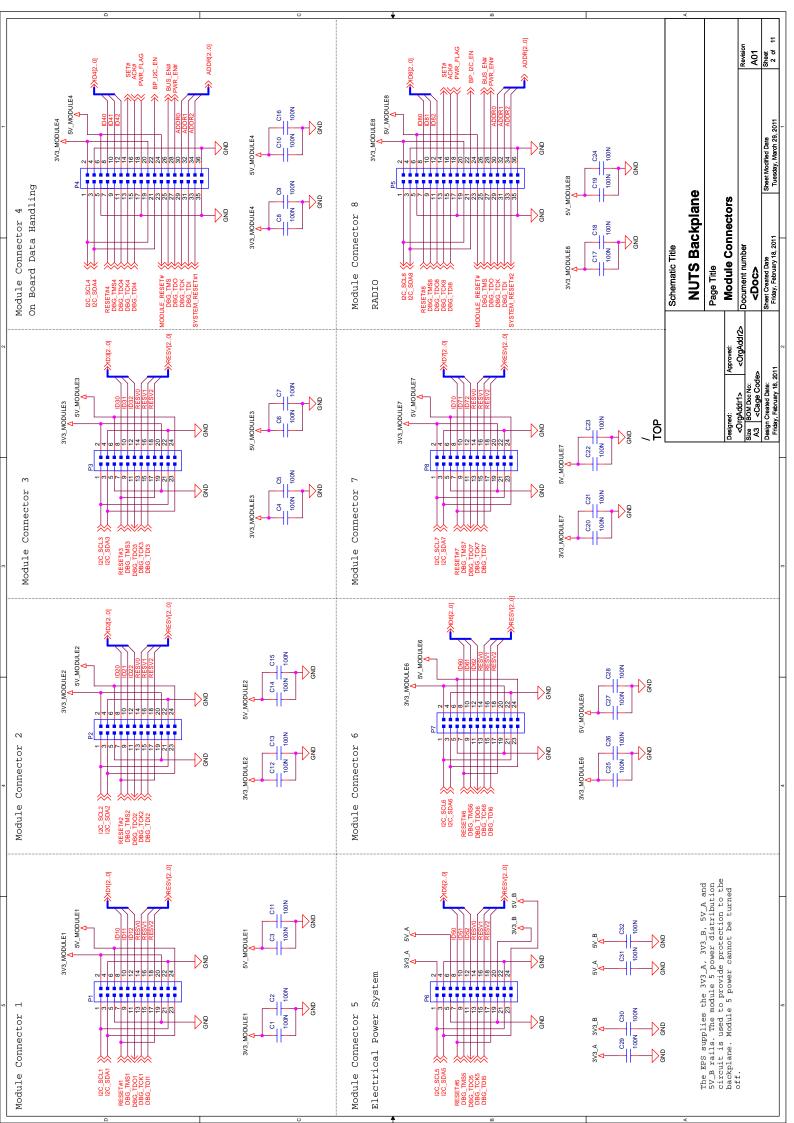

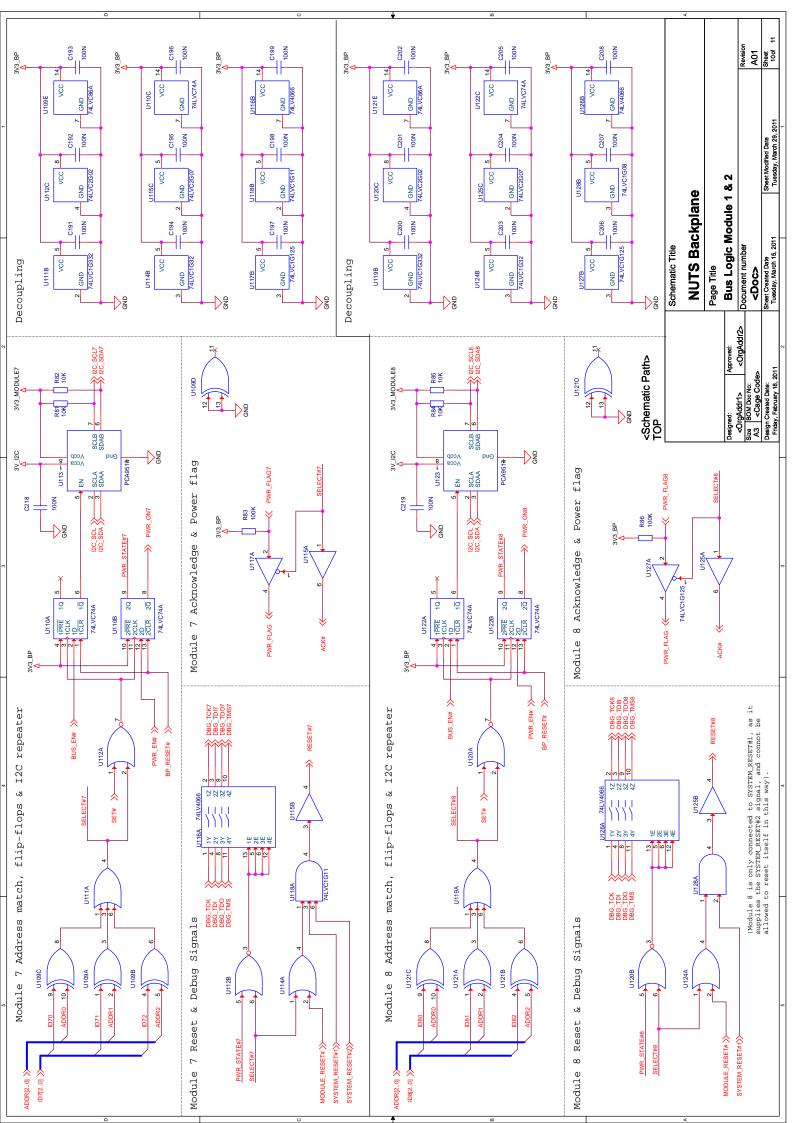

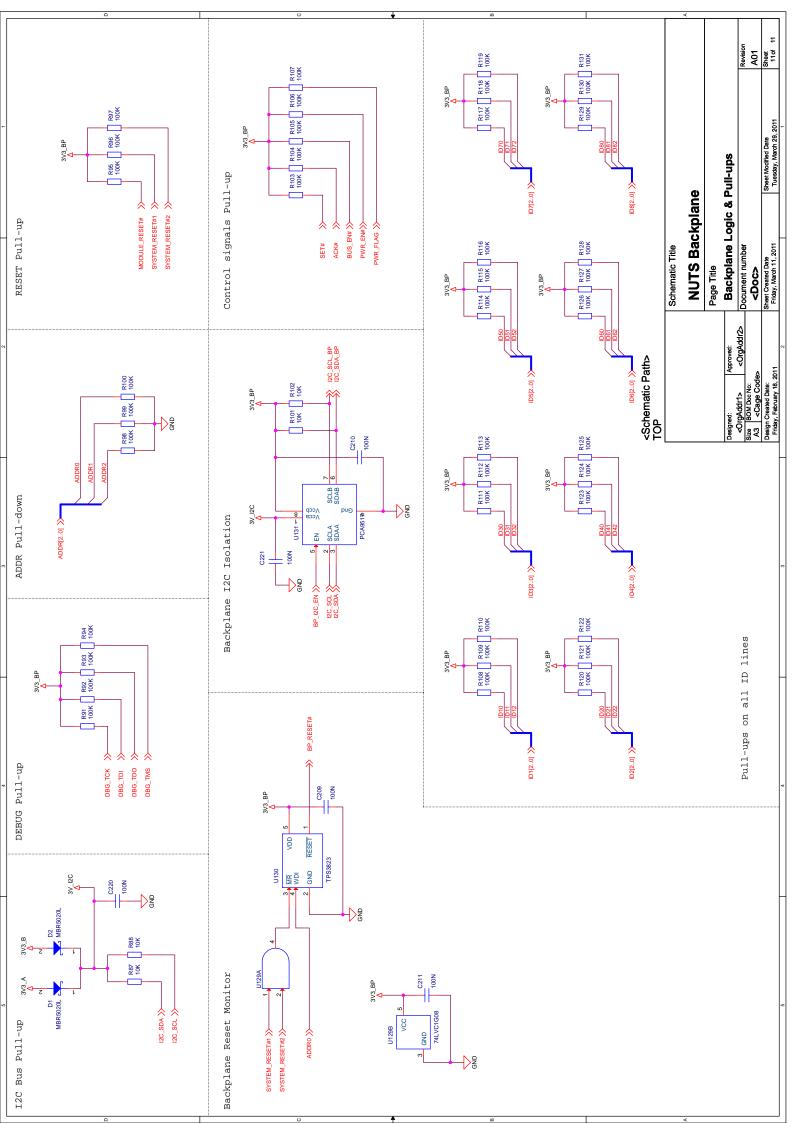

|                   | B.1 Backplane Schematics               | 133 |  |

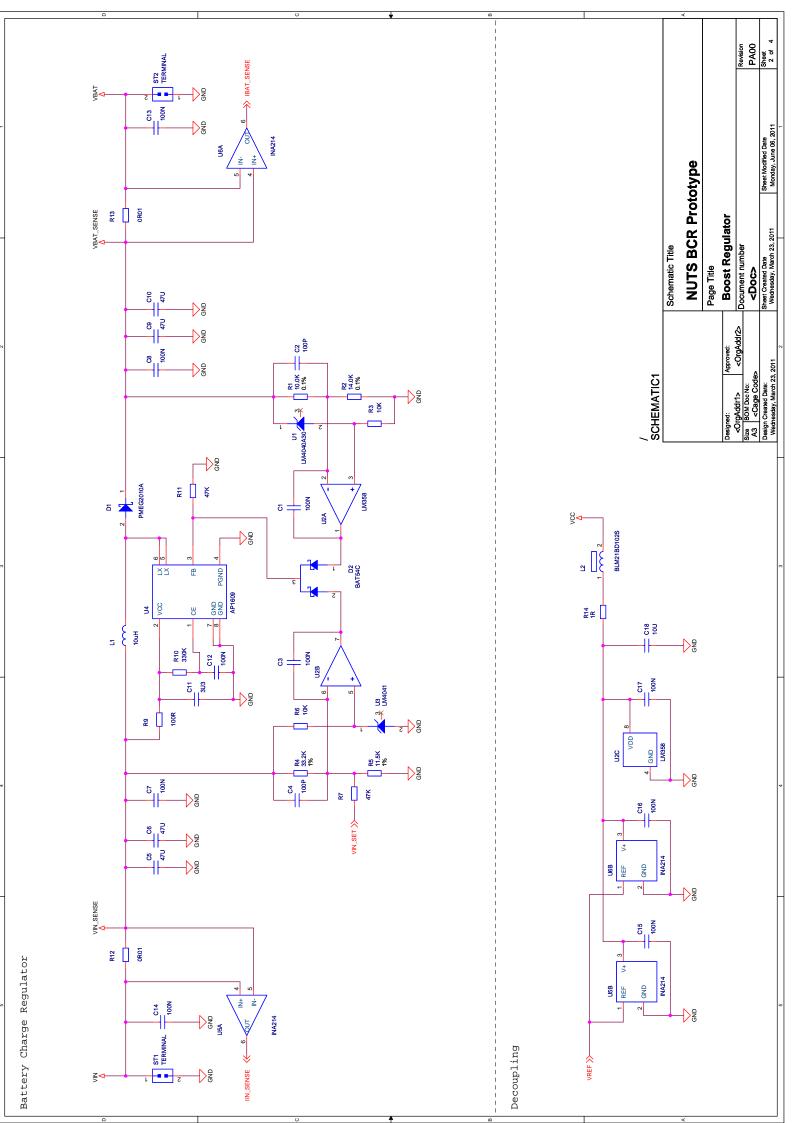

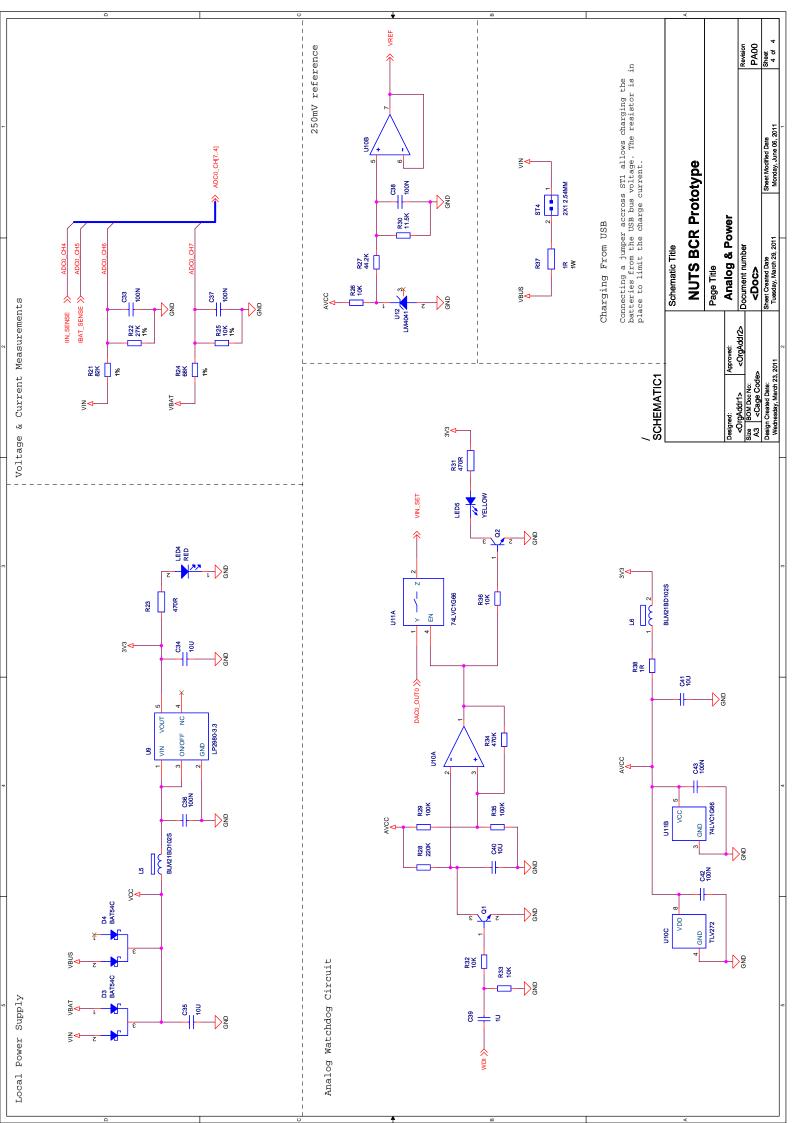

|                   | B.2 BCR Prototype Schematics           |     |  |

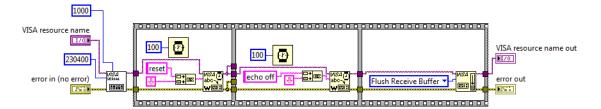

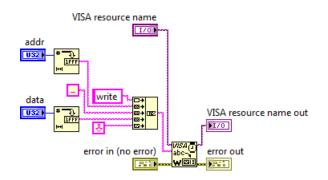

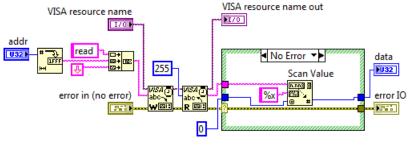

| $\mathbf{C}$      | LabView VIs                            | 151 |  |

|                   | C.1 Power Distribution Unit Test Setup | 151 |  |

| D                 | Loadbench EFM32 Source Code            | 155 |  |

|                   | D.1 main.c                             | 155 |  |

|                   | D.2 cmdshell.c                         |     |  |

|                   | D.3 $\operatorname{cmdlist.h}$         | 163 |  |

|                   | $D.4 \text{ cmd}_{funcs.c}$            | 164 |  |

# List of Figures

| 1.1 | NCUBE2, a 1U CubeSat designed in Norway                         | 6  |

|-----|-----------------------------------------------------------------|----|

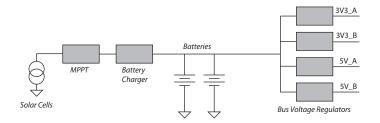

| 1.2 | Power System Architecture by Lars Opkvitne                      | 8  |

| 2.1 | 1U CubeSat Dimensions                                           | 12 |

| 2.2 | Eclipse                                                         | 14 |

| 2.3 | Spectrolab 29.5% XTJ Solar Cell Typical I-V characteristic [20] | 16 |

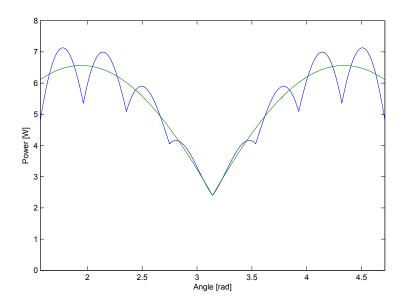

| 2.4 | Worst-case power vs. $\theta$                                   | 18 |

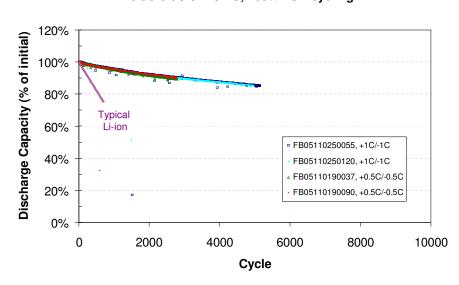

| 2.5 | A123 Systems Inc. Capacity vs. Charge Cycles [12]               | 20 |

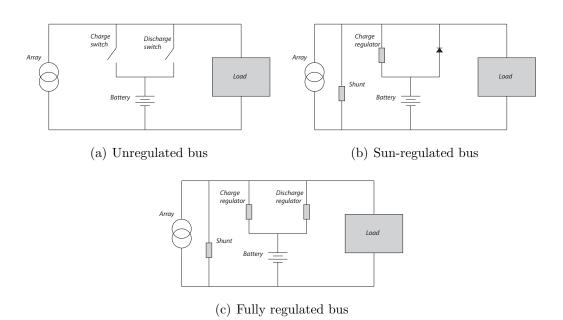

| 2.6 | Basic levels of bus regulation [4]                              | 20 |

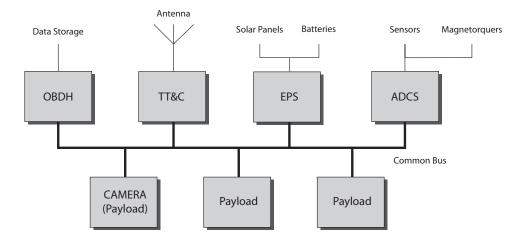

| 2.7 | NUTS Sub System Modules                                         | 24 |

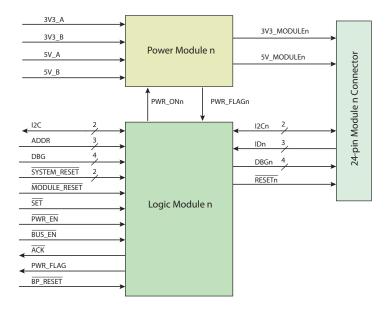

| 3.1 | NUTS Backplane power distribution module                        | 35 |

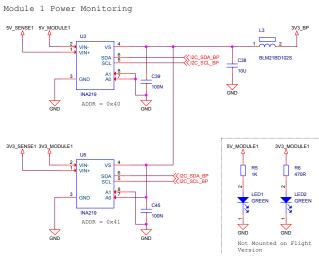

| 4.1 | Module Power Distribution                                       | 38 |

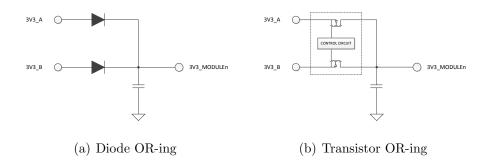

| 4.2 | Power Supply OR-ing                                             | 39 |

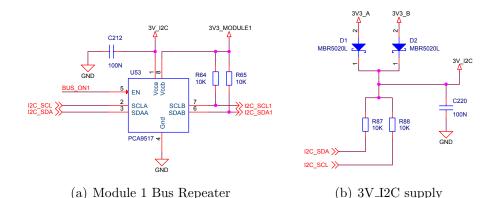

| 4.3 | Backplane I <sup>2</sup> C bus repeaters                        | 44 |

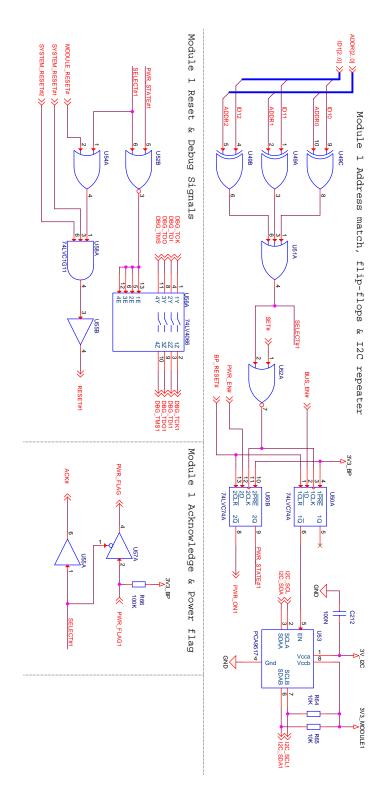

| 4.4 | Backplane Logic Unit                                            | 45 |

| 4.5 | Backplane Logic Circuit for Module 1                            | 47 |

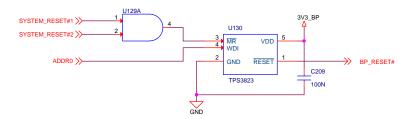

| 4.6 | Backplane Reset Monitor                                         | 49 |

| 4.7 | Connector Pinouts                                               | 50 |

| 4.8 | Final Backplane Board                                           | 53 |

| 5.1 | Power Distribution Module Test Setup                            | 56 |

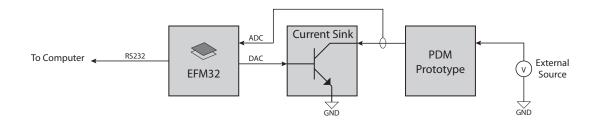

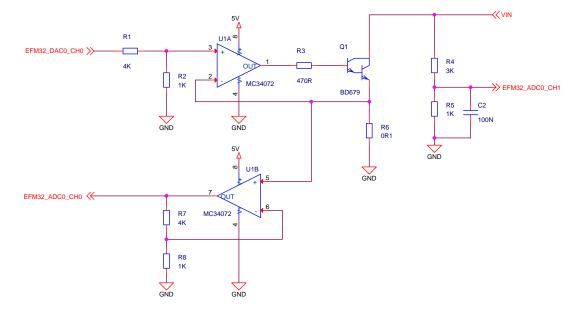

| 5.2 | Programmable Load Circuit                                       | 56 |

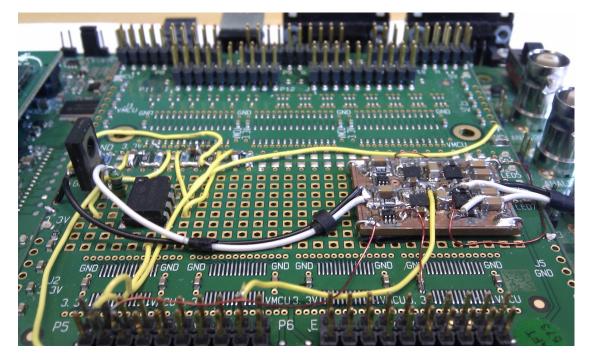

| 5.3 | Test setup on the Gecko DK                                      | 57 |

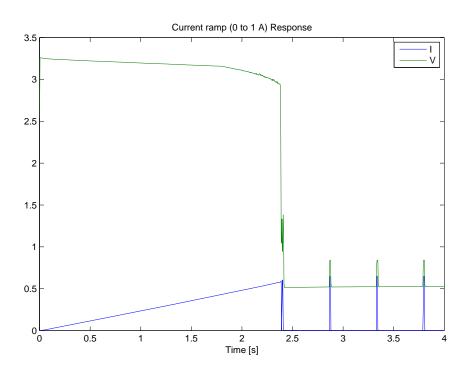

| 6.1 | Response to a linear current ramp over 4 seconds                | 62 |

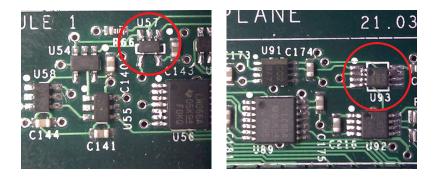

| 6.2 | Components in wrong packages                                    | 63 |

| 9.1 | EPS Architecture                                                | 80 |

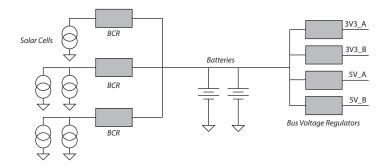

| 9.2 | EPS with 3 BCR units                                            | 82 |

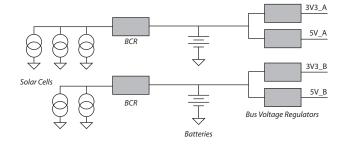

| 9.3 | Separate battery charging                                       | 82 |

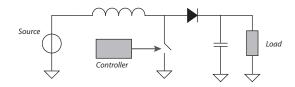

| 10.1  | Basic Step-up Converter                                                       |

|-------|-------------------------------------------------------------------------------|

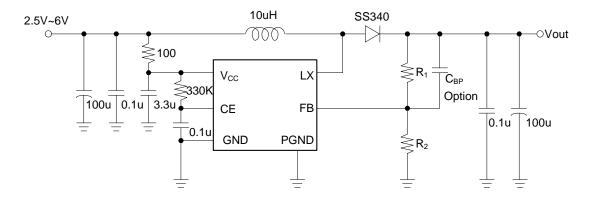

| 10.2  | AP1609 Typical Application. Taken from the data sheet [13] 88                 |

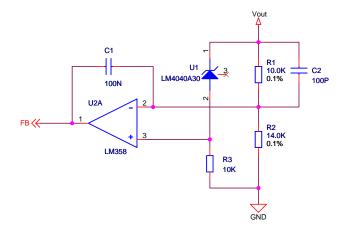

| 10.3  | BCR End-of-Charge Control                                                     |

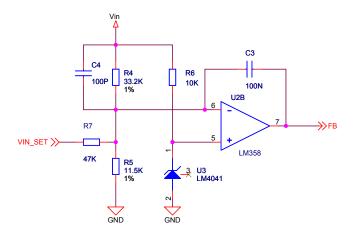

| 10.4  | BCR Input Voltage Regulation                                                  |

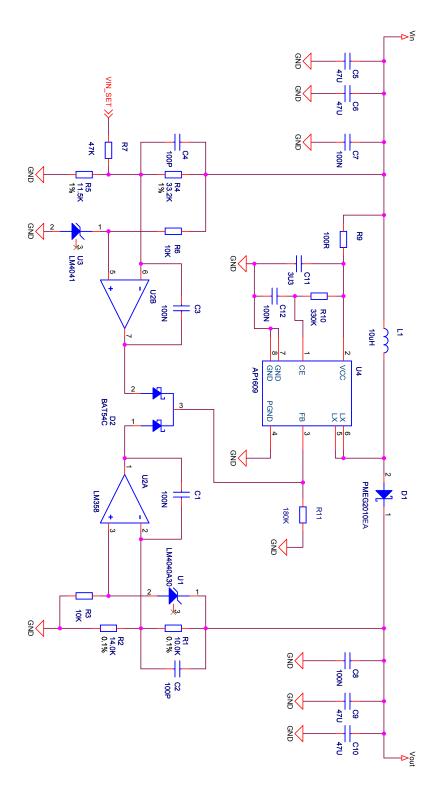

| 10.5  | Battery Charge Regulator                                                      |

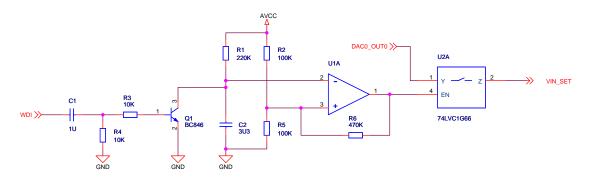

|       | EPS Watchdog Circuit                                                          |

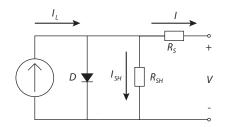

| 10.7  | One-Diode Model                                                               |

|       | Simplified model I-V characteristic                                           |

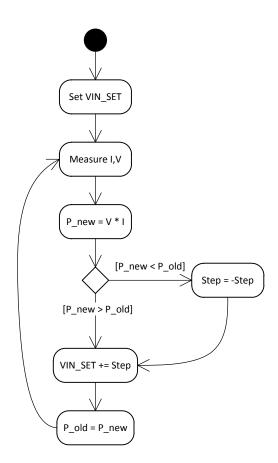

| 10.9  | Simple MPPT Algorithm                                                         |

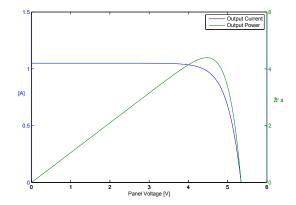

| 10.10 | OSimulink Test of MPPT Algorithm                                              |

|       |                                                                               |

|       | BCR Prototype Block Diagram                                                   |

|       | Battery Pack used in testing of the BCR Prototype 101                         |

|       | I-V characteristic of a current limited PSU with series resistor $\ldots$ 102 |

| 11.4  | Efficiency Measurement Setup                                                  |

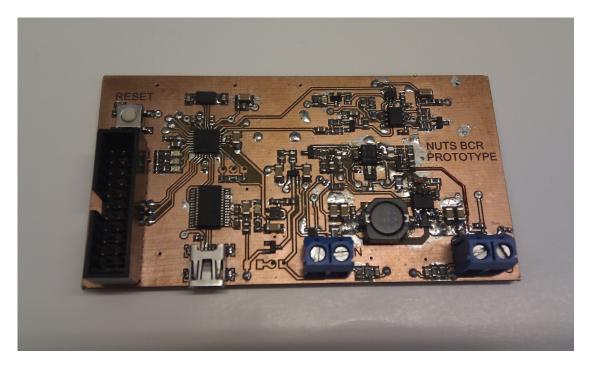

| 19.1  | BCR Prototype                                                                 |

|       | BCR Results                                                                   |

|       |                                                                               |

| 12.5  | Simulation of MPPT Algorithm                                                  |

| A.1   | Backplane Assembly Drawing (top)                                              |

| A.2   | Backplane Assembly Drawing (bottom)                                           |

| A.3   | Backplane Bill of Materials (print-out)                                       |

| A.4   | Backplane TOP & BOTTOM layers                                                 |

| A.5   | Backplane GND & PWR layers                                                    |

|       |                                                                               |

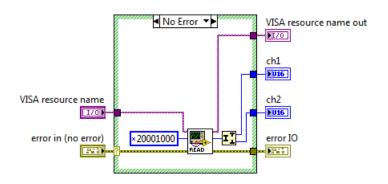

| C.1   | init.vi                                                                       |

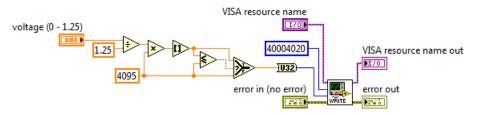

| C.2   | write.vi                                                                      |

| C.3   | read.vi                                                                       |

| C.4   | adc.vi                                                                        |

| C.5   | dac.vi                                                                        |

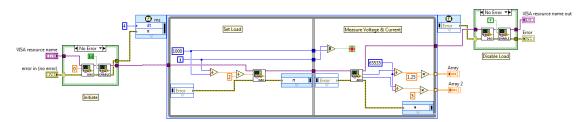

| C.6   | Current Ramp VI                                                               |

# Part I Overview

# Chapter 1 Introduction

Access to space for universities has traditionally been limited by the extreme costs associated with space missions. Large communication satellites can have a total cost of ownership of more than \$100 million. Recent developments in nano- and picosatellites has opened up a whole new frontier for universities and other organizations with small budgets and time frames, allowing payloads to be launched with a fraction of the cost of incorporating it into a traditional satellite.

A nanosatellite is defined as an artificial satellite with a mass between 1 and 10 kg, while a picosatellite weighs less than 1 kg. These small satellites are usually launched as passengers alongside larger satellite missions. [16]

As solar cells increase in efficiency, the amount of useful work that can be achieved with nanosatellites is also increasing. These small satellites can be used to test novel components for future space missions, or to perform specific scientific missions on a small scale. Many universities around the world have taken an interest in the development and launching of nanosatellites, which provides unique educational opportunities spanning many fields of engineering. [9]

A typical nanosatellite mission differs greatly from the development and deployment of tradition satellites in a number of ways. Firstly, the development costs and development time is drastically reduced by scaling the design down, and by using *commercial off the shelf* (COTS) components. Secondly, the mission duration of nanosatellite missions is often very short compared to commercial missions, usually around 3-6 months of operation instead of 5-10 years. The combination of low cost and short mission lifespan allows new and innovative components to be used which would not normally be considered for a satellite mission.

A number special considerations and limitations apply to nanosatellites that do not normally apply to larger satellites, requiring special design. For example, in a commercial satellite mission, the solar panels are dimensioned so that the end of life capacity is high enough to support the payload until the end of the mission timespan. In a nanosatellite, the amount of available power is very limited, and not much can be done to increase this, so the payload and mission length has to be adapted accordingly, and power-efficiency in the satellite systems becomes much more important. Other limiting factors are volume and weight constraints.

Despite having serious constraints on available power, volume and weight, nanosatellites have some great advantages. Since the mission duration is relatively short, and the investment is small, requirements on reliability and redundancy are greatly eased. This allows for greater flexibility in the system design, and allows other factors such as simplicity and power-efficiency to be weighted. Because of the very low cost of launching a nanosatellite, the common approach held by many developers is that redundancy can simply lie in the ability to launch another satellite.

Although the development of nanosatellites differs significantly from traditional satellite design, it also differs from the design earth-based systems. The space environment can be very harsh, as radiation, vacuum and temperature effects have to be taken into consideration. Possibilities for maintenance or recovery are virtually non-existent once the satellite has been launched. Since the satellites are usually launched as passengers together with other satellite missions, considerations has to be taken to prevent the nanosatellite from influencing the main mission. This includes thermal vacuum bakeout to ensure proper outgassing of components, which can otherwise effect the solar cells, optics or other systems of other satellites.

## 1.1 NTNU Test Satellite Project

The NTNU Test Satellite, also abbreviated "NUTS" is a project aiming to launch a nanosatellite into Low Earth Orbit (LEO). The satellite, measuring only  $10 \times 10 \times 20$  cm, and weighing less than 2.66 kg, conforms to the CubeSat Standard, which allows easy and affordable access to space for universities and other organizations.

The NUTS (NTNU Test Satellite) project was started in September 2010. The project is part of the Norwegian student satellite program run by NAROM (Norwegian Centre for Space-related Education). The projects goal is to design, manufacture and launch a double CubeSat by 2014. The national student satellite program involves three educational establishments, namely the University of Oslo (UiO), Narvik University College (HiN) and NTNU.

As main payload, the NUTS project will fly an IR-camera for atmospheric observations. In addition, a concept for a wireless short range data bus connecting different subsystems will be added. For communication, the satellite will use the common amateur radio bands and fly one transceiver for each frequency. During the first half of 2011, ten students from different departments and curriculums were involved in the project.

The work outlined in this thesis has been done in the early stages of the project's

development, and can in a way be viewed as a bottom-up approach to satellite design. Many high level mission parameters and decisions are left for later, when more information about the payload and launch parameters become available.

The main goals of this thesis work has been to lay down a basis with which further development can proceed. The overall architecture of the satellite is based around a backplane with multiple module cards. The backplane provides common power and communication buses, while the rest of the satellite functionality and payloads are divided into several modules. Because of the limited development time available, it has been very important to quickly get a working prototype of the system backplane up and running, so that development of other modules can proceed.

A very important part of any satellite design is the power management system, as the satellite cannot function at all without power. The power system must provide constant regulated supply to all the modules, but must also be able to control the power drain in order to keep the battery voltage within safe limits. Furthermore, the system must be protected from anomalous situations such as short circuit faults.

### 1.2 Related Work

NTNU has previously been involved in the NCUBE student satellite project together with other Norwegian universities. Two satellites were constructed, NCUBE-1 and NCUBE-2. NCUBE-2 was launched first on October 27, 2005, but radio contact with the satellite was never achieved. It has later been tracked and identified by radar. NCUBE-1 was launched on July 26, 2006, but a problem with the second stage of the rocket caused a launch abort. Both NCUBE satellites were single CubeSats, measuring  $10 \times 10 \times 10$  cm, and weighing around 1 kg.

In the autumn semester of 2006, three master students started from scratch with a new specification for the design of a small student satellite. The new satellite was specified to be a double CubeSat unit, with dimensions of  $10 \times 10 \times 20$  kg. It is their report, "Design of a Small Student Satellite" [5] that forms the basic grounds for this project. With this report, a new CubeSat project at NTNU was initiated, largely moving away from the previous designs of the NCUBE satellites.

Since then a few other students have written project reports or thesis around the design and specification of different sub-systems for the NUTS project. A brief overview of previous work at NTNU concerning power management for NUTS is presented here.

Figure 1.1: NCUBE2, a 1U CubeSat designed in Norway

#### 1.2.1 Birkeland, Blom & Narverud, autumn 2006

The report by Roger Birkeland, Elisabeth Blom and Erik Narverud still serves as the main specification document for the NUTS satellite project. The choice of satellite platform was evaluated, and it was decided to conform to the CubeSat standard, with the double cube configuration.

They provide a general system specification, including a preliminary weight and energy budget for the satellite. It includes a considerations on the mechanical system and structure, antenna systems, power management, data handling, and the communications system. Thermal and orbital considerations are also taken into account. A distributed architecture is chosen for the organization of different system modules in the satellite, with modules communicating together on a shared communication bus. [5]

#### 1.2.2 Edgar Elden, autumn 2008

Elden addresses the power management problem, and proposes a strategy for charging the batteries from the solar cells, and distributing both batter power and raw solar cell voltage to the payload. The design is centered around a Master Power Manager, which has the responsibility to control the power of individual system modules, as well as perform error recovery should the on board computer (OBC) encounter problems. He proposes separate power management controllers for the payload and other system modules, consisting of power switches, fuses and a microcontroller for individual payload power management.

In his design, the Master Power Manager controls the charge and discharge of the battery, but leaves the responsibility of voltage regulation to the individual modules. [10]

#### 1.2.3 Ingulf Helland, autumn 2008

In his project report, Helland addresses the problems and design of a central communication bus. He proposes a redundant bus system, with two equivalent busses providing both communication and power. This solution provides full redundancy in case one of the busses should fail. Each module contains two slave bus controllers, two sets of power switches and fuses, a bus selection multiplex-er/demultiplexer and an intelligent power regulator. Support also exists for several addressable units within each module card, requiring additional multiplexing/demultiplexing circuitry. In his design, Helland estimates about 50% of the PCB area on each module to be occupied by bus logic and power regulation & control.

Helland also presents a significant effort in failure analysis of the design, and also presents some general guidelines for failure analysis for the NUTS project as a whole. [11]

#### 1.2.4 Lars O. Opkvitne, spring 2009

The report by Lars Opkvitne is the most recent contribution to the work on a Power Management System for the NUTS project. Opkvitne presents a thorough study of power management strategies for small satellites. A few different strategies for power management is discussed including the use of MPPT (Maximum Power Point Tracking) and DPPM (Dynamic Power Path Management).

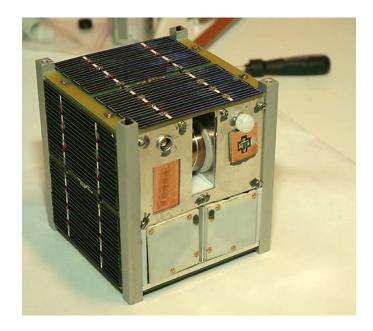

The design he proposes is again based on two redundant power buses. He proposes a system where half the solar cells are used to charge half the batteries, with two power systems in hot redundancy. Figure 1.2 is an overview of the power management system as proposed by Opkvitne. A prototype has been constructed which tests the battery charging and state of charge (SOC) monitoring circuits. [17]

#### **1.2.5** Commercial Solutions

The related work mentioned so far has only included previous projects at NTNU. As the interest for CubeSats is steadily growing several companies have started to offer complete platform solutions in the form of satellite kits. This has evolved to the extent that one can purchase an entire satellite, incorporate one's own payload, and launch in a very short time span. This is worth mentioning because

Figure 1.2: Power System Architecture by Lars Opkvitne

many of the problems encountered in this project has already been addressed, and commercial solutions are available. For example the website www.cubesatkit.com sells a complete system solution, including chassis, solar panels and several avionics boards from Pumpkin Inc.

Other manufacturers of CubeSat components worth mentioning are GOMSpace, stemming from the University of Aalborg in Denmark, and UK-based Clyde-Space. Both these companies are also involved in small satellite projects other than Cube-Sats. [1,2]

The main reason for choosing not to base the NUTS project on existing solutions is the educational value present in designing a satellite from scratch. The wish to design a system around a backplane instead of using the standard PC-104 stacking system also eliminates many possiblities of choosing existing solutions for system components.

Lastly, since the CubeSat Project consists of a collaboration between more than 40 universities, high schools and private firms around the world, it is easy to obtain a lot of useful information about other CubeSat missions. Universities usually release their student's reports, and since many of the problems solved are similar to the ones encountered in the NUTS project, a lot can be learned from studying other successful and unsuccessful projects.

## **1.3** Scope & Disposition

Most of the previous work done in the NUTS project has been mainly theoretical work. Many important aspects of the design of a small student satellite has been covered in the different reports, but little actual hardware for further development in the project has been produced. Furthermore, many of the proposed solutions has focused mainly on reliability through redundancy, with less focus on simplicity and power, weight and area efficiency.

In this work, an overview is presented of the problems and challenges associated with power management in a small satellite, and a design proposal is made where the power management problem is split into two parts. The two parts are power distribution and power conditioning, to be implemented as separate hardware units in the system. The power distribution part is integrated into a satellite backplane together with a communication bus and control logic, and the power conditioning is designed as a module that plugs into the backplane.

This work presents the design of the entire backplane, including power distribution and protection, communication bus and control logic. A fully functional hardware prototype has been produced that will form the basis of further satellite development. A proposed design for the electrical power system (EPS) module will also be presented, which handles charging batteries from solar cells and converting power for use in the rest of the system. A functional prototype of a battery charge regulator (BCR) with maximum power point tracking has been produced, which forms an important part of the EPS.

Chapter 2 presents some important background information and theory necessary to understand the problems posed. This includes information about the CubeSat standard, general theory about satellite power systems, a simple design philosophy and an overview of the different NUTS systems.

Part II is dedicated to the NUTS Backplane. Chapter 3 gives an overview over the backplane design requirements and specifications and chapter 4 details the implementation of the required functionality and the design of the circuit board. Chapter 5 presents a test setup used to test the power distribution module, as well as a functional verification of the backplane prototype. The results are presented in chapter 6, and discussed in chapter 7, and a short conclusion with recommendations for further work is given in chapter 8.

Part III is dedicated to the EPS module. Chapter 9 describes the design and architecture of the power conditioning system, and presents some functional requirements. Chapter 10 presents the implementation of a BCR prototype, and testing of the BCR is presented in chapter 11. The results are presented in chapter 12, and discussed in chapter 13, and a short conclusion with recommendations for further work is given in chapter 8.

Finally, part IV provides a combined summary and conclusion for the project

# Chapter 2 Background

To put this work in perspective, a brief overview of satellite power systems is given in this chapter. This will help to map the specific requirements and challenges related to power management for the NUTS nanosatellite. The CubeSat Standard is also presented, as this provides a set of external requirements to the project to make it eligible for launch.

## 2.1 The CubeSat Standard

The CubeSat Project is a concept developed by the Polytechnic University of California (Cal-Poly) and Stanford University to ease the development and deployment of picosatellites. By conforming to this standard, a satellite can be launched using the Poly Picosatellite Orbital Deployer, or P-POD, developed at Cal-Poly. The P-POD is a tubular, spring loaded mechanism designed for deploying up to three CubeSats, and can be integrated into almost any launch vehicle.

A basic CubeSat is a  $10 \times 10 \times 10$  cm cube weighing less than 1.33 kg. A satellite with the dimensions of two or three cubes can also be constructed and launched, called a double CubeSat (denoted 2U) or a triple CubeSat (denoted 3U). The P-POD can then either be loaded with three 1U satellites, one 2U and one 1U, or one 3U Satellite.

#### 2.1.1 Mechanical Requirements

The CubeSat Design Specification [6] consists of a set of requirements that need to be fulfilled in order to ensure compatibility with the P-POD, and to protect the launch vehicle, it's primary payload and other CubeSats. Conforming to this design specification is necessary to be able to launch a CubeSat.

Some important mechanical specifications from [6] are:

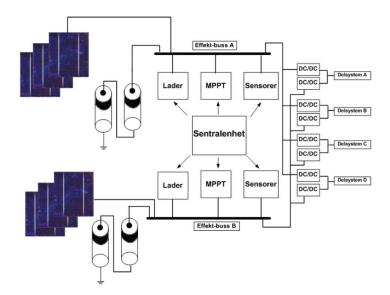

Figure 2.1: 1U CubeSat Dimensions

- The CubeSat shall be  $100.0\pm0.1$  mm wide.

- A single CubeSat shall be  $113.5\pm0.1$  mm tall, a triple CubeSat shall be  $340.5\pm0.3$  mm tall.

- Contact with the rails in the P-POD shall have a minimum width of 8.5 mm.

- Each single CubeSat shall not exceed 1.33 kg mass, each triple CubeSat shall not exceed 4.0 kg mass.

- The CubeSat center of gravity shall be located within a sphere of 2 cm form it's geometric center.

Figure 2.1 contains information about the coordinate system used to define the CubeSat dimensions. Although the official specification only contains information about single and triple CubeSats, the dimensions for a double CubeSat can easily be derived: A double CubeSat shall be  $227.0\pm0.2$  mm tall, and shall not exceed 2.66 kg mass.

In addition, the mechanical specification also defines the use of separation springs for separating the different CubeSats after they have been deployed by the P-POD.

#### 2.1.2 Electrical Requirements

The CubeSat Design Specification also contains requirements to the electrical system, mainly to prevent interfering with the launch vehicle, the primary payload or other CubeSats. No electronics shall be active during launch to prevent any electrical or RF interference. A deployment switch, which is depressed when the satellite is in the P-POD, is used to turn off satellite power during launch. According to the specification, all systems has to be turned off, including real time clocks. As the satellite is deployed, the deployment switches are released, and the satellite can be powered up.

In addition to the deployment switches, the CubeSat must also implement a Remove Before Flight (RBF) pin. This pin disconnects all power, and is removed after the CubeSat is integrated into the P-POD. The CubeSat Design Specification document includes designated areas for the RBF pin and for umbilical connectors, which can be used for diagnostics and battery charging after the CubeSat has been integrated into the P-POD.

After being ejected from the P-POD, the satellite must wait at least 30 min before it can begin transmitting with RF transmitters greater than 1 mW. Deployment of antennas or other structures also have to wait a minimum of 30 minutes after leaving the P-POD. Another requirement present in [6] is that CubeSats with batteries shall have the capability to receive a transmitter shutdown command.

## 2.2 Satellite Power Systems

The electrical power system of any satellite mission is considered one of the most critical components. Without electrical power, a satellite in orbit becomes nothing more than space debris. Almost all spacecraft orbiting the earth today use solar cells as the primary energy source, backed up with batteries to sustain power during eclipse.

Some alternatives to solar power exist for special cases, such as hydrogen fuel cells used on board the space shuttles, or radioisotope thermoelectric generators (RTG) used on board the Cassini and Gallileo missions. These are however considerably more expensive, and are only used when solar cells become impractical, for example if the spacecraft is too far away from the sun.

In the design of satellites, the size of solar panels and batteries often become the driving factor in dimensioning the satellite size and weight. The required size of solar panels and batteries is dependent on the requirements of the payload, and the lifetime of the satellite mission. Both solar cells and batteries lose efficiency over time, so it is important to dimension them so that the end of life (EOL) capacity is sufficient to sustain the payload and satellite systems. For long missions, this generally leads to significantly larger solar panels and batteries compared to the requirements at the beginning of life. [4]

For a satellite in LEO the light from the sun will frequently be blocked by the earth as the satellite travels behind it. This is called eclipse, and causes the

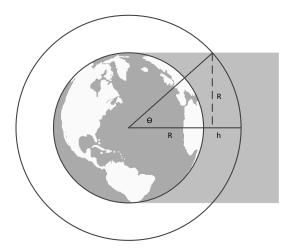

Figure 2.2: Eclipse

satellite to rely completely on battery power for a portion of every orbit. Knowing the maximum eclipse duration is important in dimensioning the power budget and the on board battery.

As an example, consider a satellite in LEO, at a height of 600 km above the earth surface. To gain a rough estimate for the maximum time spent in eclipse, it is sufficient to approximate both the earth and the orbit as spherical. The time for one orbital period is given by Kepler's Third Law as:

$$\tau^2 = \frac{4\pi^2}{\mu} a^3 \Leftrightarrow \tau = 2\pi a \sqrt{a/\mu} \tag{2.1}$$

with the semimajor axis a given in km and

$$\mu = GM = 398\ 601\ \mathrm{km}^3/\mathrm{s}^2 \tag{2.2}$$

(the universal constant of gravitation  $G = 6.6742 \times 10^{-11} \text{ m}^3/\text{kg}^2/\text{s}^2$  and the earth's mass  $M = 5.9736 \times 10^{24} \text{ kg.}$ ) With an orbital height of 600 km, a = (R+600) km = 6971 km, the orbital period becomes  $\tau = 5792 \text{ s} = 96.5 \text{ min}$ .

To determine the longest possible time in eclipse, consider figure 2.2. The time spent in eclipse can be calculated as

$$t_{ecl} = \frac{2\theta}{2\pi} \cdot \tau \tag{2.3}$$

with:

$$\theta = \sin^{-1}\left(\frac{R}{R+h}\right) = \sin^{-1}\left(\frac{R}{a}\right) \tag{2.4}$$

Inserting 2.1 into 2.3 gives:

$$(t_{ecl})_{max} = 2a\sqrt{\frac{a}{\mu}}\sin^{-1}\left(\frac{R}{a}\right)$$

(2.5)

With a height of 600 km this gives  $(t_{ecl})_{max} = 2125 \text{ s} = 35.4 \text{ min.}$

#### 2.2.1 Power Supply

The most common source of power for satellites is photovoltiac solar cells, which consists of a doped semiconductor p-n junction, and is protected by a UV filter and a layer of cover glass. The cell releases electrons when irradiated with sunlight. Today's most efficient cells uses gallium arsenide (GaAs), with the highest efficiencies achieved by using multiple layers to utilize energy from different parts of the sun's spectrum. Each cell provides a limited voltage and current, so cells are stringed together and strings are placed in parallel to obtain the desired voltage and current ratings.

The amount of power available depends on the solar power flux and the efficiency of the solar cells. The solar power flux in the earth's vicinity varies between  $S_{max} = 1399 \text{ W/m}^2$  in early January and  $S_{min} = 1309 \text{ W/m}^2$  in mid-summer. An annual mean of  $S = 1353 \text{ W/m}^2$  is often assumed for design purposes. [4] The angle of the sun to the panel defines the area of irradiance, and scales the amount of power available. Many larger satellites have deployable solar panels, which are folded up when the satellite is inside the launch vehicle. The solar panels can often be oriented towards the sun using actuators, to maximize the irradiated panel area.

The solar cell efficiency depends on the cell construction, temperature and age. The efficiency of a modern GaAs solar cell is only about 30%. The cell efficiency drops as they heat up, giving the most power when the satellite emerges from eclipse and the panels are still cold. The performance of a solar cell also degrades over time due to damage caused by the influx of high-energy protons and electrons in the Van Allen belts, and due to ultraviolet radiation from the sun. [4]

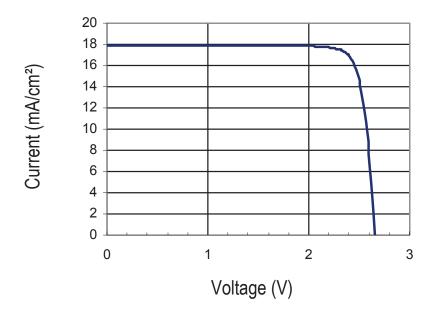

The IV charactaristic of a commercially available solar cell is shown in figure 2.3. These cells have have a short circuit current  $J_{SC} = 17.76 \text{ mA/cm}^2$ , and an open circuit voltage  $V_{OC} = 2.633 \text{ V}$ . Since power  $P = I \cdot V$ , the power at open circuit and at short circuit are both zero. The cell is exploited most efficiently if the working point is chosen at the "knee" where the output power reaches a maximum. In order for the cells to be used efficiently, a voltage bias is required to keep the operating point close to the maximum power point (MPP). According to the datasheet, the voltage at the MPP is about  $V_{mpp} = 2.348 \text{ V}$  and the current  $J_{mpp} = 17.02 \text{ mA/cm}^2$ . [20]

Figure 2.3: Spectrolab 29.5% XTJ Solar Cell Typical I-V characteristic [20]

| Orientation                                             | Available Power  |  |

|---------------------------------------------------------|------------------|--|

| One side panel only                                     | $4.80\mathrm{W}$ |  |

| Top panel only (minimum)                                | $2.40\mathrm{W}$ |  |

| Two side panels                                         | $6.79\mathrm{W}$ |  |

| One side panel & top panel $(25^{\circ} \text{ angle})$ | $5.36\mathrm{W}$ |  |

| Two side panels & top panel (maximum)                   | $7.20\mathrm{W}$ |  |

Table 2.1: Produced power at different orientations to the sun

#### 2.2.2 NUTS Solar Cells