# Hardware Implementation of a Time Management Unit (TMU)

Stian Juul Søvik

Master of Science in Engineering Cybernetics Submission date: December 2010 Supervisor: Amund Skavhaug, ITK

Norwegian University of Science and Technology Department of Engineering Cybernetics

# **Problem Description**

The purpose of this master thesis is to develop a hardware mechanism for execution time control hereby named a Time Management Unit (TMU). The TMU is to have high resolution execution time measurement, running at the same frequency as the CPU clock. The TMU shall allow execution time clocks to be swapped with low overhead. The TMU is to be implemented as a slave module connected to the APB of the Atmel AVR32 UC3.

A functional specification for the TMU is given in the paper "Functional specification for a Time Management Unit" by Gregertsen and Skavhaug. Proposing improvements to this specification and implementing a subset of these, is also a part of this thesis. A software framework consisting of device drivers will be provided. Finally, various functional and performance tests will be created and performed. The resulting product of the master thesis is intended to be used for further research within dependable real-time systems at NTNU.

To achieve these goals, the student is to:

Familiarize himself with earlier work and relevant theory Implement a TMU as specified Suggest and preferably implement improvements to the original specification Evaluate the final product with regards to correct functional operation and performance Develop necessary drivers and example software Create documentation for the final product

Assignment given: 23. August 2010 Supervisor: Amund Skavhaug, ITK

## Preface

This master thesis is the final part of my master's degree at the department of Engineering Cybernetics, Norwegian University of Science and Technology (NTNU). A large portion of the work was practical, as a digital hardware module was implemented. This work has been performed at Atmel Norway AS.

I am very grateful for the support from my supervisors, hereby Associate Professor Amund Skavhaug who has given advice both about the project as a whole and about the report; PhD Student Kristoffer N. Gregertsen who participated in valuable discussions regarding the specification and implementation of the Time Management Unit; and Dr. Chong-Fatt Law who has been very helpful in answering technical questions about Verilog, giving advice about best practices for digital hardware design, and reviewing the module's code to ensure it meets Atmel's quality standards.

I also appreciate the support from Atmel Corporation, as I have been allowed to use their proprietary source code of the AVR32 UC3 microcontroller to simulate my module, and they have provided tools and resources necessary to complete the project. Also, several of their skilled and kind employees have provided help with setup of tools and given advice.

Finally, I would like to thank my parents, who have spent some of their Christmas vacation proofreading my report.

At the time of completion, a paper based on this thesis is being prepared for submission to the 14<sup>th</sup> Euromicro Conference On Digital System Design (DSD), alternatively the 23<sup>rd</sup> Euromicro Conference on Real-Time Systems (ECRTS) if time does not permit preparation before DSD's deadline. (http://www.euromicro.org/Events.php).

Trondheim, December 23, 2010

Stian Juul Søvik

#### Summary

This thesis describes the implementation of a Time Management Unit (TMU) in hardware as specified by Gregertsen and Skavhaug (1), the specification and implementation of several improvements to the proposed specification, and the creation of a software framework to enable use of the module in a convenient way. A set of thorough automatic functional tests are also described and provided. The performance of the module is assessed and discussed. A user description similar to the AVR32 UC3 datasheets is also created.

The TMU has been implemented as a hardware module on the peripheral bus (APB) on the AVR32 UC3 microcontroller, which makes it easy to develop and test stand-alone, and simple to integrate into future UC3 microcontrollers. Also, as the APB interface of the AMBA standard is an open standard used by several System-on-a-chip (SoC) designs (2), the module can be implemented on other microcontrollers with very low effort.

The final product makes it possible to measure and control the execution time of tasks with high precision and low overhead. It supports atomic swapping of registers in a manner closely related to a context switch.

Gregertsen and Skavhaugs's research in implementing support for the Ada language and runtime environment on the UC3 microcontroller will benefit directly from this project, as the system relies on the hardware support provided by the TMU. Also, as the project can be used in proving that hardware support of execution time monitoring may allow for new ways of ensuring schedulability in real-time systems, it can possibly be a part of a new direction in realtime research.

## Contents

| 1   | INTRODUCTION1                                     |

|-----|---------------------------------------------------|

| 1.1 | Problem Description and Motivation1               |

| 1.2 | Previous Work1                                    |

| 1.3 | Main Contributions from This Project2             |

| 1.4 | Scope of This Project2                            |

| 1.5 | Outline3                                          |

| 2   | THEORY AND BACKGROUND5                            |

| 2.1 | Real-Time Systems5                                |

| 2.2 | AVR32 Architecture7                               |

| 2.3 | Digital Hardware Design13                         |

| 2.4 | Verilog for C Programmers17                       |

| 3   | ORIGINALLY PROPOSED SPECIFICATION OF THE TMU      |

| 3.1 | Introduction23                                    |

| 3.2 | Specification and High-level Design23             |

| 3.3 | Implementation of the TMU26                       |

| 4   | IMPROVEMENTS TO THE ORIGINAL SPECIFICATION        |

| 4.1 | Introduction                                      |

| 4.2 | Overflow Interrupt                                |

| 4.3 | Changes to Compare Match Interrupt                |

| 4.4 | Enable Flag and Halting of the TMU36              |

| 4.5 | Status Register and Status Clear Register         |

| 4.6 | Interrupts and Configuration Registers            |

| 4.7 | Clearing and Moving of Previous Interrupt Flags40 |

| 4.8 | Automatic Increase of Value Written to COUNT41    |

| 4.9 | Clock Source                                      |

| 4.10 | ) No Reading Back of COMPARE During Context Switch  |    |

|------|-----------------------------------------------------|----|

| 4.11 | l Memory Ordering                                   |    |

| 4.12 | 2 Remove Buffering for Reading the COMPARE Register | 45 |

| 4.13 | 3 32-bit Mode                                       |    |

| 4.14 | 4 Relative COMPARE Value                            |    |

| 5    | DESCRIPTION AND USER GUIDE OF THE FINAL TMU         | 47 |

| 5.1  | Features                                            |    |

| 5.2  | Overview                                            |    |

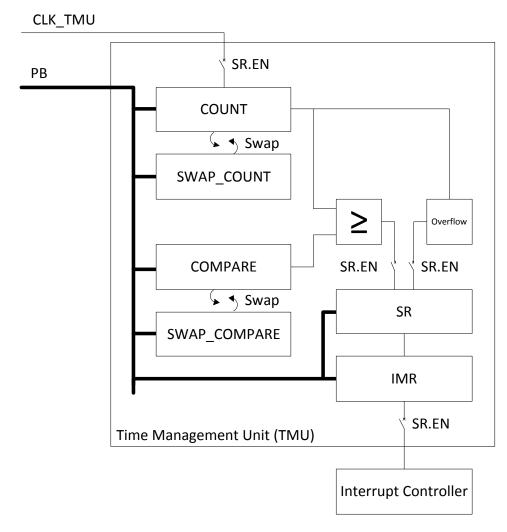

| 5.3  | Block Diagram                                       |    |

| 5.4  | Product Dependencies                                |    |

| 5.5  | Functional Description                              |    |

| 5.6  | Example of Swap Operation                           | 53 |

| 5.7  | User Interface                                      |    |

| 6    | SOFTWARE DRIVERS AND FRAMEWORK                      | 57 |

| 6.1  | Introduction                                        |    |

| 6.2  | Low-level Part of C Driver                          |    |

| 6.3  | High-level Part of C Driver                         |    |

| 7    | TESTING AND EVALUATION                              | 61 |

| 7.1  | Introduction                                        | 61 |

| 7.2  | Functional Testing of Stand-alone Module            | 61 |

| 7.3  | Functional Testing of Module Integrated with UC3    | 68 |

| 7.4  | Performance Measurement                             | 71 |

| 7.5  | Size and Cost                                       | 72 |

| 8    | DISCUSSION                                          | 73 |

| 8.1  | Approach                                            | 73 |

| 8.2  | Choices Taken                                       | 74 |

| 8.3  | Differences to Other Implementations     | 75 |

|------|------------------------------------------|----|

| 8.4  | Instant of Task Swapping                 | 78 |

| 8.5  | Performance, Cost and Flexibility        | 79 |

| 8.6  | Impact of Other Research and Development | 79 |

| 8.7  | Limitations                              | 79 |

| 8.8  | Application Range                        | 80 |

| 9    | CONCLUSION AND FURTHER WORK              | 81 |

| REFI | ERENCES                                  | 82 |

| APP  | ENDICES                                  | 84 |

| A-1  | TMU USER INTERFACE                       | 84 |

| A-2  | FILE ARCHIVE                             | 92 |

# **List of Figures**

The source of each figure is referenced to in the figure text. Figures without references are created by the author of this thesis.

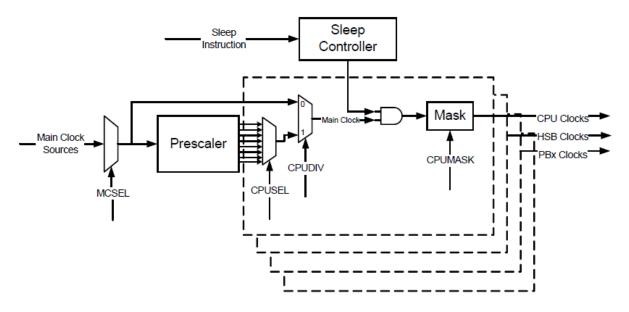

| Figure 1 – UC3 clock distribution (17)              | 8  |

|-----------------------------------------------------|----|

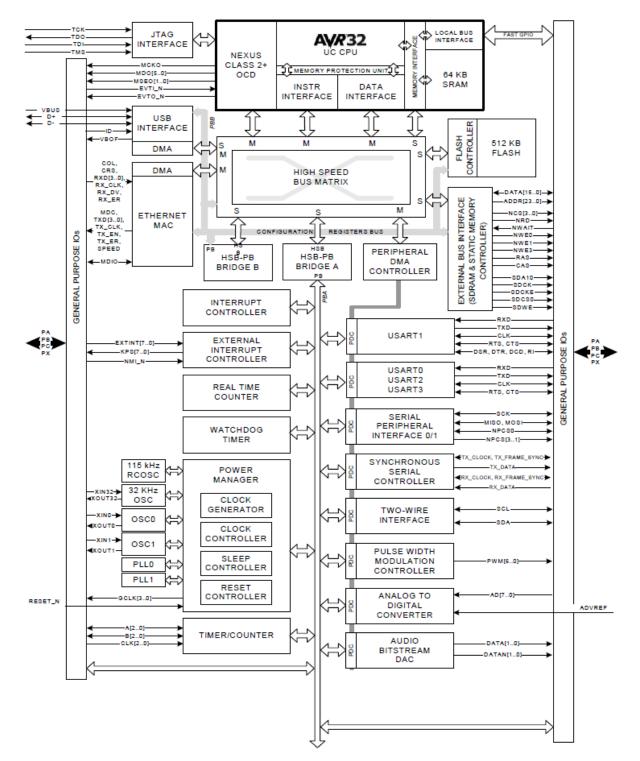

| Figure 2 – AT32UC3A block diagram (15)              | 9  |

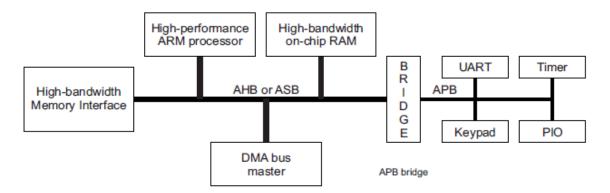

| Figure 3 – AMBA buses (9)                           |    |

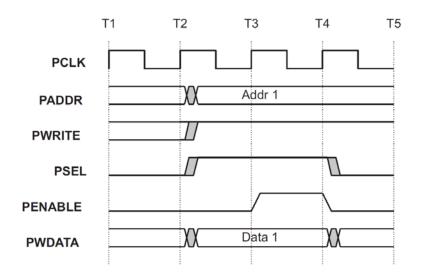

| Figure 4 – APB write transfer (9)                   |    |

| Figure 5 – APB read transfer (9)                    |    |

| Figure 6 – APB slave module (9)                     | 12 |

| Figure 7 – development process used in this project | 14 |

| Figure 8 – connection between UC3 core and TMU (1)  | 23 |

| Figure 9 – TMU Block Diagram                        |    |

| Figure 10 – illustration of ideal swap example      | 54 |

| Figure 11 – simulation of swap operation            | 71 |

# List of Code Examples

| Code 1 – blocking assignment example                                      |    |

|---------------------------------------------------------------------------|----|

| Code 2 – non-blocking assignment example                                  | 19 |

| Code 3 – clocked logic example                                            |    |

| Code 4 – module example                                                   | 21 |

| Code 5 – register definitions                                             |    |

| Code 6 – buffering registers on writes                                    |    |

| Code 7 – buffering registers on reads                                     |    |

| Code 8 – putting data on bus                                              |    |

| Code 9 – putting buffered data on the bus                                 | 27 |

| Code 10 – incrementing counter                                            |    |

| Code 11 – atomic swapping of registers and increasing of count value      |    |

| Code 12 – interrupt signal generation                                     |    |

| Code 13 – clocked storing to buffer                                       |    |

| Code 14 – combinational reading of registers                              |    |

| Code 15 – APB write transfers                                             |    |

| Code 16 – setting overflow flag                                           |    |

| Code 17 – setting compare match flag                                      |    |

| Code 18 – manipulating the enable flag by writing to the control register |    |

| Code 19 – clearing status register                                        |    |

| Code 20 – combinational logic related to interrupt signal                 |    |

| Code 21 – clearing and moving interrupt flags                             |    |

| Code 22 – automatic increase of COUNT                                     |    |

| Code 23 – syntax and operation of st.d and ld.d                           |    |

| Code 24 – order of access when using st.d and ld.d (3rd addressing mode)  |    |

| Code 25 – assembly example of performing swap operation                   |    |

| Code 26 – C example of reading count value and writing compare value      |    |

| Code 27 – testbench interface                                             | 61 |

# List of Tables

| Table 1 – explanation of context switch                                           | 25 |

|-----------------------------------------------------------------------------------|----|

| Table 2 – available features when the TMU is enabled or disabled                  | 50 |

| Table 3 – TMU Register Memory Map                                                 | 55 |

| Table 4 – C user interface layers                                                 | 57 |

| Table 5 – low-level C driver interface                                            | 58 |

| Table 6 – high-level C driver interface                                           | 59 |

| Table 7 – stand-alone test summary                                                | 63 |

| Table 8 – test combinations                                                       | 67 |

| Table 9 – integrated UC3 and TMU test summary                                     | 68 |

| Table 10 – number of cycles for reading and writing registers on the UC3 with TMU | 72 |

| Table 11 – feature comparison of the various implementations                      | 77 |

## Nomenclature

## Abbreviations

| ADDIEVIAL | 10115                                                             |

|-----------|-------------------------------------------------------------------|

| AHB       | Advanced High-performance Bus                                     |

| AMBA      | Advanced Microcontroller Bus Architecture (ARM)                   |

| APB       | Advanced Peripheral Bus                                           |

| ARM       | Advanced RISC Machines Ltd                                        |

| ASB       | Advanced System Bus                                               |

| AVR       | Atmel's microcontroller architecture and product line             |

| CLK       | Clock                                                             |

| СМР       | Compare Match                                                     |

| CPU       | Central Processing Unit                                           |

| DUT       | Device Under Test                                                 |

| DVE       | Discovery Visualization Environment                               |

| EDF       | Earliest Deadline First                                           |

| FPGA      | Field-Programmable Gate Array                                     |

| FPS       | Fixed Priority Scheduling                                         |

| HDL       | Hardware Description Language                                     |

| HI        | High                                                              |

| HSB       | High Speed Bus, Atmel's name for AHB                              |

| IDR       | Interrupt Disable Register                                        |

| IER       | Interrupt Enable Register                                         |

| IMR       | Interrupt Mask Register                                           |

| INT       | Interrupt                                                         |

| LO        | Low                                                               |

| negedge   | Negative edge                                                     |

| OVF       | Overflow                                                          |

| PB        | Peripheral Bus, Atmel's name for APB                              |

| РС        | Personal Computer                                                 |

| posedge   | Positive edge                                                     |

| PREVCMP   | Previous Compare Match                                            |

| PREVOVF   | Previous Overflow                                                 |

| RISC      | Reduced complexity Instruction Set Computer (as defined by Atmel) |

| RM        | Rate Monotonic                                                    |

| RST       | Reset                                                             |

| RTL       | Register Transfer Level                                           |

| SCR       | Status Clear Register                                             |

| SR        | Status Register                                                   |

| TMU       | Time Management Unit                                              |

| UC3       | Atmel microcontroller series                                      |

| VCS       | Synopsys Verilog Compiler                                         |

| VHDL      | VHSICHDL                                                          |

| VHSIC     | Very High Speed Integrated Circuits                               |

| WCET      | Worst-Case Execution Time                                         |

| XML       | Extensible Markup Language                                        |

|           |                                                                   |

### Formatting

Code examples are either given inline, such as "result = doComputation();", or in separate blocks, as shown below. Comments to the reader that are not a part of the original code are written in italics, and where implementation details have been removed, a short description of what is done is given in parenthesis where relevant.

```

for (i = 0; i < ITERATIONS; i++)

(Compute new result)</pre>

```

Signal, register or variable names are written in bold, such as "**COUNT**". Uppercase variable names used in underlying articles or reports have been retained, although the same case is not necessarily used in the code implementing this project. When a register or variable is referenced to by its general usage, no special formatting is applied, such as "the counter".

Larger quotes are indented and italicized.

Chapters without a separate introduction section give a shorter introduction to the reader which describes the intention of the chapter, or other notes to make the text easier to read and understand. These notes are italicized.

Empty pages are inserted so that each chapter starts on a left page, to make it easier to keep illustrations and their references visible at the same time when reading the printed booklet.

#### **Code Shortening**

Most code example blocks have been shortened in several ways. Many identifiers require several prefixes due to code standards, such as apb\_tmu\_pwrite, but in the code examples only pwrite is displayed. Some comments from the original code are removed, and explained in the text instead. Also, the implementation uses wires called apb\_write and apb\_read, which hides the implementation of APB control signal logic. This makes the code simpler to read.

All blocks writing to registers are synchronous with the clock, which is not necessarily displayed in the code. Other context of many statements is also removed where it is not directly relevant to the example. For instance, if an action happens when a register is written using a bus, only the action itself might be displayed, and the control flow constructs checking that the correct address and control signals are set might be omitted. In these cases, the conditions for the statement to be executed are implied from the text.

#### Language

Chapter 5 gives a description of the final module in a format that is intended to be similar to a chapter describing a module in the AVR32 UC3 datasheets, that is, it follows the Atmel Document Standards (3). This implies that the text is written in a more standardized and repetitive manner than what would otherwise be expected in a report.

The rest of the report only follows these standards where it is beneficial for consistence without decreasing readability. When there is a conflict between these goals, readability is intended to be given most weight.

In cases where threads, processes, tasks, or other entities that can be executed are referred to without the need of being more specific, "tasks" have been used.

# 1 Introduction

## 1.1 Problem Description and Motivation

The correctness of a real-time system depends not only on the logical result of the computation, but also on the time at which the results are produced.

#### Quote 1 – Definition of a real-time system (4)

Tasks running on hard real-time systems are regarded as incorrect if they do not complete before their deadline, and on hard real-time systems, failure can have catastrophic results (4). Tasks need to be scheduled to ensure that they will be able to complete in correct time, hence the timing capabilities of a real-time system is essential.

In real-time systems, the worst-case execution time (WCET) of a process is a widely used measure in the process of ensuring that a system will be schedulable. However, due to modern processors' performance enhancing techniques such as pipelining, caching and branch prediction, finding WCET may be very hard (4; 5), and it will often be much greater than the average execution time (6). This leads to the dilemma between choosing to have poor CPU utilization to decrease probability of deadline misses, or use optimistic budgets and risk deadlines being missed. (1)

An alternative approach is to base the scheduling on giving each task a budget of at least its average or excepted execution time. Overruns of these budgets can be handled dynamically with an alternative task with a constant or limited short execution time. The alternative task can for instance return a result based on a simpler algorithm, or perform necessary handling of the error to prevent the system from failing. Because of the alternative task's simplicity, its WCET can be computed.

This will let the programmer allow higher utilization of the processor and still ensure schedulability (1; 6). On the other hand, this approach depends on the availability of a precise mechanism for execution time monitoring. To handle overruns, a mechanism for interrupting the processor when the execution time budget is depleted is necessary.

# 1.2 Previous Work

Bjørn Forsman has previously implemented a Time Management Unit (7) based on a specification given by Håvard Skinnemoen and Amund Skavhaug (8) to improve predictability of real-time systems. It will limit the execution times of tasks as well as the occurrences of interrupts as perceived by the CPU. The module is implemented as a peripheral device on the APB bus (9) of the LEON3 processor. It requires modifying the CPU's internal workings, that is, it interferes with the interrupt lines to stop the signals from propagating when the interrupt line in question has reached its limit of interrupts per time. It contains a dedicated timer for each interrupt line.

A simpler approach is to use a hardware unit with only the capabilities of counting CPU cycles and generating an interrupt when this count reaches a given number. This allows for more flexible scheduling policies as they are implemented in software, as well as improved portability because of the unit's simplicity. Gregertsen and Skavhaug took this approach when *implementing*  *the new Ada 2005 timing event and execution time control features on the AVR32 architecture* (10). Here, the built-in **COUNT** and **COMPARE** registers of the AVR32 UC3 processor were used (11). *A real-time framework for Ada 2005 and the Ravenscar profile* has also been created (12), which is based on the work in (10).

The hardware implementation used in their works has some drawbacks, that is, relative time has to be used as the counter is only 32-bit which results in computational overhead, and special care is needed to prevent the counter from overflowing. Also, atomic swapping of the **COUNT** and **COMPARE** registers was desired. Hence, there is a need for a dedicated timer unit to support this work (1).

The TMU implemented in this project will be compared to these implementations in section 8.3.

# **1.3** Main Contributions from This Project

This master's thesis supports the work of Gregertsen and Skavhaug by implementing the proposed Time Management Unit (TMU) in hardware as specified in (1). This work also contributes to the research by making improvements to the specification of the TMU and implementing a subset of these in the hardware unit.

Successful completion of this project has led to a module that extends the AVR32 UC3 microcontroller. Also, a testbench and tests both for the TMU as a stand-alone module, written in Verilog; and for the TMU integrated with UC3, written in C; were developed as a part of this project. In addition to proving the correctness of the implemented module, the tests can facilitate further work with the project. Furthermore, an introduction to Verilog for programmers familiar with C was created, which will benefit students extending the implementation.

To make the module as ready as possible for integrating into a commercial UC3 model, the relevant parts of a datasheet were also created. A software framework consisting of drivers and example code is also provided.

# 1.4 Scope of This Project

Exploring or choosing target processor is not relevant to this thesis, as the AVR32 UC3 is already chosen in the work this project is based on (1; 10; 12). Several soft-core processors are explored in (7); hereby LEON, OpenRISC and AEMB. Also, as Atmel Corporation requires Verilog to be the hardware description language used for their modules, no research and choice of language is performed.

To implement a digital unit in hardware as is required in this project, knowledge of digital hardware design is mandatory. This includes learning the discipline of designing hardware, as well as learning a hardware description language. Furthermore, one needs to be familiar with real-time related principles such as scheduling theory, timing concepts and real-time requirements. Good knowledge to microcontrollers in general, the microcontroller to host the module in particular, and the buses needed to interface the module, is also important.

The use of various tools such as hardware simulators, waveform viewers, compilers, verification frameworks and proprietary scripts is also a part of the required work, although this will not be a main focus in this report.

To gain the necessary understanding of the application for the module, literature about real-time systems and related concepts, as well as the articles relevant to Gregertsen and Skavhaug's research and earlier related work, need to be read and understood.

The proposed specification is very simple, and suggesting additional improvements, making choices where details are missing, correcting any errors detected, and implementing some of the improvements, are natural parts of this project as well.

To ensure the correct function of the module, tests need to be created and executed, and possible errors must be corrected. Furthermore, tests for assessing performance are desired. Creating software drivers that make the module easy to use is also a part of the project.

## 1.5 Outline

After this first introductory chapter, the second chapter presents background theory necessary to understand the rest of the report. Both real-time concepts, the AVR32 architecture and digital hardware design will be touched. The third chapter describes the TMU as it was originally proposed, and how this version was implemented. Then, the fourth chapter proposes and discusses several improvements, and gives details about implementation where it is relevant.

Chapter five is a description of the final product, and can also be used as a user guide which resembles the description of a module in an AVR32 UC3 datasheet. Chapter six presents the software framework developed for the hardware module. The seventh chapter treats functional and performance tests of the final product, and the eighth chapter discusses the module as a whole. Finally, the ninth chapter concludes the report and project.

Each chapter contains either an introductory section, or a shorter explanation of the chapter's purpose and other useful information to the reader.

Because this report covers several details that need to be discussed, the discussions are often written at the same place as the detail is presented. The final discussion chapter covers the TMU at a higher level.

# 2 Theory and Background

As the reader is expected to be familiar with common real-time concepts, this chapter presents a brief introduction of the subject with references to relevant literature. Then, the AVR32 architecture with a main focus on the UC3 family is introduced. Some concepts of special interest to this thesis are emphasized. Then, some background information of digital hardware design is given. The chapter is concluded with an introduction of Verilog to C programmers.

# 2.1 Real-Time Systems

As mentioned in the introduction, the correctness of real-time systems is determined both by their functional correctness, as well as the time the results are delivered. For instance, the result of a computation must be available early enough to output a new set point in a control system. Real-time computing does not necessarily imply high performance; qualities such as predictability and safety better describe its most important properties.

Real-time systems are divided into three categories; soft, firm and hard, which are defined in (4). Soft real-time systems have deadlines but can tolerate some being missed, possibly leading to degraded quality. For instance, a video communication system relies on data being delivered with low latency for the video to appear without any significant delay, but can allow some frames to be received late or not at all and still perform satisfactory. Firm real-time systems are similar, but have no use of the data being delivered too late.

In hard real-time systems, it is absolutely crucial that the system responds within the deadline. For instance, the airbags in a car need to be released within milliseconds. Missing deadlines in hard real-time systems might cause large negative consequences; for instance financial loss or even risk human lives.

# 2.1.1 Scheduling

# Scheduling for multitasking in general purpose operating systems

In regular computers, such as PCs or servers, fast response time as perceived by the user and fair allocation of system resources are common objectives for the scheduler. By rapidly switching between tasks, they seem to run concurrently, thus enabling multi-tasking.

Linux achieves this by dynamically allocating priorities to tasks according to how much they have been using the CPU earlier. If a task with a higher priority than the currently running task becomes ready to run, the current task is interrupted and the high priority task might be allowed to execute (13). In this way, historical data is used to schedule tasks.

This approach is not satisfactory for real-time systems, however. Because the Linux kernel as described in (13) is non-preemptive, real-time processes might be blocked for several milliseconds while the system is in Kernel Mode.

# Real-time scheduling

Scheduling schemes for real-time systems can be divided in two categories; static and dynamic. Both might use priorities to determine which task is allowed to run next, and the main goal is to ensure that all tasks will complete within their deadlines if possible. Static scheduling algorithms do calculations before execution, while dynamic algorithms do the computations at run-time. Several scheduling algorithms are described in (4), including the dynamic earliest deadline first (EDF) algorithm, and the static fixed-priority scheduling (FPS) with rate monotonic (RM) priority assignment.

A disadvantage of EDF is that if the system gets overloaded, the set of tasks that are allowed to run is unpredictable, and not necessarily the most important tasks. As explained in (14), this is a considerable disadvantage to real-time systems. Also, the algorithm is difficult to implement in hardware, and have issues about representing deadlines in different ranges. Because of these disadvantages, this algorithm is not commonly found in industrial real-time systems.

FPS with RM is more common in real-time systems. As the priorities are fixed, one can guarantee which tasks will miss their deadlines if the system is overloaded. A disadvantage with both this approach and EDF is that the worst case execution time (WCET) is expected to be known (4). This can be hard or intractable to compute; and even if the execution time is measured, it is difficult to know when the worst case has been observed. Also, although the real issue is to ensure that tasks complete within their deadlines, FPS' mapping of deadlines to priorities can be regarded as an indirect means to solve the problem.

#### Primary and alternative tasks

An interesting alternative to the scheduling schemes mentioned above is presented in (6). Here, instead of having to prepare for the worst case by allocating enough time for all processes to run even if they reach their WCETs, two versions of each task is used, called primary and alternative. These must be specified so that completing either the primary or alternative can be regarded as successful completion of the task.

The primary task will provide the best service, for instance by returning a set point value calculated with high accuracy and precision in control systems, or simply by completing the job the task was intended to do. The alternative task will, however, merely offer a service that is just acceptable. Examples include returning the previous value of the calculated set point, or perform cleanup of the primary task that did not finish.

The primary task is allowed to run for a pre-determined time, for instance close above its average or expected execution time. The alternative task should have a low WCET, which is easier to achieve because of its simplicity. For all tasks in a system to be schedulable, it suffices to guarantee that the sum of all primary tasks' allowed execution time plus the WCETs of all alternative task do not result in the system exceeding a utilization of 100%.

However, this approach depends on support for measuring execution time with high precision, and the ability to interrupt a task as soon as it has reached its execution time limit.

# 2.2 AVR32 Architecture

AVR32 is a new high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow for a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid- or high-performance processors. AVR32 extends the AVR family into the world of 32- and 64-bit applications.

## Quote 2 – AVR32UC Introduction (15)

The AVR32 series consists of several processors, which are divided in two product families according to CPU core: AP7 and UC3. The AVR32 AP7 family is optimized for embedded Linux applications, and is not relevant to this project.

AVR32 is a microprocessor architecture with focus on achieving high code density, which lowers memory requirements and contributes to the core's low power characteristics (11). Load and store operations for up to double words (64 bits) are provided. To accommodate for several applications, different micro architectures are defined. AVR32B is implemented in the AP7 family, while UC3 implements AVR32A.

AVR32B is suited for applications where interrupt latency is important, by for instance providing registers to hold the status register and return address for interrupts, exceptions and supervisor calls, and allowing hardware shadowing of registers. AVR32A is targeted at cost-sensitive lower-end applications like smaller microcontrollers, and does not provide these features.

## 2.2.1 UC3 Core

AVR32UC is the first implementation of the AVR32A architecture. There exist three revisions of this implementation, where UC3 is the most current one. All revisions are backward compatible.

AVR32 UC3 (may be referenced to as "UC3" from now on) is the microcontroller family of interest to this thesis, as previous related work is based on it. UC3 microcontrollers are optimized for highly integrated embedded applications requiring integrated flash memory (16). The UC3 family is focused on high CPU performance relative to power consumption. The UC3 core and the AMBA buses used for internal communication are of special interest for this project, and will be detailed in the following sections.

The UC3 microcontrollers use AMBA buses for internal communication between many of its modules. The devices on the buses are memory mapped, easily accessible for a user. The AVR32 framework includes C header files that provide structs the user can utilize to communicate with the different modules in a convenient manner that enables writing maintainable and portable code.

Models such as the most recent AT32UC3L run at clock frequencies up to 50 MHz (17). The Power Manager (PM) is responsible for generating clock and reset signals for digital logic, and distributes a possibly scaled down signal from a main clock source to the CPU, High Speed Bus, and Peripheral Buses (referenced to as APB in this report). This is illustrated in Figure 1. Clocks may be disabled individually.

Figure 1 – UC3 clock distribution (17)

#### Instruction set and issue latency

AVR32 is a RISC architecture, and (11) contains a description of all instructions. Note that Atmel's definition of RISC is "Reduced Complexity Instruction Set Computer" (18), in contrast to the more popular "Reduced Instruction Set Computer". Atmel's view is that it is not the number of instructions that is reduced, but the complexity of the digital circuitry required to decode the instructions. The AVR32 instruction set is fully orthogonal, which means that any instruction can use data of any type via any addressing mode (19). There are a rich number of instructions available, and many allow formats of operands such as post-increment or pre-decrement of pointer registers which reduces code size and speeds up execution.

The pipelined architecture allows one instruction per clock cycle (11), but some instructions, like those that change the program counter, will cause a pipeline flush and hereby require more clock cycles. Also, performance of memory accesses and instruction fetching are affected by the performance of system memories and system bus (20). That is, accesses to external modules might be delayed because of wait states, slow responding modules, restrictions given by the bus protocol, and occupied buses.

An instruction is *issued* when it leaves the instruction decode stage and enters the execute stage. The *issue latency* represents the number of clock cycles required between the issue of the instruction and the issue of the following instruction, that is, how many cycles the instruction "delays" the total system. These definitions and the issue latency of each instruction are given in the AVR32UC3 Technical Reference Manual (20). Factors that can be taken into consideration when computing number of clock cycles include issue latency, memory delay and occupied buses.

#### 2.2.2 AMBA Buses

For internal communication between modules, UC3 uses an ARM Advanced Microcontroller Bus Architecture (AMBA) compatible bus. This is not specified in public available manuals or datasheets as it is first and foremost of interest to those who develop the microcontrollers. The knowledge of the use of AMBA is given from Atmel internally, while the technical specification of the bus (9) is publicly available. AMBA was introduced by ARM Ltd in 1996, and three versions have been created since then (2). UC3 uses the second version.

Figure 2 - AT32UC3A block diagram (15)

The AMBA specification (9) describes three buses, namely Advanced High-performance Bus (AHB), Advanced System Bus (ASB) and Advanced Peripheral Bus (APB). This thesis will use the ABP to connect the TMU, and that particular bus will be given the most detailed explanation here.

Figure 2 illustrates the AVR32UC3A microcontroller including its CPU core, peripheral devices and their interconnections. Note that Atmel references to the AHB and APB as HSB and PB, respectively. Figure 3 illustrates how ARM perceives a typical system using the AMBA buses.

The AHB is intended for high-performance, high clock frequency system modules, and is used as the system backbone bus in UC3. The ASB is an alternative system bus, suitable for applications which do not require the high-performance features of the AHB. UC3 uses the APB for its peripherals.

#### Figure 3 - AMBA buses (9)

AHB implements features such as burst transfers, split transactions and wide bus configurations (64/128 bit), and is thus suited for high-performance, high clock frequency systems. The bus can be bridged together with the APB to allow connection of low-bandwidth peripherals. The APB bridge appears as an AHB slave module, and is responsible for handling the bus handshake and control signal retiming on behalf of the local peripheral bus. It provides latching of all address, data and control signals, and generates slave select signals for the APB peripherals by providing a second level of decoding.

The APB appears as a local secondary bus, and is intended to interface any low bandwidth peripherals that do not require a pipelined bus interface. The bus is optimized for minimal power consumption and reduced interface complexity.

In the following, **PSEL** will refer to the select signal of the APB slave in question, or a general slave where it is relevant. In reality, the APB bridge will assert at most one of several select signals based on the current value on the address bus.

The APB can be in one of three states; **IDLE**, **SETUP** or **ENABLE**. **IDLE** is the default state, and indicates that no transfer is ongoing. When a read or write transfer is initiated, the bus enters the **SETUP** state where a device connected to the APB is selected using the **PSEL** signal, and the **ENABLE** state is then entered in the beginning of the next clock cycle. During this last transition, the address, write, and select signals all remain valid and stable, and the **PENABLE** signal is asserted. The **ENABLE** state also lasts for only one clock cycle. If another transfer is pending, the bus will return to the **SETUP** state; otherwise, it will move to **IDLE** again.

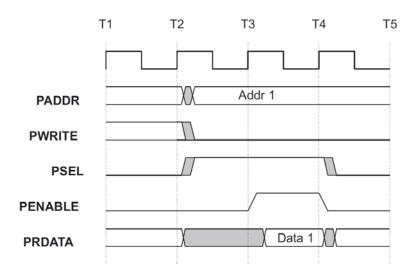

In a write transfer, the address, data, and control signals change after a positive clock edge. This occurs in the **SETUP** state, and is illustrated in the period starting with **T2** in Figure 4. The next clock period starting with **T3** corresponds with the **ENABLE** state, where the **PENABLE** signal is asserted, and the other signals remain valid. In the end of this period, the transfer completes. **PENABLE** will become low after this period, and if there is no transfer immediately after the current one, the **PSEL** signal will also go low. The address and write signal will remain the same to reduce power consumption.

Figure 4 – APB write transfer (9)

A read transfer is specified to have the same timing of the address, write, select and strobe signals as for the write transfer. However, during the **ENABLE** state, the slave will provide the data which is sampled on the rising clock edge at the end of that cycle. An illustration of the read transfer is given in Figure 5.

Figure 5 - APB read transfer (9)

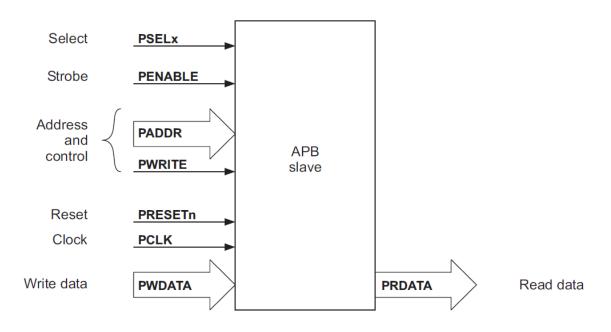

An APB slave module, as illustrated in Figure 6, must adhere to the interface given in (9). For a write transfer, data can either be latched on the rising edge of **PCLK** or **PENABLE**, when **PSEL** is high. For a read transfer, data should be driven when **PWRITE** is low and both **PSEL** and **PENABLE** are high. In both cases, the **PADDR** determines which slave device to be activated by

the APB bridge, and it can also decide which internal register or function to be activated in the slave.

Figure 6 - APB slave module (9)

# 2.3 Digital Hardware Design

This section first presents an overall workflow, which can apply to a general project. Then, a brief overview of the steps taken to create, simulate, and finally integrate the TMU on the UC3 with Atmel's tools is provided. Also, some of the most important tools used in this project are mentioned.

## 2.3.1 Workflow for Designing Digital Hardware

When designing digital electronics, following a well-planned workflow will help the designer in having an effective process, and ensure that documentation is created and testing/verification is performed properly.

An example of a workflow with examples of tools is given in the following quote:

- 1. Specification: Word processor like Word, Kwriter, AbiWord, Open Office.

- 2. High Level Design: Word processor like Word, Kwriter, AbiWord, for drawing waveform use tools like waveformer or testbencher or Word, Open Office.

- 3. Micro Design/Low level design: Word processor like Word, Kwriter, AbiWord, for drawing waveform use tools like waveformer or testbencher or Word.

- 4. RTL Coding: Vim, Emacs, conTEXT, HDL TurboWriter

- 5. Simulation: Modelsim, VCS, Verilog-XL, Veriwell, Finsim, Icarus.

- 6. Synthesis: Design Compiler, FPGA Compiler, Synplify, Leonardo Spectrum. You can download this from FPGA vendors like Altera and Xilinx for free.

- 7. Place & Route: For FPGA use FPGA' vendors P&R tool. ASIC tools require expensive P&R tools like Apollo. Students can use LASI, Magic.

- 8. Post Si Validation: For ASIC and FPGA, the chip needs to be tested in real environment. Board design, device drivers needs to be in place.

Quote 3 – design and tool flow (21)

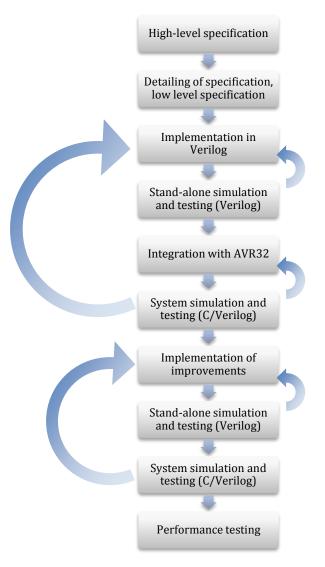

As the specification and high-level design was already given in (1), this project concentrated on low-level design, RTL coding and testing. The author of this thesis was unfamiliar with hardware development, hence it was not easy to estimate how much time was needed to set up a development environment, learn Verilog and implement features. Thus, it was decided that the module should be implemented according to the original specification at first, and then improvements and new features should preferably be introduced at a later stage according to available time.

Sample code for a tutorial module was used as a framework for syntax, tab spacing etc, and it also demonstrated communications with the APB and a testbench. Although this code was not directly usable for the TMU, it was utilized as a starting point when a new language had to be learned in short time.

Automatic tests have been used extensively in this project. There are several benefits of developing thorough test programs, as described in 7.1. Figure 7 illustrates the workflow used in this project.

Figure 7 – development process used in this project

## 2.3.2 Workflow with Atmel's Tools

Substantial configuration and setup is needed to create a hardware module and integrate it with an existing microcontroller, and possibly synthesize it to run on an FPGA. Unfortunately, most of the procedures and tools will differ between projects and hardware configurations. The tools and procedures used in this project are provided by Atmel Corporation, and the information about the procedures, scripts, tutorials and some tools is confidential and cannot be published in this report. Also, one would need assistance from several people to be given necessary access, so cooperation with Atmel is needed in order to continue the work of this project in any case.

However, a brief overview of the tools and procedures used in this project is provided here. Hopefully, this can be used as a starting point for students continuing to work on this project.

Atmel has an internal tutorial for creating a module connected to the APB on UC3. Although the guide does not go into any details, it provides some key information about where some of the necessary tools are located, and hints about where to look for more information. As the tutorial is far from complete, assistance from the experts at Atmel is needed to complete implementation of the module. Also, the tutorial does not provide anything related to describing the hardware using Verilog – only an overview of steps related to workflow.

## Setup of tools and environment

The following presents a more concrete list of required actions to perform the steps of the workflow given in 2.3.1 when using Atmel's tools and equipment.

- 1. User account needs to be set up with correct permissions, SVN access, and internal Atmel modules need to be activated.

- 2. Check out stand-alone tree

- 3. Write code for module

- 4. Compile the module

- 5. Create testbench and tests in Verilog

- 6. Run tests and verify that module works properly stand-alone

- 7. Check out a project containing complete module

- 8. Extend "modules file" to include your own module

- 9. Run avr 32-checkout to get necessary files

- 10. Use PartTool to create XML file for module

- 11. Run PartTool for complete microcontroller to configure it and include XML file for module

- 12. Run generate scripts to generate various header files, Verilog files and so on

- 13. Modify necessary files describing interconnections in device, instantiation of modules, clock signal distribution etc.

- 14. Simulate the complete microcontroller with integrated module

- 15. Create tests in C for testing module integrated with UC3

- 16. Run tests and verify that the module works properly as an integrated UC3 module

Some of the most used tools are described in the following. This is provided as a starting point for exploring the tools involved in the workflow. For a full description, consult the respective user manuals.

## Synopsys Verilog Compiler (VCS)

When the module itself has been implemented using Verilog, it is possible to compile it to an executable that will simulate the hardware by using VCS. In order to get output from the module, input data needs to be provided. A testbench is normally used to generate input data and verify output data. The output data can be displayed on the terminal, and all signals are stored in a database so that they can be displayed in a waveform displayer (described next). The same program can be used to simulate a complete microcontroller with the module integrated.

## Discovery Visualization Environment (DVE)

To study all internal signals and values, DVE provides a graphical user interface that can read the database output of the VCS compiler and display waveforms of signals of the user's choice. Various forms of debugging are available, such as tracing of signal drivers and loads.

# Spyglass

Spyglass can generate a graphical view of the physical units and interconnections that would be generated from the Verilog files, and also give useful warnings and hints of possible problems in the code. This tool is useful to inspect the result of the code, and for instance discover unnecessary latches resulting from mistakes.

# PartTool

PartTool is an internal Atmel tool which can generate and modify XML files containing metadata about modules and complete microcontrollers. For instance, all registers and bit fields of a module can be described using this tool, and various parameters can be set. The XML files output from this tool are then used to generate several support files for the complete microcontroller, see the next section for a more detailed description.

# "Generate" scripts

A microcontroller contains a vast amount of registers belonging to various modules and a lot of interconnections between them. To make the process maintainable, much of the Verilog code describing interrupt lines and memory maps are automatically generated from the XML files describing the module. Also, C header files including register definitions are automatically generated. These support tools reduces both development time and the occurrence of errors from manually maintaining such files.

# 2.4 Verilog for C Programmers

This section is not intended to be a full guide for learning Verilog, but rather an introduction for programmers familiar with C or similar languages, which will likely be the case for students continuing the work of this project. Some barriers and new concepts a C programmer is likely to meet are described here, as the main focus is on what the author of this thesis found challenging when learning to develop digital hardware. (21) provides a tutorial, and for a reference manual which describes the exact syntax and semantics of the language see (22).

Verilog is a hardware description language (HDL) used to model electronic circuits by describing their behavior. The language can be used in many of the development stages of an electronic system. An important part of the design process is implementing the system in Verilog code, which can later be simulated and tested in the verification stage. Test programs and a testbench can also be written in Verilog. By synthesizing the code, the system can eventually be implemented in e.g. an FPGA or ASIC.

A C programmer will find some of Verilog's syntax familiar. The language is case-sensitive, includes a basic preprocessor with e.g. `include and `define statements, equivalent control flow keywords (if/else, for, while, case etc.) and compatible operator precedence (23). As an example of the differences between the languages, blocks of code are demarked with begin ... end in Verilog instead of { ... } as in C.

To support encapsulation and modularization of a system, Verilog provides the possibility to organize the code into a hierarchy of modules. Modules communicate with other modules through ports, which can be declared as inputs, outputs or both, and constitute the module's interface. The internal behavior of a module is defined using internal net or register definitions and concurrent or sequential statements. A module can also instantiate other modules. Verilog supports tasks and functions which are analog to procedures and functions, respectively, in programming languages.

What is written in Verilog is often intended to eventually translate to a set of basic electronic circuits (flip-flops, latches, registers, gates etc) and their interconnections. Thus, one should keep in mind that the synthesizer will try to recognize patterns in the code that corresponds to the various components, and follow conventions and best practices when writing code.

As for the semantics, or the meaning of statements in the code, there are some important cases where HDLs differ from programming languages, which are described in the following sections.

## 2.4.1 Data Types and Storage Elements

Most data types in Verilog can store four different basic values (22):

- 0: logic zero, or a false condition

- 1: logic one, or a true condition

- x: unknown logic value

- z: high-impedance state

To store useful information or sets of logical values, it is possible to declare registers which store a given number of such values, or arrays of the different data types. A net or variable declaration (see next paragraph) is 1 bit wide per default, but can be extended by specifying a range, which makes a vector. The vector definition consists of two constant expressions, representing the most and least significant bits.

Two main groups of data types exist: nets and variables. Nets represent physical connections between structural entities, and shall (in most cases) not store a value. The value of a net will be determined by its drivers, which could for instance be continuous assignments. The basic net type is called wire. Various other nets exist, providing the possibility of modeling wired logic.

Variables represent data storage elements, which will store their values between assignments. Variable types include reg (registers) and integer. As the name indicates, a reg can be used to model a hardware register, but can also represent combinational logic. An integer is a general-purpose variable used for manipulating quantities that are not regarded as hardware registers, but shall be assigned values in the same manner as reg (22).

#### 2.4.2 Assignments

There are two basic kinds of assignments in Verilog; continuous and procedural. Both have conceptual differences to assignments in programming languages that one should be aware of. In brief, continuous assignments drive nets and are evaluated and updated whenever an input operand changes value, while procedural assignments update the value of variables according to the control flow elements that surround them (22). Continuous assignments are used to model combinational logic, while procedural assignments also can model sequential logic.

Continuous assignments connect a net data type to an expression, in practice, an output of a combinational circuit. In C, an expression like x = 3 + y; would store the value of y at the time of evaluation increased by 3 into x, but the similar Verilog continuous assignment assign x = 3 + y, makes x always equal 3 + y, that is, x gets updated whenever y changes.

In contrast, a procedural assignment puts a value into a variable, which will store the value until a subsequent assignment to that variable occurs. This behavior is similar to what a C programmer would expect, with non-blocking assignments as an important exception, explained below. Procedural assignments occur within procedures such as always, initial, task or function, and will be evaluated or "triggered" when control flow reaches that statement (22).

A procedural assignment can either be blocking (=) or non-blocking (<=). In sequential code blocks, a blocking assignment will be executed before the following statement is executed, just as in C. In the following example, assume that a initially contains the value 2.

a = a + 1; b = a; a = a - 2;

#### Code 1 – blocking assignment example

When the code is executed, a will first increase to 3 and b will then copy the same value. Finally, a will decrease to 1. In the end, a contains 1 and b contains 3.

In contrast, a code block of non-blocking assignments are evaluated in two steps when simulating. The first step evaluates all the right-hand-sides and the last step stores the results to the left-hand-sides. This means that they can be considered as executed in parallel, and that the

right-hand-sides always use the "previous" value of the variables. This manner of operation resembles the operation of for instance actual flip-flops. The following example demonstrates how two values can swap without using a temporary variable, as one would have needed to accomplish the same in C.

a <= b; b <= a;

#### Code 2 – non-blocking assignment example

After this, a and b would have swapped values.

#### 2.4.3 Creating Clocked Logic with the Always Construct

One important control construct is the always construct. It executes a statement repeatedly, with a possible event that needs to occur before each execution. This construct is often used to create clocked, or synchronous, sequential logic. Assuming the existence of a clock signal, the event used to let the statement execute is the clock signal changing value. One can specify whether the transition is high to low (negedge) or low to high (posedge). It is also common to include reset logic, as illustrated in the example below.

```

always @(posedge clk or posedge reset) begin

if (reset)

count <= 0;

else begin

if (psel && penable && pwrite && (paddr[5:0] == COUNT))

count <= {buffer, wdata} + 1;

else

count <= count + 1;

end

end

```

Code 3 - clocked logic example

This example sets count to 0 if the reset signal is active (high). Otherwise, it checks various control signals and a part of an address bus to determine whether count is to be set from the concatenation of buffer and wdata plus 1, or simply increased by 1. This could correspond to a series of clocked flip-flops (register) with asynchronous reset and an input multiplexed between the output of an adder connected to the register output, and an adder connected to a data bus and a buffer.

#### 2.4.4 Timing

There are several ways to specify timing requirements in Verilog, although not all are synthesizable. When describing synchronous logic, a clock signal is often used to ensure that operations happen simultaneously, and to represent time. The simple statement always @(posedge clk) if (e)  $q \le d$ ; models a flip-flop with enable signal, which is

enabled with the e signal and lets q store the value d had in the previous clock cycle. Note that in clocked statements, the right hand side represents the state of the system *just before* the clock edge, while the left hand side determines where the result is to be stored *right after* the clock edge.

One can also wait for an event to happen just once, by using the @ operator. @(negedge clock) halts execution until the next negative clock edge, which can be useful when needing to introduce delays. It is also possible to wait for a statement to be true, using wait. wait(x == 2) halts execution until x equals 2.

Finally, it is possible to delay execution by a number of simulation time units by using # and the number of units, for instance  $\#1 \ge y$ ; will delay one time unit before the statement is executed. This can for instance be useful when having to ensure that a statement is not executed at the instant the clock signal changes state in a testbench.

## 2.4.5 Parallel Execution

It is important to remember that many of Verilog's statements execute in parallel, and to avoid race conditions. For instance, specifying several clocked blocks implies that they are all executed every clock cycle, and by using the non-blocking assignment operator, many assignments happen at the same instant.

Race conditions occur if several assignments to the same variable happen at the same moment. By only manipulating a register in one always-block, as suggested in 2.4.8, it is easier to verify that only one of the assignments can happen at once.

# 2.4.6 Synthesizable and Non-Synthesizable Constructs

Not all constructs are possible to synthesize, that is, to be used to generate hardware. For instance, the initial construct runs only at the beginning of a simulation, and can be used to initialize values in a test bench, but cannot be used to define initial values in a real hardware product. To accomplish this, reset signals must be used.

Synthesis tools may ignore non-synthesizable constructs or return an error. Which constructs are synthesizable or not depends on the tool in use.

## 2.4.7 Modules and Encapsulation

Modules provide encapsulation of entities in the system, and can for instance be used for partitioning a unit containing a vast amount of logic into several smaller, manageable modules. The interface of a module is defined by its ports, which can be of type input, output or both. A module is defined by the module keyword and its name, and its ports are listed in a way that resembles parameters in C functions. A module can contain tasks and functions in addition to its logic statements, and can be regarded as a construct similar to object-oriented programming languages' classes.

The following example defines a simple module with one input and one output, and all it does is to invert the input signal. After reset, the output of the module is 0. This module could further be instantiated in another module.

```

module invert (clock, reset, i, o);

input clock;

input reset;

input i;

output o;

reg o;

always @(posedge clock or posedge reset) begin

if (reset) o <= 0;

else o <= ~i;

end

endmodule

```

## Code 4 – module example

## 2.4.8 Best-practices and Guidelines

The following list consists of best-practices that were given in tutorials or by Atmel's personnel while the author was learning Verilog.

- Only manipulate a register in one always-block

- Use non-blocking assignments in clocked logic

- Use blocking assignments in combinational logic

- Do not mix synthesizable code with test-code for simulation

- Follow internal code guidelines, if such exist

# **3** Originally Proposed Specification of the TMU

# 3.1 Introduction

The Time Management Unit (TMU) is a hardware unit intended to keep record of a task's total execution time. It can also interrupt a running task when its execution time budget is depleted. It offers the possibility of low overhead execution time monitoring, as it has built-in 64-bit registers and can store a task's total execution time without the need for extra computations in the CPU. It also supports atomic swapping of values between the currently running task and the next task.

# 3.2 Specification and High-level Design

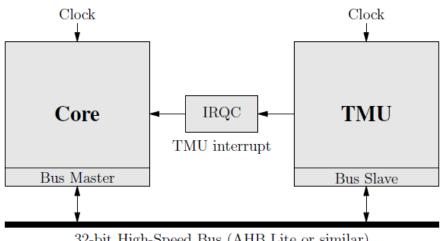

The paper "Functional specification for a Time Management Unit" (1) has been used as a foundation for the intended behavior of the TMU. In addition, a specification written by the same author in SystemC was used to elaborate the desired manner of operation. The author of this thesis' interpretation of these documents is given in this section. Figure 8 illustrates the intended connection between the CPU core and the TMU.

32-bit High-Speed Bus (AHB Lite or similar)

# Figure 8 - connection between UC3 core and TMU (1)

Two registers, **COUNT** and **COMPARE**, are essential for the TMU. The **COUNT** register is initially 0, and increases by 1 every clock cycle. It is intended to keep track of the number of clock cycles used by the active task. **COMPARE** contains a user-defined value, and when **COUNT** reaches this level, an interrupt signal is asserted. **COMPARE** is used to represent a budget of clock cycles for the active task, and the TMU will interrupt the processor when a task's budget is depleted to let the run-time system take appropriate action. When a task is interrupted or blocked and another task is resumed, **COUNT** and **COMPARE** are intended to be loaded with the new task's values as a part of the context switch, and the previous values are stored together with the previous task's context.

The registers are 64 bits wide to be able to contain the total running time of a task. The maximum value **COUNT** can take is  $2^{64} > 1,8 * 10^{19}$ , hence a task will be able to run thousands of years at reasonable clock frequencies before the registers overrun. Because of the APB data bus is 32 bits wide in UC3, the values have to be transferred in two parts. Each 64-bit register is

therefore divided into a high and low part, which appears as two 32-bit registers to the CPU core.

Both registers have their corresponding swap registers which are intended to offer atomic operations for exchanging new **COUNT** and **COMPARE** values with previous ones when switching tasks. First, the **SWAP\_COMPARE** value is written. After the **SWAP\_COUNT** value subsequently has been written, the values in the **COUNT** and **COMPARE** registers are swapped with their respective swap registers. Thus, the previous value of the primary registers are stored in the swap registers in the same clock cycle as they get updated by new values, and are ready to be read back to be stored into the previous task's context. The primary **COUNT** and **COMPARE** values can also be accessed directly if desired, as these registers are available on the TMU's external interface.

Because of the rapid changes to **COUNT**, the lower part is stored in a buffer when the high part is read. This ensures that the value returned is as close as possible to **COUNT**'s value when the read instruction was issued. It also avoids that an invalid value is returned in the case of an overflow of the low part happening between reading the high and low part. **COMPARE** is specified to use the same buffer, although this register can only be modified by the user and thus will not change between reads.

When writing to the high part of **COUNT** or **COMPARE**, the value is stored in the same buffer. Then, when writing to the low part, the written value is stored together with the buffered value into the destination register. This ensures that the entire registers are updated at the same instant, which could otherwise lead to unintended interrupt signals being generated or corruption of the counter value.

As the buffer is shared between **COUNT** and **COMPARE**, and is used for both reading and writing, it is important to complete an operation with one register before accessing other registers in the module.

## 3.2.1 Context Switch Code Example Explained

An example of how a context switch including the swap operation could be performed was given in (1), however few comments were given. Also, the author of this thesis discovered some bugs in the example, and suggested an optimization as well. The updated code was developed by Gregertsen in cooperation with the author of this thesis, and is explained in this section.

| Store address of running thread in R9 |                               |                                                |  |  |

|---------------------------------------|-------------------------------|------------------------------------------------|--|--|

| lda.w                                 | r8, running_thread            | Load address of running thread's context       |  |  |

| ld.w                                  | r9, r8[0]                     | Dereference pointer                            |  |  |

|                                       |                               |                                                |  |  |

|                                       | Save CPU conte                | xt of running thread                           |  |  |

| sub                                   | r9, -(CONTEXT_SIZE + 4)       | Makes space for context                        |  |  |

| stm                                   | r9, <i>r0, r1…r</i> 7, sp, lr | Store CPU context                              |  |  |

| mfsr                                  | r0, SYSREG_SR                 | Copy system register                           |  |  |

| st.w                                  | r9, r0                        | Store system register to context               |  |  |

|                                       |                               |                                                |  |  |

|                                       | Store address                 | of first thread in R1                          |  |  |

| lda.w                                 | r1, first_thread              | Load address of first thread's context         |  |  |

| ld.w                                  | r2, r1[0]                     | Dereference pointer                            |  |  |

| st.w                                  | r8[0], r2                     | Set running_thread to first thread             |  |  |

|                                       |                               |                                                |  |  |

|                                       |                               | context switch                                 |  |  |

| mov                                   | r8, TMU_SWAP_COUNT_HI         | Load address of first swap register            |  |  |

| ld.d                                  | r4, r2++                      | Load TMU context of first thread               |  |  |

| ld.d                                  | rб, r2++                      |                                                |  |  |

| st.d                                  | r8++, r4                      | Store TMU context to TMU                       |  |  |

| st.d                                  | r8++, r6                      |                                                |  |  |

| ld.d                                  | r6,r8                         | Load TMU context of previous thread            |  |  |

| ld.d                                  | r4,r8                         |                                                |  |  |

| st.d                                  | r9, r6                        | Store TMU context to previous thread's context |  |  |

| st.d                                  | r9, r4                        |                                                |  |  |

|                                       |                               |                                                |  |  |

| Load CPU context of first thread      |                               |                                                |  |  |

| mov                                   | r9, r2                        | Copy pointer to first thread to R9             |  |  |

| ld.w                                  | r0, r9++                      | Load system register from context              |  |  |

| mtsr                                  | SYSREG_SR, r0                 | Restore system register                        |  |  |

| sub                                   | pc, -2                        | Increment program counter                      |  |  |

| ldm                                   | r9++, r0, r1r7, sp, pc        | Restore CPU context                            |  |  |

#### Table 1 - explanation of context switch

Note that the next thread that is scheduled to run is called first\_thread, because it is first in the ready queue. Also, note the distinction between "context", "CPU context" and "TMU context". The first refers to CPU and TMU context together, which is stored in memory. "CPU context" refers to the normal context of a task, while "TMU context" means the **COUNT** and **COMPARE** registers of the TMU.

# **3.3** Implementation of the TMU

The TMU is an independent module connected to the microcontroller's bus. Originally, the High Speed Bus (HSB, or AHB) was proposed. As discussed in 8.2.1, the slower Peripheral Bus (PB, or APB) was chosen partly because of its simplicity. By implementing the TMU as an independent module connected to this bus, it is simple to integrate on any processor using the AMBA APB interface.

## 3.3.1 Interface Registers

4 registers of 64 bits width should be user accessible; **COUNT**, **COMPARE**, **SWAP\_COUNT** and **SWAP\_COMPARE**. These were implemented as the reg type, that is, their values should be retained between assignments in Verilog. Each register has a width of 64 bits, with the MSB and LSB given as named constants.

reg [HI\_MSB:LO\_LSB] count, compare, swap\_count, swap\_compare;

#### Code 5 – register definitions

These registers are memory mapped and accessed through the APB interface, described in 3.3.6. As the APB data bus is 32 bits wide, two accesses are needed to read or write the 64-bit registers. This has to be done in the correct order, because of the buffer described in 3.3.2 and swap functionality as described in 3.3.4.

## 3.3.2 Internal Buffer

As described in section 3.2, some of the 64-bit registers need a buffer to store a value between their two 32-bit accesses. This was implemented by using a shared buffer for all registers, and thus it restricts the user from accessing the high part of a register and then accessing another register before completing the first access by reading from or writing to the low part of that register.

When writing to the high part of one of the registers that needs buffering, the value is actually written to the internal buffer. On a subsequent write to the low part of the register, the concatenation of the buffer and what was written to the low part is stored in the target register.

Writing of the **COMPARE** register is used as an example below, as the **COUNT** register has additional side-effects (described in following sections). The offsets are parts of a case statement in a clocked code block, with a part of the APB address bus as input. In the code below, data is buffered when writing the high part, then both the buffer and the written value is stored when writing the low part.

```

COMPARE_HI:

buffer <= wdata;

COMPARE_LO:

compare <= {buffer, wdata};</pre>

```

#### Code 6 – buffering registers on writes

Reads are carried out in a slightly different manner. When the high part of a buffered register is accessed, its value is immediately put on the bus, and the low part is stored into the buffer simultaneously. This ensures that both the high and low part of the read value are from the same instant. The first example below displays the clocked write to the buffer that occurs when the high part is read:

```

COMPARE_HI:

buffer <= compare[LO_MSB:LO_LSB];</pre>

```

#### Code 7 - buffering registers on reads

The next example indicates how the high part is put on the bus when reading. Note that this is a combinational statement (this is not obvious as the context of the statement is not shown here). The buffering in Code 7 and the output of data to the bus in Code 8 are performed at the same time.

```

COMPARE_HI:

prdata = compare[HI_MSB:HI_LSB];

```

#### Code 8 – putting data on bus

When the low part then is accessed, it is actually the contents of the buffer that is put on the bus:

```

COMPARE_LO:

prdata = buffer;

```