# En Time Management Unit (TMU) for sanntidssystemer

Bjørn Forsman

Master i teknisk kybernetikk Oppgaven levert: Juni 2008 Hovedveileder: Amund Skavhaug, ITK

Norges teknisk-naturvitenskapelige universitet Institutt for teknisk kybernetikk

# Oppgavetekst

I et sanntidssystem må tidsfristene nås, ellers degraderes eller feiler systemet. For å kunne garantere at tidsfristene blir nådd må programmenes verste kjøretid (WCET) være kjent, maskinvaren til systemet må være predikterbar og hyppigheten av eksterne avbrudd må være begrenset. Å oppnå alle disse faktorene er vanskelig og derfor er hensikten med denne oppgaven å utvikle en Time Management Unit (TMU) som kan måle og begrense kjøretiden prosessoren bruker på vanlige prosesser og avbruddsrutiner under kjøring.

Prosjektet kan deles inn i mindre oppgaver:

- \*Utfør et litteratursøk omkring temaet

- \*Lag en spesifikasjon for TMUen

- \*Evaluer mulige plattformer for implementering og diskuter fordeler og ulemper

- \*Utfør en implementering på en passende platform

- \*Test implementasjonen for å verifisere at designet fungerer etter spesifikasjonene

Oppgaven gitt: 07. januar 2008 Hovedveileder: Amund Skavhaug, ITK

# **Problem description**

# A Time Management Unit (TMU) for Real-Time Systems

In real-time systems the time deadlines must be met or the system degrades or even fails. To guarantee that the deadlines are met, the worst-case execution time (WCET) of the programs must be known, the underlying hardware must be deterministic and the occurrences of interrupts must be bounded. All these factors may be hard to achieve, therefore this project aims to provide a Time Management Unit (TMU) that is capable of measuring and controlling the execution time spent by tasks and interrupt service routines (ISRs).

The assignment can be split into several smaller tasks:

- 1. Perform a background research on the subject and related work

- 2. Propose a design for the TMU

- 3. Evaulate possible implementations of the proposed TMU and discuss its pros and cons

- 4. Implement the TMU on a suitable platform according to its proposed design

- 5. Perform tests on the implementation to verify that the design is operating according to its specifications

| Assignment given:   | 2008-01-07            |

|---------------------|-----------------------|

| To be handed in by: | 2008-06-23            |

| Supervisors:        | Amund Skavhaug (ITK)  |

|                     | Bjørn B. Larsen (IET) |

# Preface

This master thesis is written as a compulsory part of the study for the degree of Master of Science in Engineering Cybernetics with the specialisation Dedicated Computer Systems at the Norwegian University of Science and Technology (NTNU).

Although my native language is Norwegian, I have chosen to write this report in English because most literature on the subject at hand is written in English, and also because I would like to improve my English skills.

The thesis is written in the  $\[Mathbb{L}^{A}T_{E}X$  document preparation system and the figures are created with the diagram creation program Dia.

I would like to thank my supervisor Amund Skavhaug for his guidance and inspiration throughout this project and both Mikael K. Eriksen and Christopher T. P. de Lange for their help on the report. Also, I would like to thank Jan Anders Mathisen for being kind enough to lend me his FPGA development board.

Trondheim, 2008-06-23

Bjørn Forsman

# Abstract

In real-time systems the time deadlines must be met or the system degrades or even fails. To support timely behaviour, the real-time system must be predictable at the hardware and software level. Estimating the Worst Case Execution Time (WCET) of any non-trivial code is difficult and when taking into account the underlying hardware with features like deep execution pipelines, caches and DMA, the overall effort will be unmanageable [20]. Further, realtime systems are often subjected to unbounded external stimuli, known as asynchronous events or interrupts, which may drive the system into overload. Because of these two key problems, there is a need for a dynamic approach to measuring and controlling the execution times of tasks and interrupt service routines (ISRs).

In this project, a study of scheduling in real-time systems have been carried out. Based upon this study, a hardware unit called Time Management Unit (TMU) is designed aiding real-time systems in keeping deadlines by measuring and controlling the execution times of tasks and asynchronous events. A test system was implemented, comprising an Field Programmable Gate Array (FPGA) with a LEON3 soft-core processor running the eCos embedded operating system.

The result is that with the use of the proposed TMU, execution times for tasks and ISRs can be bounded. Thus one can achieve system predictability and guarantee that the system will not be overloaded, if the unit is used appropriately. The TMU introduces very little processor time overhead and utilise little to moderate amounts of FPGA logic resources.

The principal conclusion is that the TMU brings predictability to real-time systems operating in unpredictable environments at a relatively low cost; both concerning processor overhead and the increased use of FPGA logic resources.

# Contents

| A                    | bbre | viations                                                | x               |  |  |  |  |  |

|----------------------|------|---------------------------------------------------------|-----------------|--|--|--|--|--|

| 1                    | Intr | roduction                                               | 1               |  |  |  |  |  |

|                      | 1.1  | Motivation                                              | 2               |  |  |  |  |  |

|                      | 1.2  | Work in the same field                                  | 2               |  |  |  |  |  |

|                      | 1.3  | Thesis organisation                                     | 2               |  |  |  |  |  |

| <b>2</b>             | Bac  | Background literature 5                                 |                 |  |  |  |  |  |

|                      | 2.1  | Real-time system definition                             | 5               |  |  |  |  |  |

|                      | 2.2  | Real-Time Operating System                              | 6               |  |  |  |  |  |

|                      |      | 2.2.1 What makes an OS real-time?                       | 7               |  |  |  |  |  |

|                      | 2.3  | Scheduling                                              | 7               |  |  |  |  |  |

|                      |      | 2.3.1 Scheduling periodic tasks                         | 8               |  |  |  |  |  |

|                      |      | 2.3.2 Rate Monotonic Scheduling                         | 9               |  |  |  |  |  |

|                      |      | 2.3.3 Earliest Deadline First                           | 9               |  |  |  |  |  |

|                      |      | 2.3.4 Scheduling Aperiodic Tasks                        | 10              |  |  |  |  |  |

|                      | 2.4  | FPGA                                                    | 13              |  |  |  |  |  |

|                      |      | 2.4.1 IP Cores                                          | $13^{-3}$       |  |  |  |  |  |

|                      |      | 2.4.2 Design Flow Overview                              | 14              |  |  |  |  |  |

|                      | 2.5  | VHDL                                                    | 14              |  |  |  |  |  |

|                      | 2.6  | GHDL                                                    | 15              |  |  |  |  |  |

|                      | 2.7  | GTKWave                                                 | 16              |  |  |  |  |  |

| 3 System development |      | tem development                                         | 17              |  |  |  |  |  |

|                      |      | TMU theory of operation                                 | 17              |  |  |  |  |  |

|                      | 0.1  | 3.1.1 OS support for the TMU                            | 19              |  |  |  |  |  |

|                      | 3.2  | TMU implementation alternatives                         | 19              |  |  |  |  |  |

|                      | 0.2  | 3.2.1 Peripheral device                                 | 19              |  |  |  |  |  |

|                      |      | 3.2.2 Coprocessor                                       | 19              |  |  |  |  |  |

|                      |      | 3.2.3 Register File                                     | 20              |  |  |  |  |  |

|                      |      | 3.2.4 Chosen implementation                             | $\frac{-0}{20}$ |  |  |  |  |  |

|                      | 3.3  | Host development platform                               | $\frac{20}{20}$ |  |  |  |  |  |

|                      | 0.0  | 3.3.1 Installation of Xilinx software and cable drivers | $\frac{20}{21}$ |  |  |  |  |  |

|                      |      | 3.3.2 GHDL                                              | $\frac{21}{22}$ |  |  |  |  |  |

|                      |      | 3.3.3 GTKWave                                           | $\frac{22}{22}$ |  |  |  |  |  |

|                      | 3.4  | FPGA development board                                  | $\frac{22}{22}$ |  |  |  |  |  |

|                      | 0.1  |                                                         |                 |  |  |  |  |  |

|          |              | 3.4.1   | Spartan-3 Starter Board                |     |     |   |   |   |   | 23         |

|----------|--------------|---------|----------------------------------------|-----|-----|---|---|---|---|------------|

|          |              | 3.4.2   | Spartan-3A DSP 1800A Development Board |     |     |   |   |   |   | 26         |

|          |              | 3.4.3   | Virtex-4 ML401 Evaluation Platform     |     |     |   |   |   |   | 27         |

|          | 3.5          | Soft-co | re processor alternatives              |     |     |   |   |   |   | 28         |

|          |              | 3.5.1   | LEON                                   |     |     |   |   |   |   | 28         |

|          |              | 3.5.2   | OpenRISC                               |     |     |   |   |   |   | 29         |

|          |              | 3.5.3   | AEMB                                   |     |     |   |   |   |   | 29         |

|          |              | 3.5.4   | Chosen soft-core processor             |     |     |   |   |   |   | 29         |

|          | 3.6          | RTOS    | alternatives                           |     |     |   |   |   |   | 29         |

|          |              | 3.6.1   | RTEMS                                  |     |     |   |   |   |   | 30         |

|          |              | 3.6.2   | eCos                                   |     |     |   |   |   |   | 30         |

|          |              | 3.6.3   | Chosen RTOS                            |     |     |   |   |   |   | 31         |

|          | 3.7          | LEON    | 3 development tools                    |     |     |   |   |   |   | 31         |

|          |              | 3.7.1   | GRLIB IP Library                       |     |     |   |   |   |   | 31         |

|          |              | 3.7.2   | GRMON debug monitor                    |     |     |   |   |   |   | 31         |

|          |              | 3.7.3   | TSIM LEON simulator                    |     |     |   |   |   |   | 32         |

|          |              | 3.7.4   | BCC                                    |     |     |   |   |   |   | 33         |

|          | 3.8          | Implen  | nenting a LEON3 system                 |     |     |   |   |   |   | 34         |

|          |              | 3.8.1   | Running applications on target         |     |     |   |   |   |   | 34         |

|          | 3.9          | Config  | uring eCos and building applications   |     |     |   |   |   |   | 36         |

|          | 3.10         |         | lesign of the TMU                      |     |     |   |   |   |   | 39         |

|          |              |         | TMU VHDL model                         |     |     |   |   |   |   | 40         |

|          |              |         | TMU register details                   |     |     |   |   |   |   | 41         |

|          |              |         | TMU logic utilisation                  |     |     |   |   |   |   | 43         |

|          | 3.11         |         | g the TMU to a LEON3-design            |     |     |   |   |   |   | 44         |

|          |              |         | are simulation                         |     |     |   |   |   |   | 45         |

|          |              |         | Problems                               |     |     |   |   |   |   | 48         |

|          |              |         | Results                                |     |     |   |   |   |   | 48         |

|          | 3.13         |         | es to eCos for TMU support             |     |     |   |   |   |   | 48         |

|          |              |         | Changes to the HAL                     |     |     |   |   |   |   | 49         |

|          |              |         | The TMU API                            |     |     |   |   |   |   | 53         |

|          |              |         | Changes to the configuration system    |     |     |   |   |   |   | 54         |

|          | 3.14         |         | ng the Task Timer timeout              |     |     |   |   |   |   | 55         |

|          |              |         | Problems                               |     |     |   |   |   |   | 56         |

|          |              |         |                                        |     |     |   |   |   |   |            |

| <b>4</b> | Test         | s       |                                        |     |     |   |   |   |   | <b>57</b>  |

|          | 4.1          | Setup   |                                        |     |     |   |   |   |   | 57         |

|          | 4.2          | Test 1: | Sporadic events                        |     | •   | • | • | • | • | 58         |

|          |              | 4.2.1   | Results                                |     | •   |   | • | • | • | 58         |

|          | 4.3          | Test 2: | Tasks with variable execution times    |     |     |   | • |   | • | 60         |

|          |              | 4.3.1   | Results                                |     | • • |   | • | • | • | 60         |

| 5        | Dia          | ussion  |                                        |     |     |   |   |   |   | 63         |

| J        | 5.1          |         | 5                                      |     |     |   |   |   |   | <b>6</b> 3 |

|          | $5.1 \\ 5.2$ |         | are choices                            |     |     |   |   |   |   | 63         |

|          | 5.2          |         | re choices                             |     |     |   |   |   |   | 64         |

|          | 5.3<br>5.4   |         |                                        |     |     |   |   |   |   | 64         |

|          | 0.4          | Design  | of the TMU                             | • • | • • | • | • | · | • | 04         |

| 6  | Conclusion                                         | 65                    |

|----|----------------------------------------------------|-----------------------|

| 7  | Further work                                       | 67                    |

| Bi | ibliography                                        | 69                    |

| Α  | CD         A.1       Contents         A.2       CD | <b>73</b><br>73<br>75 |

| в  | Source code<br>B.1 TMU                             | <b>77</b><br>77       |

# List of Abbreviations

| API  | Application Programming Interface           |

|------|---------------------------------------------|

| ATC  | Asynchronous Transfer of Control            |

| CPLD | Complex Programmable Logic Device           |

| CPU  | Central Processing Unit                     |

| DMA  | Direct Memory Access                        |

| DS   | Deferrable Server                           |

| DSR  | Deferred Service Routine                    |

| DUT  | Device Under Test                           |

| EDF  | Earliest Deadline First                     |

| FPGA | Field Programmable Gate Array               |

| GNU  | GNU's Not Unix                              |

| GPL  | General Public License                      |

| GUI  | Graphical User Interface                    |

| HDL  | Hardware Description Language               |

| ISA  | Instruction Set Architecture                |

| ISR  | Interrupt Service Routine                   |

| Ків  | kibibit = $2^{10}$ bits = 1,024 bits        |

| LGPL | Lesser General Public License               |

| LUT  | Look-Up Table                               |

| MIB  | mebibyte = $2^{20}$ bytes = 1,024 kibibytes |

| OS   | Operating System                            |

| PS   | Polling Server                              |

| RTOS | Real-Time Operating System                  |

| SoC  | System-on-Chip                              |

| SS   | Sporadic Server           |

|------|---------------------------|

| TMU  | Time Management Unit      |

| VSR  | Vector Service Routine    |

| WCET | Worst Case Execution Time |

| XSR  | Exception Service Routine |

### Chapter 1

# Introduction

Real-time computing systems play a vital role in our society, and they cover a spectrum from the very simple to the very complex. Examples of real-time systems include multimedia players, microwave ovens, control systems for cars, airplanes, military weapon systems and factory control systems.

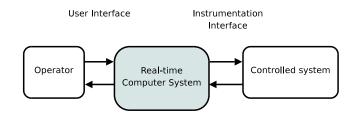

In real-time computing the correctness of the system depends not only on the logical result of the computation but also on the time at which the results are produced. Typically, a real-time system consists of a controlling system and a controlled system. For example, in an automated factory the controlled system is the factory floor with its robots, assembling stations and the assembled parts. The controlling system is the computer and human interfaces that manage and coordinate the activities on the factory floor. Thus, the controlled system can be viewed as the environment with which the computer interacts.

Figure 1.1: Real-time system

The controlling system interacts with its environment, the controlled system, via sensors and actuators. It is imperative that the percepted state of the environment, as seen by the controlling system, is consistent with its actual state. Otherwise, the controlling systems' activities may have disastrous effects. Hence, periodic monitoring and timely processing of the information is necessary.

#### 1.1 Motivation

Knowing the Worst Case Execution Time (WCET) is of prime importance for the timing analysis of hard real-time systems. WCET analysis is becoming more difficult as modern computer systems become more complex. Features like deep execution pipelines, branch prediction, caches and virtual memory, all lack deterministic behaviour, and must be included in the WCET analysis. Estimating the WCET of any non-trivial code is in general very difficult, and when taking into account the unpredictable hardware, WCET analysis requires unmanageably high efforts [20]. Also, real-time systems are often subjected to unbounded external stimuli, known as asynchronous events or interrupts, which may drive the system into overload. To lower the chances of missing deadlines, systems have to be over-dimensioned to reduce the risk of an unexpected temporal resource shortage during operation. Because of this, there is a need for a dynamic measurement and control of the execution times of tasks and asynchronous events.

This thesis will focus on how to make a hardware unit, called a Time Management Unit (TMU), able to improve the predictability of real-time systems based on standard processor architectures with unpredictable timing behaviour. The TMU will limit the execution times of tasks as well as the occurrences of interrupts. The unit shall preferably be architecture independent and not depend on any special programming language feature.

#### 1.2 Work in the same field

Hardware platforms for real-time system have gained little interest compared to that of the software, where programming language features and scheduling algorithms have been thoroughly studied. An accurate Time-Management Unit for real-time processors was proposed by Kailas and Agrawala [19]. It is a fine granularity clock embedded in CPUs solving problems with the software clock approach, updating a memory location with a new time value at regular intervals, controlled by an external interrupt. The unit is not intended for measuring or controlling execution times. Others have studied processor support for temporal predictability; The SPEAR design example [7] is a processor design with predictable timing and interrupt response aimed at hard real-time systems. Colnaric and Halang [6] presents an asymmetrical multiprocessor architecture for hard real-time systems, whose temporal behaviour is fully predictable. As for software, Puschner and Koza [26] created new programming language features making WCET analysis easier.

#### **1.3** Thesis organisation

This thesis is organised as follows:

- Chapter 2 presents the necessary background literature regarding realtime systems, scheduling theory, FPGA development and the basic software tools used in this project.

- Chapter 3 describes the system development phase. This includes the proposed TMU's theory of operation, implementation choices, host and target development platforms, HDL design and implementation of the TMU, hardware simulations and the modifications to eCos for TMU support.

- Chapter 4 presents the final tests performed on the implemented system.

- Chapter 5 gives a discussion of the project and the work that has been done.

- Chapter 6 presents the conclusion of this project.

- Chapter 7 gives an overview of further work.

### Chapter 2

# **Background literature**

The purpose of this chapter is to present real-time systems and RTOSs, basic concepts of scheduling, and to introduce FPGAs and soft-core processors. And finally to describe the basic tools and utilities used in this project.

#### 2.1 Real-time system definition

There are several definitions of a real-time system; however, they all have in common the notion of response time – the time taken for the system to generate output from some associated input. The Oxford Dictionary of Computing gives the following definition:

Any system in which the time at which the output is produced is significant. This is usually because the input corresponds to some movement in the physical world, and the output has to relate to that same movement. The lag (delay) from the input time to the output time must be sufficiently small for acceptable timeliness.

Krishna and Shin [20] have another definition:

A real-time system is anything that we, the authors of this book, consider to be a real-time system. This includes embedded systems that control things like aircraft, nuclear reactors, chemical power plants, jet engines, and other objects where Something Very Bad will happen if the computer does not deliver its output in time. These are called *hard* real-time systems. There is another category called (not surprisingly) *soft* real-time systems, which are systems such as multimedia, where nothing catastrophic happens if some deadlines are missed, but where the performance will be degraded below what is generally considered acceptable. In general, a real-time system is one in which a substantial fraction of the design effort goes into making sure that task deadlines are met.

#### 2.2 Real-Time Operating System

A Real-Time Operating System (RTOS) is a multitasking operating system intended for real-time applications. The RTOS provides an abstraction layer that hides the hardware details from the application software. The abstraction layer typically consists of the following five categories:

- 1. Task management

- 2. Intertask communication and synchronisation

- 3. Timers

- 4. Dynamic memory allocation

- 5. Device I/O

The most basic job of the RTOS kernel is task management. This set of services allows application software developers to design their software as a number of separate pieces of software known as tasks – each handling a distinct topic, a distinct goal, and perhaps its own real-time deadline. Services in this category include the ability to create and control tasks and assign priorities to them. The main RTOS service in this category is the scheduling of tasks as the embedded system is in operation.

The scheduler controls the execution of application software tasks, and is a component of RTOSs that have been studied thoroughly. Most RTOSs do their scheduling of tasks using a scheme called priority-based preemptive scheduling. Each task in a software application must be assigned a priority, with higher priority values representing the need for quicker responsiveness. Very quick responsiveness is made possible by the preemptive nature of the task scheduling. Preemptive means that the scheduler is allowed to stop any task at any point in its execution, if it determines that another task needs to run immediately. The basic rule that governs priority-based preemptive scheduling is that at every moment in time, the highest priority task that is ready to run, will be the task that must be running. In other words, if both a lowpriority task and a higher-priority task are ready to run, the scheduler will allow the higher-priority task to run first. The low-priority task will only get to run after the higher-priority task has finished with its current work. But sometimes, the task with the highest priority depends on a resource held by a lower priority task. This scenario is called *priority inversion*. This causes the execution of the high priority task to be blocked until the low priority task has released the resource, effectively inverting the relative priorities of the two tasks. If some other medium priority task, that does not depend on the shared resource, attempts to run in the interim, it will take precedence over both the low priority task and the high priority task. Solutions to this problem are disabling all interrupts to protect critical sections, the priority ceiling protocol or priority inheritance.

The second category of kernel services is intertask communication and synchronisation. These services make it possible for tasks to pass information from one to another, without danger of that information ever being damaged. They also make it possible for tasks to coordinate, so that they can productively cooperate with one another. Without the help of these RTOS services, tasks might communicate corrupted information or otherwise interfere with each other. Message passing, mutexes, semaphores, event flags and signals are examples of services in this category.

Since many embedded systems have stringent timing requirements, most RTOS kernels also provide some basic timer services, such as task delays, event counters and alarms.

Some RTOSs provide dynamic memory allocation and device drivers.

#### 2.2.1 What makes an OS real-time?

Many general purpose operating systems provide similar kernel services as real-time operating systems. The key difference between general-computing operating systems and real-time operating systems is the need for deterministic timing behaviour in the real-time operating systems. Formally, deterministic timing means that operating system services consume only known and expected amounts of time. In theory, these service times could be expressed as mathematical formulas. These formulas must be strictly algebraic and not include any random timing components. Random elements in service times could cause random delays in application software and could then make the application randomly miss real-time deadlines – a scenario clearly unacceptable for a real-time embedded system.

An RTOS does not necessarily have high throughput; rather, an RTOS provides facilities which, if used properly, guarantee deadlines can be met generally (soft real-time) or deterministically (hard real-time). Designers of general purpose OSs on the other hand, will strive for better throughput, not determinism. An RTOS is valued more for how quickly and/or predictably it can respond to a particular event than for the given amount of work it can perform over time.

#### 2.3 Scheduling

It is the job of the scheduling algorithm and operating system scheduler to provide predictability to the system and to coordinate resources to meet the timing constraints of the physical system. Traditionally, real-time systems have used the cyclical executives approach for scheduling. Cyclical executives provide a deterministic schedule for all tasks and resources in a real-time system by creating a static timeline upon which tasks and resources are assigned specific time intervals. While such an approach is manageable for simple systems, it quickly becomes unmanageable for large systems. It is a painful process to develop application code that fit in the time slots of a cyclical executive while ensuring that the critical sections of different tasks do not interleave. This approach is typically expensive to create, verify, and update.

An alternative approach uses preemptive and priority-driven scheduling algorithms to schedule tasks. A scheduling algorithm is a set of rules that determines the task to be executed at a particular moment. This means that whenever there is a request for a task of higher priority than the one currently being executed, the running task is immediately interrupted and the newly requested task is started. Thus the specification of such algorithms amounts to the specification of the method of assigning priorities to tasks. Using well defined algorithms to schedule tasks in a real-time system yields an understandable scheduling solution.

The preemptive real-time scheduling algorithms can be broadly classified into two categories: *static priority* and *dynamic priority*. This classification is based on the manner in which priorities are assigned to tasks. A scheduling algorithm is said to be static if priorities are assigned to tasks a priori and they do not change during run-time. A static algorithm is also called a fixed priority scheduling algorithm, an example of which is the Rate Monotonic (RM) algorithm. A scheduling policy is said to be dynamic if priorities of a task might change from request to request. The Earliest Deadline First (EDF) algorithm falls under the category of dynamic priority scheduling policy. Before discussing these algorithms in detail, some of the terms associated with real-time scheduling theory will be explained.

A task is a thread of execution performing a specific function. For example, a task could be a simple thread polling the serial port to check if any data has arrived. A real-time task can be classified as periodic or aperiodic depending on its arrival pattern or as soft or hard based on the consequences of a missed deadline.

#### 2.3.1 Scheduling periodic tasks

Tasks with regular arrival times are called periodic. A common use of periodic tasks is to process sensor data. For example, a temperature monitor of a nuclear reactor should be read periodically to detect any changes promptly. Tasks with irregular arrival times are aperiodic tasks and are used to handle the processing requirements of random events such as operator requests.

Each of the tasks must complete execution before some fixed time has elapsed since its request. This fixed time is known as the deadline of the task. If meeting a given task's deadline is critical to the system's operation the task is called a hard real-time task. If missing occasional deadlines of a particular task does not adversely affect the system's performance it is a soft real-time task.

#### 2.3.2 Rate Monotonic Scheduling

Liu and Layland presented an optimal fixed priority algorithm known as the Rate Monotonic (RM) algorithm [22]. In this algorithm, priorities are assigned according to the request rate (frequency) of tasks. Specifically, tasks with higher frequency will have higher priority. The Rate Monotonic priority assignment is optimum in the sense that no other fixed priority assignment rule can schedule a task set which cannot be scheduled by the RM algorithm.

One drawback of the RM algorithm is that the schedulable bound is less than 100 %. Schedulable bound is the maximum value of the CPU utilisation for a set of tasks up to which all tasks will be guaranteed to meet their deadline. Since  $C_i/T_i$  is the fraction of processor time spent in executing task  $\tau_i$ , the total CPU utilisation for a set of n tasks is:

$$U = \sum_{i=0}^{n} C_i / T_i \tag{2.1}$$

where  $C_i$  is the worst-case execution time and the period is  $T_i$ .

Liu and Layland [22] proved that the worst-case schedulable bound  $W_n$  for n tasks is:

$$W_n = n \left( 2^{1/n} - 1 \right) \tag{2.2}$$

This worst case utilisation bound decreases monotonically from 0.83 when n = 2 to 0.693 as n approaches infinity. This shows that any periodic task set of any size will meet deadlines all the time if the RM algorithm is used and the total utilisation is not greater than 0.693. Note that this is a sufficient but not necessary schedulability test. The task set may still be schedulable even if the processor utilisation is above the schedulable bound.

#### 2.3.3 Earliest Deadline First

Liu and Layland [22] also present a dynamic scheduling algorithm called the Earliest Deadline First (EDF) because the task with the nearest deadline for its current request has the highest priority. At any instant, the task with the highest priority and an unfulfilled request gets hold of the CPU. This contrasts with the RM algorithm in which priorities do not change with time. One drawback of the EDF algorithm is the higher scheduling overhead with respect to the RM algorithm, as it has to dynamically compute priorities of tasks.

The necessary and sufficient condition for the feasibility of a task set with EDF is given below:

$$U = \sum_{i=0}^{n} C_i / T_i \leqslant 1 \tag{2.3}$$

where, n is the total number of tasks.

The ratio of  $C_i/T_i$  is the CPU utilisation by the *i*th task. The above condition is necessary because the tasks should not overload the CPU if they have to meet all the deadlines. EDF is an optimal algorithm in the sense that if a task set can be scheduled by any algorithm, it can also be scheduled by EDF.

Dynamic priority scheduling with the EDF algorithm has a distinct advantage over fixed priority scheduling: the schedulable bound for EDF is 100 % for all task sets. This means that you can fully utilise the computing power of the CPU. The major problem with the EDF algorithm is that there is no way to guarantee which tasks will fail in a transient overload. With RM, low priority tasks are always the first to fail. However, no such priority assignment exists with EDF.

#### 2.3.4 Scheduling Aperiodic Tasks

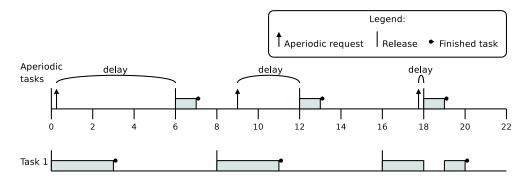

A task with random arrival times is called an aperiodic task. A sporadic task is a subset of aperiodic tasks, having with a minimum interarrival time. Aperiodic tasks result from operator actions or asynchronous events. Noncritical aperiodic tasks can be executed as background tasks. On the other hand, if the aperiodic task is critical it can be incorporated into the RM algorithm through the use of a periodic server, which is a periodic task whose function is to service one or more aperiodic tasks. The simplest periodic server is the Polling Server (PS) and is illustrated in Figure 2.1. The PS is activated every period. If no aperiodic tasks are available, the server suspends itself until the next period. The major disadvantage of this approach is unpredictable response times for aperiodic tasks. An aperiodic task arriving just after the PS has been invoked, has to wait for the server's next period.

Figure 2.1: A polling server for handling aperiodic tasks

An efficient scheduler should be able to meet the hard deadlines of periodic tasks and provide a fast average response time for aperiodic tasks. Two of the algorithms that strive to achieve this goal are: the Deferrable Server (DS) algorithm and the Sporadic Server (SS) algorithm. These algorithms overcome

the major limitation of the polling method where the aperiodic task arrives after the polling instant.

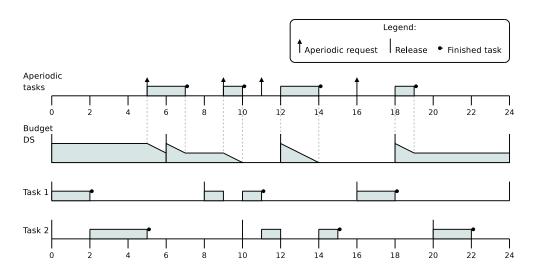

#### Deferrable Server Algorithm

Lehoczky, Sha and Strosnider proposed an algorithm for scheduling aperiodic tasks called the Deferrable Server (DS) algorithm [38]. This algorithm creates a periodic server  $\tau_i$  with  $C_i$  execution time, or execution *budget*, with a priority defined by the server's period  $T_i$ . The DS has the entire period to use its  $C_i$ budget at priority  $P_i$ . When the server has consumed its budget, its priority is set to background – the lowest priority of the system, only allowing it to run when no periodic tasks are available. At the beginning of each period, the budget is set to  $C_i$ . If the DS has any remaining budget from the previous period, it will be discarded.

The difference between the PS and the DS is that a DS can service an aperiodic task anytime during its period provided that it still has some unused execution time. On the other hand, a polling server can only service an aperiodic task that is pending at the start of its period.

Figure 2.2 illustrates a schedule of two periodic tasks and a DS which handles aperiodic tasks. Vertical arrows indicate an aperiodic request and vertical lines represent the release of periodic tasks. The release of the DS means that its budget is replenished. The tasks are ordered by priority, although once the DS has spent its budget, it will receive the lowest priority.

Figure 2.2: An example schedule with a Deferrable Server

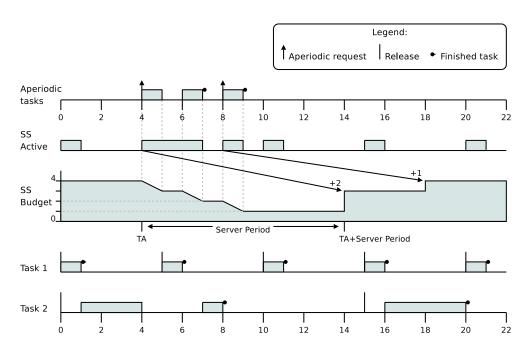

#### Sporadic Server Algorithm

Another algorithm for scheduling soft deadline aperiodic tasks was given by Sprunt, Sha and Lehoczky [34], called the Sporadic Server (SS). The SS algorithm creates a high priority task for servicing aperiodic tasks and preserves its server execution time at its high priority level until an aperiodic request occurs. It differs from the DS algorithm in the way it replenishes its server execution time. Thus, the sporadic server does not recover its capacity to its full value at the beginning of each new period, but only after it has been consumed by aperiodic task execution. More precisely, the sporadic server replenishes its capacity each time TA it becomes active and its capacity is greater than 0. The replenishment time is set to TA plus the server period. The replenishment amount is set to the capacity consumed within the interval TA and the time when the sporadic server becomes idle or its capacity has been exhausted. The sporadic server is considered to be *active* if the priority at which the system is currently executing is equal to or greater than its priority, otherwise it is *idle*. Figure 2.3 illustrates an example schedule with a medium priority sporadic server and two periodic tasks.

Figure 2.3: A medium priority sporadic server for handling aperiodic tasks

According to Sprunt et al. [34], from a scheduling point of view, a sporadic server can be treated as a standard periodic task with the same period and execution time as the sporadic server. They proved that a periodic task set that is schedulable with a task,  $\tau_i$ , is also schedulable if  $\tau_i$  is replaced by a sporadic server with the same period and execution time.

#### 2.4 FPGA

A Field Programmable Gate Array (FPGA) is a semiconductor device containing cells of programmable logic known as Configurable Logic Blocks (CLB) and programmable interconnections. Each CLB has a Look-Up Table (LUT) that can be configured to give a specific type of logic function when programmed. Additionally, there are clocked flip-flops in the CLBs, allowing an optionally synchronous operation and a basic memory element. A typical FPGA has thousands of CLBs and often have special features such as dedicated hardware multipliers and block RAM. Modern FPGAs contain enough logic blocks to implement a number of 32-bit processors on a single device [40]. Most FP-GAs are volatile and lose their configuration upon power loss. Thus the use of non-volatile memory, i.e. flash, for holding the configuration bits is necessary. Often a Complex Programmable Logic Device  $(CPLD)^1$  is used to read the non-volatile memory and program the FPGA when powering up. To define the behaviour of the FPGA the user provides schematics or Hardware Description Language (HDL) source code. The most common HDLs are VHDL and Verilog.

#### 2.4.1 IP Cores

To simplify the design of complex systems in FPGAs, there exist libraries of predefined complex functions and circuits that have been tested and optimised to ease the design process. These predefined circuits are commonly called Intellectual Property cores, or IP cores, and are available from FPGA vendors and third-party IP suppliers. These cores are rarely free, and typically released under proprietary licenses. Other cores are available from developer communities such as OpenCores [24], which are typically free and released under GNU General Public License (GPL) or similar license.

#### Soft-core processor

A soft-core processor is a processor IP core that can be wholly implemented using logic synthesis. It can be implemented in different semiconductor devices containing programmable logic, e.g. FPGAs and CPLDs. Because of this implementation, the processor will not operate at the speeds or have the performance of a hard-core solution. In many embedded applications, the high performance achieved by the hard-core processor is not required, and performance can be traded for expanded functionality and flexibility. With a soft-core processor, its functionality can be tweaked and peripheral devices can be added and removed very easily.

<sup>&</sup>lt;sup>1</sup>CPLDs are also programmable logic devices, similar to FPGAs, but are non-volatile and typically has less logic resources than FPGAs

#### 2.4.2 Design Flow Overview

The general design flow of FPGAs consists of the system design entry where the user supplies HDL files or schematics providing a description of the desired hardware functionality. Then functional simulation may be performed until the result is satisfactory. The next step is to synthesise the design, that is, the synthesis tool will analyse the HDL files and will extract RAM, counters, multiplexers and arithmetic blocks out of the code. When synthesis is done, it is time for place and route. The place and route tool generates a netlist and a timing file. With the timing file it is possible to perform a timing simulation again, in the same simulation environment as before. This timing simulation will be more accurate than the one from synthesis, since it involves timing for routing as well. The last step is to generate a bit-file and download it into the device.

#### 2.5 VHDL

VHDL is the VHSIC Hardware Description Language. VHSIC is an abbreviation for Very High Speed Integrated Circuit. VHDL is used for describing the structure and behaviour of digital electronic hardware designs, such as ASICs and FPGAs as well as conventional digital circuits.

VHDL was originally developed in order to document the behaviour of digital systems, that is to say, VHDL was developed as an alternative to huge, complex manuals which were subject to implementation-specific details. Later, logic simulators were developed that could read the VHDL files. The next step was the development of logic synthesis tools that read the VHDL, and output a definition of the physical implementation of the circuit. Modern synthesis tools can extract RAM, counter, and arithmetic blocks out of the code, and implement them according to what the user specifies. Thus, the same VHDL code could be synthesised differently for lowest cost, highest power efficiency, highest speed, or other requirements.

VHDL is strongly-typed, is case insensitive and has many similarities with the Ada programming language.

In VHDL, a design consists at a minimum of an *entity* which describes the interface and an *architecture* which contains the actual implementation. In addition, most designs import library modules. Some designs also contain multiple architectures and configurations. The following example is a counter with parameterised register width, asynchronous reset and parallel load.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity counter is

generic (

```

```

width : integer := 4

):

port (

clk,rst,load : in std_ulogic;

: in unsigned(width-1 downto 0);

data

: out unsigned (width-1 downto 0)

count

);

end counter;

architecture behaviour of counter is

begin

process(rst,clk)

variable q : unsigned(width-1 downto 0);

begin

if rst = '1' then

q := (others => '0');

elsif rising_edge(clk) then

if load = '1' then

q := data;

مادم

q := q + 1;

end if;

end if;

count <= q;

end process;

end behaviour;

```

#### 2.6 GHDL

GHDL is a complete free software simulator for VHDL using GCC technology. It works by compiling VHDL files into a binary which simulates, or executes, the design. GHDL is strictly a simulator; it does not do synthesis and it cannot translate a design into a netlist.

Below is an example of how to simulate a simple design with GHDL. The Device Under Test (DUT) is in the file design.vhd and the testbench file is design\_tb.vhd in which the top entity is called design\_tb. A simple testbench is built by instantiating the DUT, generating a sequence of input patterns and comparing the output to what output the system should produce. The synopsys library specified on the command line enables the use of the standard textio package in the testbench, needed for printing diagnostics to the standard ouput, stdout. The first step is to *analyse* the design, the next step is to *elaborate* the design. Note how the name of the entity is used instead of the filename here. The last step is to execute the compiled binary file.

```

$ ghdl -a --ieee=synopsys design.vhd design_tb.vhd

$ ghdl -e --ieee=synopsys design_tb

$ ./design_tb

```

GHDL can also create VCD or GHW files, which may be visually inspected with a waveform viewer such as GTKWave. VCD format files are defined in the Verilog HDL standard which limits its use with VHDL. The GHW format is specially designed for the use with GHDL, enabling inspection of all VHDL datatypes.

```

$ ./design_tb --vcd=dump.vcd

$ ./design_tb --wave=dump.ghw

```

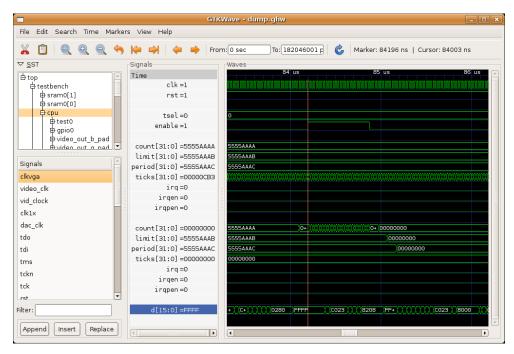

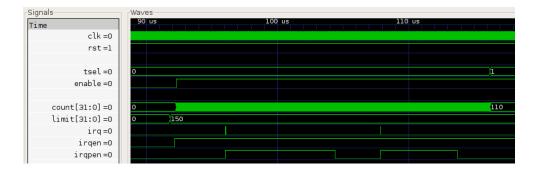

#### 2.7 GTKWave

GTKWave is a fully featured waveform viewer which reads many dumpfile formats, i.e. GHW and VCD, and allows their viewing. GTKWave is developed for Linux, with ports for various other operating systems. Figure 2.4 shows a screenshot of GTKWave, displaying a dumpfile. GTKWave support save files, enabling window and signal display settings to be restored – as shown below.

\$ gtkwave dump.ghw gtkwave.sav

Figure 2.4: A screenshot of GTKWave

### Chapter 3

# System development

This chapter presents the theory of operation of the TMU system and the whole development process; from the choice of host and target platforms to the HDL model of the TMU, hardware simulations and the modifications to the eCos RTOS for TMU support.

#### 3.1 TMU theory of operation

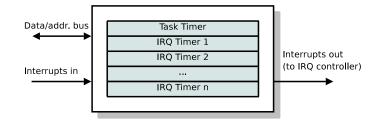

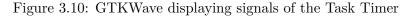

The TMU is a hardware unit that is integrated in, or in close proximity to, the CPU. Its purpose is to measure and control the execution time of both tasks and Interrupt Service Routines (ISR). For each interrupt level the unit has an execution timer called *IRQ Timer* and for the ordinary execution state the unit has a single execution timer called the *Task Timer*, as illustrated in Figure 3.1.

Figure 3.1: A block diagram of the TMU

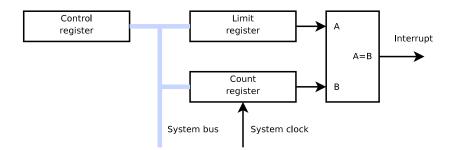

The Task Timer, shown in Figure 3.2, has three processor accessible registers; *count, limit* and *control*. The count register is incremented every clock cycle and compared with the limit register. When they equal, an interrupt is generated, signalling that the current task has exceeded its given budget. The control register manages the interrupt generation capabilities of the timer.

Figure 3.2: A block diagram of the TMU Task Timer

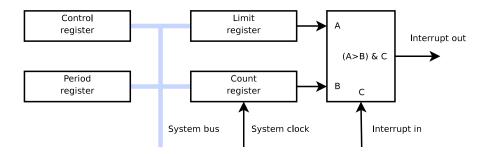

Each IRQ Timer has an extra register, the *period* register, as seen in Figure 3.3. The period register stores the interval at which the count register shall be cleared. Thus, the IRQ Timers support the DS algorithm presented in section 2.3.4 by replenishing the execution budget at regular intervals. Actually, the IRQ Timer requires another register too, the *ticks* register. Ticks always increments and is compared with the period register, but is not accessible to the processor. When ticks and period equals, both ticks and count will be cleared. Interrupt signals previously connected directly to the IRQ controller are routed via the IRQ Timers. While there is execution budget left, all IRQ signals are passed through. But when the budget is spent, no more signals will pass until the next replenish period.

Figure 3.3: A TMU IRQ Timer block diagram

The TMU also has a *configuration* register and a *timer select* register. The configuration register has a global enable bit for the TMU and some read only information about the current implementation, helping software determine its underlying platform. The timer select register sets the active TMU timer and is controlled by software. Only one timer is running at any given time.

Count, limit and period registers are preferably 64-bit wide, but may be less. The minimum register width is the one with a register overflow period of more than the longest relative deadline for any task in the system.

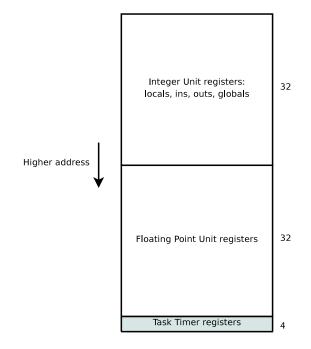

#### 3.1.1 OS support for the TMU

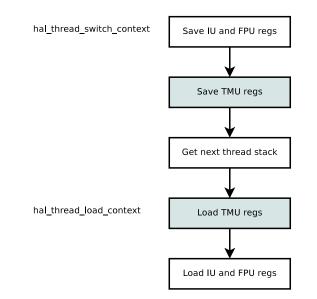

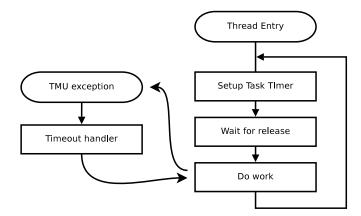

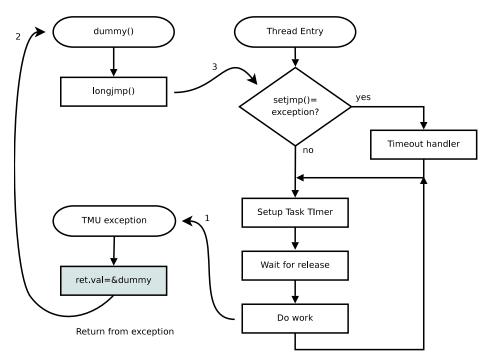

The TMU must be incorporated into the Operating System (OS) for proper handling. The Task Timer registers shall become a part of the task, or thread, context. That is the count, limit and control registers of the Task Timer. That way, all threads share the same hardware timer, but are under the impression of having their own timer. The following operations must be performed by the OS:

- When a thread is created, default values for the TMU registers must be provided.

- During a context switch, the OS must save the current threads TMU registers to the threads stack, and load the next threads TMU registers from its stack and into the TMU hardware.

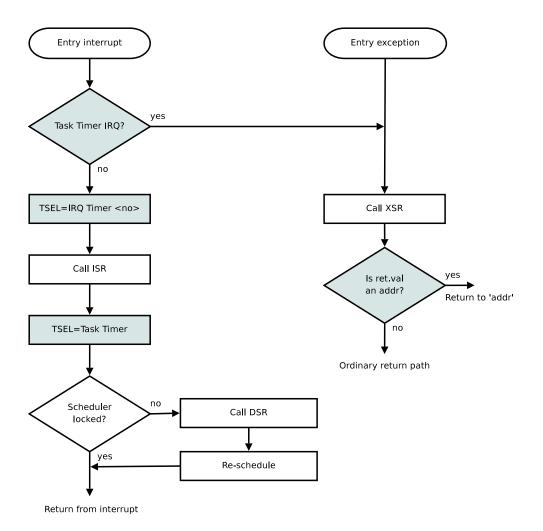

- When an interrupt occurs, the OS must change the active timer of the TMU to that of the corresponding interrupt by writing to the Timer Select register. And when the Interrupt Service Routine (ISR) has completed, the Timer Select register must be written again to reselect the Task Timer.

Further, a suitable Application Programming Interface (API) to the TMU must be provided by the system for application program use.

#### 3.2 TMU implementation alternatives

The objective is to find the implementation giving the lowest overhead, but at the same time is flexible enough to allow the TMU being implemented with various processor architectures.

#### 3.2.1 Peripheral device

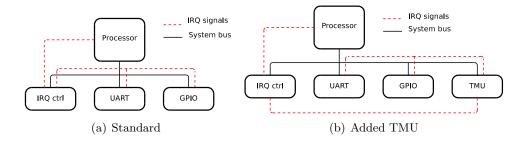

For a System-on-Chip (SoC), functions such as timers, General Purpose Input/Output (GPIO), system timers and UARTs are commonly known as peripheral devices. These devices are on the same chip as the CPU and are accessed through a system bus. Being a peripheral device, the TMU benefits of the standardised system bus and processor architecture independence. On the negative side, accessing a device through a bus means slower access times.

#### 3.2.2 Coprocessor

A coprocessor is a processor that operates under the supervision of the primary processor, the CPU. Typically, it has no means of accessing memory without the use of the CPU and it supports a limited instruction set. The purpose of a coprocessor is to alleviate the CPU load by handling some computational intensive tasks. Typical application areas are floating point arithmetic, graphics and signal processing. As for the TMU, being implemented as a coprocessor means tight integration with the CPU. This shortens the register access times and gives high flexibility as the coprocessor has its own instruction set. On the other hand, many systems only allow for a single coprocessor, and thus using the TMU comes at the expense of other coprocessor functions. Further, the TMU has no benefit of having its own instruction set, and it does not do anything computational intensive; it only counts and compares its registers. Additionally, the coprocessor interface is architecture specific and would make it harder to implement the TMU on other processor systems.

#### 3.2.3 Register File

The register file is a set of registers that the CPU uses for temporarily storing data. These registers are addressed by the operand fields of processor instructions which are defined by the Instruction Set Architecture (ISA) for that particular architecture. Since the registers are addressed in the instruction itself, it is the fastest memory access times of the computer memory hierarchy. Because the register file is closely related to the ISA, adding registers to the register file means expanding the ISA. In turn, the assembler for the given architecture has to be modified to support the new instruction format, making it an intrusive approach. Thus, implementing the TMU inside the register file means that the ISA and assembler have to be modified, making it a highly architecture specific and complicated implementation.

#### 3.2.4 Chosen implementation

Based on the above given aspects of the various TMU implementations, the decision fell on peripheral device implementation. As a peripheral device, the TMU is very easy to implement compared to the coprocessor and register file alternatives. It also means that the TMU will be easy to adapt to new systems and architectures. There is no need to modify the compiler/assembler or in any way modify the ISA. The only negative side is that accessing the device through a bus means slower access times.

#### 3.3 Host development platform

The host development platform is a standard desktop computer with a parallel port for FPGA programming and a serial port or ethernet port for communicating and debugging the target. Linux is opted as the host platform OS because it is a convenient platform for development with GNU tools. Using GNU tools on MS Windows often involve programs like Cygwin or MinGW, emulating a UNIX environment. The Ubuntu 7.04 Linux distribution was used as the host OS.

To be utilised as a development platform, additional software must be installed on the host. The following sections describe the installation procedure of the basic tools used throughout this project.

### 3.3.1 Installation of Xilinx software and cable drivers

A user account was created at the Xilinx home page, http://www.xilinx. com, before the download of the Xilix WebPACK could take place. When the download had finished, the installer was started like this:

```

$ cd /path/to/dl/

$ unzip <name>.zip

$ cd <name>

$ sudo ./setup

```

When using Xilinx JTAG software like Impact, Chipscope and XMD on Linux, the proprietary kernel module windrvr from Jungo is needed to access the parallel- or USB-cable. As this module does not work with current linux kernel versions (versions above 2.6.18) a library was developed by users on the Internet, which emulates the module in userspace and allows the tools to access the JTAG cable without the need for a proprietary kernel module. Thus, "Install cable drivers" in the install procedure was deselected and the third-party cable driver was installed instead. The cable driver was downloaded from http://rmdir.de/~michael/xilinx/. and is called *libusb-driver*.

The library was built like this:

```

$ cd /path/to/dl/

$ tar xzf usb-driver-HEAD.tar.gz

$ cd usb-driver

$ make

```

The built library is named libusb-driver.so and exists in the working directory. Although the library is called lib*usb*, it also handles the parallel programming cables.

The Xilinx software depends on several environment variables defined in the file settings.sh in the installation directory. settings.sh must be sourced in the shell before starting any Xilinx utility. The example below starts Xilinx ISE Project Navigator.

```

$ source /path/to/Xilinx92i/settings.sh

$ ise

```

When using the FPGA download utility Impact, the path to libusb-driver.so must be set:

\$ su

\$ source /path/to/Xilinx92i/settings.sh

\$ export LD\_PRELOAD=/path/to/libusb-driver.so

```

$ impact

```

Note that using the cable drivers requires root privileges by default. Ordinary user access to the parallell port device used for FPGA programming was enabled by adding the user to the "lp" group:

\$ sudo usermod -a -G lp username

When trying to program the FPGA with iMPACT, the error "Programming failed" and "DONE did not go high" appeared. This was fixed by setting the option "Use HIGHZ" instead of "BYPASS" in Edit  $\rightarrow$  Preferences  $\rightarrow$  iMPACT  $\rightarrow$  Configuration Preferences.

Now, most of the Xilinx IDE was running correctly, but when trying to run i.e. Floorplanner, the following error appeared:

```

$ floorplanner

Wind/U X-toolkit Error: wuDisplay: Can't open display

```

This behaviour was corrected by setting the environment variable DISPLAY to :0.

To sum up, the following entries were added to the shell resource file<sup>1</sup> after installation of the Xilinx WebPACK, so that all utilities would work.

```

source /path/to/Xilinx92i/settings.sh

export LD_PRELOAD=/path/to/libusb-driver.so

export DISPLAY=:0

```

# 3.3.2 GHDL

The VHDL simulator GHDL can be installed through the package management system of Ubuntu:

```

$ sudo apt-get install ghdl

```

# 3.3.3 GTKWave

The waveform viewer GTKWave can be installed through the package management system of Ubuntu:

```

$ sudo apt-get install gtkwave

```

# 3.4 FPGA development board

There are two market leading FPGA manufacturers, Xilinx and Altera. Both provide free tools for MS Windows platforms. Xilinx also provide free development tools for Linux, while Linux tools from Altera must be purchased.

<sup>&</sup>lt;sup>1</sup>The shell resource file is named, on Ubuntu systems at least, .bashrc, and exists in the home directory of the user

Because Linux has been chosen as the host platform OS, Xilinx FPGA development boards were opted. In the next sections, the following Xilinx boards will be presented:

1. Spartan-3 Starter Board

This board was readily available at project start and was subject to the first implementation tests, presented in the next section.

2. Spartan-3A DSP 1800A Development Board

This board was ordered when it became clear that the first board had insufficient resources. As the supplier could not deliver the board in time, no actual implementation was performed on this platform. But while the order was being processed, an implementation was prepared and simulations were performed.

3. Virtex-4 ML401 Evaluation Platform This board was obtained when the supplier of the Spartan-3A DSP 1800A Development Board could not deliver in time. The Virtex-4 ML401 Evaluation Platform is the board in which the final design is implemented.

### 3.4.1 Spartan-3 Starter Board

The Spartan-3 Starter Board, Figure 3.4, was readily available at project start and was subject to the first implementation tests. As will be discussed in this text, the board was an unsuitable platform for testing the TMU and another board had to be obtained.

Figure 3.4: Xilinx Spartan-3 Starter Board, source http://www.xilinx.com

The Xilinx Spartan-3 Starter Board features:

- Xilinx Spartan-3 XC3200 FPGA with 1 920 slices<sup>2</sup>, 30 Kib distributed RAM and 216 Kib of block RAM

- On-board 2 Mib Platform Flash (XCF02S)

- 8 slide switches, 4 pushbuttons, 9 LEDs, and 4-digit seven-segment display

- Serial port, VGA port, and PS/2 mouse/keyboard port

- 1 MiB<sup>3</sup> on-board 10ns SRAM (256 Kib<sup>4</sup> x 32)

- Three 40-pin expansion connectors

#### Trying out an 8-bit soft-core processor

The idea behind the first implementation attempt was to keep the system as simple as possible, finding a good match of an 8-bit soft-core MCU running a suitable RTOS in which the TMU could be embedded. Table 3.1 shows a selection of 8-bit MCU IP cores found through OpenCores [24] and the Internet. Listed compilers and RTOSs are also free. Note that the quality of cores found on the Internet varies greatly. Some cores are totally equivalent to a particular device, implementing the same instruction set and set of peripherals, while others are only partially compatible, either lacking some peripheral devices, not implementing the full instruction set or have not been tested in hardware. The cores listed below provide an acceptable quality standard, suitable for implementation in an FPGA.

Table 3.1: A selection of free 8-bit MCU IP cores

| Arch. | Name     | Compatible | HDL     | Compiler | RTOS     |

|-------|----------|------------|---------|----------|----------|

| AVR   | avr_core | ATmega103  | VHDL    | GCC      | FreeRTOS |

| 8051  | 8051     | -          | Verilog | SDCC     | FreeRTOS |

| PIC16 | CQPIC    | PIC16F84   | VHDL    | $SDCC^1$ | -        |

| PIC18 | ae18     | PIC18      | Verilog | $SDCC^1$ | FreeRTOS |

Of these cores, the AVR Core was chosen because of its support by the well known GCC compiler and that it has been thoroughly tested. The AVR Core is written by Ruslan Lepetenok in synthesisable VHDL and is an Atmel ATmega103 equivalent device, having the same instruction set and instruction timing. The core features 32 8-bit general purpose registers, 23 interrupt vectors and support for up to 128 KiB of program and up to 64 KiB of data

$<sup>^2 \</sup>mathrm{On}$  Spartan-3 architectures: 1 CLB = 4 slices = 8 LUTs

$<sup>^{3}</sup>$ mebibyte =  $2^{20}$  bytes = 1,024 kibibytes (MiB)

$<sup>{}^{4}</sup>$ kibibit =  $2^{10}$  bits = 1,024 bits (Kib)

<sup>&</sup>lt;sup>1</sup>SDCC support for PIC16 and PIC18 MCUs is a work in progress as of March 2008

memory. It also has a programmable UART, two 8-bit timers, eight external interrupt sources and two 8-bit parallell ports.

The AVR Core is supported by FreeRTOS – a minimal RTOS featuring:

- Multitasking capabilities

- Preemptive, cooperative and hybrid kernel configuration options

- Support for co-routines

- Intertask communication and synchronisation

- Priority inheritance

- Scalable

FreeRTOS is licensed under a modified GPL and can be used in commercial applications under this license, without having to open source user application code.

A new project in the Xilinx ISE Project Navigator was created and all AVR Core VHDL files were copied into the project. The program memory of the AVR Core is hardcoded in the file PROM.vhd, and must be specified before the design can be synthesised. The AVR Core distribution comes with an utility called, hex2vhd, reading Intel Hex format files and generating a PROM VHDL entity in a file named PROM.vhd containing the program instructions and static data. An example of compiling a program for the AVR Core and generating PROM.vhd is shown below.

```

$ avr-gcc -mcall-prologues -mmcu=atmega103 -Os -g prog.c -o prog.elf

$ avr-objcopy -j .text -O ihex prog.elf prog.hex

$ hex2vhd prog.hex

```

avr-gcc and avr-objcopy is a part of the AVR development tools that was installed through the package management system of Ubuntu:

```

$ sudo apt-get install avr-libc binutils-avr \

> gcc-avr gdb-avr simulavr

```

Having specified the location of the generated PROM. vhd in Project Navigator, the design can be implemented. Test programs were written, testing the parallel ports by flashing LEDs and writing to the UART. These test programs can be found in Appendix A. When building the FreeRTOS demo design, updating PROM. vhd and implementing the design, it became clear that the generated bit-file was too big for the XC3S200 FPGA. Thus, an implementation of the TMU with an RTOS for proper testing would be impossible. Even if the design could fit into the FPGA, the AVR Core has no debug unit, making single stepping through programs impossible. Also, the process of updating the PROM memory with a new program takes a significant amount of time, as the FPGA design cycle has to be performed each time.

#### Instantly updating block RAM contents in a .bit file

In designs like the AVR Core, the contents of the program memory is hardcoded into a HDL file. When loading a new program, the whole FPGA design flow has to be performed. This process is very time consuming, and when only the memory contents of a design is changing, it is also unnecessary. Xilinx provide a tool called Data2Mem, which decreases development time by orders of magnitude by directly replacing block RAM data in bit files without the intervention of any other Xilinx implementation tools.

Data2Mem needs a .bmm (Block Memory Map) file to direct the translation of data into the proper initialisation form. A .bmm file is a text file that has syntactic descriptions of how individual Block RAMs constitute a contiguous logical data space. However, as Data2Mem is a part of Xilinx automated design flow for embedded processors, proper syntax of the .bmm file is poorly documented for stand-alone use. As a result, usage of this tool failed.

# 3.4.2 Spartan-3A DSP 1800A Development Board

As the XC3S200 FPGA on the Spartan-3 Starter Board had too little resources, a new development board was ordered. Although the supplier could not deliver the board in time, and the Virtex-4 ML401 Evaluation Platform was used for the implementation, the board is still presented here. The time between ordering the board and obtaining the Virtex-4 ML401 Evaluation Platform was spent simulating and preparing a LEON3 design for actual implementation on the Spartan-3A DSP 1800A Development Board. Because there was no demo design in GRLIB for this board, a lot of time was spent on making one. The Spartan-3A DSP 1800A development board, Figure 3.5, features:

- Spartan-3A XC3SD1800A DSP FPGA with 16 640 slices, 260 Kib distributed RAM and 1 512 Kib of block RAM

- 128 MiB DDR2 SDRAM (32 Mib x 32), 16 Mib x 8 parallel flash, 64 Mib SPI serial flash

- 10/100/1000 Ethernet PHY

- RS232 serial port

- Video RGB Port

- 8 user LEDs, 8-position user DIP switch, 4 user push button switches, reset push button switch

- JTAG programming/configuration port

Figure 3.5: Xilinx partan-3A DSP 1800A Development Board, source http: //www.xilinx.com

# 3.4.3 Virtex-4 ML401 Evaluation Platform

As the XC3S200 FPGA on the Spartan-3 Starter Board had too little logic resources, another development board was obtained. The Virtex-4 ML401 Evaluation Platform, Figure 3.6, featuring:

Figure 3.6: Xilinx Virtex-4 ML401 Evaluation Platform, source http://www.xilinx.com

• Xilinx Virtex-4 XC4VLX25 FPGA with 10 752 slices, 168 Kib distributed RAM and 1 296 Kib of block RAM

- 64 MiB DDR SDRAM, 8 Mib ZBT SRAM, 64 Mib Flash, 4 kb I<sup>2</sup>C EEPROM

- 16-character x 2-line LCD

- General purpose DIP switches LEDs, and push buttons

- Stereo AC97 audio codec with line-in, line-out, 50-mW headphone, and microphone-in (mono) jacks

- RS-232 serial port

- USB Ports (2 Peripheral/1 Host)

- VGA port with 24-bit video DAC

- PS/2 mouse and keyboard connectors

- On-board 32 Mib Platform Flash (XCF32P)

- System ACE CompactFlash controller with Type I/II CompactFlash connector for FPGA configuration from CF-cards

# **3.5** Soft-core processor alternatives

The 8-bit AVR Core MCU test proved to be a difficult development platform, as discussed in Section 3.4.1. In the second design, larger processors with debug facilities and rapid program downloading functionalities was opted. Table 3.2 lists a selection of free 32-bit soft-core processors suitable for implementation. As before, listed processors and RTOSs are free and all architectures use the GCC. All processors are supported by Linux and uClinux, but as they have poor real-time capabilities, only RTOSs are listed.

| Name     | ISA        | HDL     | RTOS        |

|----------|------------|---------|-------------|

| LEON     | SPARC V8   | VHDL    | RTEMS, eCos |

| OpenRISC | OpenRISC   | Verilog | RTEMS       |

| AEMB     | MicroBlaze | Verilog | FreeRTOS    |

Table 3.2: A selection of free 32-bit soft-core processors

## 3.5.1 LEON

The LEON processor is a 32-bit synthesisable processor core written in VHDL based on the SPARC V8 architecture. The core is highly configurable, and particularly suitable for System-on-Chip (SoC) designs. The LEON3 core is a newest implementation of the LEON family, with a 7 stage integer pipeline

and multi-processor support. It is distributed as part of the GRLIB IP library under the GNU GPL.

# 3.5.2 OpenRISC

OpenRISC, or more specifically OpenRISC 1000, is a processor family based on an open source 32/64-bit RISC ISA design by the OpenCores team [24] released under the GNU Lesser General Public License (LGPL). The only finished implementation is the 32-bit OpenRISC 1200 which is a 32-bit scalar RISC with Harvard microarchitecture, 5 stage integer pipeline and virtual memory support (MMU), written in Verilog HDL. Being Wishbone compliant<sup>5</sup>, OpenRISC will easily integrate with many other open source cores that use the same open bus specification.

### 3.5.3 AEMB

The AEMB is an open source 32-bit microprocessor core written in Verilog HDL. It is instruction compatible with the Xilinx Microblaze and comes with several architectural enhancements. It will easily run C/C++ code and has been independently proven in hardware. AEMB is Wishbone compliant and will easily integrate with many other open source cores that use the same open bus specification. The AEMB core is fully parameterisable, without using any unwieldy define files. This includes the address space and optional functional units, such as the barrel-shifter and multiplier. This allows customisation in the design without having to make any changes to the original AEMB files.

#### 3.5.4 Chosen soft-core processor

Of the given processors, LEON3 was chosen as it seemed to be the easiest processor to start out with, having a large user base, lots of peripherals, included testbench and demo designs for many FPGA boards. Also, Kjetil Svarstad, a professor dealing with system level design and analysis of digital systems at NTNU, recommended it.

# **3.6 RTOS alternatives**

Suitable RTOSs for the LEON3 soft-core processor are RTEMS and eCos, as listed in Table 3.2. Both are presented here before the choice is made.

<sup>&</sup>lt;sup>5</sup>Wishbone is an open bus standard for SoC designs

#### **3.6.1 RTEMS**

RTEMS (Real-Time Executive for Multiprocessor Systems) is a free open source RTOS designed for embedded systems. RTEMS is designed to support various open API standards including POSIX and uITRON. The basic features of the RTEMS kernel include:

- Multitasking capabilities

- Event-driven, priority-based preemptive scheduling

- Optional rate-monotonic scheduling

- Intertask communication and synchronisation

- Priority inheritance

- Dynamic memory allocation

- High level of user configurability

Additionally, RTEMS provide networking, filesystems and debugging support.

RTEMS is distributed under a modified GPL licence, allowing linking RTEMS objects with other files without requiring the full executable to be covered by the GPL. This license is based on the GNAT Modified General Public License with the language modified to not be specific to the Ada programming language.

### 3.6.2 eCos

Embedded Configurable Operating System, or eCos, is an open source Real-Time Operating System (RTOS) intended for embedded and real-time systems.

It can be customised to precise application requirements, with hundreds of options, delivering the best possible run-time performance and minimised hardware needs. It is written in the C and C++ programming languages, and its standard application interface is C. eCos also has compatibility layers and APIs for POSIX and uITRON. eCos was designed for devices with memory size in the tens to hundreds of kilobytes, and it can be used on hardware with too little RAM to support embedded Linux, which currently needs a minimum of about 2 MiB of RAM, not including application and service needs. The basic features of the eCos kernel include:

- Multitasking capabilities

- Event-driven, priority-based preemptive scheduling choose between the bitmap scheduler and the multi-level queue (MLQ) scheduler

- Intertask communication and synchronisation

- Priority inheritance and priority ceiling protocol

- Integration with the system's support for interrupts and exceptions

- High level of user configurability

eCos also provide device drivers, filesystem support and network capabilities. eCos is distributed under the GPL license with an exception which permits proprietary application code to be linked with eCos without itself being forced to be released under the GPL. It is also royalty and buyout free.

### 3.6.3 Chosen RTOS

Both RTEMS and eCos seemed like equally good alternatives, but only one could be chosen. eCos was chosen as the system RTOS because it is highly configurable and simple, both important aspects when implementing the TMU.

# 3.7 LEON3 development tools

### 3.7.1 GRLIB IP Library

GRLIB is a collection of reusable IP cores distributed under GNU GPL. It is based on the AMBA AHB and APB on-chip buses, which is used as the standard interconnect interface. The implementation of the AHB/APB buses is compliant with the AMBA-2.0 specification [1], with additional "sideband" signals for automatic address decoding, interrupt steering and device identification. The AHB and APB signals are grouped according to functionality into VHDL records, declared in the GRLIB VHDL library. All GRLIB cores use the same data structures to declare the AMBA interfaces, and can then easily be connected together.

GRLIB is downloaded from the home page of Gaisler Research, http://www.gaisler.com. It can be installed anywhere, just extract the downloaded archive:

\$ tar xzvf grlib-gpl-1.0.17-b2710.tar.gz

# 3.7.2 GRMON debug monitor

GRMON is a general debug monitor for the LEON processor, and for SoC designs based on the GRLIB IP library. GRMON features:

- Read/write access to all system registers and memory

- Built-in disassembler and trace buffer management

- Downloading and execution of LEON applications

- Breakpoint and watchpoint management

- Remote connection to GNU debugger (gdb)

- Support for USB, JTAG, RS232, PCI, Ethernet and SpaceWire debug links

GRMON can be run in stand-alone mode, or connected through a network socket to the GNU GDB debugger. In stand-alone mode, a variety of debugging commands are available to allow manipulation of memory contents and registers, breakpoint/watchpoint insertion and performance measurement. Connected to GDB, GRMON acts as a remote target and supports all GDB debug requests. The communication between GDB and GRMON is performed using the GDB extended-remote protocol.

GRMON is released under both a professional and an evaluation license. The evaluation version may be used during a limited period without purchasing a license. GRMON can be downloaded from http://www.gaisler.com. Untar the download and add the the path to the GRMON executable in the search path:

```

$ tar xzvf grmon-eval-1.1.27b.tar.gz

$ echo "export PATH=/path/to/grmon-eval/linux:$PATH" >> $HOME/.bashrc

```

# 3.7.3 TSIM LEON simulator

TSIM is an instruction-level simulator capable of emulating LEON-based computer systems. TSIM features:

- Accurate and cycle-true emulation

- High performance: up to 30 MIPS on high-end PC (Xeon@3.2GHz)

- Standalone operation and remote connection to GNU debugger (gdb)

- Instruction trace buffer

- Stack backtrace with symbolic information

- Unlimited number of breakpoints and watchpoints

TSIM can be downloaded from http://www.gaisler.com and installed like this:

```

$ tar xzvf tsim-eval-2.0.10.tar.gz

$ echo "export PATH=/path/to/tsim-eval/tsim/linux:$PATH" >> $HOME/.bashrc

```

TSIM can be run in stand-alone mode, or connected through a network socket to the GNU GDB debugger. It acts very similarly to the GRMON debugger and has a variety of debugging commands allowing manipulation of memory contents and registers, breakpoint/watchpoint insertion and performance measurement.

A stand-alone TSIM session:

\$ tsim-leon3 tsim> load hello tsim> go resuming at 0x40001114 Hello, eCos world!

A session with TSIM and gdb, using two terminals: Terminal 1:

\$ tsim-leon3 -gdb

gdb interface: using port 1234

connected

Hello, eCos world!

#### Terminal 2:

```

$ sparc-elf-gdb