# Interconnection of an Isolated Power System to an External Power Supply

- Dimensioning, modelling and control

# Ferdinand Meltzer Dahl

Master of Energy and Environmental Engineering Submission date: June 2014 Supervisor: Lars Einar Norum, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

# Preface

This master thesis concludes my five-year master degree in Energy and Environmental engineering. Throughout the work with this thesis, I have used much of what I have learned at my time at the Norwegian University of Science and Technology. I have also gained new and deeper understanding of the dynamics in power systems, converter control, faults and fault protection.

First, and foremost, I would like to thank my supervisor, Professor Lars Einar Norum at the Department of Electric Power Engineering at the Norwegian University of Science and Technology for guidance and advice throughout the semester. I would also like to thank my co-supervisor, Espen Haugan at Siemens, and Sverre Skaldeberg Gjelde at Siemens for help defining the task, and guidance throughout the semester.

Special thanks are given to Santiago Sanchez Acevedo at NTNU and Jon Are Suul at SINTEF for help with converter control related issues.

Ferdinand Meltzer Dahl

Trondheim, June 2014

# Abstract

In this master thesis, a possible solution on how to connect a jack-up rig to an external supply was proposed. Using a conceptual layout of a typical jack-up rig power system as the basis, a suitable solution was proposed. The solution consists of a three winding transformer, and a frequency changer consisting of a twelve pulse rectifier and a voltage source converter. The frequency changer was needed because of the different frequencies on the supply and jack-up rig systems. In addition, filters, and a simple overcurrent protection relay were designed. After presenting the theoretical basis for the design of the components, a model was made in Matlab/Simulink to test and verify the solution.

It was assumed that the external supply was a stiff network, and the external supply was therefore modelled as a voltage source. The external supply supplies the jack-up rig through a sub-sea cable with voltage of 36 kV and frequency of 50 Hz. A simple RL equivalent was used to model this based on a suitable cable from Nexans. The twelve-pulse rectifier model was made using two premade six-phase rectifiers in Simulink connected in series. This to minimize DC link ripple. The DC link filter was dimensioned analytically with respect to allowed current and voltage ripple and the resulting values were inductance, L = 13.63 mH and, capacitance, C = 1.2 mF.

A two level voltage source converter was used to convert DC to AC at the desired 60 Hz frequency. The control system was based on proven methods using a cascaded control structure with an outer voltage control loop, and an inner current control loop. The control was performed in the d-q reference frame allowing the use of PI controllers. These were tuned using the pole placement technique.

The inverter output filter was tuned to attenuate the dominant inverter induced harmonics. A cut-off frequency of  $\omega_o$ = 1257 [rad/s], with inductance, *L* = 6.3 mH, and capacitance, *C* = 100.36 µF proved to give good attenuation.

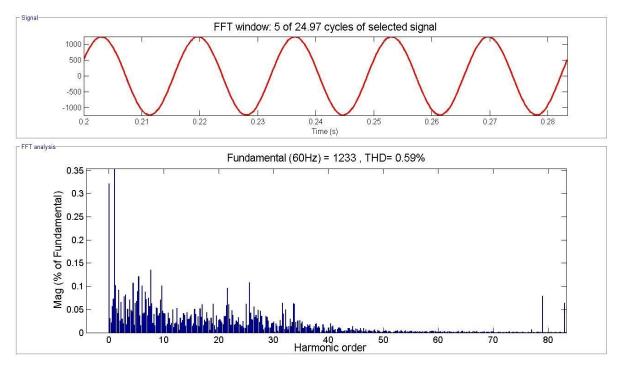

All steady state simulations proved successful with respect to harmonic distortion, voltage level and frequency. The largest load side THD was the current THD on the HV switchboard. This was 0.59 %. The supply line current THD at nominal load was 9.28 % due to the twelve pulse rectifiers and the lack of a filter.

During simulations of different load scenarios, step changes in load caused a maximum voltage dip of 20 V, and a current overshoot in one of the phases of about 1500 A. Using a linear ramp load instead, with a change in load power,  $\frac{dP}{dt} = \pm 6$  MW/s, and reactive power change,  $\frac{dQ}{dt} = \pm 4$  MVAr/s the supply followed perfectly, without any transients.

Fault simulations were done with a three-pole short circuit on different places on the jack-up AC side, and a bolted pole-to-pole short circuit of the DC link. None of the faults at the load islands caused any overcurrent in the interconnection. The largest being 159.2 kA at the inverter terminals. The initial peak fault currents during jack-up AC side fault simulations was caused by the inverter filter capacitors. A short circuit of the inverter switches proved critical. This yielded a peak fault current of 747 kA, and would destroy the inverter switches. The short

circuit on the DC link had a peak current of 23 kA, and would probably destroy the rectifier diodes. The overcurrent protection relays used proved successful in interrupting the fault currents, and selectivity was maintained.

Studying the results, it is apparent that the proposed solution works during normal operation, but that a multilevel converter should be used instead to minimize filter capacitors and thereby peak fault currents.

# Sammendrag

I denne masteroppgaven ble en mulig løsning på hvordan en jack-up rig kan kobles til en ekstern kraftforsyning foreslått. Ved å ta utgangspunkt i hvordan et kraftsystem på en typisk jack-up rig ser ut, ble en passende løsning foreslått. Løsningen består av en tre-viklings transformator, og en frekvensomformer bestående av en tolv-puls likeretter og en vekselretter. Det var nødvending med en frekvensomformer grunnet ulik frekvens på den eksterne kilden, og jack-upen. I tillegg ble ett enkelt overstrøms relé, og filtre dimensjonert og designet.

Etter at det teoretiske grunnlaget for oppgaven ble presentert, ble en modell av den foreslåtte løsningen laget i Matlab/Simulink for å kunne teste og verifisere løsningen.

Det ble antatt at den eksterne forsyningen hadde ett stivt nett, og denne ble derfor modellert som en spenningskilde. Den eksterne forsyningen forsyner jack-upen gjennom en undervannskabel med et spenningsnivå på 36 kV, og frekvens 50 Hz. Kabelen ble modellert som en RL ekvivalent, basert på en passende kabel fra Nexans. En modell av en tolvpulslikeretter ble laget ved bruk av to ferdiglagde sekspulslikerettere koblet i serie. Tolv pulser ble brukt for å minimere rippel på DC skinnen. Filteret på DC skinnen ble dimensjonert analytisk med hensyn på tillatt strøm og spennings rippel. De resulterende verdiene var: induktans, *L* = 13.63 mH og kapasitans, *C* = 1.2 mF.

En to-nivå spenningskildeomformer ble benyttet for å konvertere DC til 60 Hz AC. Kontrollsystemet var basert på velutprøvde metoder, med en ytre spenningskontroll løkke, og en indre strømkontroll løkke. Kontrollen ble foretatt i et d-q referanse system slik at PI regulatorer kunne brukes. Regulatorene ble stilt inn ved bruk av pol plassering.

Utgangsfilteret på vekselretteren ble stilt inn for å fjerne de mest dominante harmoniske ordner fra vekselretteren. En knekkfrekvens på  $\omega_o$ = 1257 [rad/s], med induktans *L* = 6.3 mH, og kapasitans, *C* = 100.36 µF gav god dempning.

Alle simuleringer der systemet var i stabil tilstand var suksessfulle med hensyn på harmonisk forvrengning, spenningsnivå og frekvens. Den største THD observert på lastsiden var i strømmen på høyspenningstavlen, med en THD = 0.59 %. I tilførsel kabelen var det en strøm THD = 9.28 %. Dette skyldes tolvpulslikeretteren samt mangelen av et filter.

I løpet av simuleringene med forskjellige lastscenarier førte en stegendring av lasten til en spenningsdypp på 20 V, og en overstrøm på rundt 1500 A. Under simularing av en lineær rampelast, med en endring i lasteffekt på  $\frac{dP}{dt}$  = ± 6 MW/s, og endring i reaktiv lasteffekt på  $\frac{dQ}{dt}$  = ± 4 MVAr/s, greide forsyningen å forsyne lasten tilfredstillende, og uten transienter.

Feilsimuleringer ble gjort med en trepolet kortslutning på forskjellige steder i jack-up riggens AC system, og en kortslutning av DC skinnene i frekvensomformeren. Ingen av feilene på lastøyene førte til noe overstrøm i sammenkoblingen. Den største feilstrømmen var på 159.2 kA ved en kortslutning på terminalene til vekselretteren. Den initiale strømtoppen ved feil på AC systemet skyldes filterkondensatorene på utgangen av vekselretteren. En kortslutning av vekselretterbryterene viste seg å være kritisk. Dette førte til en strømtopp på 747 kA, noe som ville ødelagt bryterne. Kortslutningen på DC skinnen hadde en strømtopp på 23 kA, og ville sannsynligvis ødelagt diodene i likeretteren. Overstrømsvernene viste seg suksessfulle, og greide å bryte feilstrømmene. Selektivitet var også ivaretatt.

Ved å studere resultatene er det åpenbart at den foreslåtte løsningen fungerer som tiltenkt under normal drift. En fler-nivå omformer burde dog brukes for å minimere filterkondensatorene og dermed strømtopper ved feil.

# Table of Contents

| 1 | Intr | oduc  | tion                                                                 | 1  |

|---|------|-------|----------------------------------------------------------------------|----|

|   | 1.1  | Mot   | tivation for Work                                                    | 1  |

|   | 1.2  | Pro   | blem Description                                                     | 1  |

|   | 1.3  | Lim   | itations of Work                                                     | 1  |

| 2 | The  | oreti | ical Background                                                      | 3  |

|   | 2.1  | Jack  | c-up Rigs                                                            | 3  |

|   | 2.2  | Jack  | -up Rig Loads                                                        | 3  |

|   | 2.3  | Exte  | ernal Power Supply                                                   | 3  |

|   | 2.4  | Sub   | sea Cable                                                            | 4  |

|   | 2.5  | Trar  | nsformers                                                            | 4  |

|   | 2.5. | 1     | Two Winding Transformer                                              | 4  |

|   | 2.5. | 2     | Three Winding Transformer                                            | 5  |

|   | 2.6  | Syst  | em Description                                                       | 6  |

|   | 2.7  | Inte  | rconnecting an External Power Supply to the Jack-up Rig Power System | 8  |

|   | 2.7. | 1     | Interconnection Topology                                             | 8  |

|   | 2.7. | 2     | Twelve Pulse Series Connected Rectifier                              | 8  |

|   | 2.7. | 3     | DC Link Filter Inductor                                              | 9  |

|   | 2.7. | 4     | DC Link Filter Capacitor                                             | 9  |

|   | 2.7. | 5     | Inverter                                                             | 9  |

|   | 2.7. | 6     | Inverter Output Low Pass LC Filter                                   | 17 |

|   | 2.7. | 7     | Faults                                                               | 18 |

|   | 2.7. | 8     | Fault Protection                                                     | 19 |

|   | 2.7. | 9     | Selectivity                                                          | 20 |

|   | 2.8  | Har   | monics                                                               | 20 |

| 3 | Syst | tem l | Nodelling                                                            | 22 |

|   | 3.1  | Exte  | ernal Power Supply Modelling                                         | 22 |

|   | 3.2  | Sub   | sea Cable Modelling                                                  | 22 |

|   | 3.3  | Inte  | rconnection Topology                                                 | 22 |

|   | 3.4  | Jack  | -up Rig Cables                                                       | 23 |

|   | 3.5  | Thre  | ee Winding Transformer Model                                         | 23 |

|   | 3.6  | Twe   | elve Pulse Rectifier                                                 | 23 |

|   | 3.7  | DC I  | Link Filter Inductor Model                                           | 24 |

|   | 3.8   | DC I   | ink filter Capacitor Model         | 24 |

|---|-------|--------|------------------------------------|----|

|   | 3.9   | DC I   | ink Voltage Level                  | 24 |

|   | 3.10  | Volt   | age Source Converter Model         | 25 |

|   | 3.10  | ).1    | IGBT Valves Simulink Model         | 25 |

|   | 3.10  | ).2    | Switching Frequency                | 25 |

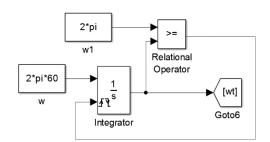

|   | 3.10  | ).3    | Frequency Generator Simulink Model | 26 |

|   | 3.10  | ).4    | Inverter Output LC filter          | 26 |

|   | 3.11  | Two    | Winding Transformer                | 26 |

|   | 3.12  | Load   | d                                  | 27 |

|   | 3.13  | Fau    | lt Modelling                       | 27 |

|   | 3.14  | Faul   | It Current Protection Relay Model  | 29 |

|   | 3.15  | Coo    | rdination of Protection            | 29 |

| 4 | Res   | ults f | rom Simulations in Matlab/Simulink | 31 |

|   | 4.1   | VSC    | Control System Verification        | 31 |

|   | 4.2   | Stea   | ady State System Verification      | 31 |

|   | 4.2.  | 1      | DC Link Voltage                    | 31 |

|   | 4.2.  | 2      | HV Switchboard Voltage             | 32 |

|   | 4.2.  | 3      | HV Switchboard Current             | 33 |

|   | 4.2.  | 4      | Load Voltage                       | 34 |

|   | 4.2.  | 5      | Load Currents                      | 34 |

|   | 4.2.  | 6      | Subsea Cable Voltages              | 35 |

|   | 4.2.  | 7      | Subsea Cable Currents              | 35 |

|   | 4.3   | Load   | d Scenarios                        | 36 |

|   | 4.3.  | 1      | Step Changes in Load               | 36 |

|   | 4.3.  | 2      | Ramp Load                          | 37 |

|   | 4.3.  | 3      | Sudden Loss of Load                | 38 |

|   | 4.4   | Sho    | rt Circuit Fault Simulations       | 39 |

|   | 4.4.  | 1      | Fault on Location F1               | 39 |

|   | 4.4.  | 2      | Fault on Location F2               | 43 |

|   | 4.4.3 |        | Fault on Location F3               | 46 |

|   | 4.4.  | 4      | Fault on Location F4               | 48 |

|   | 4.4.  | 5      | Fault on Location F5               | 50 |

|   | 4.4.  | 6      | Selectivity                        | 50 |

| 5 | Discussion of Results51 |                  |       |                                          |

|---|-------------------------|------------------|-------|------------------------------------------|

|   | 5.                      | 1                | Stea  | ady State Verification Simulations51     |

|   | 5.                      | 2                | Loa   | d Scenarios                              |

|   | 5.                      | 3                | Fau   | It Simulations                           |

|   |                         | 5.3.             | 1     | System Behaviour during Faults52         |

|   |                         | 5.3.             | 2     | System behaviour during fault clearing53 |

|   |                         | 5.3.             | 3     | Comparison of results                    |

| 6 |                         | Con              | clusi | on55                                     |

| 7 |                         | Furt             | her ' | Work                                     |

| 8 |                         | Bibl             | iogra | aphyI                                    |

| A | рр                      | endi             | ces.  | IV                                       |

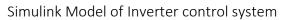

|   | A.                      | Si               | muli  | nk ModelsIV                              |

|   |                         | Ove              | rviev | w of Simulink ModelIV                    |

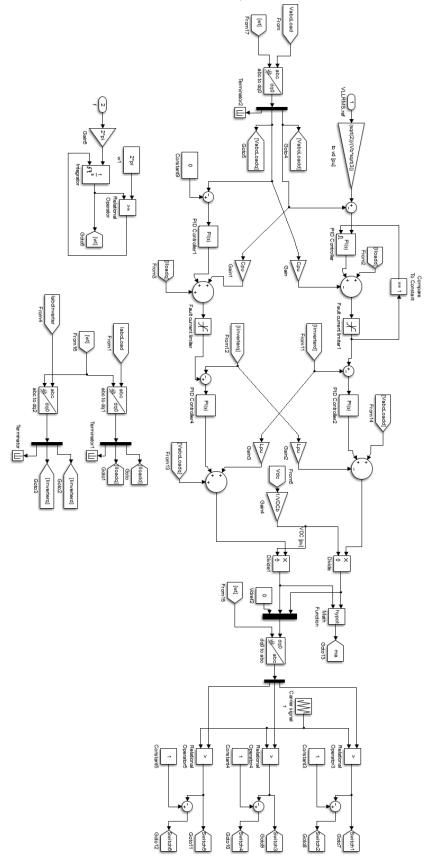

|   |                         | Inve             | erter | and Output Filter Simulink ModelV        |

|   |                         | Sim              | ulink | Model of Inverter control systemVI       |

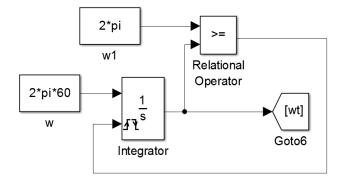

|   |                         | Sim              | ulink | model of Frequency generatorVII          |

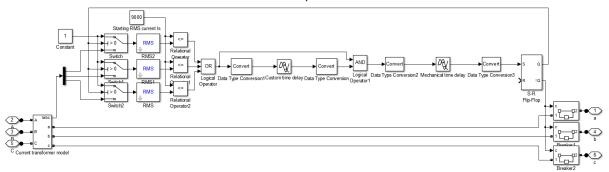

|   |                         | Sim              | ulink | Model of Overcurrent Protection RelayVII |

|   | Β.                      | N                | latla | b Parameters ScriptVIII                  |

|   | C.                      | P                | er Ur | nit SystemIX                             |

|   | D.                      | . Ti             | uning | g of PI ControllersX                     |

|   | E.                      | Pa               | ark T | ransform                                 |

|   | F.                      | Ja               | ick-u | p Cable InductanceXIV                    |

|   | G                       | . Ca             | alcul | ation of DC link Filter InductorXV       |

|   | H.                      | D                | atasl | neetsXVII                                |

|   |                         | Cab              | le da | tasheet from NexansXVII                  |

|   |                         | Dio              | de da | atasheet from InfineonXVII               |

|   |                         | IGB <sup>-</sup> | T dat | asheet from InfineonXVII                 |

# Table of figures

| Figure 1 – A jack-up rig                                                                     | 3    |

|----------------------------------------------------------------------------------------------|------|

| Figure 2 – Two winding transformer equivalent impedance circuit                              | 4    |

| Figure 3 – Three winding transformer equivalent impedance circuit                            | 5    |

| Figure 4 – Single line simplified conceptual diagram of jack-up rig AC power system          | 6    |

| Figure 5 – Jack-up rig interconnection single line diagram                                   | 8    |

| Figure 6 – Two level voltage source converter                                                | . 10 |

| Figure 7 – Sinusoidal pulse width modulation                                                 | . 11 |

| Figure 8 – Single line diagram of inverter and output filter                                 | . 13 |

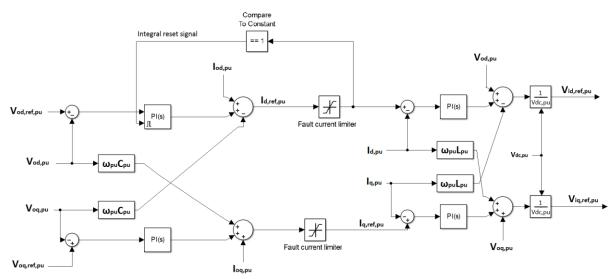

| Figure 9 – Inverter control block diagram. All quantities in per unit                        | . 16 |

| Figure 10 – Protection layout in simplified single line diagram                              | . 19 |

| Figure 11 – Harmonics in the supply line currents of a twelve-pulse rectifier.               | . 20 |

| Figure 12 – Simulink model of interconnection topology and load model                        | . 22 |

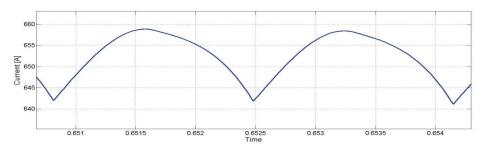

| Figure 13 – 14 A current ripple on DC link                                                   | . 24 |

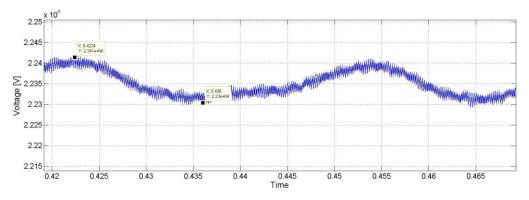

| Figure 14 – DC link voltage ripple of about 100 V                                            | . 24 |

| Figure 15 – Simulink model of IGBT valve consisting of seventeen IGBT/diodes. Not all        |      |

| IGBT/diode blocks are depicted                                                               |      |

| Figure 16 – Simulink model of frequency generator                                            |      |

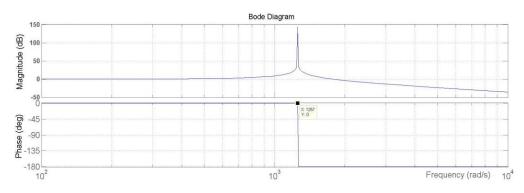

| Figure 17 – Bode plot of output AC filter voltage-frequency response                         |      |

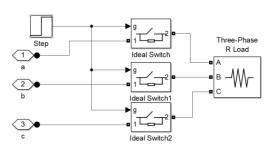

| Figure 18 – Simulink static load model                                                       |      |

| Figure 19 – Three phase dynamic Simulink load model                                          |      |

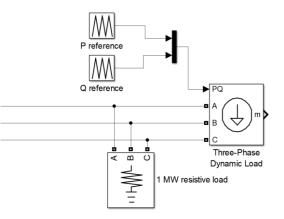

| Figure 20 – Three-phase short circuit Simulink model                                         | . 28 |

| Figure 21 – Fault circuit with fault locations F1, F2 an F3 marked in red                    | . 28 |

| Figure 22 – Fault location F4 between inverter and inverter output filter and fault location |      |

| marked in red                                                                                |      |

| Figure 23 – Overcurrent protection relay Simulink model                                      | . 29 |

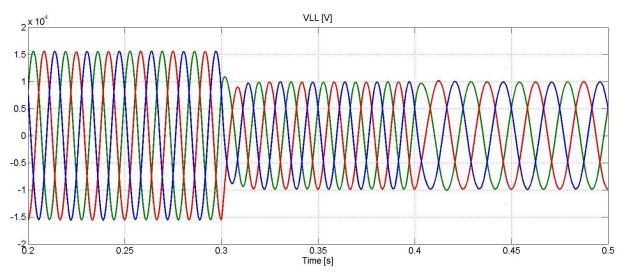

| Figure 24 – Inverter control system test. Reference voltage changed from 11 kV to 7 kV at    |      |

| t=0.3 s. Reference frequency changed from 60 Hz to 40 Hz at t = 0.4 s                        |      |

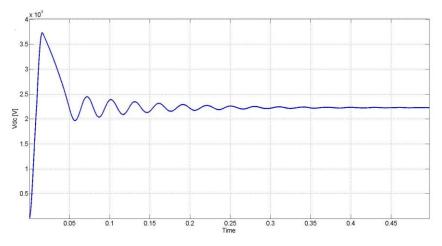

| Figure 25 – DC voltage start up and steady state                                             |      |

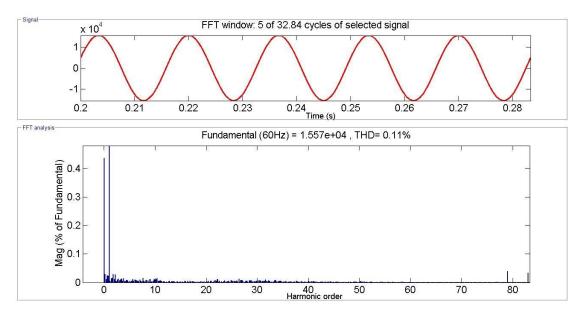

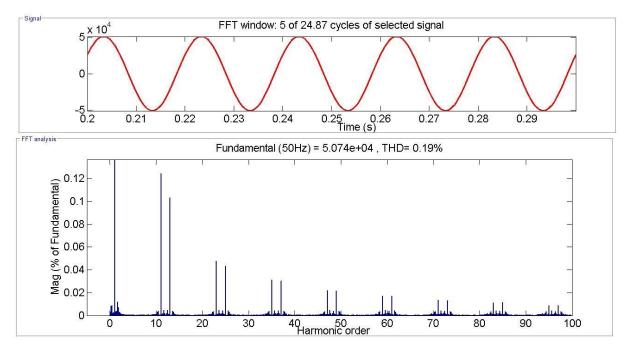

| Figure 26 – Harmonic analysis of inverter output voltage                                     | . 32 |

| Figure 27 – Line current waveform and harmonic analysis of the inverter filtered output      |      |

| currents                                                                                     |      |

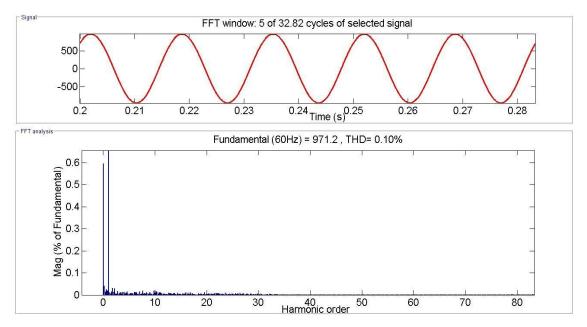

| Figure 28 - Load side two winding transformer line-to-line voltage waveform and harmonic     | С    |

| spectre                                                                                      |      |

| Figure 29 - Load side two winding transformer line current waveform and harmonic spectr      |      |

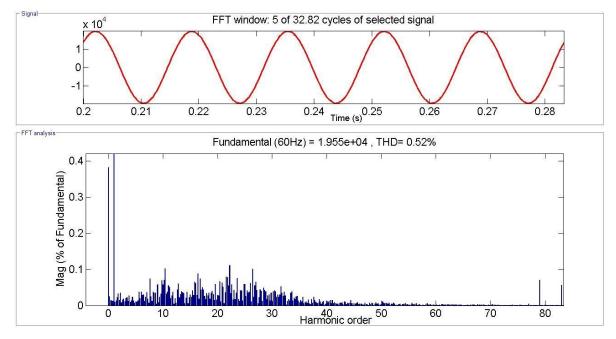

| Figure 30 – Waveform and harmonic analysis of subsea cable line-to-line voltages             |      |

| Figure 31 – Subsea line current waveform and harmonic spectrum                               |      |

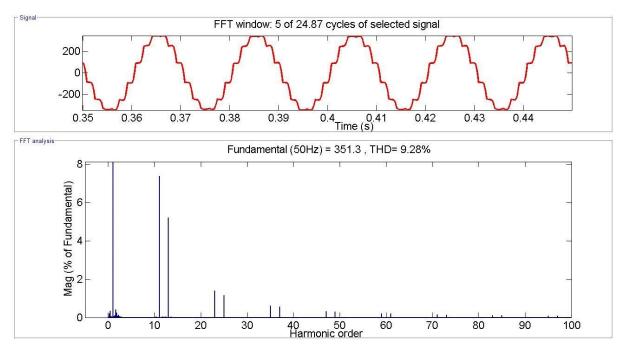

| Figure 32 – Step changes in load                                                             |      |

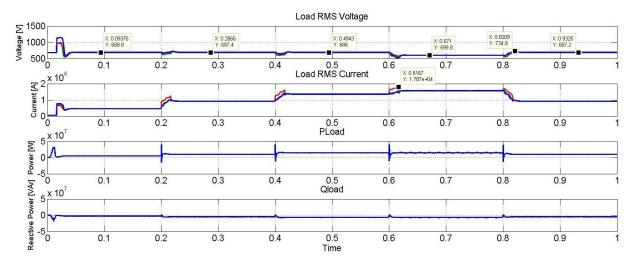

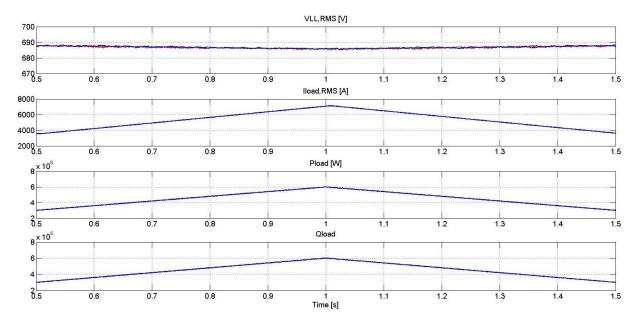

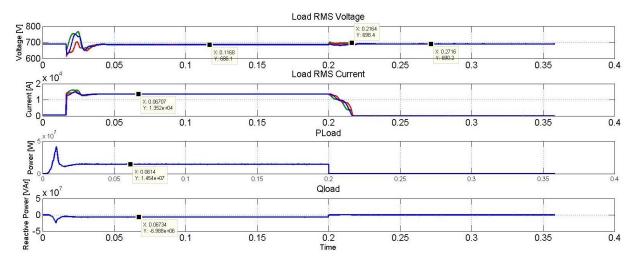

| Figure 33 – RMS voltage, RMS current, active and reactive power, during dynamic ramp lo      | ad.  |

| Figure 34 – Voltage, Current and Power graphs during sudden loss of nominal load             |      |

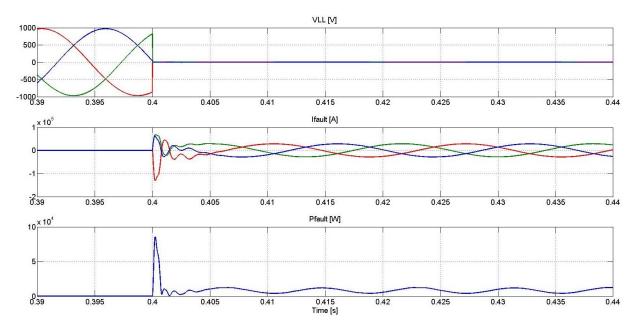

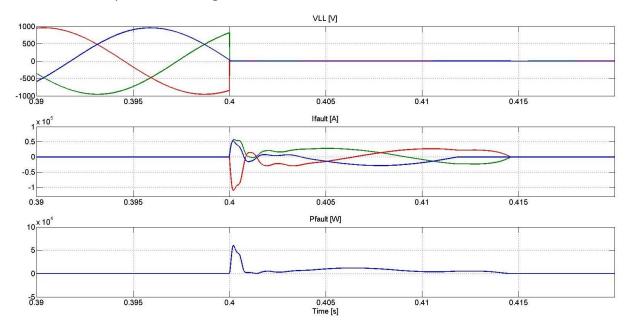

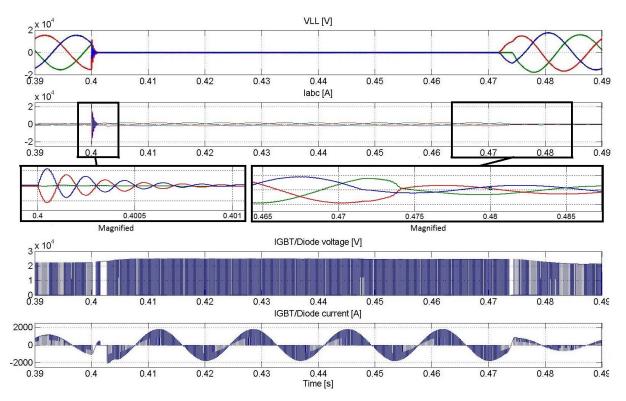

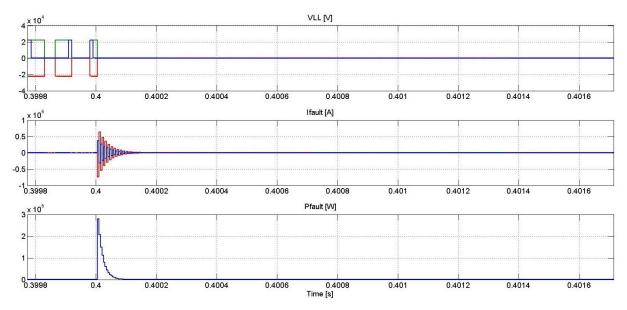

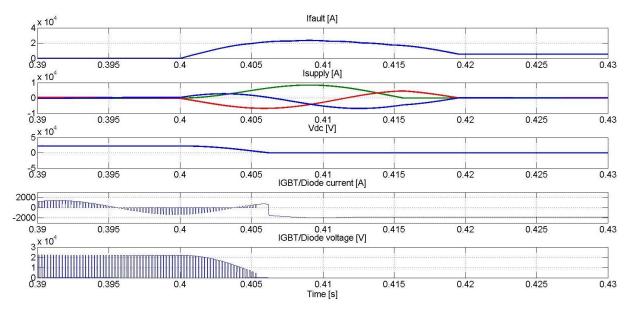

| Figure 35 – Voltage, current and power at the fault location F1 during a three-pole short    |  |

|----------------------------------------------------------------------------------------------|--|

| circuit                                                                                      |  |

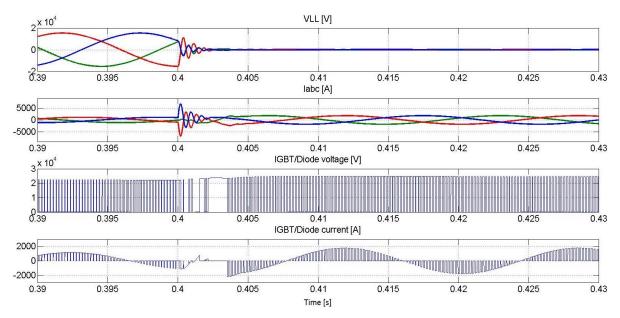

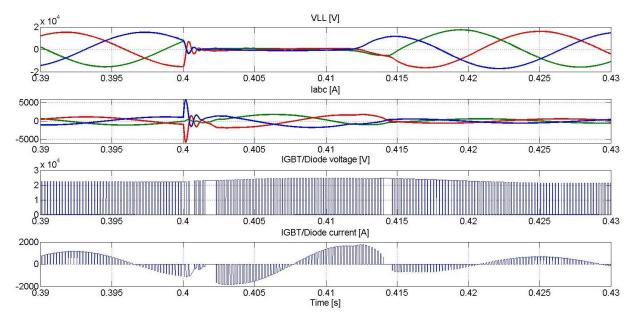

| Figure 36 – Inverter terminal voltage and current, and switch voltage and current during     |  |

| fault                                                                                        |  |

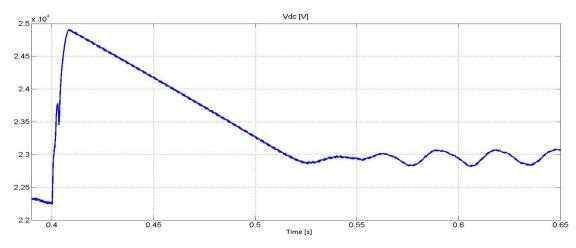

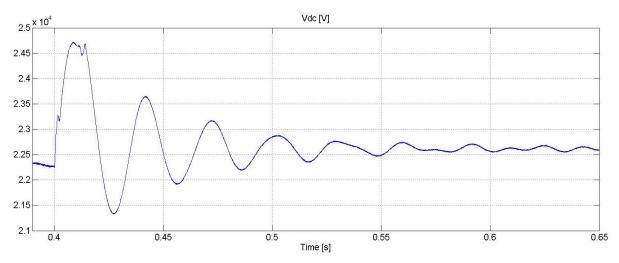

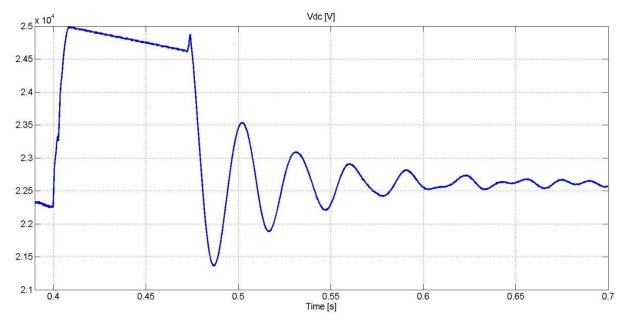

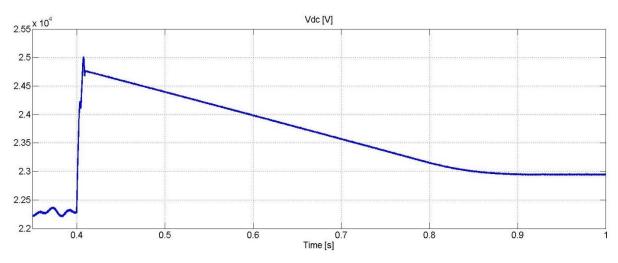

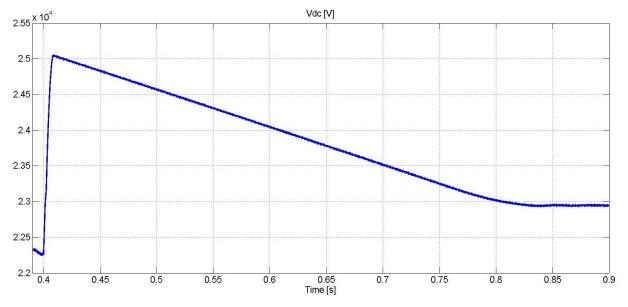

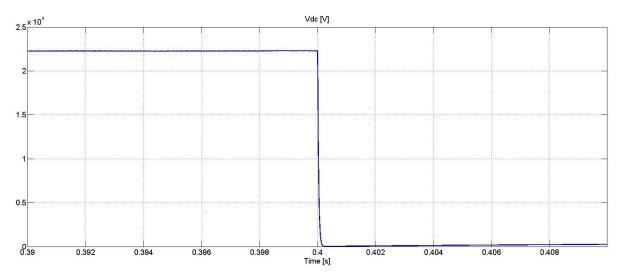

| Figure 37 – DC voltage during AC side fault at F1                                            |  |

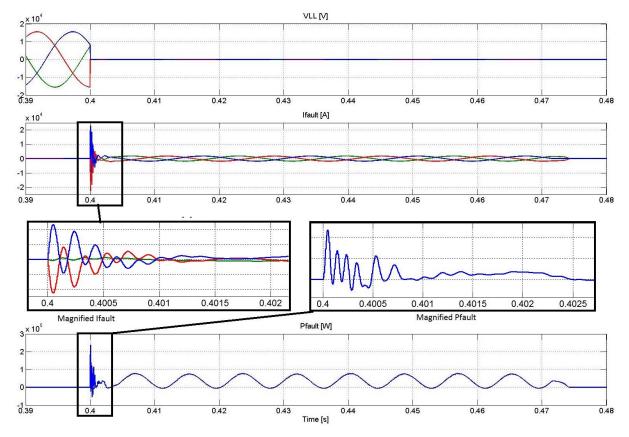

| Figure 38 - Voltage, current and power at the fault location F1 during a three-pole short    |  |

| circuit with overcurrent protection relay installed42                                        |  |

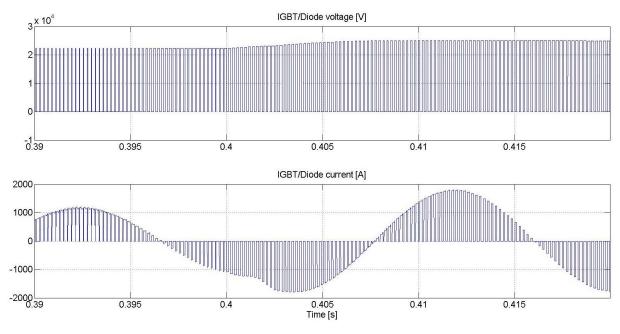

| Figure 39 - Inverter terminal voltage and current, and IGBT/Diode voltage and current during |  |

| fault with overcurrent relay tripping after 30 ms                                            |  |

| Figure 40 – DC voltage during fault at F1 with overcurrent relay tripping after 30 ms        |  |

| Figure 41 -Voltage, current and power at the fault location F2 during a three-pole short     |  |

| circuit with overcurrent protection relay tripping after 70 ms                               |  |

| Figure 42 - Inverter terminal voltage and current, and IGBT/Diode voltage and current during |  |

| fault at F2 with overcurrent relay installed                                                 |  |

| Figure 43 - DC voltage during fault at F2 with overcurrent relay tripping after 70 ms        |  |

| Figure 44 – DC voltage during fault at F2 without protection relays installed                |  |

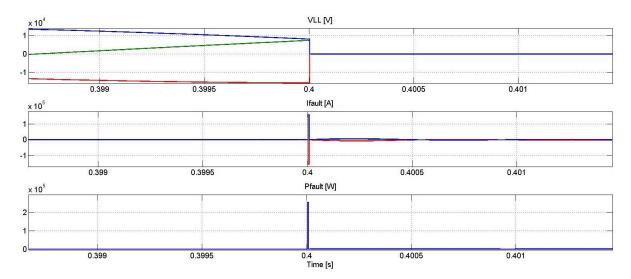

| Figure 45 - Voltage, current and power at the fault location F3 during a three-pole short    |  |

| circuit                                                                                      |  |

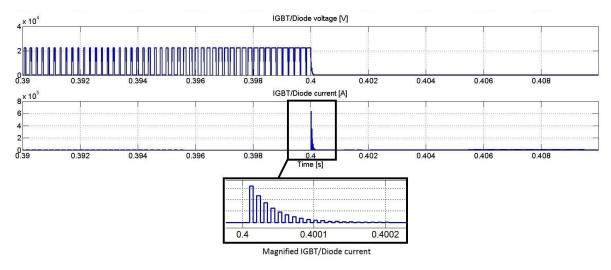

| Figure 46 - IGBT/Diode switch voltage and current during fault at F3                         |  |

| Figure 47 – DC voltage during fault at F3                                                    |  |

| Figure 48 – Inverter switch voltage, fault current and fault power during fault at F4        |  |

| Figure 49 – IGBT/Diode voltage and current during fault at F4                                |  |

| Figure 50 – DC voltage during fault at F4                                                    |  |

| Figure 51 – Fault current, supply line current, DC voltage, and switch voltage and current   |  |

| during bolted short circuit at the DC link                                                   |  |

| Figure 52 –System Simulink model overviewIV                                                  |  |

| Figure 53 – Inverter and output filter Simulink modelV                                       |  |

| Figure 54 – Inverter control system Simulink modelVI                                         |  |

| Figure 55 – Inverter frequency generator Simulink modelVII                                   |  |

| Figure 56 – Overcurrent protection relay Simulink modelVII                                   |  |

| Figure 57 – Simplified control block diagram for the current loopX                           |  |

| Figure 58 – Three-phase cable cross sectionXIV                                               |  |

# List of tables

| Table 1 – PI controller gains                                                               | 17   |

|---------------------------------------------------------------------------------------------|------|

| Table 2 – Subsea cable data                                                                 | 22   |

| Table 3 – Three winding transformer inductances and resistances                             | 23   |

| Table 4 – Two winding transformer per unit parameters                                       | . 26 |

| Table 5 – Relay tripping levels and delay times                                             | 29   |

| Table 6 – Load profiles and time intervals                                                  | 36   |

| Table 7 – Simulation results during step-changes in load                                    | . 37 |

| Table 8 – Load pattern during ramp loads                                                    | 37   |

| Table 9 - RMS voltage, RMS current, active and reactive power, at extreme values during     |      |

| dynamic ramp load                                                                           | 38   |

| Table 10 – Peak parameters measured at fault location during fault at F1                    | 40   |

| Table 11 – Inverter output voltage and current, and switch voltage and current during a fa  | ault |

| at F1                                                                                       |      |

| Table 12 - Peak voltage, current and power, measured at fault location during fault at F2   | 44   |

| Table 13 – Peak voltage, current and power values at inverter terminals and IGBT/Diode      |      |

| switch peak voltage and current values                                                      | 45   |

| Table 14 – Peak voltage, current and power measured at fault location during fault at F3.   | 47   |

| Table 15 Peak voltage, current and power values measured at fault location during fault a   | t    |

| F4                                                                                          |      |

| Table 16 – IGBT/Diode switch peak voltage and current during fault at F4                    | 49   |

| Table 17 – Peak fault current, supply line current and inverter switch current during a bol | ted  |

| fault at the DC link, F5                                                                    | 50   |

| Table 18 – Comparison of peak currents, power and DC voltage during faults at different     |      |

| locations                                                                                   |      |

| Table 19 – Per unit system base values                                                      | IX   |

# Nomenclature

| Definition                          | Abbreviation |

|-------------------------------------|--------------|

| Low voltage                         | LV           |

| Medium Voltage                      | MV           |

| High Voltage                        | HV           |

| Alternating Current                 | AC           |

| Direct Current                      | DC           |

| Insulated Gate Bipolar Transistor   | IGBT         |

| Metal Oxide Field Effect Transistor | MOSFET       |

| Root Mean Square                    | RMS          |

| Proportional Integral               | PI           |

| Per Unit                            | ри           |

| Voltage Source Converter            | VSC          |

| Equation                            | Eq.          |

| Cross-Linked Poly-Ethylene          | XLPE         |

| Phase Locked Loop                   | PLL          |

| Total Harmonic Distortion           | THD          |

| Power factor                        | Pf           |

| Pulse Width Modulation              | PWM          |

# 1 Introduction

## 1.1 Motivation for Work

The focus on global warming and climate change in recent years, along with the global dependence on fossil fuel, has led to an increased focus on limiting emission associated with the Norwegian oil and gas industry. One of the most debated efforts in this context is the electrification of offshore units. This can either by done via a shore connection from land, or from an offshore power production unit. The possibility of an external supply is also advantageous because of the increased flexibility, reduced weight, reduced deck space usage and possible reduced cost. In either case, the offshore oil and gas units need a reliable, economical, and feasible way of interconnecting to the external power production units. This work tries to make one such solution.

## 1.2 Problem Description

This work studies how to interconnect a jack-up rig power system to an external power supply. A possible solution will be proposed. The solution has to be capable of supplying the entire platform, and perform equally or better than the existing power supply on the platform with respect to voltage and current distortion, power quality, and system behaviour during faults. The solution and a simplified jack-up rig power system are to be modelled in Matlab/Simulink using the SimPowerSystems extension.

After creating the model, the model is to be tested by running simulations with various load and fault scenarios. The purpose of the simulations are to test how the solution performs during both normal and extreme situations and to identify possible weaknesses with the solution.

Although this thesis studies the interconnection of an external power supply to a jack-up rig, the principles presented are applicable to many different types of offshore units, such as semisubmersibles; floating production, storage and offloading (FPSO) vessels; and drilling ships.

The system studied is not an actual system, but conceptual, and the goal of this work is therefore not to recreate the exact behaviour of a real system, but highlight the challenges related to creating and running a system on an external power supply.

## 1.3 Limitations of Work

- Inrush current protection, i.e. pre-magnetizing, pre-energizing and soft start circuits, are not studied. A real system would probably have such capabilities, and inrush currents during system start-up is therefore not studied in detail.

- The contribution and behaviour of the interconnection is studied solely, and it is therefore assumed that there is no jack-up rig side power production.

- Only the jack-up rig side of the interconnection is studied in detail.

- Only overcurrent protection is studied. This with the purpose of studying the behaviour and impact fault clearing has on system performance and stability.

- A discrete solver with variable step-size is used when simulating the system. This means that some transients may fail to be registered and that inaccuracies may occur in system control, performance and parameter measurements. In spite of this, the simulation results are considered valid for studying power flow, faults and tendencies. It will be pointed out in the relevant simulations where the simulation tool may be inaccurate, and what the consequences are.

- Many choices of design parameters depend on cost versus desired system performance. The choices made in this work seek to satisfy a balance between the two.

# 2 Theoretical Background

## 2.1 Jack-up Rigs

The jack-up rig, depicted in Figure 1, is the smallest class of offshore drilling platforms. As the name implies, the jack-up rig has legs attached to the buoyant hull that is used elevate, or jack, the rig up and above the sea thereby anchoring it. These self-elevating jackups are the most common offshore drilling unit [1]. Besides drilling, the mobile jack-up rigs are also used for maintenance of other offshore installations such as servicing fixed platforms or wind turbines. Based on experience, the weight of equipment on-board is approximately proportional to cost and should

Figure 1 – A jack-up rig

be kept at a minimum. Additionally, as jack-up rigs are relatively small and mobile, the deck space is limited.

## 2.2 Jack-up Rig Loads

The jack-up rig load profile depend on the operational status. As the jack-up rig is drilling most of the time, and it is during drilling that the load demand are the greatest, this will be the dimensioning load profile. When drilling, a base load consisting of the drilling loads, hotel load, control system load and various other minor loads exists. The drilling loads consisting of the draw works, top drive, mud pumps and other auxiliary loads are mostly inverter fed, variable frequency induction motors. Based on experience, the total load is assumed to be 15 MW, with a power factor,  $\cos(\varphi) = 0.9$ , so that the total nominal apparent power,  $S \approx 16.6$  MVA.

Another load scenario is the "tripping" operation where the drill bit is replaced. The drill string is then raised one 30 m segment at a time until the whole string is up. The drill bit is replaced, and the drill string is then lowered in the same manner. This gives a highly dynamic load pattern that the power supply should be designed to accommodate.

Additionally, some jack-up rigs are installed with thrusters to assist in towing [2].

## 2.3 External Power Supply

The external power supply could be a shore connection connected through a HVAC or HVDC cable, it could be an offshore wind farm, or, as in this, a large production platform with gas turbines. The gas turbines on the production platform are rated at 25 MW, and the synchronous generators has a sub transient reactance of 18 %. Throughout this thesis, it is assumed the production platform has a power management system that maintains the supply voltage constant. This minimizes the jack-up side control complexity and equipment requirements, and thereby weight and cost. From the production platform a HVAC subsea cable, connected through transformers at both ends, supplies the jack-up rig.

## 2.4 Subsea Cable

The jack-up rig is connected to the external power supply by a subsea cable. For subsea medium voltage (MV) applications, one common alternative is a cross-linked poly-ethylene (XLPE) cable.

The modelling of a subsea cable can be performed with different levels of accuracy. According to [3], the length and voltage of the line determines how the line can be modelled with acceptable accuracy. For lines less than 80 km long, or if the voltage is not over 69 kV, the line capacitance can often be ignored without much error. The model then consist of a series impedance with a resistance and an inductance.

For lines above 80 km and below 250 km, a  $\pi$ -equivalent line model may be used [3]. For lines longer than 250 km, distributed parameters must be considered [3].

One challenge associated with the subsea cable are that harmonic currents injected into the cable may cause a parallel resonance due to the shunt capacitance of the subsea cable interacting with the inductance of the power system [4]. This will however not occur if the short line model is used.

## 2.5 Transformers

The system includes various transformers. The theoretical basis for modelling is described in the following.

## 2.5.1 Two Winding Transformer

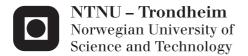

The two winding transformer is used to connect low voltage loads to the main switchboard. The equivalent impedance circuit is illustrated in Figure 2.

Figure 2 – Two winding transformer equivalent impedance circuit.

A simple approach to determine the winding resistances and inductances is assuming equal winding impedances in per unit. Voltage level conversion of the impedances is then unnecessary as this is handled implicitly in the per unit system [5]. Using a transformer also provides galvanic isolation, and as both loads and transformer secondary winding is isolated from ground, ground fault current loops are interrupted.

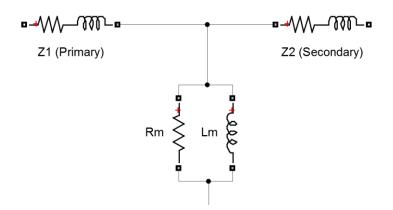

#### 2.5.2 Three Winding Transformer

A twelve-pulse rectifier is used in the interconnection. When using a twelve-pulse rectifier, six input phases are needed. To create six phases, a three winding,  $\Delta/Y/\Delta$  connected transformer is used as input to the rectifiers. The delta connected tertiary winding provides a 30-degree voltage phase shift, thereby creating six output phases. According to [6], if all windings are connected to the grid, the fictitious per winding, per phase, equivalent impedances in linear conditions can be calculated by:

$$\bar{Z}_1 = \frac{1}{2}(\bar{z}_{12} + \bar{z}_{13} - \bar{z}_{23})$$

$$\bar{Z}_2 = \frac{1}{2}(\bar{z}_{12} - \bar{z}_{13} + \bar{z}_{23})$$

$$\bar{Z}_3 = \frac{1}{2} \left( -\bar{z}_{12} + \bar{z}_{13} + \bar{z}_{23} \right)^{Eq. 3}$$

Where:

- $\bar{Z}_1, \bar{Z}_2, \bar{Z}_3$  are the primary, secondary and tertiary transformer impedances [ $\Omega$ ], respectively.

- $\bar{z}_{12}$ ,  $\bar{z}_{13}$ ,  $\bar{z}_{23}$  are the primary to secondary, primary to tertiary and secondary to tertiary transformer impedances [ $\Omega$ ], respectively.

The three winding transformer impedance equivalent circuit are depicted in Figure 3:

Figure 3 – Three winding transformer equivalent impedance circuit

A consequence of using this type of transformer is that with a delta-connected primary winding, excitation unbalances are avoided. The non-sinusoidal excitation currents can be taken from the supply system so that there is a complete ampere-turn balance [7]. Additionally, third harmonic currents (does not sum up to zero) and the multiples are trapped in the delta connection preventing third harmonic content reaching the supply, but causing heating of the transformer windings. In addition, a Y connected secondary winding provides access to a common neutral point if this is desired.

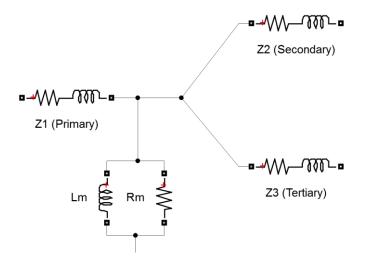

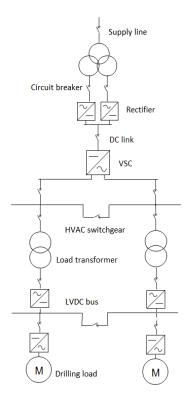

#### 2.6 System Description

Traditionally, power systems on jack-up rigs have used alternating current (AC) on the main distribution, but direct current (DC) on the drilling load bus, with loads connected through inverters. These systems typically includes both high and low voltage sections. The system studied in this thesis are simplified and conceptual based on experience of how typical power systems on offshore rigs are designed. As the interconnection of the rig to an external supply are the focus of this thesis, the rest of the system are not discussed in detail. A simplified conceptual single line diagram of the system is illustrated in Figure 4:

Figure 4 – Single line simplified conceptual diagram of jack-up rig AC power system

The simplified single line diagram depicts four generators, but the actual number of generators may differ. The generators are connected to an 11 kV AC switchboard through circuit breakers. Depending on the application and design of the system, the high voltage switchboard may be omitted by placing transformers at the power feeds. The switchboard is separated into segments of two diesel-generator sets pr. segment. These segments are called islands. The islands are interconnected through bus-ties that may be open or closed depending on the system state. From the main switchboard step-down transformers supplies power at various voltage levels to the various loads. The inverter drilling loads are connected to a DC bus to allow variable frequency operation. The DC bus islands are also separated by a bus tie. These are depicted at the bottom of Figure 4. Additionally, there is a conductor

connecting the endpoints of the high voltage switchboard. This may be connected to redirect power in case of a fault or maintenance.

## 2.7 Interconnecting an External Power Supply to the Jack-up Rig Power System

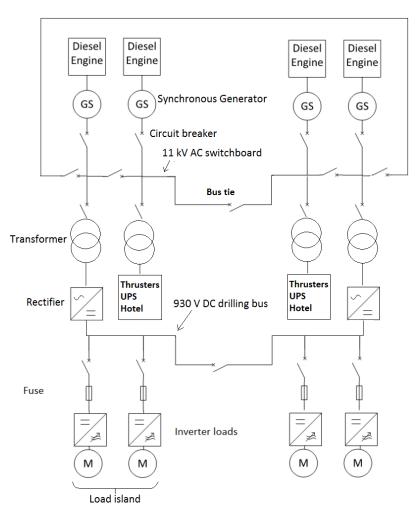

### 2.7.1 Interconnection Topology

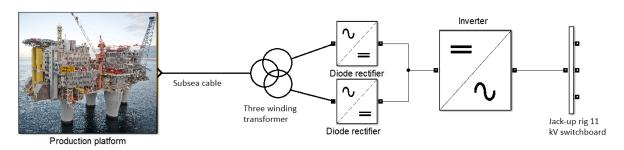

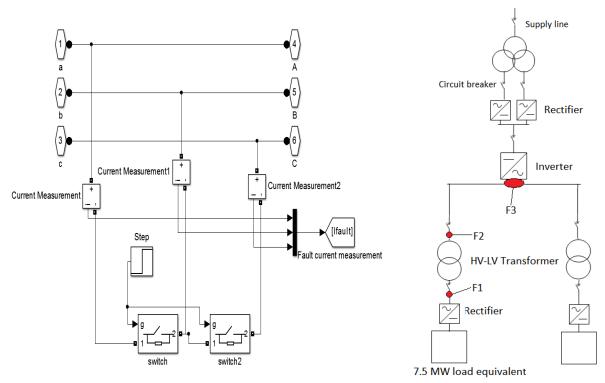

The proposed interconnection layout simplified single line diagram is depicted in Figure 5:

Figure 5 – Jack-up rig interconnection single line diagram

Because many of the jack-up rigs are designed to operate at 60 Hz, but needs to be able to be connected to a 50 Hz supply, a frequency changer is needed. A frequency changer adds flexibility if the jack-up rig is to operate worldwide.

To realize this the subsea cable from the production platform is feed into a three winding transformer. The three winding transformer steps down the high voltage from the subsea cable and creates six output phases. This is done to minimize DC link ripple in the frequency changer. Two full bridge diode rectifiers then rectify the voltage, before a voltage source converter (VSC) converts the DC to 60 Hz AC.

Redundancy is important in offshore installations. Therefore, a possible alternative to a single cable is to have another cable connected to yet another offshore unit and so on. By making a grid in this way, the power has two feeding points at each unit and a failure of one cable or interconnection will not lead to a blackout. An example of this kind of interconnection topology is the DNV "OPera" project [8].

Having a sole converter supplying the entire jack up rig load is also risky, as a failure of this will lead to a blackout unless the jack up rig has adequate local backup generators or UPS systems. Extra interconnecting converters with redundant power handling capabilities could then be considered.

As Figure 4 illustrates, the grid layout is radial, with distributed loads connected in parallel at the main switchboard separated into islands by bus ties. The interconnection to the external power supply should therefore have at least one feeder from the interconnection to each island.

#### 2.7.2 Twelve Pulse Series Connected Rectifier

To improve the DC output voltage and current waveforms, a twelve-pulse diode rectifier is used. It consist of two three-phase full bridge diode rectifiers connected in series. The rectifier is supplied by the six output phases of the three winding transformer described in 2.5.2, thereby supplying twelve output pulses. A series connection is selected to avoid problems associated with paralleling of diodes.

#### 2.7.3 DC Link Filter Inductor

A DC link filter inductor is used to reduce harmonics on the AC sides, and improve inverter operation. The inductance, *L*, as a function of transformer output line-to-line voltage,  $V_{LL}$  [V], supply frequency,  $\omega$  [rad/s] and allowed current ripple,  $\Delta i_L$  [A], is calculated in Appendix G. The resulting equation is presented in Eq. 4:

$$L = \frac{0.00654972V_{LL}}{\omega\Delta i_L} \ [H]$$

#### 2.7.4 DC Link Filter Capacitor

A filter capacitor is used to minimize voltage ripple. Because the inverter is controlled as a voltage source inverter, the capacitor should ensure a quite constant DC link voltage.

According to [9], the dc-link voltage variation is generally caused by front end and inverter power unbalance, and the filter capacitance, *C*, can be calculated as:

$$C = \frac{P_{max}}{(V_{do}\Delta V \pm \frac{1}{2}\Delta V^2)f_{sw}} [F]$$

Eq. 5

Where:

- *P<sub>max</sub>* is the maximum(nominal) load power [MW]

- $\Delta V$  is the allowed voltage change [V]

- $f_{sw}$  is the inverter switching frequency [Hz]

#### 2.7.5 Inverter

2.7.5.1 Topology

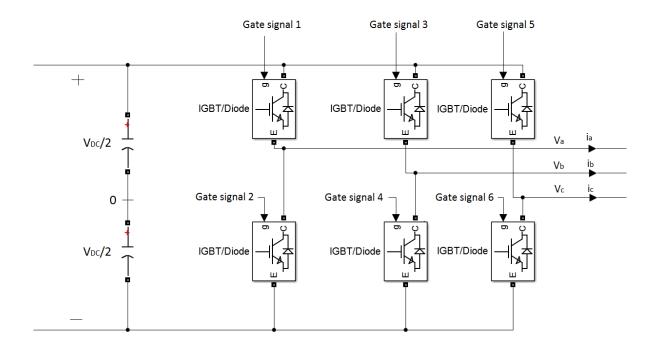

A two-level VSC is used to convert DC to AC. The topology is depicted in Figure 6:

#### Figure 6 – Two level voltage source converter

The two level VSC consist of three half-bridge converters, one for each phase. It is called twolevel VSC since each of its AC-side terminals can assume either of the voltage levels  $-V_{DC}$  and  $V_{DC}$  [10]. The state of each switch is controlled by the gate signal, which in turn are determined by the control system. Depending on the application, more complex topologies, such as a three level "Neutral point clamped" or multilevel topologies can be used.

#### 2.7.5.2 IGBT Valves

Insulated gate bipolar transistor (IGBT) technology has come a long way, and IGBTs with several kilo volts blocking voltage, and more than a kilo ampere of collector current are commercially available. However, for high power applications these IGBTs may not suffice. It is then possible to connect two or more IGBTs in parallel to increase the current handling capability [11]. A disadvantage of this is the possibility of uneven split in losses due to difference in IGBT characteristics. Similarly, to increase the voltage handling capability, several IGBTs can be connected in series [12]. This series connection is then called a valve. The most extreme example of this being IGBTs in HVDC applications, where hundreds of IGBTs may be connected in series to achieve the desired voltage level [13]. One challenge associated with this is that all the series connected IGBTs in one valve needs to be switched at the same time [10]. In addition, parallel resistors should be employed to enforce static voltage sharing, and RC snubber circuits should be employed to equalize voltage rate of rise [14].

For safety, [15] recommends that the maximum peak voltage the IGBT has to block,  $V_{o,max}$ , should not exceed 80 % of the IGBT rated voltage,  $V_{CES}$ , in an AC system. For  $n_{sd}$  series connected devices this yield:

$$\frac{V_{o,max}}{n_{sd}} \le 0.8V_{CES}$$

If one series connected IGBT fails, the inverter should still be able to function. This can be achieved by using press pack IGBTs. Using press pack IGBTs, one or more extra IGBTs can be installed in each valve for redundancy. If a press pack IGBT fails, it short circuits, and the other IGBTs are still useable [16], [17]. The faulty IGBT can then be replaced during the next maintenance of the inverter.

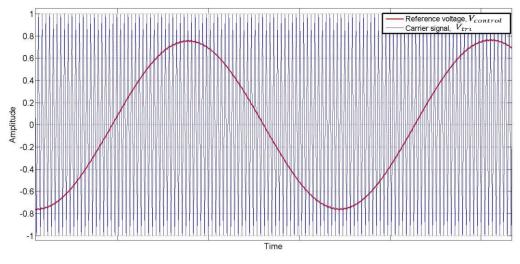

#### 2.7.5.3 Pulse Width Modulation

To control the state of the IGBT switches the sinusoidal pulse width modulation (PWM) technique is employed. A sinusoidal reference voltage signal,  $V_{control}$  [V], is compared to a triangular carrier signal,  $V_{tri}$  [V], as depicted in Figure 7.  $V_{control}$  is supplied by the control system that controls the amplitude and frequency of this signal. The state of the switches in each inverter leg is then determined as follows: If  $V_{control} > V_{tri}$ , the upper switch of is on, else the lower switch is on. In this manner, an alternating output voltage in synthesized as the width and polarity of the resulting output rectangular pulses is varied.

Figure 7 – Sinusoidal pulse width modulation.

Note that the amplitude may differ from the above figure.

#### 2.7.5.4 DC Link Voltage

According to [18], the DC link voltage level has to satisfy:

$$(\hat{V}_{AN})_1 = m_a \frac{V_{DC}}{2}$$

Eq. 7

Where:

- $m_a = \frac{\hat{V}_{control}}{\hat{V}_{tri}}$ , is the amplitude modulation ratio, i.e. the ratio between the peak of the control signal,  $\hat{V}_{control}$ , and the peak of the carrier signal,  $\hat{V}_{tri}$ .

- $(\hat{V}_{AN})_1$  is the peak value of the fundamental frequency component in one inverter leg

To operate in the linear region  $m_a$  is constrained to  $0 < m_a \le 1$ . Operating in the linear region minimizes distortion of the output voltage [18].

#### 2.7.5.5 Switching Frequency

The frequency modulation ratio,  $m_f$ , is defined as [18]:

$$m_f = \frac{f_s}{f_1}$$

Eq. 8

Where:

- $f_s$  is the switching frequency [Hz]

- $f_1$  is the output voltage fundamental frequency [Hz]

According to [18], the choice of switching frequency depend on several factors. One the one hand, switching losses increases with increasing frequency, but on the other hand, filtering of higher frequency harmonics are easier. The switching also causes audible noise between 6 kHz and 20 kHz, so this interval should be avoided if noise is an issue. Additionally, using an integer value of  $m_f$  causes the carrier and control signal to be synchronous. This is called synchronous PWM, and by using synchronous PWM, undesirable sub-harmonics are avoided. Finally,  $m_f$  should also be an odd multiple of three. This result in odd symmetry and half-wave symmetry and the even harmonics are cancelled.

#### 2.7.5.6 Inverter Control

As the VSC in the interconnection is considered the only power source, and the jack-up rig network is passive, the main purpose of the VSC is to maintain the grid voltage and frequency. If the network had other power supplies besides the external feed, e.g. diesel generators running, the external power supply would need synchronization with the jack-up power system. This could be achieved by using a phase locked loop (PLL), but as there are no jack-up side power generation in this model, the synchronization is omitted. If there were more than one power supply, another control strategy, such as controlling the output power, would be desirable [10], [19]. This allows the use of load sharing strategies and power management, which is necessary with multiple power sources acting in the same system. Examples of such strategies are the droop control method, and the master-slave control method.

A common strategy to control the inverter switching is by the use of the Park transform [10]. This transforms sinusoidal AC signals into DC signals and therefore allows control by PI controllers [10]. A "dq0 transform" block in Simulink is used to perform the transform. Some variations of the transform exist. As described in Appendix E, the transform can be made voltage magnitude invariant. This version of the transform is the same as used in the Simulink block [20] and is used in this work.

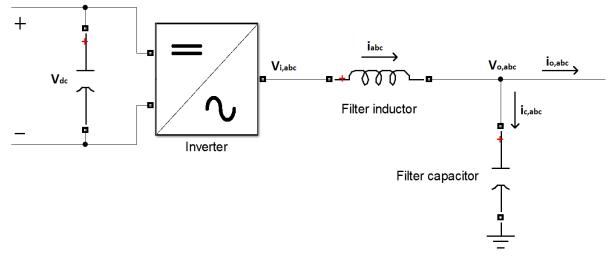

A proven and well-tested way of controlling a VSC is by using an in a cascaded control structure consisting of an outer voltage control loop and an inner current control loop. The purpose of the voltage control loop is to control the grid voltage by controlling output filter capacitor voltage, i.e. the line to neutral voltage magnitude, and to control output frequency. The purpose of the current control loop is to control the inverter output current. This is done by controlling the output filter inductor current. The reason for controlling the current in this

standalone mode is to protect the inverter IGBTs from overloading [21], [19]. A current limitation is then imposed on the current controller. A control scheme based on the control schemes presented in [10], [22], [23] and [24] are used. As a basis for design, instantaneous switching i.e. no blanking time, is assumed. The inverter output system overview is depicted in Figure 8:

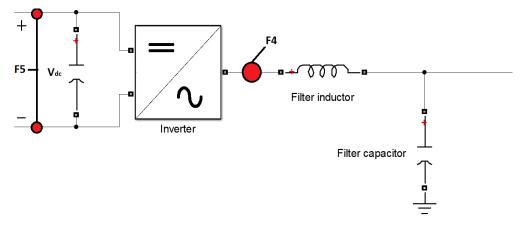

Figure 8 – Single line diagram of inverter and output filter

The basis for the control are derived:

The expressions for three balanced sinusoidal entities are:

$$f_a = \hat{f}\cos(\omega t + \theta_0) \qquad \qquad Eq. 9$$

$$f_b = \hat{f}\cos(\omega t + \theta_0 - \frac{2\pi}{3})$$

Eq. 10

$$f_c = \hat{f}\cos(\omega t + \theta_0 - \frac{4\pi}{3})$$

Where *f* represents voltages or currents,  $\omega t$  is the angle [rad], and  $\theta_0$  is the initial angle [rad]. According to [10], Eq. 9, Eq. 10 and Eq. 11 can be represented as a space vector by:

$$\vec{f}(t) = \frac{2}{3} \left[ f_a(t) e^{j0} + f_b(t) e^{j\frac{2\pi}{3}} + f_c(t) e^{j\frac{4\pi}{3}} \right]^{Eq. 12}$$

This can be decomposed into a real and an imaginary component in a stationary  $\alpha - \beta$  reference frame as:

$$\vec{f}(t) = f_{\alpha}(t) + jf_{\beta}(t)$$

Eq. 13

Which can be transformed onto a rotating d-q axis reference frame as:

$$\vec{f}(t) = (f_d(t) + jf_q(t))e^{j\theta(t)}$$

Eq. 14

Where  $\theta(t)$  is the angle [rad] at time *t*.

The magnitude of  $\vec{f}(t)$  is then:

$$|f| = \sqrt{f_d^2 + f_q^2}$$

Eq. 15

The generic filter capacitor current equation are:

$$i_C = C \frac{dv_o}{dt} = i - i_o$$

Eq. 16

In addition, neglecting inductor resistance, the generic inductor voltage equation are:

$$v_L = L \frac{di}{dt} = v_i - v_o$$

Eq. 17

Where:

- *i<sub>C</sub>* is the capacitor current [A]

- $v_o$  is the capacitor voltage [V]

- *i* is the inverter output current [A]

- *i<sub>o</sub>* is the load current [A]

- $v_L$  is the inductor voltage [V]

- $v_i$  is the inverter terminal voltage [V]

- *C* is the filter capacitor capacitance [F]

- *L* is the filter inductor inductance [H]

All voltages are line to neutral and all currents are phase currents.

Representing Eq. 16 and Eq. 17 as space vectors:

$$C\frac{d\vec{v}_o}{dt} = \vec{\iota} - \vec{\iota}_o$$

$$L\frac{d\vec{i}}{dt} = \vec{v}_i - \vec{v}_o$$

Eq. 19

Inserting Eq. 14 in Eq. 18 and Eq. 19, yields:

$$C \frac{d(v_{od} + jv_{oq})e^{j\theta(t)})}{dt} = (i_d + ji_q)e^{j\theta(t)} - (i_{od} + ji_{oq})e^{j\theta(t)}$$

Eq. 20

$$L\frac{d(i_d + ji_q)e^{j\theta(t)})}{dt} = (v_{id} + jv_{iq})e^{j\theta(t)} - (v_{od} + jv_{oq})e^{j\theta(t)}$$

Eq. 21

Carrying out the differentiations with  $\frac{d\theta(t)}{dt} = \omega$  [rad/s], eliminating all the exponential terms and separating the real and imaginary components yield:

$$C\frac{dv_{od}}{dt} = C\omega v_{oq} + i_d - i_{od}$$

$$C\frac{dv_{oq}}{dt} = -C\omega v_{od} + i_q - i_{oq}$$

Eq. 23

$$L\frac{di_d}{dt} = L\omega i_q + v_{id} - v_{od}$$

Eq. 24

$$L\frac{di_q}{dt} = -L\omega i_d + v_{iq} - v_{oq}$$

Eq. 25

The control variables are the inverter voltages and currents:  $i_d$ ,  $i_q$ ,  $v_{id}$  and  $v_{iq}$ , respectively. For convenience the inverter are controlled using a per unit system. The base values used are given in Appendix C. Expressing Eq. 22, Eq. 23, Eq. 24 and Eq. 25 in the Laplace domain, and dividing by the base values,  $i_{base}$  and  $v_{base}$ , the per unit expressions becomes:

$$\frac{sC_{pu}v_{od,pu}(s)}{\omega_{base}} = C_{pu}\omega_{pu}v_{oq,pu}(s) + i_{d,pu}(s) - i_{od,pu}(s)$$

Eq. 26

$$\frac{sC_{pu}v_{oq,pu}(s)}{\omega_{base}} = -C_{pu}\omega_{pu}v_{od,pu}(s) + i_{q,pu}(s) - i_{oq,pu}(s)$$

Eq. 27

$$\frac{sL_{pu}i_{d,pu}(s)}{\omega_{base}} = L_{pu}\omega_{pu}i_{q,pu}(s) + v_{id,pu}(s) - v_{od,pu}(s)$$

Eq. 28

$$\frac{sL_{pu}i_{q,pu}(s)}{\omega_{base}} = -L_{pu}\omega_{pu}i_{d,pu}(s) + v_{iq,pu}(s) - v_{oq,pu}(s)$$

Eq. 29

Where *s* is the Laplace operator.

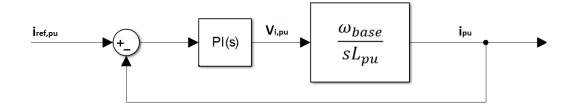

As seen in Eq. 26, Eq. 27, Eq. 28 and Eq. 29, , the state variables  $v_{od}$ ,  $v_{oq}$ ,  $i_d$  and  $i_q$  is dependent on  $v_{oq}$ ,  $v_{od}$ ,  $i_q$  and  $i_d$ , respectively. Additionally, all state variables depend on the load. To mitigate this effect and allow independent control of the d and q axis components, feedforward of the load and cross coupling terms are added to the control loops as illustrated in Figure 9. The feed forward terms are considered ideal, and are therefore eliminated from the above equations. Furthermore, by assuming a fast current control loop and neglecting inverter time delay, the current loop transfer functions can be approximated by a first order time constant,  $\tau_{eq}$ , [10] so that:

$$i_{dq,pu}(s) \approx \frac{1}{1 + \tau_{eq}s} * i_{dq,ref,pu}(s)$$

Eq. 30

Inserting this in Eq. 26, Eq. 27 and rearranging, rearranging Eq. 28 and Eq. 29, and removing all feed forward terms, yield the following transfer functions:

$$\frac{v_{o,dq,pu}(s)}{i_{dq,ref,pu}(s)} \approx \frac{1}{1 + \tau_{eq}s} * \frac{\omega_{base}}{sC_{pu}}$$

Eq. 31

And:

$$\frac{i_{dq,pu}(s)}{v_{i,dq,pu}(s)} \approx \frac{\omega_{base}}{sL_{pu}}$$

Eq. 32

Where:

- $i_{dq,ref,pu}(s)$  is the d or q axis output of the voltage PI controller, with the feed forward terms removed.

- $v_{i,dq,pu}(s)$  is the d or q axis output of the current PI controller, with the feed forward terms removed, i.e. the PWM modulating signals controlling the input to the system.

This means that  $v_{o,dq,pu}(s)$  can by controlled by the output of the voltage PI controllers,  $i_{dq,ref,pu}(s)$ ; and that  $i_{dq,pu}(s)$  can be controlled by the output of the current PI controllers,  $v_{i,dq,ref,pu}(s)$ .

The corresponding control block diagram (with some additions) is depicted in Figure 9.

The voltage control loop produces the current references, and the current control loop produces the PWM voltage references i.e. the modulating d and q axis signals. These references are transformed from the d-q plane back to abc per unit quantities which are compared to a triangular carrier signal with amplitude 1 and frequency equal to the switching frequency as described in 2.7.5.3.

*Figure 9 – Inverter control block diagram. All quantities in per unit.*

A saturation block is added to the current references in the control system to protect the IGBTs from overcurrent and to limit fault currents. During a short circuit, the inverter will be unable to sustain the output voltage due to the saturation. This will lead to a windup of the integrator in the d-axis voltage PI controller. To avoid this, the integral is reset continuously while the current reference is saturated. This effectively makes the PI controller a P controller, and avoids large voltage offsets in the period after the fault is cleared.

As the DC voltage level is not perfectly stable, the voltage reference signals are divided by the measured DC voltage in per unit. The DC voltage base is chosen as the nominal DC voltage. By doing this the VSC controller is decoupled from the DC voltage level, which is done to make the controller more accurate.

#### 2.7.5.7 Tuning of PI Controllers

The PI controllers are tuned using pole placement. The voltage control are the slowest and hence the poles are placed closest to the right half plane. The detailed tuning procedure of the controllers is included in Appendix D. The resulting proportional gain,  $K_p$ , and integral gain,  $K_i$ , values are presented in Table 1.

| Controller | K <sub>p</sub> | Ki      |

|------------|----------------|---------|

| Voltage    | 0.3496         | 75.4877 |

| Current    | 3.3781         | 7294    |

Table 1 – PI controller gains.

#### 2.7.6 Inverter Output Low Pass LC Filter

A low pass LC filter is used on the inverter output to remove dominant load side harmonic components. The filter inductance, *L*, and capacitance, *C*, can be determined designing for minimum reactive power or system time constant, the cost function and total harmonic distortion (THD) [25]. On the one hand, to avoid voltage distortion, the filter capacitance should be maximized, and the inductance minimized when selecting the cut-off frequency. On the other hand, this means that the inverter has to supply more reactive power, thereby reducing the inverter active power capacity [25]. Here, the THD requirement is considered. The per phase filter diagram is depicted in Figure 8. The LC filter forms a voltage divider. Neglecting inductor resistance, this is described in the Laplace domain as:

$$v_o(s) = \frac{\frac{1}{sC}}{\frac{1}{sC} + sL} v_i(s) \Longrightarrow \frac{v_o(s)}{v_i(s)} = h(s) = \frac{1}{s^2 LC + 1}$$

The standard form of this equation is [26]:

$$h(s) = \frac{K}{\frac{s^2}{\omega_0^2} + 1}$$

Eq. 34

Where:

- $\omega_o$  = The undamped resonance frequency [rad/s]

- K = Constant gain

- s = the Laplace operator

For this system, the resonant frequency,  $\omega_o$ , equals the corner frequency [26]. However, choosing a corner frequency close to the fundamental frequency can boost the fundamental frequency component due to resonance. Therefore, the corner frequency should be several times larger than the fundamental frequency to avoid resonant voltages. Similarly, the corner frequency should be several times smaller than the switching frequency to provide good attenuation of the switching harmonics. After the corner frequency, because of the two integral terms, the asymptote drops with 40 dB/decade. Solving Eq. 33 and Eq. 34 for  $\omega_o$ :

$$\omega_o = \frac{1}{\sqrt{LC}}$$

Eq. 35

The size of *L* are determined by the allowed current ripple. The inductor value are determined as described in [25], using:

$$L = \frac{1}{6} \frac{V_{DC} \delta}{\Delta I f_{s}}$$

Eq. 36

Where:

- *L* = Filter inductance [H]

- $V_{DC}$  = DC link voltage [V]

- $\delta$  = Inverter duty cycle at maximum voltage output

- $\Delta I$  = Current ripple [A]

- $f_s$  = Inverter switching frequency [Hz]

After this, the capacitance is determined using Eq. 35.

#### 2.7.7 Faults

Faults at different locations in the jack-up rig AC system, and a bolted short circuit of the DC link is studied. The purpose is to study the reliability of the system feed by an external supply, the reliability of the interconnection, and identify critical faults. Therefore, only worst-case fault currents are studied. Additionally, the demands to fault protection has to be fulfilled. On the AC side, a three-pole short circuit of the phases, although not the most common fault, often yields the largest fault current [27]. As this is a symmetrical fault, it is unnecessary to use symmetrical components analysis while studying it. Additional AC side faults may be topole short circuit, or phase to ground faults. As the low voltage load side on jack-up rigs are isolated from ground, a single phase to ground fault will not cause a fault current because of the galvanic isolation provided by the transformer. A multiphase ground fault may however cause fault currents.

#### 2.7.8 Fault Protection

To protect all loads and equipment against faults, and allow redirection of power, protection relays are installed at all interconnecting points. The protection layout is depicted in the simplified single line diagram in Figure 10, with only a few of the drilling loads included. Similar protection layout can be applied to all loads. In addition to the relay-controlled circuit breakers depicted, fuses could be considered as a backup at certain places. The relay protection can measure voltages, currents or impedance, and protect against overcurrent, over/under voltages.

The system topology is radially connected, so the nominal current in each branch is less than that of the inverter. In addition, there are multiple voltage levels in the system. This means that the tripping level of each relay has to be adjusted for this. The circuit breakers on the high voltage branches operates at the same voltage as the inverter, but only has to accommodate a portion of the current at nominal load and below. This allows the circuit breakers to be installed with a lower current handling capability and tripping level than the inverter current handling capability. The circuit breakers on the low voltage, load side of the transformers has to have a much higher nominal current than those on the high voltage side. The tripping level of these breakers then has to be below the corresponding inverter current handling capability on the high voltage side.

As an additional safety barrier, there are current limitations included in the inverter control system that limits the inverter current to rated current. Although the inverter output current is limited, the protection relay are still able to trip, because, as explained above, the system has a radial topology, and the inverter is therefor able to supply enough short circuit current to

Figure 10 – Protection layout in simplified single line diagram

trip the relays. During a fault, other loads may experience a transient dip in power until the circuit breaker trips and steady state is restored.

In case of an inverter terminal fault, a separate fast acting detection system disconnects the inverter to protect the IGBTs. This is however, is a last resort, as disconnecting the VSC cuts all power to the jack-up.

Faults inside the frequency changer is also critical because, due to the large filter capacitors the initial currents are large and may destroy the frequency changer before any protection trips. Protection against faults on the DC link is also difficult, because the current does not have a natural zero crossing. Fault currents and arcs needs to be interrupted by other means. One solutions is to force the current to zero by employing parallel, pre-charged, capacitor that discharges opposing current into the arc hen the fault occurs [28]. Another solution is by employing fast acting IGBTs that open, and cuts the current. This is used in the intelligent load controller (ILC), a DC switch developed by Siemens.

There are also circuit breakers installed at the AC supply side of the rectifiers, cutting the supply line contribution to fault currents if necessary.

#### 2.7.9 Selectivity

An important criterion when designing fault protection in a power system is to ensure selectivity. Selectivity means that only the fault protecting device closest to the fault trips, so that as much of the rest of the grid as possible still is operational [27]. In addition, if the fault protecting device closest to the fault fails to trip, the next series connected fault protecting device should trip, and so on. This is accomplished by letting the relay furthest away from the power supply should have the fastest tripping, and then increasing the time delay for each relay toward the supply.

It is important to protect the IGBTs in the VSC from overcurrent, so that the VSC still are able to supply power to the non-faulted part of the network after the fault. To accomplish this, all subsequent circuit breakers has to trip within the time dictated by the IGBT  $I^2t$  rating. This means that the circuit breakers detection time, movement time, and arc extinction time has to be smaller than the critical time before the IGBTs are destroyed.

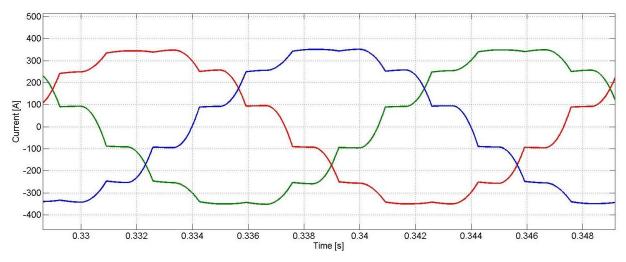

#### 2.8 Harmonics

When using non-linear elements in a circuit, such as power electronic converters, the voltage and current waveforms may become distorted with respect to a sinusoidal shape as illustrated in Figure 11:

Figure 11 – Harmonics in the supply line currents of a twelve-pulse rectifier.

This distorted waveform can be described as the sum of many smaller sinusoidal waveforms at various frequencies. These waveforms are called harmonics. The frequency by which the distorted waveforms repeat are called the fundamental frequency [18], and all harmonic components are at integer multiples of this fundamental frequency [18]. The harmonics can be analysed by Fourier analysis [18]. An important design parameter when designing a power system is the total harmonic distortion (*THD*), which is defined as [18]:

$$\% THD_i = \sqrt{\sum_{h \neq 1} \left(\frac{I_{sh}}{I_{s1}}\right)^2}$$

Eq. 37

Where the subscript *i* indicates the THD in current.  $I_{sh}$  is the line current  $h^{th}$  harmonic, and  $I_{s1}$  is the fundamental. Similarly, replacing the currents with voltages yield the voltage *THD*,  $\% THD_v$  [18]. The power factor (PF) in the system depend on the  $THD_i$ . According to [18]:

$$PF = \frac{I_{s1}}{I_s} \cos\phi_1 = \frac{\cos\phi_1}{\sqrt{1 + THD_i^2}}$$

Where  $cos\phi_1$  is the same as the power factor in linear circuits, also called the displacement power factor (DPF) as it describes the displacement between the voltage and current.

As Eq. 38 illustrates, the power factor depend on the harmonics, and increasing harmonics reduces the PF and vice versa.

Harmonic sources in the presented system are the rectifiers and the inverter. The twelve pulse rectifiers draw current from the supply in pulses and creates harmonics of order  $12k \pm 1$  at the source side [29]. The inverter synthesizes a sinusoidal output voltage with alternating DC pulses of different widths. There is therefore an inherent harmonic content in the output voltages and currents of the inverter. The transformers in the system may also cause harmonics if operated above rated power, voltage or frequency. This can cause the transformer to saturate and exhibit a nonlinear magnetizing current [29]. Transformer saturation is however not modelled in this work.

Using a delta connected transformer traps third harmonic currents, and these are not transferred to the wye (load) side [5]. This does however reduce the capacity of the transformer because of the circulating harmonic currents.

Based on IEC 61000-2-4, Det Norske Veritas (DNV) states "the total voltage harmonic distortion shall not exceed 8 %. In addition no single order harmonic shall exceed 5 %." [30]. In addition, IEEE recommends that the total current harmonic distortion at nominal load should not exceed 5 % [31]. This will be used as the limits in this thesis.

# 3 System Modelling

All models are implemented in Matlab/Simulink with the SimPowerSystems toolbox.

## 3.1 External Power Supply Modelling

The external power supply is a 25 MW gas turbine connected to the jack-up rig via a subsea AC cable. It is assumed that the external supply has a robust power management system that manages to keep the supply line voltage constant regardless of the jack-up side load. The external power supply is therefore modelled as a 36 kV three-phase voltage source with a resistance and inductance. The resistance and inductance represent the subsea cable as explained in the next paragraph. The external generator has a sub-transient reactance,  $X''_d = 18$  %. As the gas turbine most likely operates at a lower voltage than 36 kV, this means that a transformer is needed on the supply side. The modelling of this is not studied in this thesis.

## 3.2 Subsea Cable Modelling

The supply-line voltage level is chosen to be 36 kV. With the nominal load, S = 16.6 [MVA], the nominal cable RMS line current is 266.2 A. Adding a 10 % safety margin, the cable should be able to carry 292.85 A. High voltage is chosen to limit currents, losses, and cable diameter. The cable parameters are based on a suitable cable from Nexans [32]. The datasheet is included in Appendix H. The RL parameters are summarized in Table 2:

| Conductor AC resistance $[\Omega/km]$ | Inductance [mH/km] |

|---------------------------------------|--------------------|

| 0.26                                  | 0.4                |

| Table 2 – Subsea cable data           |                    |

As the distance between the supply unit and the jack-up rig is unknown, it is arbitrarily assumed 1 km, and hence the short line model described in 2.4 is used. The supply line frequency is 50 Hz.

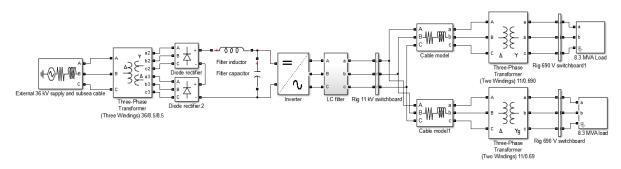

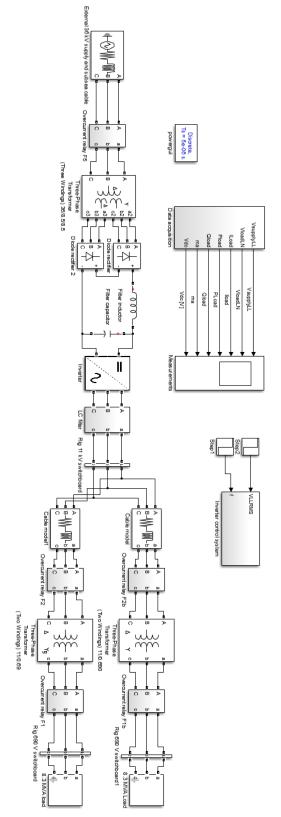

## 3.3 Interconnection Topology

In this thesis, only one cable and one feeding point is considered in simulation models. The Simulink model of the interconnection and two load islands is depicted in Figure 12. The bus tie on the LVDC bus is open and therefore not included.

Figure 12 – Simulink model of interconnection topology and load model.

As Figure 12 illustrates, the sub-sea cable is connected to a three winding transformer that supplies a frequency changer. The frequency changer consist of a twelve-pulse rectifier, a DC link filter, a VSC, and an output filter. To study the effect of, and on, the low voltage loads, two

load islands with a two winding transformer and a load model is included. The modelling of all these components are described in the following.

## 3.4 Jack-up Rig Cables

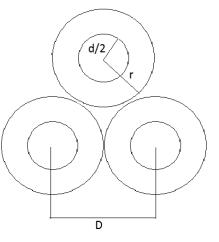

As faults are studied in this work, approximate values of the HV side cable parameters are calculated. The load side LVAC cables are considered negligible because of the short distance, and because the fault are studied at the transformer terminals and above. The cable resistance are based on the "BATT cables, 11kV 3 core SWA PVC Cable BS6622" cable [33], and is set to  $R = 60 \ [\mu\Omega/m]$  at 90<sup>o</sup> C. The length of the cables are assumed to be 30 m. The cable inductance is calculated in Appendix F, and is  $L = 0.327 \ [\mu H/m]$ .

## 3.5 Three Winding Transformer Model

As this transformer would have to be custom made to the application, the transformer impedance values are unknown. Based on usual transformer impedance values, the values chosen that satisfy Eq. 1, Eq. 2 and Eq. 3 are summarized in Table 3.

| Winding:         | Primary (Z1) | Secondary (Z2) | Tertiary (Z3) | Magnetizing |

|------------------|--------------|----------------|---------------|-------------|

| Resistance [pu]: | 0.005        | 0.001          | 0.001         | 300         |

| Inductance       | 0.035        | 0.035          | 0.035         | 200         |

| [pu]:            |              |                |               |             |

Table 3 – Three winding transformer inductances and resistances.

The rated power of the transformer is 17 MVA, and the rated frequency is 50 Hz. The per unit values are based on the nominal power, frequency and winding voltage as in [34]. The primary/secondary/tertiary voltage ratios are: 36/8.5/8.5. These values are used in the premade "three winding transformer" model included in SimPowerSystems. Transformer saturation is not modelled.

## 3.6 Twelve Pulse Rectifier

Two full bridge diode rectifiers connected in series are used. The rectifiers are pre-made models in SimPowerSystems. Each rectifier are feed from the three winding transformer with a line-to-line RMS voltage of 8500 V to yield an approximate DC voltage of 23 kV (resistive losses and voltage drop due to current commutation excluded). As the average maximum currents through the diodes are about 660 A at nominal load, this is within commercially available diode ratings. The maximum steady state repetitive reverse blocking voltage over each diode is half the DC link voltage, i.e. 12.5 kV. As this is higher than commercially available diode ratings at the time of writing, multiple diodes in series are used. One of the highest rated diodes available at the time of writing is the "Infineon D 711N" rectifier diode with a maximum repetitive reverse voltage,  $V_{RRM} = 6800 V$ , and an maximum average forward current,  $I_{FAVM} = 790 A$  [35], at 100° C. A part of the datasheet is included in Appendix H.

To accommodate the voltage, and as with the IGBTs in 2.7.5.2, include a 20 % safety margin, this means that at least three diodes are needed in series in each diode valve. In reality, the absolute maximum reverse voltage should be considered, but as limiting of inrush currents/soft start circuits not are studied in this thesis, the maximum voltages are unknown and 23 kV with at 20 % safety margin is assumed.

#### 3.7 DC Link Filter Inductor Model

The maximum current ripple are set to 2 % of the nominal load current:

$$\Delta i_L = \frac{0.02P_N}{V_{DC}} = \frac{0.02 * 15 MW}{23 kV} \approx 13 A$$

Eq. 39

The filter inductance, with  $V_{LL}$  = 8500 V, using Eq. 4 and Eq. 39, becomes L = 13.63 mH. Actual simulations proved this to give a good accuracy, as depicted in Figure 13, where  $\Delta i_L \approx 14 A$ .

Figure 13 – 14 A current ripple on DC link

#### 3.8 DC Link filter Capacitor Model

The allowed voltage ripple are set to 0.5 % of the average DC voltage,  $V_{do}$ , i.e.  $\Delta V = 0.005*23000 \text{ V} = 115 \text{ V}.$

Inserting the values in Eq. 5, with  $f_{sw}$  = 4860 Hz (from 2.7.5.5) yield a capacitance of C = 1.2 mF. Actual simulations yielded an acceptable ripple of 100 V as depicted in Figure 14.

Figure 14 – DC link voltage ripple of about 100 V.

#### 3.9 DC Link Voltage Level

Using Eq. 7, with  $m_a = 1$  as a constraint, the required DC voltage is:  $V_{DC} \ge 18$  kV. The choice of voltage level depend on, among other things, desired system performance and cost. If the system connected has a large nominal load, and there are high transmission losses from the source supplying the DC link, the DC voltage will vary significantly with load. Changes in load and inrush currents may also cause transients in the DC voltage. Therefore, to ensure linear operation at all times, the no load DC voltage level should be higher than the minimum level so that it does not go below the minimum level during heavy load or transients. In this model,  $V_{DC}$  is chosen to be 23 kV to have good margin and allow linear operation even with oscillations in the DC voltage. This means that  $m_a = 0.78$  at nominal voltage with ideal components and no load.

### 3.10 Voltage Source Converter Model

In the frequency changer, a single two level voltage source inverter is supplying the entire load the control system presented in 2.7.5.6. Although multiple inverters may be considered for redundancy, implementing load sharing controllers and power management systems associated with multiple inverters in parallel are outside the scope of this thesis. The inverter uses IGBTs because of the higher current handling capability compared to metal oxide semiconductor field effect transistors (MOSFETS) [18]. The output fundamental frequency is,  $f_1 = 60$  Hz. The modelling of the VSC components are described in the following.

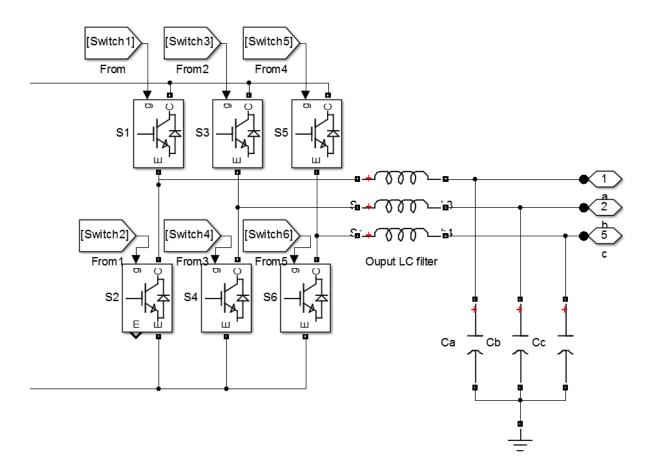

#### 3.10.1 IGBT Valves Simulink Model

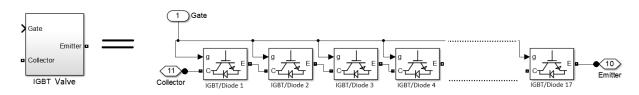

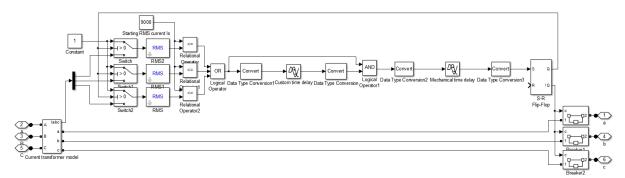

One of the highest rated IGBTs commercially available at the time of writing is rated with a collector-emitter voltage,  $V_{CES} = 1700 V$  and nominal collector DC current,  $I_{c,nom} = 2400 A$  [36]. To accommodate the high voltage, several IGBTs are connected in series, together constituting an IGBT valve. The DC voltage is 23 kV, so using Eq. 6, the number of IGBTs in series needed are 23 kV / 0.8\*1.7 kV = 16.9  $\approx$  17. The Simulink model is illustrated in Figure 15: