# Multilevel Converters for Offshore Wind Systems

A Comparative Study

### Abel Assegid Taffese

Wind Energy Submission date: August 2014 Supervisor: Tore Marvin Undeland, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

### Multilevel Converters in Offshore Wind Systems

A Comparative Study

Abel A. Taffese

30 July, 2014

European Wind Energy Master - EWEM- Electric Power System Track

# Multilevel Converters in Offshore Wind Systems A Comparative Study

MASTER OF SCIENCE THESIS

For obtaining the degree of Master of Science in Electrical Engineering at Delft University of Technology and in Technology-Wind Energy at Norwegian University of Science and Technology.

Abel A. Taffese

30 July, 2014

European Wind Energy Master - EWEM DUWIND - Delft University of Technology Norwegian University of Science and Technology

Copyright © Abel A. Taffese All rights reserved.

### EUROPEAN WIND ENERGY MASTER - EWEM

$\mathbf{OF}$

#### ELECTRIC POWER SYSTEM TRACK

The undersigned hereby certify that they have read and recommend to the European Wind Energy Master - EWEM for acceptance a thesis entitled "Multilevel Converters in Offshore Wind Systems" by Abel A. Taffese in partial fulfillment of the requirements for the degree of Master of Science.

Dated: 30 July, 2014

Supervisor: prof.dr.end. Tore M. Undeland of Norwegian University of Science and Technology

# **Problem Statement**

Offshore wind farms are getting more attention because of stronger and steadier wind compared to on-land farms. Economic benefits and growing opposition from environmental activists against onshore wind farms, are also the driving factors for offshore installations. Different farm layouts have been developed in light of cost effectiveness, power system stability, and contingency management. Among these layouts, the ones involving DC transmission are favored because of possibility of longer step-out and connection to weak points in the grid.

Accompanying these DC links, are high voltage power electronic converters at different points in the system. There are different converter topologies advertised by main players in the industry and academic researchers. The market of these converters is shifting towards Modular Multilevel Converters (MMC) because of their modular design, reliability and a number of attractive features. However, the development of such converters is at its early stage. Therefore, more investigation is required to understand their operation and quantify their merit in contrast to existing proven technology. Comparison of these topologies with respect to generated harmonics, power loss, ease of control, and cost, is main goal of this thesis.

The thesis will be approached in three phases: Phase I, preliminary research to identify three dominant topologies; Phase II, detailed comparison using simulation of the selected topologies to come up with the most promising candidate; Phase III, validate the theoretical work with experiment on the selected candidate topology. The thesis was proposed by Statiol and it involves both analytic and experimental work.

Assignment Given: Feb 2014, Trondheim Supervisor: Prof. Tore M, Undeland

# Summary

Offshore Wind systems have recently gained popularity. However, as the distance from shore increase, different challenges arise. The use of HVDC link to shore helps to overcome most of the challenges. Current Source converters have long been used as HVDC converters despite of their large footprint and reactive power consumption challenges. Recent development in the converter led to the use of Voltage Source Converters (VSC).

There are a number of VSC topologies proposed by the industry and academic researchers. The purpose of this thesis was to compare the dominant converter topologies and identify their merits. The work was done in three phases. Phase I was initial study and literature review where three dominant topologies were selected at the end. Two level VSC, Three level NPC, and Modular Multilevel Converter (M2C) were selected at the end of Phase I.

Phase II involved detailed modelling and simulation of the selected converter topologies. The simulation was mainly focused on harmonics and losses. The M2C was found to produce lower harmonics and losses under the same operating conditions and using the same switching device. The M2C also exhibits modular design which gives it scalability. This is critical in todays power system which changes very frequently. The M2C was selected for next phase analysis because of the above and a number of other reasons.

Phase III was the final part which included practical work on the selected topology. This task was undertaken on a small scale setup of M2C with 3 cells. The purpose of the setup was to verify theoretical results obtained from simulation. The results showed good correspondence with the ones obtained from simulation. The overall study pointed in the direction of M2C for future HVDC installations despite of the capacitor ripple and complex control challenges.

# Acknowledgements

I would like to extend my heart felt gratitude to my Supervisors Prof. Tore M. Undeland and Prof. J.A. Ferreira for their invaluable comments and support. I would also like to thank everyone in the Electric Power Engineering service lab, especially Vladimir Klubicka, for their help on the experimental setup.

Delft, The Netherlands 30 July, 2014

Abel A. Taffese

# Contents

| $\mathbf{P}_{\mathbf{I}}$ | Problem Statement v |        |                              |   |   |   |   |   |          |

|---------------------------|---------------------|--------|------------------------------|---|---|---|---|---|----------|

| Sι                        | ımma                | ary    |                              |   |   |   |   |   | vi       |

| $\mathbf{A}$              | cknov               | wledge | ments                        |   |   |   |   |   | viii     |

| Li                        | st of               | Figure | es                           |   |   |   |   |   | xiii     |

| $\mathbf{Li}$             | st of               | Tables | 5                            |   |   |   |   |   | XV       |

| A                         | crony               | yms    |                              |   |   |   |   |   | xvii     |

| 1                         | Intr                | oducti | on                           |   |   |   |   |   | 1        |

|                           | 1.1                 | Harmo  | onics                        |   |   |   |   |   | 2        |

|                           | 1.2                 | Power  | Loss                         |   |   |   |   |   | 3        |

|                           | 1.3                 | DC Fa  | ult Management               | • |   |   |   |   | 3        |

|                           | 1.4                 | Conve  | rter Topologies              |   |   |   |   |   | 3        |

|                           | 1.5                 | Thesis | Outline                      | • | • | • | • | • | 4        |

| <b>2</b>                  | Cas                 | e Stud | y Model                      |   |   |   |   |   | <b>5</b> |

|                           | 2.1                 | Introd | uction                       |   |   |   |   |   | 5        |

|                           | 2.2                 | Shared | l System Components          | • | • | • |   | • | 5        |

|                           |                     | 2.2.1  | Grid Models                  |   |   |   |   |   | 6        |

|                           |                     | 2.2.2  | DC Cables                    |   |   |   |   |   | 6        |

|                           |                     | 2.2.3  | Converter Stations           | • |   |   |   |   | 6        |

|                           |                     | 2.2.4  | Harmonic Filters             | • | • | • |   | • | 7        |

|                           |                     | 2.2.5  | System Modelling and Control | • | • | • |   |   | 7        |

|                           | 2.3                 | Quant  | ifying Figures of Merit      |   |   |   |   |   | 14       |

|   |     | 2.3.1  | Harmonic Content                  | 14 |

|---|-----|--------|-----------------------------------|----|

|   |     | 2.3.2  | Converter Losses                  | 14 |

|   |     | 2.3.3  | Implementation of the calculation | 17 |

| 3 | Two | o Leve | el VSC                            | 19 |

|   | 3.1 | Introd | luction                           | 19 |

|   | 3.2 | Opera  | ation Principle                   | 19 |

|   | 3.3 | Modu   | lation                            | 21 |

|   | 3.4 | Analy  | <i>r</i> sis                      | 21 |

|   |     | 3.4.1  | DC Side Voltage Ripple            | 23 |

|   |     | 3.4.2  | AC Side Current Ripple            | 24 |

|   | 3.5 | Dimer  | nsioning                          | 27 |

|   |     | 3.5.1  | DC Capacitor                      | 27 |

|   |     | 3.5.2  | Series Reactor                    | 28 |

|   |     | 3.5.3  | Switching Devices                 | 28 |

|   | 3.6 | Contr  | ol                                | 28 |

|   |     | 3.6.1  | Inner Current Loop                | 28 |

|   |     | 3.6.2  | Outer P,Q Controller              | 30 |

|   |     | 3.6.3  | DC Voltage Regulator              | 32 |

|   | 3.7 | Simula | ation                             | 33 |

|   |     | 3.7.1  | Controller Performance            | 33 |

|   |     | 3.7.2  | Harmonics                         | 35 |

|   |     | 3.7.3  | Loss                              | 36 |

| 4 | Thr | ee Lev | vel NPC VSC                       | 37 |

|   | 4.1 | Introd | luction                           | 37 |

|   | 4.2 | Opera  | ating Principle                   | 37 |

|   | 4.3 | Modu   | lation                            | 38 |

|   | 4.4 | Analy  | rsis                              | 41 |

|   |     | 4.4.1  | Mid point current                 | 41 |

|   |     | 4.4.2  | DC Voltage Ripple                 | 41 |

|   | 4.5 | Dimer  | nsioning                          | 42 |

|   | 4.6 | Contr  | ol                                | 42 |

|   | 4.7 |        | ation                             | 42 |

|   |     | 4.7.1  | Harmonics                         | 42 |

|   |     | 4.7.2  | Loss                              | 44 |

| <b>5</b> | Mo            | dular Multilevel Converters (M2C)                                                                         | 45 |  |  |  |  |

|----------|---------------|-----------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|          | 5.1           | Introduction                                                                                              | 45 |  |  |  |  |

|          | 5.2           | Principle of Operation                                                                                    | 46 |  |  |  |  |

|          | 5.3           | Modulation Techniques                                                                                     | 47 |  |  |  |  |

|          |               | 5.3.1 High Frequency Techniques                                                                           | 47 |  |  |  |  |

|          |               | 5.3.2 Fundamental Frequency Techniques                                                                    | 48 |  |  |  |  |

|          | 5.4           | Analysis                                                                                                  | 49 |  |  |  |  |

|          | 5.5           | Dimensioning                                                                                              | 55 |  |  |  |  |

|          |               | 5.5.1 Capacitance                                                                                         | 55 |  |  |  |  |

|          |               | 5.5.2 Arm Inductance                                                                                      | 57 |  |  |  |  |

|          | 5.6           | Control                                                                                                   | 57 |  |  |  |  |

|          |               | 5.6.1 Voltage Balancing                                                                                   | 57 |  |  |  |  |

|          |               | 5.6.2 System Control                                                                                      | 58 |  |  |  |  |

|          | 5.7           | Simulation                                                                                                | 60 |  |  |  |  |

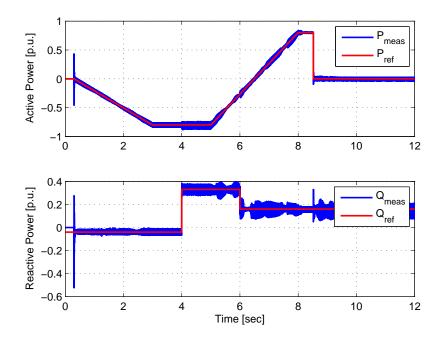

|          |               | 5.7.1 Controller Performance                                                                              | 60 |  |  |  |  |

|          |               | 5.7.2 Harmonics $\ldots$ | 60 |  |  |  |  |

|          |               | 5.7.3 Losses $\ldots$    | 64 |  |  |  |  |

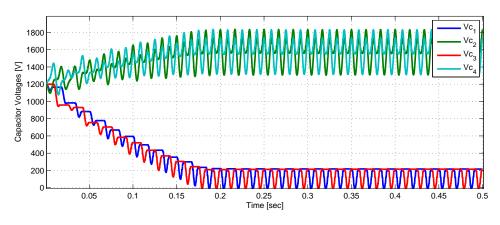

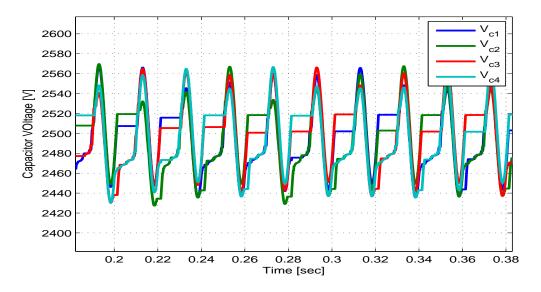

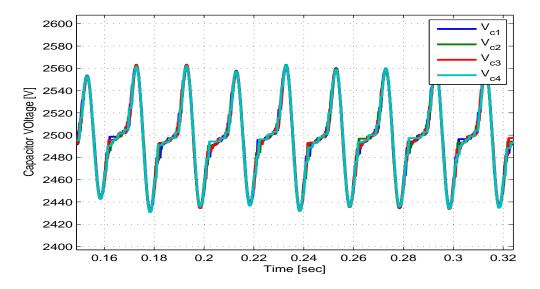

|          |               | 5.7.4 Capacitor Voltages                                                                                  | 64 |  |  |  |  |

| 6        | Comparison 6' |                                                                                                           |    |  |  |  |  |

|          | 6.1           | Industry Experience                                                                                       | 69 |  |  |  |  |

| 7        | Exp           | perimental Work                                                                                           | 73 |  |  |  |  |

|          | 7.1           | Objective                                                                                                 | 73 |  |  |  |  |

|          | 7.2           | Scope                                                                                                     | 73 |  |  |  |  |

|          | 7.3           | System Description                                                                                        | 73 |  |  |  |  |

|          |               | 7.3.1 Hardware                                                                                            | 74 |  |  |  |  |

|          |               | 7.3.2 Software                                                                                            | 76 |  |  |  |  |

|          | 7.4           | Simulation Benchmark                                                                                      | 77 |  |  |  |  |

|          | 7.5           | Experimental Results                                                                                      | 80 |  |  |  |  |

| 8        | Cor           | nclusion and Future Work                                                                                  | 85 |  |  |  |  |

# List of Figures

| 1.1  | Mixed AC/DC Wind farm layout                                                         |

|------|--------------------------------------------------------------------------------------|

| 2.1  | Case Study Model block diagram                                                       |

| 2.2  | $\pi$ model for medium length line                                                   |

| 2.3  | Different harmonic filters                                                           |

| 2.4  | High level system model components                                                   |

| 2.5  | PLL block diagram                                                                    |

| 2.6  | Simplified AC side circuit                                                           |

| 2.7  | Plant block diagram in $dq$ -frame                                                   |

| 2.8  | IGBT Datashet parameters 16                                                          |

| 2.9  | Diode Datashet parameters 16                                                         |

| 2.10 | Cauer equivalent of the thermal network                                              |

| 3.1  | Two level VSC circuit                                                                |

| 3.2  | Half bride converter and its operation                                               |

| 3.3  | Triangle comparison modulation waveforms                                             |

| 3.4  | Common mode injection on the reference                                               |

| 3.5  | DC side current, $m_f = 27, V = 0.9p.u., I = 0.8p.u., \phi = \frac{\pi}{6} \dots 24$ |

| 3.6  | Capacitor ripple for for two choice of capacitance                                   |

| 3.7  | Equivalent circuit for AC side ripple                                                |

| 3.8  | Output voltage and ripple component                                                  |

| 3.9  | Output current ripple and its spectrum, $m_f = 27$                                   |

| 3.10 | Frequency response of the current controller for different values of inductance      |

| 3.11         | Step response of the current controller for different values of inductance        | 30       |

|--------------|-----------------------------------------------------------------------------------|----------|

| 3.12         | Frequency response of the P controller                                            | 31       |

| 3.13         | Step response of the P controller                                                 | 31       |

| 3.14         | Step response of the DC bus regulator                                             | 32       |

| 3.15         | Load current disturbance response of DC bus regulator                             | 33       |

| 3.16         | Active and Reactive Power tracking in the Offshore Station controller             | 34       |

| 3.17         | $V_{dc}$ regulation and Reactive Power tracking in the Onshore station controller | 34       |

| 3.18         | Phase to neutral voltage of offshore converter                                    | 35       |

|              | Line current of offshore converter                                                | 36       |

|              | Loss under different conditions                                                   | 36       |

| 4 1          |                                                                                   | 97       |

| $4.1 \\ 4.2$ | Three level NPC circuit                                                           | 37<br>39 |

| 4.2          | Modulation waveforms for three level NPC                                          | 40       |

| 4.3<br>4.4   | Phase to neutral voltage of offshore converter, NPC                               | 40<br>43 |

| 4.5          | Mid point current of offshore converter, NPC                                      | 43       |

| 4.6          | Line current of offshore converter, NPC                                           | 44       |

| 4.7          | Loss under different conditions, NPC                                              | 44       |

| 4.7          |                                                                                   | 44       |

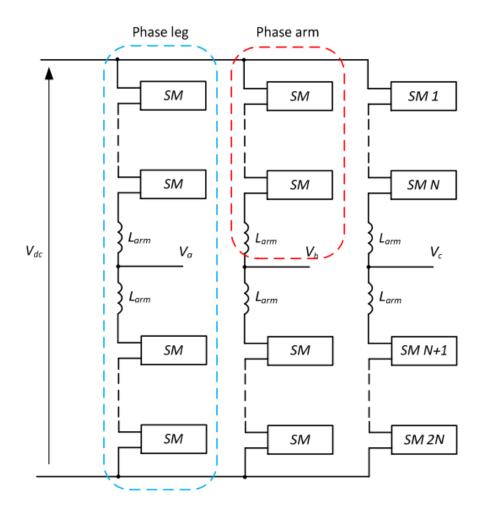

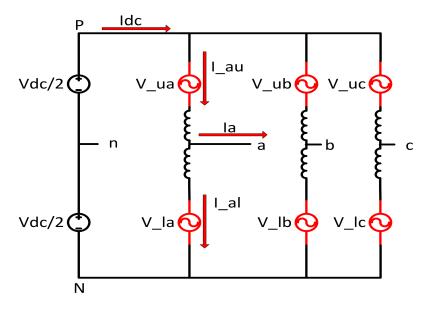

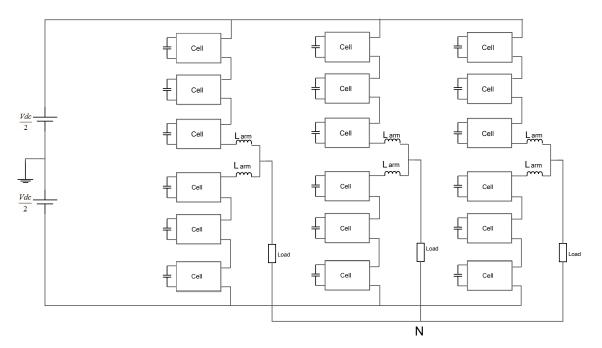

| 5.1          | M2C Basic Structure                                                               | 46       |

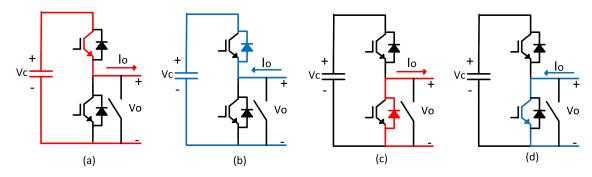

| 5.2          | Half Bridge cell and its operating modes                                          | 47       |

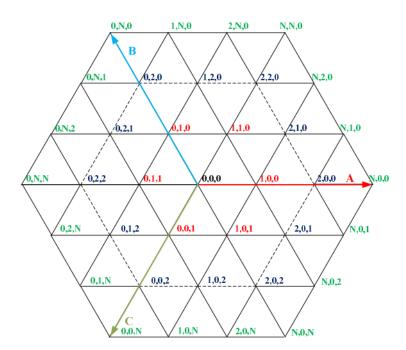

| 5.3          | Switching states of Space vector Modulation $[2]$                                 | 48       |

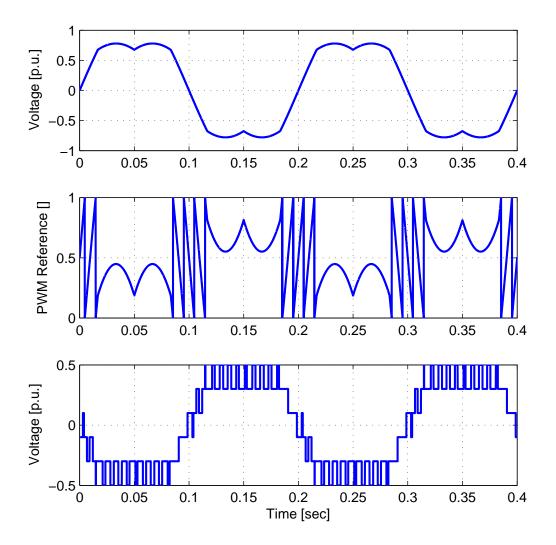

| 5.4          | M2C Modulation Waveforms                                                          | 50       |

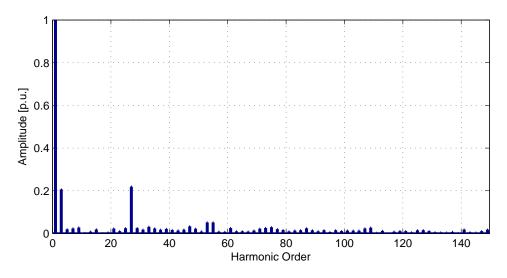

| 5.5          | Harmonics in 5 cell M2C, $m = 0.9$ , $m_f = 27$                                   | 51       |

| 5.6          | Model of M2C as voltage source                                                    | 52       |

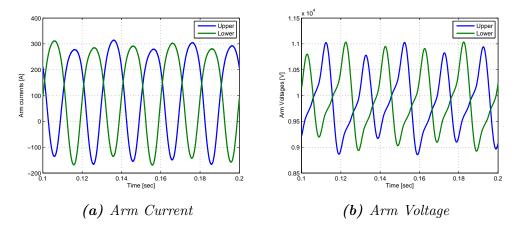

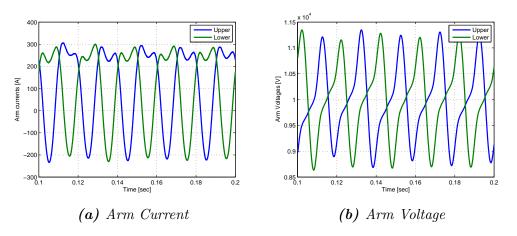

| 5.7          | Arm voltages and currents with large arm inductance                               | 54       |

| 5.8          | Arm voltages and currents with large arm inductance                               | 54       |

| 5.9          | Capacitor voltages without balancing algorithm, 4 cell                            | 58       |

| 5.10         | Capacitor voltages with sorting method                                            | 59       |

| 5.11         | Capacitor voltages with sorting method and supplementary logic                    | 59       |

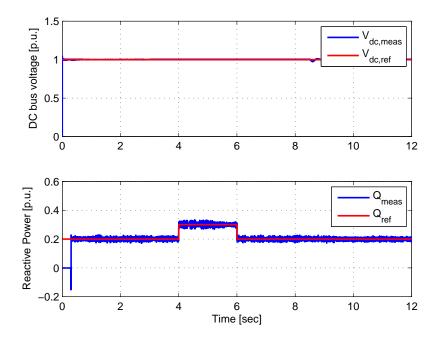

| 5.12         | Offshore Active and Reactive Power response, M2C                                  | 61       |

| 5.13         | Offshore DC bus voltage and Reactive Power response, M2C                          | 61       |

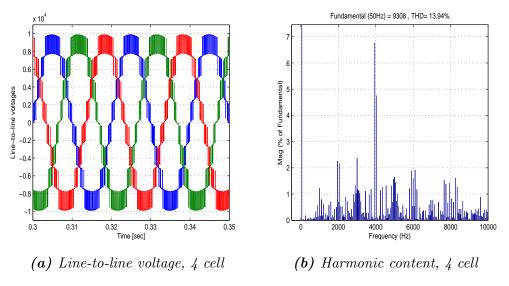

| 5.14         | 4 cell MMC                                                                        | 62       |

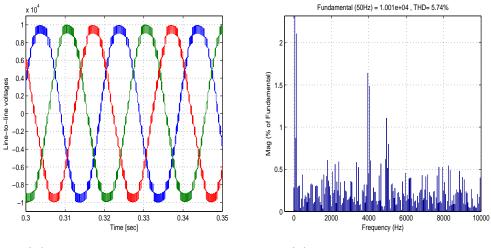

| 5.15         | 8 cell MMC                                                                        | 63       |

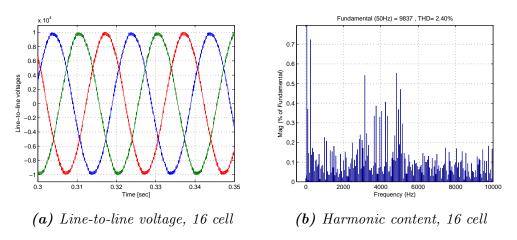

| 5.16         | 16 cell MMC                                                                       | 63       |

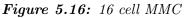

|              | 32 cell MMC                                                                       | 63       |

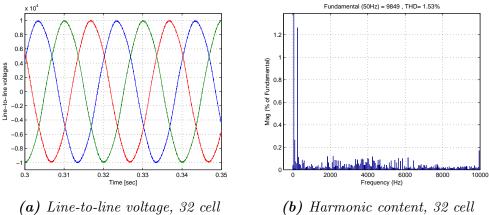

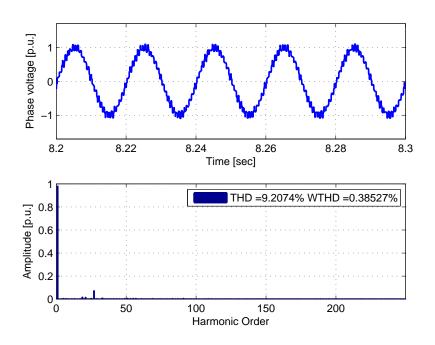

|              | Phase voltage and its harmonic spectrum, M2C                                      | 64       |

| 5.19         | Phase current and its harmonic spectrum, M2C                                      | 65       |

| 5.20 | Losses under different conditions, M2C                                                         | 65 |

|------|------------------------------------------------------------------------------------------------|----|

| 5.21 | Capacitor voltages when transferring Active Power                                              | 66 |

| 5.22 | Capacitor voltages when transferring Reactive Power                                            | 66 |

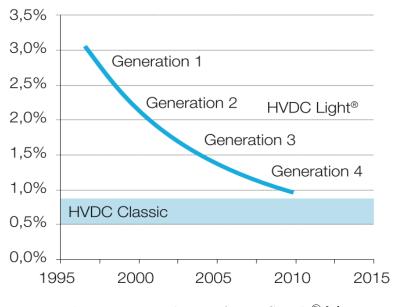

| 6.1  | Evolution of HVDC Light <sup>®</sup> [3] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 70 |

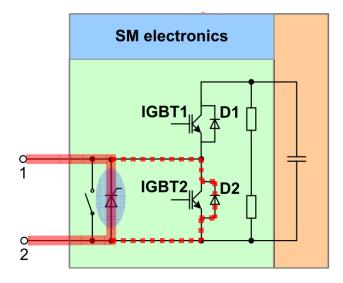

| 6.2  | Fault Protection in HVDC PLUS <sup>®</sup> Sub-module [4] $\ldots \ldots \ldots$               | 71 |

| 6.3  | Evolution of VSC based HVDC Converters [5]                                                     | 72 |

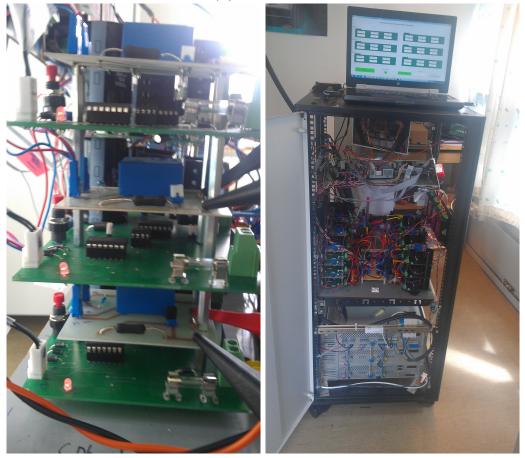

| 7.1  | Practical setup of 3 cell M2C converter circuit                                                | 74 |

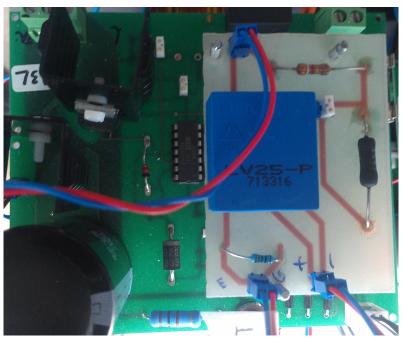

| 7.2  | Pictures of the experimental setup                                                             | 75 |

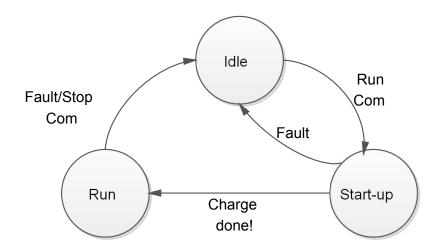

| 7.3  | Main state machine                                                                             | 76 |

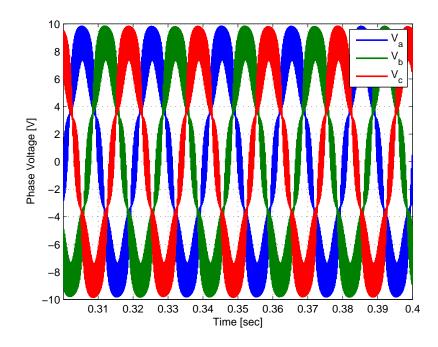

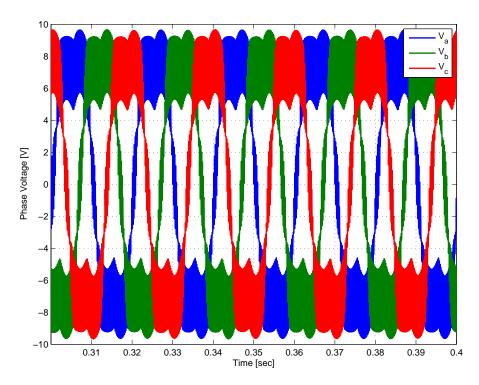

| 7.4  | Three phase voltages with grounded neutral, Simulations $\ldots$ .                             | 78 |

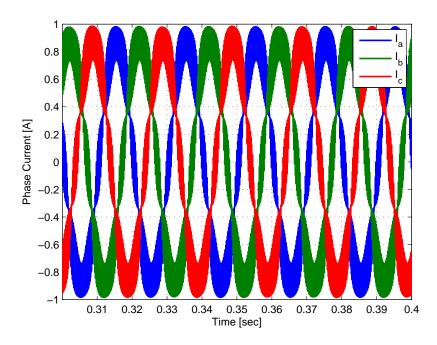

| 7.5  | Three phase Currents with grounded neutral, Simulations                                        | 79 |

| 7.6  | Three phase voltages with grounded neutral and Harmonic injection, Simulations                 | 79 |

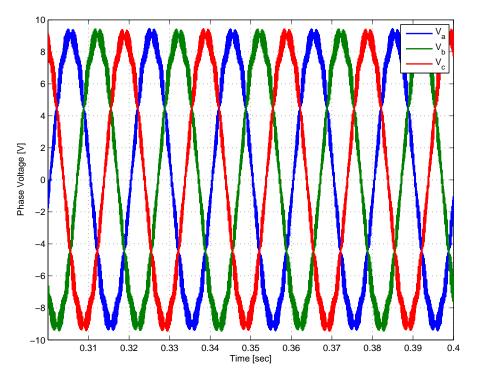

| 7.7  | Three phase voltages with out grounded neutral, Simulations                                    | 80 |

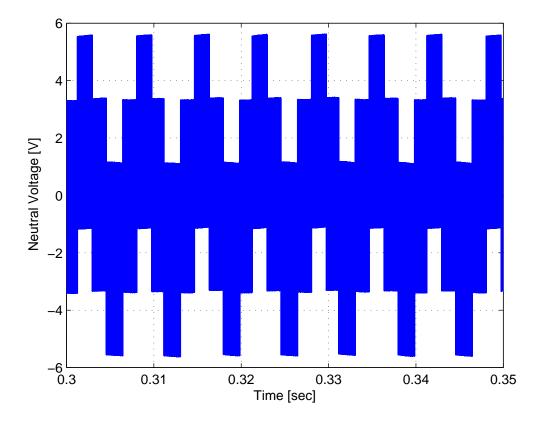

| 7.8  | Neutral voltage referred to DC mid point, Simulations                                          | 81 |

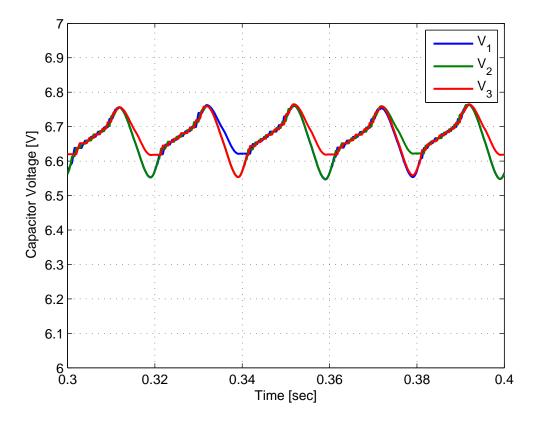

| 7.9  | Capacitor voltages, Simulations                                                                | 82 |

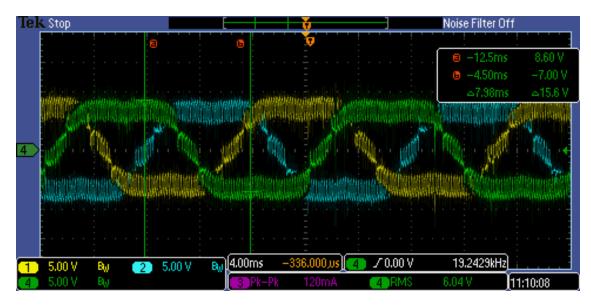

| 7.10 | Three phase Currents with grounded neutral, Experiment                                         | 82 |

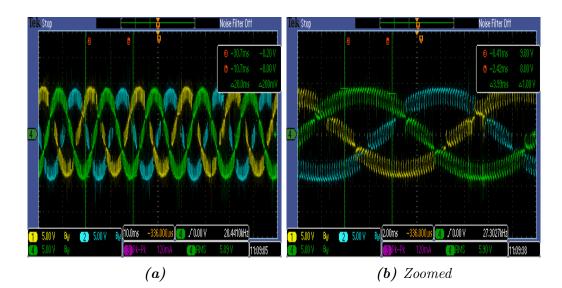

| 7.11 | Three phase voltages with grounded neutral and Harmonic injection,<br>Experiment               | 83 |

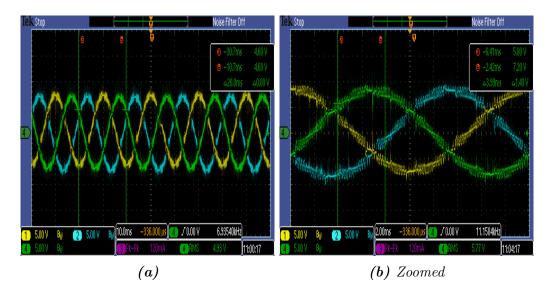

| 7.12 | Three phase Currents without grounded neutral, Experiment                                      | 83 |

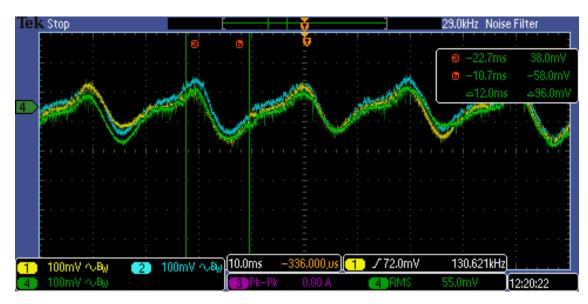

| 7.13 | Capacitor voltages, Experiment                                                                 | 84 |

# **List of Tables**

| 2.1 | DC cable parameters                       | 7  |

|-----|-------------------------------------------|----|

| 3.1 | Operating states of Half bridge converter | 20 |

| 4.1 | Switching States of NPC converter         | 38 |

|     | Half Bridge Cell Operating Modes          |    |

| 6.1 | Summary of comparison of the topologies   | 69 |

| 7.1 | Circuit parameters of the converter       | 74 |

| 7.2 | parameters of the Test Setup, Simulation  | 78 |

## Acronyms

- AC Alternating Current

- DC Direct Current

- HVDC High Voltage Direct Current

- VSC Voltage Source Converter

- CSC Current Source Converter

- NPC Neutral Point Clamped

- M2C Modular Multilevel Converter

- EMI Electromagnetic Interference

- PI Proportional-Integral

- PLL Phase Locked Loop

- MO Modulus Optimum

- SO Symmetric Optimum

- THD Total Harmonic Distortion

- WTHD Weighted Total Harmonic Distortion

- IGBT Insulated Gate Bipolar Transistor

# Chapter 1

## Introduction

Offshore wind farms are getting more attention because of stronger and steadier wind compared to on-land farms. Economic benefits [6] and growing opposition from environmental activists against onshore wind farms, are also the driving factors for offshore installations. Offshore power systems are typically characterized by challenges in power transmission, grid interface and local grid designs. Different wind farm layout were studied in [7]. Transmission challenges are mainly related to capacitance of AC cables used to connect to onshore system. The problem becomes worse as the distance from shore is increased. HVDC based solution are used to overcome this challenge through the use of DC cables. There are different ways in which the wind farm is laid out: Small AC, Large AC, Mixed AC/DC, Small DC, Large DC and Series DC [7].

Small AC layout does not require offshore station and is very suitable for small wind farms located close to shore. The Large AC has offshore connection point and substation making it a good candidate for large wind farms located at distances where reactive compensation for the cable is acceptable. Local AC grid with DC transmission makeup the Mixed AC/DC layout. AC power coming from each wind turbine is stepped up, collected and rectified at an offshore converter station. Onshore inverter then interfaces the farm to the power system. Small DC and Large DC are similar to the AC counterparts with the transformer station replaced by DC-DC converters and inverters. The Series DC, on the other hand, does not need any transformer or DC-DC converter to connect to HVDC transmission system.

Choice among these layouts is dependent on the specific project and there is no single best solution. But, the industry and researchers are focusing more on the ones with DC transmission because of possibility of longer step-out and connection to weak points in the grid. This fact made power electronic converters very important part of the the power system. Use of power electronics converters introduces other set of problems like harmonics, power losses, and Electromagnetic Interference (EMI).

The main focus of this thesis is to study different power converter used in such a system and compare their performance with respect to these generated harmonics, power loss, scalability, and fault handling capability. These performance measures will be discussed in detail in subsequent sections. The system used to compare the different converters is the Mixed AC/DC layout shown in Figure 1.1.

Figure 1.1: Mixed AC/DC Wind farm layout

### 1.1 Harmonics

Almost all components of a power system generate harmonics at different levels. Among these sources, power converters are one of the dominant ones. In windgenerator systems, these are generated whenever the voltage or current of the converter deviates from the sinusoidal fundamental component. These could be due to the converter topology, characteristic harmonics, or operating point and control scenario of the individual converter, non-characteristic harmonics.

One of the main effects of harmonics is the possibility of amplification of harmonic levels resulting from series and parallel resonances[8]. These resonances are due to the interaction of various inductive elements with capacitive elements like cables and reactive power compensators. Voltage harmonics produce series resonances while current harmonics produce parallel resonances.

A reduction in the efficiency of the generation, transmission and utilization of electric energy is also caused by harmonics. The losses in the system is increased in the presence of harmonics. This is because of two reasons: increased Ohmic losses due to increased RMS current, and losses due to Eddy currents and skin effect.

Harmonics also result in aging of insulation of electrical plant components with consequent shortening of their useful life. They could also cause malfunctioning of system or plant components. This is observed in system components like protection devices and measurement instruments. Interference with external system like communication is also unfavorable effect of harmonics.

If proper measures were not taken in the design of individual wind generator, connecting a wind park to a grid may result in amplification of harmonic content [9]. Having listed some of the effects of harmonics on the power system, it has been taken as one of the measures of performance.

### 1.2 Power Loss

Power losses are due to non-ideality of semiconductor devices and passive components in the converter [10]. There are two types of power losses: conduction loss and switching loss. Conduction losses are caused by nonzero resistance of the switches and passive components. Conduction loss depends on construction of the devices and the number of devices, in a given topology, connected in series.

Switching loss, on the other hand, is caused by overlap between current and voltage during switching. This type of loss is dependent on switching frequency of the switch and the number of switches in the converter. Some converters, like M2C, employ a technique that allows the switches to be switched at lower frequency while the converter is still running at higher frequency.

In optimizing for power loss, the number of components should be kept to the minimum. This reduces both switching and conduction losses. Switching frequency should also be kept minimum to reduce switching loss. These factors will be considered when comparing different converter topologies.

### **1.3 DC Fault Management**

This aspect is specially important when considering Multi-terminal or Meshed HVDC networks. If a DC short circuit occurs, the fault should be isolated without affecting the AC side considerably [11]. This is desired in order for the other, non faulty, terminals to continue transmission. This issue arise because of the absence of simple and inexpensive protection equipment like the AC circuit breakers. This puts a demand on the Converter to have a certain way to isolate such faults by itself.

For point-to-point connection, however, fault handling is not a big issue because there is only one link and if there is a fault it will be disconnected. So the AC side circuit breaker in conjunction with current rise limiter inductance can be used to isolate DC side faults. But Multi-terminal DC grids are inevitable in the future, so having fault isolation capability is advantageous.

### 1.4 Converter Topologies

A number of topologies have been studied in literature for HVDC application. However, in actual installation, the number of topologies is quite low. The topologies fall into two categories; Voltage source and Current source.

### **Current Source Converters**

Current source converter based HVDC stations have long been in the industry with the first installation going back to 1954 [12]. Each node actc as a current source where power flow direction is dictated by polarity of the voltage. These converters use Thyristors, which are line commutated [10], valves as switching devices. Being line commutated, the converters have a reactive power demand which is undesired [13],[14]. For this reason, these converters are slowly being replaced by other topologies.

#### Voltage Source Converters

Voltage source converter emerged for the first time in 1999[15] with the benefits of flexible reactive power support for the grid [5]. From VSCs, three topologies have been used in existing HVDC installations[5]. These are, the two level VSC, three level NPC, and Modular Multilevel Converter. These topologies were selected for detailed study in subsequent chapters.

### 1.5 Thesis Outline

The selected topologies are compared with detailed simulation model. Chapter 2 gives description of the case study model which is used for comparison. Chapters 3,4, and 5 give analysis and simulation results pertaining to each of the selected topologies. Chapter 6 summarizes the comparison. The experimental setup is described in Chapter 7. The thesis then finalizes with conclusion in Chapter 8.

# Chapter 2

# **Case Study Model**

### 2.1 Introduction

After the discussion presented in the previous chapter, three converters have been selected. To perform analysis on these converters, a common framework is required. For this purpose, the case study model was developed. This chapter describes the model in detail. A method to quantify the figures of merit is also presented. It should be noted that the objective of the comparison is not to identify best stateof-the-art converter topology. This would require access to techniques used by the different manufacturers which, in most cases, are confidential. Therefore the comparison will focus on advantages and challenges inherent to each topology. The same semiconductor device will be used in each of the topologies to have a reasonable comparison.

### 2.2 Shared System Components

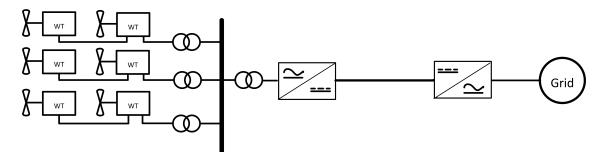

The system used in the comparison is shown in Figure 2.1.

Figure 2.1: Case Study Model block diagram

The system has AC offshore grid that is collected and stepped up before being fed in to the offshore rectifier station. The power is transmitted via a 100 km DC cable to the onshore inverter station that is directly connected to the main grid. The system base values are V = 100 kV and S = 100 MVA, f = 50 Hz. The DC bus voltage is chosen to be 160 kV to achieve 0.9 modulation index with harmonic injection. Some of the components that are common to all the topologies will be discussed in what follows.

#### 2.2.1 Grid Models

The onshore grid is assumed to be strong since it is coupled without transformer and under the assumption that there are large generating stations nearby. A small impedance, equivalent to 4 GVA (40 p.u.), is included to account for transmission system impedance onshore. The offshore grid, on the other hand, is assumed to be coupled via a transformer at the collection point. Therefore, leakage impedance of the transformer, 15%, is included. In either case, the grid is modelled with a stiff voltage source in series with equivalent impedance. Frequency stiffness of the grid is not modelled because the scope of this study does not include frequency dynamics and control.

#### 2.2.2 DC Cables

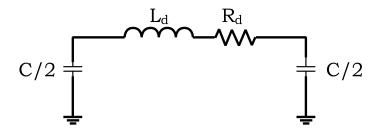

There are two HVDC cables which are 100 km long each. Since 100 km is considered medium length [16]  $\pi$ -model is used for the cable. The model is shown in Figure 2.2 and the parameters are given in Table 2.1.

Figure 2.2:  $\pi$  model for medium length line

### 2.2.3 Converter Stations

The converters are voltage source type which can assume one of the three implementations: Two level, Three level NPC, and Modular Multilevel Converter. For simulation purpose, the converters are modelled as detailed switching converter. This approach takes longer to simulate compared to average models for the same

| Parameter   | Value             |

|-------------|-------------------|

| Resistance  | $10 \ m\Omega/km$ |

| Inductance  | 1 mH/km           |

| Capacitance | 50 nF/km          |

| Length      | 100 km            |

Table 2.1: DC cable parameters

simulation period. But, it allows access to detailed waveforms that enable loss calculation and harmonic analysis. Implementation details vary between the topologies except for the top level system controller. Therefore, only system controller is described here.

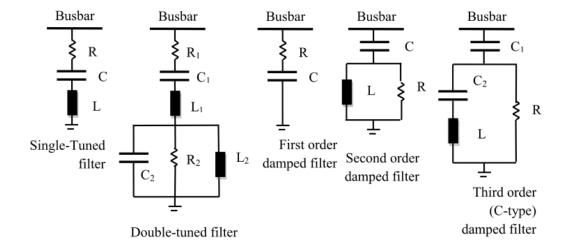

### 2.2.4 Harmonic Filters

Harmonic filters are placed in the system to improve harmonic distortion introduced by the converter. There are a number of ways to provide harmonic filtering that can be grouped in to two: Active and Passive [1]. Active filters are more efficient but they are more expensive. Therefore, passive filters are considered because of the cost advantage. There are different filtering topologies as shown in the Figure 2.3 [1]. Single tuned filter is used to provide low impedance path at a specified frequency. To remove more than one harmonic components a number of filters are connected in parallel. A more economically efficient implementation is to use high pass circuit. Harmonic filters might not be needed in some of the converter because the waveforms are inherently clean.

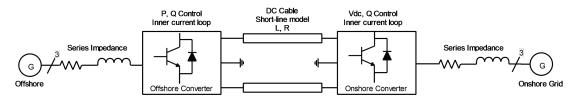

#### 2.2.5 System Modelling and Control

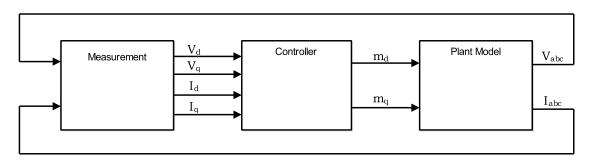

In this section, top level modelling and control of the system will be presented. From the controller's point of view, all the topologies similar; they all produce a commanded AC reference signal. The low level details are disregarded with the exception of delay introduced by the modulator. The system model is divided into three blocks as shown in Figure 2.4. Each of these block will be derived in subsequent sections.

Figure 2.3: Different harmonic filters

Figure 2.4: High level system model components

#### Measurement

This block represents all measurement, transformation, and filtering functions in the converter control. The basic building block is dq0-transform [17] which is used to transform quantities from *abc* reference frame to dq0 frame. A version of the transform, implemented in Simulink, is given in equation (2.1) and equation (2.2).

$$T = \frac{2}{3} \begin{bmatrix} \sin(\omega t) & \sin\left(\omega t - \frac{2\pi}{3}\right) & \sin\left(\omega t + \frac{2\pi}{3}\right) \\ \cos(\omega t) & \cos\left(\omega t - \frac{2\pi}{3}\right) & \cos\left(\omega t + \frac{2\pi}{3}\right) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2.1)

$$T^{-1} = \begin{bmatrix} \sin(\omega t) & \cos(\omega t) & 1 \\ \sin\left(\omega t - \frac{2\pi}{3}\right) & \cos\left(\omega t - \frac{2\pi}{3}\right) & 1 \end{bmatrix}$$

(2.2)

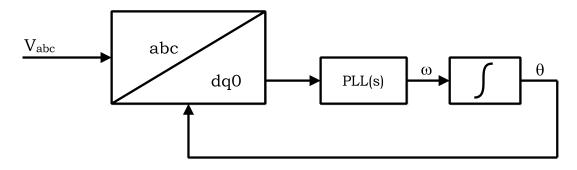

Since the controller is implemented in discrete time, anti-aliasing filters are required to limit frequency range of the input[18]. Detail of the filter design depends on the sampling and switching frequencies which are in turn dependent on the topology. For the transformation to work, it requires phase angle from the grid which is often obtained via the use of Phase Locked Loop (PLL) [19].

$\sin\left(\omega t + \frac{2\pi}{3}\right) \quad \cos\left(\omega t + \frac{2\pi}{3}\right) \quad 1$

A simple PLL configuration is shown in Figure 2.5. A number of other PLL configurations are described in [20] with the aim of improving harmonic rejection and operation under unbalanced conditions. However, for the purpose of this thesis, the simple configuration is adequate and hence adopted. The transfer function PLL(s) represents the compensator which in this case is PI type. Dynamics of the PLL can be approximated by an integrator as long as the error is small. The closed loop transfer function of the PLL is given in equation (2.3).

$$G_{cl}(s) = \frac{k_p s + k_i}{s^2 + k_p s + k_i}$$

(2.3)

The equation has the form of a standard second order transfer function. It can be seen that the controller gains  $K_p$  and  $K_i$  can be independently used to set the

Figure 2.5: PLL block diagram

natural frequency and damping. This make the controller design straightforward. A damping of  $\zeta = \frac{1}{\sqrt{2}}$  and  $\omega_n 2\pi \times 10$  are selected. The controller can be designed to have faster dynamics. But, it is shown that if the controller is too fast, it could result in harmonic resonance and voltage instability [21]. The PLL response is drastically affected by deviation of the initial values of frequency from the nominal values. Therefore, output of the integrator should be saturated not to deviate from the nominal value by large quantity.

#### Plant Model

The plant model is developed with the objective of inner current control and outer P,Q and  $V_{dc}$  control. The plant model takes reference waveforms  $m_d$  and  $m_q$  as inputs and returns phase voltages and current as outputs. The grid and DC side are assumed to be ideal. This results in a simplified single phase equivalent circuit in *abc* frame shown in Figure 2.6. The filter model, shown by dotted lines, is not considered since it does not have significant effect at low frequencies. The filter is normally has corner frequency close to the switching frequency. This allows the aforementioned approximation to be valid as long as the model is used for analysis far below the switching frequency.

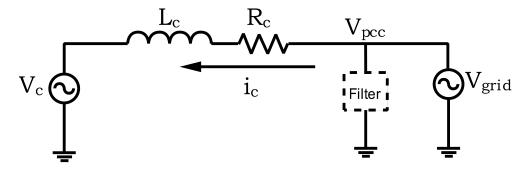

Figure 2.6: Simplified AC side circuit

From Figure 2.6, dynamics of the converter can be derived as shown in what follows. The derivation assumes a balanced system, constant DC bus, and good PLL design.

$$L_c \frac{di_c^{abc}}{dt} = v_{pcc}^{abc} - R_c \cdot i_c^{abc} - v_c^{abc}$$

$$\tag{2.4}$$

$$v_c^{abc} = m^{abc} \cdot \frac{V_{dc}}{2} \tag{2.5}$$

By using dq0 Transform and combining equation (2.4) and equation (2.5), an equation in dq frame can be derived.

$$L_c \frac{d\left(T^{-1}i_c^{dq0}\right)}{dt} = T^{-1} v_{pcc}^{dq0} - R_c \cdot T^{-1} i_c^{dq0} - T^{-1} v_c^{dq0}$$

(2.6)

Left multiplying both sides with T gives the following.

$$L_c T \frac{d\left(T^{-1} i_c^{dq0}\right)}{dt} = v_{pcc}^{dq0} - R_c \cdot i_c^{dq0} - v_c^{dq0}$$

(2.7)

Expanding left hand side of equation (2.7),

$$L_c T \frac{d\left(T^{-1} i_c^{dq0}\right)}{dt} = L_c \left[T \frac{dT^{-1}}{dt} i_c^{dq0} + \frac{di_c^{dq0}}{dt}\right]$$

(2.8)

The first term on the right hand side of equation (2.8) represents mutual coupling between the dynamics along the different axes introduced by the transformation. For a balanced system (0 - axis component ignored), the final plant model becomes

$$L_{c}\frac{d}{dt}\begin{bmatrix}i_{c}^{d}\\\\i_{c}^{q}\\\\i_{c}^{q}\end{bmatrix} = \begin{bmatrix}v_{pcc}^{d}\\\\v_{pcc}^{q}\end{bmatrix} - R_{c}\begin{bmatrix}i_{c}^{d}\\\\i_{c}^{q}\\\\i_{c}^{q}\end{bmatrix} + \begin{bmatrix}0 & \omega L_{c}\\\\-\omega L_{c} & 0\end{bmatrix}\begin{bmatrix}i_{c}^{d}\\\\i_{c}^{q}\\\\\vdots\\i_{c}^{q}\end{bmatrix} - \begin{bmatrix}m^{d}\\\\m^{q}\end{bmatrix} \cdot \frac{V_{dc}}{2}$$

(2.9)

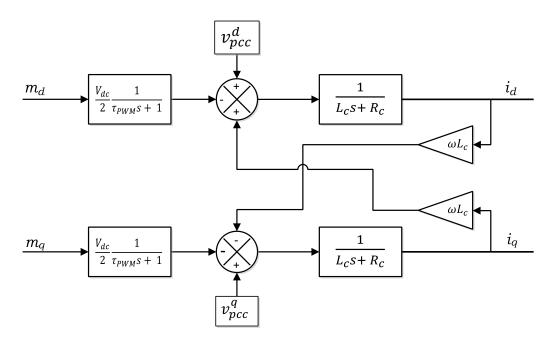

The plant model derived so far does not consider effect of delay in converter due to modulation. To account for the delay a small time constant,  $\tau_{PWM}$ , will be added to the last part of equation (2.9). The delay differs from converter to converter so it will not be quantified here. After Laplace transform is applied to equation (2.9), the complete plant block diagram is shown in Figure 2.7.

Active and Reactive power at the point of common coupling can be calculated from the quantities in dq0-frame as shown in equation (2.10) and equation (2.11).

$$p(t) = \frac{3}{2} \left( v_{pcc}^{d} i_{c}^{d} + v_{pcc}^{q} i_{c}^{q} \right)$$

(2.10)

$$q(t) = \frac{3}{2} \left( v_{pcc}^{q} i_{c}^{d} - v_{pcc}^{d} i_{c}^{q} \right)$$

(2.11)

Figure 2.7: Plant block diagram in dq-frame

Model for DC voltage dynamic varies between the topologies; therefore, it is given under each topology in subsequent chapters.

#### Controller

There are different ways to control a voltage source converter system [18, 22]. Cascaded control topology with PI controllers is adopted for this thesis because of its simplicity and widely acceptable application. The PI controllers in this scheme can be tuned in a number of ways that can be broadly grouped into two: trail-and-error and model-based approaches. Trail and error approach might provide a simple solution when little is known about the system dynamics. However, the controller designed in such a way should be tested thoroughly to avoid unforeseen instabilities. An elegant alternative is to use the model available in the design process. One of the most popular model-based approaches, in control design for power converters, is the use of Modulus Optimum (MO) method for the inner loop and Symmetric Optimum (SO) for the outer loop with slow pole [22]. These tuning criteria are presented in the following paragraphs.

Modulus Optimum: In this method, the plant is assumed to have one dominant time constant and a number of other fast poles that can be grouped together [REF] as shown in equation (2.12).

$$G_p(s) = \frac{K}{(sT_a + 1)(sT_{eq} + 1)}$$

(2.12)

where  $T_a$  is the dominant time constant, K is the plant gain, and  $T_{eq}$  is equivalent time constant other delays, like anti-aliasing filters, in the plant. According to MO criterion, the dominant pole should be canceled by zero of the PI controller which results in the following relations.

$$\frac{k_p}{k_i} = T_a \tag{2.13}$$

$$G_{cl}(s) = \frac{K \cdot k_i}{T_{eq}s^2 + s + K \cdot k_i}$$

(2.14)

where  $kp + \frac{k_i}{s}$  is the assumed controller structure and  $G_{cl}(s)$  is the closed loop transfer function. The second step in MO is to choose the value of  $k_i$  so that the closed loop system has a damping of  $\frac{1}{\sqrt{2}}$ . Referring to equation (2.14), the previous statement implies that  $k_i$  is given by equation (2.15). The closed loop system can be approximated by a first order system with time constant  $2 \cdot T_{eq}$ .

$$k_i = \frac{1}{2 \cdot K \cdot T_{eq}} \tag{2.15}$$

**Symmetric Optimum**: This method is used whenever pole cancellation is not feasible due to the presence of a pole close to the origin. Cancellation of such a pole could ,in best case, deteriorate disturbance rejection performance of the closed loop system and in worst case it could destabilize the system. The plant model considered for SO design is shown in equation (2.16).

$$G_p(s) = \frac{K}{sT_a \, (sT_{eq} + 1)}$$

(2.16)

where  $T_a$  is time constant of the slow pole. The tuning rule in SO is to optimize for maximum phase margin [22]. Zero of the controller forms a lead-lag network with pole of the plant at  $-\frac{1}{T_{eq}}$ . The controller zero is then placed in order to attain maximum phase boost at the desired crossover frequency  $\omega_d$  which is shown in equation (2.17).

$$\omega_d = \frac{1}{\sqrt{T_{eq}T_c}} = \frac{1}{a^2 T_{eq}} \tag{2.17}$$

where  $T_c = \frac{k_p}{k_i}$ , *a* is a design parameter recommended to be between 2 and 4 [22]. The equation derived in this section will be utilized for tuning controllers in subsequent sections.

### 2.3 Quantifying Figures of Merit

Some of the performance metrics are purely qualitative in the context of this thesis: reliability and complexity. Losses and Harmonic content, on the other hand, can be quantified. A method used to calculate these quantities will be given in this section.

#### 2.3.1 Harmonic Content

Comparison of harmonic performance indicators is discussed in [23]. Total Harmonic Distortion (THD) and Weighted Total Harmonic Distortion (WTHD) are used in this thesis. THD is the ratio of RMS value of unwanted components, in the voltage or current waveform, to the desired fundamental component as shown in equation (2.18).

$$THD = \sqrt{\left(\frac{V_{rms}}{V_{1,rms}}\right)^2 - 1} \tag{2.18}$$

where  $V_{rms}$  is the total RMS voltage,  $V_{1,rms}$  is RMS value of the fundamental component. THD is not a good measure of harmonic performance because it only portrays harmonic content not really displaying its significance. WTHD is better because it gives more weight to harmonic components that have the most severe effect; namely, low frequency harmonics. With WTHD it is clear and easy to compare to systems.

$$WTHD = \frac{\sqrt{\sum_{n=2}^{\infty} \left(\frac{V_n}{n}\right)^2}}{V_1} \tag{2.19}$$

where  $V_n$  is the  $n^{th}$  harmonic voltage,  $V_1$  is the fundamental component. Both THD and WTHD will be used to compare the topologies.

#### 2.3.2 Converter Losses

In this section, a method to calculate losses in converter is presented.

#### General equations

The losses in a semiconductor are grouped as conduction and switching losses. Conduction losses are caused by parasitic resistance of the device and overlap between voltage and current after the switching process has completed. Switching losses, on the other hand, are caused by overlap of voltage and current during the switching process. These losses are commonly parameterized with the device on-state voltage and switching energies. The following description will adhere to these conventions.

On state voltages and switching energies of the device are specified as functions of the device current and junction temperature. Dependence on junction temperature will be differed to latter sections. Hence, device on state voltages are given approximately by equation (2.20).

$$v_{on}(i_{dev}) = V_0 + i_{dev} \cdot R_0 \tag{2.20}$$

where  $v_{on}$  is the on-state voltage,  $i_{dev}$  is the device current,  $V_0$  and  $R_0$  are parameters to be determined by curve fitting. The switching energies are denoted by  $E_{on}$ ,  $E_{off}$ , and  $E_{rec}$ . By using these parameters the average switching and conduction losses are given by equation (2.21) and equation (2.22).

$$Pcon, av = \frac{1}{t - t_0} \int_{t_0}^t v_{on}(i_{dev}) \cdot i_{dev} \cdot dt$$

$$(2.21)$$

$$Psw, av = \frac{E_x(i_{dev}, v_{on})}{t - t_0}$$

(2.22)

where x denotes on, off, and rec.

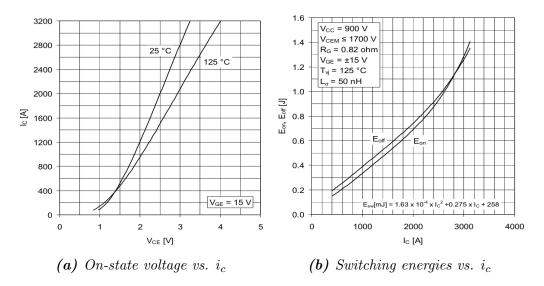

#### **Datasheet Parameters**

In this section, datasheet parameters of the selected device (5SNE0800M170100) will be presented. First, IGBT parameters will be presented. Common notation for the device current and on-state voltage are  $I_c$  and  $V_{ce}$  respectively. Figure 2.8 shows the relevant parameters. It can be seen that the on-state voltage depends only on the device current which makes it possible to implement it using 1-dimensional lookup. The switching energies, however, also depend on the device voltage,  $V_{cc}$  besides the devices current. So, it will be implemented using a 2-dimensional lookup table.

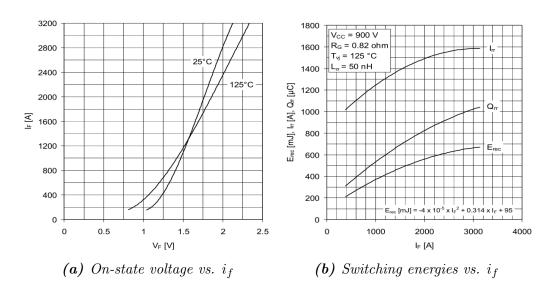

In the same manner, the diode characteristics, on-state voltage and switching energies, can also be found from the datasheet. These parameters are often denoted by  $V_F$  and  $E_{rec}$  respectively. These parameters are shown in Figure 2.9. One peculiar feature of the diode characteristics is that it's turn on and off losses are negligible; but, a phenomena called reverse recovery results what is known are reverse recovery losses denoted by  $E_{rec}$ . This phenomena is related to the finite amount of time it takes to remove the reverse recovery charge stored in the diode. The data points from these graphs will be fed into 1- and 2-dimensional lookup tables similar to the ones described for the IGBT.

Figure 2.8: IGBT Datashet parameters

Figure 2.9: Diode Datashet parameters

#### Junction Temperature Feedback

The parameters, descried so far, are all dependent on the junction temperature. But, the junction temperature is also dependent on the power losses forming a loop. This is a challenge, specifically, for hand calculation and analytic results. One approach to overcome this challenge is to assume a constant junction temperature which might be acceptable in some cases. The second, and more attractive, approach is to incorporate thermal model of the system and dynamically calculate junction temperature and feed it back to the loss calculation.

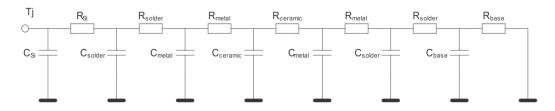

Thermal model of the device is described in the application note [24] where Cauer model was proposed for interconnected systems. The equivalent Cauer model is shown in Figure 2.10.

Figure 2.10: Cauer equivalent of the thermal network

Since the model also includes heatsink properties, the only input required is the ambient temperature. Each of the lookup tables will have one more dimension to account for junction temperature.

#### 2.3.3 Implementation of the calculation

The loss calculation implementation in Simulink<sup>®</sup> is described in this section. The material in this section derived from [25]. For conduction loss, the values from the graph are fed into a 2-D lookup table where the on state voltage can be read for each current. Multiplication of the on state voltage and current gives the conduction loss. The Switching losses uses the voltages and currents just before switching, preswitching, and just after switching, post-switching. Turn on and Turn off losses are described in the following paragraphs.

**Turn-on loss**: Pre-switching value of the voltage across the device, post-switching value of the device current, and the junction temperature are used to read the energy losses from a 3-D lookup table. This energy is converted into a power pulse which is injected into the thermal network. The power pulses are then filtered to get the average turn-on power loss.

**Turn-off loss**: This is similar to Turn-on except for the fact that pre-switching value of the device current and post-switching value of the voltage across the device are used

Reverse recovery loss of the diode is also calculated in a similar fashion.

## Chapter 3

## **Two Level VSC**

### 3.1 Introduction

Two level VSC is the simplest and most studied VSC topology used in HVDC installations. This converter is the first VSC to be used in HVDC installation [26]. The topology is shown in Figure 3.1.

Figure 3.1: Two level VSC circuit

### 3.2 Operation Principle

Two level VSC has a half bridge as its building block as shown in Figure 3.2.

Figure 3.2: Half bride converter and its operation

| $S_1$ | $S_2$ | i <sub>out</sub> | Conducting Device          | V <sub>out</sub> |

|-------|-------|------------------|----------------------------|------------------|

| 0     | 0     | > 0              | $D_2$                      | 0                |

| 0     | 1     | > 0              | $D_2$                      | 0                |

| 1     | 0     | > 0              | $S_1$                      | $V_{dc}$         |

| 0     | 0     | < 0              | $D_1$                      | $V_{dc}$         |

| 0     | 1     | < 0              | $S_2$                      | 0                |

| 1     | 0     | < 0              | $D_1$                      | $V_{dc}$         |

| 1     | 1     | < 0              | $S_1, S_2$ (Short circuit) | 0                |

Table 3.1: Operating states of Half bridge converter

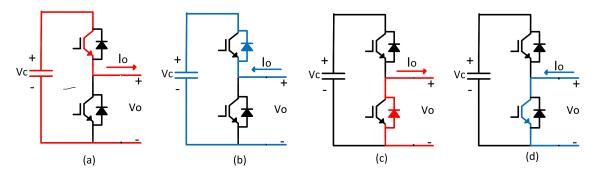

State of the output voltage,  $V_{out}$ , is controlled by inputs  $S_1$  and  $S_2$  (Figure 3.2. The output is either 0 or  $V_{dc}$ . To get AC voltage variation, swing between positive and negative, mid-point of the DC side is taken as reference. This is only required for single phase case. For three phase, there will be three parallel connected half bridges, Figure 3.1, which allows star point of the load connection to be taken as reference.

Conduction state of each device is also dependent on direction of the AC side current, Table 3.1. The last entry in Table 3.1 should be avoided, by using complementary control, as it might damage the converter. Different ways to produce a desired AC waveform using this converter is discussed in next section.

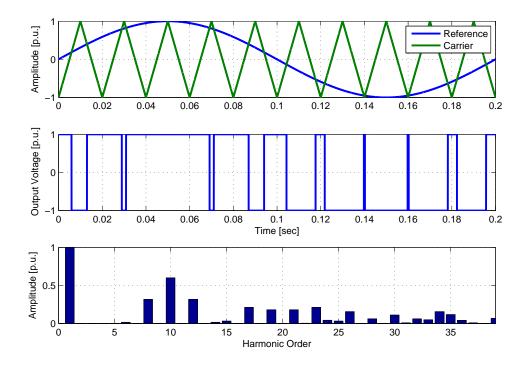

### 3.3 Modulation

Modulation refers to techniques used to control switches in a converter to produce a desired waveform on average. Modulation can also be used to achieve secondary goals: reducing loss and harmonic content. The simplest form of modulation is carrier comparison (Figure 3.3). The operation is very simple; the pulse sent to the top switch is 1 whenever the reference is above the triangle waveform. Harmonic analysis indicate that the output voltage has the correct fundamental component and harmonics centered at multiples of the switching frequency [10]. The frequency modulation ratio,  $m_f$ , is 10 in the figure.

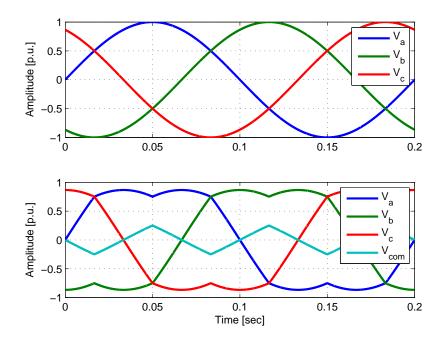

Space Vector Modulation (SVM) is another scheme widely used in VSC which has the advantage of better DC voltage utilization. A similar advantage can be gained by injecting a common mode voltage on top of the phase references (Figure 3.4). There are different ways to generate the common mode voltage depending on the goal. In this analysis, the goal is to extend the DC voltage utilization and hence a triangular common mode voltage, Figure 3.4, as calculated in equation (3.1) is used. Figure 3.4 shows that injection of the common mode results in reduction in the reference waveforms indicating better DC bus utilization.

$$v_{com} = \frac{max(v_a, v_b, v_c) + min(v_a, v_b, v_c)}{2}$$

(3.1)

$$v_{ref,new}^{abc} = v_{ref}^{abc} - v_{com} \tag{3.2}$$

### 3.4 Analysis

The converter's interaction with the AC and DC sides, in steady state, will be analyzed in this section. Main focus is on DC side current and ripple.

Figure 3.3: Triangle comparison modulation waveforms

Figure 3.4: Common mode injection on the reference

$$v_{a} = V \sin(\omega t)$$

$$v_{b} = V \sin\left(\omega t - \frac{2\pi}{3}\right)$$

$$v_{c} = V \sin\left(\omega t - \frac{4\pi}{3}\right)$$

(3.3)

where V is peak of the AC voltage. The AC side current is assumed to be ripple free and having peak I and a phase lag,  $\phi$ , with respect to the voltage.

$$i_{a} = I \sin(\omega t - \phi)$$

$$i_{b} = V \sin\left(\omega t - \frac{2\pi}{3} - \phi\right)$$

$$i_{c} = V \sin\left(\omega t - \frac{4\pi}{3} - \phi\right)$$

(3.4)

### 3.4.1 DC Side Voltage Ripple

From equation (3.3) and equation (3.4), average values of apparent, active, and reactive power are give in equation (3.5).

$$S = \frac{3}{2}VI \quad P = \frac{3}{2}VI\cos(\phi) \quad Q = \frac{3}{2}VI\sin(\phi)$$

(3.5)

Average value of the DC side current in thus:

$$i_{dc,av} = \frac{2}{3} \frac{VI}{V_{dc}} \tag{3.6}$$

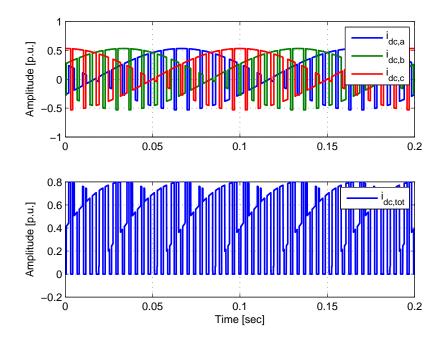

However, the DC side current also contains addition harmonic content due to switching action. The actual current is difficult to write analytically in closed form, therefore a time domain simulated waveform is used for the analysis. Equations (3.7) to (3.9) are used in the calculation of the DC current shown in Figure 3.5.

$$S_x = \begin{pmatrix} 1, & \text{for } S_1 = on \\ \\ -1, & \text{for } S_1 = off \end{pmatrix} \quad x \in \{a, b, c\}$$

(3.7)

$$i_{dc,x} = S_x i_x \tag{3.8}$$

**Figure 3.5:** DC side current,  $m_f = 27$ , V = 0.9p.u., I = 0.8p.u.,  $\phi = \frac{\pi}{6}$

$$i_{dc,tot} = \sum_{x} S_x i_x \tag{3.9}$$

Three important points should be noted from Figure 3.5.

- The DC side exhibits current switching at high frequency. This could introduce over voltages on every switching if the DC side is inductive.

- Average value of the DC side current is constant (DC).

- Switching component of the current is responsible to ripple voltage on the DC link capacitance. Size of the capacitor is inversely proportional to the capacitance value, Figure 3.8.

#### 3.4.2 AC Side Current Ripple

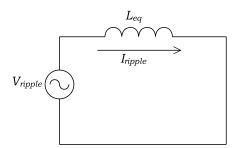

To analyze the AC side current ripple, the grid is assumed to be a harmonic free voltages source in series with inductive impedance. With this assumption, the AC side circuit can be simplified to the equivalent circuit shown in Figure 3.7.  $V_{ripple}$  is the difference between generated output voltage and the fundamental component referred to neutral point. The neutral point voltage is calculated by equation (3.10).

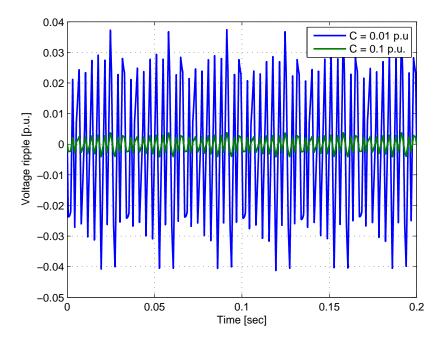

Figure 3.6: Capacitor ripple for for two choice of capacitance

Figure 3.7: Equivalent circuit for AC side ripple

$$v_n = \frac{1}{3} \left( v_a + v_b + v_c \right) \tag{3.10}$$

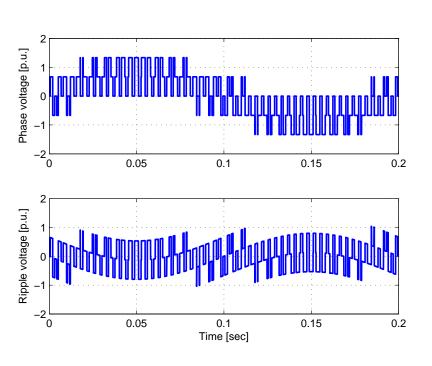

Figure 3.8: Output voltage and ripple component

Phase to neutral voltage and the corresponding ripple component are shown in Figure 3.8. This ripple voltage is applied as a source in Figure 3.9 to produce AC ripple current as governed by equation (3.11).

$$i_{ripple} = \frac{1}{L_{eq}} \int_0^t v_{ripple}(\tau) d\tau$$

(3.11)

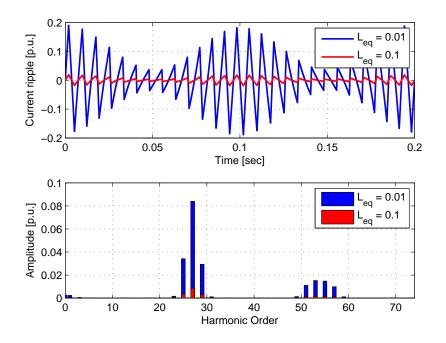

The ripple has the following characteristics:

- The ripple is independent of amplitude of current. This implies that harmonic distortion is high when the current amplitude is low.

- The ripple has peak around zero crossing of the phase voltage. As modulation index, the number of peaks in the ripple increases.

- Peak of the ripple decrease with increasing value of  $L_{eq}$

- It is mainly due to switching and has harmonic components centered around the switching frequency.

Putting these facts together, sizing of components is presented in next section.

Figure 3.9: Output current ripple and its spectrum,  $m_f = 27$

### 3.5 Dimensioning

This section deals with selection of components and their ratings. The frequency modulation ratio,  $m_f$ , is chosen to be 27 in order to achieve a good compromise between losses and filtering requirements. in [10], it is recommended that  $m_f$  be multiple of three to eliminate certain harmonics.

### 3.5.1 DC Capacitor

The purpose of DC link capacitor is limit the ripple in DC bus. Its value is selected to meet two opposing constraints. The first requirement is that of low ripple which demand capacitance to be as large as possible (Figure 3.8). The second one is related to transient response of the converter; if the capacitance is to high, the converter response will be slow. The response time is quantified as time constant [27], equation (3.12).

$$\tau = \frac{1}{2} \frac{CV_{dc}^2}{S_N} \tag{3.12}$$

where  $S_N$  is nominal apparent power,  $V_{dc}$  is the DC bus voltage, and C is the capacitance value. The value of capacitance as a function of the ripple is given by

equation (3.13) where inverse relation between ripple magnitude and capacitance is depicted.

$$C = \frac{S_N}{2V_{dc}\omega} \cdot \frac{1}{\Delta v_{dc}} \tag{3.13}$$

where  $\omega$  is fundamental frequency and  $\Delta v_{dc}$  is ripple magnitude. With the system parameters,  $S_N = 100MVA$ ,  $V_{dc} = 160kV$ , the capacitance was chosen to be  $C \approx 80\mu F$ . This choice results on time constant of  $\tau = 10ms$ .

#### 3.5.2 Series Reactor

The purpose of this reactor is three fold: filtering harmonics from the AC current, limiting fault current, and providing means for power transfer. The first two objective require high value of the reactance. The third objective, on the other hand, requires low reactance since average active power is inversely proportional to the reactance. The value is chosen to be 0.15 p.u. [27].

#### 3.5.3 Switching Devices

Although the design is centered around a chosen device, this section presents rating of the component to verify that they are within operating limits. Peak value of the current and voltage on the device are 669A and 1300V which have acceptable safety margins.

### 3.6 Control

Modulus and Symmetric optimum method are are used in this section to tune controller gains. The controller structure is described in previous chapter. It has inner and outer control loop. The outer loop can be DC voltage, active power, or reactive power controller. The inner is current controller and it will be treated first.

#### 3.6.1 Inner Current Loop

The model derived in section 2.2.5, model of the system from modulation index to currents in dq-frame was derived. Feed-forward is used to decouple the two axes and

hence the coupling is ignore for controller tuning. The open-loop transfer function for current control is given by equation (3.14).

$$G_{ol}(s) = \frac{V_{dc}}{R_c} \left(\frac{1}{\frac{L_c}{R_c}s + 1}\right) \left(\frac{1}{T_{eq}s + 1}\right) \left(k_p + \frac{k_i}{s}\right)$$

(3.14)

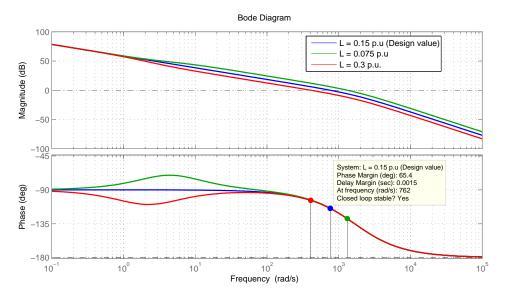

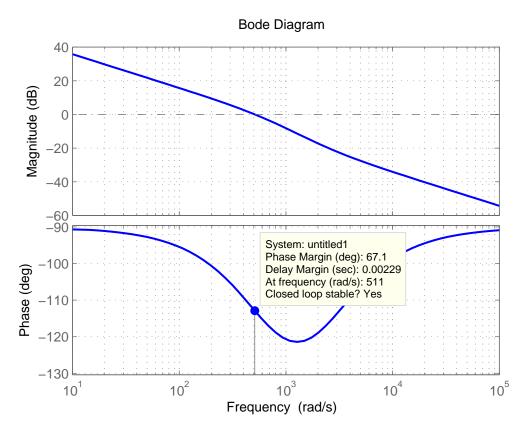

where all the quantities are in per unit.  $T_{eq}$  is the total delay in the loop. The first part is PWM delay approximated to equal half the switching period [22]. The other is delay due to anti-aliasing filter cornered at half the switching frequency. Adding these delays together gives  $T_{eq} \approx 600 \mu s$ . The controller gains are calculated, as per Modulus Optimum criterion, to be  $k_p = 0.4$  and  $k_i = 1.25$ . To verify the design and check it robustness, Bode plot and step response of the controller are plotted in Figure 3.10.

Figure 3.10: Frequency response of the current controller for different values of inductance

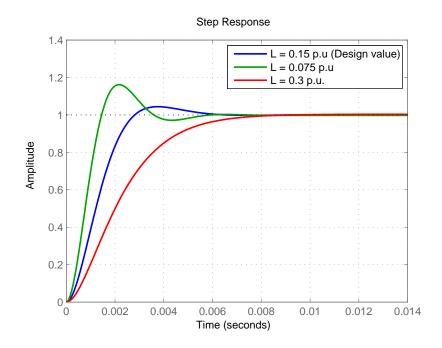

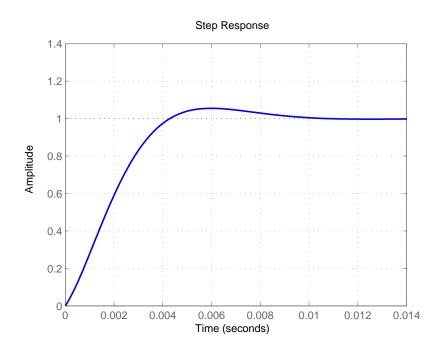

At the design value, the controller exhibits the expected phase margin of  $\approx 65^{\text{deg}}$ . Robustness of the controller under deviation of inductance value can be seen on the same figure. Increase in inductance, compared to design value, results in more damped system which is slower and more stable. In contrast, reduction of inductance reduces the phase margin resulting in faster system with more overshoot. This is confirmed by step response plot in Figure 3.11.

Figure 3.11: Step response of the current controller for different values of inductance

### 3.6.2 Outer P,Q Controller

Active Power, P, and Reactive Power, Q, are identical as derived in this section. The PLL is set to lock to grid phase angle which implies that there will be no q-axis component in the grid voltage at the point of coupling. Under this condition P and Q in per unit are

$$P = \left(\frac{v_d}{v_{dc}}\right) i_d \quad Q = -\left(\frac{v_d}{v_{dc}}\right) i_q \tag{3.15}$$

Since the current controller in d and q axis are identical, dynamics of P and Q controller is the same with the only difference being sign. Therefore, P controller will be designed and the same controller will be applied to Q. Anti-aliasing filter delay and closed loop response time of the current loop are included in the open loop transfer function,

$$G_{ol}(s) = \left(\frac{v_d}{v_{dc}}\right) \frac{1}{T_{eq}s + 1} \left(k_p + \frac{k_i}{s}\right)$$

(3.16)

The values are once again in per unit.  $T_{eq}$  is the sum of filter delay and current loop response time. Its value is  $\approx 1.4ms$ .  $k_p$  and  $k_i$  are calculated to be 0.243 and 552 ,respectively, in order to achieve damping of  $\zeta = \frac{1}{\sqrt{2}}$  and natural frequency of  $\omega_n = 628rad/s$ .

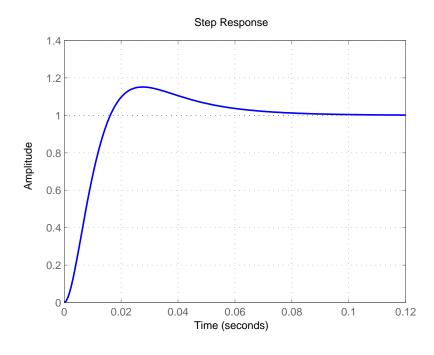

Figure 3.12: Frequency response of the P controller

Figure 3.13: Step response of the P controller

Figures 3.12 and 3.13 show frequency response and the respective step response once again showing good correlation between phase margin and overshoot.

#### 3.6.3 DC Voltage Regulator

The DC bus control problem is more of a regulation problem with the aim of rejecting disturbances, like load current change. Dynamics of the system from current input to DC bus voltage output is given by

$$G_{ol}(s) = \left(\frac{v_d}{V_{dc}}\right) \left(\frac{1}{Cs}\right) \left(\frac{1}{T_{eq}s+1}\right) \left(k_p + \frac{k_i}{s}\right)$$

(3.17)

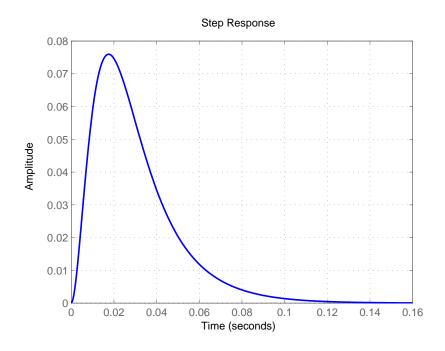

where all the quantities are in per unit and  $T_{eq}$  represents sum of all delays including the current loop response;  $T_{eq} \approx 3ms$ . Cancellation of slow poles to improve system performance is not advised since these poles would appear as closed loop poles on the disturbance to output transfer function making the system's rejection performance very poor. To overcome this problem Symmetric Optimum design is adopted. Using this method, the controller gains are calculated to be  $k_p = 9.87$  and  $k_i = 365$  setting the parameter a to be 3. Figures 3.14 and 3.15 show response of the regulator designed. The step response exhibits large overshoot. However, the main objective is to reject disturbances and the system show satisfactory 100ms rejection time for 1.0 p.u disturbance without ringing.

Figure 3.14: Step response of the DC bus regulator

Figure 3.15: Load current disturbance response of DC bus regulator

All the controllers designed so far are put into time domain simulation model described in [CASE STUDY MODEL]. This will be the topic of next section.

### 3.7 Simulation

The simulation model has been described in Chapter 2. Here simulation results under different test cases are presented.

### 3.7.1 Controller Performance

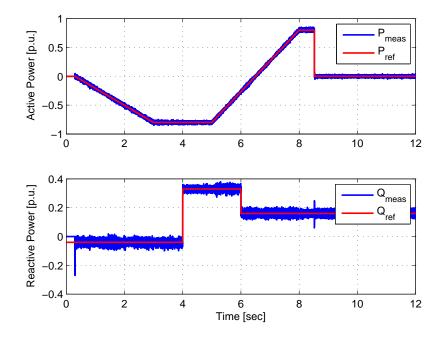

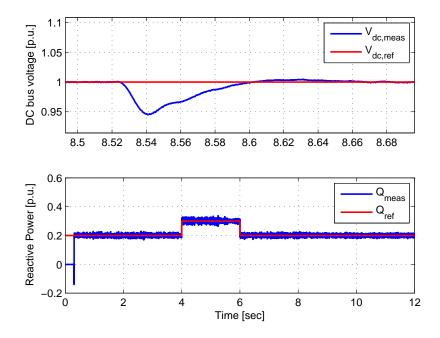

This test is performed to evaluate tracking and regulation performance of outer control loops as defined in the previous section. The reference tracking of the offshore converter to ramp and step changes is shown in Figure 3.16. The tracking performance is quite satisfactory since it track the ram signal with no error and the step response has no overshoot. Change in active power offsets the balance between power flowing into and out of the DC link causing the DC voltage to change. This is dealt with by the DC voltage regulator by passing the extra power to the grid, thus, restoring the balance.

Figure 3.17 shows regulation of the DC bus voltage where it has been zoomed around t = 8.5sec to show rejection of step disturbance in active power in the offshore station. The rejection time is inline with the one predicted by the linear transfer function.

Figure 3.16: Active and Reactive Power tracking in the Offshore Station controller

Figure 3.17:  $V_{dc}$  regulation and Reactive Power tracking in the Onshore station controller

#### 3.7.2 Harmonics

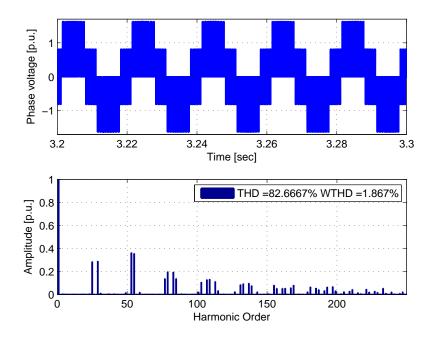

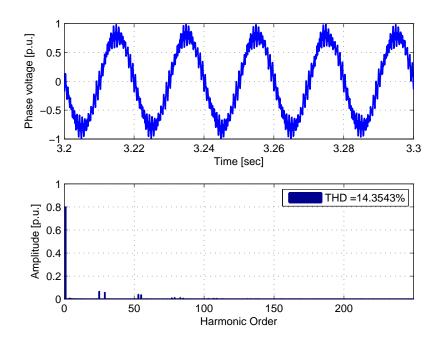

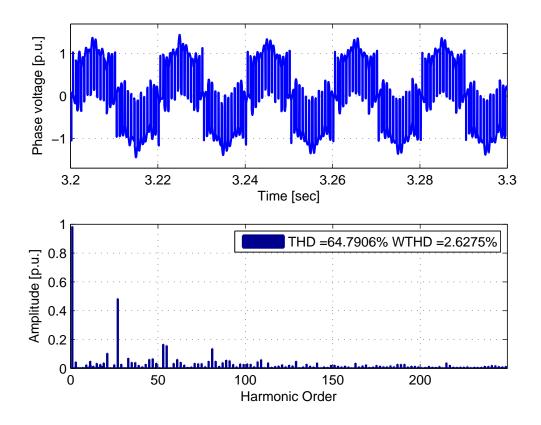

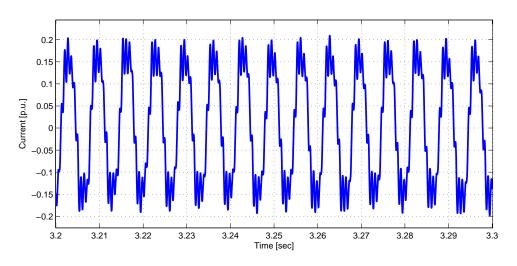

Harmonic content in current and voltage waveforms of the AC side are presented in this section. Phase voltage waveform at the terminal of the converter, together with its harmonic content, is shown in Figure 4.4. Two harmonic distortion indicators are shown on the figure. The THD,  $\approx 83\%$ , indicates that is highly polluted. However, the harmonics are centered around the switching frequency which is relatively high,  $m_f = 27$ . Out of the harmonics, the ones having more pronounced effect on filtering requirement are those with low frequency. Therefore, THD is not a good measure of performance for filtering requirement. WTHD,  $\approx 1.9\%$ , is related to the current harmonics which propagate in the system and increase the losses.

Figure 3.18: Phase to neutral voltage of offshore converter

The relation between WTHD of the voltage and THD of the current is given by equation (3.18).

$$THD_i = \frac{WTHD_v}{X_{pu}} \tag{3.18}$$

where  $X_{pu}$  is per unit series impedance between the converter and the grid. The current waveform and its harmonic content is shown in Figure 4.6. The current waveform exhibits THD of  $\approx 14.6\%$  which is close to the one predicted with equation (3.18),  $\approx 13\%$

Figure 3.19: Line current of offshore converter

### 3.7.3 Loss

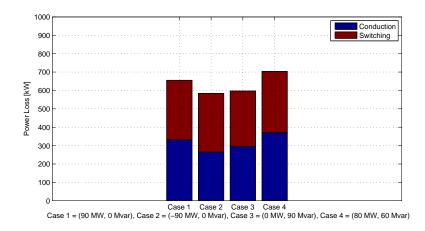

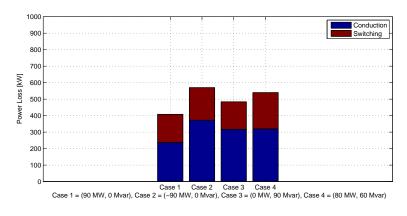

Power loss in the converter under different operating conditions is shown in Figure 4.7. The losses vary when active power directions is reversed. This is due to the fact that different devices (IGBT or Diode) conduct for longer duration depending on the operating condition. The figure also shows breakdown of the loss into switching and conduction. The total loss in the range  $0.5\% \sim 0.7\%$  of the converter rating under all the condition considered.

Figure 3.20: Loss under different conditions

## Chapter 4

## Three Level NPC VSC

### 4.1 Introduction

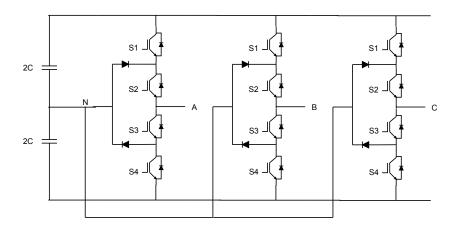

This chapter deals with three level NPC converter used in HVDC transmission. The circuit topology is shown in Figure 4.1. Most of the components are similar to the two level VSC. Therefore, it is not treated in great detail.

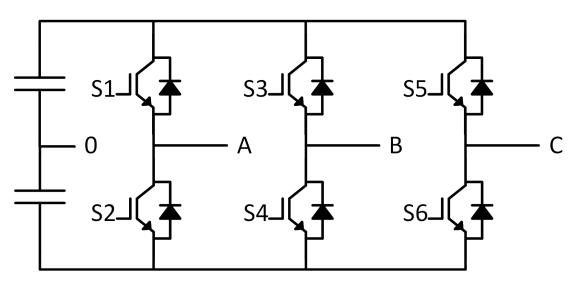

Figure 4.1: Three level NPC circuit

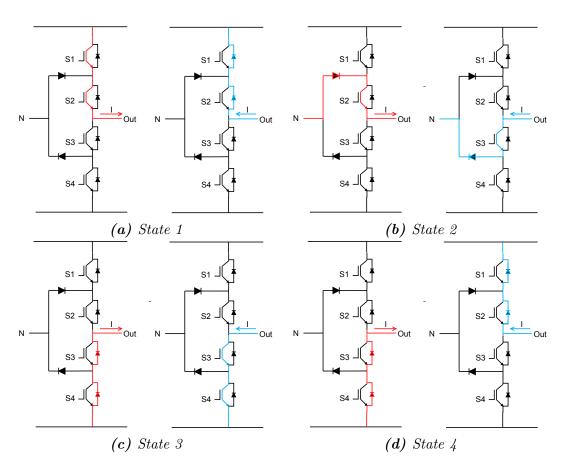

### 4.2 Operating Principle

The NPC is a combination of two half bridges described in the previous chapter. These are  $S_1$  and  $S_3$  forming the first half bridge while  $S_2$  and  $S_4$  forming the second one. Table 4.1 depicts operation of the converter under each of the four feasible states when the two bridges are operated in complementary mode. The bar on top

| State | $S_1/\bar{S}_3$ | $S_2/\bar{S}_4$ | $V_{out}$ for $i_{out} > 0$ | $V_{out}$ for $i_{out} < 0$ |

|-------|-----------------|-----------------|-----------------------------|-----------------------------|

| 1     | 1               | 1               | $\frac{V_{dc}}{2}$          | $\frac{V_{dc}}{2}$          |

| 2     | 0               | 1               | 0                           | 0                           |

| 3     | 0               | 0               | $-\frac{V_{dc}}{2}$         | $-\frac{V_{dc}}{2}$         |

| 4     | 1               | 0               | $-\frac{V_{dc}}{2}$         | $\frac{V_{dc}}{2}$          |

Table 4.1: Switching States of NPC converter

of the switching states,  $S_x$ , indicates logical NOT. The fourth state gives different outputs depending on the current direction. The first three, on the other hand, produce the same output irrespective of the current direction. These states can be used to produce three different voltages and hence the name three-level. The output voltage is referred to the DC mid point.

Figure 4.2 indicates which device is conducting for each state and current direction combination.

### 4.3 Modulation

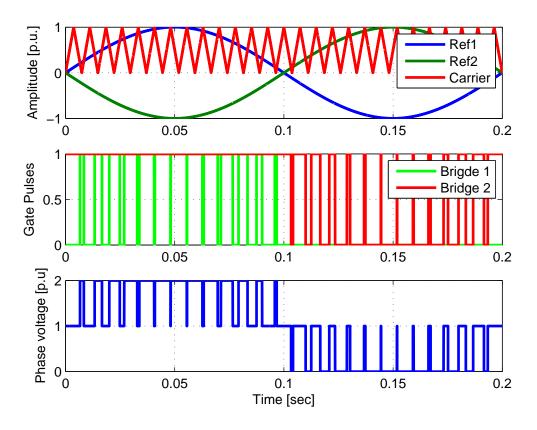

As described in the previous section, the NPC has two independent half bridges driven by two pair of complementary signals. Different modulation techniques have been described in literature [28], [19] to generate the gating signals. These can be grouped in the same manner as two level modulation strategies. One group uses multiple carriers while the other use multiple modulating signal. Since generating modulating signals is generally easier than generation carriers, the second approach will be utilized.

From Table 4.1, it can be seen that positive output voltage can be generated when the second half-bridge is high (upper switch turned on). In this scenario, the output jumps between  $\frac{V_{dc}}{2}$  and 0 generating average positive voltage over the switching period. To generate negative voltage, the first half bridge has to be low (lower switch turned on). This would imply that when a certain polarity voltage is to be generated, only one half bridge is actively switching while the other is forced to either high or low state. Therefore, the modulating signal, and 180° shifted version of it, can be used with a carrier that spans from 0 to 1 to generate the gating signals for the two half bridges. This arrangement, together with the three level output, is shown in Figure 4.3.

Figure 4.2: States of a single leg of NPC with current flow

Figure 4.3: Modulation waveforms for three level NPC

### 4.4 Analysis

Analysis of the NPC focuses on AC side current ripple and the DC voltage ripple as was the case for two level VSC. The AC side current ripple has the same equivalent circuit as the two level VSC. The DC voltage ripple, on the contrary, has a different mechanism due to the mid point current. This section briefly describes peculiar properties of the NPC to avoid repetition.

#### 4.4.1 Mid point current

The current through the DC mid point is superposition of the value for positive voltage and negative voltage. When generating positive voltage, the load current, i, is the sum of positive bus current and the mid point current. Similarly, when generating negative voltage, the load current is sum of negative bus current and mid point current. Putting these two arguments together, the mid point current is give by equation (4.1) [19]

$$i_{mid} = i - (i_p + i_n)$$

(4.1)

where  $i_p$  and  $i_n$  are currents in the positive and negative buses respectively. Average value of the mid point current over a switching interval is given by equation (4.2).

$$\bar{i}_{mid} = i - m \cdot i \left( sgn(m) - sgn(-m) \right) \tag{4.2}$$

where m is fundamental voltage reference,  $sgn(\cdot)$  returns 1 when its argument is positive and 0 otherwise. In [19] simplified analysis of the mid point current of three phase NPC was performed. The result shows that the mid point current contains triplen harmonics with third harmonic being the most dominant one. It was also shown that the amplitude of the third harmonic lies between 51% and 76% of the AC side current the worst case occurring when operating at zero power factor.

#### 4.4.2 DC Voltage Ripple

The DC voltage ripple is generated by the same mechanism as two level VSC. The current through the capacitor charge and discharge the capacitor depending on its direction. Additional component of the capacitor current that is related to the NPC is the mid point current. As discussed in the previous section, the mid point current contains a dominant third harmonic component which is split between the two DC link capacitors. This results in third harmonic ripple on each capacitor. The capacitance plays a major role in attenuating the ripple. [[19] analyses effect of DC voltage ripple on harmonic content of the AC side voltage. The results reflect that the dominant third harmonic ripple in the DC voltage imposes third and fifth

harmonic voltages on the AC side. This would require bulky filtering and hence it is considered a major drawback.

### 4.5 Dimensioning

Since the objective of this thesis is to compare merits inherent to the topology, most of the components had to be chosen to be similar. In light of this argument, the series reactor and DC link capacitance (total series combination) are kept the same as the two level counterpart. The major difference is rating of semiconductor devices used. In contrast to two level VSC, all the semiconductor devices (valves) are rated to half the DC bus voltage. Therefore, each valve contain series connection of 75 devices giving the same safety margin as the two level VSC.

### 4.6 Control

The controller used for the NPC is the same as the two level counterpart therefore, it is not presented here.

### 4.7 Simulation

This section presents simulation results for the three level NPC used in the case study model. The controller exhibits the same transient response as it did with the two level VSC. Therefore, it is not repeated here. Harmonic and Loss results are presented in what follows.

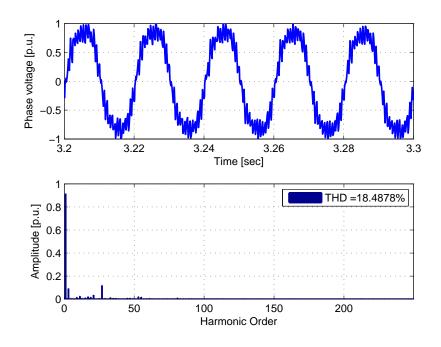

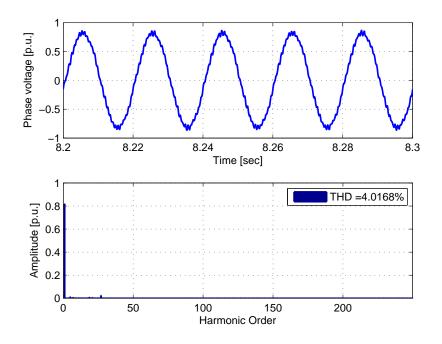

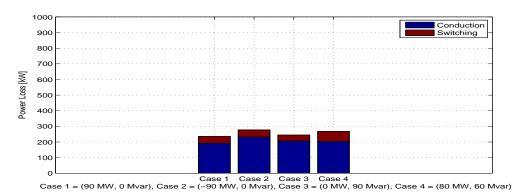

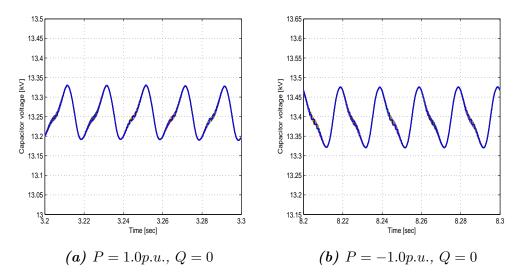

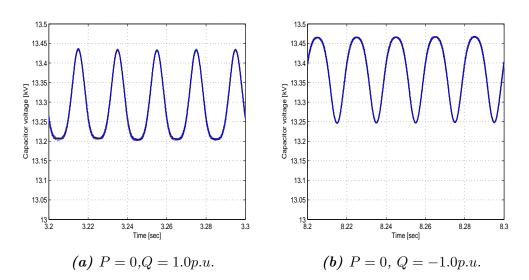

### 4.7.1 Harmonics