# Synchronous Optimal Modulation for Medium voltage Multi-phase Machines

Implementation of three-level modulators in Field Programmable Gate Arrays

# Mamta Maharjan

Master of Science in Electric Power Engineering

Submission date: June 2013

Supervisor: Tore Marvin Undeland, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

Problem Description

Medium voltage ac drives based on voltage source inverters are in increasing demand for

numerous industrial applications. The advancement in power electronics devices like IGBTs has

allowed to rise the low voltage ac drive to the medium voltage drive system. Medium Voltage

IGBTs must have low switching frequency. Operation at reduced switching frequency requires

synchronous modulation techniques because the conventional asynchronous modulation will

generate too much harmonics.

Programmed modulation is synchronous modulation which pre-calculates optimal switching angles

within a period of the fundamental period. If those switching angles are calculated by minimizing

total harmonic contents then it is called Synchronous Optimal Modulation. These switching angles

are not formed by carrier wave like in conventional way. These optimized PWM strategies are

extremely difficult to realize with conventional analog circuitry. Therefore, the firmware

implementation of synchronous optimal modulation in digital circuitry will be created by an

extremely fast computation microchip called Field-Programmable Gate Array (FPGA).

In this Master thesis a modulator for a 3-level converter should be developed. The modulator

should be possible to be extended to 9-phase machines. The modulator should give the interrupt to

the processor routine where the calculation of relative switching instance is executed. From the

software point of view the input to the modulator is memory mapped as an array with switching

instance stored increased order due to time. The tasks to be performed are:

Work out a specification together with the master student making the control software

for the modulator.

Decide which method to be used for dc-bus balancing for the 3-level converter

Implement the modulator in a FPGA

Test the modulator in the Lab by help of a 3-level 3-phase inverter operating an

**Induction Machine**

**Supervisor:** Prof. Tore M. Undeland

Co-supervisor: Roy Nilsen, Wärtsilä Norway AS

i

# **ABSTRACT**

The advancement in power electronics devices like Insulated Gate Bipolar Transistors (IGBT) has increased the low voltage ac drive to the medium voltage drive system. These IGBTs have higher voltage capability. For eliminating the harmonic content three level converters are chosen rather than two level converters. But these inverter switches using IGBTs should be operated in low switching frequency so that the huge loss associated with switching loss is reduced to large extent. When switching frequency is low then conventional asynchronous modulation technique is not appropriate because of the formation of sub-harmonic components. Therefore, it is wise to apply synchronous modulation technique. Programmed Modulation is one of best synchronous modulation technique which pre-calculates the optimum switching angles. If those switching angles are calculated by minimizing total harmonic contents then it is called Synchronous Optimal Modulation.

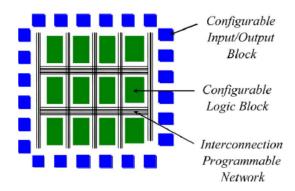

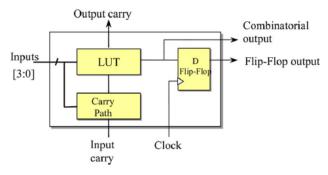

These optimized PWM strategies are extremely difficult to realize with conventional analog circuitry, but they can be effectively implemented in field-programmable gate array (FPGA) which has extremely fast computation capability and allows a few microseconds real-time computation of complex control algorithms. FPGA is a microchip which consists of matrix of configurable logic blocks (CLB) made up of flip flops and lookup tables. VHDL is Hardware Descriptive Language which is utilized to synthesize hardware designs in FPGA. VHDL creates digital circuitry, which performs operations in parallel so FPGA is extremely fast and performs various time critical tasks in the system.

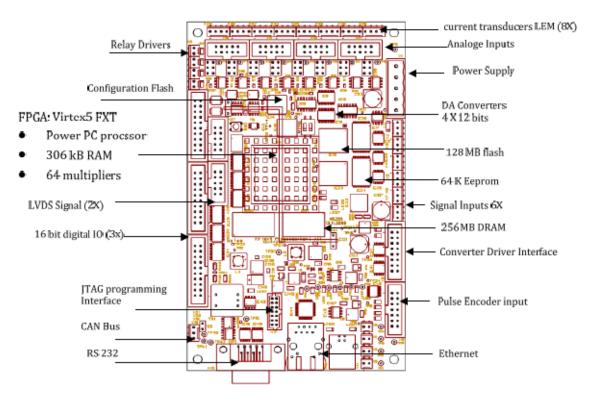

The FPGA which is used in this project is Vertex-5 ppc440 FX30T. The digital electronics for implementing Synchronous Optimal Modulation are written in Xilinx Embedded System. The extremely fast computation power of FPGA finds its application in multiphase machine. Although this thesis deals with three phase Induction motor, it can easily be extended up to nine phase Machine.

This master thesis implements synchronous optimal modulation in FPGA for Neutral Point Clamped inverter feeding Induction machine. The result shows that synchronous optimal modulation can be applied for low switching frequency with lower total harmonics distortion.

# **Preface**

Electric Drives, Power electronics and digital control system have always been my favourite subjects. I am extremely overwhelmed to do this project titled **Synchronous Optimal Modulation for Medium voltage Multi-phase Machines**. This master thesis requires the ideas of all these subjects. Doing this master thesis, my practical knowledge in these fields has immensely flourished.

I want to thank my supervisor Prof. Tore Undeland for his lecture in Design of power electronic converter which has augmented my knowledge in power electronics to great extent. I want to show my deep gratitude and respect towards my co-supervisor Roy Nilsen, Wartsila, Norway. I would like to express my co-supervisor how much immensely lucky I feel to get all those supports, guidance from the initiation of the project work. I would not have been able to fulfil this project work without the knowledge, encouragement and the positive spirit from my co-supervisor consistently.

My unlimited gratitude goes to Kjell Ljøkelsøy from SINTEF without whom timely completion of master thesis would have been impossible for me. He has helped me a lot during my learning of FPGA and embedded development kit (EDK). The threshold of learning FPGA using Xilinx tools is very extremely high. The statement found on the Internet tells how FPGAs are seen by most software developers: "FPGA is a dark and scary corner of the universe teeming with HDLs, synthesis, place-and-route, and other unseen evils". He made this journey easier for me by being there in all my confusions. He was always so much supportive, encouraging and helpful.

I am also thankful to my classmate Biruk Bekele for supporting me through technical advice, profitable discussion. I also want to thank Sverre Skalleberg Gjerde for helping me learn VHDL language. My sincere thanks go to all the technical staffs of department of Electrical Engineering, NTNU for being so much supportive in dealing with the lab equipments. I am very grateful towards Prof. Indraman Tamrakar, Institute of Engineering, Nepal for always helping me out with my confusion in Induction Machine. Last but not the least I would like to thank Kabin Tamrakar for giving me ideas on programming skills and also for the care, moral support and encouragement throughout the thesis.

Mamta Maharjan, Trondhiem, Norway

yeta

# Contents

| 1 | Intr | oduc  | tion                                          | 1    |

|---|------|-------|-----------------------------------------------|------|

|   | 1.1  | Bac   | kground                                       | 1    |

|   | 1.2  | Mo    | tivation                                      | 2    |

|   | 1.3  | Lite  | erature review                                | 3    |

|   | 1.4  | The   | esis Scope and Limitation                     | 4    |

|   | 1.5  | Org   | anization of report                           | 4    |

| 2 | The  | eory. |                                               | 5    |

|   | 2.1  | Ele   | ctric Propulsion                              | 5    |

|   | 2.2  | Mu    | ltiphase Machine                              | 6    |

|   | 2.2. | .1    | Harmonic Losses in Induction Machine          | 8    |

|   | 2.3  | Thr   | ee Level Converter                            | 9    |

|   | 2.3. | .1    | Switching loss in voltage source Inverter     | . 12 |

|   | 2.3. | .2    | Harmonic content of voltage source Inverter   | . 13 |

|   | 2.3. | .3    | DC Bus Balancing                              | . 15 |

|   | 2.4  | Mo    | dulation Strategy                             | . 19 |

|   | 2.5  | Pro   | gram Modulation Technique                     | . 24 |

|   | 2.5. | 1     | Background                                    | . 24 |

|   | 2.5. | .2    | Program Modulation                            | . 25 |

|   | 2.6  | Syn   | chronous Optimal Modulation                   | . 27 |

|   | 2.7  | Оре   | en Loop Method                                | . 31 |

|   | 2.8  | Syn   | chronous Optimal Modulation signal flow graph | . 32 |

| 3 | Intr | oduc  | etion to FPGA and Xilinx EDK                  | . 34 |

|   | 3.1  | Bac   | kground                                       | . 34 |

|   | 3.2  | Ger   | neral Architecture of FPGA                    | . 35 |

|   | 3.3 E  | mbedded System Development                     | 36 |

|---|--------|------------------------------------------------|----|

|   | 3.4 X  | ilinx Board                                    | 37 |

|   | 3.4.1  | Communication Port                             | 37 |

|   | 3.4.2  | memory                                         | 38 |

|   | 3.4.3  | clock                                          | 38 |

|   | 3.4.4  | Converter                                      | 38 |

|   | 3.4.5  | Pulse Encoder:                                 | 39 |

|   | 3.4.6  | Relay drivers.                                 | 39 |

|   | 3.4.7  | LVDS:                                          | 39 |

|   | 3.4.8  | Signal Inputs:                                 | 39 |

|   | 3.4.9  | AD Converter:                                  | 39 |

|   | 3.4.10 | Digital Input Output port:                     | 40 |

|   | 3.5 X  | ilinx Embedded Development Kit                 | 40 |

|   | 3.5.1  | Introduction                                   | 40 |

|   | 3.5.2  | Different Abstraction Level                    | 41 |

|   | 3.5.3  | Xilinx ISE overview                            | 42 |

|   | 3.5.4  | Xilinx platform studio overview                | 45 |

|   | 3.5.5  | Xilinx Software Development Kit overview       | 47 |

| 4 | Firmw  | vare Implementation of SOM in FPGA             | 50 |

|   | 4.1 E  | DK install                                     | 52 |

|   | 4.2 P  | roject Local Pcores (user)                     | 53 |

|   | 4.2.1  | Phase to Phase Vs Space vector Implementation. | 53 |

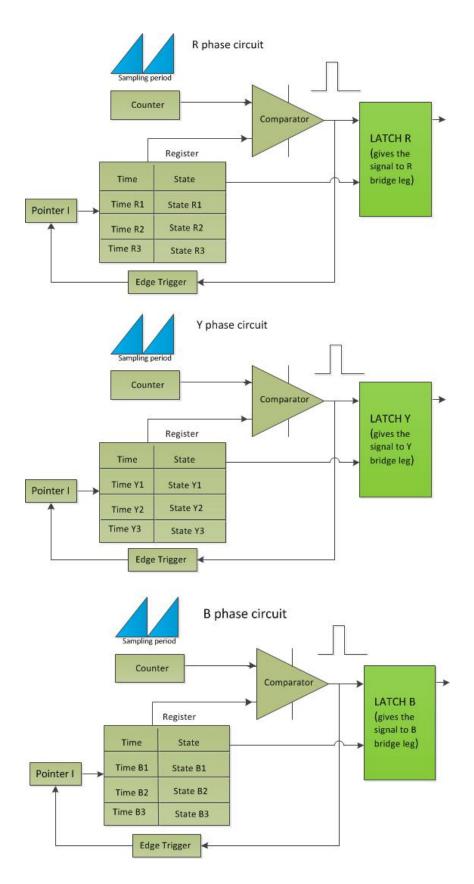

|   | 4.2.2  | SOM_PHASE IP                                   | 55 |

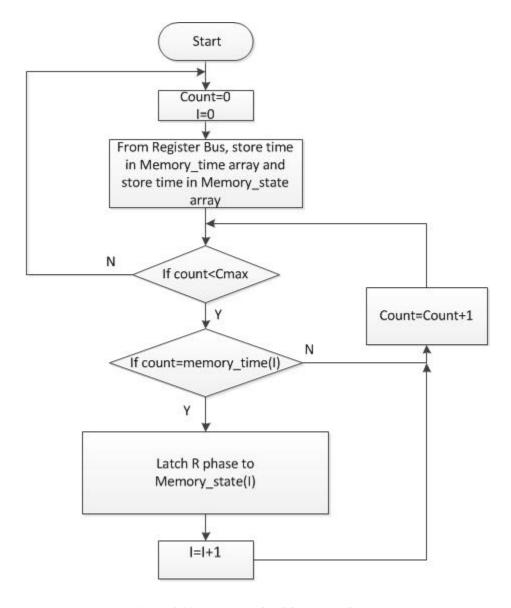

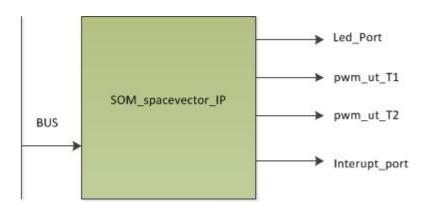

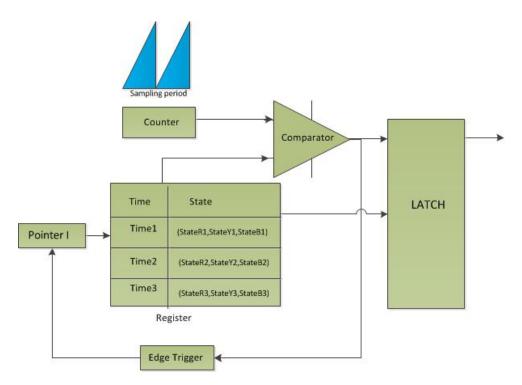

|   | 4.2.3  | SOM_spacevector_IP                             | 61 |

|   | 4.3 G  | lobal Peripheral Repository (user)             | 65 |

|   | 4.3 | .2    | Driver Interface via dig_io_connection       | 69   |

|---|-----|-------|----------------------------------------------|------|

|   | 4.4 | Dri   | ver circuit                                  | 71   |

|   | 4.5 | Cor   | nmunication with other collaborating project | 72   |

|   | 4.6 | Cha   | ıllenges faced                               | 73   |

|   | 4.7 | Sim   | ulation                                      | 74   |

|   | 4.7 | .1    | SOM_PHASE_IP                                 | 75   |

|   | 4.7 | .2    | SOM_spacevector_IP                           | 81   |

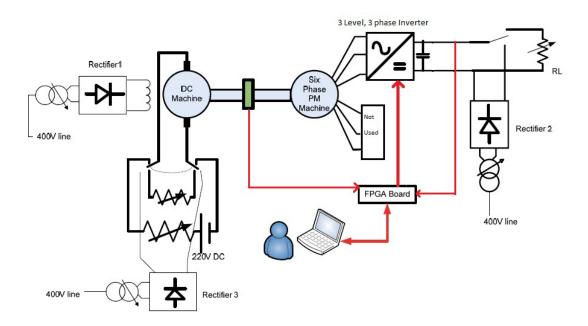

| 5 | Ex  | perim | ent Setup                                    | 83   |

|   | 5.1 | Har   | dware Setup                                  | 83   |

|   | 5.1 | .1    | Setup Overview                               | 83   |

|   | 5.1 | .2    | Six-Phase Induction Machine                  | 84   |

|   | 5.1 | .3    | DC Machine                                   | 85   |

|   | 5.1 | .4    | Converter                                    | 85   |

|   | 5.1 | .5    | FPGA control card                            | 87   |

|   | 5.1 | .6    | Current Measurements                         | . 88 |

|   | 5.2 | Sof   | tware Implementation                         | . 88 |

|   | 5.2 | .1    | Software Environment                         | . 88 |

|   | 5.2 | 2     | Program Structure                            | 89   |

| 6 | Ex  | perim | nental Results and Discussion                | 91   |

|   | 6.1 | Dri   | ver, Voltage and Current signal              | 91   |

|   | 6.1 | .1    | Driver signal                                | 91   |

|   | 6.1 | .2    | Voltage waveform                             | 92   |

|   | 6.1 | .3    | Current Waveform                             | 93   |

|   | 6.1 | .4    | Digital, Voltage, Current signal             | 94   |

|   | 6.2 | Vor   | istion of N with Stator frequency            | 95   |

| (  | 6.3 | Tota   | al harmonic distortion           | 98  |

|----|-----|--------|----------------------------------|-----|

|    | 6.3 | 3.1    | Line-Line Voltage                | 98  |

|    | 6.3 | 3.2    | Measurement of THD               | 99  |

|    | 6.3 | 3.3    | Analysis                         | 100 |

|    | 6.3 | 3.4    | Comparison                       | 103 |

| (  | 6.4 | Son    | me of Errors found in the system | 104 |

|    | 6.4 | l.1    | Analysis                         | 106 |

|    | 6.4 | 1.2    | Suggestion                       | 106 |

| (  | 6.5 | Disc   | cussion                          | 108 |

| 7  | Co  | nclus  | ion and further work             | 109 |

| ,  | 7.1 | Con    | nclusion                         | 109 |

| ,  | 7.2 | Fur    | ther Works                       | 110 |

| 8  | Bil | oliogr | aphy                             | 111 |

| 9  | Ap  | pendi  | ix A                             | 114 |

| 10 | 1   | Apper  | ndix B                           | 115 |

| 11 | 1   | Apper  | ndix C                           | 128 |

| 12 | 1   | Apper  | ndix D                           | 133 |

| 13 | 1   | Apper  | ndix E                           | 138 |

| 14 | 1   | Apper  | ndix F                           | 139 |

| 15 | 1   | Apper  | ndix G                           | 141 |

| 16 | 1   | Apper  | ndix H                           | 143 |

| 17 |     | Anner  | ndix I                           | 145 |

# **List of Figure**

| Figure 2-1 Overview of electric propulsion                                 | 5  |

|----------------------------------------------------------------------------|----|

| Figure 2-2 Nine Phase Synchronous Machine [19].                            | 7  |

| Figure 2-3 Stator winding types [3].                                       | 7  |

| Figure 2-4 Six Phase Induction Machine(SPIM) [3].                          | 8  |

| Figure 2-5 Three level inverter NPC Technology [24]                        | 10 |

| Figure 2-6 Bridge leg of three level converter [24].                       | 10 |

| Figure 2-7 Naturally sampled PWM for 3 level converter [25]                | 11 |

| Figure 2-8 Bridge leg voltage [26]                                         | 12 |

| Figure 2-9 Line to Line voltage[26]                                        | 12 |

| Figure 2-10 Space vector diagram for three level converter                 | 16 |

| Figure 2-11 Position of current at different level [26]                    | 16 |

| Figure 2-12 Charging of upper capacitor and discharging of lower capacitor | 18 |

| Figure 2-13 Modulation strategies[24].                                     | 20 |

| Figure 2-14 Naturally sampled PWM[23].                                     | 21 |

| Figure 2-15 Symmetric and asymmetric regular sampled PWM                   | 22 |

| Figure 2-16 Carrier based PWM [23].                                        | 23 |

| Figure 2-17 Programmed PWM pattern (M=N)[22].                              | 25 |

| Figure 2-18 Programmed PWM                                                 | 27 |

| Figure 2-19 SOM pattern for N=4 [25].                                      | 29 |

| Figure 2-20 Harmonics for N=4 [25]                                         | 30 |

| Figure 2-21 Pulse generated from SOM pattern.                              | 30 |

| Figure 2-22 Switching Pulse in one fundamental frequency.                  | 32 |

| Figure 2-23 Synchronous Optimal Modulation signal flow graph [29].         | 32 |

| Figure 3-1 General architecture of FPGA [31].                              | 35 |

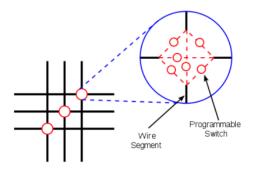

| Figure 3-2 Interconnection programmable network.                           | 35 |

| Figure 3-3 Inside logic block [31].                                        | 36 |

| Figure 3-4 FPGA control card[35]                                           | 38 |

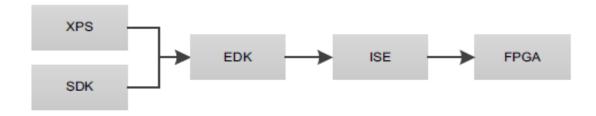

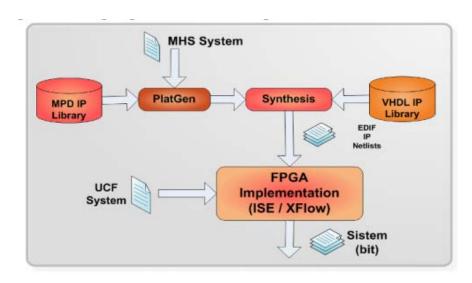

| Figure 3-5 FPGA design flow adopted in this work.                          | 40 |

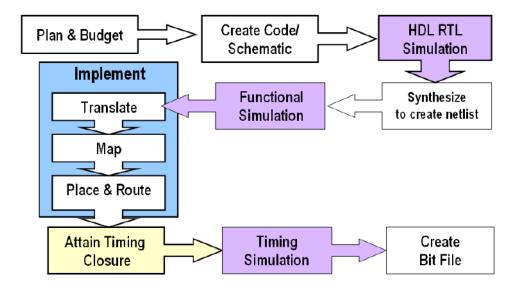

| Figure 3-6 Overview of various steps in design flow of digital system.     | 43 |

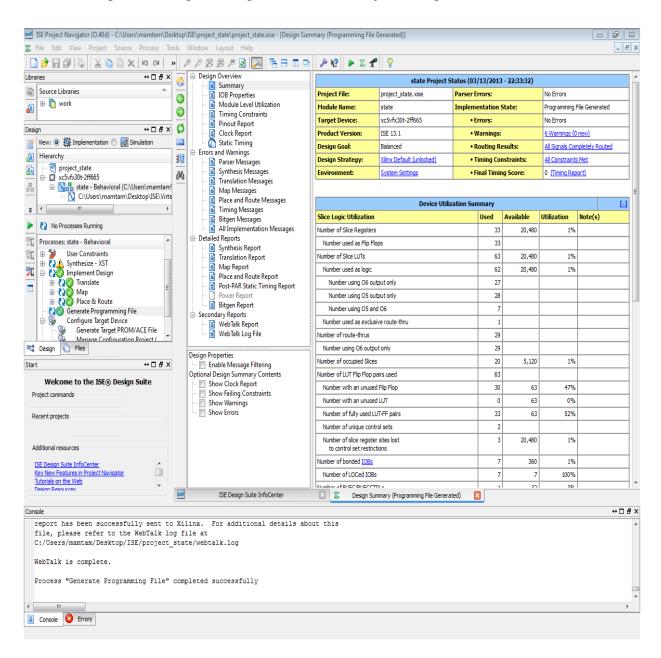

| Figure 3-7 ISE windows.                                                    | 44 |

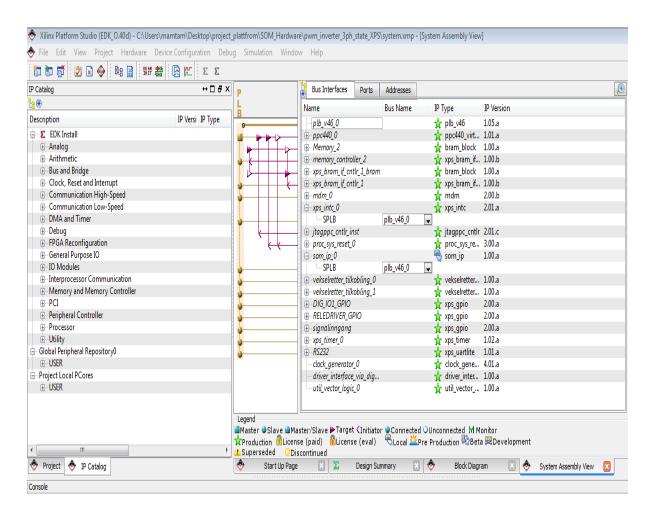

| Figure 3-8 XPS windows.                                                  | 46 |

|--------------------------------------------------------------------------|----|

| Figure 3-9 Microprocessor Peripheral Description (MPD) file              | 46 |

| Figure 3-10 Xilinx EDK flow for processor based design.                  | 47 |

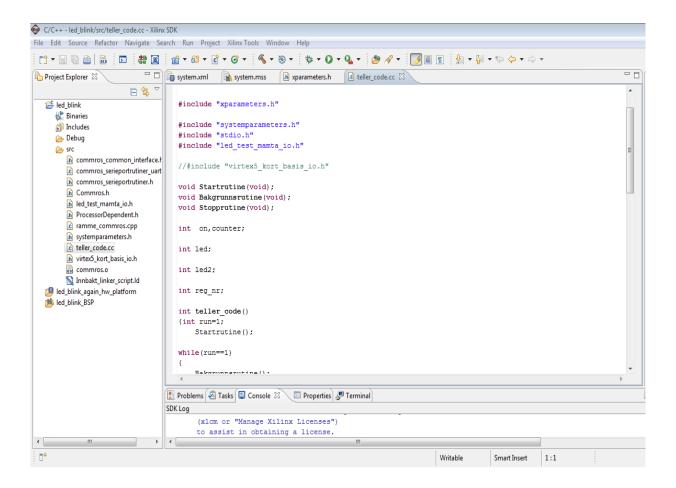

| Figure 3-11 SDK windows.                                                 | 48 |

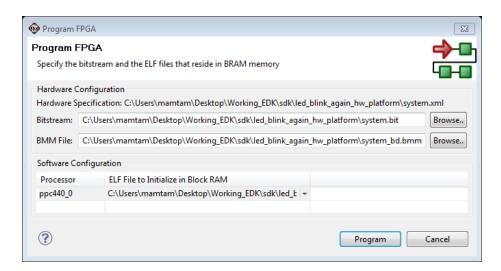

| Figure 3-12 Program FPGA.                                                | 49 |

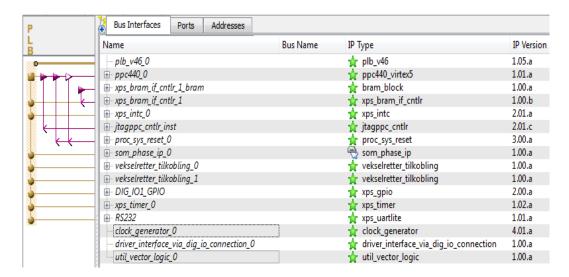

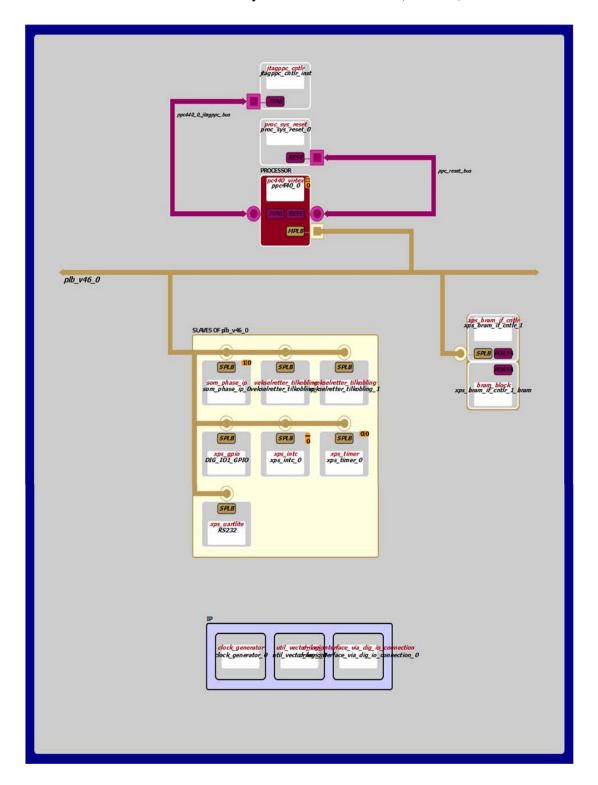

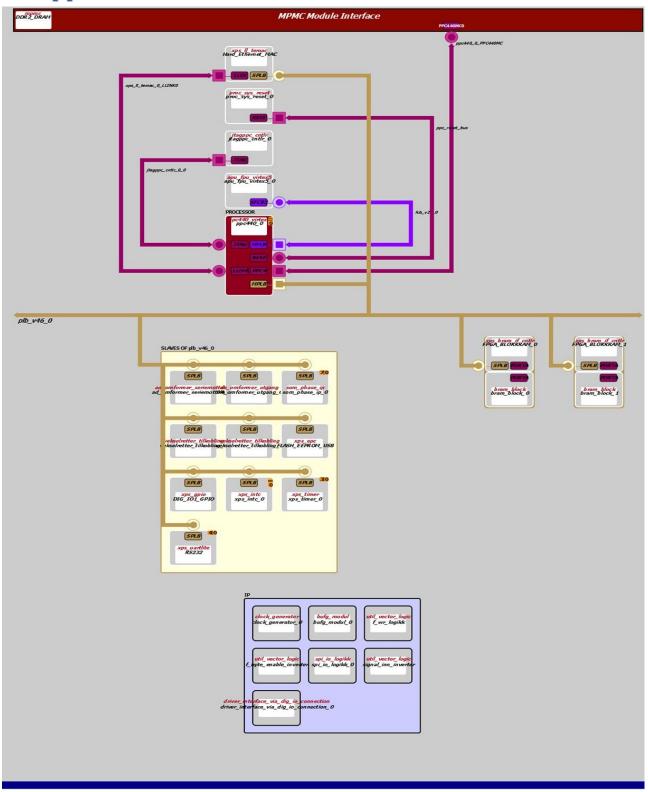

| Figure 4-1 List of IPs used in the project.                              | 50 |

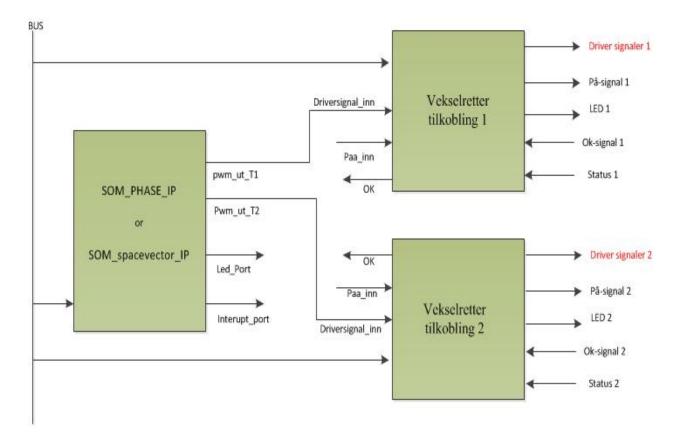

| Figure 4-2 Block diagram.                                                | 51 |

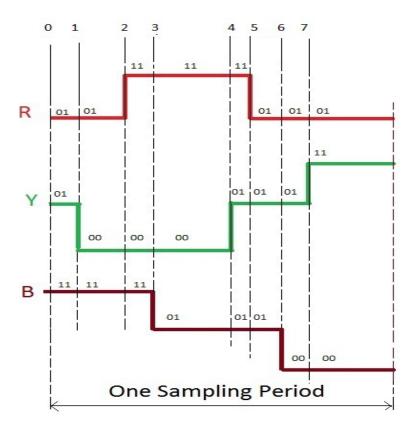

| Figure 4-3 Switchings in three phase for one sampling period.            | 54 |

| Figure 4-4 Register used for phase to phase implementation.              | 55 |

| Figure 4-5 Register used for spacevector implementation.                 | 55 |

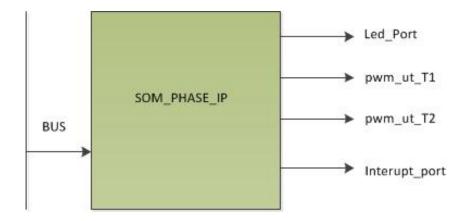

| Figure 4-6 Input and output for SOM_PHASE_IP                             | 55 |

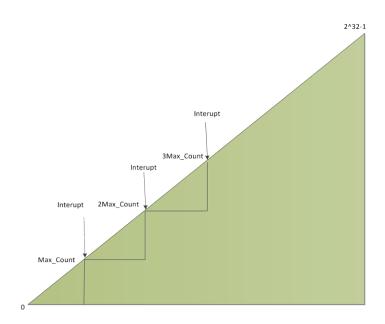

| Figure 4-7 Program Modulation with sampling period.                      | 56 |

| Figure 4-8 Register for phase to phase implementation.                   | 57 |

| Figure 4-9 Function of SOM_PHASE_IP [43]                                 | 59 |

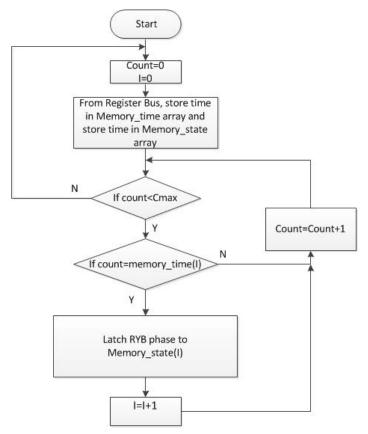

| Figure 4-10 Flowchart for SOM_PHASE_IP.                                  | 60 |

| Figure 4-11 Input and output of SOM_spacevector_IP.                      | 61 |

| Figure 4-12 Register used for SOM_spacevector_IP.                        | 62 |

| Figure 4-13 Function of SOM_spacevector_IP[43].                          | 63 |

| Figure 4-14 Flowchart for SOM_spacevector_IP.                            | 64 |

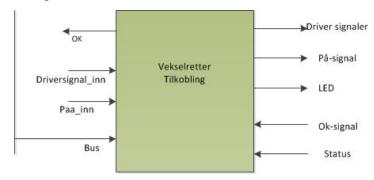

| Figure 4-15 Input and output Vekslretter Tilkobling                      | 65 |

| Figure 4-16 Two Level three phase converter.                             | 65 |

| Figure 4-17 Function of Vekslretter Tilkobling[42].                      | 66 |

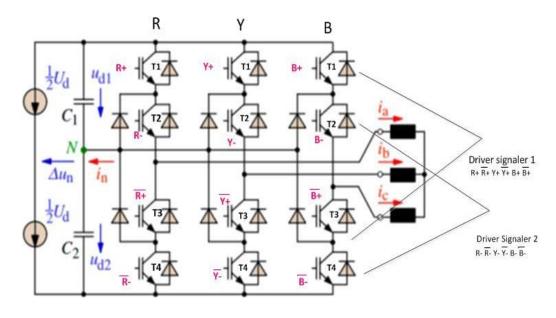

| Figure 4-18 Neutral Point Clamped Converter.                             | 67 |

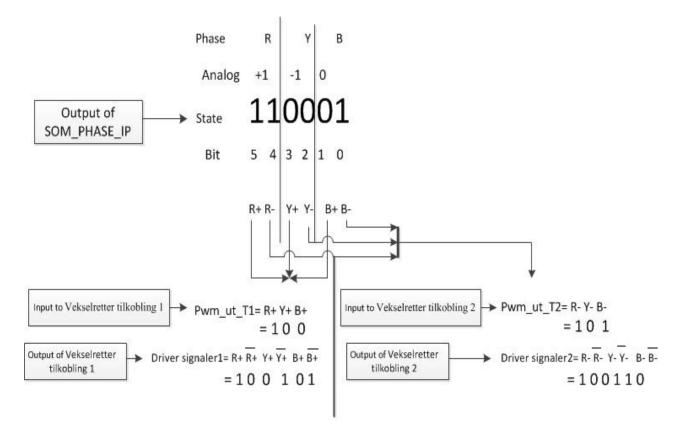

| Figure 4-19 Use of two Vekselretter tilkobling for three level converter | 67 |

| Figure 4-20 Example                                                      | 68 |

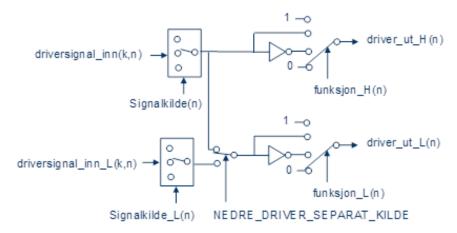

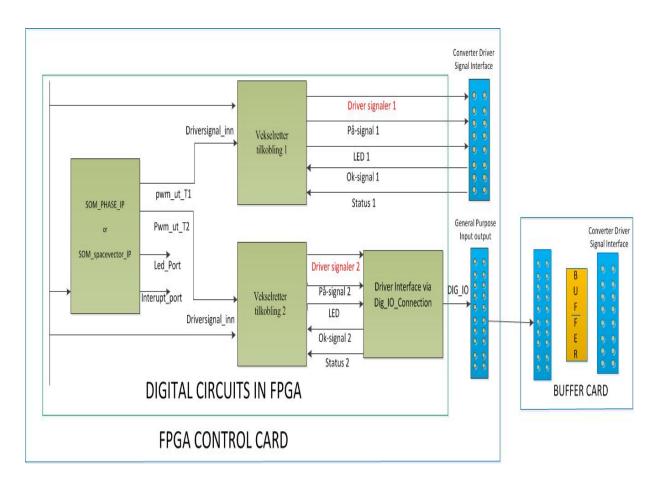

| Figure 4-21 Use of Driver Interface via Dig_IO_Connection.               | 70 |

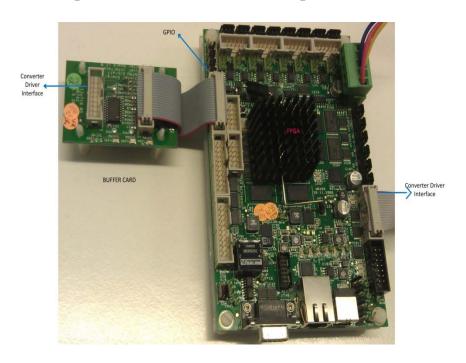

| Figure 4-22 FPGA card with buffer card.                                  | 70 |

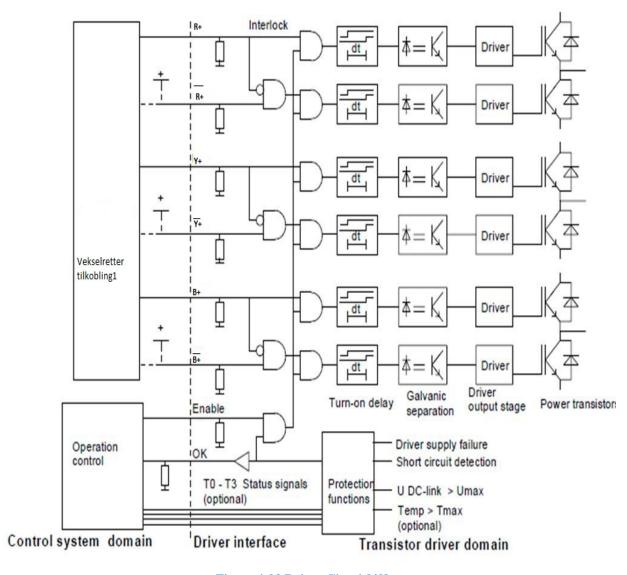

| Figure 4-23 Driver Circuit[42]                                           | 71 |

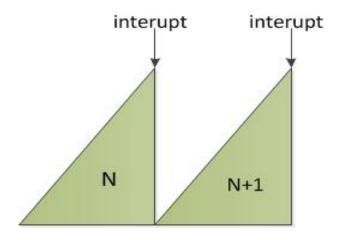

| Figure 4-24 Samples N and N+1.                                           | 72 |

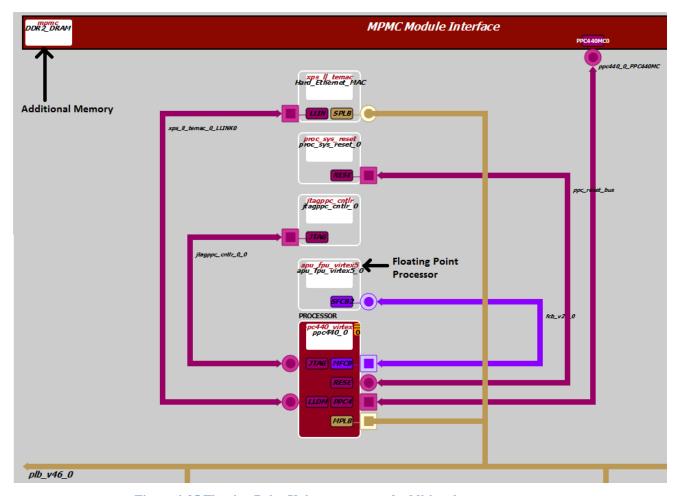

| Figure 4-25 Floating Point Unit processor and additional memory.         |    |

| Figure 4-26 Test signals.                                                | 75 |

| Figure 4-27 R phase.                                                              | 75  |

|-----------------------------------------------------------------------------------|-----|

| Figure 4-28 Y phase.                                                              | 76  |

| Figure 4-29 B phase.                                                              | 76  |

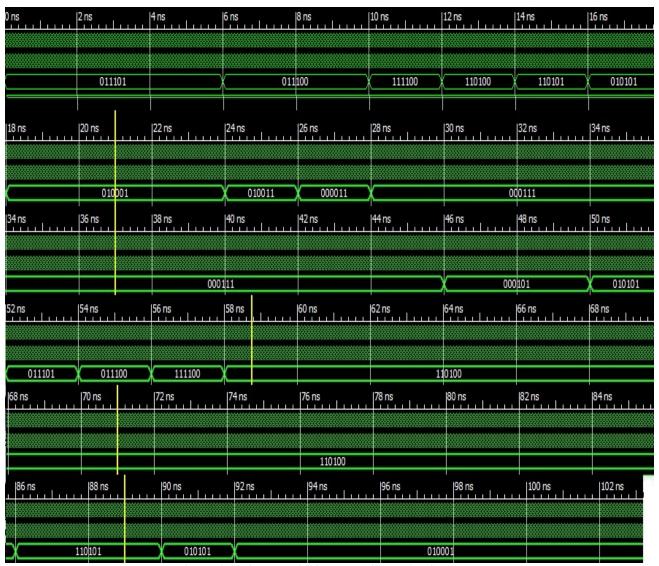

| Figure 4-30 Output of SOM_PHASE_IP in ISIM                                        | 78  |

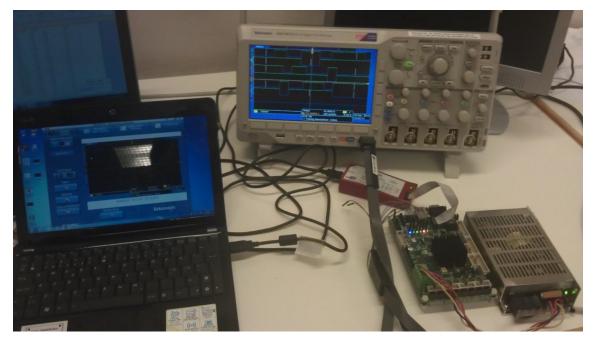

| Figure 4-31 Testing in FPGA card                                                  | 80  |

| Figure 4-32 Graphical output of states in oscilloscope                            | 80  |

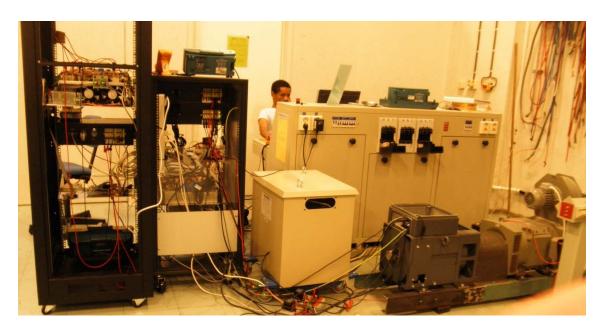

| Figure 5-1 Overview of experimental setup.                                        | 83  |

| Figure 5-2 Assembly of Six phase machine drives                                   | 84  |

| Figure 5-3 Six Phase Induction machine (external overview).                       | 84  |

| Figure 5-4 Six Phase Induction Machine, stator terminal                           | 85  |

| Figure 5-5 Rectifier used in the lab.                                             | 86  |

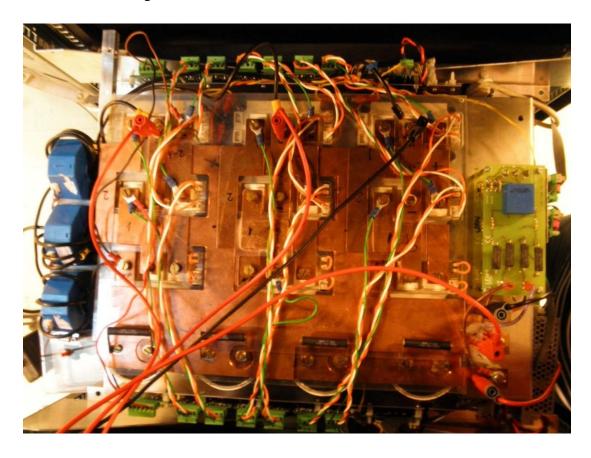

| Figure 5-6 Three Level Inverter.                                                  | 86  |

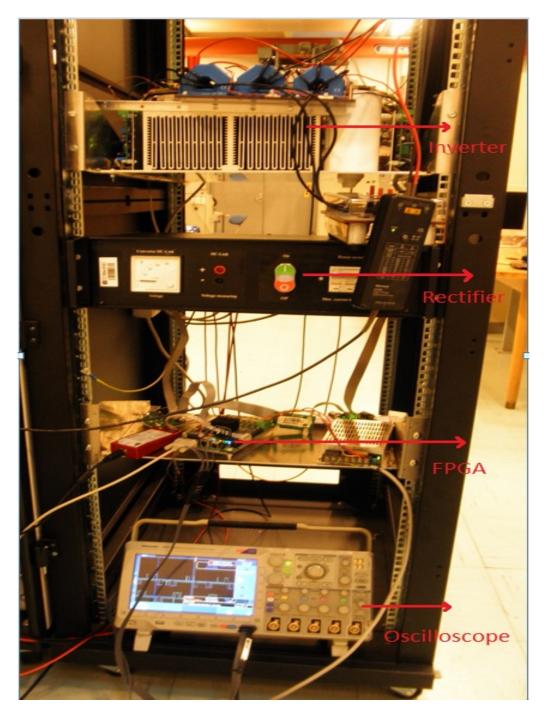

| Figure 5-7 Use of FPGA in experiment.                                             | 87  |

| Figure 5-8 Current sensor.                                                        | 88  |

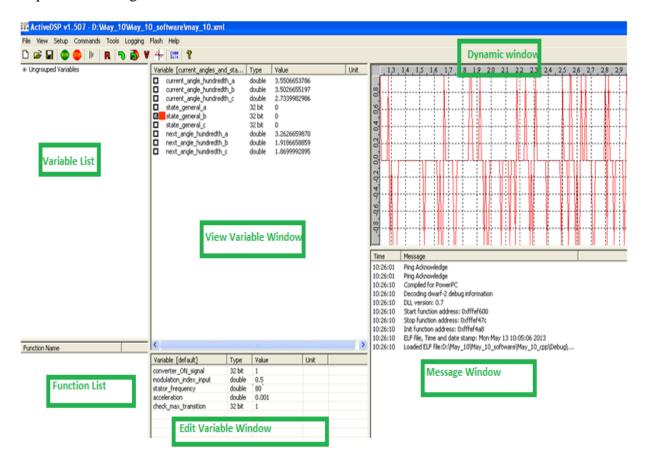

| Figure 5-9 Active DSP for real time monitoring.                                   | 89  |

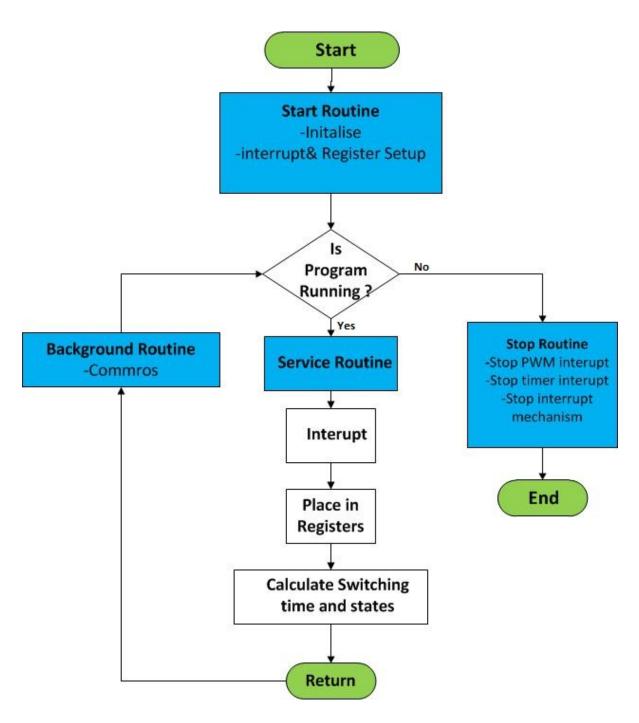

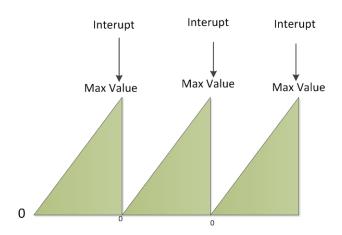

| Figure 5-10 Program flow and interrupt.                                           | 90  |

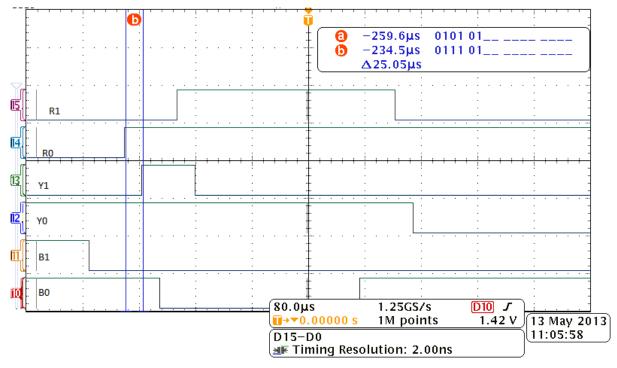

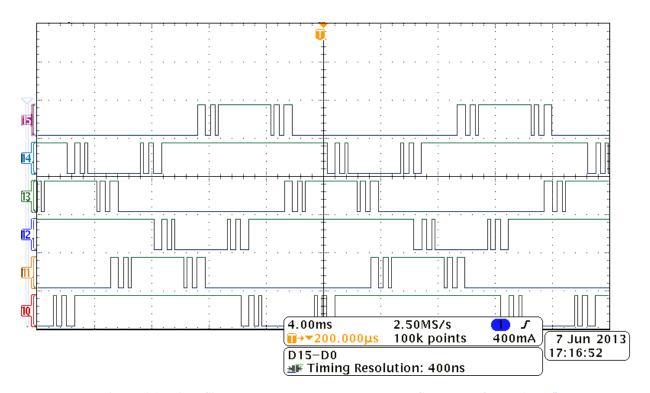

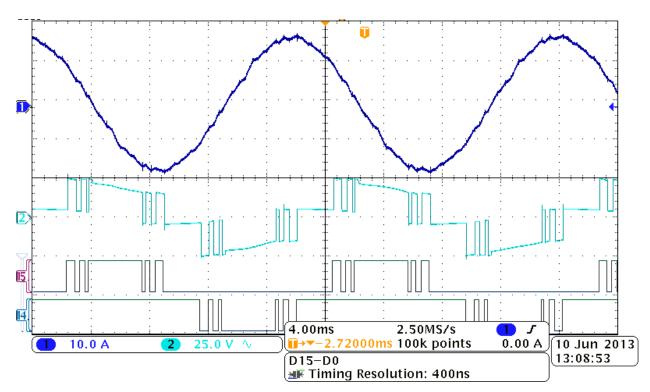

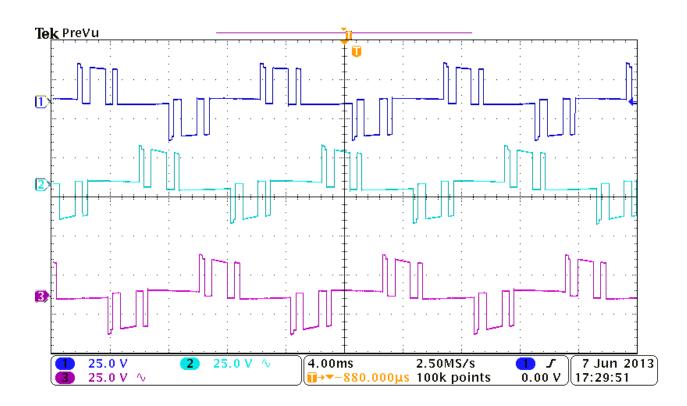

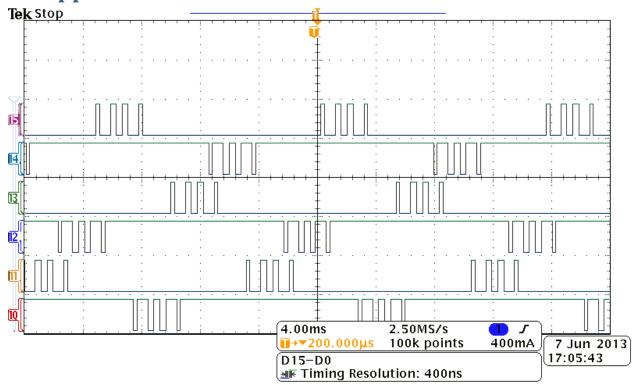

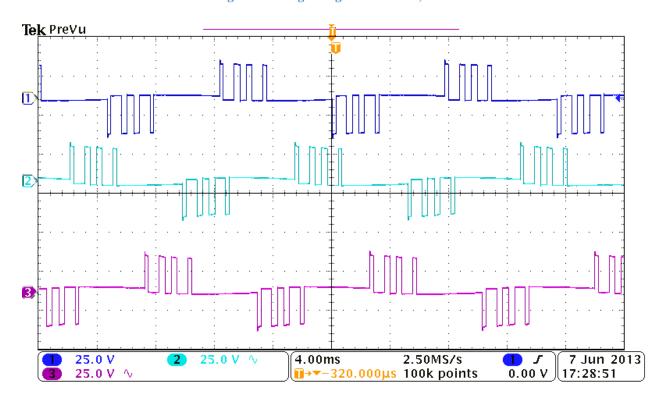

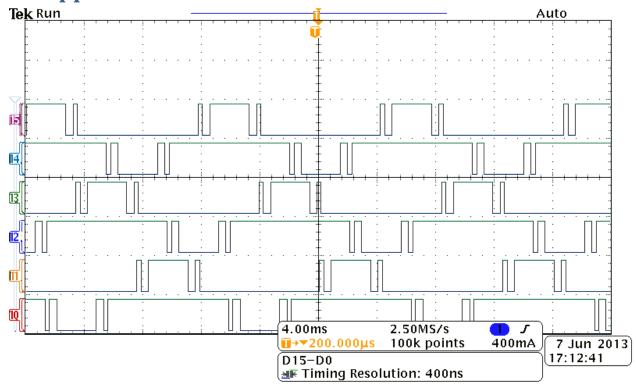

| Figure 6-1 Driver Signals For Three phase, Three level Converter (for m=1, N=5)   | 91  |

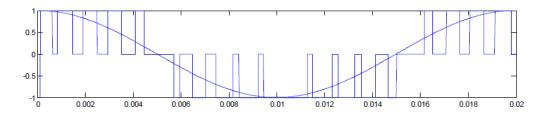

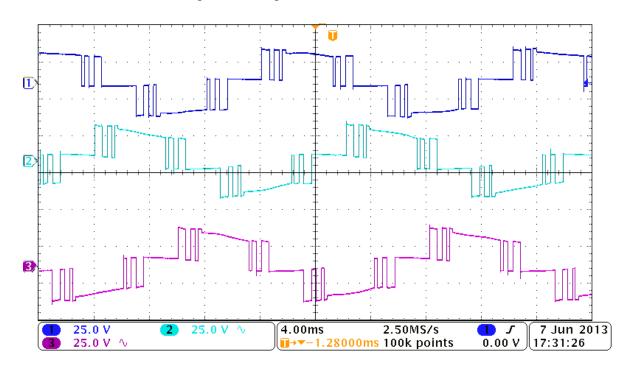

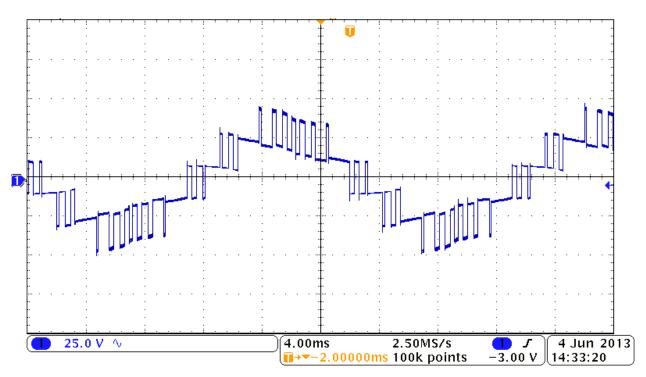

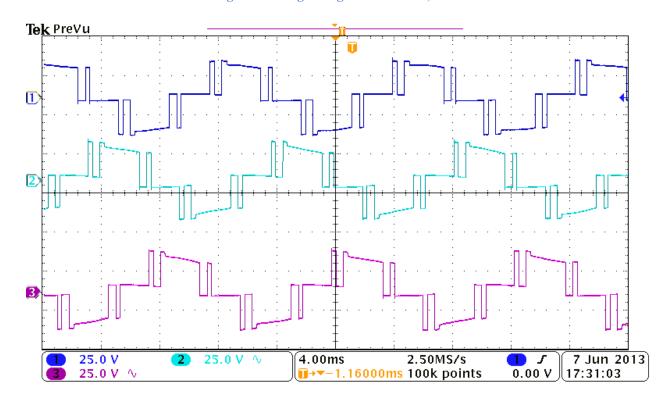

| Figure 6-2 Voltage generated by Three phase, Three level Converter (for m=1, N=5) | 92  |

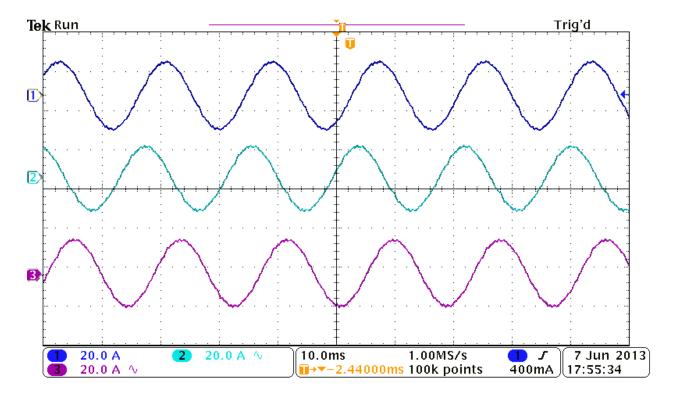

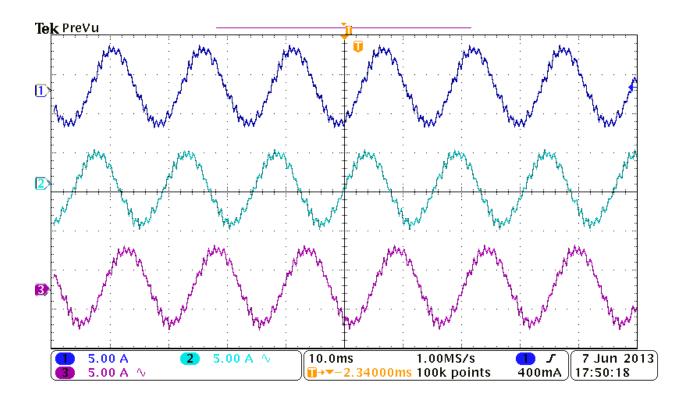

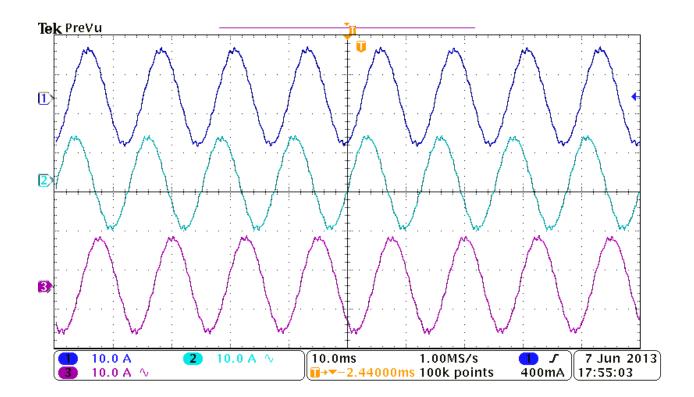

| Figure 6-3 Current given to load (for m=1, N=5).                                  | 93  |

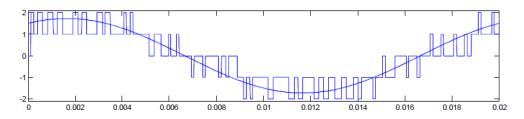

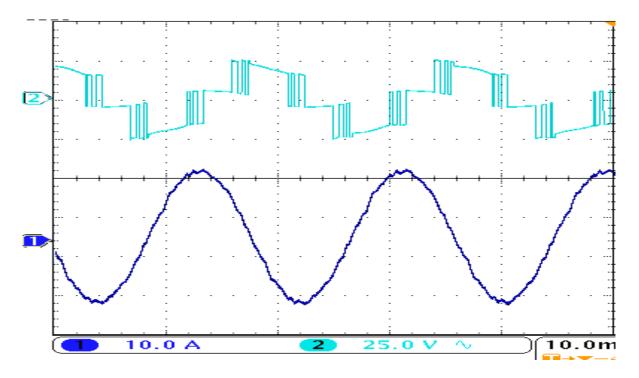

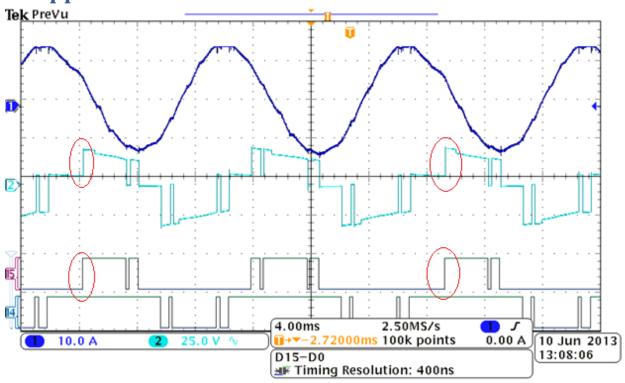

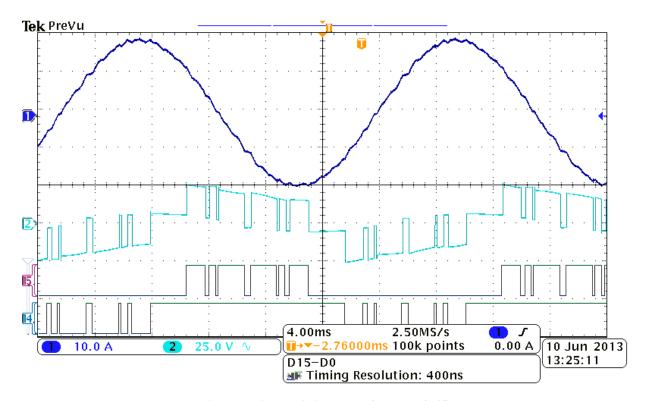

| Figure 6-4 Digital, Voltage, Current signal per phase for m=1, N=5                | 94  |

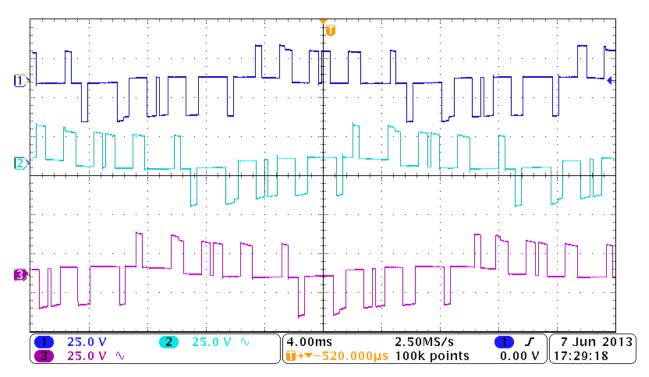

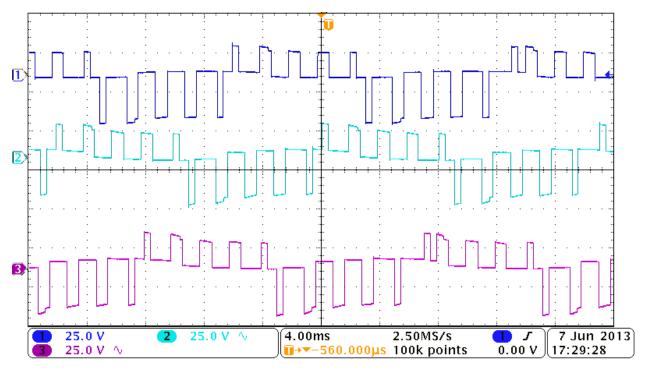

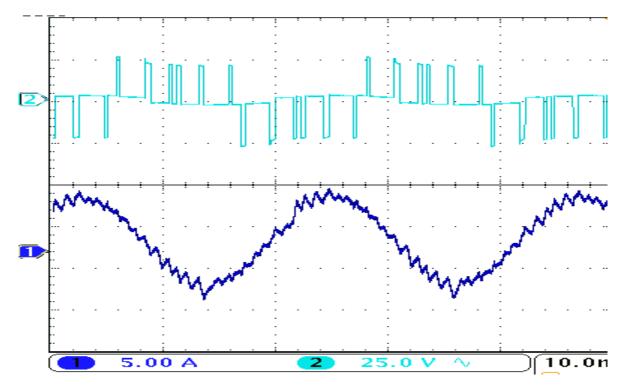

| Figure 6-5 For m=0.5, fs=45Hz, N=6                                                | 95  |

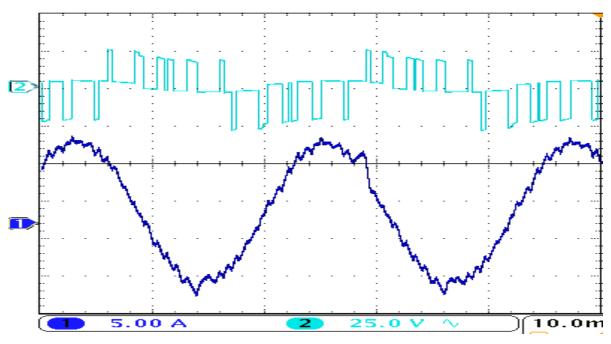

| Figure 6-6 For m=0.5, fs=55Hz, N=5                                                | 96  |

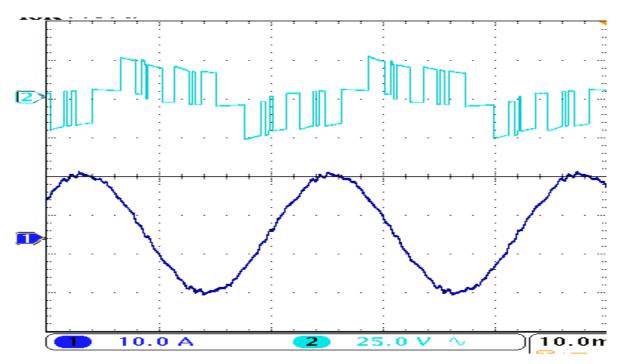

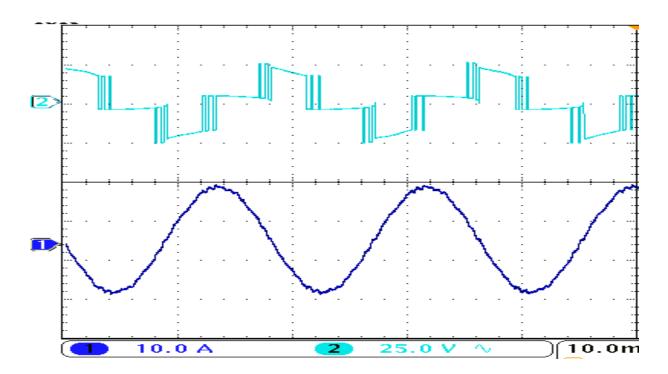

| Figure 6-7 For m=0.5, fs=65Hz, N=4                                                | 96  |

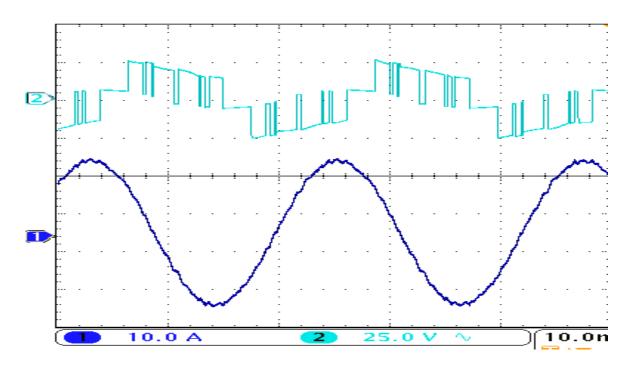

| Figure 6-8 For m=0.5, fs=80Hz, N=3                                                | 97  |

| Figure 6-9 For m= 0.87, fs=45 Hz.                                                 | 98  |

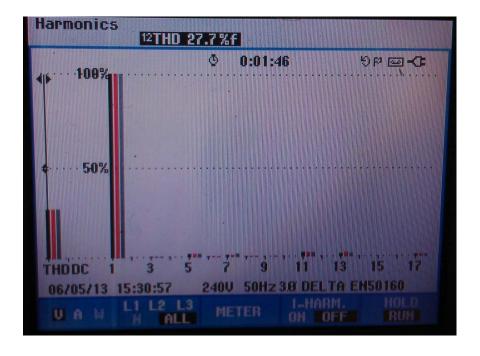

| Figure 6-10 THD for line voltage for m=1, 45 Hz.                                  | 99  |

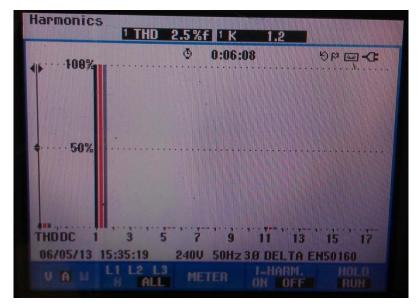

| Figure 6-11 THD for line current for m=1, 50 Hz.                                  | 100 |

| Figure 6-12 Current and Voltage for m=0.3, f=45Hz, N=6                            | 101 |

| Figure 6-13 Current and Voltage for m=0.5, f=45Hz, N=6                            | 101 |

| Figure 6-14 Current and Voltage for m=0.8, f=45Hz, N=6                            | 102 |

| Figure 6-15 Current and Voltage for m=1, f=45Hz, N=6                              | 102 |

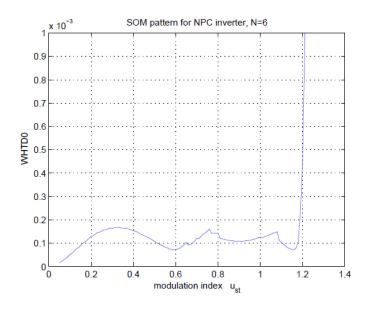

| Figure 6-16 WHTD0 vs modulation index for N=6 (f=45Hz).                       | 103 |

|-------------------------------------------------------------------------------|-----|

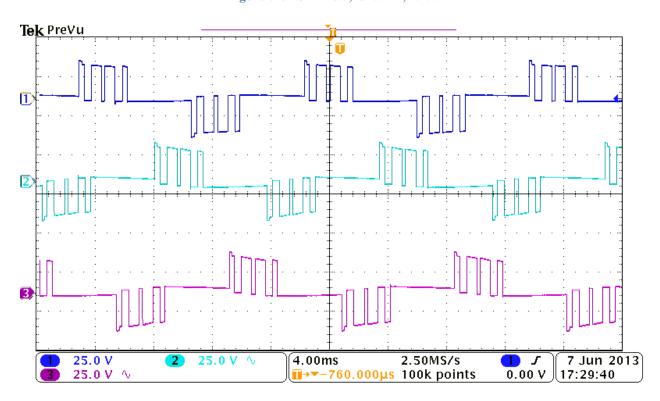

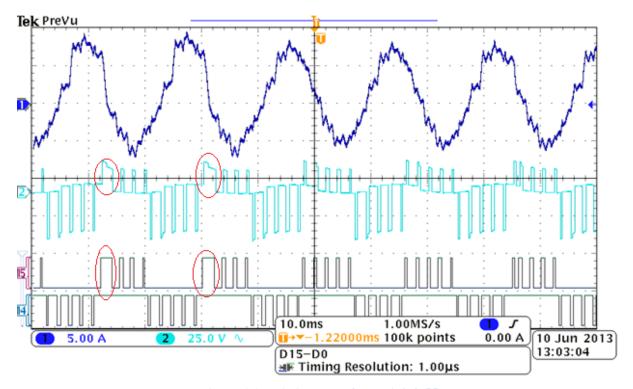

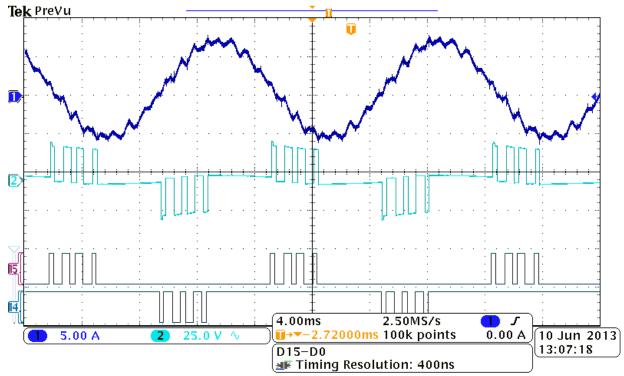

| Figure 6-17 Missing Pulse for m=0.4, f=55 Hz                                  | 105 |

| Figure 6-18 No missing Pulse for m=0.4, f=65 Hz                               | 105 |

| Figure 6-19 Reseting counter.                                                 | 106 |

| Figure 6-20 Overflow counter.                                                 | 107 |

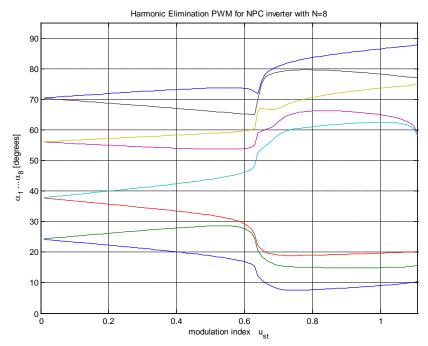

| Figure 9-1 SOM pattern for N=8.                                               | 114 |

| Figure 14-1 Digital signal for m=0.3, N=4.                                    | 139 |

| Figure 14-2 Voltage signal for m=0.3, N=4.                                    | 139 |

| Figure 14-3 Current signal for m=0.3, N=4.                                    | 140 |

| Figure 15-1 Digital Signal for m=0.87, N=3.                                   | 141 |

| Figure 15-2 Voltage Signal for m=0.87, N=3                                    | 141 |

| Figure 15-3 Current Signal for m=0.87, N=3.                                   | 142 |

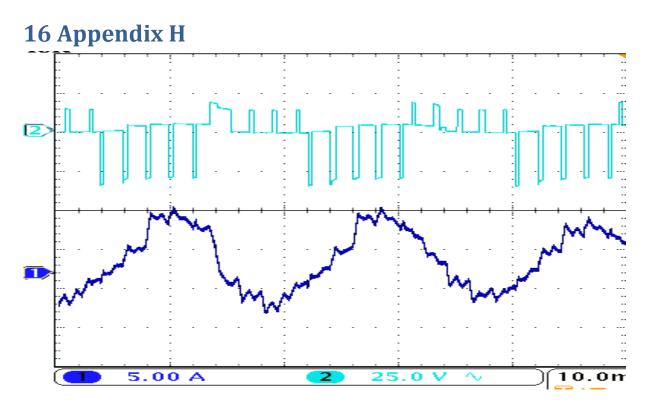

| Figure 16-1 Current and Voltage for m=0.3, f=55Hz, N=5                        | 143 |

| Figure 16-2 Current and Voltage for m=0.5, f=55Hz, N=5                        | 143 |

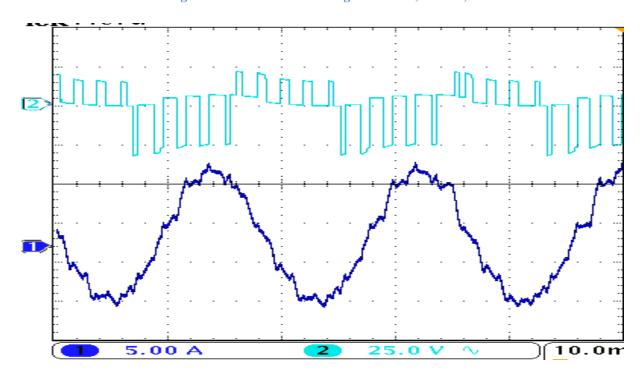

| Figure 16-3 Current and Voltage for m=0.8, f=55Hz, N=5                        | 144 |

| Figure 16-4 Current and Voltage for m=1, f=55Hz, N=5                          | 144 |

| Figure 17-1 Missing Pulse for m=1, f=80 Hz.                                   | 145 |

| Figure 17-2 No Missing Pulse for m=1, f=45Hz.                                 | 145 |

| List of Table                                                                 |     |

| Table 2-1 Harmonics and sequence [21].                                        | 9   |

| Table 2-2 Switching states in three level converter[24].                      | 11  |

| Table 2-3 Overview of space vectors[26]                                       | 17  |

| Table 2-4 Overview of relation between space vectors and neutral current [26] | 17  |

| Table 2-5 Switching angles for different modulation index                     | 30  |

| Table 4-1 Placement of Switching Time and State by Software                   | 77  |

| Table 4-2 result of the simulation.                                           |     |

| Table 4-3 Test result.                                                        |     |

| Table 4-4 Placement of state vector in SOM_spacevector_IP                     |     |

| — ı       —                                                                   | •   |

| Accompany                                                       |     |

|-----------------------------------------------------------------|-----|

| Table 9-1Rating of induction machine.                           | 114 |

| Table 6-4 Comparison with conventional PWM technique            | 104 |

| Table 6-3 THD(Line current) for different modulation index (m). | 100 |

| Table 6-2 THD (Line Voltage) for different modulation index (m) | 99  |

| Table 6-1 variation of N for different fs (m=0.5).              | 97  |

## Acronym

| Acronym | Description                                                       |

|---------|-------------------------------------------------------------------|

| IGBT    | Insulated Gate Bipolar Transistor                                 |

| THD     | Total Harmonic Distortion                                         |

| WHTD    | Weighted Total Harmonic Distortion                                |

| WHTD    | Normalised Weighted Total Harmonic Distortion                     |

| FPGA    | Field-programmable Gate Array                                     |

| SOM     | Synchronous Optimal Modulation                                    |

| SPIM    | Six Phase Induction Machine                                       |

| CLB     | Configurable Logic Block                                          |

| HDL     | Hardware Descriptive Language                                     |

| VHDL    | Very High Speed Integrated Circuits Hardware Descriptive Language |

| IP      | Intellectual Property                                             |

| LVDS    | Low Voltage Differential Signal                                   |

| ADC     | Analog to Digital Converter                                       |

| DSP     | Digital Signal Processor                                          |

| PWM     | Pulse Width Modulator                                             |

| NPC     | Neutral Point Clamped                                             |

| BJT     | Bipolar Junction Transistor                                       |

| MOSFET  | Metal Oxide Semiconductor Field Effect Transistor                 |

| USB     | Universal Serial Bus                                              |

| DRAM    | Dynamic Random Access Memory                                      |

| EROM    | Erasable Read Only Memory                                         |

| MAC     | Media Access Controller MSPS                                      |

| CMOS    | Complementary Metal oxide Semiconductor                           |

| TTL     | Transistor Transistor Logic                                       |

| ISE     | Integrated Software Environment                                   |

| XPS     | Xilinx Platform Studio                                            |

| SDK     | Software Development Kit                                          |

| EDK     | Embedded Development Kit                                          |

| NPSM    | Nine-phase Synchronous Machine                                    |

| UCF     | User Constraint File                                              |

| MPD     | Microprocessor Peripheral Description                             |

| MHS     | Microprocessor Hardware Specification                             |

| PLB     | Processor Local Bus                                               |

| SPWM    | Sinusoidal PWM                                                    |

| SVPWM   | Space Vector PWM                                                  |

| BSP     | Board Support Package                                             |

# **Chapter 1**

## 1 Introduction

In this chapter, the background of this master thesis is presented. In addition to that the motivation to this master thesis is discussed. The literatures read during this master thesis are reviewed and presented here. Because of the time constraints, this master thesis has scope and limitation. These are also given in this chapter.

# 1.1 Background

The power electronic converters decouple three phase mains from the variable speed ac drives so the number of phases of ac machine do not have to be limited to three anymore [1]. This led to the development of multiphase machine. Even though the concept of multiphase machine was emerged some 40 years ago, its interest took new surge in recent years through the advancement of power electronics switching devices [2]. The pace of research in the field of multiphase machine was even more accelerated from 1990s along with the development of electric ship propulsion. Even though there are many other benefits of multiphase machine, they find their major application in area of electric ship propulsion [1].

Electric ship propulsion is beneficial as it provides precise control of the shaft speed, increased manoeuvrability, increased fuel efficiency, reduced environmental impact, and quiet operation [3]. Multiphase machine drives are preferred to the conventional three phase machine drives in electric ship propulsion. It is because the requirements of high power rating, high efficiency, reliability and fault tolerant operation of electric drives for ship propulsion can be met by multiphase machine drives [4].

Medium Voltage ac drives produce greater power than lower voltage drive. They have ability to control high rating electric motors that industrial load require. The higher voltage of MV drive also indicates the lower loss and use of smaller cables that outputs higher efficiency and lower system cost [5].

Wärtsilä, a global leader in ship power technology, has been conducting research on the application of multiphase machine and medium voltage drives in electric ship propulsion. This Master thesis is also done as the part of the research.

#### 1.2 Motivation

The research of multiphase variable speed drives started from 1960s when inverter-fed ac drives were in the initial development stage. In six steps mode of three phase inverter operation, there was one particular problem with low frequency torque ripple. "Since the lowest frequency torque ripple harmonic in an n-phase machine is caused by the time harmonics of the supply of the order  $2n \pm 1$  (its frequency is 2n times higher than the supply frequency), an increase in the number of phases of the machine appeared as the best solution to the problem "[1].

Previously, Voltage source pulse width modulated inverters use square wave or sinusoidal PWM strategies for low voltage ac drives [6]. As industrial load require higher rating ac drives, medium voltage ac drives based voltage source inverter are of higher demand [7]. Advancement in the development of semiconductor devices with higher voltage capabilities like insulated gate bipolar transistors (IGBTs), has allowed increasing the voltage level to medium voltage and power rating of the system up to several MVAs. These IGBTs must be operated in lower switching frequency to keep the switching loss to tolerable level. Once the switching frequency is reduced, appropriate modulation technique is required. The appropriate modulation technique is called Synchronous Optimal Modulation [8].

In order to use IGBTs for Medium Voltage drive, sophisticated technology like Synchronous Optimal Modulation (SOM) is the better choice as it minimizes total harmonic contents. This optimized PWM technique is extremely difficult to be implied by conventional analog circuitry hence they need modern microprocessor or digital hardware like DSP. These sophisticated techniques have access to the effective look-up tables on which this modulation technique can be implemented effectively[9].

Industrial electrical control system has progressed due to technology revolution. The revolution has outcome very powerful components to solve extremely complex control algorithm. The most recent advancement of extremely fast computing device is called field programmable gate array

(FPGA). FPGA allows real time computation of complex control algorithm in a few microseconds [10].

Therefore, it is of interest to implement this sophisticated modulation strategy like SOM in medium voltage drive by using field-programmable gate array (FPGA) components.

#### 1.3 Literature review

For the industrial demand of high power, medium voltage drive is used. Medium voltage ac machines must be operated at low switching frequency to reduce the switching losses of the power semiconductor devices. Once the switching frequency is reduced, appropriate modulation technique like program modulation is required. In 1973 Patel and Hoft [11] generalised the method for eliminating fixed number of harmonic. They provided the solution for eliminating up to five harmonics. While the unlimited higher order harmonics can be attenuated by using filter circuits. Buja and Indri [12] in 1977 started to develop optimal PWM for AC motor. They developed the analytical procedure to calculate proper choice of commutation angles which minimise the rms value of the current harmonics. In 1992, Programmed PWM technique was used by Enjeti and Jakkli [13] to eliminate lower harmonics at the output of Neutral point clamped inverter topology. In 1994, Holtz [14] employed the method called Synchronous optimal pulsewidth modulation(SOM) for medium voltage drives at low switching frequency. SOM is type of Program Modulation pattern.

Murphy, Howard and Hoft[9] came with the idea in 1979 that these optimized PWM strategies are extremely difficult to realize with conventional analog circuitry, but they can be effectively implemented with using a look-up table accessed by modern microprocessor-based control techniques or digital hardware. Recently digital hardware like FPGA is developed which has exceptionally fast computation capability hence complex control algorithm can be computed in few microseconds. In 2007 Naouar and Monmasson [10] presented the interest of implementing digital controllers in AC machine using field-programmable gate array (FPGA) components. Numerous experimental results are given in order to illustrate the efficiency of FPGA-based solutions to achieve high-performance control of electrical systems.

## 1.4 Thesis Scope and Limitation

For generating synchronous optimal modulation technique, the optimal angles must be calculated. This calculation itself accepts lot of work. Hence such calculation is done in other collaborating master thesis. This can be referred from [15]. In this thesis, it is assumed that the optimal angles are already provided by the collaborating thesis. The other collaborating thesis is termed as software and processor routine in this master thesis.

Even though this project is meant to produce synchronous optimal modulation technique for multiphase machine up to 9 phases, this project generates modulation pulse only for three phases. Hence if this project is successful in implementing modulation pulse for three phases, only the slight modification can be done to make it appropriate for nine phases.

# 1.5 Organization of report

In Chapter 1, background, motivation, literature review, scope and limitation of the project are discussed. The theory behind the generation of Synchronous Optimal Modulation is provided in Chapter 2. The type of inverter used is three level Neutral Point Clamped Inverter. Since this project is for medium voltage, Insulated Gate Bipolar Transistor is used as switch. The implementation of three level modulator is done on extremely fast digital device called Field Programmable Gate Array (FPGA). The important portion of the project commence from Chapter 3 which introduces FPGA architecture, FPGA control card developed by SINTEF along with the description of tool called Xilinx which is used to program FPGA. The methodology applied in this project for implementing SOM by using FPGA is presented in Chapter 4 which contains the description of Intelligent Properties (IP) and the connection between various IPs used in this project. The output of the simulation is also shown in this chapter. This thesis also consists of laboratory works for verification of the theories. Therefore Chapter 5 discuss about the experimental setup of the project. Finally results, discussion are presented in Chapter 6 to verify the validity of digital circuitry created in FPGA to fulfil the objective of the project. At last conclusion and further works are presented in the Chapter 7.

.

# Chapter 2

# 2 Theory

In this chapter, multiphase machines are described. In addition inverters and modulators needed for feeding the machine are discussed. The converter which is used is Neutral Clamped Three Level converter while new modulation technique called Synchronous Optimal Modulation is discussed along with its implication in this project.

## 2.1 Electric Propulsion

The shipping industry has advanced from its conventional era. The cost of propulsion has reduced significantly without increasing marine pollution [16]. Electrically powered ship requires energy source for all the ship's functions, including propulsion. They are quieter, are less susceptible to vibration and are comfortable for everyone on board [17].

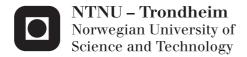

Figure 2-1 Overview of electric propulsion.

The schematic overview of the main electrical and automation components for electric propulsion is shown in Figure 2-1. The propeller shaft of the ship is connected to large motors, which is A.C driven and are known as propulsion motors. These propulsion motors are fed by inverter. Inverters are controlled by Modulator to convert the DC from the DC grid in ships to

required AC needed by motor. Figure shows three phase propulsion motor. But the intense research is going on to replace the three phase motor by multiphase machine.

# 2.2 Multiphase Machine

The power electronic converters decouple three phase mains from the variable speed ac drives so the number of phases of ac machine do not have to be limited to three anymore [1]. This led to the development of multiphase machine. Even though the concept of multiphase machine was emerged some 40 years ago, its interest took new surge in recent years through the advancement of power electronics switching devices [2]. The advantage of multiphase machine include high power ratings, efficiency, reliability and fault tolerant operation. Its advantages over three phase induction machine are listed below.

- The stator copper loss for multiphase machine are less than three phase machine assuming the same torque and same speed [18].

- The harmonics of stator current are of higher order and more attenuated than three phase machine which will reduce the torque pulsation[18].

- As the number of inverter switches increases, ratings of inverter switches decrease which helps to reduce the cost[3].

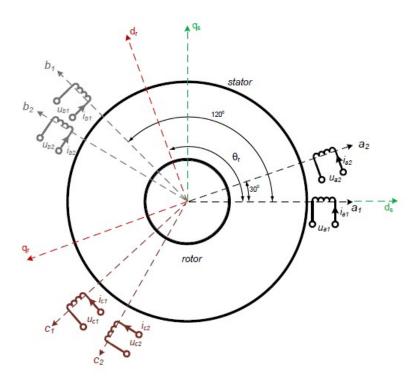

Even though this thesis deals with three phase Induction machine, the main motivation of this project is to make suitable modulation technique which can be extended up to nine phase machine like Nine-phase Synchronous Machine (NPSM). There are not many NPSM in industries. But it has many advantages over three phase machine that its research is intensively going on. The nine-phase Synchronous Machine can be presented by windings as shown in Figure 2-2.

Different winding layouts can be chosen for nine-phase machines. For the physical modelling, nine phase synchronous machine with 3 sets of three phase with 20<sup>0</sup> phase shift is used [19]. The modelling of multiphase machine is out of scope of this project. This project deals with modulation technique developed for the multiphase machine.

Figure 2-2 Nine Phase Synchronous Machine [19].

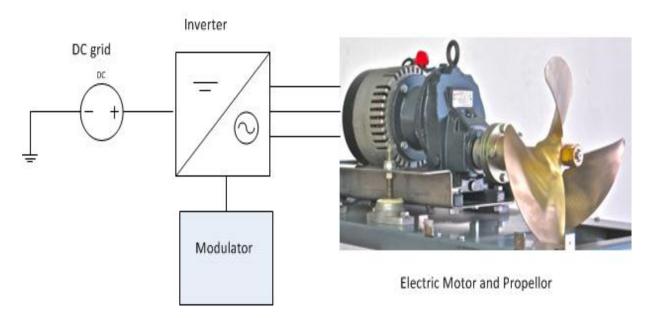

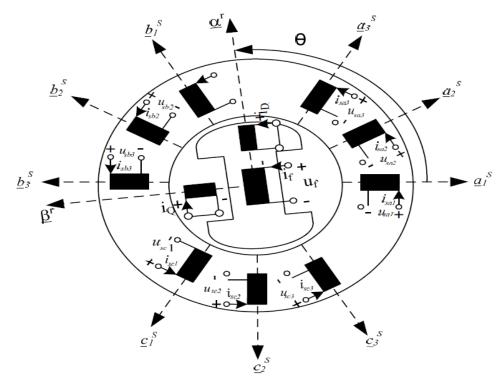

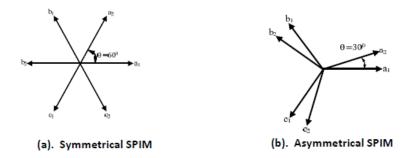

Another kind of multiphase machine can be Six Phase Induction machine (SPIM). It consists of 2 sets of three phase windings. They have gathered lot of interest of drive engineers for the industrial applications. The SPIM can be of two types, symmetric and asymmetric depending upon the winding arrangements as shown in the Figure 2-3, if the axes of the individual phase windings are spaced equiangular as shown in (a) then the machine is called symmetrical SPIM. In asymmetrical SPIM the winding axes are spaced as shown in the Figure 2-3(b).

Figure 2-3 Stator winding types [3].

Asymmetrical SPIM is used for the research purpose than symmetrical as it has less pulsating torque and less harmonic currents as compared to symmetric SPIM [20].

Figure 2-4 Six Phase Induction Machine(SPIM) [3].

#### 2.2.1 Harmonic Losses in Induction Machine

Power electronic converter lies between three phase mains and the induction machine. The voltage generated by power electronics device to be fed to the induction machine is not pure sinusoidal. Fourier Analysis can be done to such non sinusoidal signal which helps to split them into harmonic components. The typical definition for a harmonic is "a sinusoidal component of a periodic wave or quantity having a frequency that is an integral multiple of the fundamental frequency." Except the fundamental frequency, all other higher harmonic components participate in losses of induction machine. Motors are susceptible to harmonic pollution. In a balanced system, the fundamental, 4<sup>th</sup>, 7<sup>th</sup> and other such types of voltage harmonics are positive sequence and they rotate the motor forward. The 2<sup>nd</sup>, 5<sup>th</sup>, 8<sup>th</sup> voltage harmonics are negative sequence, which try to rotate motor backward while the 3<sup>rd</sup>, 6<sup>th</sup>, 9<sup>th</sup> voltage harmonics are zero sequence, which just heat up the motor[21].

Table 2-1 Harmonics and sequence [21].

| HARMONIC | FUND | 2ND | 3RD | 4TH | 5TH | 6TH | 7TH | ETC |

|----------|------|-----|-----|-----|-----|-----|-----|-----|

| SEQUENCE | +    | -   | 0   | +   | -   | 0   | +   |     |

However the losses are not divided evenly over the harmonic spectra. The lower harmonic components contribute more to losses than the higher harmonic components [22]. The reason is lower harmonics indicates lower impedance increasing harmonic current. The higher order harmonics produce lower harmonic current and they can be eliminated easily by using filter circuits in the output stage of the inverter [11]. The filters to attenuate higher order of harmonic components are smaller in size, weight and cost efficient [23].

The uneven distribution of loss in the harmonic spectra require appropriate performance indicator that weights the lower frequency spectra of harmonic components more dominant than the high spectra of the harmonic components [22]. Such indicator is commonly known as Weighted Total Harmonic Distortion (WTHD), which can be calculated by normalizing the total current harmonic distortion by the maximum inrush current. This theory after simplification becomes as equation below[22].

$$WTHD = \frac{\sqrt{\sum_{n=2}^{\infty} (\frac{Un}{n})^2}}{U1}$$

Where, n is  $n^{th}$  number of harmonic component. From equation it is clear that the lower order harmonics participate more due to their high  $1/n^2$  factor compared to that of higher order harmonics.

Harmonic currents also introduce unwanted torque pulsations in induction machines due to the interaction of the harmonic currents and the magnetic field of fundamental frequency. This would create mechanical oscillations and eventual wear of the machine.

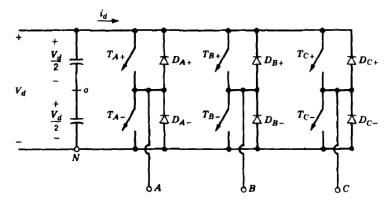

#### 2.3 Three Level Converter

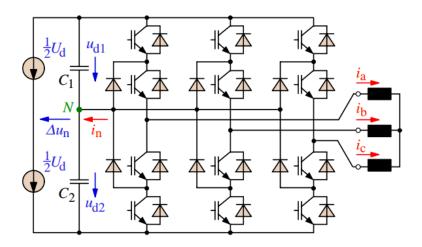

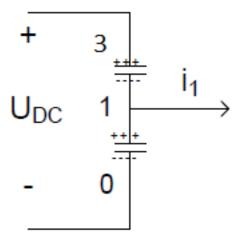

The fundamental advantages of the Multilevel Converter topologies are low distorted output waveforms and limited voltage stress on the switching devices [24]. In this Project, three level converters called Neutral Point Clamped (NPC) is implemented as shown in Figure 2-5. Further,

the NPC inverter is particularly suitable in high-voltage applications since it guarantees equal voltage sharing of series-connected power devices in each phase [13]. The figure is shown for three phase induction motor but if the numbers of bridge leg are added then it can be extended to any multiphase machine. The working principle of three level converters can be understood by analysing single branch as illustrated in Figure 2-6.

Figure 2-5 Three level inverter NPC Technology [24].

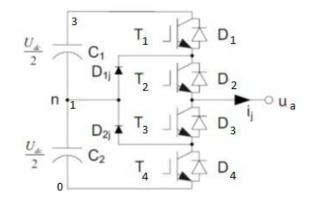

Figure 2-6 Bridge leg of three level converter [24].

Figure 2-6 shows one phase-leg of a three-level, three phase converter. This topology can produce three levels at the output with respect to the neutral point n. Table 2-2 indicates the possible output voltages for each switching state of device. There are three switching levels or states which are +1, 0, -1.

Table 2-2 Switching states in three level converter[24].

| Switching of each IGBT |                |                |       | 2 <i>Uoj</i><br><i>Udc</i><br>(analog | Digital<br>switching<br>state(taking | Ua0                |

|------------------------|----------------|----------------|-------|---------------------------------------|--------------------------------------|--------------------|

| T <sub>1</sub>         | T <sub>2</sub> | T <sub>3</sub> | $T_4$ | switching state)                      | T1 and T2)                           |                    |

| 1                      | 1              | 0              | 0     | +1                                    | 11 (3)                               | $U_{dc}$           |

| 0                      | 1              | 1              | 0     | 0                                     | 01 (1)                               | $\frac{U_{dc}}{2}$ |

| 0                      | 0              | 1              | 1     | -1                                    | 00 (0)                               | 0                  |

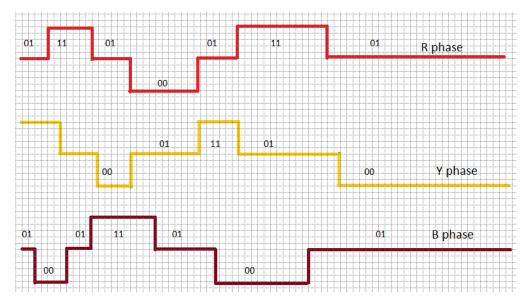

If the signals to upper two IGBTs are considered for three level converter, then +1 can be obtained by giving signal 11 to  $T_1$  and  $T_2$ , while 0 can be obtained by giving signal 01. Similarly -1 can be obtained by giving signal 00 to  $T_1$  and  $T_2$ . Hence 11, 01, 00 are the states that can define the signal +1, 0, -1 or in decimal, the states are 3,1,0. Here 10 (2) is the forbidden state. Signal to T3 and T4 are complementary to T1 and T2 respectively.

Conventionally, the three level modulating signals for the IGBTs are generated by comparing two carrier waves with the sinusoidal wave as shown in Figure 2-7. If sinusoidal wave is greater than carrier signal, switch is turned on otherwise turned off. The upper carrier wave decides the switching state of  $T_1$  while the lower carrier decides the switching state of  $T_2$ . The two switches below,  $T_3$  and  $T_4$  are complementary to two switches above  $T_1$  and  $T_2$  respectively.

Figure 2-7 Naturally sampled PWM for 3 level converter [25].

By combining the different states, it is possible to get waveform close to sinusoidal averaged bridge leg output as shown in figure Figure 2-8. There are three states in bridge leg voltage. Line to Line voltage is also calculated. The voltage between two phases, the line-to-line voltage can achieve five different voltage levels which are +2,+1,0,-1,-2.

Figure 2-8 Bridge leg voltage [26].

Figure 2-9 Line to Line voltage[26].

### 2.3.1 Switching loss in voltage source Inverter

The switching power loss  $P_{sv}$  of a Voltage source Inverter with a sinusoidal ac line current is estimated using the following relation [27]:

$$P_{sv} = \frac{6}{\pi}.f_{s.} \left( E_{on,1} + E_{off,1} + E_{off,D} \right) \cdot \frac{V_{dc}}{V_{ref}} \cdot \frac{I_{L}}{I_{ref}}$$

Where  $f_s$  is the switching frequency,  $E_{on,1}$  and  $E_{off,1}$  are the turn-on and the turn-off energies of the IGBT respectively,  $E_{off,D}$  is the turn-off energy in the power modules' diode due to reverse recovery charge current,  $V_{dc}$  is the dc link voltage,  $I_L$  is the peak value of the ac line current assumed to be sinusoidal and  $V_{ref}$  and  $I_{ref}$  are the reference voltage and current where the switching energies provided by data sheets are given.

It is seen that switching loss increases with increasing switching frequency and increase in Dc link voltage. If Medium voltage is used in order to increase the power rating in drive system then

switching loss is also increased along with it. Therefore as the compensation, switching frequency can be reduced. For medium voltage and low switching frequency, the perfect choice of power conductor device is IGBT. The construction of IGBT is made is such a way that it has higher reverse voltage blocking capability being suitable for medium voltage drive and lower operating switching frequency which shows its suitability for lower operating frequency. However if the switching frequency is low then there will be problem in modulation which will be discussed in the remaining sections.

#### 2.3.2 Harmonic content of voltage source Inverter

The output of the voltage source converter is not pure sinusoidal wave. Hence it possesses certain amount of harmonics at their output due to finite switching frequency. The output voltage of the converter can be analyzed by Fourier series.

$$V(t) = V_o + \sum_{h=1}^{\infty} V_h (t)$$

The three level voltage source converter is shown in Figure 2-5.

If the load is balanced three phase load then some harmonics in line to line voltage will be cancelled out even though they exist in bridge leg voltage. Let  $U_{a0}$ ,  $U_{b0}$  and  $U_{c0}$  are the voltages at the phase outputs (or bridge leg) of the inverter with respect to the dc-link then line-to-line voltage will be [25].

$$U_{ab}(t) = U_{a0}(t) - U_{b0}(t)$$

$$U_{bc}(t) = U_{b0}(t) - U_{c0}(t)$$

$$U_{ca}(t) = U_{c0}(t) - U_{a0}(t)$$

The neutral voltage  $U_0$  (t) is common in all the bridge leg hence the above equation can be further expressed as.

$$U_{a0}(t) - U_{b0}(t) = U_{a}(t) - U_{b}(t)$$

$$U_{b0}(t) - U_{c0}(t) = U_{b}(t) - U_{c}(t)$$

$$U_{c0}(t) - U_{a0}(t) = U_{c}(t) - U_{a}(t)$$

In balanced three phase load, phases are  $120^0$  out of phase with each other, so at any instant the sum of all the phase voltage sum upto zero.

$$U_{a0} + U_{b0} + U_{c0} = 0$$

$$U_a - U_0 + U_b - U_0 + U_c - U_0 = 0$$

The neutral voltage  $U_0$  can be expressed as function of the phase voltages of the load as follows:

$$U_0(t) = \frac{U_a(t) + U_b(t) + U_c(t)}{3}$$

Using this value and inserting in above equations, the following equations can be obtained.

$$\begin{split} &U_{a}(t) = \frac{1}{3} \cdot \left( 2 \cdot U_{a0}(t) - U_{b0}(t) - U_{c0}(t) \right) + U_{0} \\ &U_{b}(t) = \frac{1}{3} \cdot \left( 2 \cdot U_{b0}(t) - U_{c0}(t) - U_{a0}(t) \right) + U_{0} \\ &U_{c}(t) = \frac{1}{3} \cdot \left( 2 \cdot U_{c0}(t) - U_{a0}(t) - U_{b0}(t) \right) + U_{0} \end{split}$$

The classical dq0-transformation one obtains:

$$\begin{bmatrix} U_{sd}^{s} \\ U_{sq}^{s} \\ U_{s0} \end{bmatrix} = \frac{1}{3} \cdot \begin{bmatrix} 2 & -1 & -1 \\ 0 & \sqrt{3} & -\sqrt{3} \\ 1 & 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} U_{a} \\ U_{b} \\ U_{c} \end{bmatrix} = \frac{1}{3} \cdot \begin{bmatrix} 2 \cdot U_{a0}(t) - U_{b0}(t) - U_{c0}(t) \\ \sqrt{3} \cdot (U_{b0}(t) - U_{c0}(t)) \\ 3 \cdot U_{0}(t) \end{bmatrix}$$

The d-axis voltage component is equal to the difference between two line voltages. The q-axis voltage component is proportional to the line voltage:

$$U_{sd}^{s}(t) = \frac{1}{3} \cdot \left( 2 \cdot U_{a0}(t) - U_{b0}(t) - U_{c0}(t) \right) = \frac{1}{3} \cdot \left( U_{ab}(t) - U_{ca}(t) \right)$$

$$U_{sq}^{s}(t) = \frac{1}{\sqrt{3}} \cdot \left( U_{b}(t) - U_{c}(t) \right) = \frac{1}{\sqrt{3}} \cdot \left( U_{b0}(t) - U_{c0}(t) \right) = \frac{U_{bc}(t)}{\sqrt{3}}$$

The d-component will have the same harmonics as the difference between two line voltages, while the q-component has the same harmonics as one line voltage. As common components in all bridge leg voltages will not be present in the load. This indicates that motor as a load will not

see the harmonics presented in the bridge leg voltage but it only sees the harmonics presented in the line-to-line voltage. Some harmonics in line to line will be cancelled out even though they exist in bridge leg voltage. If the PWM patterns of the three bridge legs are 120 degree phase shifted, i.e. the pattern is three phase symmetrical so no harmonics of multiple of three, exists in the d- and q-axis system even if they exist in the bridge leg voltages. Two important conclusions are:

- Even signals in the bridge leg voltages is cancelled in the line voltages

- Harmonics multiple with 3 do not exist in the d- and q- voltages.

## 2.3.3 DC Bus Balancing

#### 2.3.3.1 Introduction

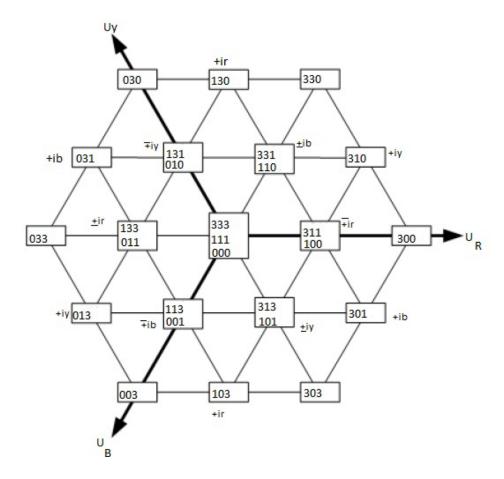

In NPC converter as shown in Figure 2-5, there are two capacitors. Depending upon the type of neutral point current, the charging of two capacitors may differ creating voltage difference between them. This phenomenon can increase the voltage stress in the equipment connected across them. In the worst case, all the DC link voltage could be across only one of the capacitors. Hence DC Bus balancing is necessary to keep the voltage difference between the two capacitors small. The output voltage also does not follow the reference value and increase the harmonic distortion in presence of unbalance in capacitor voltages [26]. Space Vector method can be used in order to control the voltage across the capacitor. In space vector, Phase R,Y,B are located 120° out of phase to each other in vector space. A three level converter has 27 vectors to create the desired voltage with 19 different states as shown in Figure 2-10.

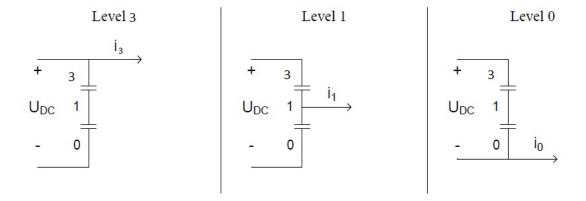

NPC converter has three states namely 0,1,3 where 2 is the forbidden state. In Figure 2-10 MSB consists the state of R phase while LSB consist of state of B phase. The currents flowing in different states for a bridge leg are given in Figure 2-11. In level 3, the current flows from the top, in level 1, there is flow of current from neutral point while in level 0, there is flow of current from the bottom.

Figure 2-10 Space vector diagram for three level converter.

Figure 2-11 Position of current at different level [26].

Vectors can be divided into four different groups according to magnitude of the vectors. The overview is given in Table 2-3.

Table 2-3 Overview of space vectors[26].

| Zero Vectors | Small Vectors        | Medium Vectors | Large Vectors |

|--------------|----------------------|----------------|---------------|

| (000)        | (100)(311)(110)(331) | (310)(130)     | (300)(330)    |

| (111)        | (131)(010)(011)(133) | (031)(013)     | (030)(033)    |

| (333)        | (001)(113)(101)(313) | (103)(301)     | (003)(303)    |

The vectors are

$$U_{s} = \frac{1}{2}U_{DC}.e^{j\theta}$$

$$U_{m} = \frac{1}{\sqrt{3}}U_{DC}.e^{j\theta}$$

$$U_{l} = \frac{2}{3}U_{DC}.e^{j\theta}$$

Where, U<sub>DC</sub> is DC link voltage. U<sub>s</sub>, U<sub>m</sub>, U<sub>l</sub> means small, medium, large vectors respectively.

The neural current determines the charging and discharging of capacitor. A zero vector is when all the bridge legs are connected to the same point and all of the line-to-line voltages are zero. Hence zero vector does not create voltage difference. The six large vectors also do not affect unbalance in voltage in capacitor. It is because the large vector do not have neutral current as it does not involve level 1. Therefore only six medium vectors and six pairs (twelve) of small vectors influence voltage balance. The overview is given in Table 2-4. The sum of current in three phase equal to zero. The same table shows the neutral current flowing at different vector combination. For instance 100, Ir flows through neutral point in R bridge leg while Iy and Ib flows through the bottom of the Y and B bridge leg as shown in Figure 2-11.

Table 2-4 Overview of relation between space vectors and neutral current [26].

| Positive small vectors | $I_{Np}$ | Negative small Vectors | $I_{Np}$ | Medium vectors | $I_{Np}$ |

|------------------------|----------|------------------------|----------|----------------|----------|

| 100                    | Ir       | 311                    | -Ir      | 310            | Iy       |

| 331                    | Ib       | 110                    | -Ib      | 130            | Ir       |

| 010                    | Iy       | 131                    | -Iy      | 031            | Ib       |

| 133                    | Ir       | 011                    | -Ir      | 013            | Iy       |

| 001                    | Ib       | 113                    | -Ib      | 103            | Ir       |

| 313                    | Iy       | 101                    | -Iy      | 301            | Ib       |

Similarly for 311, Ir flows through top of R bridge leg while Iy and Ib flows through the neutral point in Y and B bridge leg. But we know, Ir+Iy+Ib=0 and Iy+Ib=-Ir. So it can be said that the total neutral current flowing for the state 311 is –Ir as shown in Table 2-4.

The positive neutral current will charge the upper capacitor while discharge the lower capacitor while negative neutral current charges oppositely. It can be seen in Figure 2-12, where the direction of current is taken positive. The figure clearly shows how this positive current is charging the upper capacitor and discharging the lower capacitor. For the negative current, the phenomenon is just opposite. In the Figure 2-10 the belonging phase currents are shown with a plus and minus sign. The plus sign is representing a positive vector, while a negative sign is representing a negative vector.

Figure 2-12 Charging of upper capacitor and discharging of lower capacitor.

#### 2.3.3.2 DC balancing

In order to remove the unbalance in voltage between two capacitors, six small vector pairs are controlled. When a small vector pair is involved a total duty cycle of d1 is calculated, where d1 is a duty cycle of  $T_{tri}$ . This is given in detail in [26]. This duty cycle is divided into two for DC bus balancing.

$$d_1 = d_{1,p} + d_{1,n}$$

Where  $d_{1,n}$ = duty cycle of negative vector  $d_{1,p}$  =duty cycle of positive vector

These two duty cycle will be equal in the case of balanced voltage. For unbalanced voltage control parameter  $f_1$  is introduced to define positive and negative vector.

$$d_{1,p} = f_1 \cdot d_1$$

and  $d_{1,n} = (1 - f_1) \cdot d1$

The value of  $f_1$  must be calculated which depends on phase current and capacitor voltage. For the situation when voltage in upper capacitor is greater than the lower capacitor or  $U_{dcu} > U_{dcl}$ , such vector which discharge the upper and charge the lower must be selected. That means that negative vector must be selected. It is already defined in above section that negative vector will give negative neutral current which discharges the upper capacitor and charge the lower capacitor. For the opposite case, positive vector must be selected. The value of  $f_1$  should be 0.5 at balanced situations and it should be regulated depending on the voltage difference and direction of the current. The equation of  $f_1$  is as shown below.

$$f_1 = 0.5 - k. \frac{abs(U_{dcu} - U_{dcl})}{(U_{dcu} + U_{dcl})}$$

K is in this case a constant which has to be given a proper value. As it can be seen from the formula, the value of  $f_1$  is depending on the difference in capacitor voltage.

# 2.4 Modulation Strategy

At present, voltage source converters are mostly used in electrical drives. These converters utilize capacitors in the DC-link to store temporarily electrical energy. Switching the power electronic devices allows the DC voltage to be modulated which can result in a variable voltage and frequency waveform. The purpose of the modulator is to generate the required switching signals for these switching devices.

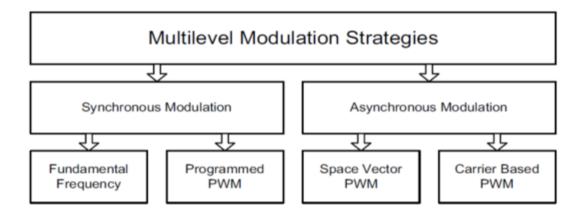

There are various ways of modulation. The overview of a modulation method is listed in Figure 2-13. Multilevel Modulation strategies are mainly divided into Synchronous and Asynchronous Modulation[25]. The division is based on the value of index called frequency modulation index.

$m_f = \frac{f_c}{f_s}$ . Here  $m_f$  is called frequency modulation index,  $f_c$  is called carrier frequency and  $f_s$  is called reference fundamental frequency or stator frequency.

Figure 2-13 Modulation strategies[24].

The modulation strategies are as shown in Figure 2-13. Modulation strategies are divided into two major areas which are as follows:

#### a) Asynchronous Modulation:

When stator frequency is very low, it impacts frequency modulation to be greater than 20. There will be high pulse number. In such scenario, zero crossing between carrier wave and reference signal is not synchronized even if it results in unequal number of pulses in positive and negative half cycle. For such high pulse number, difference of few pulse numbers between positive and negative half cycle does not make huge impact hence the effect of sub-harmonic component is minimal. Such kind of modulation in which zero crossings between the carrier wave and reference signal are not synchronized is called asynchronous modulation.

There are two types of asynchronous modulation.

- i) Space Vector PWM

- ii) Carrier Based PWM

Among these two type Carrier Based is discussed here.

#### Carrier Based PWM :

In Carrier Based PWM, generally there is reference wave which is compared with carrier wave. The switching pulses are determined by the result of the comparison. If reference wave is greater in magnitude than the carrier wave then pulse is ON otherwise OFF. Carrier Based PWM is further divided according to the sampling of the reference wave. They are

- a) Naturally sampled PWM

- b) Regularly Sampled PWM

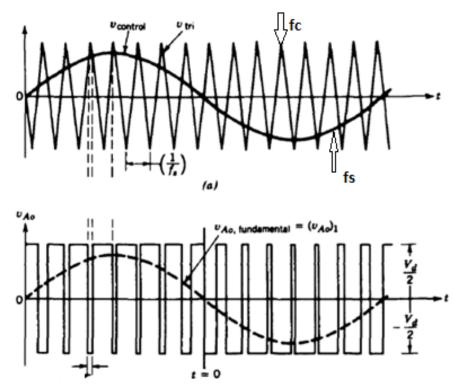

#### ➤ Naturally sampled Pulse Width Modulation:

This is the classical method where analog circuitry like amplifier is used for comparison of carrier wave and reference wave. The reference voltage then change continuously within the triangular period (carrier wave) as in Figure 2-14. If continuously changing reference wave is greater than triangular wave, the switching pulse is ON otherwise OFF.

Figure 2-14 Naturally sampled PWM[23].

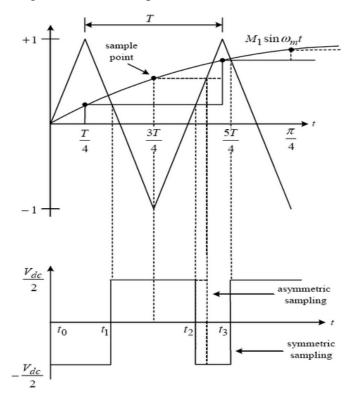

#### Regular sampled Pulse Width Modulation:

A method which is easier to implement in digital form is the regular sampled PWM. In this case the reference voltage is sampled at top and bottom of the triangular wave and then kept constant until next sample. This sampled reference wave is compared with the magnitude of triangular wave and switching occurs. Similar to Naturally Sampled PWM, the pulse is ON if sampled reference wave is greater than triangular wave and OFF for the opposite case. This method is further divided into:

- Symmetrical Regular sampled PWM

- Asymmetrical Regular sampled PWM

- Symmetrical Regular sampled PWM: The reference voltage is only sampled at the top of the triangular wave and kept constant within the complete triangular period.

- Asymmetrical Regular sampled PWM: The reference voltage is sampled both at the top and bottom of the triangular wave and kept constant within half the triangular period.

Figure 2-15 Symmetric and asymmetric regular sampled PWM.

The reference wave is stator frequency, which keep on changing. There will be change in the carrier wave as well if frequency modulation is kept constant. As we know the formula for the frequency modulation,

$$m_f = \frac{f_c}{f_s}$$

where  $m_f$  is called frequency modulation index,  $f_c$  is called carrier frequency (or switching frequency) and  $f_s$  is called reference fundamental frequency.

$$f_c = m_f * f_s$$

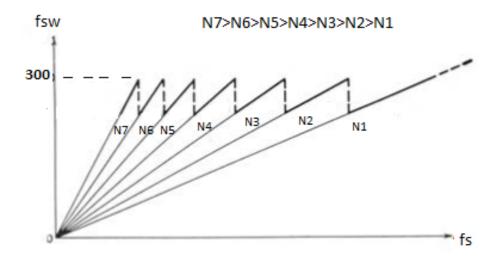

For, the application in motor, for the variable speed drive, the stator frequency (or fundamental frequency  $f_s$ ) may vary. For particular  $m_f$ ,  $f_c$  varies proportional to  $f_s$ . However to keep the carrier frequency constant, close to its maximum value, frequency modulation index must

decrease when stator frequency is increased or vice versa as seen in Figure 2-16. In order to keep carrier frequency constant, there is change in the ratio  $(m_f)$  in the different ranges of  $f_c$ .

Figure 2-16 Carrier based PWM [23].

#### b) **Synchronous Modulation**:

For small values of frequency modulation (20 or less), the number of pulse are lower hence even the difference in pulse number in positive and negative half cycle by one unit will generate sub harmonics. To prevent from such scenario, the carrier waveform signal and the control signal should be synchronized to each other. That means the zero crossing of carrier wave (triangular) and reference wave (sinusoidal) should coincide in order to prevent from sub harmonic. This type of modulation is called synchronous modulation. As a result of this, number of pulses in positive half cycle is equal to that in negative half cycle. The average switching frequency is  $f_c$  /2. This type of modulation is important for low pulse number whose violation can result in sub-harmonics in motor voltage. Synchronous Modulation is further divided into two parts called fundamental frequency synchronous PWM and Program PWM.

- i) Fundamental frequency Synchronous PWM:

- ii) **Program Modulation PWM**:

Among these two, this thesis deals with the second type.

#### • Program Modulation PWM

This method pre-calculates optimal switching angles within a period of the fundamental period  $1/f_s$  to minimize the harmonic distortion. But these switching angles are not formed by carrier wave like in conventional way. This pattern or angles are programmed, or stored, as look-up

tables in hardware. This type of modulation is termed as Program Modulation. Since this is also synchronous modulation the number of pulses in positive and negative half cycle are equal. This is explained in detail in section below.

## 2.5 Program Modulation Technique

### 2.5.1 Background

BJT and MOSFET have characteristic that complement each other. BJT have lower conduction losses in the on state, especially in devices with larger blocking voltages, but have low operating frequency. MOSFETs can be turned on and off much faster but their on state conduction losses are larger, especially in devices rated for higher blocking voltages. Hence device is made whose performance is midway between BJT and MOSFET called Insulated Gate Bipolar Transistor (IGBT). Its switching frequency is higher than a comparable BJT but lower than MOSFET whereas the on state losses are smaller than MOSFET and are comparable with those of BJT for larger blocking voltage [23].

It is shown in section 2.3.1, switching loss increases with increasing switching frequency and increase in Dc link voltage. If Medium voltage is used in order to increase the power rating in drive system then switching loss is also increased along with it. Therefore as the compensation, switching frequency can be reduced. For medium voltage and low switching frequency, the perfect choice of power conductor device is IGBT. The construction of IGBT is made is such a way that it has higher reverse voltage blocking capability and lower operating switching frequency.

For the medium voltage drive, the inverter will be designed for a 6.6 kV output voltage, which means a dc-link voltage of approximately 10 kV. The most realistic choice of IGBTs are those with a blocking voltage of 4.5 kV [25]. Hence series connection of devices is required in a three Level inverter. In these devices the switching loss is a quite large part of the total losses. Hence the switching frequency of IGBT must be lower, in the range of 200-1000Hz.

In the equation,  $m_f = \frac{f_c}{f_s}$ , f<sub>s</sub>=stator frequency and f<sub>c</sub>=carrier frequency or switching frequency

$m_f$ = frequency modulation index. For lower frequency, the value of frequency modulation is low (20 or less). Lower carrier frequency results in lower pulse number hence even the difference of pulse in positive and negative cycle by one unit will make huge difference. However such kind of equalization is not necessary in higher carrier frequency.

Hence, the lower carrier/switching frequency demand synchronized modulation. Among two types of synchronous modulation, Programmed Modulation is introduced here. Program Modulation pre-calculates optimal switching angles within a period of the fundamental period 1/fs. These patterns or angles are programmed, or stored, as look-up tables in hardware [25].

### 2.5.2 Program Modulation

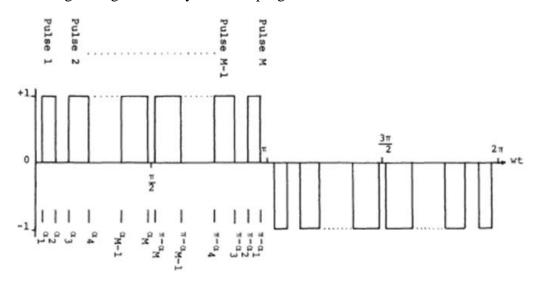

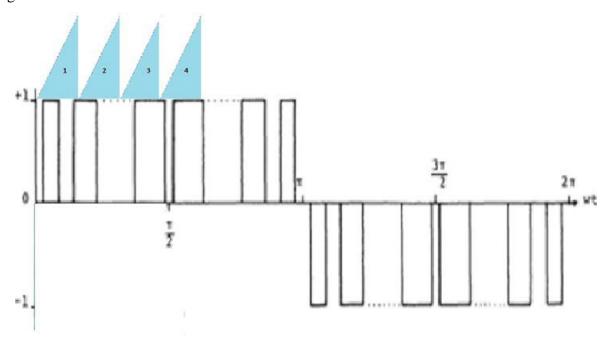

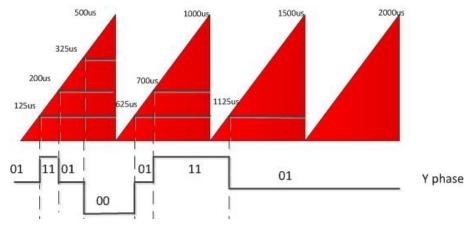

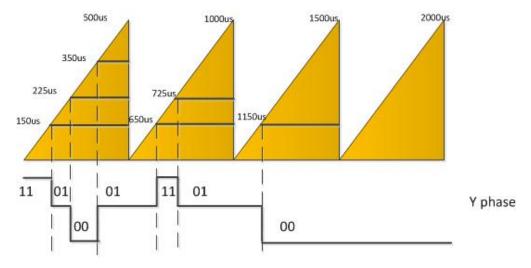

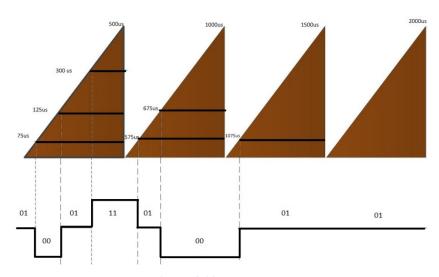

Programmed Modulation is a synchronous modulation technique. In Programmed Modulation switching events can take place freely over the fundamental period as indicated in Figure 2-17. However, these switching instances are not given by a carrier signal. These switching instances are pre-calculated by some software program. The Figure 2-17 is the output for the program modulation for three level converter for one phase. This method is described initially in [13] and revised in [22] and [25]. For two level converter this method is initially studied in [11]. This type of modulation signal is generated by software program.

Figure 2-17 Programmed PWM pattern (M=N)[22].

In Figure 2-17, Instead of M, N will be used in this thesis. There are some parameters which characterize this signal which are number of pulses in a half period (N), fundamental frequency or stator frequency ( $f_s$ ) and switching frequency of IGBT ( $f_{sw}$ ).

N is number of pulses per half period. In addition, the number of turn-on of upper switch is N and number of turn-off is N as well in one half period. The total number of commutations is thus 2\*N per half period and 4\*N per period. In a complete three-phase inverter this becomes 12\*N switching. The average switching frequency over one period for the upper switch is thus:

$$f_{swl.avg} = N \cdot f_s$$

where  $f_s$  is stator frequency.

If this is compared with a carrier based PWM, with the same number of pulses N per half period the equivalent ratio  $m_f$  becomes:

$$N = \begin{cases} 0.5 \cdot (m_f + 1) \\ 0.5 \cdot (m_f - 1) \end{cases} \qquad m_f = \frac{f_c}{f_s} = 3,9,15,21,27,\dots$$

Program Modulation technique is synchronous modulation. Hence at first it is needed to check if synchronous or asynchronous modulation has to be applied. At low speed and thus frequency  $f_s$ , asynchronous modulation can be used with a fixed switching frequency of 200 Hz. For 200 Hz max switching frequency this gives a max motor frequency  $f_s$ , with N=10 (even):

$$f_{s1} = \frac{f_c}{m_f} = \frac{200}{21} = 9.52Hz$$

Above this stator frequency, synchronous modulation is chosen. This also means below N=10 (below  $m_f = 21$ ), synchronous modulation is chosen.

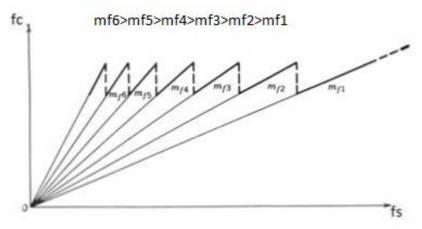

For synchronous modulation in motor drives using Program Modulation, the number N has to be selected to give a proper curve similar to Figure 2-16, but with N as parameter instead of  $m_f$  and  $f_{sw}$  instead of  $f_c$ , where  $f_{sw}$  is called switching frequency while  $f_c$  is called carrier frequency. The Figure 2-16 is modified for program modulation and it looks like Figure 2-18

Figure 2-18 Programmed PWM.

Switching frequency increases with increase in stator frequency for constant N. However the maximum operating frequency for IGBT is 300 Hz. In this process, if switching frequency becomes more than 300Hz then N is decreased as stator frequency increases.

## 2.6 Synchronous Optimal Modulation

In Program Modulation, these switching instances are pre-calculated by some software program, in order to achieve a purpose by applying some kind of constraint in Fourier series of the fundamental frequency. Usually these methods are divided into **Harmonic Elimination PWM** and **Minimum-loss PWM** methods. Harmonic Elimination PWM is used for the active rectifier which is out of scope of this thesis. For motor drive application Minimum-loss Program Modulation method can be used. This kind of modulation technique is called Synchronous Optimal Modulation (SOM). In SOM pattern, switching events are determined by software in a way that reduces the harmonic content in the current, also reducing losses due to harmonic distortion in the controlled induction machine [28].

Losses in an induction machine due to presence of harmonic components of higher order than the fundamental component, is not divided evenly over the harmonic spectra. The lower harmonic components contribute more to losses than the higher harmonic components. The low harmonic components produce lower impedance resulting in higher harmonic current. The uneven distribution of loss in the harmonic spectra require appropriate performance indicator that weights the lower frequency spectra of harmonic components more heavily than the high spectra

of the harmonic components [22]. Such indicator is commonly known as Weighted Total Harmonic Distortion (WTHD).

In drives applications the motor leakage inductance is limiting the harmonic currents. The weighted total harmonic distortion factor for current is then [22]:

$$THD_{i} = \frac{1}{\omega_{1}L} \cdot \sqrt{\sum_{h=2}^{\infty} \left(\frac{\hat{U}_{a,h}}{h}\right)^{2}}$$

$$WTHD = \frac{THD_{i}}{\hat{I}_{a,1}} = \frac{\omega_{1}L \cdot THD_{i}}{\hat{U}_{a0,1}} = \frac{1}{\hat{U}_{a0,1}} \cdot \sqrt{\sum_{h=2}^{\infty} \left(\frac{\hat{U}_{a0,h}}{h}\right)^{2}}$$

The SOM pulse patterns for a Three-Level NPC converter is as shown in Figure 2-17. In the figure, Instead of M, N will be used in this paper. N stands for number of pulses in a half period or number of transitions in quarter wave. Here +1 actually means Udc1 and -1 is equal –Udc2 and zero potential is the Neutral Point (NP) in the three level inverter. The total dc-link voltage Udc is equal:

$$U_{dc} = U_{dc1} + U_{dc2}$$

$U_{dc1} = U_{dc2} \Rightarrow U_{dc1} = U_{dc2} = \frac{U_{dc}}{2}$

The Fourier series coefficients do only have sine-term and odd number of harmonics due to Half Wave Symmetry (HWS) and the Quarter Wave Symmetry (QWS). The peak value of the h<sup>th</sup> harmonic becomes [22]:

$$\hat{U}_{a0,h} = \frac{4 \cdot U_{dc1}}{h \cdot \pi} \cdot \sum_{k=1}^{N} (-1)^{k+1} \cdot \cos(h \cdot \alpha_k) \qquad 0 < \alpha_1 < \alpha_2 \dots < \alpha_N < \frac{\pi}{2}$$

$$h = 6 \cdot i \pm 1, \qquad i = 1, 2, 3, 4 \dots$$

(1)

At this point, another modulation index called amplitude modulation index ( $u_{st}$  or m) is introduced. Amplitude Modulation index is proportional to fundamental voltage component [29] amplitude modulation, m or  $u_{st} = \frac{u}{u_{dc}}$ , u is rms voltage of the modulated signal,  $u_{dc}$  is dc link voltage. The modulation index is

$$u_{st} = u_{a0,1} = \frac{4}{\pi} \cdot \sum_{k=1}^{N} (-1)^{k+1} \cdot \cos(\alpha_k) \qquad 0 < \alpha_1 < \alpha_2 \dots < \alpha_N < \frac{\pi}{2}$$

(2)

Hence the objective function is to minimize the following WHTD expression

$$WTHD = \frac{1}{\hat{U}_{a0,1}} \cdot \sqrt{\sum_{h=2}^{\infty} \left(\frac{\hat{U}_{a0,h}}{h}\right)^2} = \frac{1}{\hat{U}_{a0,1}} \cdot \sqrt{\sum_{i=1}^{\infty} \left(\left(\frac{\hat{U}_{a0,6i-1}}{6i-1}\right)^2 + \left(\frac{\hat{U}_{a0,6i+1}}{6i+1}\right)^2\right)}$$

(3)

The optimization task is then, for each modulation index, to find the set of N angles from  $\alpha 1$ , ...,  $\alpha N$  of equation (2), to minimize the function of WTHD of equation (3).

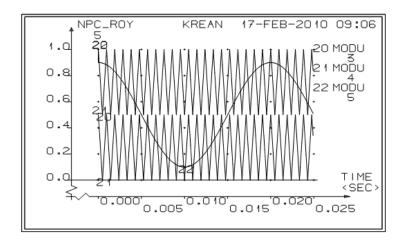

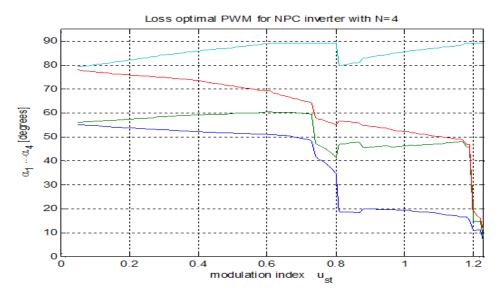

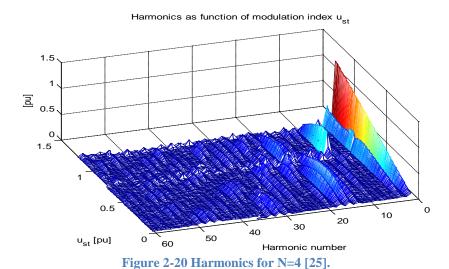

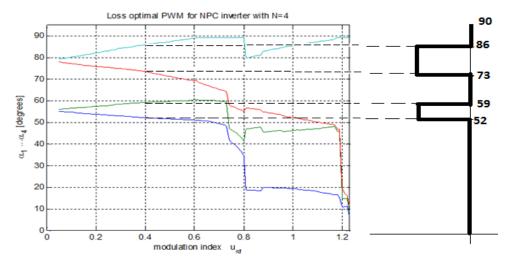

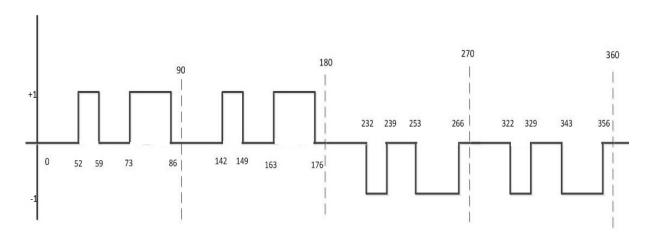

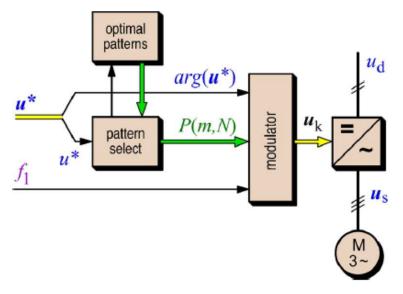

Algorithm is developed by Roy Nilsen at Wartsila Norway [25] to find the required switching angles for given amplitude modulation index to minimize the total harmonic distortion. The example is shown in Figure 2-19 for N (no. of switching transitions in quarter wave)=4. Whenever the value of modulation index varies, the switching angles are changed in order to minimize the harmonic loss. The angles are only shown for quarter wave but the angles for rest of the period can easily be predicted as will be mentioned in section 2.7. Table 2-5 has tabulated the angles for five amplitude modulation index. As the modulation index change, the angles also change. Similarly there are other SOM patterns for different values of N. The example is shown for N=8 in the Appendix A. It means that for one particular value of (m,N) there is one particular type of switching signals. The harmonics as the function of modulation index is given in Figure 2-20.

Figure 2-19 SOM pattern for N=4 [25].

Table 2-5 Switching angles for different modulation index

| $u_{st}$ | α1 | α2 | α3 | α4 |

|----------|----|----|----|----|