# Development of a Universal Verification Component for CPU UVM Verification

Bernhard Bakken

Master of Science in ElectronicsSubmission date:July 2018Supervisor:Kjetil Svarstad, IESCo-supervisor:Vitaly Marchuk, Microchip Technologies Norway AS

Norwegian University of Science and Technology Department of Electronic Systems

## PROJECT ASSIGNMENT

Candidate name: Bernhard Bakken

**Assignment title:** Development of a Universal Verification Component for CPU UVM verification

Assignment text: The current UVM CPU verification framework contains several agents for working with different bus types. They were developed in accordance with earlier UVM methodology. Recent development showed possibility of creation of a single unified agent working with various buses by encapsulating bus functionality into interfaces, thus substantially reducing amount of resources required for developing and maintaining verification components.

- 1. Student needs to create universal verification component (UVC agent) by moving functionality from drivers and monitors to bus.

- 2. Modify current verification framework to work with UVC.

- 3. Find optimal way of configuring UVC to operate on different buses by using UVM configuration database.

- 4. Show benefits in terms of code reduction.

- 5. Compare advantages and disadvantages of both methodologies.

Prerequisites: understanding of CPU architecture, SystemVerilog for design and verification, basic understanding of UVM, some scripting language as Perl or Python would be an advantage.

Assignment proposer/Co-supervisor: Vitaly Marchuk, Microchip Technology Norway AS

Supervisor: Kjetil Svarstad

## Abstract

The time used debugging and developing testbenches in FPGA and ASIC/IC projects is around 60% of the total time spent in verification. The last years has shown an increase in the adoption of the Universal Verification Methodology(UVM), which can help increase the maximum reuse, and decrease the time spent creating and debugging testbenches.

This thesis presents the development of a Universal Verification Component(UVC) for CPU UVM verification. An existing framework has been used as a base in the development. In the project an improvement of the existing sequence items has been done by creating a new sequence item that is functional for several protocols, and can be extended for additional functionality. Specialised functionality, that can be called through tasks, has been moved from the driver and monitor to the interface, which helps create generic components. A task implemented in the interface, which converts signals from the DUT to a sequence item, is called from the monitor and used to write to the analysis ports. There has also been developed a sequencer that is functional for various protocols in the framework. Parameterisation has been utilised for all the components in the hierarchy, in order to grant the specialised functionality for the protocols. The agent, which is parameterised with a configuration object and sequence item, builds the testbench with configuration that has been retrieved from the configuration database, by using the the handle for the various protocols' agent to find the correct path.

The amount of code lines has been used to quantify some of the efficiency of the UVC, as a decrease in code lines would most likely result in less bugs, and therefore less time spent debugging. There was a total of 28% decrease in amount of code lines for the protocols, when compared to the base framework. 21 files in the framework have also been replaced by the generic components developed in this project.

The UVC that has been developed, can be reused in several frameworks with its parameterisation. The framework that adopts the UVC has to set the configuration in the configuration database as presented in this thesis for correct functionality. This UVC can decrease the time used debugging and creating testbenches, and the time saved can help the verification engineer to reach deadline, or be used to further improve the quality of the tests.

## Sammendrag

Tiden som blir brukt i debugging og å lage testbenker for FPGA- og ASIC/ICprosjekter er rundt 60% av den totale tiden som går med i verifikasjon. De siste årene har vist en økning av å ta i bruk Universal Verification Methodology(UVM), som kan hjelpe i å gi en økning av gjenbruk, og senke tiden som blir brukt i å lage og debugge testbenker.

Denne avhandlingen presenterer utviklingen av en Universal Verification Component(UVC) for CPU UVM verifikasjon. Ett eksisterende rammeverk har blitt brukt som grunnlag i utviklingen. I prosjektet har en forbedring av ett eksisterende sequence item blitt gjort, slik at den fungerer for flere protokoller eller kan bli utvidet for mer funksjonalitet. Spesialisert funksjonalitet, som kan bli kalt gjennom funksjoner, har blitt flyttet fra driveren og monitoren til grensesnittet, som hjelper lage en generisk component som kan bli brukt av flere protokoller. En funksjon som konverterer signaler fra DUTen til sequence items er implementert i grensesnittet, er kalt fra monitoren og brukt til å skrive til analyse portene. Det har også blitt utviklet en sequencer som er funksjonell for forskjellige protokoller i rammeverket. Alle komponentene i hierarkiet har blitt parametrisert for å få spesialisert funksjonalitet i alle protokollene. Agenten, som er parametrisert med et konfigurasjonsobjekt og sequence item, bygger testbenken ved hjelp av konfigurasjon som er hentet fra konfigurasjonsdatabasen ved å bruke håndtaket for de forskjellige protokollenes agenter for å velge riktig vei.

Antall kodelinjer har blitt brukt for å kvantifisere noe av effektiviteten av UVCen, siden mindre kodelinjer vil mest sannsynlig resultere i mindre bugs og derfor mindre tid brukt på å finne de. Det var totalt 28% mindre kodelinjer for protokollene når det ble sammenlignet med det gamle rammeverket. 21 filer i rammeverket har også blitt erstattet med de generiske komponentene utviklet i dette prosjektet.

UVCen som har blitt utviklet kan bli gjenbrukt i flere rammeverk ved å bruke parameteriseringen. Rammeverket som bruker UVCen må sette konfigurasjonen i konfigurasjonsdatabasen i tråd med det som har blitt gjort i denne avhandlingen, for korrekt funksjonalitet. Denne UVCen kan også redusere tiden brukt for å debugge og lage testbenker, og tiden spart kan brukes til å nå deadlines eller for å forbedre kvaliteten på testene.

## A cknowledgements

I would express my gratitude to my supervisors: Vitaly Marchuk from Microchip Technologies Norway AS and Professor Kjetil Svarstad from NTNU for their expert advice, guidance, support and encouragement throughout this project.

# Contents

| Project Assignment | i    |

|--------------------|------|

| Abstract           | ii   |

| Sammendrag         | iv   |

| Acknowledgements   | v    |

| List of Figures    | xi   |

| List of Tables     | xiii |

| Abbreviations      | xv   |

|                    | -    |

| T        | Intr | oducti | ion          | 1     |        |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 1        |

|----------|------|--------|--------------|-------|--------|----------------------|----|------|------|-----|----|-----|-----|---|---|--|---|--|---|--|---|---|---|----------|

|          | 1.1  | Motiva | atio         | on    |        |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 1        |

|          | 1.2  | Contri | ibu          | tion  | s      |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 2        |

|          | 1.3  | Metho  | odo          | logy  | ·      |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 3        |

|          | 1.4  | Thesis | s O          | verv  | riew   |                      | •  |      |      | •   | •  |     |     | • | • |  | • |  | • |  | • | • | • | 3        |

| <b>2</b> | Bac  | kgroun | nd           |       |        |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | <b>5</b> |

|          | 2.1  | Univer | rsa          | l Ve  | rifica | tion                 | Ν  | ſetl | nod  | ol  | og | у.  |     |   |   |  |   |  |   |  |   |   |   | 5        |

|          |      | 2.1.1  | Η            | loriz | ontal  | l and                | łV | /ert | tica | 1 I | Re | use | e . |   |   |  |   |  |   |  |   |   |   | 6        |

|          |      | 2.1.2  | Т            | est   |        |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 7        |

|          |      | 2.1.3  | Е            | nvir  | onm    | $\operatorname{ent}$ |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 7        |

|          |      | 2.1.4  | $\mathbf{S}$ | core  | boar   | d.                   |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 8        |

|          |      | 2.1.5  | Α            | gent  | 5      |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 8        |

|          |      | 2.1.6  | D            | rive  | r      |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 9        |

|          |      | 2.1.7  | N            | Ionit | tor .  |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   | 10       |

|          |      |        |              |       |        |                      |    |      |      |     |    |     |     |   |   |  |   |  |   |  |   |   |   |          |

|   |            | 2.1.8          | Sequencer                                  |

|---|------------|----------------|--------------------------------------------|

|   |            | 2.1.9          | Sequence Item 10                           |

|   |            | 2.1.10         | Interfaces                                 |

|   |            | 2.1.11         | Transaction Level Modeling                 |

|   |            | 2.1.12         | Transaction Methods                        |

|   |            | 2.1.13         | Polymorphism 13                            |

|   |            | 2.1.14         | Factory 14                                 |

|   |            | 2.1.15         | Generic Programming 15                     |

|   |            | 2.1.16         | Parameterisation                           |

|   |            | 2.1.17         | Inheritance                                |

|   |            | 2.1.18         | Configuration Objects                      |

|   |            | 2.1.19         | Configuration                              |

|   | 2.2        | Comp           | rehensive UVM                              |

|   |            | 2.2.1          | Universal Verification Component           |

|   |            | 2.2.2          | Dual Top for Accelerated Verification      |

|   |            | 2.2.3          | Synchronisation                            |

| 3 | Vor        | ificatio       | n Infrastructure 27                        |

| J | 3.1        |                | ng CPU UVM Framework                       |

|   |            | 3.1.1          | Protocols                                  |

|   |            | 3.1.2          | Top Level                                  |

|   |            | 3.1.3          | Environment                                |

|   |            | 3.1.4          | Configuration                              |

|   |            | 3.1.5          | Virtual Sequencer and Sequencers           |

|   |            | 3.1.6          | Agents                                     |

|   |            | 3.1.7          | Drivers                                    |

|   |            | 3.1.8          | Monitors                                   |

|   |            | 3.1.9          | Sequencer and Sequences 35                 |

|   |            | 3.1.10         | Interface                                  |

|   |            | 3.1.11         | Sequence Item                              |

|   |            | 3.1.12         | Instruction Set Simulator                  |

|   | 3.2        | Improv         | ving the Existing Framework                |

|   |            | 3.2.1          | Attempt to Create a Unified Agent          |

|   |            | 3.2.2          | Considerations when Creating a Unified UVC |

| 4 | Мо         | difying        | the Verification Infrastructure 41         |

| 4 | 4.1        |                | ng a Starting Point                        |

|   | 4.1        |                | ng from the Bottom                         |

|   | 4.2<br>4.3 |                | ving the Sequence Items                    |

|   | 4.3<br>4.4 |                | g Functionality                            |

|   | 4.4        | 4.4.1          | The Interfaces         48                  |

|   |            | 4.4.1          | Configuration Object                       |

|   |            | 4.4.2<br>4.4.3 | Attacking the Driver       51              |

|   |            | 1.1.0          |                                            |

|          |      | 4.4.4 Modifying the Monitor                                                                                                       | 57 |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|          |      | 4.4.5 Parameterisation                                                                                                            | 61 |

|          |      | 4.4.6 Changing the Configuration                                                                                                  | 62 |

|          |      | 4.4.7 Changing the Cache Setup                                                                                                    | 64 |

|          |      |                                                                                                                                   | 66 |

|          |      | 4.4.9 Further Improvement of the Components                                                                                       | 66 |

|          |      | 4.4.10 Minor Modifications                                                                                                        | 70 |

|          | 4.5  | Adopting the UVC                                                                                                                  | 72 |

| <b>5</b> | Res  | ults                                                                                                                              | 75 |

|          | 5.1  | The Non-generic Code                                                                                                              | 75 |

|          | 5.2  | Generic Code                                                                                                                      | 76 |

| 6        | Disc | cussion                                                                                                                           | 79 |

|          | 6.1  | Code Reduction                                                                                                                    | 79 |

|          | 6.2  | Parameterisation and Object Oriented Programming                                                                                  | 81 |

|          | 6.3  | Configuration                                                                                                                     | 81 |

|          | 6.4  | Advantages and Disadvantages                                                                                                      | 82 |

|          | 6.5  | The Inconveniences                                                                                                                | 84 |

|          |      | 6.5.1 Incomplete code $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                     | 84 |

|          |      | 6.5.2 Lost in Translation $\ldots$                                                                                                | 85 |

|          |      | 6.5.3 The Iobus_qr Protocol $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                        | 85 |

|          |      | 6.5.4 The Irq Protocol $\ldots \ldots \ldots$ | 85 |

|          | 6.6  | Alternative Framework Setup                                                                                                       | 85 |

| 7        | Con  | clusion                                                                                                                           | 87 |

|          | 7.1  | Future Work                                                                                                                       | 88 |

### Bibliography

89

# List of Figures

| 1.1  | Where Verification Engineers spend their time $[1]$                                    |

|------|----------------------------------------------------------------------------------------|

| 1.2  | FGPA Methodologies and Testbench Base-Class Libraries[1] 2                             |

| 2.1  | Block Level UVM Test Bench - Hierarchical Layers 6                                     |

| 2.2  | Active agent                                                                           |

| 2.3  | Passive agent                                                                          |

| 2.4  | Agent with analysis port and subscribers                                               |

| 2.5  | Abstract Factory pattern[2]                                                            |

| 2.6  | Inheritance                                                                            |

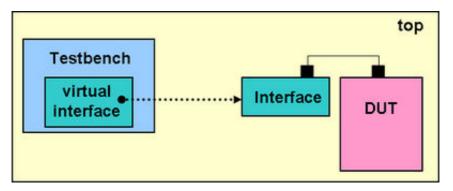

| 2.7  | Single $top[3]$                                                                        |

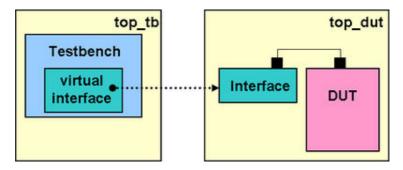

| 2.8  | Dual Top $[3]$                                                                         |

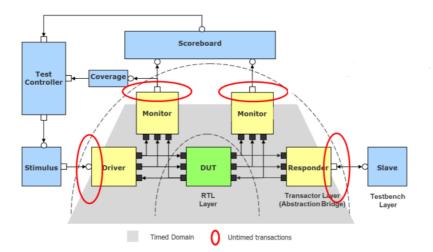

| 2.9  | UVM layered testbench [4] $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 25$ |

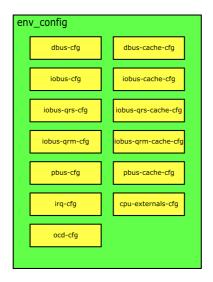

| 3.1  | Environment's configuration object                                                     |

| 3.2  | Configuration passing 32                                                               |

| 3.3  | Virtual interface passing                                                              |

| 3.4  | Monitor writes to analysis port                                                        |

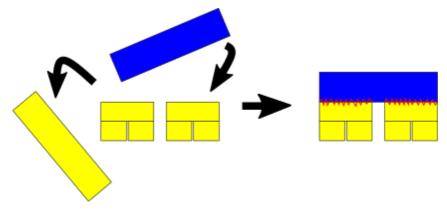

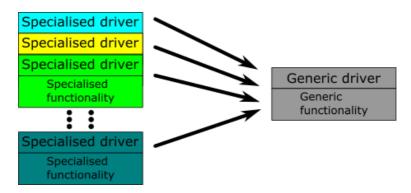

| 4.1  | Agents extended from base class 42                                                     |

| 4.2  | Specialised agents                                                                     |

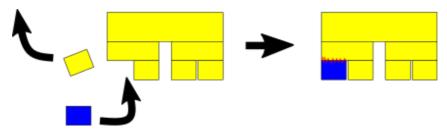

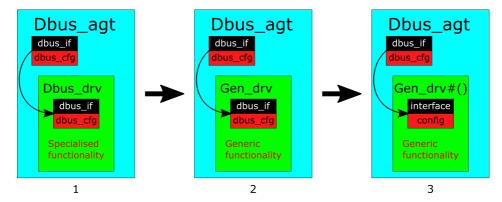

| 4.3  | Changing the top block 44                                                              |

| 4.4  | Changing bottom block 45                                                               |

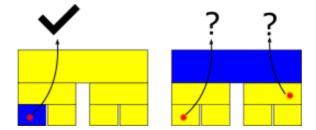

| 4.5  | Bug propagation in the different methodologies                                         |

| 4.6  | From many specialised drivers to one generic driver                                    |

| 4.7  | Creation of generic driver                                                             |

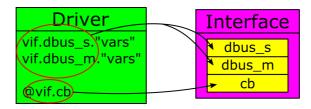

| 4.8  | Driver access variables through the interface                                          |

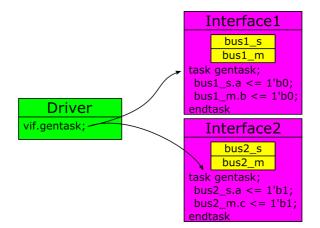

| 4.9  | Use of tasks to communicate with interface                                             |

| 4.10 | Converting signals to item                                                             |

| 4.11 | Configuration object set by database                                                   |

| 4.12 | Verification infrastructure build order                                                |

| 4.13 | Configuration objects with cache enable bit                                            |

| 4.14 | Handle to virtual interface changed                                                    |

| 5.1 | Transactions are registered            | 78 |

|-----|----------------------------------------|----|

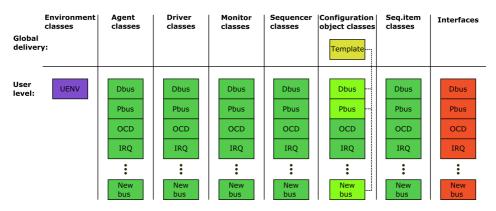

| 6.1 | Class overview for specified framework | 83 |

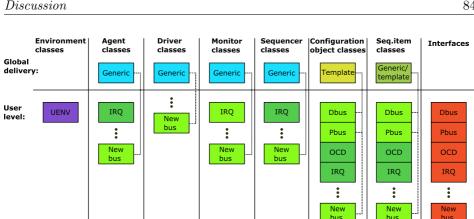

| 6.2 | Class overview for framework with UVC  | 84 |

# List of Tables

| 2.1 | Overview over inherited variables and functions                         | 18 |

|-----|-------------------------------------------------------------------------|----|

| 4.1 | Number of code lines in non-generic code                                | 44 |

| 5.1 | Lines of code in the top of the hierarchy for the specialised framework | 76 |

| 5.2 | Lines of code in the protocols, specialised framework                   | 76 |

| 5.3 | Lines of code in the top of hierarchy for the new framework             | 77 |

| 5.4 | Lines of code in developed files                                        | 77 |

| 5.5 | Files removed                                                           | 78 |

| 5.6 | Number of code lines in the protocols, new framework                    | 78 |

# Abbreviations

| $\mathbf{BFM}$ | $\mathbf{B}$ us $\mathbf{F}$ unctional $\mathbf{M}$ odel               |

|----------------|------------------------------------------------------------------------|

| $\mathbf{DUT}$ | <b>D</b> evice <b>U</b> under <b>T</b> est                             |

| HDL            | Hardware Description Language                                          |

| HVL            | ${\bf H} igh-level \ {\bf V} erification \ {\bf L} anguage$            |

| ISS            | Instruction Set Simulator                                              |

| NVM            | Non Volatile Memory                                                    |

| $\mathbf{RTL}$ | $ {\bf R} {\rm egister} \ {\bf T} {\rm ransfer} \ {\bf L} {\rm evel} $ |

| TLM            | $\mathbf{T} \text{ransaction-level } \mathbf{m} \text{odeling}$        |

| UVC            | Universal Verification Component                                       |

| UVM            | Universal Verification $\mathbf{M}$ ethodology                         |

## Chapter 1

# Introduction

### 1.1 Motivation

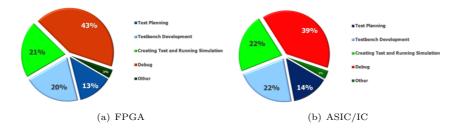

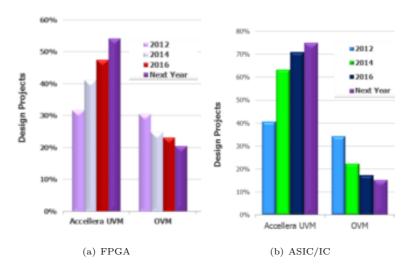

According to "The 2016 Wilson Research Group Functional Verification Study" [1] presents that the average time spent in verification in FPGA projects is 48%, and 55% in ASIC/IC projects. Figure 1.1 shows where the time is spent by Verification engineers during a project. For both projects for FPGAs and ASICs/ICs the time spent developing the testbench is around 20%, and the time used debugging can be over 40%. Maximal reuse needs to be utilised in order to reduce the development time for the testbench [5]. Reusing the same components can also reduce the time spent debugging. To reduce the time used running tests, iterations and debugging, a better, more advanced approach is needed. Figure 1.2 presents the different methodologies trends in verification used for FPGA and ASIC/IC. It shows that the adoption of UVM has drastically increased during the past years. UVM can help increase the maximum reuse.

As reuse in UVM comes more in focus, the components used in UVM should be improved. By developing a parameterised Universal Verification Component(UVC) could be a step in the right direction towards maximising reuse and decreasing the time spent developing the testbench, decreasing the total time spent in verification, and with it, increase the probability of delivering a project on deadline. The extra time granted could also be spent on quality improvement.

FIGURE 1.1: Where Verification Engineers spend their time[1]

FIGURE 1.2: FGPA Methodologies and Testbench Base-Class Libraries[1]

## 1.2 Contributions

Several techniques and methods were used in this project in the process of developing a UVC. The following has been achieved in this thesis:

- Modified an framework to develop a UVC.

- Developed an agent that only need configuration object and sequence item as parameters.

- Sequence item has been improved to function for several protocols.

- Driver, monitor and sequencer have been made generic by moving and encapsulating specialised functionality on the interfaces.

• Modified the configuration for the framework to be compatible with the UVC.

### 1.3 Methodology

In this project SystemVerilog and UVM version 1.1d have been used, with Cadence Incisive as the simulator. An existing framework for verifying a CPU has been used as a base in order to develop a unified agent for working with various busses, and the framework has been modified for it to work. During the project, the workflow has consisted of altering the framework while being true to UVM. When an alteration has been made, a script was used to execute a test for the framework. This script builds the framework, simulates and does a clean-up. It creates logs for the build and for the simulation, which was used to verify correct functionality, or debugging. SimVision has also been utilised when inspecting the waveforms for correct behaviour.

### 1.4 Thesis Overview

The successive chapters will go through how the process of the development of a Universal Verification Component, and re-working the framework to work with it. An overview over the chapters included in this thesis is given below:

Chapter 2 provides some background information about the UVM methodology. This includes information and terms that could come in handy throughout the thesis. First it will roughly go through a quick summary of UVM, its creation and the components that is used to build the testbench. It will then delve into how information is used and shared in the testbench. It will further explore how the different components can be configured, with the use of parameters and other methods.

Chapter 3 presents how the framework that is used as foundation in the development of the UVC is configured, and a little bit about the structure and components in it. This chapter also go in on how it could be possible to improve the existing framework. Chapter 4 covers how the process of developing the UVC is carried out. It starts with explaining the need for a different starting point, before it advances to the description of the work process. It then progress to describe how the functionality is moved about to create the UVC, and how the framework and configuration is adjusted to match the UVC.

Chapter 5 presents the benefits of code reduction, both in the amount of code lines and number of files, between the the a specialised framework and the framework that use the UVC.

Chapter 6 is the discussion. The discussion will be based on the entire thesis, and discuss the ways of the results found, advantages and disadvantages using the UVC, parameterisation and configuration used in the solution, some inconveniences that occurred during the project, and at last it will discuss some alternative methods that could be used to solve the problem.

## Chapter 2

# Background

The purpose of this chapter is to introduce important concepts and terms that are used in the modelling approach and discussions in this thesis. In the search for information about generic UVCs, it was revealed that there is very little, to no information regarding the development of a pure generic UVC.

## 2.1 Universal Verification Methodology

Universal Verification Methodology (UVM) is a methodology for functional verification of design units, created by Accellera. UVM is based on Open Verification Methodology (OVM) that is created by Cadence and Mentor, and VMM from Synopsis. The UVM standard is built on the principle of cooperation between EDA vendors and customers. The building blocks from the class library makes it possible to quickly develop well-constructed and reusable verification components and test environments[6]. The UVM package contains a class library that consists of three main types of classes[3]:

- *uvm\_components*, used to construct a class based hierarchical testbench structure

- *uvm\_objects*, used as data structures for configuration of the testbench

- uvm\_transactions, used in stimulus generation and analysis

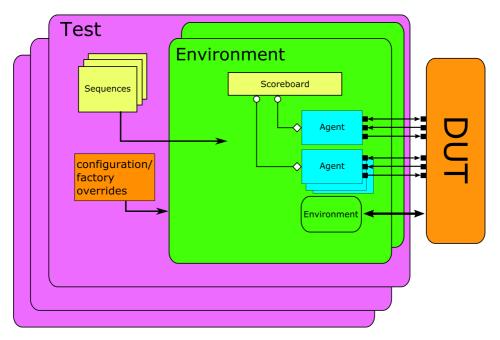

UVM uses a hierarchy built on classes in its testbenches. These classes are derived from the *uvm\_component* base class. The hierarchy is based on a class relationship, Figure 2.1 shows the hierarchical layers that are commonly used in UVM. The top level class in a UVM testbench, often called "test", is responsible for configuring the testbench, initiating the construction process by building the next level down in the hierarchy, and by initiating the stimulus by staring the main sequence. The environment and the agent are components used in order to enable reuse.

The Design/device Under Test (DUT) is the code/device that is to be verified by the testbench. It is often connected to the testbench through interfaces. It receives stimulus from the testbench, and returns the output of that stimulus.

FIGURE 2.1: Block Level UVM Test Bench - Hierarchical Layers

#### 2.1.1 Horizontal and Vertical Reuse

In order to save time and resources, and increase productivity, UVM promotes reuse. Reuse in UVM can be divided into two sections, horizontal and vertical, which describes the context of what verification artefacts are reused. Horizontal verification means that a component can be used in another system or project, "block to design", but still at approximately the same level of abstraction [7]. Vertical reuse is used when a component is used in another hierarchical abstraction level, "block to subsystem to full chip". Vertical reuse is often used when reusing sequences, and testbenches in the same system. It is often achieved by encapsulation and extensibility. Utilising vertical reuse may increase verification efficiency by writing less code, which also gives less code to maintain, and less time on initial debug. It also gives parallel development of testbenches and a architecture that can be integrated with little effort into other modules and subsystems.

#### 2.1.2 Test

The IEEE Standards Dictionary: Glossary of Terms & Definitions[8] defines test as: specific customisation of an environment to exercise required functionality of the DUT.

The test is in the top of the hierarchy. Tests are derived from the *uvm\_test* class. Typically the UVM test performs three main functions[9]:

- Initiate the top-level environment

- Configure the environment

- With factory overrides or the configuration database

- Apply stimulus by invoking UVM sequences through the environment to the DUT

#### 2.1.3 Environment

IEEE[8]: The container object that defines the testbench topology.

The UVM environment groups together verification components that are interrelated. The top-level environment usually contain all the components that are targeting the DUT. Components that are encapsulated by the environment are usually the agent, scoreboards and even other environments[9].

#### 2.1.4 Scoreboard

IEEE[8]: The mechanism used to dynamically predict the response of the design and check the observed response against the predicted response. Usually refers to the entire dynamic response-checking structure.

The scoreboards main function is to check the correctness of the DUT by comparing the DUTs output with the expected values[9]. The scoreboard can be generalised into two parts: predict, which determines the correct functionality of the DUT, and evaluate which checks if the observed results of the DUT matches the predicted results. Separating the prediction task from the evaluation task gives the best scoreboard architecture [3]. This is because it gives the most flexibility for reuse by allowing for substitution of predictor and evaluation models.

#### 2.1.5 Agent

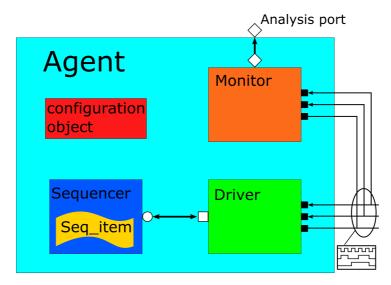

The IEEE Standards Dictionary: Glossary of Terms & Definitions[8] defines an agent as an abstract container used to emulate and verify DUT devices; agents encapsulate a driver, sequencer, and monitor.

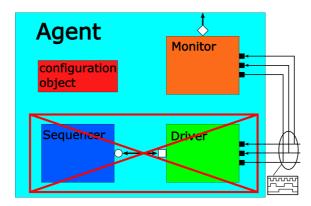

FIGURE 2.2: Active agent

In addition to a driver, sequencer and monitor there might also components related to coverage monitors or scoreboards. As seen in Figure 2.2 There is an analysis port connected to the agents monitor. This makes it possible for any external analysis component to connect without interfering with the agent. The agent can also contain a configuration object, that can hold information like:

- Sub-components created under the agent

- Handle to the virtual interfaces

- Functional behaviour of the agent

The agent can be configured active or passive, more on how configuration is done is given in Chapter 2.1.19. An active agent generate the stimulus and drive the DUT, the driver, sequencer and monitor is therefore present. A passive agent, see Figure 2.3, does not drive the DUT signals, it only samples them, and thus, it does not contain a driver or a sequencer.

FIGURE 2.3: Passive agent

#### 2.1.6 Driver

IEEE[8]: A component responsible for executing or otherwise processing transactions, usually interacting with the DUT to do so.

The driver receives individual sequence item transactions from the sequencer via a TLM port, and applies it to the DUT interface[9]. The driver therefore spans the abstraction levels by converting the transaction-level stimulus to pin-level stimulus.

#### 2.1.7 Monitor

IEEE[8]: A passive entity that samples DUT signals, but does not drive them.

The monitor samples the DUT interface, capturing information about the transactions. The information can be sent to the rest of the testbench for further analysis[9]. The monitor spans the same level of abstraction as the driver, by converting pin-level activity to transactions. The monitor typically uses a TLM analysis port to broadcast the transactions created. Processing on transactions, like coverage collection, checking, recording etc, can be done by the monitor or delegated to other components via the analysis port.

#### 2.1.8 Sequencer

IEEE[8]: An advanced stimulus generator which executes sequences that define the transactions provided to the driver for execution.

A sequencer serves as a router of transactions. The sequencer component feeds the driver with transactions with stimulus in the form of sequences and sequence items from a parent sequence[3].

#### 2.1.9 Sequence Item

A sequence item is a class-based transaction representing stimulus passed from a sequence to a driver[3]. A sequence item is also known as a transaction. A transaction is a class object that represents a communication abstraction. It is a collection of information needed to model a unit with communication between two components. The information may include variables, constraints, and other fields and methods needed to generate and operate the transactions[9]. In order to model the communication to the level of abstraction wanted, transactions can be composed, decomposed, extended, layered and manipulated.

#### 2.1.10 Interfaces

Interfaces are used to encapsulate communication, which facilitates reuse, between design blocks, and verification blocks, enabling a transition from the abstract level

used in the testbench to lower RTL(Register-transfer level) and structural levels of the design [10]. At low level an interface is an named bundle of nets and variables, and can be accessed through a port. At higher levels the interface can encapsulate functionality as well as connectivity. An advantage using interfaces is its flexibility, as it can be parameterised the same way as a module, and can contain parameters, constants, variables, functions and tasks, and continuous assignments[10]. Modports is commonly used in interfaces. The modport controls the use of tasks and functions, and provides information about the direction for the module interface for certain modules. Implementing tasks in the interface allows for a more abstract level of modelling, as the master module can call the tasks with no need for references to the wires.

#### 2.1.11 Transaction Level Modeling

Transaction level modeling(TLM) is a modelling style for building highly abstract models of components and systems[9]. An advantage of this abstraction is that simulation speed can increase, observing the traffic easier and debugging is easier with TLM than RTL[11]. TLM communication creates the possibility to communicate between components utilising functions. Where tasks and functions in one component are available in another component. UVM provides a set of interfaces and channels for use with transaction-level communication. The use of TLM interfaces promotes reuse, as it isolates the components from the interface. This means that the component can be swapped for another, given they have the same interface.

```

seq_item_port.get_next_item(req);

... //drive the response onto the interface

seq_item_port.item_done();

```

The code snippet above shows how the driver can get a transaction from the sequencer during the run-phase. The *get\_next\_item* is a blocking function, and it will block until there is an item that is available from the sequencer[12]. Opposed to using the *get*-function, once *get\_next\_item* has been called, the *item\_done* function has to be called in order to indicate that the request is complete to the sequencer.

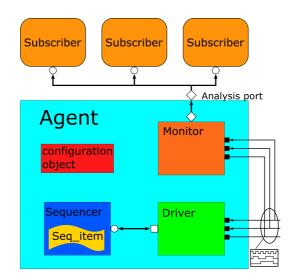

FIGURE 2.4: Agent with analysis port and subscribers

The analysis port can be used as a broadcast port[3]. The analysis port does not care if it is not connected, or connected to one or more ports. Figure 2.4 shows how the analysis port connects from the monitor, to the agents analysis port, before it is connected to several subscribers analysis export. The subscriber component is usually programmed to subscribe from analysis ports, it could for example be a checking or coverage collector. In the figure the monitor can use the push transaction function port.write(tx) in order to write to the analysis port, the subscriber should then have a write-function that is read-only. The analysis port is not supported with the factory, and needs to be created using the raw constructor "analysis\_port = new("analysis\_port", this);"

#### 2.1.12 Transaction Methods

It is common to perform operations on transactions, like copying the transaction, printing or comparing. UVM provides a standard set of methods to do this. The user transaction class is extended from the **uvm\_sequence\_item** class, which comes from the **uvm\_object** class type, and thus inherits utility methods: *copy, compare, print, pack, unpack, record* and more[13]. These methods are non-virtual and should not be overridden. If there are custom transactions that needs to be implemented, the user should override the do\_\* methods, which are called by these utility methods.

$Do\_print$  is called by *print* and *sprint*, and allows the user to decide what is printed. To ensure correct output format of the *print* and *sprint* operation, the printer should be used by all the *do\_print* implementations. Which means that instead of using *\$display*, the *do\_print* should be called through the printer's API[14].

The  $do_copy$  is called by the copy method. It is an empty method, and should therefore be user-defined if the field-macros are not used. The  $do_copy$  method should make a deep copy of a data object[3]. A deep copy is when the value of the individual properties in a data object are copied to another, in contrast to a shallow copy where the pointer is copied. The implementation of the  $do_copy$ should call *super.do\_copy*, and *\$cast* the **rhs** argument to the derived type before the copy[14].

To support the viewing of data objects as transactions in a waveform the  $do\_record$  can be used. As the other  $do\_methods$  it is called by the *record* function. This method is also empty, and the implementation should call the appropriate recorder methods.

There are however other methods than the  $do\_methods$  that is important. The create method, which should be used if the 'uvm\_object\_utils macro is not utilised, the clone method, which calls the create method before calling the copy method, and the convert2string method[14]. The convert2string method is a virtual function and works as a user-definable hook that allows users to provide object information as a string. The default convert2string method could be seen as a placeholder that returns an empty string [13]. It is recommended to override the convert2string method in every transaction class with a proper formatted string of the transaction variables. When extending a transaction class from a base transaction class it is suggested to extend the convert2string method calling super.convert2string, and not reformat all the transaction variables.

#### 2.1.13 Polymorphism

Polymorphism is one of the key-concepts in object-oriented programming, and it allows for the substitution of objects that have identical interfaces for each other at run-time[2]. The use of a variable of a superclass type, is with polymorphism, allowed to hold subclass objects and to directly reference the methods of those subclasses[10]. Polymorphism can be particulated in two: dynamic and static. Static polymorphism is also known as method overloading, as it use a method many times, but with different parameters, and decided at compile-time. Dynamic polymorphism happens at run-time and is also known as method overriding. It is where a method is overridden with the same signature in different classes.

#### 2.1.14 Factory

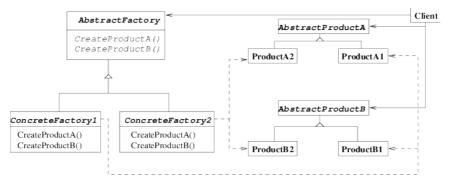

An object for creating other objects in object oriented programming is called a "factory". It is in other words a function or method that returns objects of a varying prototype or class from a method call[2]. When it comes to class-based programming, the factory works like an abstraction of the constructor class. It is possible to define an abstract factory class to declare an interface for how objects are created throughout an application. Figure 2.5 presents how an abstract factory can be utilised. The client uses the interfaces of the abstract product and abstract factory to create a product with the right specifications. The concrete factory implements the operations to create the objects, and the abstract product creates an interface for a type of product object.

FIGURE 2.5: Abstract Factory pattern[2]

To allow components to manufacture objects without needing to specify the exact class, UVM provides a factory. This means that it is possible to allow for an object to be substituted with an another, without having to edit the structure of the testbench, or the testbench code. The factory takes advantage of Object oriented programmings(OOP) polymorphism, see Chapter 2.1.13. The mechanism used by the factory is called an override, and it can be by instance or type [9]. The factory

can be seen as a special look-up table that create requested components or transaction types. The factory should be used instead of the new() class constructor[15]. The new() constructor will only create a transaction or component of the specified type. It fixes the type during construction, meaning no run-time changes are possible. It is therefore not possible to employ dynamic polymorphism. If there are changes to the components there will be need for change in the source code.

Using the factory to create the constructor grants several advantages, as it enables the choice of object type to be overridden from the test[16]. When using the factory, the components should be registered using the macros 'uvm\_component\_utils or 'uvm\_object\_utils. The ::type\_id::create() command creates an object of type\_id stored in the factory, and is needed in order to use overrides. By using the override command, tests can make type\_id substitutions. During the build phase the components are creating a tree-like hierarchy when creating the testbench structure. This process happens top to bottom, where every component names and builds its children, and passes a pointer, using .this pointer, from itself to the child[15]. If the components and transaction types do not match the structure of the testbench during the build-phase, the top-level test can change its type, and then the factory uses overrides on the rest of the testbench.

#### 2.1.15 Generic Programming

The Merriam-Webster's dictionary[17] defines "generic" as "relating to or characteristic of a whole group or class". It can also be characterised as "not specific". When it comes to generic programming, the intent is to facilitate reuse, by writing code once and invoking or instantiating it several times with generic parameters[18]. The ability to write code for an algorithm that is independent of parameters that will be specified later, can be considered the concept of generic programming. SystemVerilog, as opposed to Verilog which only allows parameterisation of certain values, adds the possibility of full parameterisation of all data types[10]. The parameterised data types are implemented through the use of type definitions in parametesised classes. To avoid writing similar code for different size and data types, it is useful to define a generic class.

#### 2.1.16 Parameterisation

Parameters increase the flexibility, but it also increases the complexity of the code[19]. In SystemVerilog it is possible to make classes with their own set of parameters that may be overridden when declaring a class variable, these classes may be called generic classes. These classes are not true data types before the parameters have been declared. When the parameters has been declared the classes can be called for a specialised class [10]. A parameterised class can be declared as following:

```

class example #(int size = 8);

bit [size-1:0];

endclass

```

Here the size integer is default 8, but can be given another value when creating the class. If there is no default value given, it has to be set before the class can be used. A parameterized class can also be extended by another parameterised class. Underneath is a few examples of the headers of extending parameterised classes.

```

class C #(type T = bit); ... endclass // base class

class D1 #(type P = real) extends C; // T is bit (the default)

class D2 #(type P = real) extends C #(integer); // T is integer

class D3 #(type P = real) extends C #(P); // T is P

class D4 #(type P = C#(real)) extends P; // for default T is real

```

Here class **D1** extends class **C**, and uses the default type from the inherited class. Class **D2** extends class **C**, but the default type in class **C** is integer instead. **P** is a parameterised class, and by extending **C** which is using **P**, the extended class, **D3**, will also be parameterised. Class **D4** uses the type parameter **P** as a base class, and the name must therefore resolve to a class type after elaboration[10].

It is possible to group the parameterisation classes into two hierarchies: containment hierarchy and inheritance hierarchy [18]. The containment hierarchy works as a "has-a" relationship of object oriented programming (OOP), where a class definition can instantiate other class variables. It is then possible for the class definition to use its parameters to parameterise the contained class members variables. This is typically done in verification environments, as they group the class components. For example the uvm test, agent, driver and monitor are each extended from **uvm\_component**. The driver and monitor are included in agent, and there can be several instantiations of agents in the test class. Given there are unique class definitions used for instantiating the classes it is therefore possible to get several specialisations of agents, drivers and monitors when declaring the test.

#### 2.1.17 Inheritance

The inheritance hierarchy is the "is-a" relationship of OOP. This is where the properties and methods of a extended class is inherited directly from the base class, and makes it possible to reference them from the extended class[18]. Parameters may then be propagated from the extended class up to the base class. For each instance of an extended class that is instantiated, the base class will also be instantiated.

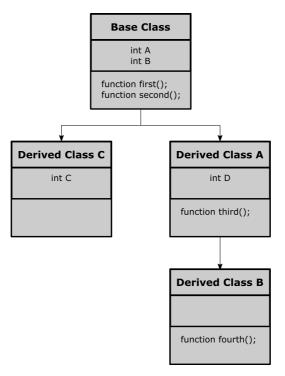

FIGURE 2.6: Inheritance

Figure 2.6 shows how a classes can be derived from a base class. The three classes are A, B and C are all extended from the base class. Table 2.1 presents the variables and functions each of the classes will have. As class C is directly inherited from the base class, it will not have any of the variables or functions that is added in class A or B. Class B is the only class with the function fourth(), which means that the other classes can not use the function.

| Class     | Variables | Functions                    |

|-----------|-----------|------------------------------|

| Base      | int A, B  | first, second                |

| Derived A | A, B, D   | first, second, third         |

| Derived B | A, B, D   | first, second, third, fourth |

| Derived C | A, B, C   | first, second                |

TABLE 2.1: Overview over inherited variables and functions

In order to create static class property for a generic class, it has to become a concrete specialisation[18]. A specialised class can be created with the use of *typedef*. The use of parameterised classes can be good for horizontal reuse, as it makes it easier to use in different projects. It could also be a good fit for the base classes in UVM. In order to register parameterised classes with the factory, the 'uvm\_component\_param\_utils and 'uvm\_object\_param\_utils macros must be used[9].

#### 2.1.18 Configuration Objects

Configuration objects are used to keep a high reusability and easily configurable testbench. A configuration object is a class that contains items necessary to configure a single target [20]. The configuration object can hold information about how the component that contains the object shall create sub-components, pass handles, and the behaviour for the component. Randomisation can be a useful feature when using configuration objects, and can be done by running the *.randomize()* function. It is also possible to set constraints to variables if it is wanted to restrict the variable. Extending the base class object, and setting new constraints can help create a new tests, without having to rewrite code, helping with the reusability. In addition is it possible for several components to have the same reference to a configuration object by passing around the handle to the object[21]. All the changes done to the object's contents will be visible to all the components with its reference. Utilising configuration objects also reduces the risk of applying

the configuration to the wrong target, as classes are strongly typed. It is also possible to see if a configuration has been provided by looking at the object handle value, if it is of null unambiguously, it is not provided.

#### 2.1.19 Configuration

In order to create a verification framework that can be easily reused, a key concept is that it should be as configurable as possible, without having having to rewrite every part of the testbench. Delivering information to various parts of the testbench from a central location, and with variables and parameters, reduces code rewriting. Variables are set at runtime, and can be organised into "configuration objects", and accessed through a resource/config database[3]. Resource databases are an in-memory database that contains objects of different types[20]. The parameters must be set during compilation, as these can not be changed during runtime. In order to be reusable, testbench elements, like components, sequences, sequence items etc., needs knowledge about its environment, and how it should operate in it. This information can be classified as configuration information. Having knowledge of the configuration information, the testbench elements can alter its topology or behaviour accordingly [22]. The most common way configuration information is passed to the elements are:

- class parameters

- constructor arguments

- function calls

For more on class parameters see Chapter 2.1.16. In UVM there are two types of databases that are closely related, the configuration database, *uvm\_config\_db*, and the resource database, *uvm\_resource\_db*. The configuration database and the resource database are closely connected, as *uvm\_config\_db* is an extension of *uvm\_resource\_db*. The *uvm\_resource\_db* works as a look-up table, and the hierarchy is not important[23]. The *uvm\_config\_db* is a type-specific configuration mechanism that offers a facility for specifying hierarchical configuration values of desired parameters[9]. The *uvm\_config\_db* is often used when sharing virtual interfaces. In order for the testbench to monitor or drive the DUT, it needs access to the interfaces. The instantiation of the interfaces happens at the top of the framework, where it checks for them, and then sets an handle to the virtual interfaces using the configuration database. The class header for the resource database and the configuration database is given below

```

class uvm_resource_db#(type T=uvm_object)

class uvm_config_db#(type T=int) extends uvm_resource_db#(T)

```

As seen, the resource database class uses a parameterisation where the default type **T** is an **uvm\_object**, while the configuration database standard is an **int**. It is possible to set or get configuration information by using *set-* or *get-* functions of the uvm\_config\_db or uvm\_resource\_db classes[23]. These functions are static and must therefore be called using the "::" operator. The syntax for the *set-* and *get-* function for **uvm\_config\_db** is:

```

uvm_config_db#(<type>)::set(uvm_component cntxt, string inst_name,

string field_name, <type> value)

uvm_config_db#(<type>)::get(uvm_component cntxt, string inst_name,

string field_name, ref value)

```

Where **cntxt** is the hierarchical starting point of where the database entry is accessible, the object hierarchy whereas. **inst\_name** is the path that limits the accessibility of the database entry. **field\_name** is the name of the object, the lookup label. Objects using set() or get() must use the same label, or else the receiving part will fail to find the object in the database[24]. **value** is the object handle shared in the database, the value that is to be stored in the database, it is of a parameterised type **type**, which is set to **int** by default.

The *set*-function uses **cntxt** and **inst\_name** in order to specify the "address" where the object handle is stored to control the recipient of the object [24]. The *get*-function can select from where it wants to retrieve information, it can for example be from elsewhere in the hierarchy. It is common to use **this** pointer in **cntxt** in order to specify the current scope for both the *set*- and *get*-function. For **inst\_name**, the *get*-function often use an empty (""), since it usually gets

objects destined for itself. The *set* function uses it to address the object to the appropriate sub-block.

With the use of cntxt, inst\_name and field\_name it is possible to make a number of different paths to the same object. When referencing down the hierarchy it is common to use the **this** pointer. When referencing upwards, the **null** pointer or the *uvm\_root::get()* function can utilised to access the hierarchy root, and then the path down the hierarchy is given by by **inst\_name**. The database combines the **cntxt**, **inst\_name** and **field\_name** parameters to make a key used for searching through the database. There are three metacharacters, "\*, + ,?", that can be used when creating the path. "\*" means 0 or more characters, "+" means 1 or more, and "?" means exactly 1 character. "\*" is usually called a wildcard

In addition to depositing resource items destined for a particular UVM object or component instance into a database before the instance has been constructed, the lookup mechanism supports keys containing wildcard and regular expression patterns[21]. This mechanism can match only a part of a object's full instance name, which supports two use cases:

- Single resource targets multiple objects, which all receives the same resource

- A resource can target an object without knowledge about the full pathname or if the object has been created.

- Helps with vertical reuse since it can appear in different levels of the hierarchy.

- Allows configuration objects to be constructed by a top level module and give information to components before they are constructed.

Every time the *uvm\_config\_db*'s *set-* or *get-* method is used, there is an entire scan of the configuration database in order to match strings. Minimising the usage of accesses to the configuration database, avoid wildcard matching, and avoid the *wait\_modified()* method is recommended, since it will take longer to find a match if the database is large and the search is little specific[4]. The *wait\_modified()* function is blocking, and is only triggered if the set function is called using the same exact cntxt, inst\_name and field\_name [20].

## 2.2 Comprehensive UVM

There are several ways to utilise UVM and its components. A UVC could ease the implementation of future frameworks, as it contain components needed in the framework. When implementing a UVC synchronisation must also be considered. It also is possible to create UVCs that are designed for multi-purposes and are acceleration ready, generic and configurable[25].

#### 2.2.1 Universal Verification Component

A UVC is a verification component for use in UVM. It is a multi-faceted definition and has different meanings in different contexts. The topologies that can be defined to be a UVC can be boiled down to[3]:

- Protocol UVC

- Each verification component connects to a DUT interface and communicates with a single protocol

- Fabric/compound UVC

- A verification component that contains a configurable number of instances of the protocol UVC configured and hooked up coherently as a unit. Purpose to verify a structured fabric with multiple interfaces of the same protocol

- Layered UVC

- Provides a higher level of abstraction than basic pin protocol, with two common ways of construction

- \* A UVC which does not connect to pins, but provides an upper layer of abstraction to an existing protocol UVC

- \* A UVC which wraps and extends a lower-level protocol UVC

A UVC should make use of the factory registration API and macros provided with UVM so that its components can participate in factory creation[3]. This way the user decide on what portions should be factory substituted. Simple protocol UVCs are normally not environments, but agents that are instantiated individually for each interface. A protocol UVC should also normally not contain scoreboards.

#### 2.2.2 Dual Top for Accelerated Verification

As design size and complexity of automated testbenches keeps on growing, the need of hardware assisted acceleration has increased as well. To achieve this a methodology based on co-emulation is recommended, which also promotes reuse[26]. Coemulation modelling describes the process of modelling and simulating a mixture of software models represented with an un-timed level of abstraction, simultaneously executing and inter-communicating through an abstraction bridge, with hardware models represented with the RTL level of abstraction, and running on an emulator or a simulator[27]. It is in other words a RTL DUT running in a hardware emulator that can interact with a testbench running on a workstation. The testbench can still be used in simulation after it has been created to be emulation ready. There is a desire for a high reusability in testbenches that can be used in emulation, and are therefore often designed thereafter.

Typically the DUT-testbench setup use a single SystemVerilog module as top level. The top level module contains the DUT and the interfaces associated to it, protocol modules, connection and support logic[3]. Figure 2.7 shows the typical encapsulation of a DUT-TB setup, it is typically a container for both the testbench and the DUT. It also contains the the connections and support logic, like the clock generation.

FIGURE 2.7: Single top[3]

To create a working co-emulation ready testbench, there are some requirements that needs to be fulfilled[26]. It needs to follow the principles of co-emulation. It is recommended to split the testbench into two top modules as seen in Figure 2.8. One that module to wrap the DUT, interface, protocol modules, clock generation logic, DUT wires, registers etc. The other module is the module that creates the testbench. The two top modules are in their own domains: the timed/synthesisable HDL(Hardware Description Language) side where the DUT, BFM(Bus Functional Mmodel), and clock/reset generation is, and the untimed HVL(Highlevel Verification Language)/TB side, where the testbench generation and analysis code is. When two top modules is used, it is called "dual top". The HDL domain needs to be synthesisable and contain all clock synchronous code that is to be used in the DUT, the clock and reset generators, and bus cycle state machines for driving and sampling the DUT interface signals. The HVL domain, contradictory to the HDL domain, needs to be strictly un-timed. This means that there should not be any use of time explicit advances[26]. These advances are for example clock synchronisations, # delays, wait or other time statements, as these should only be used in the HDL domain.

FIGURE 2.8: Dual Top[3]

When using accelerated transactors it is possible to shift the testbench load to the emulator. A transactor can be referred to as a Bus Functional Model(BFM). A transactor decomposes an un-timed transaction to a series of cycle-accurate clocked events, or, conversely, composes a series of clocked events into a single message[27]. In the hardware-assisted verification specific context, a transactor is a SystemVerilog interface or module on the HDL side[26]. The module in Figure 2.9 has a signal-level interface with the DUT and a transaction-level interface with the HVL side. With a partitioning the domain, performance can be maximised because the testbench and communication overhead is reduced, and intensive pin wiggling can be done in the dedicated timed domain, running at emulation speed[4].

FIGURE 2.9: UVM layered testbench[4]

#### 2.2.3 Synchronisation

A race condition is a flaw in a system or process that is characterised by an output that exhibits an unexpected dependence on the relative timing or ordering of events[28]. It is possible to split race conditions into two different types: hardware races and simulation induced races. The physical nature of combinational logic is typically the reason for hardware races. An example of a hardware race is when the inputs to a logic gate changes, this causes a finite delay before the output has changed.

Simulation induced races are undesirable consequences of the event-driven simulation algorithm used[28]. It is not intrinsic to the design or its physics, and it is an desire to avoid them. The simulator process event one at a time and unavoidably serialise the events that occur in the same time slot. The concurrent hardware activity is therefore modelled as a set of ordered actions by the simulator. These races can cause the simulator to cause a faulty design or to simulate a correct design, which is actually incorrect.

It is important that the testbench avoids race conditions with the DUT. In UVM it is therefore expected that the driver synchronises with a clock signal that is available in the interface to to maintain correct transfer of values from the driver to the interface variables[29]. This synchronisation grants important advantages, like simplified driver code and ease of extending the driver without having to worry about duplicate synchronisation timing. The use of a clocking block in the interface will help with race conditions, but may be incompatible with emulation.

Modports connections and interfaces, mentioned in Chapter 2.1.10, can specify signals and nets, and communicate with the DUT. However, they do not denote any explicit timing disciplines, synchronisation requirements, or clocking paradigms. Clocking blocks can identify and capture the timing and synchronisation requirements of the blocks being modelled. The clocking block assembles signals that are synchronous to a particular clock and makes their timing explicit[10]. It also enables the user to write at a higher level of abstraction, as tests can be written with the use of cycles and transactions, instead of signals and transitions in time. Using clocking block constructs will facilitate the specification of assertion, cycle operations, and synchronous interfaces[29]. It also grants race free communication between the interface and DUT, as it enforces a time when signals are sampled.

To give a powerful and efficient means of describing the communication between, and synchronisation of concurrently active processes it is possible to use **event** objects[10]. The **event** data type provide a handle to a synchronisation object, which can be explicitly triggered and waited for. An identifier declared as an **event** data type is called a "named event". The "->" operator will unblock all processes waiting on the triggered named event. It is only the effect of a named event that is observable, when the it is triggered, and not the trigger itself.

# Chapter 3

# Verification Infrastructure

There exist an incomplete UVM framework for verification of a CPU. This framework has been created in accordance with earlier UVM methodology, and will be used as a foundation in the development of a Universal Verification Component. In this chapter there will be an introduction to how the framework is set up, by presenting how the configuration is done, and clarify the structure and components in the hierarchy. This chapter will also elaborate on how an improvement to the framework can be done.

# 3.1 Existing CPU UVM Framework

The existing framework is created for the verification of a CPU, and contain several protocols for interacting with it. The framework is developed in accordance with earlier UVM methodologies, with some with some unusual features. What is unusual in this framework compared to others, is that it can use two CPUs, one with and one without cache, in the verification process. It is therefore possible for the sequencer to feed the two CPUs and ISS (Instruction Set Simulator) with random instructions, which is stored in a non-volatile memory(NVM), and be compared with each other.

#### 3.1.1 Protocols

There are several protocols for communication between the testbench and the DUT. The CPU UVM framework contain eight protocols. These protocols include an implementation for an agent, driver, monitor, configuration, interface, sequence-item, sequencer, and sequences for that protocol. The components are supposed to be implemented such that they can be used to verify the CPU with and without cache on the CPU. Some of the protocols' drivers accesses the NVM to retrieve data or instructions, if there is nothing in the memory, the driver will request a transaction from the sequencer. There are also protocols for other functionality, like on chip debug, interrupt requests and to halt the CPU externally.

#### 3.1.2 Top Level

The framework's build process is ordinary according to UVM, where it is the test that initialises and starts the simulation of the testbench. Looking at the folder structure, the existing framework includes:

- Test base

- Extended test for active agents

- The environment

- An environment configuration object

- Scoreboards

- Agents for the protocols

- A virtual sequencer

- A set of virtual sequences

- Instruction set Simulator (ISS)

Where the test base is extended from the uvm\_test class in UVM, and is used as the base to build the tests that verify the CPU. During the build phase in the test base, the environment is created and there is a check whether the interfaces for the protocols are present in the environment configuration, then there are put handles to the virtual interfaces, before they are set the configuration database. The test base then gets ready to run and report test content that is specified by extended tests. The extended test for active agents utilise the configuration database to retrieve the environment configuration, and set the **is\_active** convenience value to "UVM\_ACTIVE" for the protocols configuration objects.

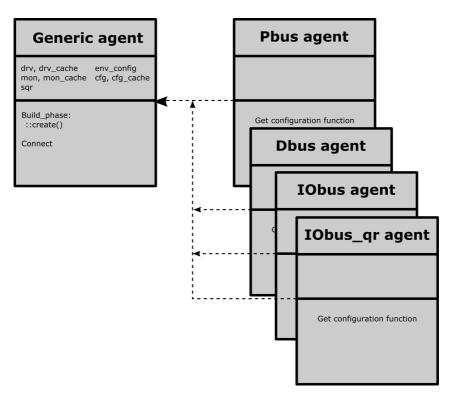

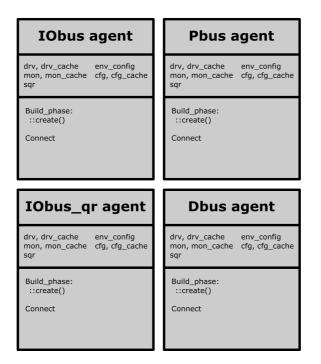

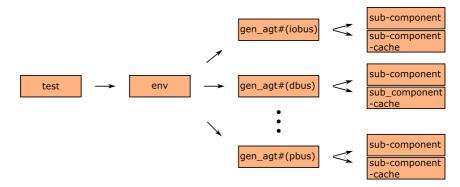

#### 3.1.3 Environment

The environment creates a virtual sequencer and the agents for the protocols in the build phase. It also checks the configuration database if it should create the scoreboards. It creates all the components using the factory method described in Chapter 2.1.14. The environment proceeds to connect the virtual sequencer to the sequencers the agents created, and connect the analysis ports from the Pbus, Dbus, Irq, Iobus, Iobus\_qr- monitors to the ISS through the scoreboard if the scoreboard enabled.

The code below shows how the agents, virtual sequencer and scoreboards are declared in the environment in the testbench, as well as how the agents are instantiated. None of the components need to specify any parameters in order to be used. There is also used a naming convention for the declaration of the different components.

```

class uenv extends uvm_env;

. . .

iobus_agt

m_iobus_agt;

iobus_qr_agt

m_iobus_qr_agt;

pbus_agt

m_pbus_agt;

dbus_agt

m_dbus_agt;

ocd_agt

m_ocd_agt;

irq_agt

m_irq_agt;

cpu_externals_agt m_cpu_externals_agt;

uvsequencer

m_vsequencer;

cpu_snapshot_agt m_cpu_snapshot_agt;

m_cpu_sbrd;

cpu_scoreboard

cpu_cpu_cache_scoreboard m_cpu_cpu_cache_sbrd;

. . .

= pbus_agt ::type_id::create("m_pbus_agt"

m_pbus_agt

, this);

m_dbus_agt

= dbus_agt ::type_id::create("m_dbus_agt"

, this);

```

### 3.1.4 Configuration

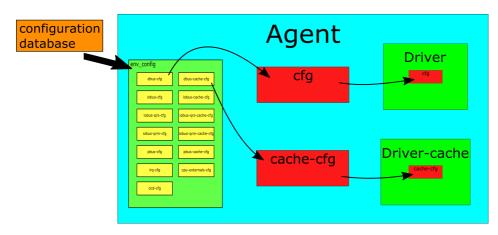

The framework configuration introduces an extra hierarchy for the verification components' configuration objects. Figure 3.1 shows how the different configuration objects are encapsulated by the environment's configuration object. The environment's configuration object also contain a bit to disable the ISS for debugging purposes, the first address for the program to jump and the first address for the interrupt service routine, and  $do_print$  function that prints the configuration of the objects.

FIGURE 3.1: Environment's configuration object

In order to get or set values in the verification component's configuration object, this framework use the configuration database to retrieve the environment configuration before it access the verification components configuration objects' value hierarchically. An example of this can be seen under, where the Iobus' agent is set active.

```

if (!uvm_config_db#(uenv_config)::get(this, "*", "env_config", env_config))

`uvm_fatal(get_name(), "Can't get env_config from uvm_config_db");

env_config.iobus_cfg.is_active=UVM_ACTIVE;

uvm_config_db#(uenv_config)::set(this, "*", "env_config", env_config);

```

As there are a lot of similarities in the different protocols, there is a template base class for the configuration that the configuration objects of the different protocols can inherit from. This template contain different variables and functions, like *convert2string* and *do\_print*, that should be common, and that can makes it possible to build the verification component as intended. The configuration template specifies that every inherited class should implement a task that generates a wait for the slave and bus signals. It is also added an handle to the interface, which is specialised when the class is extended. It is the Pbus, Dbus, Iobus and Iobus\_qr's configuration class that extends from the template, while the other protocols' configuration objects had not been ported to use the configuration object template at the time, containing some of the same variables and functions. The variables available in **config\_template** used for configuration of the testbench are:

- is\_active

- coverage

- agent\_verbosity

- lock\_sequencer

- Set to prevent interruption from other sequences

- allow\_data\_generation

- Allows generation of data in the driver

- allow\_inst\_generation

- Allows generation of instructions in the driver

- allow\_generate\_swait\_bwait

- Slave and master wait

Figure 3.2 illustrates how the configuration information that is set in the environment's object from the configuration database, is passed to the sub-components' configuration object. The environment's configuration object is included in every agent, and the protocol specific configuration copied to the sub-components.

FIGURE 3.2: Configuration passing

#### 3.1.5 Virtual Sequencer and Sequencers

Combining sequences can be used in order to create a hierarchy of stimuli, or to generate stimuli in parallel to multiple interfaces [30]. A sequence that controls stimulus generation using several sequences is a virtual sequence [3]. The virtual sequences in the framework controls and times the sequences run on a single bus interface. This approach allows users of the framework to easily create various verification programs. The virtual sequencer holds handles to all the sequencers in the framework, as shown in the code below. In the virtual sequences the declared sequencer is the virtual sequencer, which can access to all the sequences.

```

class uvsequencer extends uvm_sequencer;

`uvm_component_utils(uvsequencer)`

iobus_sqr

m_iobus_sqr;

iobus_qr_sqr

m_iobus_qr_sqr;

m_pbus_sqr;

pbus_sqr

dbus_sqr

m_dbus_sqr;

m_ocd_sqr;

ocd_sqr

irq_sqr

m_irq_sqr;

cpu_externals_sqr m_cpu_externals_sqr;

. . .

```

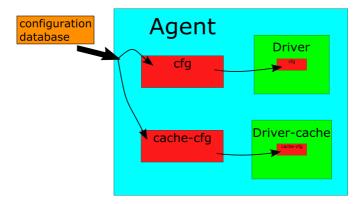

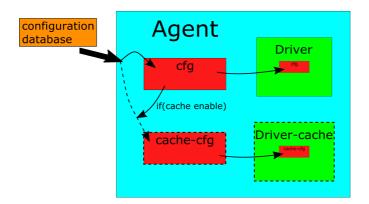

#### 3.1.6 Agents

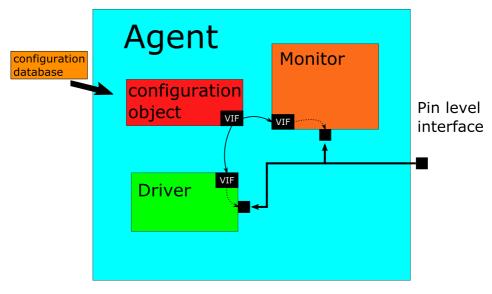

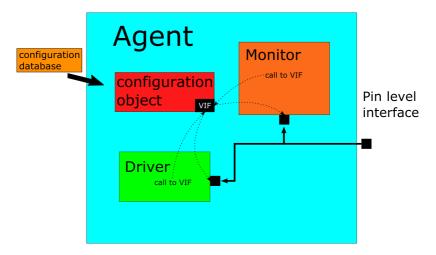

The agents' structure is similar to a normal agent, as described in Chapter 2.1.5, with the creation of a monitor, driver and sequencer. However, there are agents that create an additional driver depending on whether the cache-configuration declares it as an active agent. The handle to the interface is passed to the monitor and driver from the configuration object, as presented in Figure 3.3. The interface is set with the configuration database in the test base.

FIGURE 3.3: Virtual interface passing

#### 3.1.7 Drivers

The drivers in the framework are constructed as standard drivers, as described in Chapter 2.1.6. Nevertheless, there are some differences in the driver between the different protocols. The drivers for the different protocols varies, as the busses are required to drive the busses according to their specifications, and the protocols' natural differences. Many of the drivers hold variables and constraints that are specific for the protocol, for driving the DUT correctly.

#### 3.1.8 Monitors

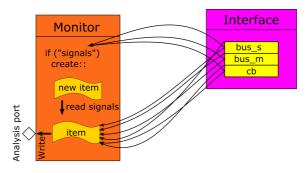

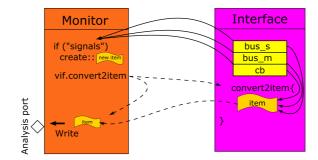

As with the drivers, the monitors are also in accordance with the UVM methodology. Even though there are differences between the monitors of the different protocols, there is a pattern that occurs. Many of the monitors use hierarchical access through the virtual interface to access and check the signals from the DUT. The code snippet underneath is taken from the run-phase in the Dbus-monitor, and Figure 3.4 helps illustrate it.

```

class dbus_mon extends uvm_monitor;

. . .

task run_phase(uvm_phase phase);

dbus_item item;

forever begin

@vif.cb;

if(!vif.cb.dbus_s.swait && !vif.cb.dbus_s.bwait

&& vif.cb.dbus_m.re && !vif.cb.reset) begin

item = dbus_item::type_id::create("item");

item.enable_recording("DBUS ITEM");

this.begin_tr(item, "DBUS ITEM");

item.re

=vif.cb.dbus_m.re;

item.we

=vif.cb.dbus_m.we;

item.dbus_m_addr=vif.cb.dbus_m.addr;

item.mdata =vif.cb.dbus_m.mdata;

@vif.cb.dbus_m.addr;

item.sdata =vif.cb.dbus_s.sdata;

ap.write(item);

end

this.end_tr(item);

end

endtask: run_phase

```

It is possible to see how it first creates a sequence item which is type-dependent to the protocol, checks for a specific combination of signals through the clocking block that resides in the interface, copies the signals over to the item, and at last writes this item to the analysis port. The  $begin_tr$  and  $end_tr$  which indicates the start and stop of the transaction, making it possible to be used in for example a waveform.

FIGURE 3.4: Monitor writes to analysis port

#### 3.1.9 Sequencer and Sequences

The frameworks sequencers are extended from the **uvm\_sequencer** and specialised with the sequence item for the corresponding protocol. For each sequence there is a sequencer declared for that specific sequence. All the sequencers in the framework has approximately the same functionality, there are however some sequencers that stands out from the rest. This is the sequencer for the Pbus, which has an access to the configuration database, and the Irq-sequencer, which builds two unlimited FIFO's.

#### 3.1.10 Interface

The interface for each protocol is naturally different for each individual protocol. The interfaces use packed structs to access the DUTs signals. The interfaces also include a clocking block, and some include properties and assertions to assert correct functionality.

#### 3.1.11 Sequence Item

Each of the protocols have their own sequence item. Where there are several similarities between the the protocols' sequence items. The ones with the most in common are: Pbus, Dbus, IObus and IObus\_qr. These sequence items all have a variables for: