# Silicon Carbide Technologies for High Temperature Motor Drives

Øyvind Holm Snefjellå

Master of Science in Energy and Environment Submission date: June 2011 Supervisor: Tore Marvin Undeland, ELKRAFT Co-supervisor: Richard Lund, SmartMotor

Norwegian University of Science and Technology Department of Electric Power Engineering

# Silicon Carbide Technologies for High Temperature Motor Drives

Øyvind Holm Snefjellå

Master of Science in Energy and EnvironmentSubmission date:June 2011Supervisor:Prof. Tore M. Undeland, ELKRAFTCo-supervisor:Ibrahim Abuishmais , ELKRAFTRichard Lund, SmartMotor

Norwegian University of Science and Technology Department of Electric Power Engineering

# **Problem description**

Down-hole motor drive systems can be important in future oil gas installations for exploitation of existing oil wells. Huge values are related to increased exploitation of the oil fields. It is expected that technology development in this area will be a large driving force for development of power electronics for high temperatures and pressure. SmartMotor has initiated a 5 years research project on development of motor drives for subsea and down-hole operation. The project is in cooperation with the Norwegian research council (NFR). Silicon Carbide (SiC) is the most promising material for making semiconductors for high temperature operation. A comparison of the material properties of Silicon Carbide and Silicon is therefore of large interest.

The performance of two different SiC transistors should be verified. The switching speed of the transistors should be adjusted to study how the switching behavior will be affected. The intrinsic properties of SiC transistors make the devices extremely fast. At high switching speeds the influence of parasitic circuit elements becomes more important. The fast switching can easily lead to oscillations and ringings. Hence, the influence of parasitics on the switching behavior should be studied. Finally a converter using Silicone Carbide transistor should be built and tested. The maximum operating temperature of the converter is dictated by the transistor housing and the devices used in the control and drive circuits. It is not the task of the thesis to find the maximum operation temperature. However, the operation of the converters with SiC transistors should be verified.

Assignment given: 17. January 2011

Supervisor: Tore Marvin Undeland, ELKRAFT

# Preface

This master thesis documents the spring work during the fifth and final year of my master degree study in Energy and Environment at the Norwegian University of Science and Technology (NTNU). Working on this project has been challenging, nevertheless it has been very interesting and I have learned allot. Especially during the late hours I have spent in the laboratory, searching for errors and trying to find explanations for strange results. The fact that the research topic is quite new has created many challenges. Finding measuring equipment suitable for measuring the fast switching transients has proved to be very difficult and also time consuming.

During my work with the thesis there are a number of peoples I will like to address a great thank to, and whom I would not been able to finish the work without. First off all I would like to thank my supervisor Prof. Tore M. Undeland for giving me the opportunity to work on such an interesting topic. He has always encouraged me and supplied me with good ideas. And then Ibrahim Abuishmais, a PhD-student at the department, for helping me analyzing the measurements and for proof reading parts of my thesis. I would also like to thank Richard Lund from SmartMotor for helping throughout the whole project. He has always replied my mails and been willing to share his practical experience.

Bard Almås from the service lab at NTNU deserves an extra acknowledgement. He has spent numerous hours helping me with the lab equipment and showing me how to make printed circuit boards.

In the end, I would like to thank my fellow students, contributing to a nice and friendly working atmosphere. Without you it would not have been the same.

Øyvind Holm Snefjellå

Trondheim, June 2009

# Summary

Many applications benefit from using converters which can operate at high temperatures among them; down-hole drilling, hybrid vehicles and space craft. The theoretical performance of transistors made of Silicon Carbide (SiC) is investigated in this work. It is shown that their properties at high temperatures are superior compared to Silicon (Si) devices. Two half-bridge converters, using SiC normally-off Junction Field Effect Transistors (JFET) and SiC Bipolar Junction Transistors (BJT), are designed and tested to verify the performance of SiC devices. The challenges which arise when replacing slow switching Si devices with extremely fast SiC transistors are thoroughly discussed.

To fully utilize the properties of SiC transistors, the converter designer must pay extra attention to the Printed Circuit Board (PCB) layout and component selection. For best device performance, all parasitics should be kept at a minimum. A high value of the Schottky diode capacitance results in voltage and current ringings, thus more ElectroMagnetic Interference (EMI) and switching energy loss. It is recommended selecting a Schottky diode with low junction capacitance as the freewheeling diode of the converter. Simulations and measurements show that the SiC transistors require special gate driving circuits to perform at their best. It is recommended to use a two-stage driver with high capability of charging and sinking gate/base currents. The JFET driver should also have a bipolar output to provide high noise immunity. The JFET is classified as a unipolar device; however the nature of the gate-source structure, which is a pn-junction, gives the device some bipolar characteristics. The gate structure is similar to BJT. To obtain a low on-state resistance some continuous gate current has to be provided. This is more pronounced at high temperatures.

An analog control board, for operating the half-bridge as a step down converter, is designed and implemented. The controller uses current mode control to obtain a constant output voltage. Slope compensation is included to ensure stable operation at high duty-cycles. This makes the converter able to operate stably for a wide range of input voltages. The step down converter shows excellent performance during stationary operations and the ripple voltage is within its limit.

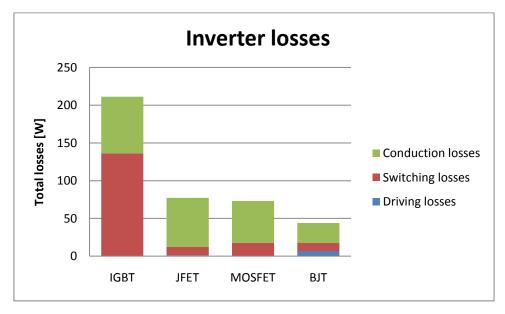

When operating at high ambient temperatures it is important to have small transistor losses to minimize the self-heating of devices. The losses of a three phase inverter are calculated based on the measured conduction and switching losses of the SiC transistors. The calculations show that both inverters, based on BJTs and JFETs, are able to operate with very high efficiency even at high temperatures. High temperature characterization of the devices shows that their dynamic behavior, i.e. switching losses and switching times, are almost unaffected by temperature changes. The transistors, tested in this work, are suited to operate at ambient temperatures up to 150 °C. This is imposed by the conventional device packaging. Higher operating temperatures are achievable by using different packaging technologies, i.e. metal packaging advanced soldering methods.

# Sammendrag

Mange applikasjoner drar nytte av å bruke omformer som kan driftes ved høye temperaturer. Blant disse applikasjonene finner en ned-i-hulls boring, hybrid biler og romfart industri. I dette arbeidet er den teoretiske ytelsen, til transistorer laget av Silisium Karbid (SiC), kartlagt. Egenskapene ved høye temperaturer er langt bedre enn for Silisium transistorer (Si). To halv-broer er designet og testet for å kartlegge ytelsen til to utvalgte SiC transistorer. De valgte transistorene er en "Junction Field Effect Transistor" (JFET) og en "Bipolar Junction Transistor" (BJT). JFETen er normalt av og leder kun når en positiv gatespenning påtrykkes. Når sakte svitsjende Silisium transistorer blir erstattet av ekstremt raske SiC transistorer oppstår det en rekke problemer. Disse problemene er studert grundig i denne rapporten.

Fo å utnytte egenskapene til SiC transistorene til det full, så må omformerdesigneren være ekstra nøye når kretskortlayouten skal tegnes. Komponenter må også velges med omhu. Den beste ytelsen oppnås hvis alle parasittiske komponenter blir minimert. En høy Schottkydiode-kapasitans resulterer i oscillasjoner i både strøm og spenning. Oscillasjonene bidrar til økt ElektroMagnetisk Interferens (EMI) og økte svitsjetap. Når en velger friløpsdiode er det derfor anbefalt å velge en Schottkydiode med lav kapasitans. Simuleringer og målinger viser at SiC transistorene er avhengig av å benytte spesielle gatedrivere for å driftes optimalt. Det er anbefalt å bruke en totrins driver som kan levere og trekke høye transiente gate/base-strømmer. Driveren for JFETen burde også ha en bipolar utgangsspenning for å øke immuniteten mot støy. JFETene viser noen av de samme egenskapene som bipolare transistorer, selv om de klassifisert som unipolare transistorer. "Gate-source" strukturen til JFETene er en pn-overgang og ligner på den for BJTer. En kontinuerlig gatestrøm må påtrykkes for å oppnå en lav ledemotstand. Størrelsen på strømmen må økes med stigende temperatur.

En analog styrekrets for halv-broen er designet og test. Kontrolleren styrer halv-broen som en Buck omformer. Kontrolleren benytter strøm modus styring for å opprettholde en konstant utspenning. Strømstigningskompensering er benyttet for å dempe underharmoniske oscillasjoner som oppstår ved høye arbeidssykluser. Buck omformeren kan derfor driftes for et bredt spekter av innspenninger. Omformeren fungerer utmerket under stasjonær drift og rippelspenningen er innenfor grensene.

Under høytemperturdrift er det viktig at transistortapene er små slik at oppvarmingen av transistorene blir minst mulig. Tapene i en tre fase vekselretter er beregnet, basert på de målte svitsje- og ledetapene for BJTene og JFETene. Beregning viser at begge vekselretterne kan driftes med høy virkningsgrad selv ved høye temperaturer. Karakteriseringen av transistorenes dynamiske egenskaper ved høy temperaturer, viser at svitsjetidene og svitsjetapene er nesten uavhengig av temperatur. De testede transistorene kan benyttes omgivelses temperaturer for opp til 150 °C. Temperaturgrensen settes begrensninger ved de konvensjonelle av transistorkapslingene. Høyere temperaturer kan oppnås ved å benytte andre kapslingsteknologier. Metall kapslinger, hvor avanserte lodde teknikker er benyttet, er et eksempel på en type høytemperaturkapsling.

# **Table of Content**

| 1 | Intro          | oduc  | tion                                                                              | 1    |

|---|----------------|-------|-----------------------------------------------------------------------------------|------|

|   | 1.1            | Pro   | blem background and motivation                                                    | 1    |

|   | 1.2            | Sys   | tem description and scope of work                                                 | 2    |

|   | 1.3            | Rep   | ort outline                                                                       | 4    |

| 2 | Bac            | kgro  | und and Theory                                                                    | 5    |

|   | 2.1            | Step  | o down converter                                                                  | 5    |

|   | 2.2            | Hal   | f bridge converter                                                                | 7    |

|   | 2.3            | Gat   | e drivers for bridge applications                                                 | 7    |

|   | 2.3.           | 1     | Signal and power isolation                                                        | 8    |

|   | 2.3.           | 2     | Dead time calculation                                                             | 9    |

|   | 2.4            | Inve  | erter losses                                                                      | . 11 |

|   | 2.4.           | 1     | Driver losses and required driver power                                           | . 11 |

|   | 2.4.<br>sinu   | _     | Analytical expression of power losses in a voltage source converter val currents  |      |

|   | 2.4.           | 3     | Total converter losses                                                            | 16   |

|   | 2.5            | Cha   | llenges at high temperature                                                       | 16   |

|   | 2.5.           | 1     | Semiconductors at elevated temperatures                                           | 17   |

|   | 2.5.           | 2     | Packaging                                                                         | 18   |

| 3 | Silic          | con ( | Carbide Technology                                                                | . 19 |

|   | 3.1            | Mat   | terial properties of SiC                                                          | . 19 |

|   | 3.1.           | 1     | Unipolar devices                                                                  | 20   |

|   | 3.1.           | 2     | Bipolar devices                                                                   | . 21 |

|   | 3.2            | Stat  | e of the art of SiC devices                                                       | 23   |

|   | 3.3            | Ava   | ilable enhancement mode SiC transistors                                           | 24   |

|   | 3.3.           | 1     | JFET                                                                              | 24   |

|   | 3.3.           | 2     | BJT                                                                               | 28   |

|   | 3.3.           | 3     | MOSFET                                                                            | 29   |

|   | 3.4<br>state-c |       | oretical efficiency comparison between available SiC transistors an e-art Si IGBT |      |

| 4 | Des            | ign c | of Converters and Control Circuits                                                | 33   |

|   | 4.1            | Hal   | f-bridge converter specifications                                                 | 33   |

|   | 4.2            | PCI   | 3 layout considerations                                                           | 34   |

|   | 4.3            | Gat   | e/base driver design and selection                                                | 38   |

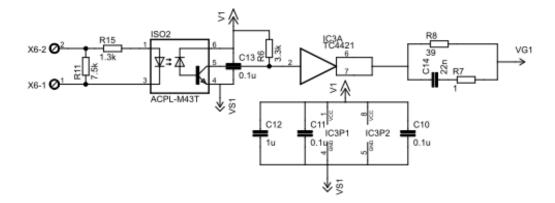

|   | 4.3.           | 1     | JFET gate driver                                                                  | 38   |

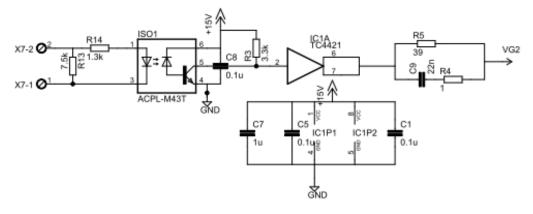

|   | 4.3.           | 2     | BJT base driver                                                                   | 39   |

|   | 4.4            | Con   | verter schematic and PCB layout                                                   | . 41 |

|   | 4   | 4.4.1   | JFET schematic and layout                                | 41 |

|---|-----|---------|----------------------------------------------------------|----|

|   | 4   | 1.4.2   | BJT schematic and layout                                 | 44 |

|   | 4.5 | Ty      | pes of control and modes of operation of Buck converters |    |

|   | 4   | 4.5.1   | Filter dimensioning                                      |    |

|   | 4   | 4.5.2   | Voltage mode                                             | 49 |

|   | 4   | 4.5.3   | Current mode                                             | 50 |

|   | 4.6 | Im      | plementation of controller IC                            | 51 |

|   | 4   | 4.6.1   | Brief control theory                                     |    |

|   | 4   | 4.6.2   | Modeling of converter                                    | 51 |

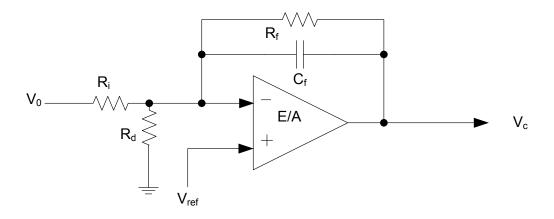

|   | 4   | 4.6.3   | Design of compensation network                           | 52 |

|   | 4   | 1.6.4   | Generation of dead time and complementary outputs        | 55 |

|   | 4   | 4.6.5   | Control board schematic and layout                       | 55 |

| 5 | Ι   | Laborat | ory Setup and Measurement Description                    | 59 |

|   | 5.1 | Ex      | perimental standards and test principles                 | 59 |

|   | 5   | 5.1.1   | Switching times and energies                             | 59 |

|   | 5   | 5.1.2   | Test principles                                          | 61 |

|   | 5.2 | Me      | asuring equipment                                        | 63 |

|   | 5   | 5.2.1   | Oscilloscope                                             | 63 |

|   | 5   | 5.2.2   | On-state characteristics                                 | 63 |

|   | 5   | 5.2.3   | SBC operation                                            | 64 |

|   | 5   | 5.2.4   | Complete list of lab equipment                           | 64 |

|   | 5   | 5.2.5   | Current measuring                                        | 65 |

|   | 5.3 | Lal     | poratory setup                                           | 68 |

|   | 5.4 | . Ini   | tial measurements                                        | 71 |

|   | 5   | 5.4.1   | DPT JFET half-bridge                                     | 71 |

|   | 5   | 5.4.2   | DPT BJT half-bridge                                      |    |

|   | 5   | 5.4.3   | Buck converter operation                                 |    |

| 6 | S   | Simulat | ions in LTspice                                          |    |

|   | 6.1 | Inf     | luence of parasitic                                      |    |

|   | 6   | 5.1.1   | Soft switching due to parasitic capacitances             |    |

|   | 6   | 5.1.2   | Problems with dead time generation                       | 86 |

|   | 6.2 | BJ      | Γ double pulse test                                      | 86 |

|   | 6.3 | PW      | M controller for Buck converter                          | 88 |

| 7 | F   | Results | and Discussion                                           |    |

|   | 7.1 | Sel     | ection of gate resistance                                |    |

|   | 7.2 | Dy      | namic characterization                                   |    |

|   | 7   | 7.2.1   | Switching characteristics of SiC JFET                    |    |

| 7.2     | 2.2 Switching characteristics of SiC BJT                              |     |

|---------|-----------------------------------------------------------------------|-----|

| 7.3     | On-state losses                                                       |     |

| 7.4     | Loss comparison and inverter efficiency                               | 103 |

| 7.5     | Verification of the step down converter performance                   | 104 |

| 7.6     | General discussion and summary                                        | 107 |

| 8 Co    | nclusion and Scope of Further Work                                    | 110 |

| 8.1     | Conclusion                                                            | 110 |

| 8.2     | Scope of further work                                                 | 110 |

| Bibliog | raphy                                                                 | 112 |

| Append  | lixes                                                                 | 116 |

| A Ma    | ntlab codes                                                           | 116 |

| A1      | Code for calculating inverter losses                                  | 116 |

| A2      | Code for calculating switching energies                               | 116 |

| B Est   | timated data sheet values                                             | 118 |

| C PC    | B Design Rules                                                        | 119 |

| C1      | Electrical clearing                                                   | 119 |

| C2      | Trace width and skin depth                                            | 119 |

| a)      | Skin depth                                                            | 119 |

| b)      | Trace width                                                           | 120 |

| D Scl   | hematics and Board Layouts                                            | 122 |

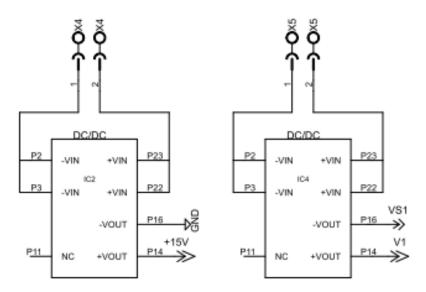

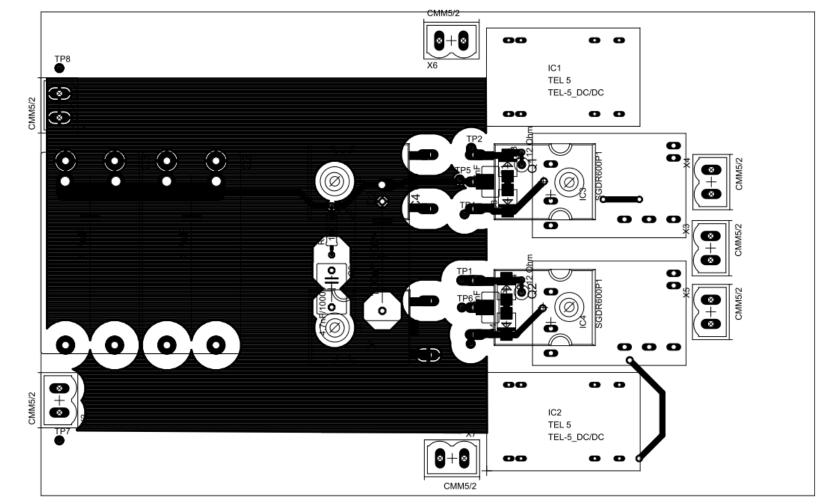

| D1      | Gate driver and DC/DC converter connections for JFET half-bridge.     | 122 |

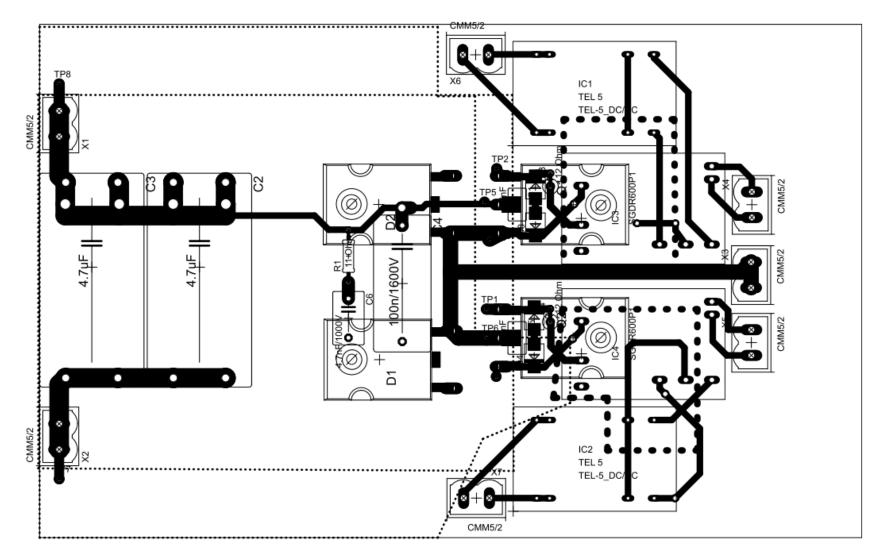

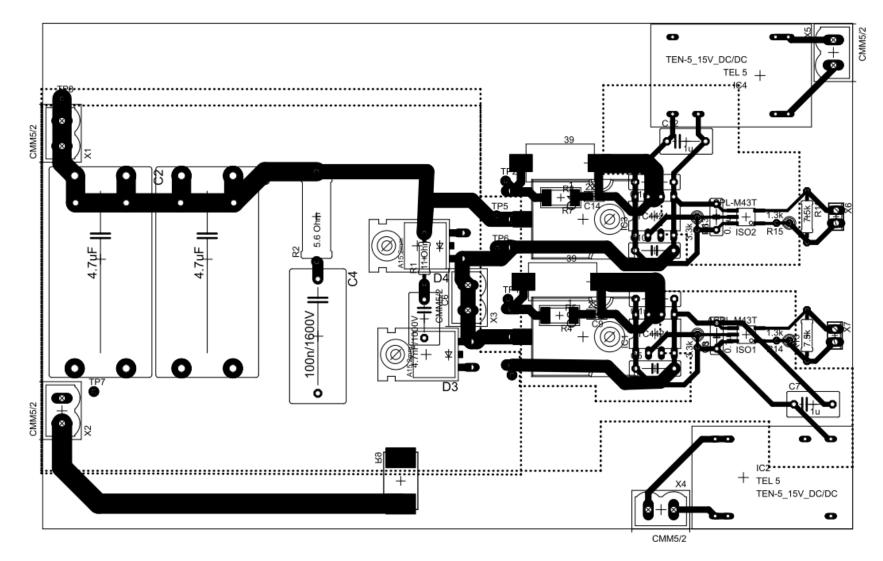

| D2      | PCB layout for the JFET half-bridge                                   | 123 |

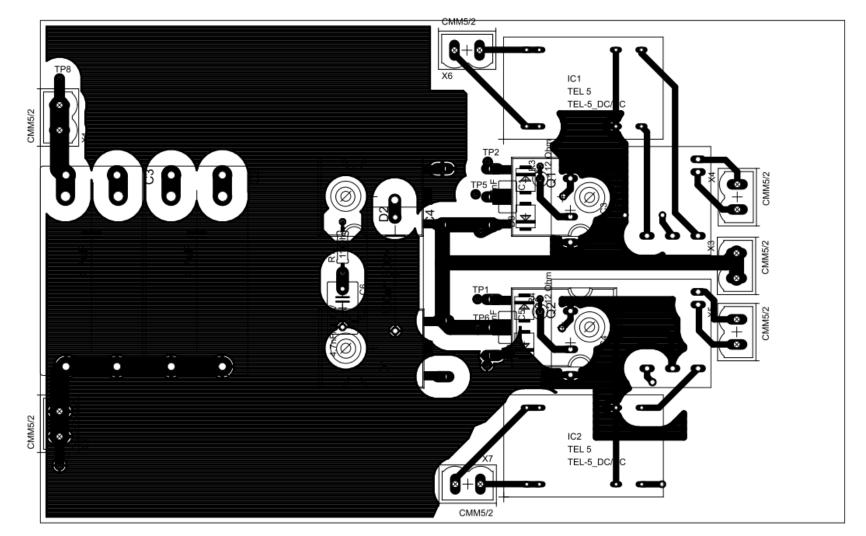

| D3      | PCB layout for the BJT half-bridge                                    | 125 |

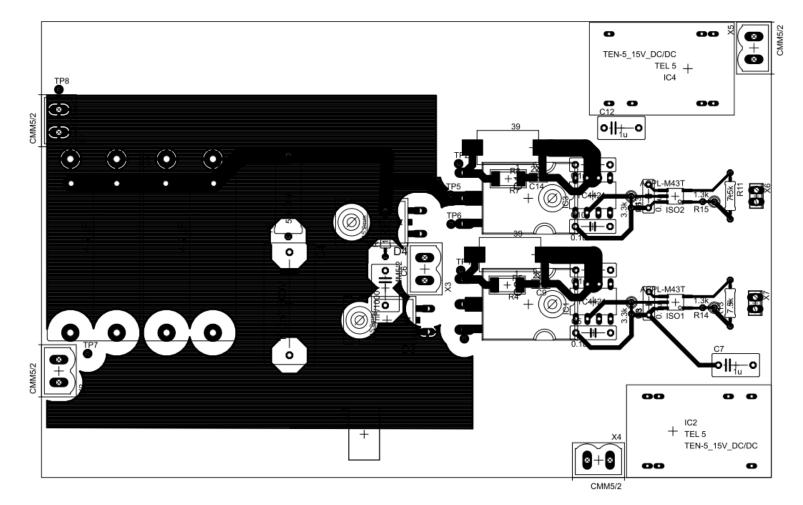

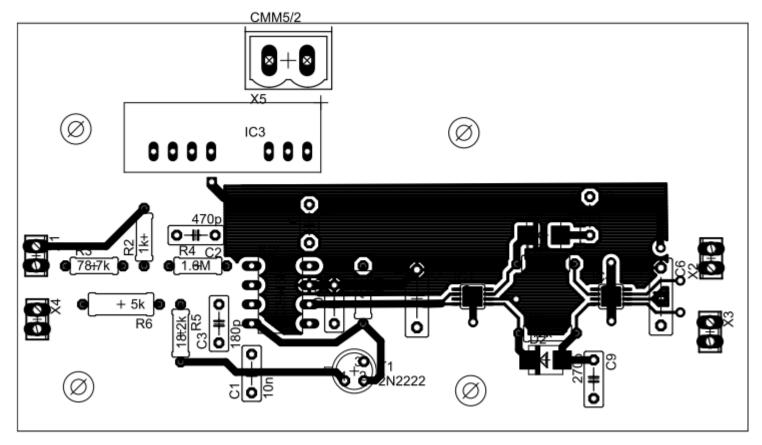

| D4      | Control card PCB layout                                               | 127 |

| E Bil   | l of Materials                                                        | 129 |

| E1      | BOM JFET half-bridge                                                  | 129 |

| E2      | BOM BJT half-bridge                                                   | 130 |

| E3      | BOM control board                                                     | 131 |

| F DF    | T measurements with JFET half-bridge                                  | 132 |

| G Sir   | nulation models in LTspice                                            | 134 |

| G1      | Investigation of soft switching                                       | 134 |

| G2      | Dead time generation model                                            | 134 |

| G3      | Model of step down converter and SBC                                  | 134 |

| H Me    | easurements of step down converter                                    | 137 |

| H1      | Output waveforms for a $59\Omega$ load                                | 137 |

| H2      | Step load from 59 $\Omega$ to 30 $\Omega$ for a input voltage of 400V | 138 |

| I Pic   | ctures from the laboratory                                            | 139 |

# List of Figures

| Figure 1-1 Oil and gas recovery system                                                 |          |

|----------------------------------------------------------------------------------------|----------|

| Figure 1-2 Three-phase inverter [9]                                                    |          |

| Figure 2-1 Step down converter with resistive load [9]                                 |          |

| Figure 2-2 Output waveforms of Buck converter [9]                                      |          |

| Figure 2-3 Inductor voltage and current assuming continuous current [9]                | 6        |

| Figure 2-4 Half bridge converter                                                       | 7        |

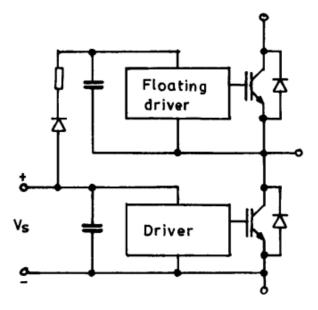

| Figure 2-5 Carrier modulated transformer isolated drive circuit [11]                   | 8        |

| Figure 2-6 Bootstrap auxiliary supply [11]                                             | 9        |

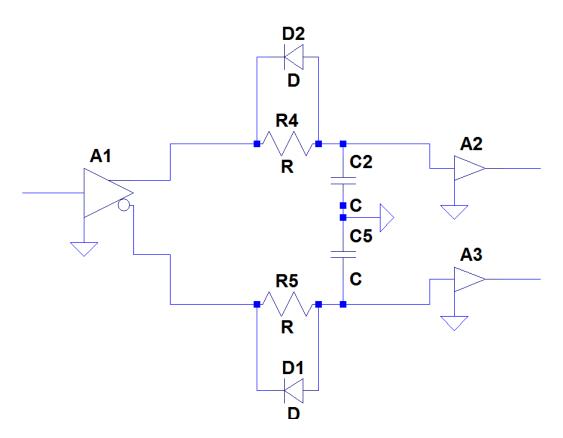

| Figure 2-7 Dead time generation circuit                                                | 10       |

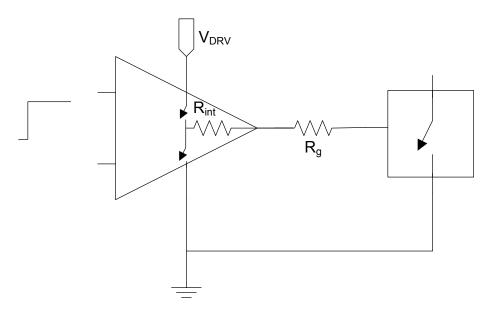

| Figure 2-8 Principle driver connection                                                 | 11       |

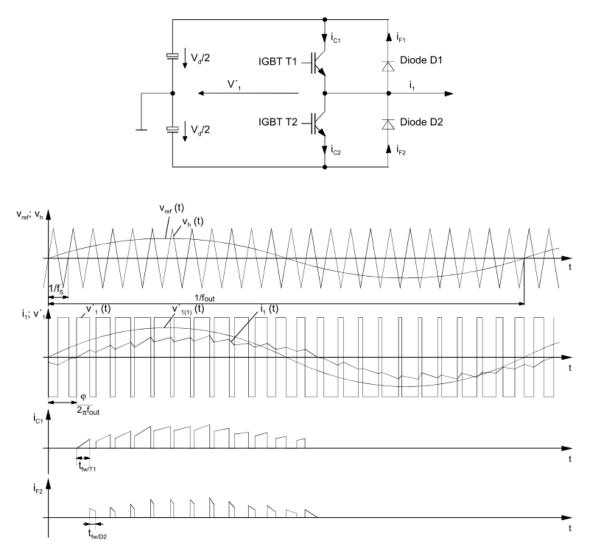

| Figure 2-9 A single converter phase with sinusoidal pulse-width modulation [15]        | 13       |

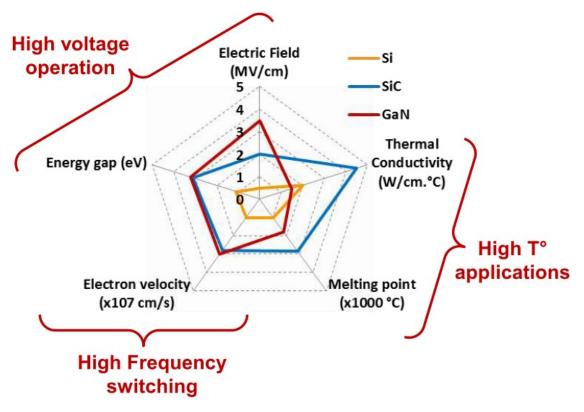

| Figure 3-1 GaN vs. SiC vs. Si Figure-of-merit [29]                                     |          |

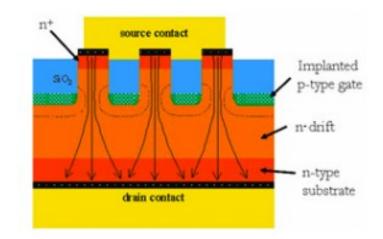

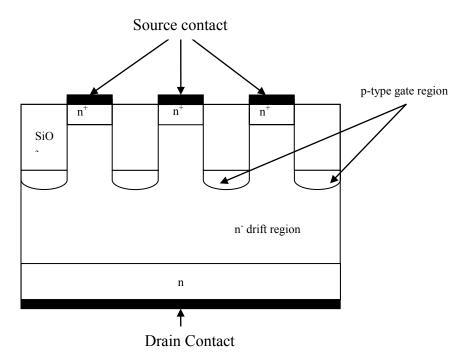

| Figure 3-2 Cross-section of a enhancement mode SiC J-FET [38]                          |          |

| Figure 3-3 Cross-section of a enhancement mode SiC J-FET.                              |          |

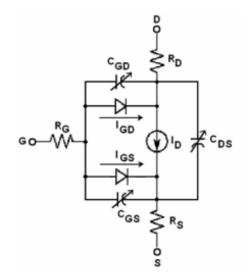

| Figure 3-4 Schematic representation of the SiC JFET [39]                               |          |

| Figure 3-5 Gate charge curve [37]                                                      |          |

| Figure 3-6 Inverter losses at $T_1 = 25$ °C                                            |          |

| Figure 3-7 Inverter losses at T <sub>i</sub> =100 °C                                   |          |

| Figure 4-1 Heat sink layout                                                            |          |

| Figure 4-2 Stray inductance in power loop                                              |          |

| Figure 4-3 Strip line connection, the copper traces are white while the insulating PCE |          |

| green                                                                                  |          |

| Figure 4-4 Stray capacitances in half-bridge circuit                                   |          |

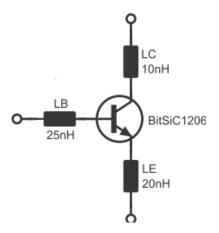

| Figure 4-5 Package inductance of BitSiC1206 TO-258/To-247 [44]                         |          |

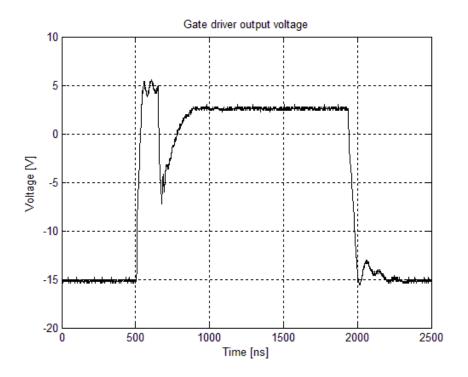

| Figure 4-6 Gate driver output waveforms                                                |          |

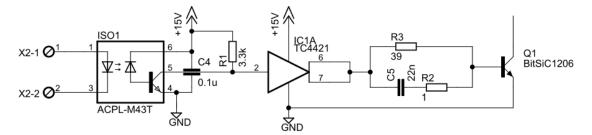

| Figure 4-7 BJT driver schematic                                                        |          |

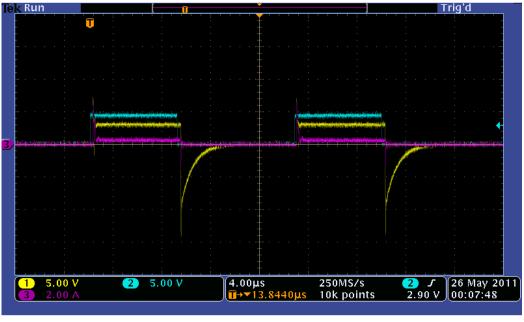

| Figure 4-8 BJT driver operation, the input voltage to the optocoupler is turquoise,    |          |

| output voltage is yellow and base current is purple                                    |          |

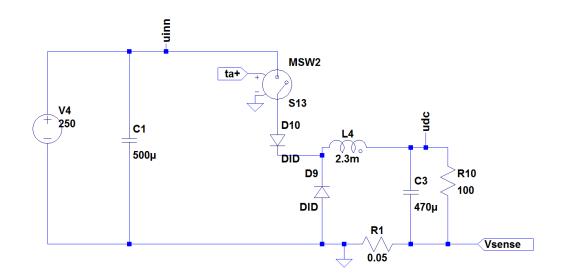

| Figure 4-9 JFET half-bridge schematic                                                  |          |

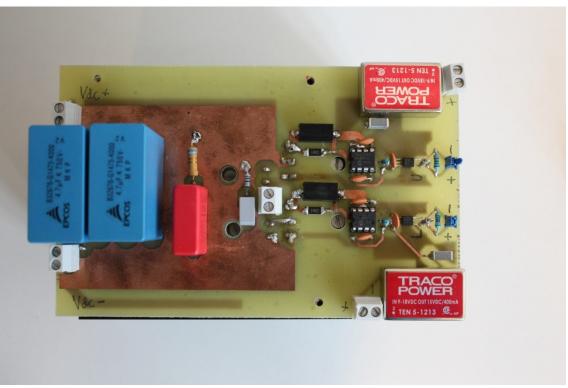

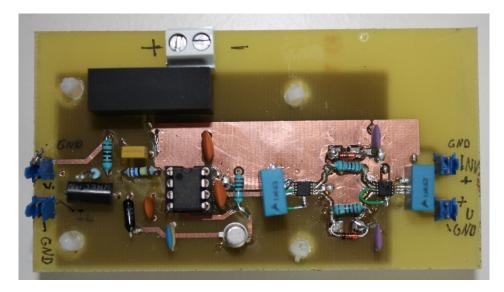

| Figure 4-10 Picture of JFET half bridge                                                |          |

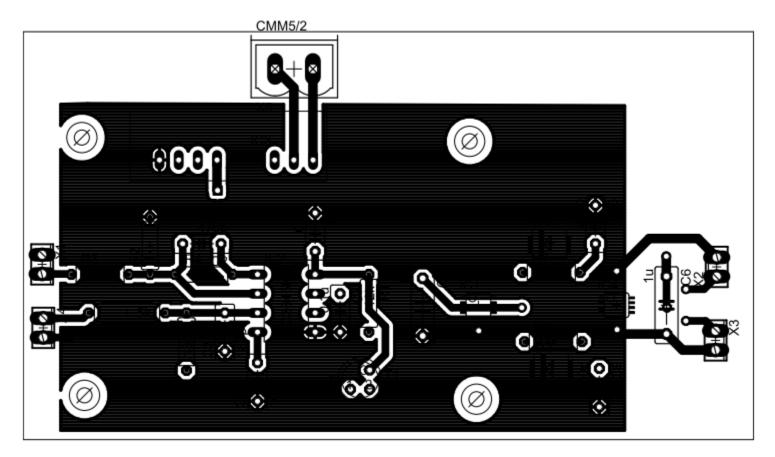

| Figure 4-11 JFET half-bridge PCB layout                                                |          |

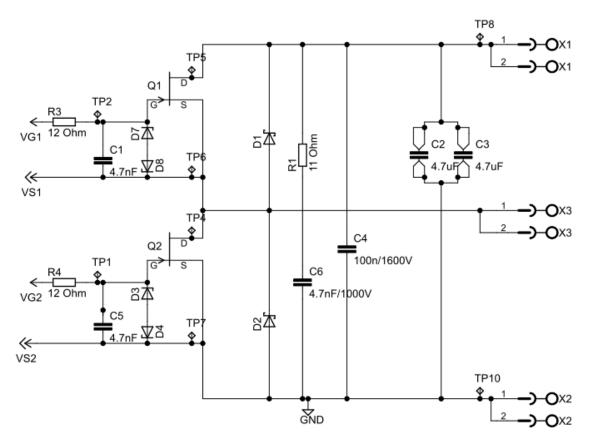

| Figure 4-12 BJT half-bridge schematic                                                  |          |

| Figure 4-13 BJT drivers schematic                                                      |          |

| Figure 4-14 Isolated gate driver supply                                                |          |

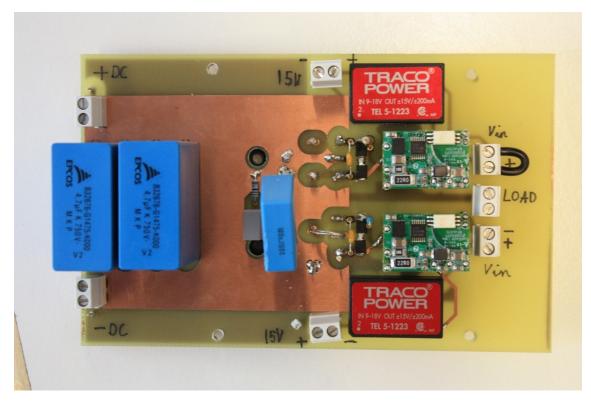

| Figure 4-15 Picture of BJT half-bridge                                                 |          |

| Figure 4-16 BJT half-bridge PCB layout                                                 |          |

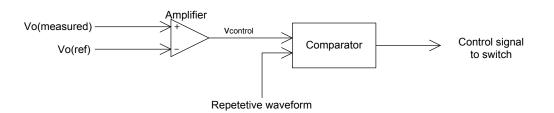

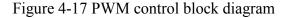

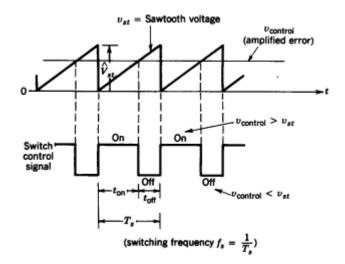

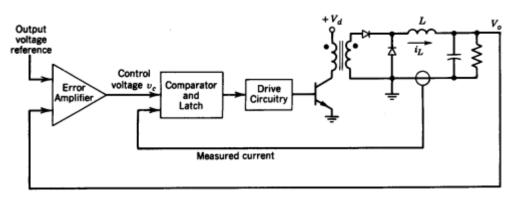

| Figure 4-17 PWM control block diagram                                                  |          |

| Figure 4-18 Comparator signal [9]                                                      |          |

| Figure 4-19 Current mode control [9]                                                   |          |

| Figure 4-20 Compensation network                                                       |          |

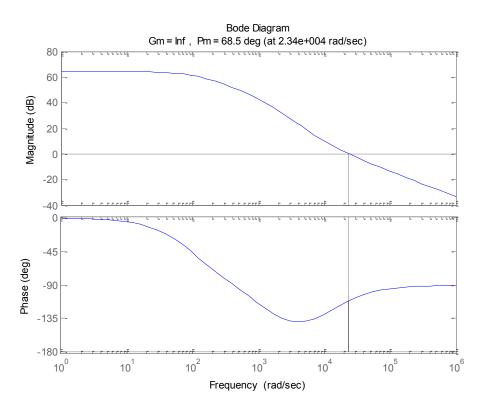

| Figure 4-21 Bode diagram of open-loop transfer fuction                                 | 54       |

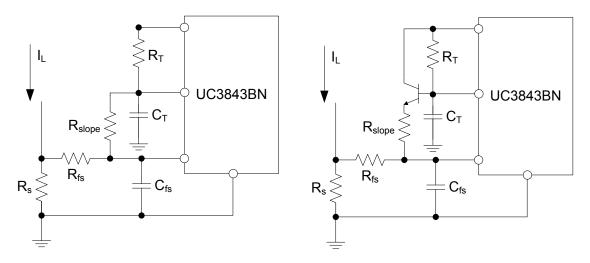

| Figure 4-22 Connection of current sensing and slop compensation                        |          |

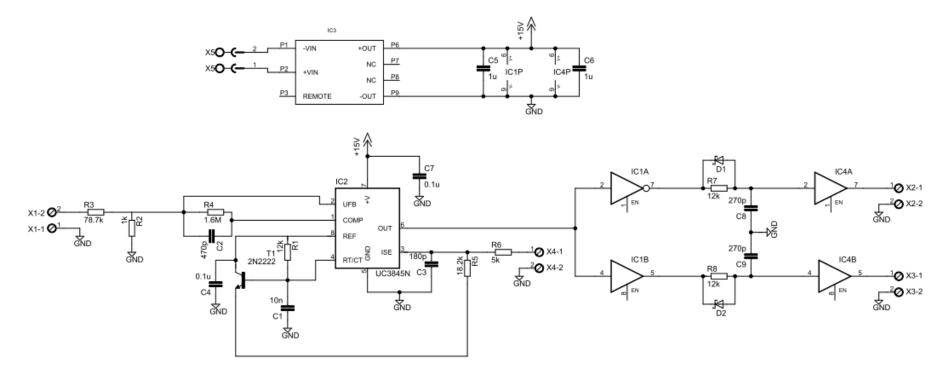

| Figure 4-23 Schematic of PWM controller and dead time generation                       |          |

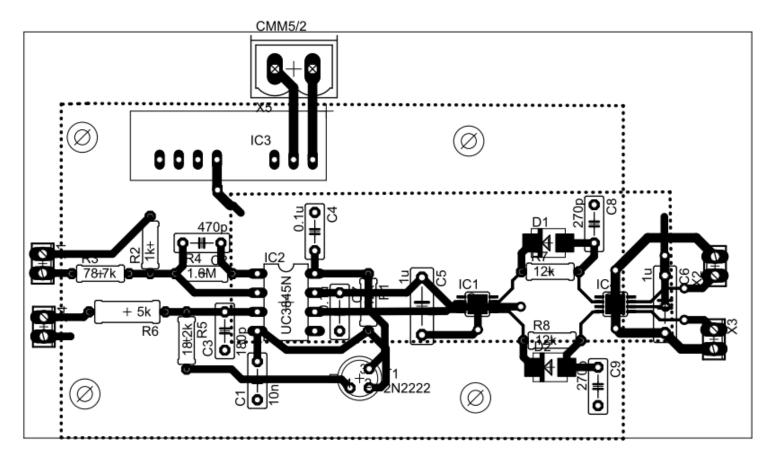

| Figure 4-24 Board layout of PWM controller and dead time generation                    |          |

| Figure 4-25 Picture of control board                                                   |          |

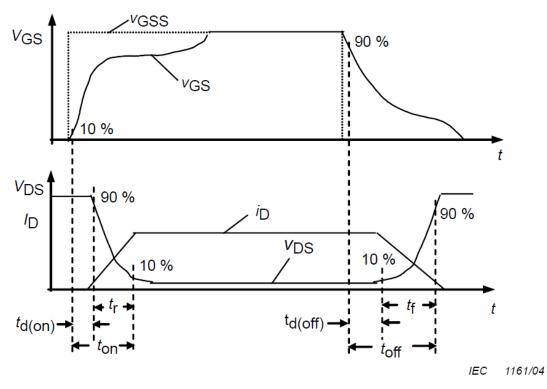

| Figure 5-1 Waveforms for turn on and turn off of a transistor [54]                     | 60       |

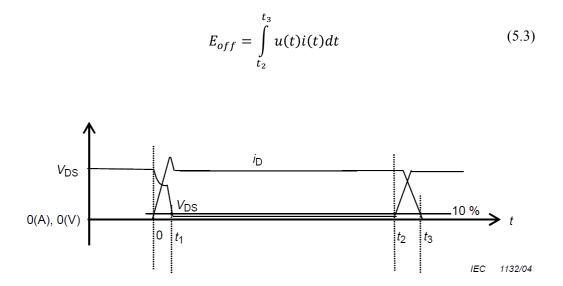

| Figure 5-2 Definition of switching losses [54]                                         |          |

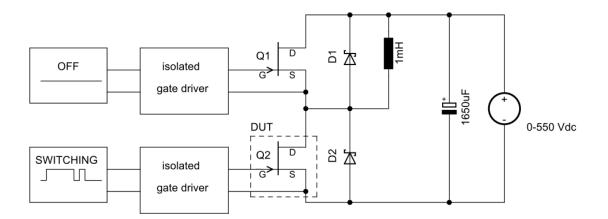

| Figure 5-3 Double pulse setup                                                          |          |

| Figure 5-4 Double pulse test principle                                                 |          |

| - Our c                                                                                | <u> </u> |

| Figure 5-5 Measurement of current time delay                                                         |          |

|------------------------------------------------------------------------------------------------------|----------|

| Figure 5-6 Measurement of time delay for CWT                                                         |          |

| Figure 5-7 Picture of current shunt                                                                  |          |

| Figure 5-8 DPT current waveforms measured by current shunt                                           |          |

| Figure 5-9 Comparison between Rogowski coils and current shunt, turn-off to the                      |          |

| and turn-on to the right                                                                             |          |

| Figure 5-10 Laboratory setup                                                                         |          |

| Figure 5-11 Principal connection of the SBC                                                          |          |

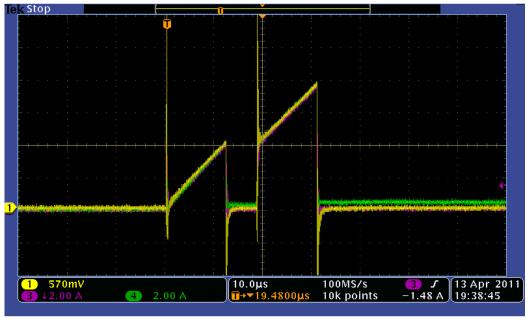

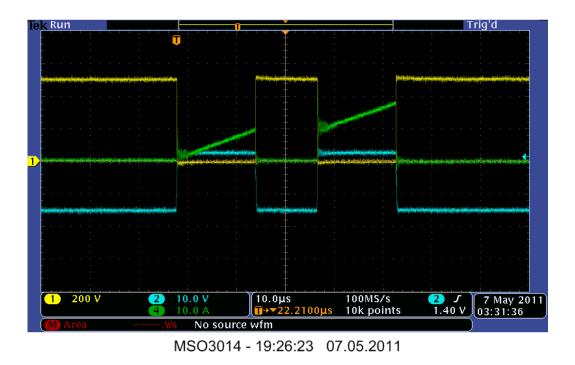

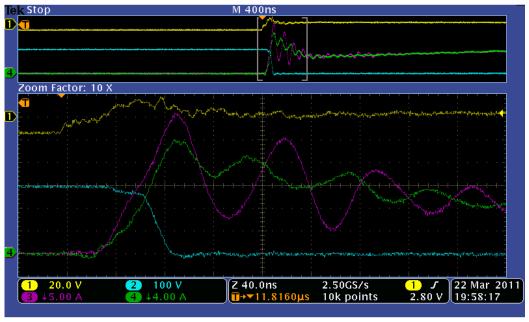

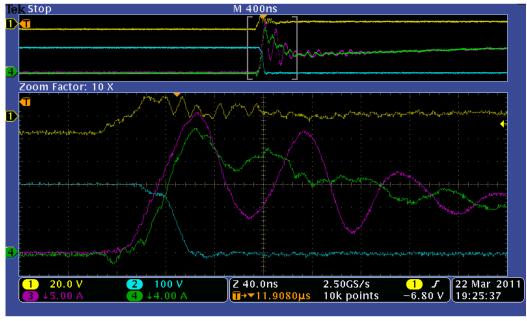

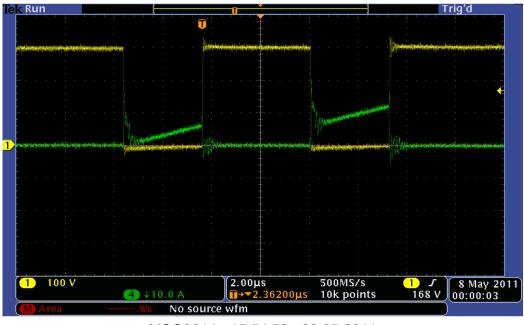

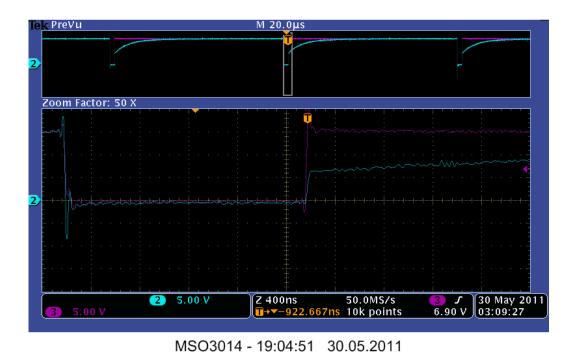

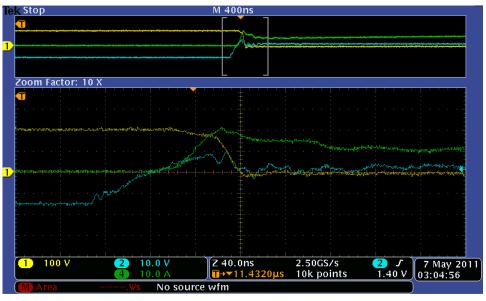

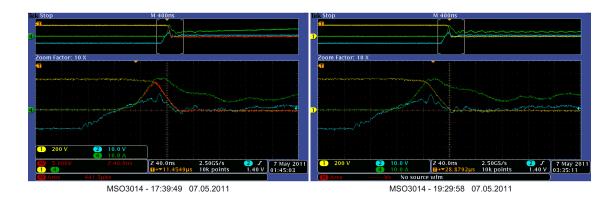

| Figure 5-12 DPT JFET with $I_d$ =10A and $V_{dc}$ =500V, $I_d$ is green and $V_{DS}$ is yellow       | OW.      |

| "Voltage shifted 6.5ns"                                                                              |          |

| Figure 5-13 DPT JFET turn-off to the left and turn-on to the right. The red curve sho                | WS       |

| the dissipated power. "Voltage shifted 6.5ns"                                                        | 72       |

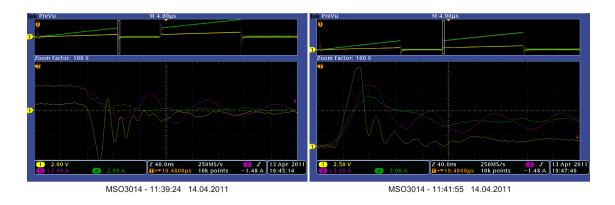

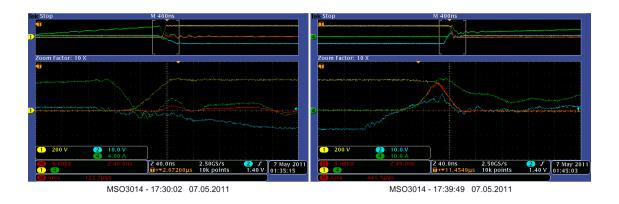

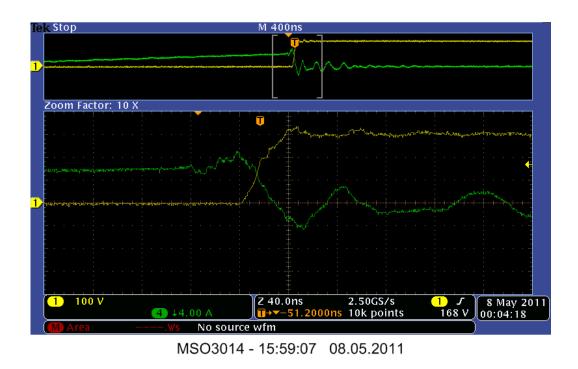

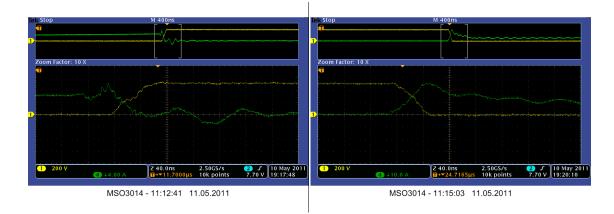

| Figure 5-14 Turn-on with $I_d=10A$ and $V_{dc}=300V$ , $R_g=0\Omega$ in the figure to the left a     | and      |

| $67.6\Omega$ in the one to the right                                                                 |          |

| Figure 5-15 Turn-off with $I_d=10A$ and $V_{dc}=300V$ , $R_g=0\Omega$ in the figure to the left a    | and      |

| $67.6\Omega$ in the one to the right.                                                                |          |

| Figure 5-16 Turn-on JFET $I_d$ =10A $V_{dc}$ =300V $C_g$ =10nF $R_g$ =1.8                            |          |

| Figure 5-17 Turn-on JFET $I_d=10A V_{dc}=300 C_g=4.7nF R_g=1.8$                                      |          |

| Figure 5-18 Turn-off JFET $I_d=10A$ $V_{dc}=500V$ , heat sink ground connected to the PG             |          |

| ground plane. "Voltage shifted 6.5ns" and "Current shifted 10ns"                                     |          |

| Figure 5-19 Turn-off JFET $I_d=10A V_{dc}=500V$ , heat sink ground not connected to                  |          |

| PCB ground plane. "Voltage shifted 6.5ns" and "Current shifted 10ns"                                 |          |

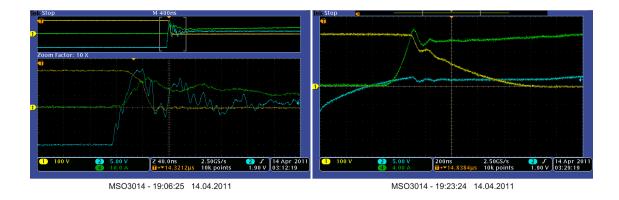

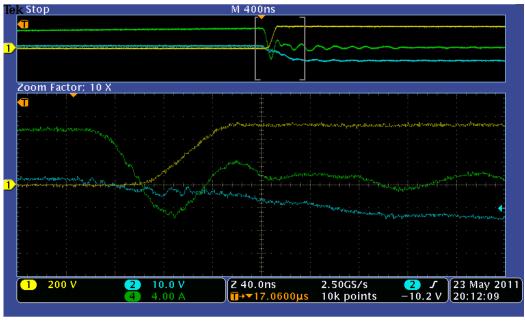

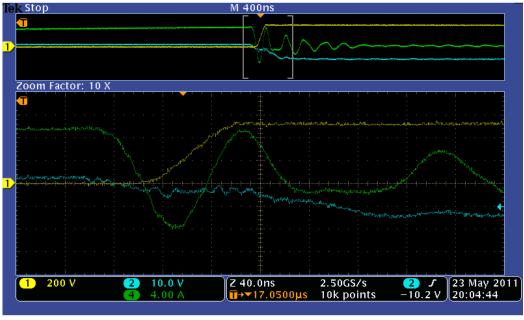

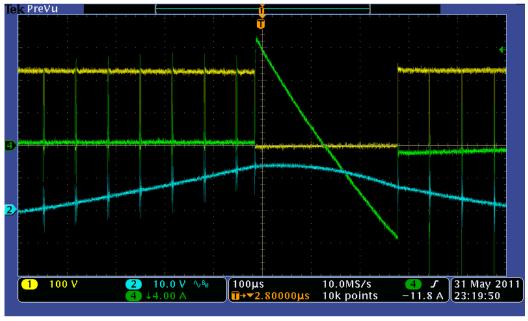

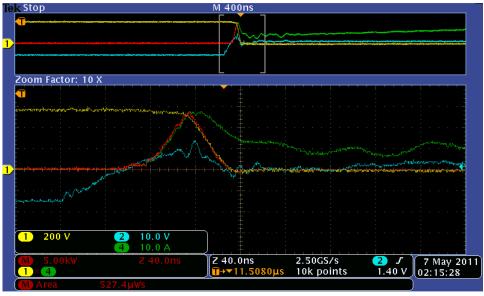

| Figure 5-20 DPT BJT with $I_d=6A$ and $V_{dc}=300V$ , $I_d$ is green and $V_{DS}$ is yello           |          |

| "Voltage shifted 6.5ns"                                                                              |          |

| Figure 5-21 Turn-on with $I_d$ =6A and $V_{dc}$ =300V, $I_d$ is green and $V_{DS}$ is yellow. "Volta |          |

| shifted 6.5ns"                                                                                       |          |

| Figure 5-22 Turn-off with $I_d=6A$ and $V_{dc}=300V$ , $I_d$ is green and $V_{DS}$ is yellow. "Volta |          |

| shifted 6.5ns"                                                                                       |          |

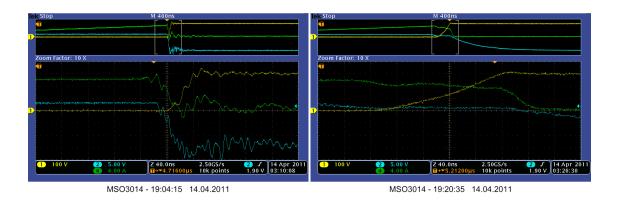

| Figure 5-23 DPT BJT with $I_d=6A$ and $V_{dc}=500V$ , turn-off to the left and turn-on to            |          |

| right. "Voltage shifted 6.5ns"                                                                       |          |

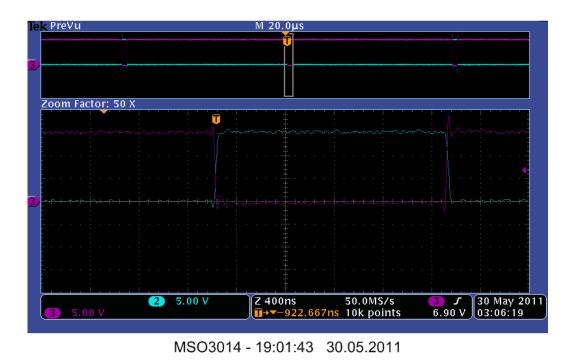

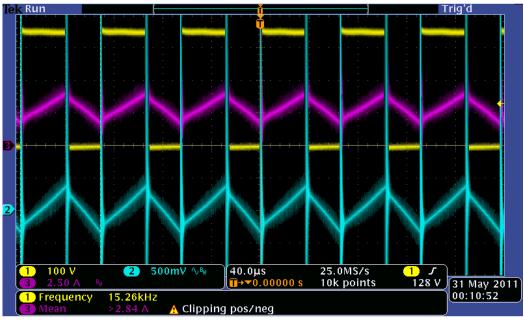

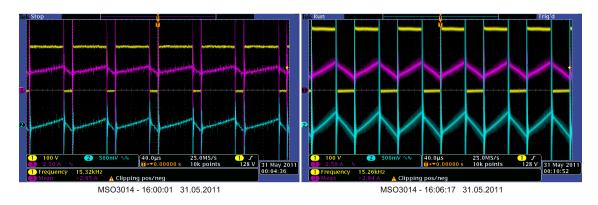

| Figure 5-24 Initial control board output                                                             |          |

| Figure 5-25 Step in voltage due to the capacitance of the Schottky diode                             |          |

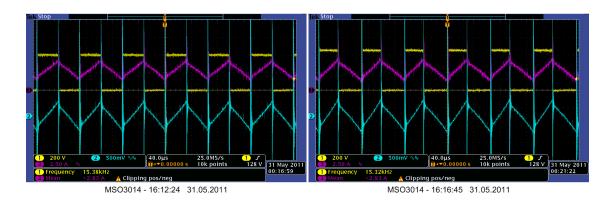

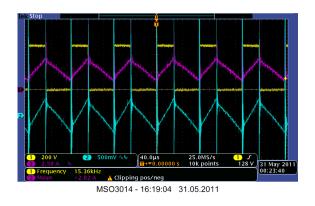

| Figure 5-26 Output waveforms SBC, the input voltage to output filter is yellow,                      |          |

| ripple component of the output voltage is blue and current through                                   |          |

| lower/freewheeling transistor is green                                                               |          |

| Figure 5-27 Stable operation of Buck converter, the input voltage to output filter                   |          |

| yellow, the ripple component of the output voltage is blue and the inductor current                  |          |

| purple                                                                                               |          |

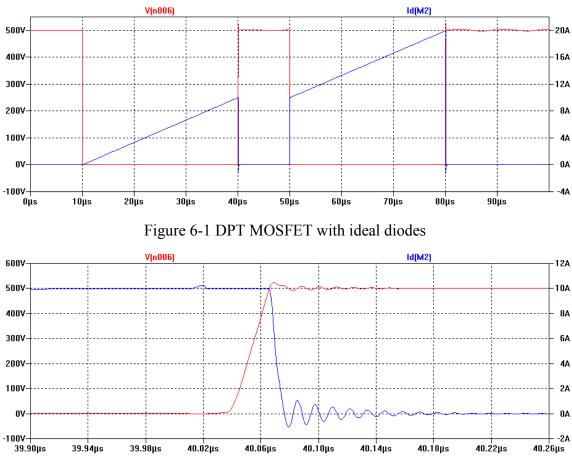

| Figure 6-1 DPT MOSFET with ideal diodes                                                              | 01<br>02 |

| Figure 6-2 Turn-off with ideal diodes                                                                |          |

| 6                                                                                                    |          |

| Figure 6-3 Turn-on ideal diode<br>Figure 6-4 DPT MOSFET with real diodes and non ideal inductor      |          |

|                                                                                                      |          |

| Figure 6-5 Turn-off with real diodes and non ideal inductor, $C_j=3.7nF$                             |          |

| Figure 6-6 Turn-on with real diodes and non ideal inductor, $C_j=3.7$ nF                             |          |

| Figure 6-7 Explanation of soft switching                                                             |          |

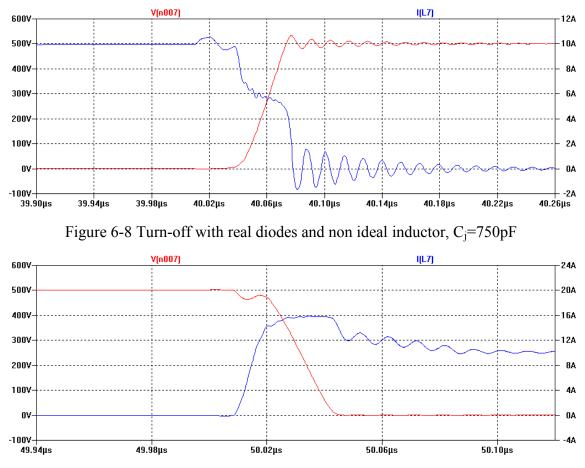

| Figure 6-8 Turn-off with real diodes and non ideal inductor, $C_j=750$ pF                            |          |

| Figure 6-9 Turn-on with real diodes and non ideal inductor, $C_j=750$ pF                             |          |

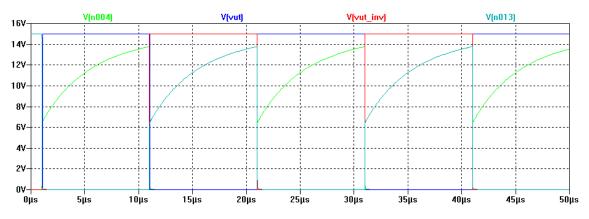

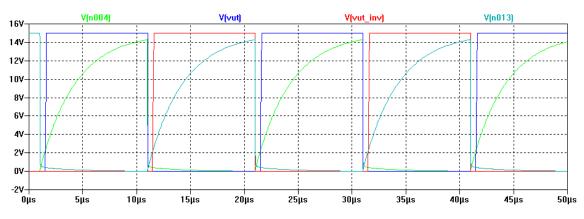

| Figure 6-10 Control output with the original diode                                                   |          |

| Figure 6-11 Control output with 1N4148 diode                                                         |          |

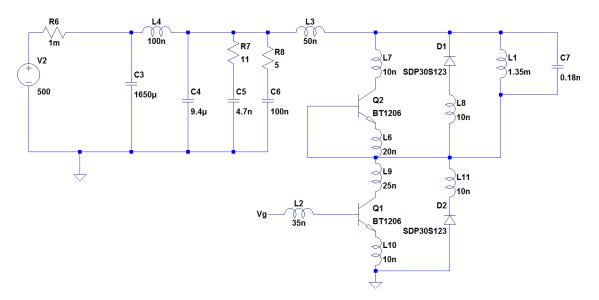

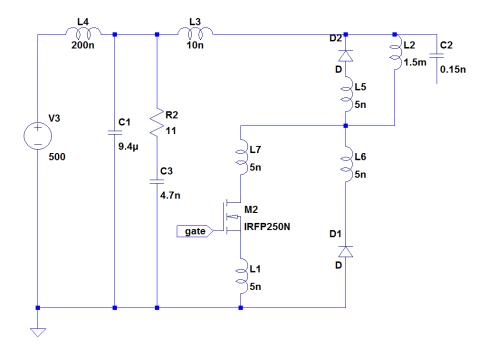

| Figure 6-12 BJT simulation model including parasitic components                                      |          |

| Figure 6-13 Base drive circuit for the BJTs                                                          | 87       |

|                                                                                                                           | ~ -   |

|---------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 6-14 Simulated DPT                                                                                                 |       |

| Figure 6-15 Simulated turn-off waveforms                                                                                  |       |

| Figure 6-16 Simulated turn-on waveforms.                                                                                  |       |

| Figure 6-17 Subharmonic oscillations in SBC with $V_{in}$ =400V and $R_0$ =59 $\Omega$                                    |       |

| Figure 6-18 Operation of Buck converter with $V_{in}$ =400V and $R_o$ =59 $\Omega$                                        |       |

| Figure 6-19 Step load for Buck converter with $V_{in}$ =500V. The load changes from                                       |       |

| to 29.5Ω                                                                                                                  |       |

| Figure 6-20 Start-up of Buck converter with $V_{in}$ =400 and $R_o$ =30 $\Omega$                                          |       |

| Figure 6-21 Voltage overshoot at turn-on of the Buck converter                                                            |       |

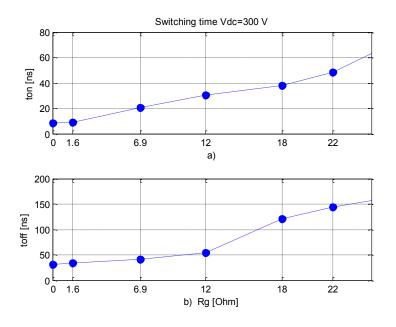

| Figure 7-1 Switching losses as a function of R <sub>g</sub> , R <sub>g</sub> is an external gate resistance.              |       |

| 10A                                                                                                                       |       |

| Figure 7-2 Switching times as a function of R <sub>g</sub> , I <sub>d</sub> =10A                                          |       |

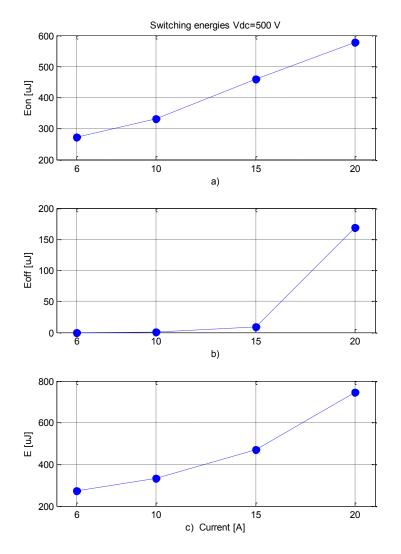

| Figure 7-3 Switching energies as function of current for $V_{dc}$ =500V                                                   |       |

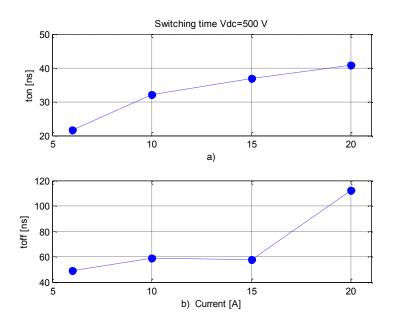

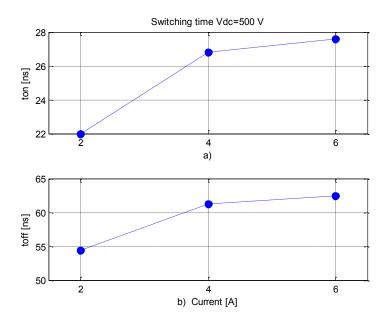

| Figure 7-4 Switching times as function of current for $V_{dc}$ =500V                                                      |       |

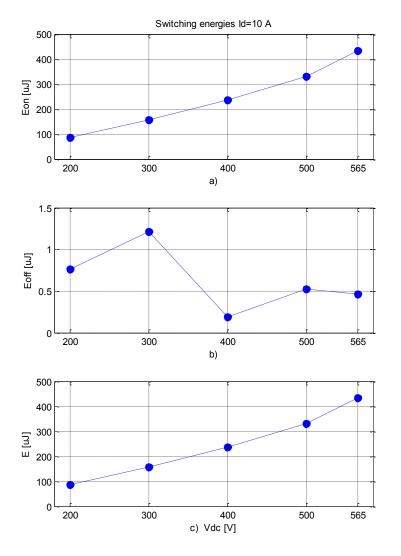

| Figure 7-5 Switching energies as function of voltage for $I_d=10A$                                                        |       |

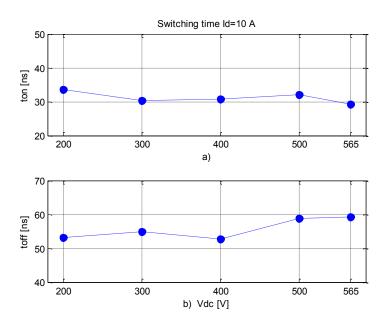

| Figure 7-6 Switching times as function of voltage for $I_d=10A$                                                           |       |

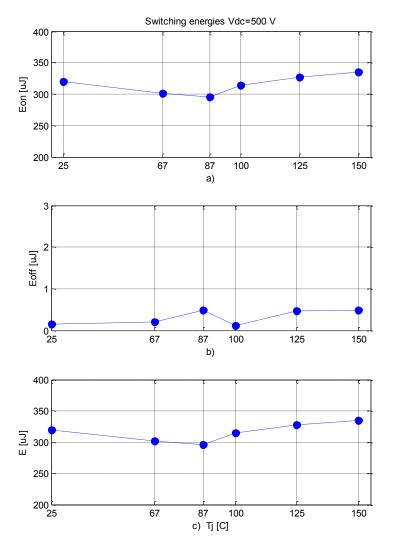

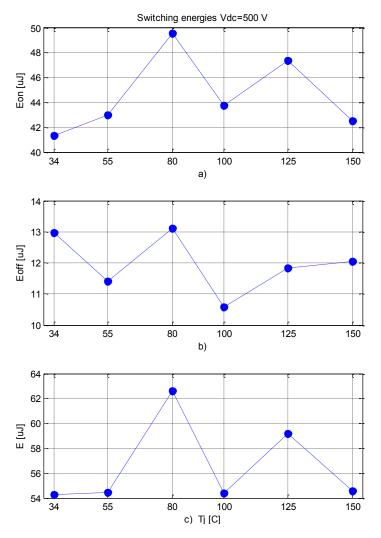

| Figure 7-7 Switching energies as function of junction temperature for $I_d=10A$                                           |       |

| V <sub>dc</sub> =500V                                                                                                     | 96    |

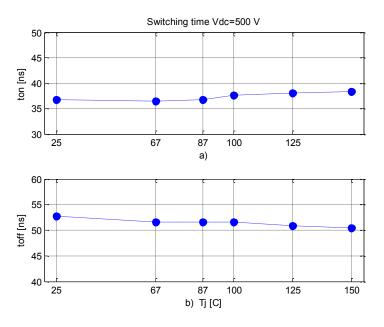

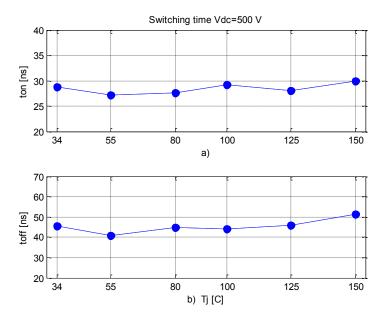

| Figure 7-8 Switching times as function of junction temperature for $I_d=10A$                                              |       |

| $V_{dc}$ =500V                                                                                                            |       |

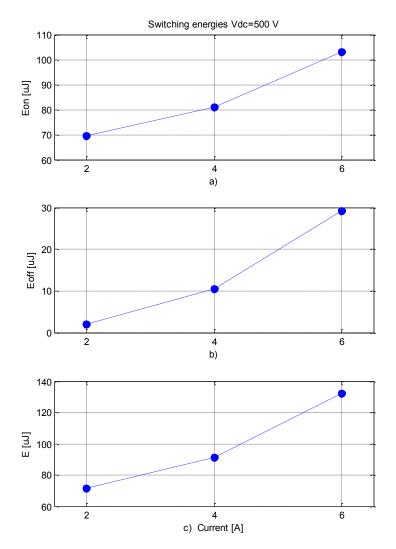

| Figure 7-9 Switching energies as function of collector current for $V_{dc}$ =500V                                         |       |

| Figure 7-10 Switching times as function of collector current for $V_{dc}$ =500V                                           |       |

| Figure 7-11 Switching energies as function of junction temperature for $I_c=6A$                                           |       |

| V <sub>dc</sub> =500V                                                                                                     | 98    |

| Figure 7-12 Switching times as function of junction temperature for $I_c=6A$                                              | and   |

| $V_{dc}$ =500V                                                                                                            |       |

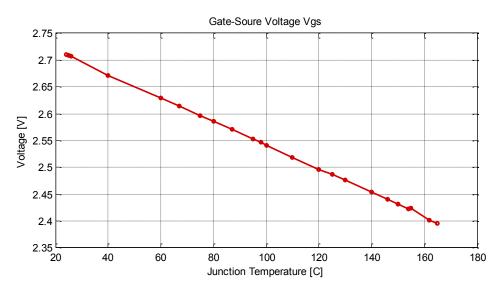

| Figure 7-13 Gate voltage as a function of temperature                                                                     |       |

| Figure 7-14 On-resistance as function of temperature<br>Figure 7-15 I-V Characteristics for $T_j=27$ °C and $V_{GS}=2.7V$ |       |

| Figure 7-16 I-V characteristics for $T_{case}=150$ °C                                                                     |       |

| Figure 7-17 On-state voltage as function of temperature for $I_c=4.05A$                                                   |       |

| Figure 7-18 BJT I-V characteristics                                                                                       |       |

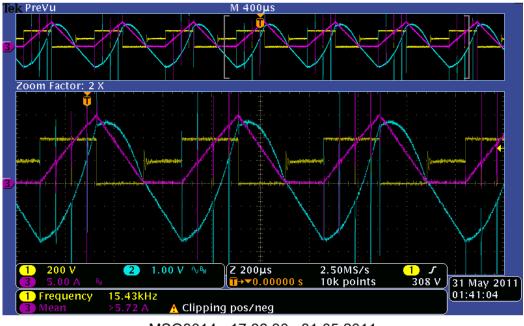

| Figure 7-19 CCM boundary check $V_{in}$ =500V R <sub>o</sub> =97 $\Omega$                                                 | 105   |

| Figure 7-20 DCM $V_{in}$ =500 $R_0$ =217 $\Omega$ .                                                                       |       |

| Figure 7-21 Stability check, $V_{in}$ =250V R <sub>o</sub> =29.5Ω                                                         | 106   |

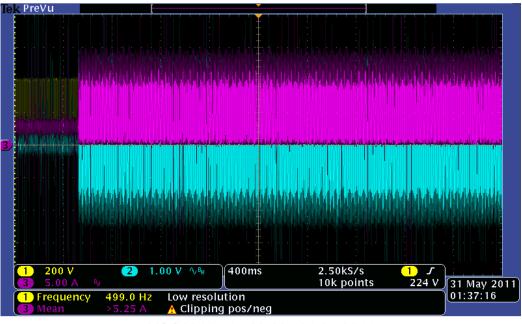

| Figure 7-22 Step in load to the left and drop in load to the right, $V_{in}$ =500V R <sub>0</sub> 0=                      |       |

| $R_0 1=30\Omega$ .                                                                                                        |       |

| Figure 7-23 Converter input current $V_{in}$ =250 R <sub>o</sub> =59                                                      |       |

| Figure C-1 Relationship between current magnitude and cross section [59]                                                  |       |

| Figure D-1 Gate driver and DC/DC converter connections for JFET half bridge                                               |       |

| Figure D-2 JFET PCB top layer                                                                                             |       |

| Figure D-3 JFET PCB bottom layer                                                                                          |       |

| Figure D-4 BJT PCB top layer                                                                                              |       |

| Figure D-5 BJT PCB bottom layer                                                                                           |       |

| Figure D-6 Topp layer                                                                                                     |       |

| Figure D-7 Bottom layer                                                                                                   | . 128 |

| Figure F-1 Turn-on JFET with $I_d=10A$ and $V_{dc}=200V$ , $I_d$ is green and $V_{DS}$ is ye                              |       |

| Peak current is equal to 21A "Voltage shifted 6.5ns"                                                                      | . 132 |

| Figure F-2 Turn-on JFET with $I_d$ =10A and $V_{dc}$ =565V, $I_d$ is green and $V_{DS}$ is ye                             | llow. |

| Peak current is equal to 28A "Voltage shifted 6.5ns"                                                                      |       |

|                                                                                                                           |       |

| Figure F-3 JFET turn-off with DC voltage of 300V, $I_d=6A$ to the left and 20A t    |     |

|-------------------------------------------------------------------------------------|-----|

| right                                                                               | 133 |

| Figure F-4 JFET turn-off with DC voltage of 500V, 150µH air coil to the left and    | 1mH |

| coil with iron core to the right. "Voltage shifted 6.5ns"                           | 133 |

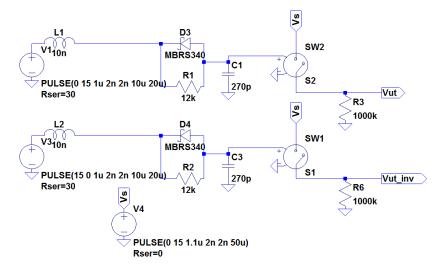

| Figure G-1 Model for investigation of soft switching                                | 134 |

| Figure G-2 Model for investigation of the dead time generation.                     | 134 |

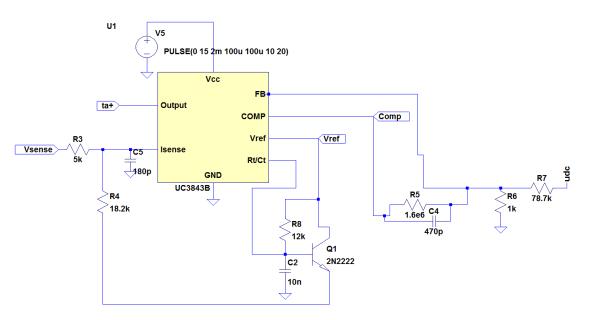

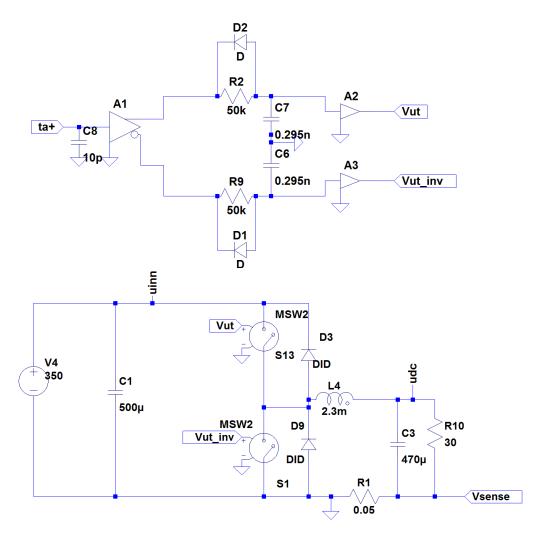

| Figure G-3 Controller circuit                                                       | 135 |

| Figure G-4 Model of Buck converter                                                  | 135 |

| Figure G-5 Model of SBC, the upper circuit generates the complementary outputs .    | 136 |

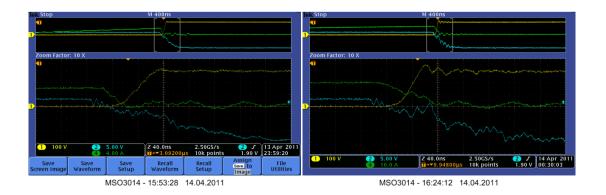

| Figure H-1 Vin=250V to the left and Vin=350V to the right                           | 137 |

| Figure H-2 V <sub>in</sub> =400V to the left and V <sub>in</sub> =450V to the right | 137 |

| Figure H-3 V <sub>in</sub> =500V                                                    | 137 |

| Figure H-4 Step load response                                                       | 138 |

| Figure H-5 Output waveforms after the step load                                     | 138 |

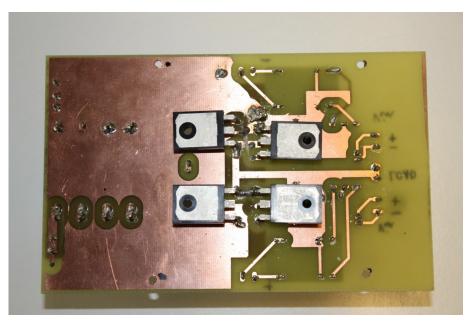

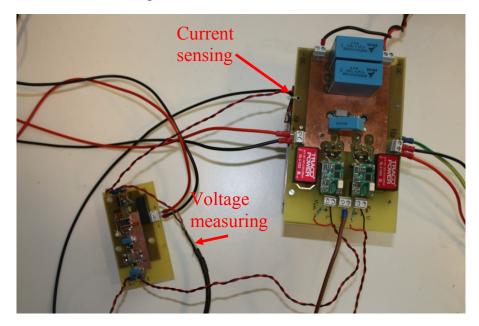

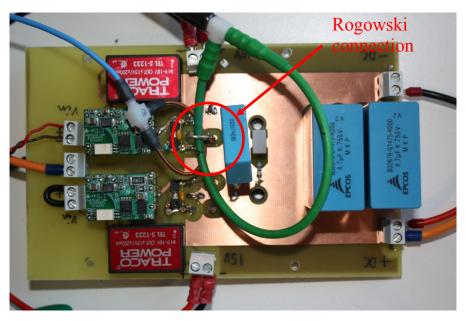

| Figure I-1 Picture of lab setup                                                     | 139 |

| Figure I-2 Bottom side of JFET PCB                                                  | 139 |

| Figure I-3 Side view of BJT PCB                                                     | 140 |

| Figure I-4 Connection of control board                                              | 140 |

| Figure I-5 Connection of Rogowski coils                                             | 140 |

## List of Tables

| Table 1-1 Drive specification                                                                   |           |

|-------------------------------------------------------------------------------------------------|-----------|

| Table 2-1 Problems regarding construction of semiconductors for high temperatu                  | res 17    |

| Table 3-1 Wide bandgap material properties in comparision with silicon [20]                     | 19        |

| Table 3-2 Comparison of some of the electrical and material properties of Si, 6                 | 6H-SiC,   |

| and 3C-SiC for power device applications                                                        | 20        |

| Table 3-3 Ratio between specific drift region resistance                                        |           |

| Table 3-4 Driving requirements for SJEP120R063 T <sub>j</sub> =25 °C and T <sub>j</sub> =150 °C |           |

| Table 3-5 Driving requirements for BT1220AC and BT1206AC                                        |           |

| Table 3-6 Driving requirements for CMF20120D                                                    | 29        |

| Table 3-7 Driving requirements for IKW15T120                                                    | 30        |

| Table 3-8 Total inverter losses and efficiencies                                                | 31        |

| Table 4-1 Self inductance of a 8 cm long loop                                                   | 35        |

| Table 4-2 Converter ratings and operation conditions                                            | 48        |

| Table 4-3 Filter requirements                                                                   | 49        |

| Table 5-1 Measuring equipment accuracy                                                          | 64        |

| Table 5-2 Instrument archive                                                                    | 64        |

| Table 7-1 BJT threshold voltage                                                                 | 103       |

| Table 7-2 Parameters for calculations of inverter losses                                        | 104       |

| Table 7-3 Calculated inverter efficiencies                                                      | 104       |

| Table 7-4 The table shows the measured peak-to-peak voltage ripple for d                        | lifferent |

| operation conditions                                                                            |           |

| Table B-1 Parameters for SJEP120R063                                                            |           |

| Table B-2 Parameters for CMF20120D                                                              | 118       |

| Table B-3 Parameters for IDH15S120                                                              | 118       |

| Table B-4 Parameters for BT1220AC                                                               | 118       |

| Table B-5 Parameters for IKW15T120                                                              | 118       |

| Table C-1 Minimum spacing between traces, IPC 2221 standad                                      | 119       |

| Table E-1 BOM for JFET half-bridge                                                              |           |

| Table E-2 BOM for BJT half-bridge                                                               | 130       |

| Table E-3 BOM for control board                                                                 | 131       |

| Parameter | Explanation                       |

|-----------|-----------------------------------|

| SBC       | Synchronous Buck Converter        |

| SPWM      | Sinusoidal Pulse Width Modulation |

| PWM       | Pulse Width Modulation            |

| LED       | Light Emitting Diode              |

| BOM       | Bill of Materials                 |

| СТЕ       | Coefficient of Thermal Expansion  |

| JFET      | Junction Field Effect Transistor  |

| BJT       | Bipolar Junction Transistor       |

| PCB       | Printed Circuit Board             |

| DR        | Design Rules                      |

| ССМ       | Continuous Conduction Mode        |

| DCM       | Discontinuous Conduction Mode     |

| DPT       | Double Pulse Test                 |

| DUT       | Device Under Test                 |

| DDCC      | Direct Duty Cycle Control         |

| SiC       | Silicon Carbide                   |

## Abbreviation

## **1** Introduction

### 1.1 Problem background and motivation

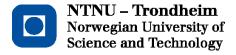

Large parts of the "easy" accessible oil and gas reserves are already discovered and exploited. To discover and access future reservoirs in a profitable manner, new technology is required. Electrification of down-hole applications have proven to be very promising, especially for exploitation of deep offshore reservoirs. Many of the processes which have been mechanically or hydraulically powered in the past are now starting to be electrified. Some of these applications are drilling motors, subsurface valves, progressive cavity pumps, intervention tools, etc. Figure 1-1 shows an overview of a possible down-hole system.

Figure 1-1 Oil and gas recovery system

The harsh environment for the power electronics with both high pressure and high temperatures demands new technologies for both control electronics and power stages. Depths of several kilometers into the sea bed are often experienced for such equipment. Temperatures increase by 15-30 °C/km, and the ambient temperature for the most extreme environments exceeds 200 °C. For down-hole operation to be successful one need to have motor drives which can operate reliably at these elevated temperatures.

Hybrid vehicles are another promising application area for high temperature motor drives. The performance and required motor size of a car are closely related to the cars size and weight. Hence, it is beneficial to reduce the weight. The cooling system for the semiconductors contributes to increased costs and weight. Converters for today's hybrid motor are based on IGBTs. Due to the high temperature on the cooling liquid of the combustion engine, the semiconductors need a separate cooling system. By introducing

Silicon Carbide (SiC) transistors and high temperature motor drives, the converters can use the same cooling system as the combustion engine [1]. This will greatly reduce both the cost and the weight of future hybrid vehicles.

Space craft and military industries have been a driving force for development of Silicon Carbide materials and high temperature electronics [2]. The fact that SiC can operate at higher temperatures and higher switching frequencies than Si [3, 4] gives a large reduction of heat sinks and passive components. Reduced size means reduced weight, and weight is one the most crucial factors when it comes to space travelling. Hence, NASA and other space explorers will benefit from the development of high temperature SiC converters.

This work is a preliminary study of Silicon Carbide converters for high temperature operation. Commercial available enhancement mode SiC transistors have been studied and two different transistors have been implemented in converters in. Inverters for high temperature operations are presented in [5, 6]. In [5] the main focus is on the packaging and the selected transistors are normally-on JFETs. [6] presents a 4kW Multi Chip Power Module (MCPM) which can operate at temperatures up to 300 °C. Large parts of the research on this topic is based on custom made packaging and non commercial transistors. In this work the focus is more directed against what can be made by using the available discrete SiC devices.

### **1.2 System description and scope of work**

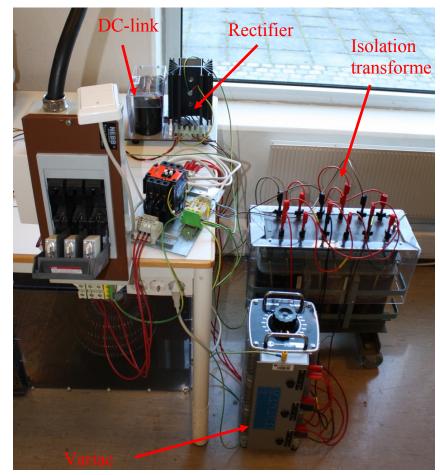

SmartMotor is working in cooperation with Badger Explorer to develop a motor drive for down-hole drilling. The concept of Badger Explorer is given in their web page: "The Badger Explorer, a new formation and reservoir evaluation tool which drills into the underground without the risks, cost and complexity of drilling an exploration well with a rig." So the idea is to replace costly drilling rigs with an autonomous drilling machine which is powered with a DC cable. The drilling tool seals the hole behind it as it travels into the sea bed, and when the job is done the cable is cut and the tool is left buried. More information of the system can be found at [7].

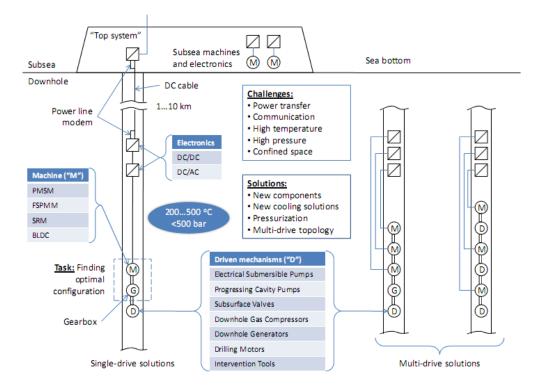

The required specifications of the drive are given in Table 1-1. The drilling motor, which the drive is controlling, is a three phase permanent magnet radial flux machine. For the desired voltage and current levels the best selection of converter topology is a three phase full-bridge inverter, see figure Figure 1-2. Motors are much more robust than the power electronics, when concerning high temperatures. Hence, the largest challenge is to design the power stage of the converter and its drive circuitry.

| 0 V<br>10 A                                        |

|----------------------------------------------------|

| 10 A                                               |

|                                                    |

| kHz                                                |

| 5 °C                                               |

| $_{c}$ is the DC-link voltage                      |

| is the rms value of the fundamental output current |

| is the switching frequency                         |

| <sub>mb</sub> is the down-hole ambient temperature |

|                                                    |

Table 1-1 Drive specification

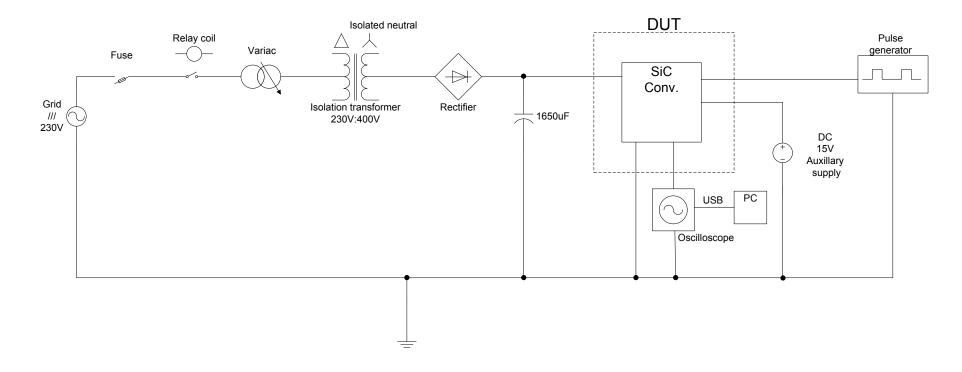

One of the first steps when designing converters for high temperature is to find appropriate power transistors. Due to the limitations at high temperatures for regular Silicon [8] it was decided to look into the new Silicon Carbide technology. A threephase inverter is basically three bridge legs, also called half-bridge converters, connected in parallel. It is therefore a good start to first design a successful bridge leg, before building the complete inverter.

The goal of this thesis is to design and test two half-bridge converter using two different types of SiC transistor. The converters should meet the electrical specification given in Table 1-1. It is both difficult and expensive to get hold on ICs, small signal transistors and capacitors for high temperature operation. Hence, the gate drivers and control electronics used in this work are designed for normal operation temperatures (80 °C). Nowadays, all motor drives are implemented with digital control. Programming of DSP and FPGA controllers are both challenging and time consuming. This work focus on the hardware and analog control will be used for controlling the half-bridge. The half-bridge will be operated either as a step down converter or as a Synchronous Buck Converter (SBC).

Figure 1-2 Three-phase inverter [9].

Most focus has been put on converter design considerations, both for bridge configurations in general and for SiC transistors in spesific. The new SiC transistors have different driving requirements than the well-known Silicon IGBT, which is used in most motor drives. Also, the dynamic behavior is very different form the one seen in IGBTs. This work treats the challenges which arise when replacing Si IGBTs or MOSFETs with SiC transistors. Especially, the influence of parasitic will be investigated closely. The work focuses on the application of semiconductor devices. However, and understanding of the semiconductor physics is necessary for an optimal design. From a control point of view normally-off transistors are preferred over normally-on devices. Hence, only enhancement mode SiC transistors will be considered in the thesis.

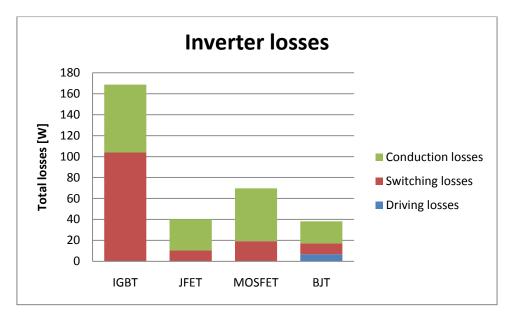

SiC devices have both lower on-state voltage and lower switching losses than comparable Si devices. It is therefore of interest to investigate what could be achieved by replacing Si transistors with SiC transistors. A theoretical comparison of the inverter losses for the two technologies will therefore be performed.

### 1.3 Report outline

This chapter has presented the motivation for looking into converters for high temperature motor drives. The scope of work and the system description have also been presented. Chapter 2 presents most of the theory which the report is based on. The theoretical properties of SiC are described in chapter 3. A theoretical loss comparison between a state-of-the-art IGBT and available SiC transistors are also performed. Chapter 4 describes the half-bridge converters designed, including layout consideration and driver selection. The design and tuning of an analog controller, for the half-bridge, is presented in the last sections of this chapter. The laboratory setup and the measuring equipment used for testing the converters are presented in chapter 5. A description of the experimental standard and principles are also given. Some initial measurements are given at the end of the chapter. These measurements are analyzed in chapter 6 by the use of the simulations program LTspice. The simulation program is also used to identify the influence of parasitic circuit elements on transistor switching waveforms. The results from the double pulse testing and from the on-state voltage measurements are presented in chapter 7. This chapter also includes verification of the performance of the step down converter. A brief conclusion followed by topics for further research is presented in chapter 8.

Matlab codes for calculation of switching losses and inverter losses are provided in appendixes. The PCB layouts and full Bill of Materials (BOM) for the converters are provided in appendix D and E respectively. The appendixes also include the simulation models and some additional measurements from the converter testing. Finally, some pictures of the laboratory setup and the converters are given.

Parts of the theory presented here is based on the background study performed in the specialization project [10]. To achieve complete substance of the thesis, some of the work from the specialization project is repeated. It is remarkable how fast the Silicon Carbide industry is developing. Some statements, from specialization project, regarding the production of SiC devices are no longer valid and large parts of chapter 3 had to rewritten before it could be presented.

## 2 Background and Theory

This chapter gives a short introduction of the convert topologies which are used in this work. Some useful equations which are used for design consideration and efficiency calculations are also presented. The challenges which arise at elevated temperatures are presented in the last section as an introduction to the Silicon Carbide chapter.

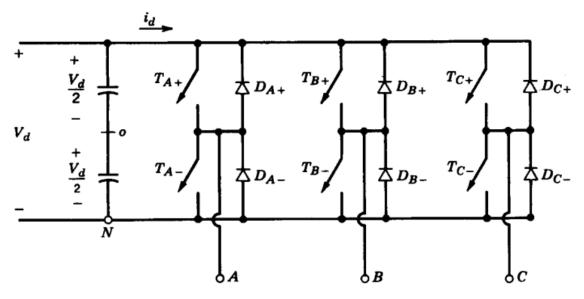

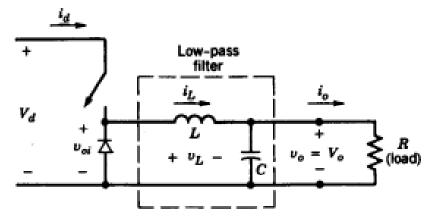

### 2.1 Step down converter

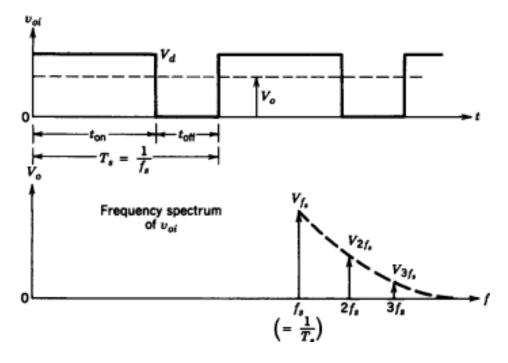

A step down converter, also called Buck converter, is a basic DC to DC converter, which produces an output voltage which is lower than the input voltage. Figure 2-1 shows the principal schematic of the converter. The reverse diode voltage is shown in Figure 2-2. The output filter of the converter acts as a low pass filter and filters out the ripple components of the switching voltage. This makes it possible to produce a DC output voltage.

Figure 2-1 Step down converter with resistive load [9]

Figure 2-2 Output waveforms of Buck converter [9]

Figure 2-3 Inductor voltage and current assuming continuous current [9]

The relationship between the input and output voltage of the converter can be derived by considering the inductor voltage shown in Figure 2-3. In stationary operation, the integral of the inductor current needs to be zero. This can be showed by equation (2.1), since the inductor current has the same magnitude at the start and the end of each switching period.

$$v_L = L \frac{di}{dt} \tag{2.1}$$

By performing the integration, of the inductor voltage over one switching period, the relationship between input voltage  $(V_i)$ , output voltage  $(V_o)$  and the duty cycle (D) can be found. When operating in continuous current mode the equation becomes:

$$V_o = V_i D \tag{2.2}$$

Where D is defined as the ratio between the on-time of the switch and the length of the switching period,  $D=t_{on}/T_s$ .

If the load gradually decrease the boundary between continuous- and discontinuous current is found at a boundary current  $I_{LB}$ . At the boundary the inductor current reaches zero amps at the end of the switching period. The value of the boundary current is therefore given by:

$$I_{LB} = \frac{1}{2}i_{L,peak} \tag{2.3}$$

An expression for  $i_{L,peak}$  can be found by integrating both sides of equation (2.1) from zero to  $t_{on}$ . If the output voltage is kept constant, then the boundary current is given by:

$$I_{LB} = \frac{V_o T_s}{2L} (1 - D)$$

(2.4)

The boundary current is increasing with decreasing duty cycle, hence the lowest duty cycle will be dimensioning for the output inductor.

### 2.2 Half bridge converter

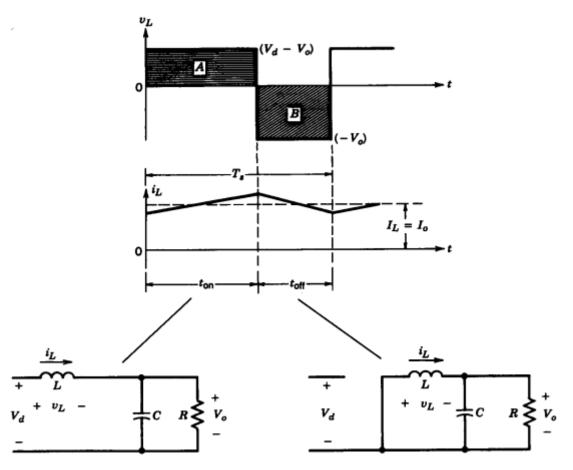

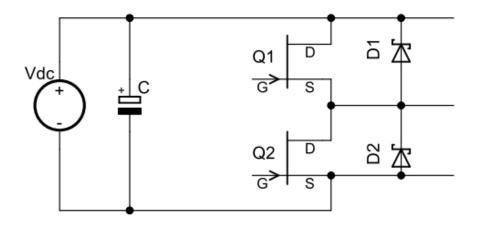

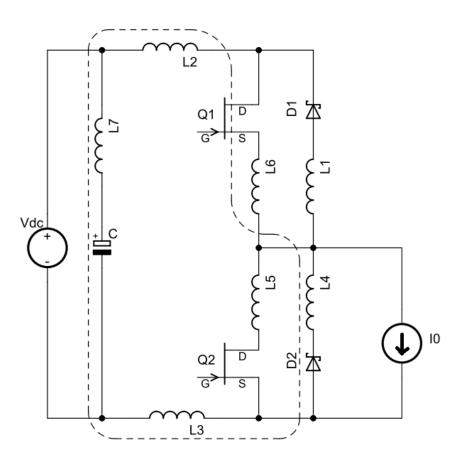

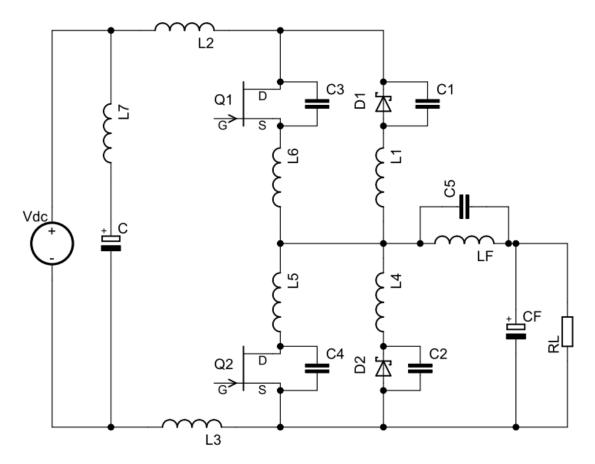

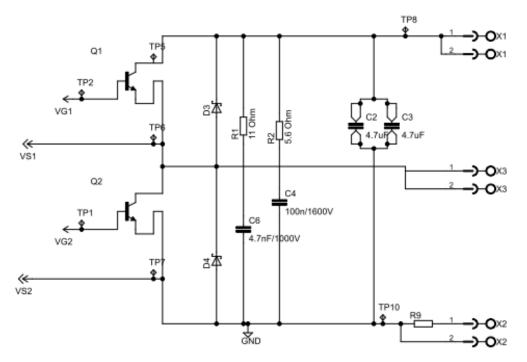

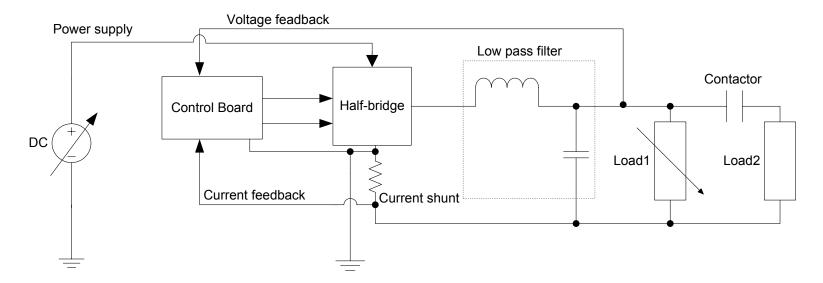

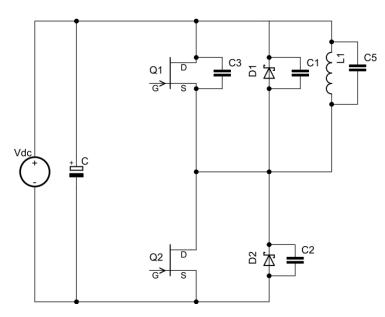

Figure 2-4 shows a principal drawing of a half-bridge converter. It consists of two transistors and two freewheeling diodes. The converter can operate as a single phase inverter by means of Sinusoidal Pulse Width Modulation (SPWM) or it can operate as a DC to DC converter. A description of the SPWM operation is given in section 2.4.2. If one of the transistors is kept off and the other is switching, then the setup can be used as a step-down converter by connecting a low pass filter across the diode which is opposite of the switching transistor. A half-bridge can also be operated as a synchronous Buck converter, which is an improved version of the Buck converter. A SBC uses a transistor instead of the freewheeling diode. By selecting an appropriate transistor, the freewheeling conduction losses can be greatly reduced. To operate the half-bridge in Figure 2-4 as a SBC; the low pass filter and the load is connected across D2. Q1 acts as the main transistor and Q2 as the freewheeling transistor. The converter controller must have a complementary output signal, which means that Q1 conducts when Q2 is off and opposite. The freewheeling diode D2 does only conduct during the short blanking time when both transistors are off. D1 will conduct if the inductor current goes negative. A description on how to generate the blanking time and how to obtain complementary control outputs are given in the next subchapter.

Figure 2-4 Half bridge converter

### 2.3 Gate drivers for bridge applications

When designing gate drivers for bridge configurations extra care must be taken, due to floating potentials and the risk of shorting the DC-link. It is common to refer the logic level control signals to ground. If the drivers are floating it is therefore required to use

signal isolation to avoid connecting together nodes with different potential. The output voltage of gate drivers are usually referred to the source potential of the transistors they are controlling. In bridge configuration the source voltage of the upper transistor jumps in potential when the lower is switching, thus signal isolation is required. If the DC-link voltage is generated by a rectifier and the negative potential of the DC-link is not grounded, then also the lower driver can be floating. The above arguments are also valid for the power supplies of the drivers, and the supply of the upper transistor must be isolated from ground. In general, all control circuits are electrically isolated from the drive circuit to prevent the high voltage of the power stage to enter the control circuit [11]. If both the upper and the lower transistor in a bridge leg is on at the same time, then the DC-link is shorted and an excessive current will flow. This phenomenon is called a shoot trough and a logic circuit must be added in the controller to prevent it. A shoot through can also occur if one of the transistors is turned on by noise. Hence, the gate drivers should be designed to provide high noise immunity.

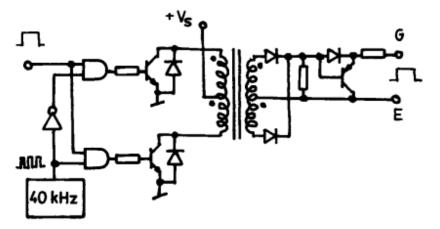

#### 2.3.1 Signal and power isolation

There are basically three ways of obtaining signal isolation, either by optocouplers, fiber optics or transformers [9]. Optocouplers and fiber optics transfer the signal by means of light produced by a Light Emitting Diode (LED). Fiber optics are more noise immune than optocoupler and they can provide very high isolation voltage and large creepage distances [9]. The advantage of opto-isolators is that they can transmit pulses of any duty cycle. On the other hand, they always require a power supply on the output side and they are somehow slower than isolation transformers. If the circuit is designed properly, isolation transformers can be used to transfer both signal and power. This is a major advantage over optocouplers. As a standalone component pulse transformers have a maximum duty cycle around 0.5, due to the requirement that the volt-seconds across the windings must balance. The duty cycle limitation can be overcome by using a high frequency square wave carrier to modulate the drive signal [11]. Figure 2-5 shows an example of such circuit; here the signal is restored by rectifying the pulses on the secondary side of the transformer.

Figure 2-5 Carrier modulated transformer isolated drive circuit [11]

As described, all optical coupled and some transformer coupled drivers require a DCsupply on the output side. For the upper driver these have to be isolated. The two most popular ways of generating the DC voltage, are by use of auxiliary supplies or bootstrap supplies. The auxiliary supplies can be made by connecting a transformer, with several secondary windings, to the mains and rectifying the outputs. Isolated high frequency DC/DC converters can also be used. They can be made much more compact, since the transformers are designed for high frequencies. A bootstrap supply can be used if the power required by the driver is very small. Figure 2-6 shows a simple circuit where the upper driver has an isolated bootstrap supply and the lower is supplied by an auxiliary DC source. The diode and the resistor act as a charge pump, and every time the lower transistor turns on, current flows from the lower supply charging the upper capacitor. When the upper transistor is on, the capacitor supplies the driver with the required energy, until the next time the lower transistor turns on, and the capacitor recharges.

Figure 2-6 Bootstrap auxiliary supply [11]

#### 2.3.2 Dead time calculation

The turn-off time of a transistor is usually different form the turn-on time. There are also differences in the propagation delay, of a gate driver, for turn-on and turn-off. Hence, the turn-on signal to one driver cannot be given at same time as the turn-off signal is given to the other. To avoid shoot through in a bridge configuration some "dead time" has to be added in the controller. The "dead time" is defined as the time from one of the gate drivers gets the turn off signal to the other gets the turn on signal. There are basically two types of dead time, one which is implemented in the controller as described above and one effective dead time where both of the transistors is off. The effective dead time is also called the blanking time. The blanking time is often a large fraction of the dead time since the controller dead time is calculated based on worst case considerations. During the blanking time, the output voltage is determined by the direction of the output current and not by the control signal. This introduces nonlinear effects and can case instability in some cases if the blanking time is too long.

The control dead time should be selected such that the blanking time always is positive, but not unnecessarily long. The controller dead time can be calculated from the following equation [12]:

$$t_{dead} = \left[ (t_{off,max} - t_{on,min}) + (t_{pdd,max} - t_{pdd,min}) \right] \cdot 1.2$$

(2.5)

Where,  $t_{off,max}$  and  $t_{on,min}$  are the respective maximum turn-off and turn-on time of the transistors for any possible operating condition.  $t_{pdd,max}$  is the maximum propagation delay of the driver at turn-off and  $t_{pdd,min}$  is the minimum propagation delay of the driver at turn-on. The factor of 1.2 is added to have some additional safety margin. A procedure for measuring the switching times is described in section 5.1.

Figure 2-7 shows an example of analog dead time generation for a half-bridge. The control signal is applied to A1 which is a buffer with complementary outputs. Complementary outputs means that one of the terminals has an inverting output while the other has a non inverting output. In a bridge configuration, A2 is connected to the upper gate driver and A3 to the lower. Assume that A3 initially is on and that the lower transistor is conducting, and then a positive signal is applied to the input terminal of A1. This results in a logic high voltage at the upper non inverting terminal and a logic low at the inverting terminal. The capacitor C5, which is charged initially, will quickly discharge through the diode D1 and A3 turns off when voltage over the capacitor is reduced under the threshold voltage.

For the upper branch, the voltage over the capacitor C2 is initially zero. When a positive voltage is applied the capacitor starts to charge through the resistor R4. After some time the voltage over the C2 reaches the threshold of A2 and the upper gate driver gets its on signal. The controller dead time is basically the charging time of the capacitor from zero voltage up to the threshold of A2.

Figure 2-7 Dead time generation circuit

If one assumes that the output voltage of A1 is a step response with amplitude equal to  $V_o$  and the capacitor voltage is denoted by  $V_{cap}$ , then the dynamic equation describing the circuit can be written as:

$$V_o = CR \frac{dV_{cap}}{dt} + V_{cap} \tag{2.6}$$

By using laplace transform followed by partial fraction decomposition and inverse laplace the time response can be found.

$$V_{cap}(t) = V_o(1 - e^{-\frac{t}{RC}})$$

(2.7)

The required time constant,  $\tau$ =RC, is found by setting V<sub>cap</sub>(t<sub>dead</sub>)=V<sub>threshold</sub>, where V<sub>threshold</sub> is the threshold voltage of A2 and A3.

### 2.4 Inverter losses

The losses in a inverter consists of driving power for the transistors, conduction and switching losses of transistors and diodes, losses in the output filter and ESR losses in the DC-link capacitor. This section focus on semiconductor related losses, and an analytical expression of the losses in a three phase inverter is presented.

#### 2.4.1 Driver losses and required driver power

When calculating converter losses, also driving losses should be included. To be able to dimension the power supplies of driver circuits, the required output power and driver losses must be known. Figure 2-8 shows the principle connection of a driver. The internal resistance of the driver,  $R_{int}$ , often changes when the output changes from on to off.

Figure 2-8 Principle driver connection

The power supplied by a driver circuit can be divided in two parts; power for charging the input capacitors and power for supplying a continuous base/gate current. The charging power is given by [13]:

$$P_{charge} = V_{DRV} Q_G f_{DRV} \tag{2.8}$$

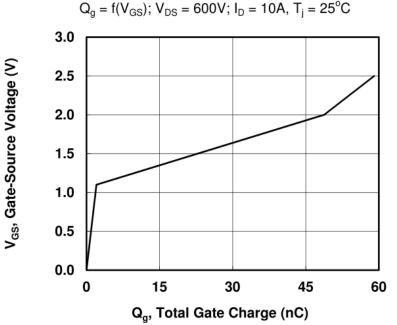

Where  $V_{DRV}$  is the amplitude of the applied gate drive voltage,  $f_{DRV}$  is the frequency of the drive signal and  $Q_G$  is the charge required to charge the input capacitance,  $C_{ISS}$ , of the device.  $Q_G$  is the integral of the gate current during turn-on or turn-off of the transistor.

$Q_G$  is a function of the applied gate voltage and it is also slightly dependent on DC-link voltage. The value of  $Q_G$  can usually be found by reading from the gate charge characteristic in the data sheet of the transistor. If the curve is omitted, the value of  $Q_G$

can be estimated by using the input capacitance of the transistor. Equation (2.9) from [14] gives a good estimation.

$$Q_G = k_c C_{ISS} \left( V_{G(on)} - V_{G(off)} \right)$$

$$k_c = \frac{Q_{G(ds)}}{C_{ISS,ds} \left( V_{G(on,ds)} - V_{G(off,ds)} \right)}$$

(2.9)

$Q_{G(ds)}$  is the value specified in the data sheet and  $V_{G(on,ds)}$  and  $V_{G(off,ds)}$  are the applied gate voltages to obtain  $Q_{G(ds)}$ .

The most popular transistors of today, which are MOSFET and IGBT, do not require a continuous gate current. Among the SiC transistors, both normally-off JFETs and BJTs needs a continuous base/gate current. Both devices have a pn-junction between the gate and the source/emitter. The required on-state power is therefore equal to product of the base current ( $I_b$ ) and the forward voltage drop of the pn-junction ( $V_{fb}$ ) multiplied with the duty cycle.

$$P_{onstate} = I_b V_{fb} D \tag{2.10}$$

In motor drives the driver has to operate at duty cycles up to 100%. The driver supply usually can operate with some overload for a short period. It is therefore common to dimension the supplies for a duty cycle of 0.95. When calculating the inverter losses the average driver duty cycle must be used. The control signals to the transistors in a bridge leg are usually complementary. Hence, the average driver duty cycle over one fundamental period is equal to 0.5, when the effect of the dead time is neglected. The required power to drive a transistor is therefore given by:

$$P_{drive} = P_{onstate} + P_{charge} = V_{DRV}Q_G f_{DRV} + I_b V_{fb} \cdot 0.95$$

(2.11)

The conduction losses in the gate driver can easily be calculated by the following equation.

$$P_{cond} = I_b^2 (R_g + R_{int}) D \tag{2.12}$$

The driver losses are the sum of the charging power and the conduction losses. By summing  $P_{drive}(D=0.95)$  and  $P_{cond}(D=0.95)$  the size of the driver power supply can be found.

$$P_{drive,supply} = V_{DRV} Q_G f_{DRV} + 0.95 [I_b V_{fb} + I_b^2 (R_g + R_{int})]$$

(2.13)

The required average power is found by changing the duty cycle from 0.95 to 0.5 in the equations above.

# 2.4.2 Analytical expression of power losses in a voltage source converter with sinusoidal currents

All derivations in this section assume sinusoidal pulse-width modulation. Figure 2-9 shows an ideal single phase inverter operating under SPWM.

Figure 2-9 A single converter phase with sinusoidal pulse-width modulation [15]

The pulse pattern in sinusoidal pulse-width modulation is generated by comparing a sinusoidal reference voltage,  $v_{ref}(t)$ , with a triangular waveform,  $v_{tri}(t)$ . The upper switch in the bridge leg is on when the magnitude of the reference voltage is higher than the magnitude of the triangular waveform. The switching frequency is equal to the frequency of the triangular waveform and the amplitude of the sinusoidal output voltage of the convert is controlled by the amplitude of  $v_{ref}(t)$ . In normal converters it is not possible to access the midpoint of the DC-link, thus the output of a single half-bridge has a DC offset. When the load is connected between the midpoints of two half-bridge converters, operating under SPWM, the DC-bias is cancelled and only the AC component is left across the load. To obtain a three phase output one need three half-bridge modules and three separate reference signals to control them. The reference signals are obtained by sampling sinusoidal phase modulation functions.

$$m_{R}(\omega t) = M\cos(\omega t)$$

$$m_{S}(\omega t) = M\cos\left(\omega t - \frac{2\pi}{3}\right)$$

$$m_{T}(\omega t) = M\cos\left(\omega t + \frac{2\pi}{3}\right)$$

(2.14)

M is the modulation index and is given bellow

$$M = \frac{2\hat{U}_{(1)}}{U_{dc}} \quad M \in [0,1]$$

(2.15)

Where  $\hat{U}_{(1)}$  is the amplitude of the output fundamental phase voltage and  $U_{dc}$  is the value of the DC-link voltage. If M is smaller or equal to 1, this is called linear modulation mode of the inverter. All transistor and diode pairs in the inverter will have the same losses, due to symmetry. Therefore, it is sufficient to consider the losses in one transistor and one diode and then multiply the losses with six to get the full three phase inverter losses. The transistor T1 and diode D2 are considered in the following derivation. Depending on the required accuracy and the available data different analytical loss models can be used.

Two loss models presented in [15] are given in the following sections.

#### 2.4.2.1 Simplified linear approach

The first loss model is a simplified linear approach. This model is based on the following assumptions:

- Transistor and diode switching times as well as switching interlocking times are neglected

- The junction temperature is temporally constant

- Linear modulation of the converter

- The switching ripple in the output AC current is neglected

- The switching frequency is much larger than the AC output frequency.

The inverter losses are divided in on-state forward losses and switching losses.

#### **Conduction losses:**

By assuming a linear characterization of the on-state voltage of the diode,  $v_F(t)$ , and the transistor,  $v_{CEsat}(t)$ , their forward voltage can be expressed as:

$$v_{CEsat}(t) = V_{CE0} + r_{CE} \cdot \hat{i}_1 \sin(\omega t)$$

(2.16)

$$v_F(t) = V_{F0} + r_F \cdot \hat{i}_1 \sin(\omega t) \qquad (2.17)$$

Where  $V_{CE0}$  and  $r_{CE}$  are the threshold voltage and the on-state resistance of the transistor respectively.  $V_{F0}$  and  $r_F$  are the threshold voltage and the on-state resistance of the diode.  $\hat{i}_1$  is the peak value of the fundamental component of the output current. The value of  $V_{CE0}$  for unipolar transistors such as MOSFETs and JFETs is equal to zero. The on-state losses of the transistor T1 can be calculated according to

$$P_{fw,T1} = \frac{1}{2} \left( \frac{V_{CE0}}{\pi} \cdot \hat{\mathbf{i}}_1 + \frac{r_{CE}}{4} \cdot \hat{\mathbf{i}}_1^2 \right) + M \cdot \cos(\varphi)$$

$$\cdot \left( \frac{V_{CE0}}{8} \cdot \hat{\mathbf{i}}_1 + \frac{r_{CE}}{3\pi} \cdot \hat{\mathbf{i}}_1^2 \right)$$

(2.18)

Where  $\varphi$  is the phase angle between the fundamental component of the output voltage and current. The diode, D2, forward losses are given by:

$$P_{fw,D2} = \frac{1}{2} \left( \frac{V_{F0}}{\pi} \cdot \hat{i}_1 + \frac{r_F}{4} \cdot \hat{i}_1^2 \right) - M \cdot \cos(\varphi) \cdot \left( \frac{V_{F0}}{8} \cdot \hat{i}_1 + \frac{r_F}{3\pi} \cdot \hat{i}_1^2 \right)$$

(2.19)

From equation (2.17) and (2.18) one can see that conduction losses are dependent of the phase angle of the current. As the phase angle increases the diode losses increase and the transistor losses reduce. The reason is that the relative conduction time of the diode increases with reduced power factor. If  $\varphi$  is increased beyond 90°, the converter operates as a rectifier.

#### Switching losses:

The switching losses are sum of turn-on and turn-off losses of the transistors and the diodes. The turn-on losses of diodes are very small compared to the other losses, thus they can be neglected. By assuming that the switching losses are linearly dependent on the transistor/diode current they can be calculated from

$$P_{on+off,T1} = \frac{1}{\pi} f_s \left[ E_{on,T}(\hat{\mathbf{i}}_1) + E_{off,T}(\hat{\mathbf{i}}_1) \right]$$

(2.20)

$$P_{off,D2} = \frac{1}{\pi} f_s \cdot E_{off,D}(\hat{i}_1)$$

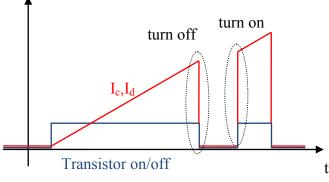

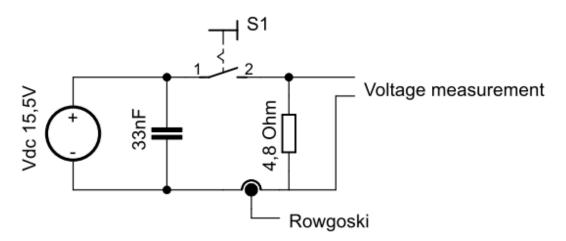

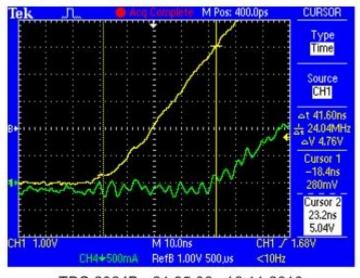

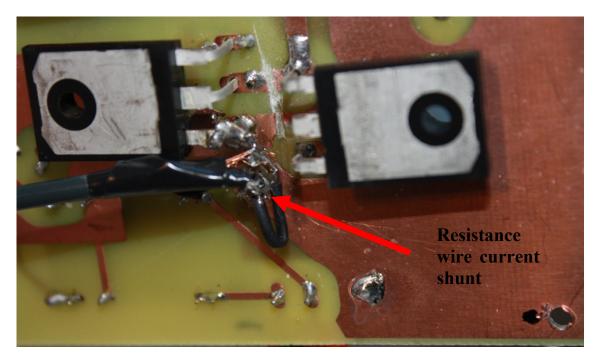

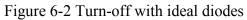

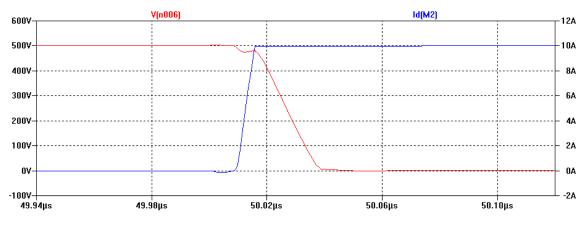

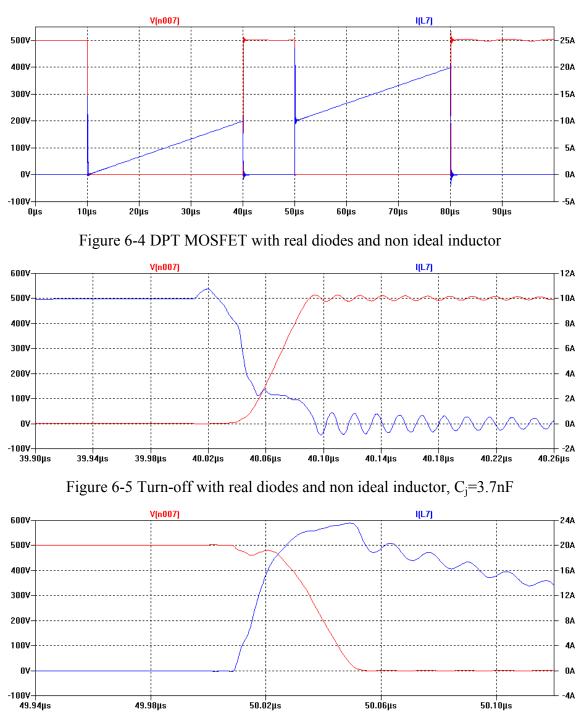

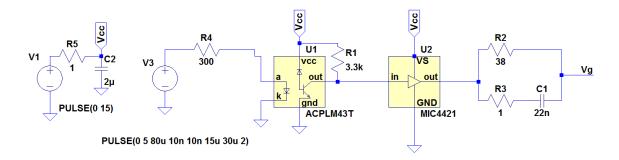

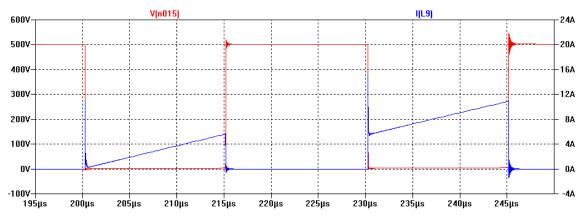

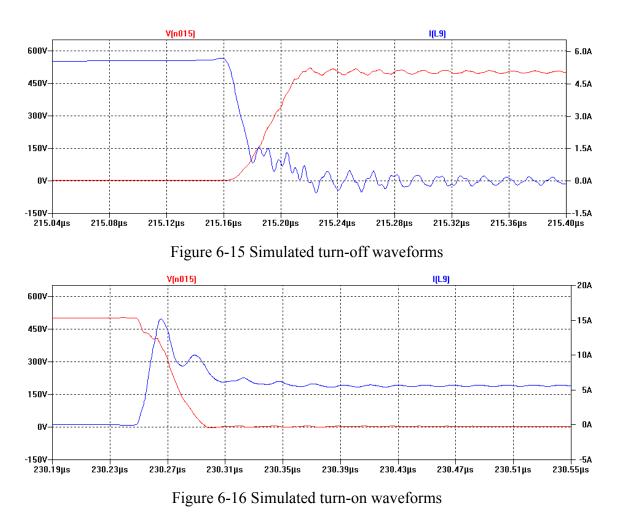

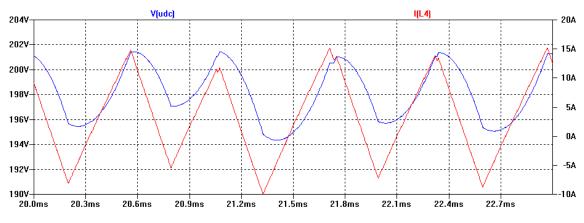

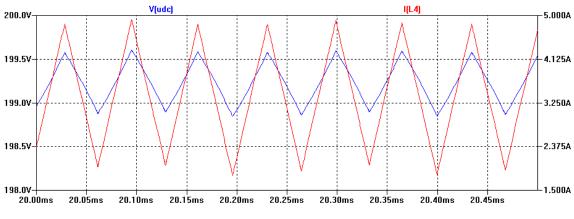

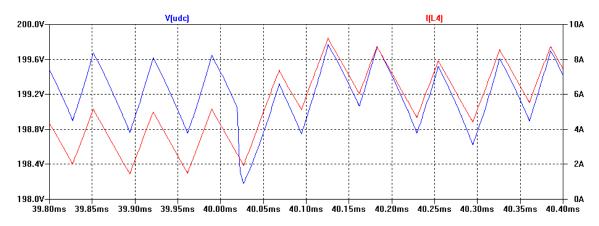

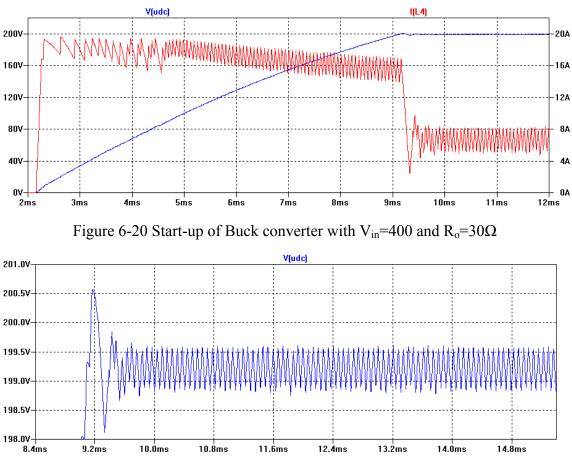

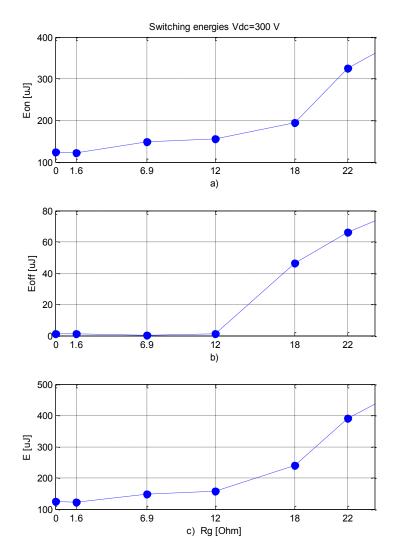

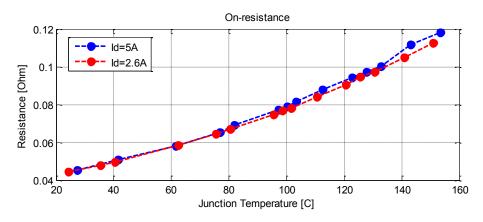

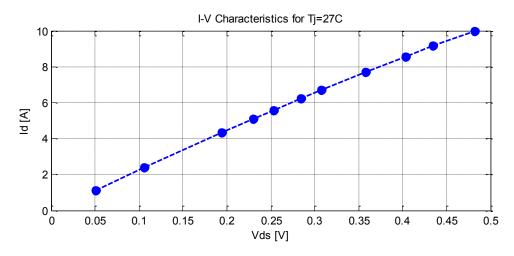

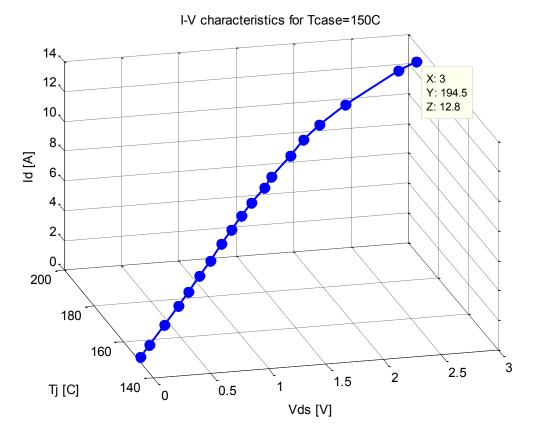

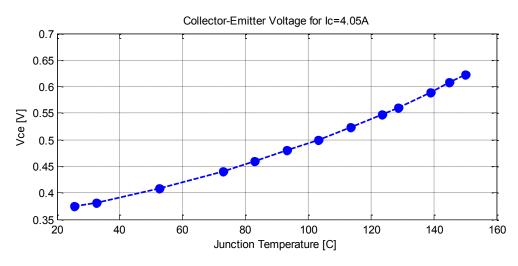

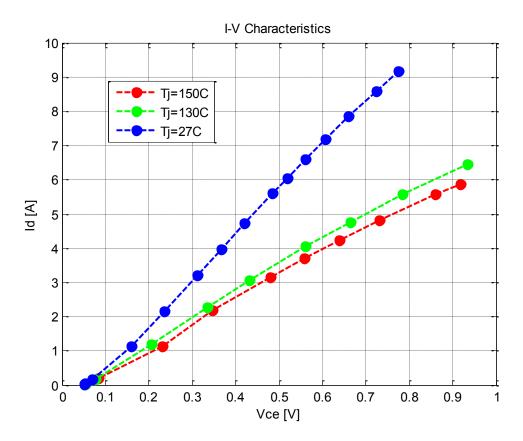

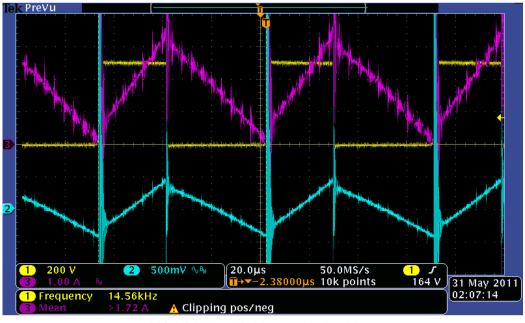

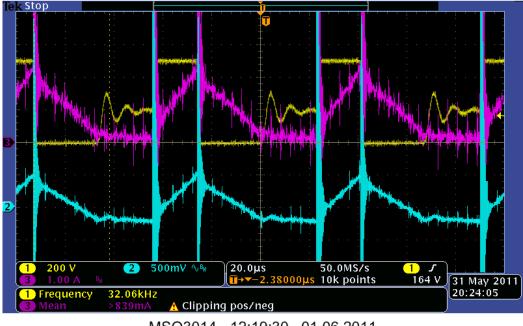

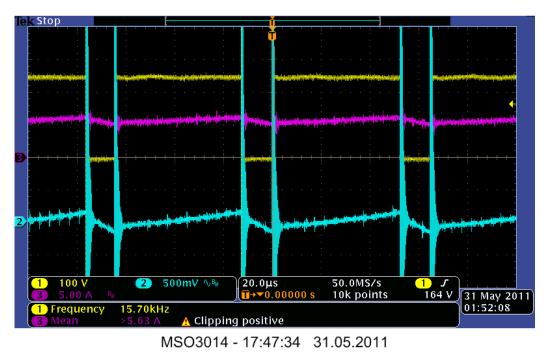

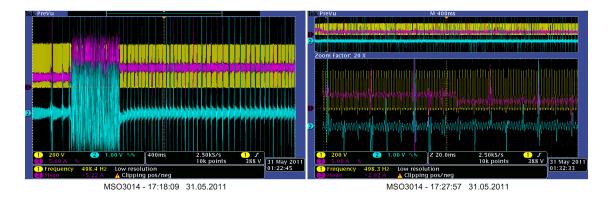

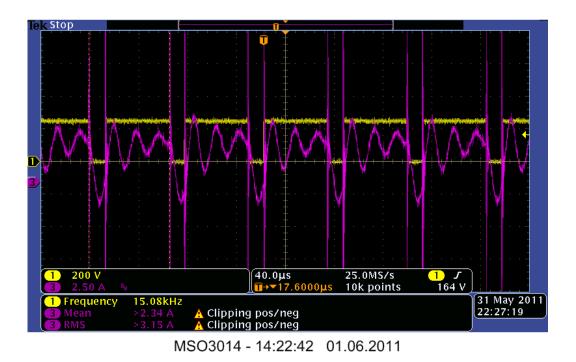

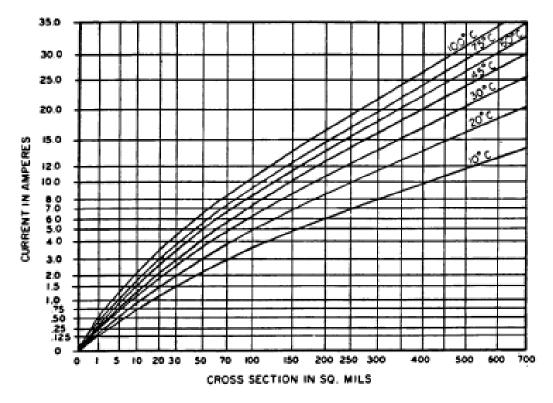

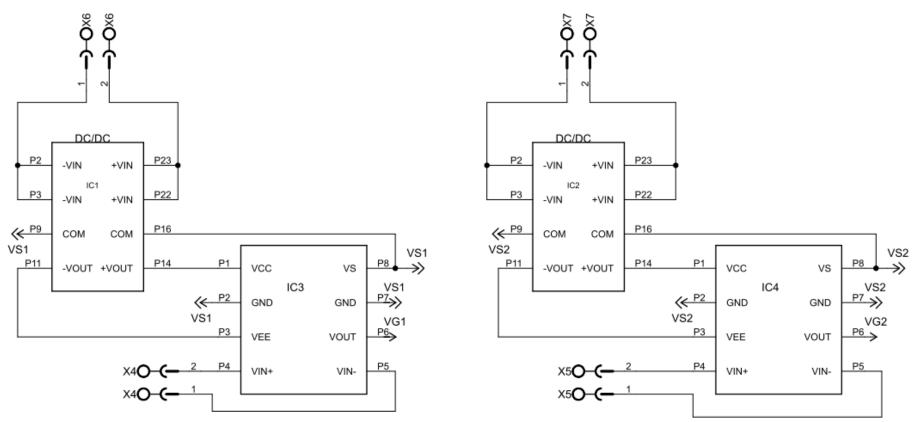

(2.21)