# Control of Power Electronic Converters in Distributed Power Generation Systems

Evaluation of Current Control Structures for Voltage Source Converters operating under Weak Grid Conditions

Tarjei Midtsund

Master of Science in Energy and EnvironmentSubmission date:July 2010Supervisor:Tore Marvin Undeland, ELKRAFTCo-supervisor:Jon Are Wold Suul, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

# **Problem Description**

The use of power electronic converters is continuously increasing, and especially the Voltage Source Converter topology is gaining widespread use as a modular topology for many different power system applications. Understanding the limits of stable control and operation for this converter topology is therefore important for interfacing renewable energy sources like wind power and photovoltaic power to the grid. The control performance for such converters is depending on the strategy for synchronization to the grid and is limited by the speed of the inner control loops. For traditional cascaded control systems, this means that the dynamics of the inner loop current controllers and of the grid voltage phase detection is of major importance to the limits for stable operation.

On this background, the objective of this study should be to investigate the dynamic performance and the influence of the inner current control loops on the stability of a Voltage Source Converter operating in a weak grid. The interaction with the synchronization method and the influence of the outer loop controllers should also be investigated from the starting point of the current controllers. The study can be divided into two main parts:

1. Investigation and comparison of the dynamic performance of different current control structures when a converter is operated in a weak grid. This first part of the study should assume balanced grid conditions, and can be based on previous work of the student in the Specialization course project. The operation and stability limits of the converter with the different current control strategies should be investigated by simulation when exposed to changes in active and reactive current references and disturbances in the grid voltage.

2. As a second step, strategies for synchronization to an unbalanced grid voltage should be implemented in the simulation models, and the investigated current control structures should be adapted for control of positive and negative sequence current components. The same investigations of operational characteristics and stability limits as described for balanced conditions should be systematically carried out with control structures adapted for operation under unbalanced grid voltages.

The simulation models should be implemented in the PSCAD/EMTDC simulation software and the description of the models should be supported by theoretical explanations and references to scientific literature. Relevant findings and observations should be illustrated by simulation results and explained with respect to the theoretical and mathematical background.

Assignment given: 09. February 2010 Supervisor: Tore Marvin Undeland, ELKRAFT

### Preface

Throughout the work with the master thesis, I have learned a lot. By doing theoretical background studies and then testing my computations by simulations. The study of the simulations has been a good way of understanding the nature of the electrical circuits and controller theory.

During my work with this master thesis there are a number of people I will like to address a great thank to, and who has been of mayor importance for me and my work. First of all I would like to thank Jon Are Suul for always taking the time to help me. He has been irreplaceable in solving my problems with the simulations program PSCAD, guiding me to helpful literature and giving me the inspiration to complete the master thesis. In addition he has been a great contributor for my first academic publication, which gave me the opportunity to travel all the way to China and participate in the IEEE 2nd international Symposium on Power Electronics for Distributed Generation System. Here I will also like to thank the department of Electric Power Engineering at NTNU and Statnett for the contribution that made it possible to participate in the conference.

I would also like to thank my supervisor Prof. Tore Undeland for his enthusiasm, ideas and inspiration and for being so understanding. He has always been quick to respond my emails, even on late Sunday evenings.

At last I would like to thank all the people who have helped me in the finishing of my thesis, both directly by reading and correcting, and for the social contribution during my work. Especially I would like to thank Øyvind Rui, Marie Midtsund, Johanna Roaldset and Martin Fløystad for both critical feedbacks on my work and by moral support during the last weeks, either over the phone or phase to phase.

Jaiji Midkund

Tarjei Midtsund

Trondheim, july 2010

iv

## Summary

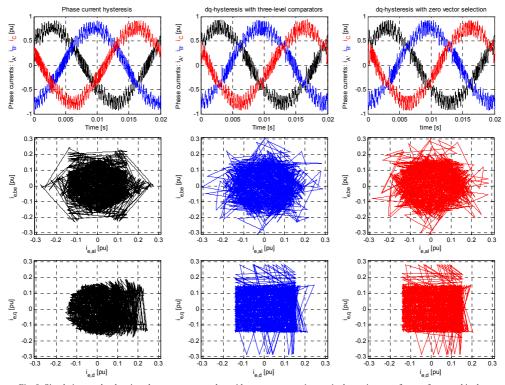

The performance of different current controller structures for Voltage Source Converters (VSC) under weak grid conditions caused by large grid impedance is investigated. The VSC is synchronized to the grid by a Phase Locked Loop (PLL). Current control techniques and PLL techniques for handling both symmetrical and asymmetrical conditions are presented and discussed. The investigated current control structures are; the conventional Proportional Integral (PI)-controller in the synchronous rotating reference frame, dual PI-controllers implemented in positive- and negative-sequence rotating reference frame, the Proportional Resonant (PR)-controller in the stationary reference frame, the phase current hysteresis controller, and a space vector base hysteresis controller in the synchronous rotating reference frame. The PLL-techniques used for synchronization are; a conventional synchronous rotating reference frame PLL, a PLL with notch filter, and a Decoupled Double Synchronous Reference frame PLL (DDSRF-PLL).

The different current control strategies and PLL-techniques are studied by simulations. The results show how large grid impedance can influence the dynamic response of the system and how the interaction between the PLLs, the current controllers and the large grid inductance can even trigger instability when the voltage measurements are highly influenced by the operation of the converter. The PI-controllers in the synchronous rotating reference frames are particularly sensitive to oscillations that can be reinforced when the measured voltage feed-forward terms are used in the control system. The response of the PR-controller is instead slowed down by the interaction with the PLL, while both the hysteresis controllers are quickly tracking the reference value as long as the interaction with the PLL is not leading to instability.

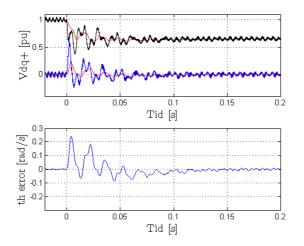

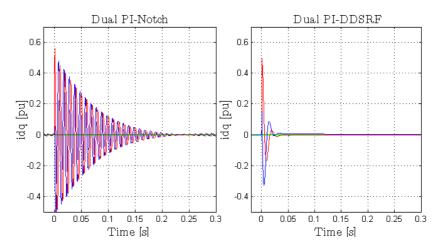

Operation under asymmetrical weak grid conditions are investigated for current controllers that exploit PLL techniques designed to remove the oscillations that occur in the positive sequence reference frame voltage during unbalanced grid voltage. The simulations show that the DDSRF-PLL has a shorter transient period than the PLL with notch filter, but with a small steady state 100 Hz oscillation under the weak asymmetrical grid conditions.

The results indicate that the tuning of the PLL is of large importance for the stability of the control system, and that a slower PLL can lead to less interaction with the current controllers at the cost of a slower and less accurate dynamic overall control performance.

## Sammendrag

Det er undersøkt ulike metoder for strømregulering av en spenningskildeomformer og hvordan disse oppfører seg i et svakt nett, forårsaket av en høy nettimpedans. Spenningskildeomformeren synkroniseres til nettet ved hjelp av en faselåst sløyfe (PLL). Strømregulerings- og PLL- metoder for å håndtere både symmetriske og asymmetriske forhold i nettet er presentert, undersøkt og diskutert. De undersøkte strømregulatorene er: En konvensjonell proporsjonal integrator (PI)-regulator i det synkront roterende referansesystemet, to doble PI-regulatorer implementer i positivt og negativt roterende referansesystem, proporsjonal resonans (PR)-regulator i stasjonært referansesystem, fasestrøm hysterese regulator i stasjonært referansesystem. PLL-metoden som er brukt for å synkronisere spenningskildeomformeren til nettet er: en konvensjonell synkront roterende referansesystem PLL, en PLL med notch-filter, og en PLL som kobler ut innvirkning mellom positiv og negativ sekvens (DDSRF-PLL).

De ulike strømreguleringsstrategiene og PLL-metodene har blitt studert ved hjelp av simuleringer. Resultatene viser hvordan en høy nettimpedans påvirker systemets dynamiske respons og hvordan interaksjonen mellom PLL, strømregulatorene og en stor nettimpedans fører til ustabilitet når de målte spenningene er sterkt påvirket av driften til omformeren. PI-regulatorene i de roterende referansesystemene er spesielt følsomme for oscillasjonene som vil bli forsterket når reguleringsstrukturene benytter foroverkopling av de målte spenningene. Responsen til PR-regulatoren blir derimot moderert av interaksjonen med den faselåste sløyfen, og hystereseregulatorene følger referansen raskt så lenge interaksjonen med den faselåste sløyfen ikke fører til ustabilitet.

Driften under asymmetriske forhold i et svakt nett er undersøkt for reguleringssystemene som benytter PLL-metoder som er designet til å fjerne oscillasjonene som oppstår i positiv sekvens referansesystem ved ubalansert nettspenning. Simuleringene viser at reguleringssystemene med en DDSRF-PLL har en kortere transient periode enn reguleringssystemet med notch-filter-PLL, men med en liten 100 Hz oscillasjon i stasjonær tilstand i et asymmetrisk svakt nett.

Resultatene indikerer videre at innstillingen til PLL-parametrene spiller en viktig rolle for stabiliteten til reguleringssystemet, og at en tregere PLL kan føre til en mer dempet interaksjon med strømregulatorene på bekostning av et tregere og mindre dynamisk nøyaktig reguleringssystem.

# Contents

| 1        | Inti | Introduction                                                |          |

|----------|------|-------------------------------------------------------------|----------|

| <b>2</b> | Bac  | kground and Theory                                          | <b>5</b> |

|          | 2.1  | Three Phase Systems                                         | 5        |

|          |      | 2.1.1 Symmetrical Components - The positive-, negative- and |          |

|          |      | zero-sequence                                               | 6        |

|          |      | 2.1.2 $\alpha\beta$ -transformation                         | 8        |

|          |      | 2.1.3 $dq$ -transformation                                  | 11       |

|          | 2.2  | pu-transformation                                           | 12       |

|          | 2.3  | The Voltage Source Converter (VSC)                          | 12       |

|          |      | 2.3.1 Two level - three phase converter                     | 13       |

|          |      | 2.3.2 3rd Harmonic injection                                | 14       |

|          |      | 2.3.3 Switching in the VSC                                  | 15       |

|          |      | 2.3.4 LCL-filter                                            | 16       |

|          |      | 2.3.5 Mathematical Model                                    | 17       |

|          |      | 2.3.6 Mathematical model for unbalanced system              | 21       |

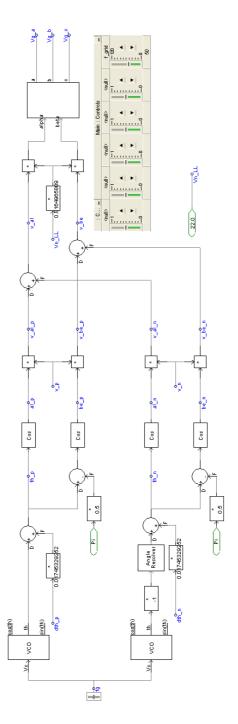

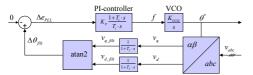

|          | 2.4  | Grid Synchronization                                        | 22       |

|          |      | 2.4.1 The Synchronous Reference Frame Phase Locked Loop     |          |

|          |      | (SRF-PLL)                                                   | 22       |

|          |      | 2.4.2 Phase Locked Loop for a Balanced System               | 23       |

|          |      | 2.4.3 Phase Locked Loop for Unbalanced Systems              | 25       |

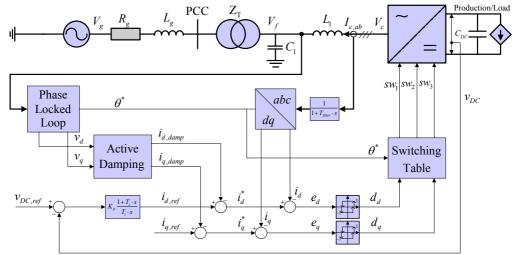

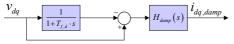

|          | 2.5  | Active Damping (AD)                                         | 29       |

|          |      | 2.5.1 AD - Using a High Pass Filter                         | 29       |

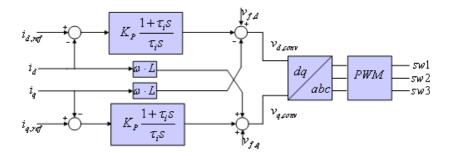

|          | 2.6  | SRF- Proportional Integrator (SRF-PI) Controller            | 32       |

|          |      | 2.6.1 Decoupling of the d and q axis                        | 33       |

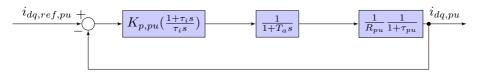

|          |      | 2.6.2 Tuning of the PI Controller for the Current Loop      | 33       |

|          |      | 2.6.3 Dual Current PI controller                            | 36       |

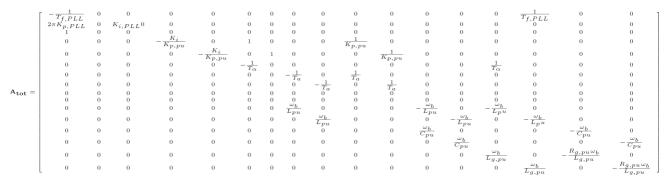

|   | 2.7            | State Space Model including the PI Current Controller                   | 37 |

|---|----------------|-------------------------------------------------------------------------|----|

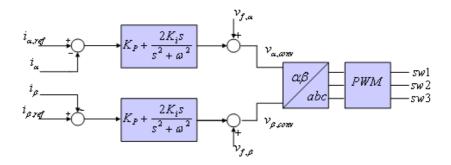

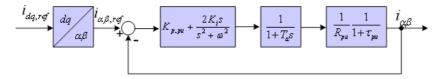

|   | 2.8            | Proportional Resonant (PR) Controller                                   | 38 |

|   |                | 2.8.1 PR-controller in unbalanced grid                                  | 40 |

|   | 2.9            |                                                                         | 41 |

|   |                | 2.9.1 Hysteresis controller in abc-reference frame                      | 41 |

|   |                |                                                                         | 43 |

|   | 2.10           | •                                                                       | 48 |

|   |                | 2.10.1 Tuning the DC-link voltage controller                            | 50 |

| 3 | Syst           | tem Design                                                              | 51 |

|   | 3.1            | System component design                                                 | 51 |

|   |                | 3.1.1 LCL-filter parameters                                             | 51 |

|   | 3.2            | Controllers Design                                                      | 52 |

|   |                | 3.2.1 PI Current Controller Parameters                                  | 53 |

|   |                | 3.2.2 PR Current Control Parameters                                     | 55 |

|   |                | 3.2.3 Hysteresis Current Control Parameters                             | 56 |

|   |                | 3.2.4 Three level dq-Hysteresis controller                              | 57 |

|   |                | 3.2.5 DC-link Voltage Controller Parameters                             | 59 |

|   |                | 3.2.6 Tuning of the Phase Locked Loop                                   | 60 |

|   | 3.3            | Active Damping                                                          | 62 |

|   | 3.4            | e e e e e e e e e e e e e e e e e e e                                   | 63 |

|   | 3.5            |                                                                         | 63 |

|   | 3.6            | Simulation Cases                                                        | 65 |

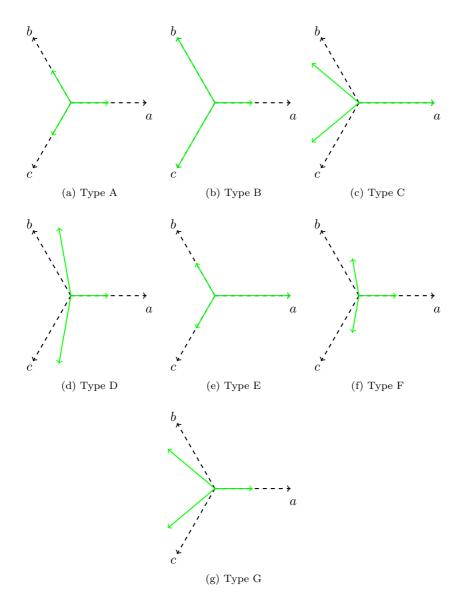

|   |                | 3.6.1 Classification of Voltage Dips                                    | 65 |

| 4 | $\mathbf{Sim}$ |                                                                         | 69 |

|   | 4.1            | 1 0                                                                     | 69 |

|   |                |                                                                         | 69 |

|   |                |                                                                         | 71 |

|   |                | 1 1 <i>i i i i i i i i i i</i>                                          | 72 |

|   |                | 4.1.4 Step response, when step change in $i_{q,ref}^+$ in a weak grid . | 84 |

|   |                | 4.1.5 Operation with a DC-link controller                               | 86 |

|   | 4.2            | Voltage Drop in the Grid                                                | 88 |

|   |                | 4.2.1 Switching Frequency in Hysteresis Current Controllers in          |    |

|   |                |                                                                         | 88 |

|   |                | 4.2.2 Evaluation of Current Control Structures with conven-             |    |

|   |                | tional PLL in a Three Phase Voltage Drop in a Weak Grid                 | 91 |

|   |                | 4.2.3 Voltage Drop in a Stiff Grid                                      | 93 |

|   |                | 4.2.4 Voltage Drop in a Weak Grid                                       | 98 |

х

| CONTENTS |

|----------|

|----------|

|              | <ul><li>4.2.5 Stability Limits for Voltage Drop in the Grid</li><li>4.3 General Discussion</li></ul>                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>5</b>     | Conclusion                                                                                                                                                                                                                                                                                                                                                               | 111                                                                                                                                                    |

| 6            | Scope for Further Work                                                                                                                                                                                                                                                                                                                                                   | 113                                                                                                                                                    |

| $\mathbf{A}$ | Negative sequence decoupling                                                                                                                                                                                                                                                                                                                                             | <b>A-1</b>                                                                                                                                             |

| в            | Modulus Optimum                                                                                                                                                                                                                                                                                                                                                          | A-3                                                                                                                                                    |

| С            | Symmetrical Optimum                                                                                                                                                                                                                                                                                                                                                      | <b>A-5</b>                                                                                                                                             |

| D            | State-space model                                                                                                                                                                                                                                                                                                                                                        | <b>A-9</b>                                                                                                                                             |

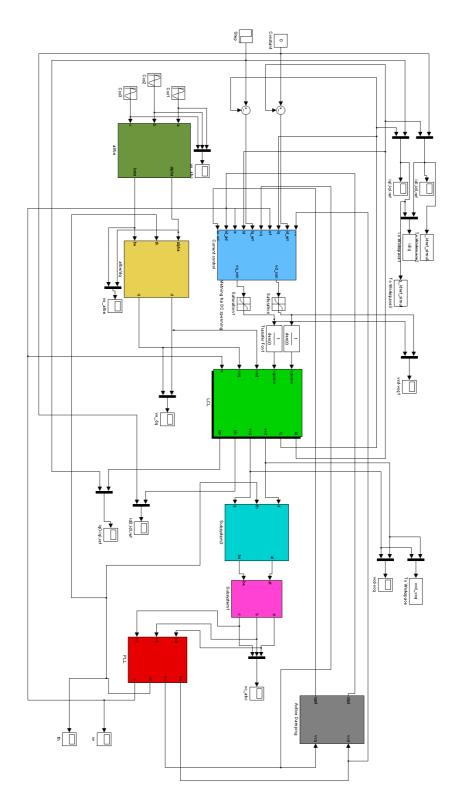

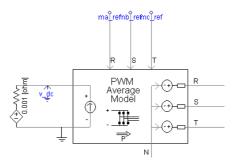

| $\mathbf{E}$ | The PSCAD-model                                                                                                                                                                                                                                                                                                                                                          | A-15                                                                                                                                                   |

| F            | Additional Simulation FiguresF.1Stiff grid step responseF.1.1Hysteresis current responseF.1.2Notch filter time responseF.1.3Negative Sequence for dual PI controller in stiff gridF.2Weak Grid Step ResponseF.2.1Feed forward loopF.2.2Step change in $i_{d,ref}$ F.3Voltage DropF.3.1Stiff grid current responseF.3.2Weak grid current responseF.3.3Switching Frequency | <ul> <li>A-19</li> <li>A-19</li> <li>A-20</li> <li>A-21</li> <li>A-21</li> <li>A-24</li> <li>A-24</li> <li>A-30</li> <li>A-30</li> <li>A-33</li> </ul> |

| G            | Digital Appendix                                                                                                                                                                                                                                                                                                                                                         | A-39                                                                                                                                                   |

| н            | Paper presented at IEEE PEDG2010 in Hefei China, June 201                                                                                                                                                                                                                                                                                                                | <b>A-</b> 41                                                                                                                                           |

| Ι            | Paper submitted for EPE-PMC 2010                                                                                                                                                                                                                                                                                                                                         | A-49                                                                                                                                                   |

CONTENTS

xii

# List of Figures

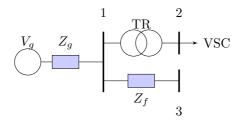

| 2.1  | The grid Thevenin equivalent                                                       | 6  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Symmetrical components                                                             | 7  |

| 2.3  | Positive and negative sequence in an unbalanced system                             | 9  |

| 2.4  | Voltage and current vector in $\alpha\beta$ -coordinates                           | 10 |

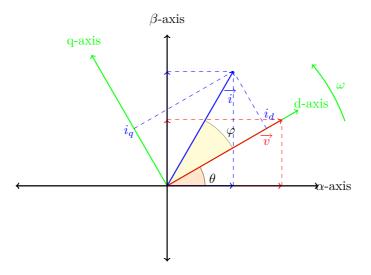

| 2.5  | Voltage and current vector in $dq$ -coordinates                                    | 11 |

| 2.6  | Two level - three phase voltage source converter                                   | 13 |

| 2.7  | PWM in the VSC                                                                     | 14 |

| 2.8  | Switching States of the VSC voltage                                                | 15 |

| 2.9  | Block diagram of VSC                                                               | 18 |

| 2.10 | PLL Control Loop                                                                   | 23 |

| 2.11 | Phase diagram, showing the $\Delta \theta$                                         | 24 |

| 2.12 | Positive and negative synchronous rotating reference frame                         | 26 |

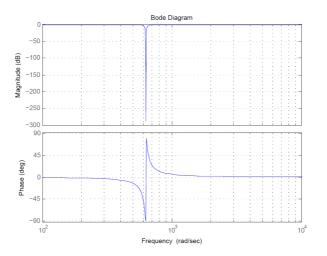

| 2.13 | Bode plot of notch filter                                                          | 28 |

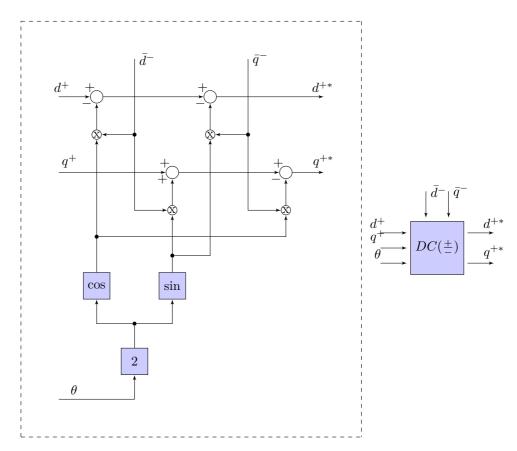

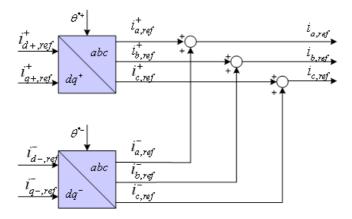

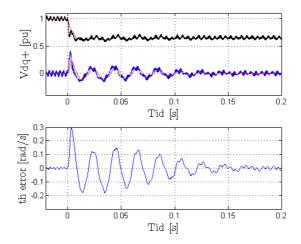

|      | Decoupling of the positive and negative sequence                                   | 30 |

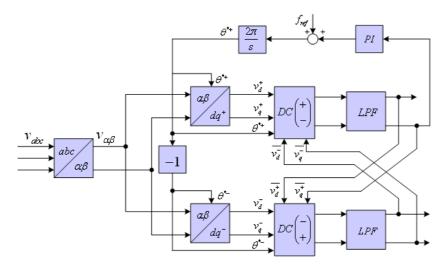

| 2.15 | The DDSRF-PLL                                                                      | 31 |

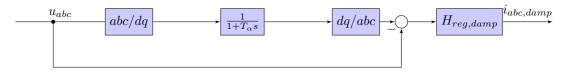

| 2.16 | The Active damping                                                                 | 31 |

| 2.17 | PI current controller with decoupling between the d-axis and the                   |    |

|      | q-axis                                                                             | 34 |

|      | Current Loop for the PI controller                                                 | 35 |

| 2.19 | The PR current controller                                                          | 39 |

| 2.20 | Current Loop for the PR controller                                                 | 39 |

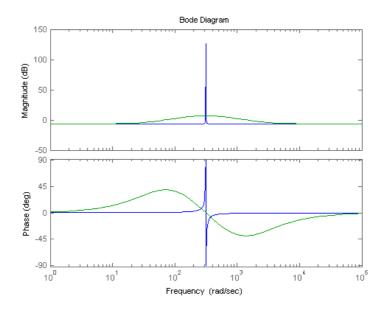

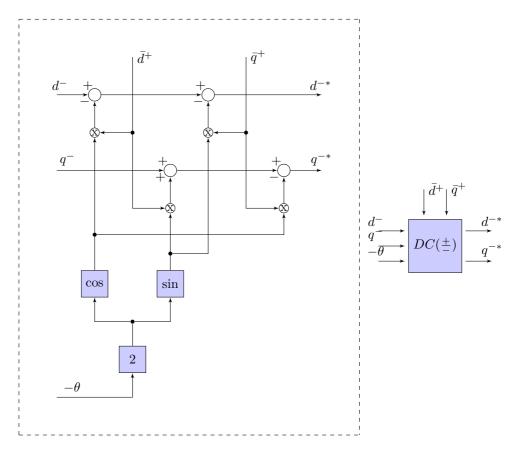

| 2.21 | Frequency response of PR controller. The blue plot shows the                       |    |

|      | bode plot for Equation 2.79 and the green plot shows for Equation                  |    |

|      | 2.80                                                                               | 40 |

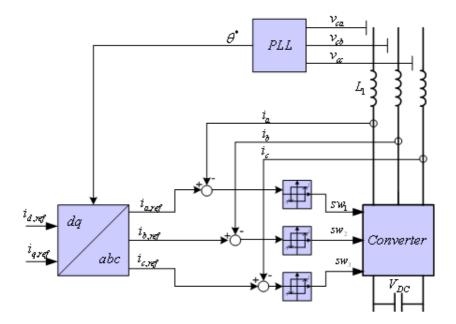

| 2.22 | $abc\mbox{-hysteresis}$ controller with three two level hysteres<br>is comparators | 42 |

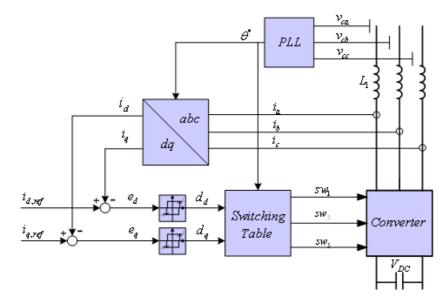

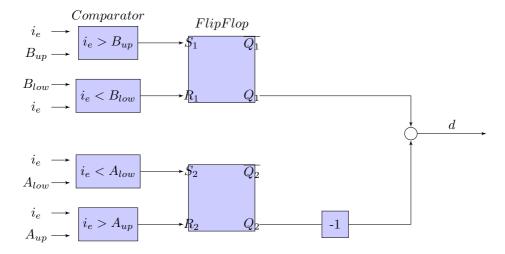

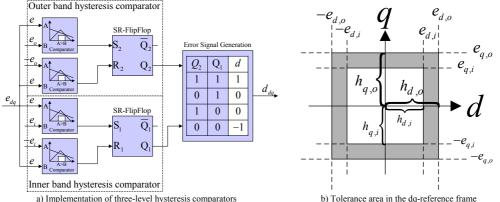

| 2.23 | $dq\mbox{-hysteresis}$ controller with two three level hysteres<br>is comparators  | 43 |

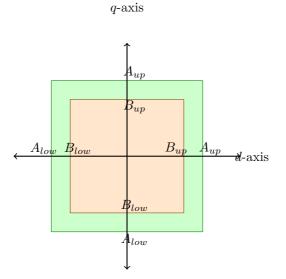

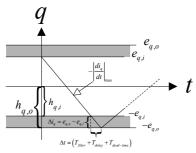

| 2.24 | Three level hysteresis band                                                        | 44 |

|      |                                                                                    |    |

| 2.25       | The three level hysteresis comparator                                                                                                          | 45         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

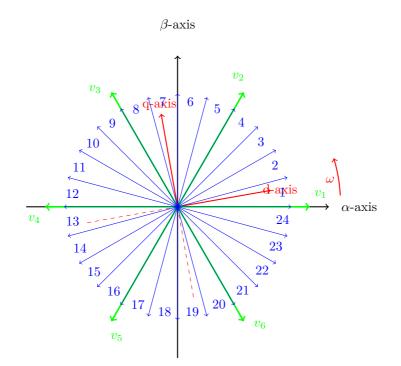

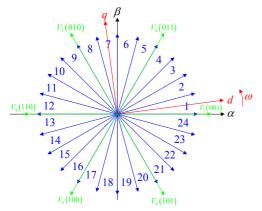

|            | The Voltage Vector plane divided into 24 sectors                                                                                               | 47         |

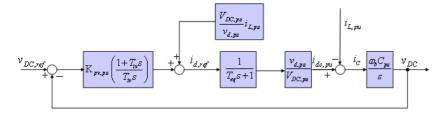

| 2.27       | Block diagram of the dc-link voltage control loop $\ldots \ldots \ldots$                                                                       | 49         |

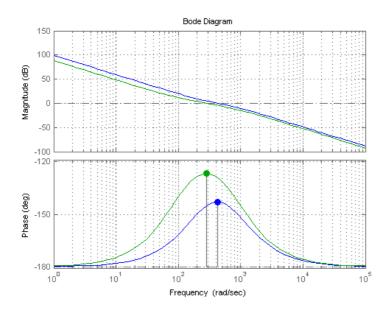

| 3.1        | Bode plot of the open loop transfer function, Equation 2.65                                                                                    | 54         |

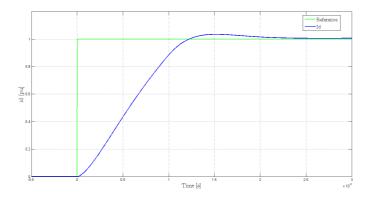

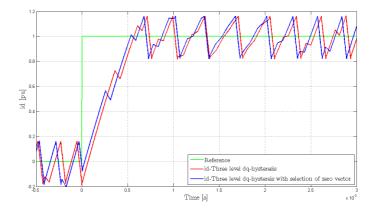

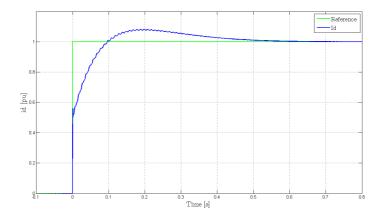

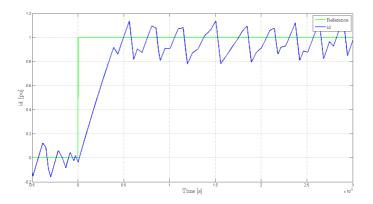

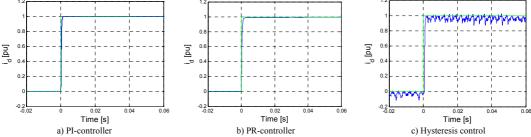

| 3.2        | PI controller, step response in $i_d$ when connected to a stiff grid .                                                                         | $54 \\ 54$ |

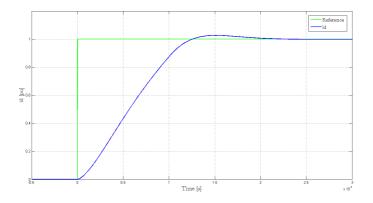

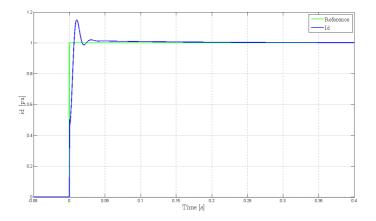

| 3.2<br>3.3 | PR controller, step response in $i_d$ when connected to a stiff grid .                                                                         | 55         |

|            |                                                                                                                                                | 99         |

| 3.4        | Phase current hysteresis controller, step response in $i_d$ when con-                                                                          | 57         |

| 25         | nected to a stiff grid                                                                                                                         | 57         |

| 3.5        | Positive and negative current reference in phase current hysteresis                                                                            | 57         |

| 9.0        | controller                                                                                                                                     | 57         |

| 3.6        | dq-Hysteresis controller, step response in $i_d$ when connected to a                                                                           | <b>F</b> 0 |

| 0.7        | stiff grid                                                                                                                                     | 58         |

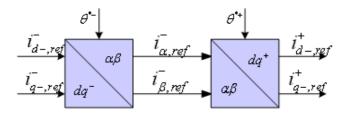

| 3.7        | Negative sequence reference                                                                                                                    | 59<br>60   |

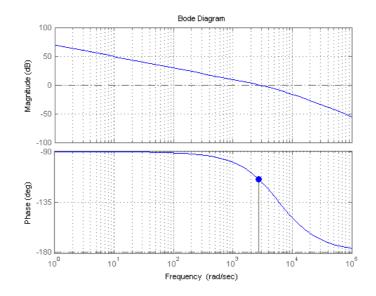

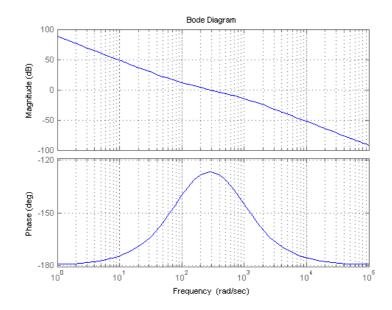

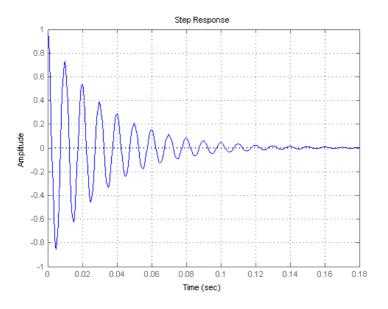

| 3.8        | Bode plot of DC-link open loop transfer function                                                                                               | 60         |

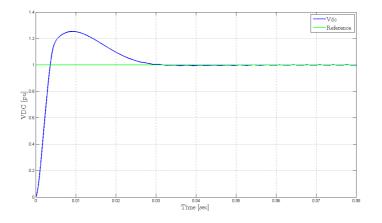

| 3.9        | Step response in $V_{DC}$ when connected to a stiff grid $\ldots \ldots$                                                                       | 61         |

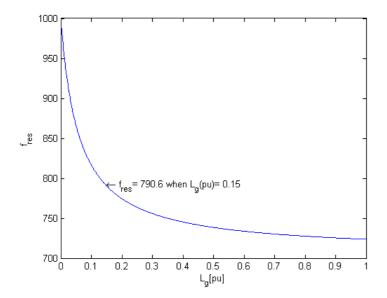

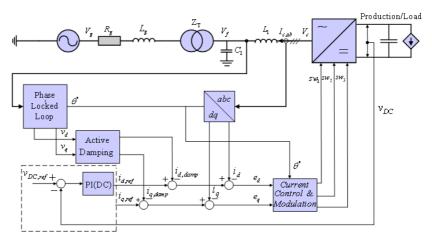

| 3.10       | The resonance frequency as a function of the grid impedance                                                                                    | 63         |

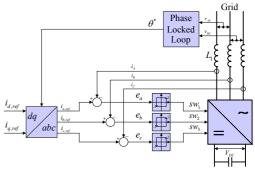

| 3.11       | The overall control system                                                                                                                     | 64         |

| 3.12       | S 1 V                                                                                                                                          | 65         |

| 3.13       | Classification of faults                                                                                                                       | 67         |

| 4.1        | Step response in $i_d^+$ when connected to a stiff grid with dual PI                                                                           |            |

| 1.1        | controller with notch filter $\ldots$                                                                                                          | 70         |

| 4.2        | Step response in $i_d^+$ when connected to a stiff grid with dual PI                                                                           | 10         |

| 4.2        | controller with decoupling $\ldots$                                                                                                            | 71         |

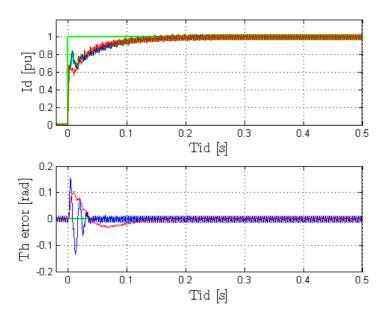

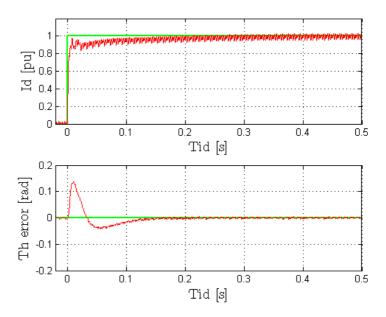

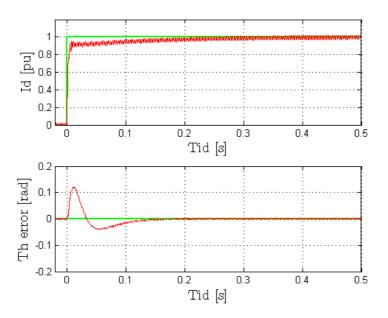

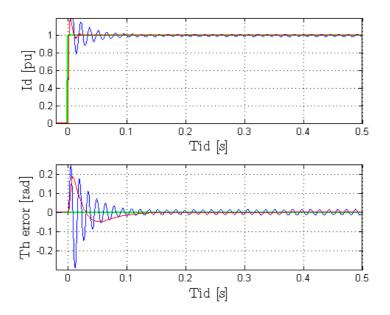

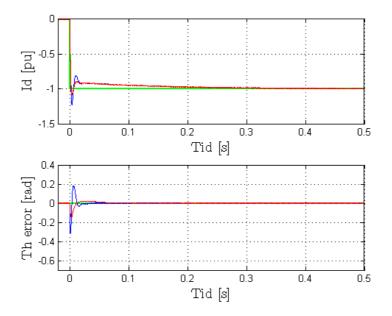

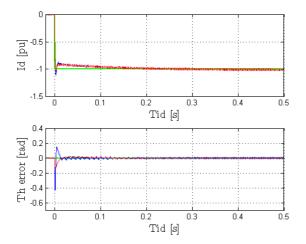

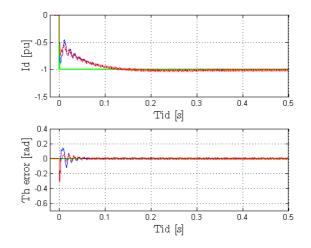

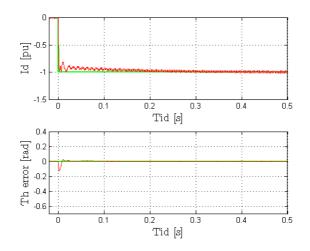

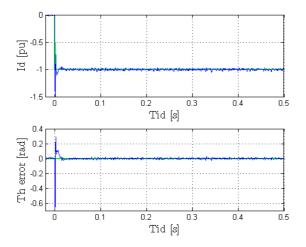

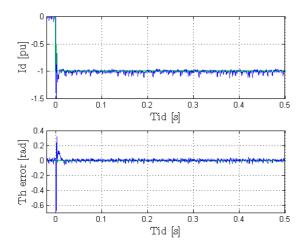

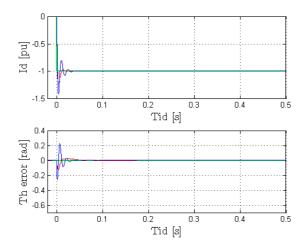

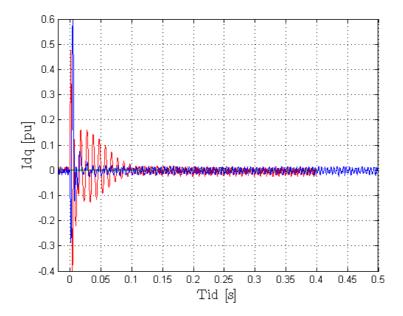

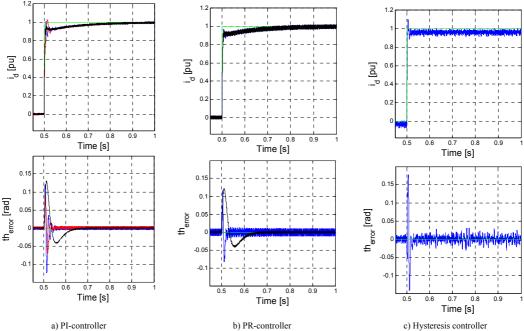

| 4.3        | PI controller, step response in $i_d^+$ when connected to a weak grid                                                                          | 73         |

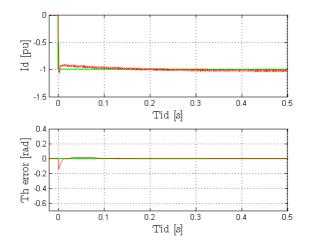

| 4.4        | PR controller, step response in $i_d^+$ when connected to a weak grid<br>PR controller, step response in $i_d^+$ when connected to a weak grid | 74         |

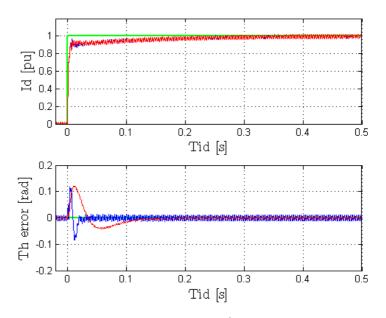

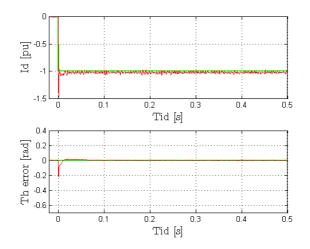

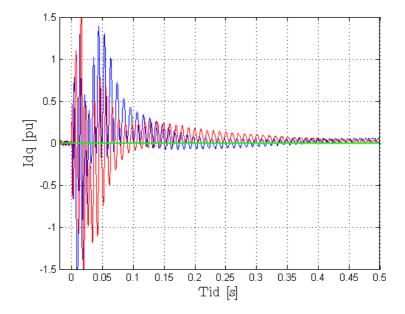

| 4.5        | Dual PI controller with notch filter, step response in $i_d^+$ when                                                                            | 14         |

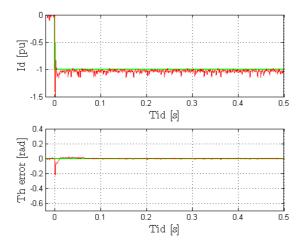

| 4.0        | connected to a weak grid $\ldots$                                                                                                              | 75         |

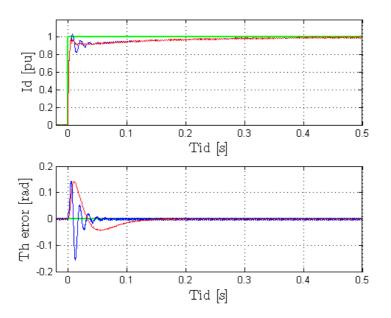

| 4.6        | Dual PI controller, sequence decoupled, step response in $i_d^+$ when                                                                          | 10         |

| 4.0        | connected to a weak grid $\ldots$                                                                                                              | 76         |

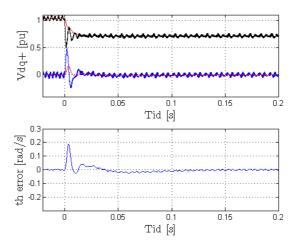

| 4.7        | Phase current hysteresis controller, step response in $i_d^+$ when con-                                                                        | 10         |

| 4.1        | nected to a weak grid $\ldots$                                                                                                                 | 77         |

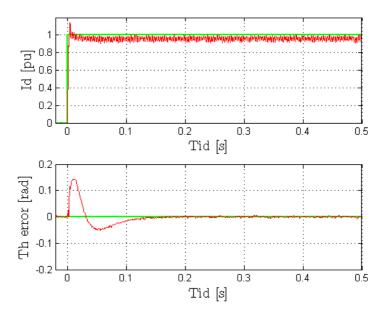

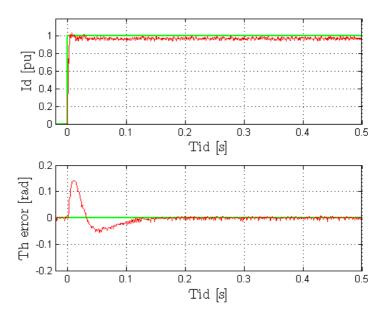

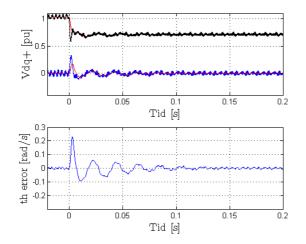

| 4.8        | Three level hysteresis-dq controller, step response in $i_d^+$ when                                                                            | 11         |

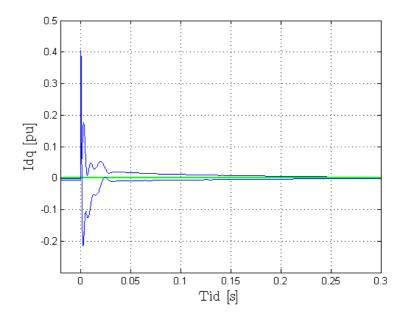

| 4.0        | connected to a weak grid $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                        | 78         |

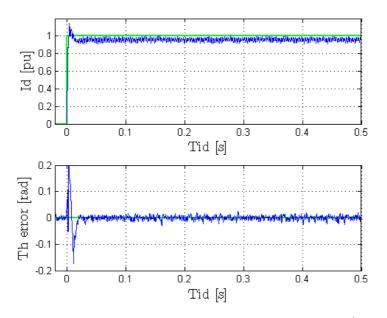

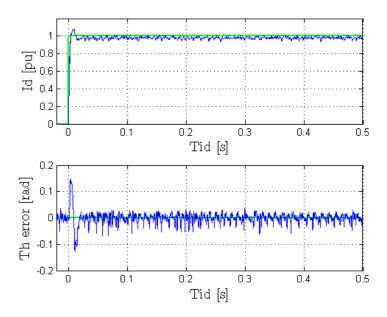

| 4.9        | PR controller, PLL sequence decoupled, step response in $i_d^+$ when                                                                           | 10         |

| 4.9        | connected to a weak grid $\ldots$                                                                                                              | 79         |

| 4 10       | Phase current hysteresis controller, PLL sequence decoupled, step                                                                              | 19         |

| 4.10       |                                                                                                                                                | 00         |

|            | response in $i_d^+$ when connected to a weak grid                                                                                              | 80         |

#### xiv

### LIST OF FIGURES

| 4.11 | Three level hysteresis-dq controller, PLL sequence decoupled,                                                                    |          |

|------|----------------------------------------------------------------------------------------------------------------------------------|----------|

|      | step response in $i_d^+$ when connected to a weak grid $\ldots$ $\ldots$                                                         | 82       |

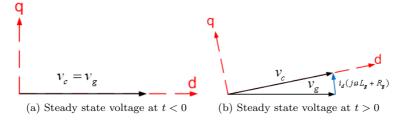

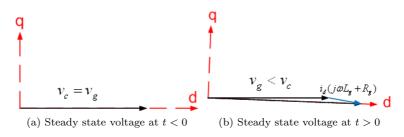

| 4.12 | Change in voltage at change in current                                                                                           | 83       |

|      | State space model with step change in $i_{d,ref}$                                                                                | 83       |

|      | PI controller, step response in $i_q^+$ when connected to a weak grid                                                            | 85       |

|      | Change in voltage at change in q-axis current                                                                                    | 86       |

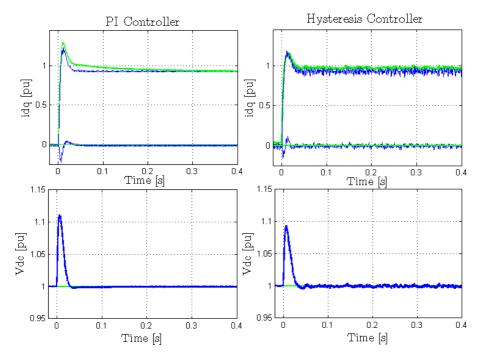

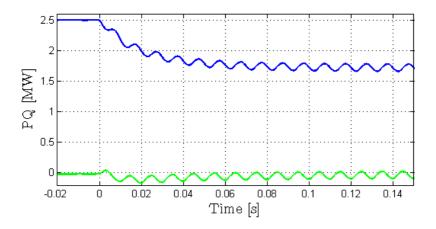

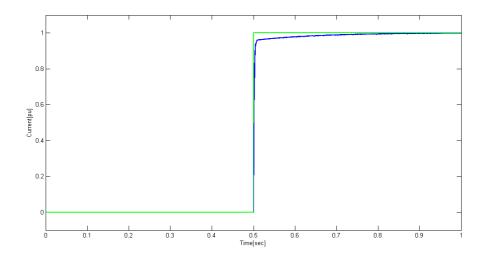

| 4.16 | Current response, and response i the DC-link voltage for a step                                                                  |          |

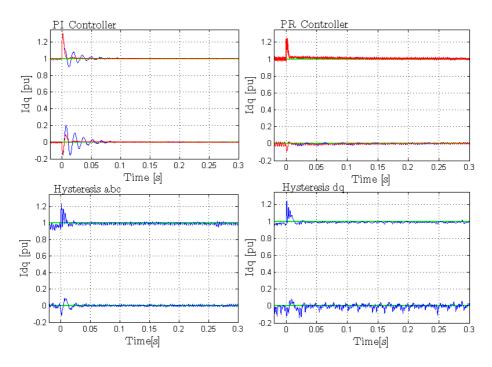

|      | change in input power for a PI current controller structure, and                                                                 |          |

|      | a Phase current hysteresis controller as the inner control loop $\ . \ .$                                                        | 87       |

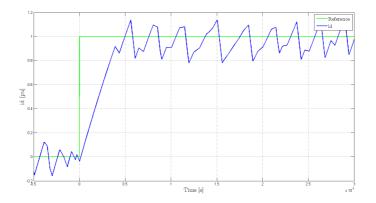

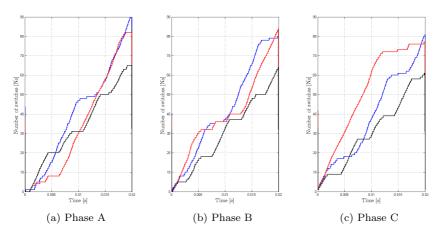

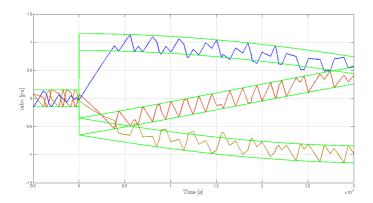

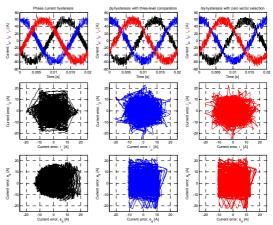

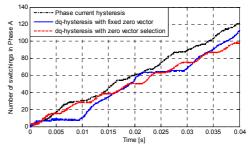

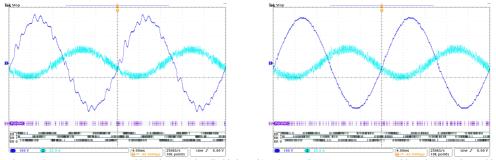

|      | Switching frequency in hysteresis controllers                                                                                    | 89       |

|      | Number of switches during one period                                                                                             | 91       |

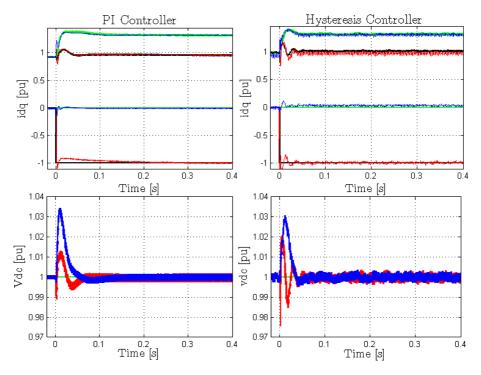

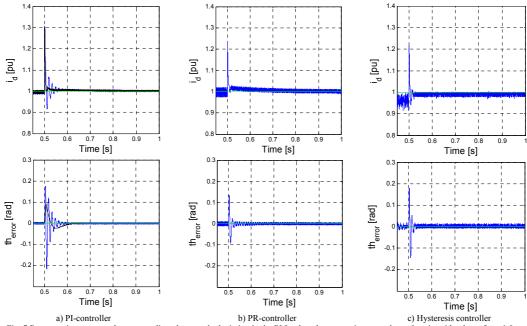

| 4.19 | Current controllers, voltage drop type A when connected to a                                                                     |          |

|      | weak grid                                                                                                                        | 92       |

| 4.20 | Current controllers, voltage drop type A when connected to a                                                                     |          |

|      | weak grid                                                                                                                        | 94       |

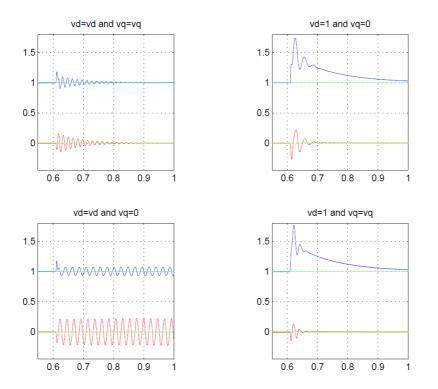

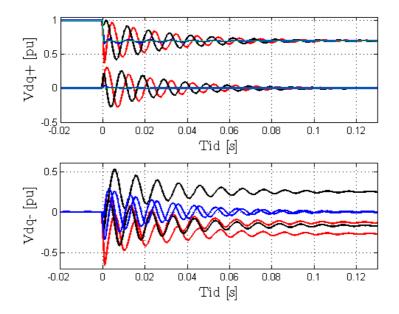

| 4.21 |                                                                                                                                  |          |

|      | the Dual PI controller with notch filter, the second row shows the                                                               |          |

|      | Dual PI controller with DDSRF, and the third row shows the PR                                                                    | 0.0      |

| 4 00 | controller with DDSRF-PLL                                                                                                        | 96<br>07 |

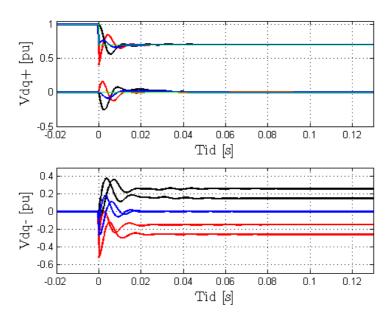

|      | Positive and negative sequence voltage at voltage drop in the grid                                                               | 97       |

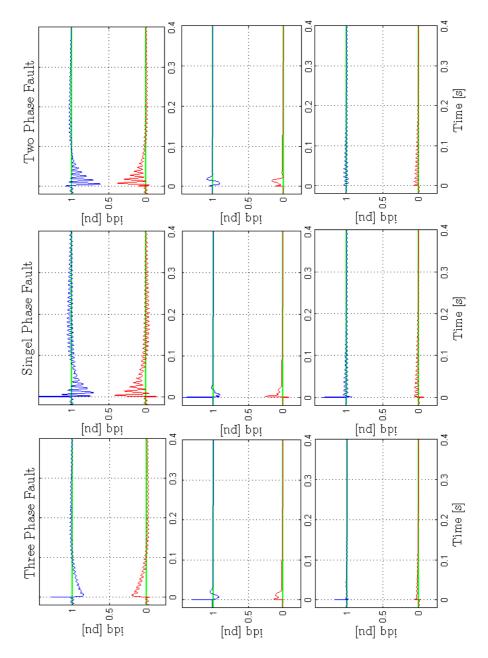

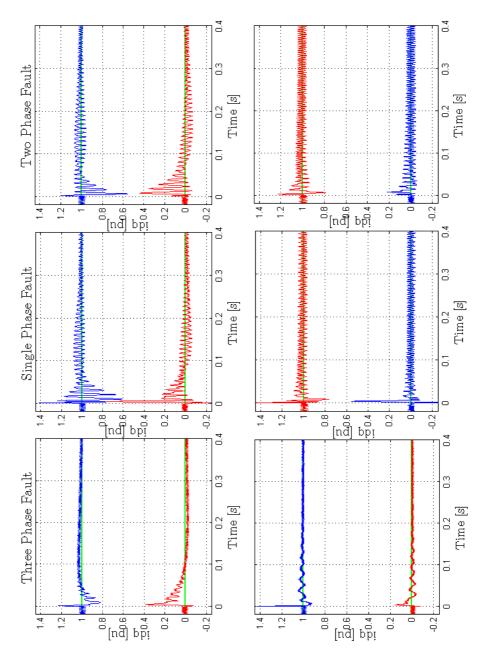

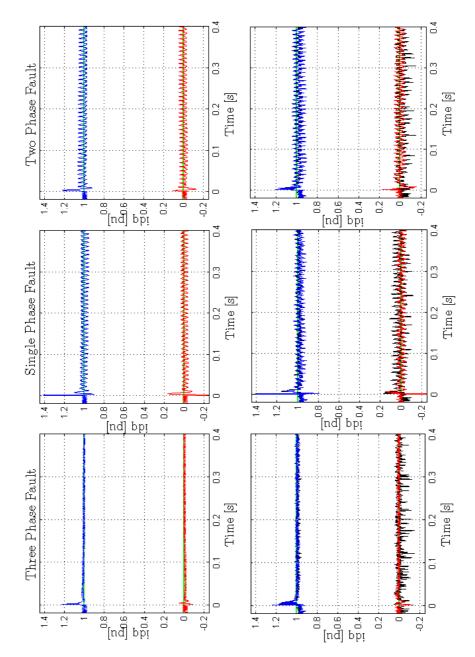

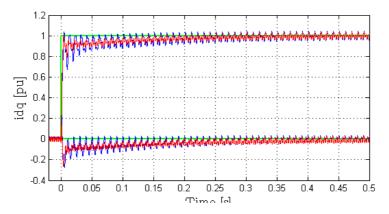

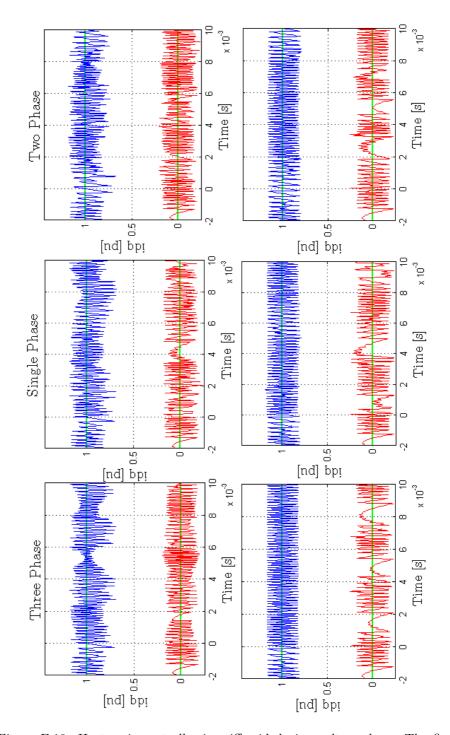

| 4.23 | Current response to voltage drop. The first row shows the Dual PI controller with notch filter and the second row shows the Dual |          |

|      |                                                                                                                                  | 100      |

| 1 24 | Current response to voltage drop. The first row shows the PR                                                                     | 100      |

| 4.24 | controller with DDSRF-PLL and the second row shows the Phase                                                                     |          |

|      | Current hysteresis controller (red and blue plot) and the dq-                                                                    |          |

|      |                                                                                                                                  | 101      |

| 4.25 |                                                                                                                                  | 103      |

|      | Positive sequence voltage and angle deviation at grid inductance                                                                 |          |

|      |                                                                                                                                  | 107      |

| 4.27 | Positive sequence voltage and angle deviation at grid inductance                                                                 |          |

|      | $0.35~\mathrm{pu}$ and PLL tuned two time slower than Table 3.7                                                                  | 107      |

|      |                                                                                                                                  |          |

| A.1  | Decoupling of the positive and negative sequence                                                                                 | A-2      |

| C.1  | Symmetrical optimum bode plot                                                                                                    | Λ 7      |

| 0.1  |                                                                                                                                  | r_ (     |

| D.1  | The Simulink model                                                                                                               | A-14     |

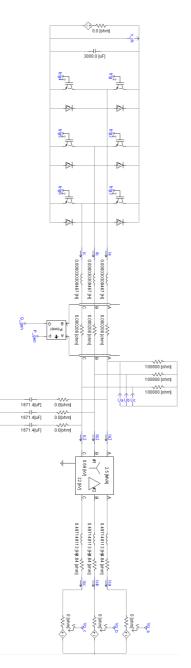

| E.1          | The PSCAD average PWM-model                                               | A-15                  |

|--------------|---------------------------------------------------------------------------|-----------------------|

| E.2          | The PSCAD-model stiff grid voltage source                                 | $\operatorname{A-16}$ |

| E.3          | The PSCAD-model electric circuit                                          | $\operatorname{A-17}$ |

| F.1          | Phase current hysteresis controller, step response in $i_d$ when con-     |                       |

|              | nected to a stiff grid                                                    | A-20                  |

| F.2          | Phase current hysteresis controller, step response in $i_{abc}$ when      |                       |

|              | connected to a stiff grid                                                 | A-20                  |

| F.3          | Step response, notch filter                                               | A-21                  |

| F.4          | Step response, notch filter                                               | $\operatorname{A-22}$ |

| F.5          | Current response with and without the voltage feed-forward loop           | A-23                  |

| F.6          | Step response for $i_d$ when step change in $i_{d,ref}$ , using open loop |                       |

|              | transfer function in Equation 4.1, $L_g = 0.2pu$ and $R_g = 0.025pu$ .    | A-24                  |

| F.7          | PR controller with conventional PLL in blue and with DDSRF-               |                       |

|              | PLL in red                                                                | A-25                  |

| F.8          | PR controller, step response in $i_q$ when connected to a weak grid       | A-25                  |

| F.9          | Dual PI controller with notch filter, step response in $i_q$ when         |                       |

|              | connected to a weak grid                                                  | A-26                  |

| F.10         | Dual PI controller, sequence decoupled, step response in $i_q$ when       |                       |

|              | connected to a weak grid                                                  | A-26                  |

| F.11         | Phase current hysteresis controller, step response in $i_q$ when con-     |                       |

|              | nected to a weak grid                                                     | A-27                  |

| F.12         | Three level hysteresis-dq controller, step response in $i_q$ when con-    |                       |

|              | nected to a weak grid                                                     | A-27                  |

| F.13         | PR controller,<br>PLL decoupled, step response in $i_q$ when connected    |                       |

| <b>F</b> 4 4 | to a weak grid                                                            | A-28                  |

| F'.14        | Phase current hysteresis controller, PLL decoupled, step response         | • • • •               |

| T 1 F        | in $i_q$ when connected to a weak grid                                    | A-28                  |

| F.15         | Three level hysteresis-dq controller, PLL decoupled, step response        | 1 00                  |

| T 10         | in $i_q$ when connected to a weak grid $\ldots$                           |                       |

|              | Step response in $i_q$ when connected to a weak grid $\ldots \ldots$      | A-29                  |

| F.17         | Negative sequence, Dual PI decoupled sequences, current response          | 1 20                  |

| E 10         | to voltage unbalance                                                      | A-30                  |

|              | Positive and negative sequence voltage at voltage drop in the grid        | A-31                  |

| F.19         | Hysteresis controller in stiff grid during voltage drop. The first        |                       |

|              | row shows the phase current hysteresis controller and the second          | A-32                  |

| F 90         | row shows the dq-hysteresis controller                                    | A-97                  |

| г.20         | to voltage unbalance                                                      | 1 30                  |

|              |                                                                           | н-ээ                  |

| F.21 Negative sequence, Dual PI notch filter, current response to volt-            |

|------------------------------------------------------------------------------------|

| age unbalance                                                                      |

| F.22 Positive sequence voltage and angle deviation at grid inductance              |

| 0.2 pu and PLL tuned five time slower than Table $3.7$ A-38                        |

| F.23 Positive sequence voltage and angle deviation at grid inductance              |

| 0.2 pu and PLL tuned two time slower than Table $3.7$ A-36                         |

| F.24 Current from Hysteresis controller, at voltage drop to $0.72 \text{ pu}$ A-37 |

LIST OF FIGURES

xviii

# List of Tables

| 1   | Subscript and superscipt used in the text                                     |

|-----|-------------------------------------------------------------------------------|

| 2   | Parameters used in the text                                                   |

| 3   | Abrivation used in the text                                                   |

| 2.1 | Flip Flop                                                                     |

| 2.2 | Output of three level hysteresis comparator 46                                |

| 2.3 | Switching table for the $dq$ -hysteresis controller $\ldots \ldots \ldots 48$ |

| 2.4 | Selection of closest zero voltage vector                                      |

| 3.1 | System parameters                                                             |

| 3.2 | Filter parameters                                                             |

| 3.3 | Filter Characteristics                                                        |

| 3.4 | PI Control Parameters                                                         |

| 3.5 | PR-Control parameters                                                         |

| 3.6 | DC-link controller parameters                                                 |

| 3.7 | PLL PI control parameters                                                     |

| 3.8 | Type of transformers                                                          |

| 3.9 | Transformation of voltage dip, through transformer                            |

| 4.1 | Stability limits with zero current injection                                  |

| 4.2 | Results from simulations                                                      |

| 4.3 | Stability limits when step change in $i_{d,ref}$                              |

| 4.4 | Stability limits when step change in power input, with dc-link                |

|     | controller                                                                    |

| 4.5 | Stability limits at three phase fault                                         |

| 4.6 | Stability limits at Single Phase Fault                                        |

| 4.7 | Stability limits at Two Phase Fault                                           |

| F.1 | Stability limits for different situation of the voltage feed-forward |      |

|-----|----------------------------------------------------------------------|------|

|     | loop in the PI controller                                            | A-22 |

|     |                                                                      |      |

| G.1 | Digital appendix                                                     | A-39 |

### List of Parameters

| Parameter | Explanation                                |

|-----------|--------------------------------------------|

| d         | Real axis of the Park Transformation       |

| q         | Imaginary axis of the Park Transformation  |

| abc       | Phases of a three-phase system             |

| pu        | pu value                                   |

| g         | Value at the grid                          |

| conv      | Value at the converter                     |

| b         | Base value                                 |

| α         | Real axis of the Clark transformation      |

| $\beta$   | Imgainary axis of the Clark transformation |

| LL        | Line to line value                         |

| up        | Upper value of the band limit              |

| low       | Lower value of the band limit              |

| RMS       | Root mean square value                     |

| ref       | Reference value                            |

| +         | Positive Sequence components               |

| —         | Negative Sequence components               |

| 0         | Zero Sequence components                   |

Table 1: Subscript and superscipt used in the text

| Parameter       | Explanation                       |

|-----------------|-----------------------------------|

| $V_n$           | Nominal voltage                   |

| $I_n$           | Nominal current                   |

| $S_n$           | Nominal Power                     |

| X               | Electric Quantity                 |

| $\varphi$       | Angle between voltage and current |

| $\theta$        | Voltage space vector angle        |

| L               | Inductance                        |

| R               | AC side Resistance                |

| $L_g$           | Grid Inductance                   |

| $R_g$           | Grid side Resistance              |

| $C_f$           | Filter capacitance                |

| i               | AC side current                   |

| V <sub>DC</sub> | DC bus voltage                    |

| $f_{sw}$        | Switching frequency               |

| $\omega_b$      | Base angular frequency            |

| $	au_i$         | Regulator Parameter               |

| $T_a$           | VSC time constant                 |

| $T_{f,PLL}$     | Time constant of PLL filter       |

| $K_p$           | Regulator Parameter               |

| $K_i$           | Regulator Parameter               |

| $K_{pv}$        | Regulator Parameter               |

| $T_{iv}$        | Regulator Parameter               |

| $f_n$           | Nominal frequency                 |

| $f_{res}$       | Resonance frequency               |

| $T_{\alpha}$    | Active damping time constant      |

| v               | AC side voltage                   |

| $A_{low}$       | Hysteresis band limit             |

| $B_{low}$       | Hysteresis band limit             |

| i               | Converter side current            |

| $i_o$           | Grid side current                 |

| $v_c$           | Filter capacitor voltage          |

| ω               | Angular frequency                 |

| $M_p$           | Maximum overshoot                 |

| $t_p$           | Instant of maximum overshoot      |

| $t_s$           | Settling time                     |

| P               | Active Power                      |

| Q               | Reactive Power                    |

### Table 2: Parameters used in the text

### Abrivation

| Parameter | Explanation                                |

|-----------|--------------------------------------------|

| VSC       | Voltage source converter                   |

| PWM       | Pulse width modulator                      |

| PLL       | Phase locked loop                          |

| PI        | Proportional integrator                    |

| PR        | Proportional resonant                      |

| SRF       | Synchronous Reference Frame                |

| DDSRF     | Decoupled Dual Synchronous Reference Frame |

| IGBT      | Insulated-gate bipolar transistor          |

| ASF       | Average switching frequency                |

| VCO       | Voltage controlled oscillator              |

Table 3: Abrivation used in the text

LIST OF TABLES

xxiv

### Chapter 1

## Introduction

Nowadays, there is a common understanding that the global warming is human made, with the energy sector as the main contributor to the green house gas emissions. In Europe, the energy sector alone contributes with 80% of the green house gas emissions [14]. The demand for energy worldwide is at the same time continuously increasing. This has led to a significant attention towards alternative energy resources, and the amount of renewable energy integrated into the power system has grown rapidly during the last years.

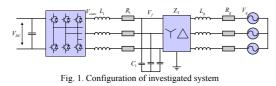

Due to the stochastic behavior of the input power from many of the new renewable energy sources and the large intervention of the renewable systems, the implementation of them will have an impact on the operation of the power system. Hence, more stringent grid connection is required. The use of power electronic equipment has then become an essential part for the utilization of the renewable energy generation systems. Especially the Voltage Source Converter (VSC) topology is becoming a standard modular solution due to its capability for reversible flow, DC-voltage control and the implementation of high performance control system [9].

Although many different control structures have been developed for VSC's in various application, the VSC for grid connection is often current controlled. The current controller as the inner control loop of a cascaded control system appears to be the most commonly used control structure [11]. With current control as the inner control loop, the overall operation will depend on the performance of the current controllers. This has led to significant attention in literature towards development and evaluation of different control structures for the VSC.

The control system should be designed for stable operation under every

grid condition, but weak grid conditions, caused by a high value of the grid impedance is one issue that can challenge the control of the VSC. There has so far been given little attention towards control and operation of a VSC in connection with a weak grid, while taking into account the dynamics of the inner current control loop and the interaction between the converter and the grid impedance [25][10].

Remote faults in distribute power systems results in voltage dips through the power system [26]. In areas with high share of decentralized distributed generation, there is grid code requirements for generator "ride-through" where the generator is imposed to stay connected during transient faults. Both balanced and unbalanced changes in the voltage may occur, and affect the operation of the converter in different ways. Hence the current control of the VSC should be able to handle operation under both balanced and unbalanced conditions.

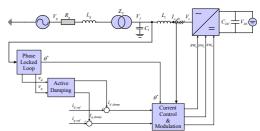

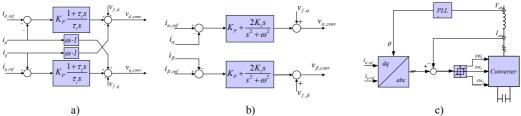

The motivation of this thesis is therefore to investigate, compare and evaluate different current control strategies when a VSC is connected to a weak point in the power system under various grid conditions. The following current control strategies will be presented in investigated: 1) The Decoupled Proportional Integrator (PI) controller in the synchronous rotating reference frame. 2) Two dual PI controller implemented in the separated positive- and negative- sequence rotating reference frame, 3) The PR controller in the stationary reference frame, 4) The two level independent phase current hysteresis controller, and 5) The three level hysteresis controller in the synchronous rotating reference frame.

In addition, the capability of handling both symmetrical and asymmetrical conditions leads the attention towards three different strategies for grid synchronization. 1) A conventional synchronous rotating reference frame Phase Locked Loop (SRF-PLL), designed to handle symmetrical grid conditions, 2) a synchronous rotating reference frame SRF-PLL with notch filter, to filter out the oscillations that occurs during asymmetrical conditions, and 3) a Decoupled Double Synchronous Reference frame-PLL (DDSRF-PLL) that decouples the components of the positive and negative rotating reference frames.

To evaluate and compare the dynamic response and the stability limits for the different current control structures and their respective grid synchronization techniques, simulation studies with the PSCAD/EMTDC simulation software have been carried out. The response to step changes in current reference, operation under various weak grid conditions, and the limits of stable operation of the converter have been investigated by the simulations.

In lack of simple mathematical models with general validity under weak grid conditions, a state space model of the system with a PI controller and a conventional PLL has been tried indentified. This has not been completely fulfilled and the obtained results are analyzed with reference to physical considerations based on the electrical circuit and on traditional control theory.

Large part of the theoretical background information used in this master thesis is based on the background study preformed in the specialization project. To achieve complete substance of this thesis, the background study in the specialization project that is required to understand the work presented here is repeated.

CHAPTER 1. INTRODUCTION

### Chapter 2

# **Background and Theory**

### 2.1 Three Phase Systems

A symmetrical three phase voltage source can be represented by three voltage vectors with the same length and the phase shifted with  $120^{\circ}$  with respect to each other, as described in Equation 2.1[2]. The three phases are named *abc* in this thesis.

$$\begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix} = \begin{bmatrix} V\cos(\omega t) \\ V\cos(\omega t - \frac{2\pi}{3}) \\ V\cos(\omega t + \frac{2\pi}{3}) \end{bmatrix}$$

(2.1)

If the symmetrical system is connected with a common isolated neutral the currents and the voltage for the three phase system fulfills the conditions of Equation 2.2.

$$i_a + i_b + i_c = 0$$

$$v_a + v_b + v_c = 0$$

$$(2.2)$$

#### The Thevenin equivalent

A power system can be large and complex with several nodes that connects a number of lines with transformers and generators or loads. During calculation of the performance of one particular node without doing a full scale analysis of the entire network, the network can be represented with its thevenin equivalent

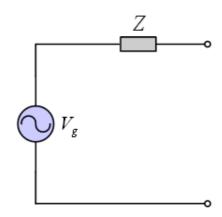

Figure 2.1: The grid Thevenin equivalent

[23]. This therein equivalent is shown in Figure 2.1 and the calculation of Z can be found by the fault level  $S_k$  at the node by Equation 2.3 [23].

$$|Z| = \frac{V^2}{S_k} \tag{2.3}$$

Where  $S_k$  is calculated from short circuit analysis of the power system and V is the nominal line-to-line voltage at the node. The thevenin equivalent voltage  $V_g$  can be taken as the nominal voltage at the point of interest. The fault level can now be expressed by the X/R ratio in Z = R + jX. The fault level is an important parameter, not only during fault conditions, but it is also predicting the performances during normal operation, as it defines the strength of the of the network at the particular point. A weak grid is a network or a part of a network where the fault level is low, that is if Z is high, and indicates that the node voltage is fragile with respect to changes in active and reactive power flow at the node.

### 2.1.1 Symmetrical Components - The positive-, negativeand zero-sequence

Ideally, the voltages and the currents will be perfectly balanced and symmetrical, which leads to greatly simplified analysis. However, this is not always the case. To analyze the three phase system under unbalanced conditions, the

#### 2.1. THREE PHASE SYSTEMS

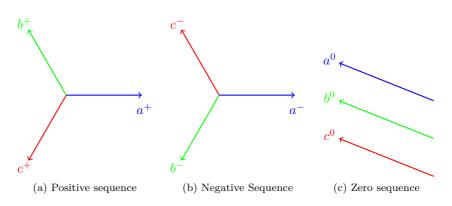

system can be decomposed by use of symmetrical components which mathematically breaks an unbalanced systems into three balanced sequences. A positive-, negative- and zero-sequence. The theory of symmetrical components comes from a paper written by Fortescue in 1918 [6]. The paper demonstrate that N set of unbalanced phasors could be expressed as the sum of N symmetrical sets of balanced phasors. The unsymmetrical voltage and currents are found by superposition of the three sequences. The voltage can be written as in Equation 2.4 and the phasors of the three phases in the positive- negative- and zero-sequence, with superscript respectively +, - and 0, are shown in Figure 2.2a-2.2c.

$$\begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix} = \begin{bmatrix} V_a^- \\ V_b^- \\ V_c^- \end{bmatrix} + \begin{bmatrix} V_a^- \\ V_b^- \\ V_c^- \end{bmatrix} + \begin{bmatrix} V_a^0 \\ V_b^0 \\ V_c^0 \end{bmatrix}$$

(2.4)

Figure 2.2: Symmetrical components

The steady state vector representation in Figure 2.2a-2.2c, has been derived in [1]and can be written as in Equation 2.5 and becomes as in Equation 2.6 in the time domain [33]. A zero sequence current may be present when there is a path in addition to the three lines, f.ex earth [34].

$$\begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 \\ 1 & h & h^2 \\ 1 & h^2 & h \end{bmatrix} \begin{bmatrix} V_a^+ \\ V_a^- \\ V_a^0 \end{bmatrix}$$

(2.5)

Where  $h = e^{j\frac{2\pi}{3}}$

$$\begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix} = \begin{bmatrix} V^+ \cos(\omega t) \\ V^+ \cos(\omega t - \frac{2\pi}{3}) \\ V^+ \cos(\omega t + \frac{2\pi}{3}) \end{bmatrix} + \begin{bmatrix} V^- \cos(-\omega t - \frac{2\pi}{3} + \phi^-) \\ V^- \cos(-\omega t - \frac{2\pi}{3} + \phi^-) \\ V^- \cos(-\omega t + \frac{2\pi}{3} + \phi^-) \end{bmatrix} + \begin{bmatrix} V^0 \cos(\omega t + \phi^0) \\ V^0 \cos(\omega t + \phi^0) \\ V^0 \cos(\omega t + \phi^0) \end{bmatrix}$$

(2.6)

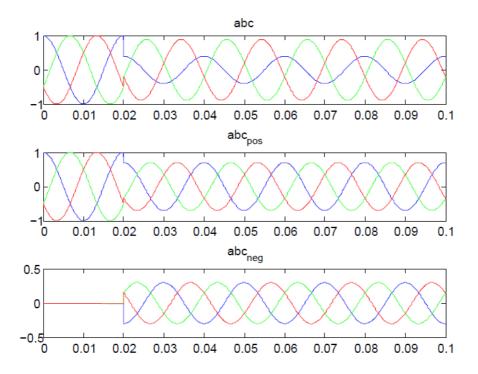

Figure 2.3 shows an system that is exposed to an unbalance at a certain instant. The negative- and the zero-sequence are initially set to zero. At the moment the unbalance occurs, the amplitude of the positive sequence voltage is set equal to 0.7 and the amplitude of the negative sequence is set equal to -0.3. The zero sequence is unchanged, equal to zero. As seen from the figure, the unsymmetrical and unbalanced system is decomposed into two symmetrical and balanced systems.

### **2.1.2** $\alpha\beta$ -transformation

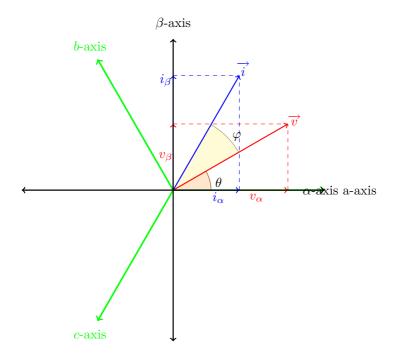

The three phases, both voltage and current, can be represented in a two phase representation. The momentarily value of the three phases can be transformed into a voltage vector or a current vector. This vector can then be represented in a orthogonal stationary  $\alpha\beta$ -reference as shown in Figure 2.4. The transformation from the abc reference to the  $\alpha\beta$ -reference is shown in Equation 2.7.

$$\begin{bmatrix} X_{\alpha} \\ X_{\beta} \\ X_{\gamma} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(0) & \cos(\frac{2\pi}{3}) & \cos(-\frac{2\pi}{3}) \\ \sin(0) & \sin(\frac{2\pi}{3}) & \sin(-\frac{2\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} X_{a} \\ X_{b} \\ X_{c} \end{bmatrix}$$

(2.7)

Introducing the positive- and the negative- sequence and ignoring the zero sequence component, the voltage transformed into in the  $\alpha\beta$ -reference frame is given by Equation 2.8.

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = V^{+} \begin{bmatrix} \cos(\omega t) \\ \sin(\omega t) \end{bmatrix} + V^{-} \begin{bmatrix} \cos(-\omega t + \phi^{-}) \\ \sin(-\omega t + \phi^{-}) \end{bmatrix}$$

(2.8)

The positive sequence voltage is supposed as the phase origin. The voltage vector consists of two sub vectors. One rotating in the positive direction and one rotating in the negative direction. Nor the magnitude or the rotational frequency of the voltage vector for an unbalanced system is constant [33].

Figure 2.3: Positive and negative sequence in an unbalanced system

Figure 2.4: Voltage and current vector in  $\alpha\beta$ -coordinates.

Figure 2.5: Voltage and current vector in dq-coordinates.

## 2.1.3 dq-transformation

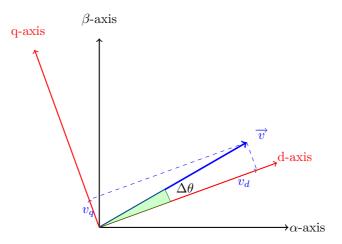

The voltage and current vectors can be represented in any coordinate system. The synchronous rotating reference (SRF)-dq coordinate system is rotating in the same angular speed as the voltage vector. Since the voltage vector and the coordinate system are aligned, the electrical components in this system behaves like DC components. This gives some obvious benefits in control manners. The transformation from  $\alpha\beta$ -reference to dq-reference is shown in Equation 2.9 and in Figure 2.5 :

$$\begin{bmatrix} X_d \\ X_q \end{bmatrix} = \begin{bmatrix} \cos(\theta) & \sin(\theta) \\ -\sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} X_\alpha \\ X_\beta \end{bmatrix}$$

(2.9)

Since the voltage vector for the park transformation is aligned with the daxis, the q component of the voltage vector is zero. The active and reactive power is then reduced to the control of  $i_d$  and  $i_q$  as shown in Equation 2.10.

$$p = \frac{3}{2} v_d i_d \tag{2.10}$$

$$q = -\frac{3}{2} v_d i_q$$

# 2.2 pu-transformation

The pu-system is a good and well spread analyzing tool. Since the values are not directly dependent for their ratings, it is useful for comparing different designs of electrical systems. There are different ways of designing the pu-system. For this thesis the base values are chosen to fit with a amplitude invariant park transformation.

$$V_{s,b} = V_{d,b} = V_{q,b} = \hat{V}_{abc,n} = \frac{\sqrt{2}}{\sqrt{3}} V_n$$

$$V_{DC,b} = 2V_{s,b}$$

$$I_{s,b} = I_{d,b} = I_{q,b} = \hat{I}_{abc,n} = \sqrt{2}I_n$$

(2.11)

$$S_{b} = \sqrt{3} \cdot V_{n}I_{n} = \frac{3}{2}V_{s,b}I_{s,b}$$

$$Z_{b} = \frac{V_{s,b}}{I_{s,b}}$$

$$\omega_{b} = 2\pi f$$

$$(2.12)$$

$V_{s,b}$  is the nominal peak phase voltage at the ac side,  $S_b$  is the nominal three phase apparent power of the ac side and  $I_b$  is the nominal peak phase current. Using the definitions in Equation 2.11 gives the pu-values in Equation 2.13:

$$L_{pu} = \frac{\omega_b L}{Z_{base}}$$

$$C_{pu} = \omega_b C Z_{base}$$

$$R_{pu} = \frac{R}{Z_{base}}$$

$$I_{pu} = \frac{I}{I_{base}}$$

$$V_{pu} = \frac{V}{V_{base}}$$

(2.13)

# 2.3 The Voltage Source Converter (VSC)

There are different ways of converting and inverting voltage with power electronic devices. For distributed generation the state of the art is the two level three phase converter. For high power wind turbines a three-level neutral point clamped VSC is an option. Also matrix converters and multilevel converters

Figure 2.6: Two level - three phase voltage source converter

are developing and been implemented in distribution power generation systems [3]. This thesis will focus on the control of a three-phase two level VSC.

## 2.3.1 Two level - three phase converter

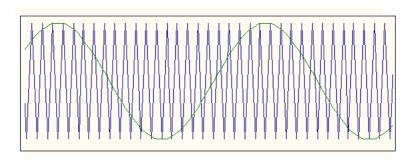

As seen in figure 2.6 the VSC contains shunted diodes and switches. The diodes are mandatory because bidirectional current flow has to be fulfilled by the semiconductor switches in the VSC. The switches, which usually are IGBTs, are turned on and off by a control trigger signal. Different strategies for triggering the switches are dependent on the control method. By use of a linear controller the switches are triggered by comparing three sinusoidal control signals, phase shifted 120° with respect to each other, with a saw tooth signal as shown in Figure 2.7. The sinusoidal signal has the same frequency as the 1st harmonic of the output voltage, and the saw tooth signal has the same frequency as the switching frequency. This method, called the sinus modulation, can be used when the switching frequency is at least 20 times the 1st harmonic frequency [30].

For nonlinear controllers the switching signals are determined by the choice of voltage vector. The different voltage vector representations are presented in Section 2.3.3. If the switches are seen as ideal and the blanking time of the switches are ignored, the output voltage of the converter is independent of the current, since the switches in one of the legs are always on.

To prevent the PWM from going in to over modulation and to attend a stabile system, the DC side of the voltage must be at least as in Equation 2.14[29]:

$$V_{DC} \ge \frac{2\sqrt{2}}{\sqrt{3}} V_{LL} \tag{2.14}$$

Figure 2.7: PWM in the VSC

## 2.3.2 3rd Harmonic injection

For operation of the voltage source converter, using a perfect sine wave as modulation reference, do not give the optimum use of the DC-side voltage of the converter for systems with isolated neutral. By decreasing the peak of the phase voltage, and maintaining the peak of the 1st harmonic, the use of the DC voltage can be increased. This can be achieved by injection of the 3rd harmonic, or every 3rd harmonic multiple, in the phase voltage. This harmonics will cancel out in the line-to-line voltage, since it is injected in all three phases. The use of the DC voltage will increase by a factor  $1.155 \left(\frac{\sqrt{3}}{2}\right)$ . From [13] the 3rd harmonic injection for optimal use of the DC-link voltage can be implemented at the modulation reference as:

$$V_a = \sin \omega t + \frac{1}{6} \sin 3\omega t \tag{2.15}$$

$$V_b = \sin(\omega t - \frac{2\pi}{3}) + \frac{1}{6}\sin 3(\omega t - \frac{2\pi}{3})$$

(2.16)

$$V_c = \sin(\omega t - \frac{4\pi}{3}) + \frac{1}{6}\sin 3(\omega t - \frac{4\pi}{3})$$

(2.17)

To maximize the use of the DC voltage, the PWM can also operate in the over modulation range. The line-to-line voltage will then not be a sine wave and contain a high harmonic distortion.

Figure 2.8: Switching States of the VSC voltage

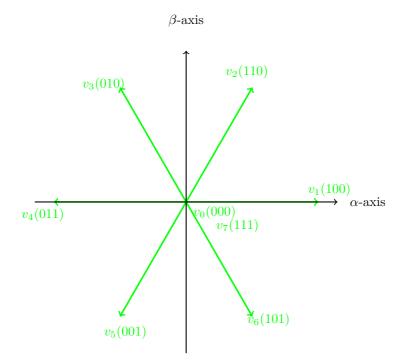

## 2.3.3 Switching in the VSC

By use of different combinations of the switches in the converter the voltage vector can be represented by eight space vectors. Since the three phases are shifted 120 degrees with respect to each other, combination of the the six switches on the three legs and phases will give the the following voltage vector representations:

$$\vec{v_k} = \begin{cases} \left(\frac{2}{3}\right) V_{DC} e^{j\pi(k-1)/3} & \text{for} \quad k = 1, \dots 6\\ 0 & \text{for} \quad k = 0, 7 \end{cases}$$

(2.18)

This give six nonzero voltage vectors and two zero voltage vectors. Figure 2.8 shows the voltage vector in the  $\alpha\beta$ -reference frame.

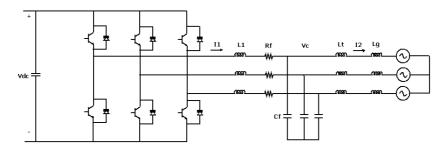

## 2.3.4 LCL-filter

The high frequency harmonics in voltage and current, generated by the high frequency switching in the VSC, can be suppressed by the use of a LCL filter. The LCL filter consists of two inductors in series and a capacitor shunted between them. Compared to a filter with the use of a single inductor, the damping of the switching harmonics, at lower switching frequency, improve by using a LCL filter. In many application, when there is a transformer in the interface between the VSC and the grid, the leakage inductance in the transformer can be used as the second filter inductance. In [24] a method for designing the LCL filter is proposed. The total inductance of the filter should be as small as possible to realize fast tracking and high dynamics, and still handel the ripple in the current.

$$\Delta i_{L1,max} = \frac{V_{DC}}{8L_1 f_{SW}} \tag{2.19}$$

The selection of current ripple is a trade off between the size of  $L_1$ , switching losses and inductor coil and core losses [40]. The choice of the capacitor is done based on the evaluation of the reactive power in the capacitor and in the inductance.

The resonance frequency of the system, ignoring the resistance for simplifications, is given by Equation 2.20.

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2 + L_g}{L_1(L_2 + L_g)C_f}}$$

(2.20)

In pu representation this becomes as in Equation 2.21.

$$\omega_{res} = \omega_b \sqrt{\frac{(L_{1,pu} + L_{g,pu})}{L_{g,pu} L_{1,pu} C_{f,pu}}}$$

(2.21)

The LCL filter itself is independent of the power level and the switching frequency as seen in Equation 2.20, but the LCL-filter resonance should be lower for lower switching frequencies to achieve better filtering. The switching in the VSC should be lower for higher power levels [25].

If the grid voltage is balanced the ripple in the current, for the use of a L-filter is described in [29] and given by Equation 2.22.

$$i_{ripple}(t) = \frac{1}{L} \int_0^t v_{ripple}(\tau) d\tau$$

(2.22)

## 2.3.5 Mathematical Model

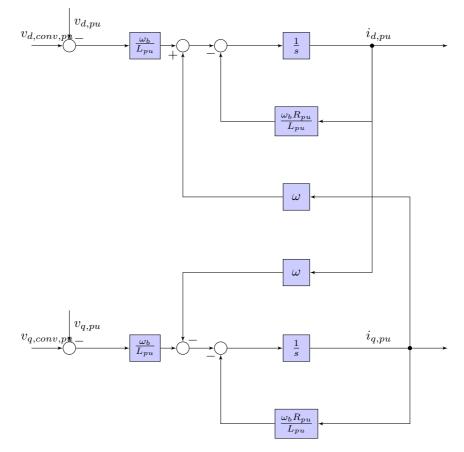

When designing the control structure for the current, it is useful to have a model of the converter to design the controller properly. In [4], a mathematical model for a three phase voltage source converter, is presented. The system is assumed balanced. This model includes the effect of the switches, and the switching function. The dq representation in a synchronous reference frame is shown in Equation 2.23

$$u_{DC} = (\frac{3}{2}(i_q d_q + i_d d_d) - i_{DC})\frac{1}{sC}$$

$$i_d = (u_{DC} d_d - v_d + \omega L i_q)\frac{1}{R + sL}$$

$$i_q = (u_{DC} d_q - v_q - \omega L i_d)\frac{1}{R + sL}$$

(2.23)

This model can be simplified by merging the DC-voltage  $v_{dc}$  and the switching function d to an average  $v_{conv}$ . The VSC will then have a vector representation as shown in Equation 2.24, the current is defined positive in direction from the VSC towards the grid as shown in Figure 2.6.

$$\frac{d}{dt} \begin{bmatrix} i_d \\ i_q \end{bmatrix} = \begin{bmatrix} -\frac{R}{L} & \omega \\ -\omega & -\frac{R}{L} \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} v_{d,conv} - v_d \\ v_{q,conv} - v_q \end{bmatrix}$$

(2.24)

By using the pu transformation introduced in Section 2.2 the mathematical model in Equation 2.24 becomes as in Equation 2.25.

$$\frac{d}{dt} \begin{bmatrix} i_{d,pu} \\ i_{q,pu} \end{bmatrix} = \begin{bmatrix} -\frac{\omega_b R_{pu}}{L_{pu}} & \omega \\ -\omega & -\frac{\omega_b R_{pu}}{L_{pu}} \end{bmatrix} \begin{bmatrix} i_{d,pu} \\ i_{q,pu} \end{bmatrix} + \frac{\omega_b}{L} \begin{bmatrix} v_{d,conv,pu} - v_{d,pu} \\ v_{q,conv,pu} - v_{q,pu} \end{bmatrix}$$

(2.25)

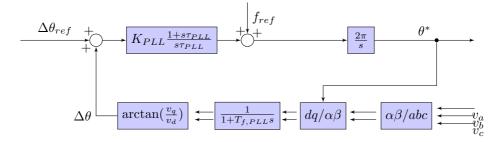

This gives the block diagram of the VSC as shown in the Figure 2.9

The switching in the PWM can be mathematical modeled as a time delay for control manners. The 1.order transfer function approximation for the time delay is as in Equation 2.26 [30].

$$\frac{1}{1+sT_a}\tag{2.26}$$

Where  $T_a$  is half the switching period.

Figure 2.9: Block diagram of VSC

#### 2.3. THE VOLTAGE SOURCE CONVERTER (VSC)

#### State-space model of the LCL circuit

The state space model presented in this thesis is largely based on the work done in [22], and modified to describe the system under investigation. The LC-circuit is described in Equation 2.23 and shown with pu-values in Figure 2.9. To include the capacitor in the filter and the weak grid thevenin equivalent inductance, that influences the point of synchronization, Equation 2.27 and Equation 2.28 are added to the mathematical model.

$$i_{od} = (v_{cd} - v_{od} + \omega L_g i_{oq}) \frac{1}{R_g + sL_g}$$

$$i_{oq} = (v_{cq} - v_{oq} - \omega L_g i_{od}) \frac{1}{R_g + sL_g}$$

(2.27)

$$v_{cd} = (i_d - i_{od} + \omega C v_{cq}) \frac{1}{sC}$$

$$v_{cq} = (i_q - i_{oq} - \omega C v_{cd}) \frac{1}{sC}$$

(2.28)

- 77

Where  $L_g$  and  $R_g$  are the grid side inductance and resistance in the weak grid thevenin equivalent. The state vector, the input vector and the output vector for this LCL-circuit subsystem is shown in Equation 2.29, Equation 2.30 and Equation 2.31 respectively.

$$\mathbf{x_{LCL}} = [i_{d,pu} \ i_{q,pu} \ i_{0,pu} \ v_{cd,pu} \ v_{cq,pu} \ v_{c0,pu} \ i_{od,pu} \ i_{oq,pu} \ i_{o0,pu}]^T$$

(2.29)

$\mathbf{u_{LCL}} = \left[ v_{d,conv,pu} \; v_{q,conv,pu} \; v_{0,conv,pu} \; v_{od,pu} \; v_{oq,pu} \; v_{o0,pu} \; \omega \right]^T$ (2.30)

$$\mathbf{y_{LCL}} = [i_{d,pu} \ i_{q,pu} \ i_{0,pu} \ v_{cd,pu} \ v_{cq,pu} \ v_{c0,pu} \ i_{od,pu} \ i_{oq,pu} \ i_{o0,pu}]^T$$

(2.31)

The zero sequence components is added in the state space model here, but not given any attention since it is not considered in this work and removed from the total state-space model. The matrixes of the state space model for the LCL circuit in a pu-representation is written as in Equation 2.32.

$$\dot{\mathbf{x}}_{\mathbf{LCL}} = \mathbf{A}_{\mathbf{LCL}} \mathbf{x}_{\mathbf{LCL}} + \mathbf{B}_{\mathbf{LCL}} \mathbf{u}_{\mathbf{LCL}} + \mathbf{R}_{\mathbf{LCL}} (\mathbf{x}_{\mathbf{LCL}}, \mathbf{u}_{\mathbf{LCL}})$$

(2.32)

Where:

$$\mathbf{R}_{\mathbf{LCL}} = \begin{bmatrix} \omega i_{q,pu} \\ -\omega i_{d,pu} \\ 0 \\ \omega v_{cq,pu} \\ -\omega v_{cd,pu} \\ 0 \\ \omega i_{oq,pu} \\ -\omega i_{0d,pu} \\ 0 \end{bmatrix}$$

(2.35)

Since the output is equal to the state, the output matrix  $(\mathbf{C})$  becomes the identity matrix  $(\mathbf{I})$ .

#### State space model of the VSC

The state space model is a simplification of the system, and do not include the switches and the physical consequences of the voltage on the converter side of the filter being turned on and off. In the state space representation of the system, the converter is represented as a 1.order time delay approximation as in Equation 2.26. The state space model of the converter then becomes as in Equation 2.37

$$\mathbf{x}_{\mathbf{VSC}} = \frac{d}{dt} \begin{bmatrix} v_{d,conv,pu}^* \\ v_{q,conv,pu}^* \end{bmatrix} = \begin{bmatrix} -\frac{1}{T_a} & 0 \\ 0 & -\frac{1}{T_a} \end{bmatrix} \begin{bmatrix} v_{d,conv,pu}^* \\ v_{q,conv,pu}^* \end{bmatrix} + \frac{1}{T_a} \begin{bmatrix} v_{d,conv,pu} \\ v_{q,conv,pu} \end{bmatrix}$$

(2.37)

Where  $v_{dq,conv,pu}^*$  is the delayed converter voltage.

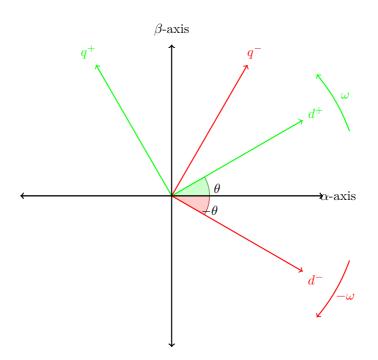

### 2.3.6 Mathematical model for unbalanced system

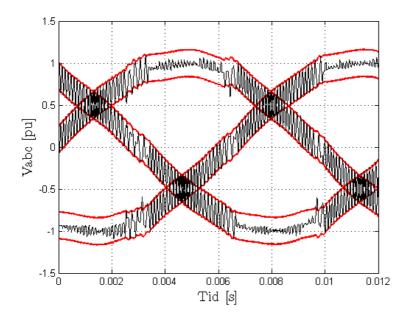

In unbalanced systems the mathematical model can be divided into the positive and negative sequence. The mathematical model for an unbalanced system has been derived in [21] and [35]. Based on the transformation of the unbalanced system into the two synchronous rotating reference frames, given in Equation 2.47 and 2.48, and the current and voltage in the positive and negative sequence, given in Equation 2.6. Since the simplification of the mathematical expression is already explained in Section 2.3.5, the derivation is skipped here, and the simplified pu-representation of the mathematical expression is shown in Equation 2.38.