### Design of a Harmonically Tuned Two-Stage Broadband Power Amplifier in Discrete GaN Technology

A Harmonic Loadpull and Harmonic Termination Approach

### Glenn Flø Karlsen

Master of Science in Electronics Submission date: July 2018 Supervisor: Morten Olavsbråten, IES

Norwegian University of Science and Technology Department of Electronic Systems

Dedicated to my Mom, my Dad and my Sister for always believing in me

## Preface

This Master's Thesis has been developed for the Department of Electronic Systems at NTNU with guidance from associate professor Morten Olavsbråten. The intent of this thesis were to go in depth in the design procedures of a two-stage power amplifier, contemplating the harmonic loadpull and sourcepull design techniques. The amplifier were intended for further work incorporating dynamic drain and gate biasing in envelope tracking applications. The simulation results in this Master's Thesis was obtained using Keysight's Advanced Design System (ADS) software and the discrete gallium nitride high electron mobility transistors from Wolfspeed.

### Acknowledgment

I would like to thank my supervisor Associate Professor Morten Olavsbråten for his guidance and support throughout the project. His valuable advices, knowledge and passion for the subject has been of great importance and an exceedingly motivational factor.

I would also like to thank my fellow master students and classmates for all the help, advices and discussions. It has truly been encouraging to work with you!

Finally, I am grateful to my family and friends who have supported me along the way.

Glenn Flø Karlsen Trondheim, July 2018

### Summary

In this master's thesis a two-stage broadband power amplifier, along with the corresponding separate driver and power stages, has been designed with an in-depth analysis of the harmonic source- and loadpull methods and the harmonic termination technique. The power amplifiers were subsequently measured.

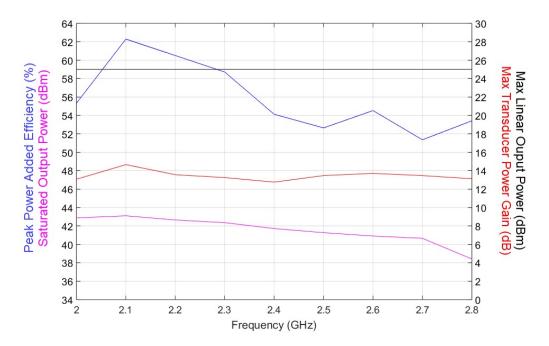

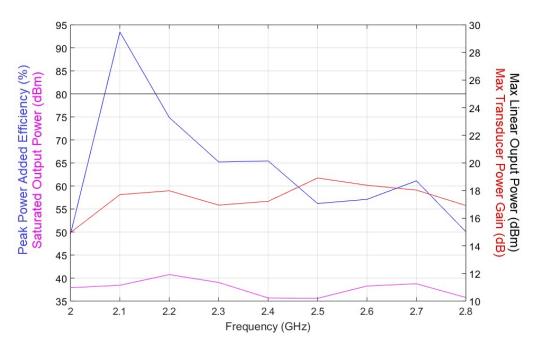

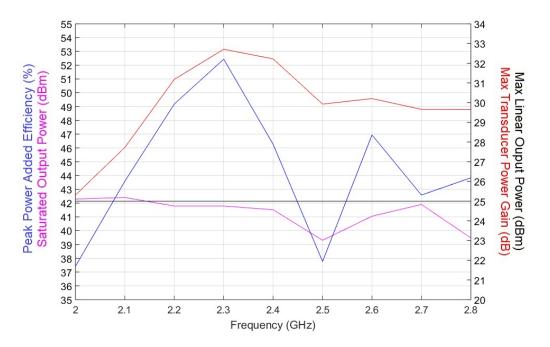

The power stage amplifier exhibit a mean transducer power gain of 13.5dB, a maximum linear output power of 25dBm, a mean saturated output power of 41.5dBm, and a mean peak Power Added Efficiency (PAE) of 54% at a quiescent voltage bias of 28V and a quiescent current bias of 200mA; The driver stage amplifier exhibit a mean transducer power gain of 17.5dB, a maximum linear output power of 25dBm, a mean saturated output power of 37.8dBm, and a mean peak PAE of 55% at a quiescent voltage bias of 28V and a quiescent current bias of 165mA; and the two-stage amplifier exhibit a mean transducer power gain of 29.8dB, a maximum linear output power of 25dBm, a mean saturated output power of 41.3dBm, and a mean peak PAE of 44.5% at a quiescent voltage bias of 28V and a quiescent current bias of 165mA and 200mA.

The power amplifiers were designed for 2.4GHz application with a bandwidth of 800MHz, but also exhibited promising performance down to 1GHz given some modifications, thus virtually doubling the intended bandwidth. The power amplifiers were designed using the gallium nitride high electron mobility transistors CGH40006P and CGH40010F from Wolfspeed.

### Sammendrag

I denne masteroppgaven har en to-stegs bredbåndet effektforsterker, med tilhørende separate driver- og effektsteg, blitt designet ved bruk av en grundig analyse gjennom metodene for harmonisk kilde- og lastvariasjon, og teknikker for harmonisk terminering. Effektforsterkerene har deretter blitt målt.

Effektstegsforsterkeren viste en gjennomsnittlig effektvinning på 13.5dB, en maximal lineær uteffekt på 25dBm, en gjennomsnittlig mettet uteffekt på 41.5dBm, og en gjennomsnittlig maksimal tilført effektivitet på 54% ved en hvilespenning på 28V og en hvilestrøm på 200mA; driverstegsforsterkeren viste en gjennomsnittlig effektvinning på 17.5dB, en maximal lineær uteffekt på 25dBm, en gjennomsnittlig mettet uteffekt på 37.8dBm, og en gjennomsnittlig maksimal tilført effektivitet på 55% ved en hvilespenning på 28V og en hvilestrøm på 165mA; og to-stegs forsterkeren viste en gjennomsnittlig effktvinning på 29.8dB, en maximal lineær uteffekt på 25dBm, en gjennomsnittlig mettet uteffekt på 41.3dBm, og en gjennomsnittlig maksimal tilført effektivitet på 44.5% ved en hvilespenning på 28V og en hvilestrøm på 165mA og å 200mA.

Effektforsterkerene ble designet for 2.4GHz applikasjoner med en båndbredde på 800MHz, men viste også lovende ytelse ned til 1GHz gitt noen modifikasjoner, og derav så og si doblet tiltenkt båndbredde. Effektforsterkerene ble deignet ved bruk av galliumnitrid høy elektronmobilitet transistorene CGH40006P og CGH40010F fra Wolfspeed.

# Abbreviations

| ADS    | Advanced Design System                      |

|--------|---------------------------------------------|

| BJT    | Bipolar Junction Transistor                 |

| DBN    | Drain Bias Network                          |

| DUT    | Device Under Test                           |

| FET    | Field Effect transistor                     |

| GBN    | Gate Bias Network                           |

| HEMT   | High Electron Mobility Transistor           |

| HLP    | Harmonic Loadpull                           |

| HSP    | Harmonic Sourcepull                         |

| IMD    | Intermodulation Distortion                  |

| IMN    | Input Matching Network                      |

| IP3    | Third-order Intercept Point                 |

| MAG    | Maximum Available Gain                      |

| MESFET | Metal-Semiconductor Field Effect Transistor |

| MSG    | Maximum Stable Gain                         |

| OMN    | Output Matching Network                     |

| PAE    | Power Added Efficiency                      |

| PCB    | Printed Circuit Board                       |

| PDK    | Process Design Kit                          |

| TOI    | Third-order Intercept Point                 |

# **Table of Contents**

|   | Prefe | ace      |                                                 | i |

|---|-------|----------|-------------------------------------------------|---|

|   | Sum   | mary     |                                                 | i |

|   | Abbi  | reviatio | ns ii                                           | X |

|   | List  | of Figur | es                                              | i |

|   | List  | of Table | <i>s</i>                                        | i |

| 1 | Intro | oductio  | n                                               | 3 |

|   | 1.1   | Goals    | and requirements                                | 1 |

|   | 1.2   | Struct   | ure of the Thesis                               | 5 |

| 2 | Bacl  | kgroun   | l and Theory                                    | 9 |

|   | 2.1   | Transi   | stor technology                                 | 9 |

|   | 2.2   | GaN T    | echnology                                       | ) |

|   | 2.3   | Transi   | stor types                                      | 1 |

|   |       | 2.3.1    | Metal-Semiconductor Field Effect Transistors 12 | 1 |

|   |       | 2.3.2    | High Electron Mobility Transistors    1         | 1 |

|   | 2.4   | High-f   | requency Power Amplifier properties             | 2 |

|   |       | 2.4.1    | Stability                                       | 3 |

|   |       | 2.4.2    | Power Gain                                      | 5 |

|   |       | 2.4.3    | Linearity                                       | 9 |

|   |       | 2.4.4    | Efficiency                                      | 2 |

|   | 2.5   | Ampli    | fier Design Techniques                          | 3 |

|   |                   | 2.5.1                                                                                                         | Power Amplifier Classes | 23                                                 |

|---|-------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------|

|   |                   | 2.5.2                                                                                                         | Loadline Method         | 25                                                 |

|   |                   | 2.5.3                                                                                                         | Loadpull                | 27                                                 |

| 3 | Prel              | iminary                                                                                                       | y design considerations | 33                                                 |

|   | 3.1               | Transi                                                                                                        | stors                   | 33                                                 |

|   |                   | 3.1.1                                                                                                         | Power Stage transistor  | 34                                                 |

|   |                   | 3.1.2                                                                                                         | Driver Stage transistor | 35                                                 |

|   | 3.2               | Equip                                                                                                         | ment                    | 36                                                 |

|   |                   | 3.2.1                                                                                                         | Connectors              | 36                                                 |

|   |                   | 3.2.2                                                                                                         | Heatsink                | 37                                                 |

|   |                   | 3.2.3                                                                                                         | Circuit substrate       | 37                                                 |

|   |                   | 3.2.4                                                                                                         | Transistor clamps       | 38                                                 |

|   |                   | 3.2.5                                                                                                         | Component library       | 38                                                 |

|   | 3.3               | Desigr                                                                                                        | n of the Bias Network   | 39                                                 |

|   | 3.4               | Summ                                                                                                          | ary                     | 40                                                 |

|   |                   |                                                                                                               |                         |                                                    |

| 4 | Pow               | er Amp                                                                                                        | lifier Stage design     | 45                                                 |

| 4 | <b>Pow</b><br>4.1 | _                                                                                                             | lifier Stage design     |                                                    |

| 4 |                   | Transi                                                                                                        |                         | 45                                                 |

| 4 | 4.1               | Transi                                                                                                        | stor loadline analysis  | 45                                                 |

| 4 | 4.1               | Transi<br>Stabili                                                                                             | stor loadline analysis  | 45<br>47                                           |

| 4 | 4.1               | Transia<br>Stabili<br>4.2.1                                                                                   | stor loadline analysis  | 45<br>47<br>47                                     |

| 4 | 4.1               | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3                                                                 | stor loadline analysis  | 45<br>47<br>47<br>49                               |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3                                                                 | stor loadline analysis  | 45<br>47<br>47<br>49<br>49                         |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-                                                       | stor loadline analysis  | 45<br>47<br>49<br>49<br>51                         |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-<br>4.3.1                                              | stor loadline analysis  | 45<br>47<br>49<br>49<br>51<br>51                   |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-<br>4.3.1<br>4.3.2                                     | stor loadline analysis  | 45<br>47<br>49<br>49<br>51<br>51<br>52             |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-<br>4.3.1<br>4.3.2<br>4.3.3                            | stor loadline analysis  | 45<br>47<br>49<br>49<br>51<br>51<br>52<br>56       |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                   | stor loadline analysis  | 45<br>47<br>49<br>51<br>51<br>52<br>56<br>57       |

| 4 | 4.1<br>4.2        | Transis<br>Stabili<br>4.2.1<br>4.2.2<br>4.2.3<br>Large-<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6 | stor loadline analysis  | 45<br>47<br>49<br>51<br>51<br>52<br>56<br>57<br>59 |

|   | 5.1  | Transis   | stor loadline analysis                       | 67  |

|---|------|-----------|----------------------------------------------|-----|

|   | 5.2  | Stabili   | ty analysis                                  | 69  |

|   |      | 5.2.1     | Small-signal stability                       | 69  |

|   |      | 5.2.2     | Stabilization network                        | 70  |

|   |      | 5.2.3     | Stability and small-signal gain optimization | 71  |

|   | 5.3  | Large-    | signal analysis                              | 73  |

|   |      | 5.3.1     | Large-signal characteristics                 | 73  |

|   |      | 5.3.2     | Harmonic loadpull                            | 74  |

|   |      | 5.3.3     | Output Network impedance trajectory          | 78  |

|   |      | 5.3.4     | Design of the Output Matching Network        | 79  |

|   |      | 5.3.5     | Harmonic Sourcepull                          | 82  |

|   |      | 5.3.6     | Design of the Input Matching Network         | 82  |

|   | 5.4  | Summ      | ary and discussion                           | 86  |

| 6 | Two  | -stage A  | mplifier design                              | 89  |

|   | 6.1  | Cascad    | led two-stage amplifier                      | 89  |

|   | 6.2  | Interst   | age network design                           | 91  |

|   | 6.3  | Summ      | ary and discussions                          | 94  |

| 7 | Mea  | sureme    | nts                                          | 99  |

|   | 7.1  | Small-    | signal measurements                          | 99  |

|   |      | 7.1.1     | Measurement setup                            | 99  |

|   |      | 7.1.2     | Power stage amplifier characteristics        | 100 |

|   |      | 7.1.3     | Driver stage amplifier characteristics       | 101 |

|   |      | 7.1.4     | Two-stage amplifier characteristics          | 102 |

|   | 7.2  | Large-    | signal measurements                          | 103 |

|   |      | 7.2.1     | Measurement setup                            | 103 |

|   |      | 7.2.2     | Calibration                                  | 104 |

|   |      | 7.2.3     | Measurement summary                          | 108 |

| 8 | Disc | cussion . |                                              | 115 |

| Re | References |                                           |  |  |

|----|------------|-------------------------------------------|--|--|

| Aj | Appendices |                                           |  |  |

| A  | Sim        | ulation setups                            |  |  |

|    | A.1        | Transistor I-V Characteristics            |  |  |

|    | A.2        | Network S-Parameters                      |  |  |

|    | A.3        | Amplifier Large-signal Characteristics    |  |  |

|    | A.4        | Harmonic Load- and Sourcepull             |  |  |

|    | A.5        | Network Impedance Trajectory Optimization |  |  |

| B  | Larg       | e-signal measurement results              |  |  |

|    | B.1        | Power stage amplifier                     |  |  |

|    | B.2        | Driver stage amplifier                    |  |  |

|    | B.3        | Two-stage amplifier                       |  |  |

| С  | Pho        | tos of the Amplifiers                     |  |  |

|    | C.1        | Power Stage Amplifier                     |  |  |

|    | C.2        | Driver Stage Amplifer                     |  |  |

|    | C.3        | Two-stage Amplifier                       |  |  |

# **List of Figures**

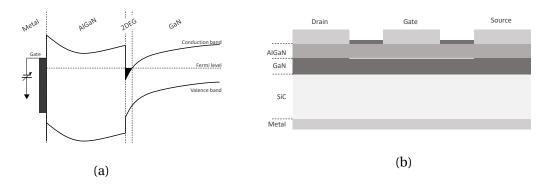

| 2.1  | The (a) Band diagram [7] and (b) layer structure of an AlGaN/GaN on SiC High            |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | Electron Mobility Transistor (HEMT).                                                    | 12 |

| 2.2  | The general transistor amplifier circuit [23, p.198]                                    | 13 |

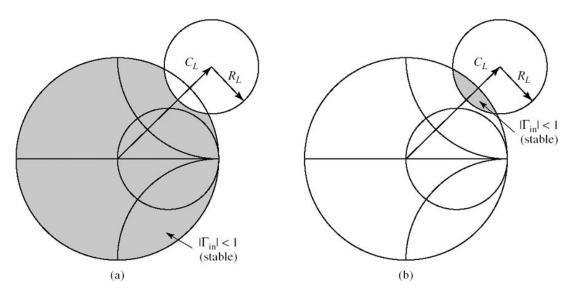

| 2.3  | The regions of stability for a conditionally stable device where (a) $ S_{11}  < 1$ and |    |

|      | (b) $ S_{11}  > 1$ . [23]                                                               | 14 |

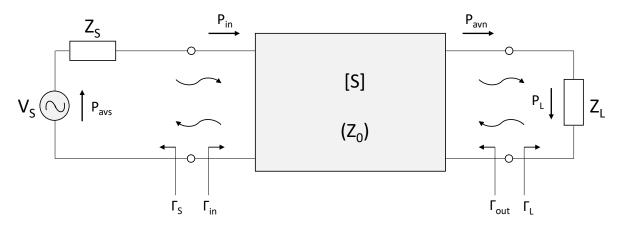

| 2.4  | A two-port network with general source and load impedances, indicating power            |    |

|      | available and delivered in the components.                                              | 16 |

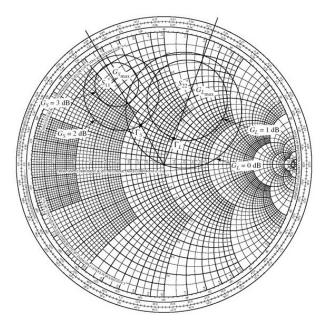

| 2.5  | Constant source and load gain circles [23]                                              | 18 |

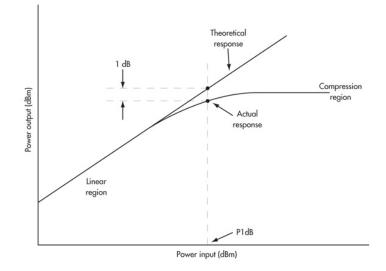

| 2.6  | The 1 dB compression point for a nonlinear amplifier [11]                               | 20 |

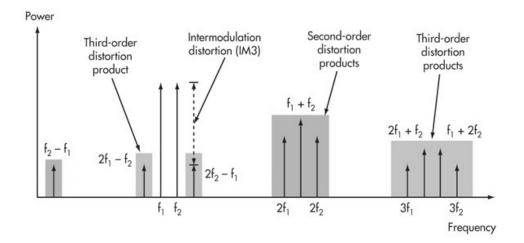

| 2.7  | Output spectrum with intermodulation products [13]                                      | 21 |

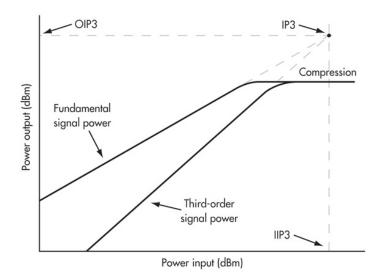

| 2.8  | Third-Order intercept point [11]                                                        | 21 |

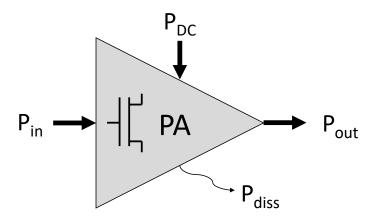

| 2.9  | Power flow diagram of a Power Amplifier                                                 | 22 |

| 2.10 | DC quiescent bias point for the linear amplifier classes. [5]                           | 24 |

| 2.11 | Harmonically tuned class F power amplifier                                              | 25 |

| 2.12 | (a) Schematic of general transistor amplifier [5] and (b) its class A loadline          |    |

|      | superimposed on the I-V characteristics.                                                | 26 |

| 2.13 | (a) The loadlines of different load resistances superimposed on the I-V charac-         |    |

|      | teristics, and (b) the representation of the same load resistances in the smith         |    |

|      | chart                                                                                   | 27 |

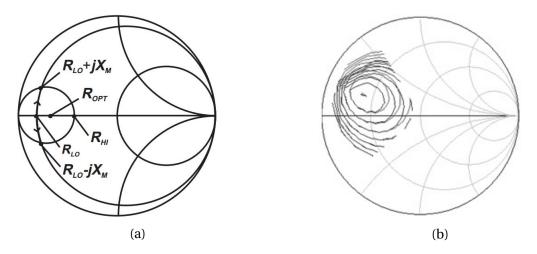

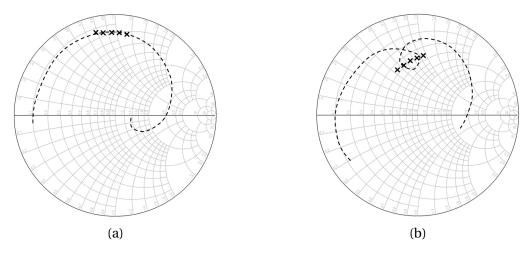

| 2.14 | (a) Constant resistance and conductance circles at $P_{opt}/p$ [8]. (b) Loadpull        |    |

|      | contours affected by parasitics.                                                        | 28 |

| 2.10 | inductions of the (a) through the (b) twittin pedance indefining teening teening | 20 |

|------|----------------------------------------------------------------------------------|----|

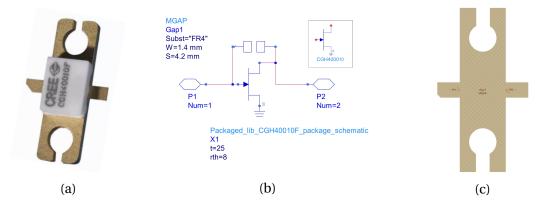

| 3.1  | (a) A picture of the screw-down flange package, (b) the modified simulation      |    |

|      | schematic, and (c) the layout model of Wolfspeed's CGH40010F, 10W RF Power       |    |

|      | CaN HEMT                                                                         | 3/ |

20

37

2.15 Illustrations of the (a) through, and (b) twirl impedance matching techniques

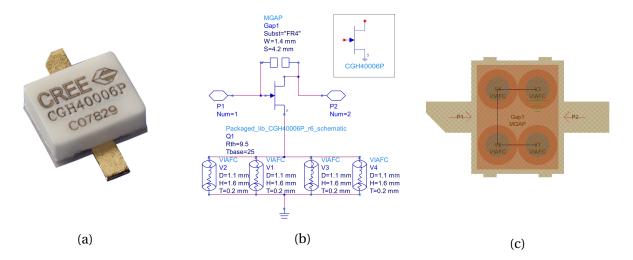

3.2 (a) A picture of the screw-down flange package, (b) the modified simulation schematic, and (c) the layout model of Wolfspeed's CGH40006P, 6WW RF Power GaN HEMT.

35

3.3 Picture of the SMA607B-12 connectors used for board-to-wire connections. . . 36

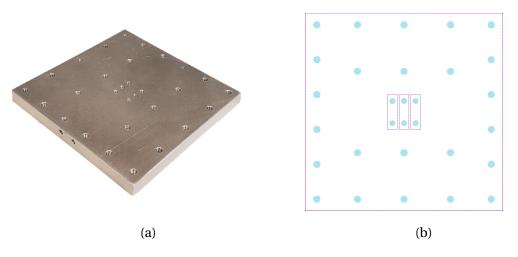

(a) Isometric view and (b) layout of the aluminium plate heatsink.

3.5 Pictures of the clamps used for the (a) power stage and the (b) driver stage . . 38

3.4

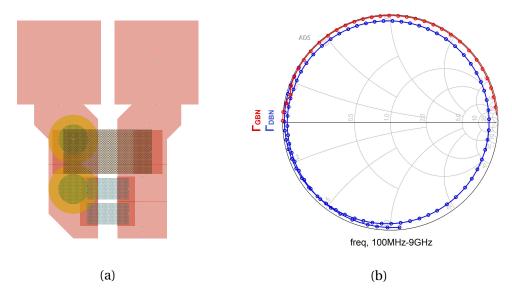

3.6 (a) The bias network layout with both the Murata and Johanson capacitors, and (b) the reflection coefficients of the Drain Bias Network (DBN) and Gate Bias Network (GBN).

40

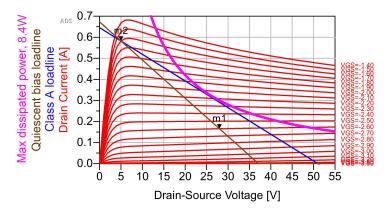

# 4.1 I-V characteristics of the CGH40010F transistor with superimposed maximum power dissipation, class A loadline, and loadline at quiescent bias m1. . . . . . 46

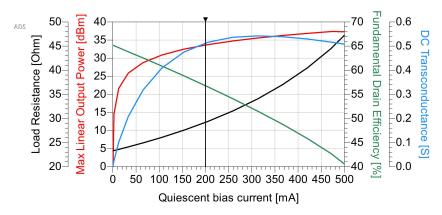

- 4.2 Maximum linear output power, fundamental drain efficiency and DC transconductance versus quiescent bias currents between class A and class B. . . . . . . 46

- 4.5 Simulation schematic of the stabilization network for the CGH40010F transistor. 49

- 4.7 (a) Constant matched gain circles and (b) small-signal gain at  $I_{DQ} = 200 m A$ . 50

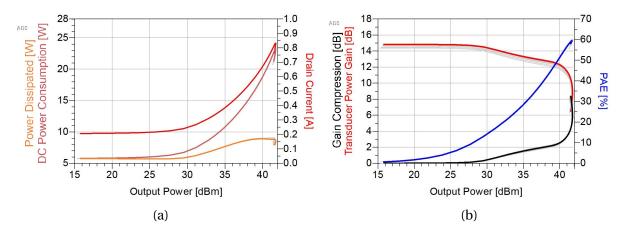

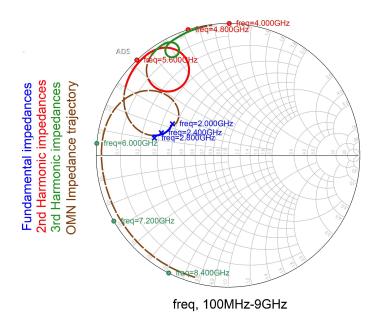

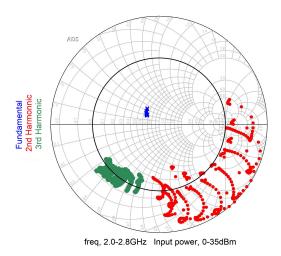

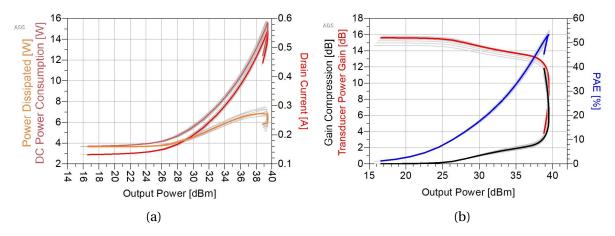

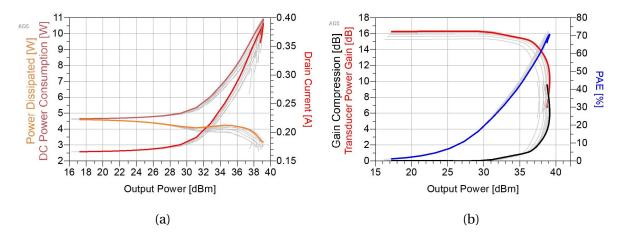

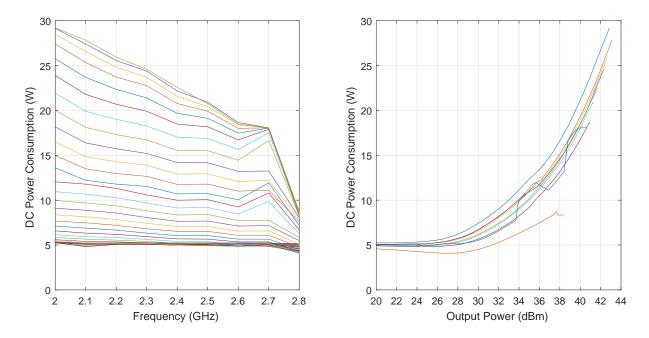

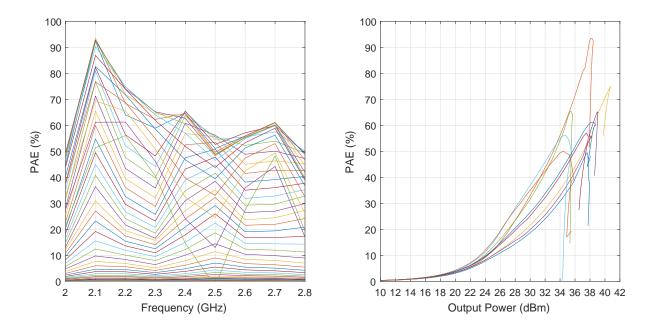

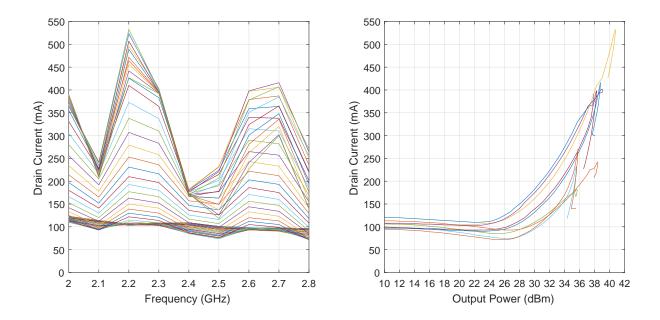

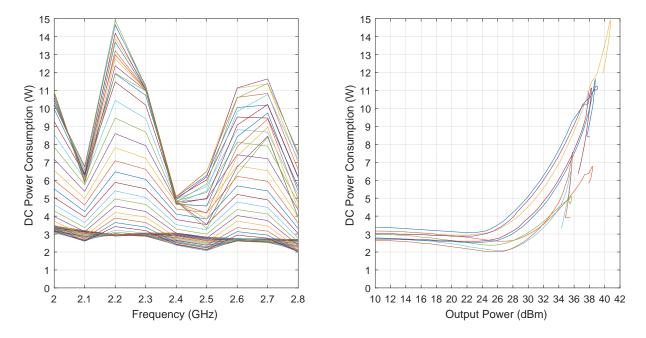

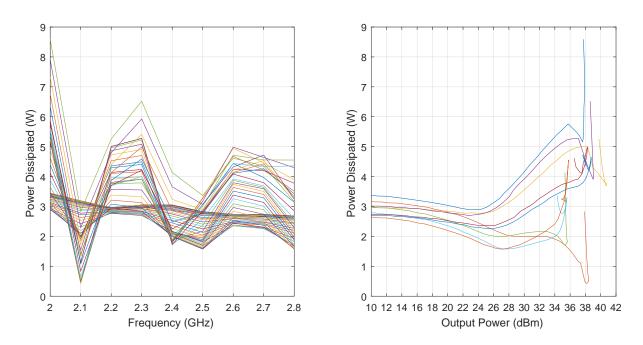

- 4.8 (a) Power Dissipated, DC Power Consumption and Drain Current, and (b) Transducer Power Gain, Gain compression and PAE of the stabilized transistor, for the frequency range 2.0-2.8GHz, highlighting the center frequency of 2.4GHz.

51

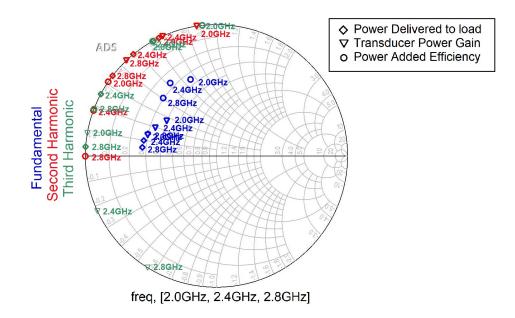

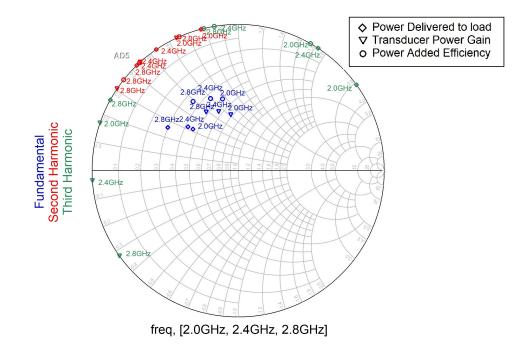

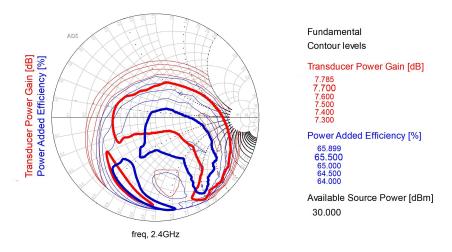

- 4.9 Optimal Harmonic Loadpull data for Power delivered, Transducer Power Gain and PAE at 2.0GHz, 2.4GHz and 2.8GHz.52

| 4.10 | Desired load impedances, superimposed on the optimal impedances from fig-      |    |

|------|--------------------------------------------------------------------------------|----|

|      | ure 4.9                                                                        | 54 |

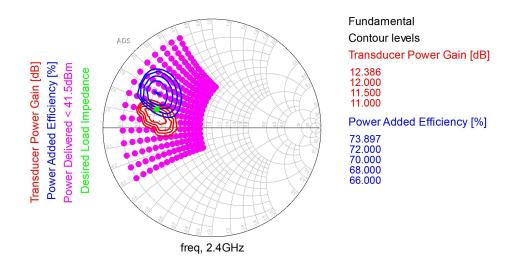

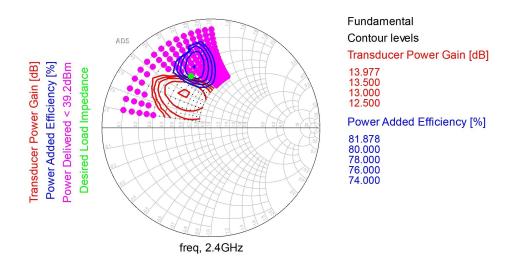

| 4.11 | Fundamental loadpull contours for 41.5dBm desired power delivered at the       |    |

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .   | 55 |

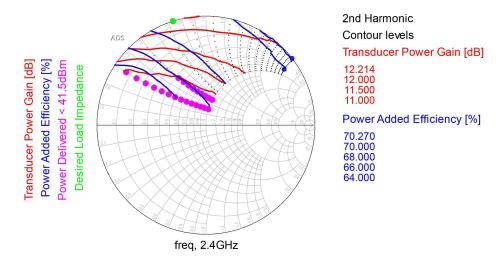

| 4.12 | 2nd Harmonic loadpull contours for 41.5dBm desired power delivered at the      |    |

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .   | 55 |

| 4.13 | 3rd Harmonic loadpull contours for 41.5dBm desired power delivered at the      |    |

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .   | 55 |

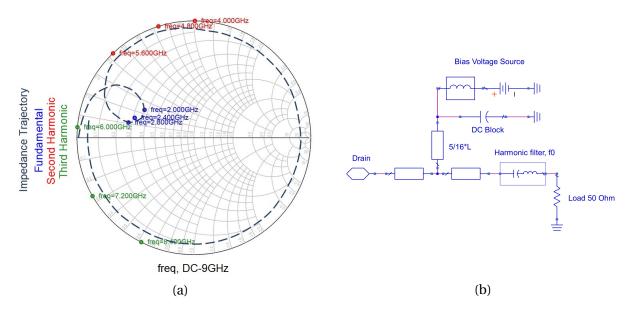

| 4.14 | The (a) desired impedance trajectory and the (b) preliminary schematic, of     |    |

|      | the output matching network.                                                   | 56 |

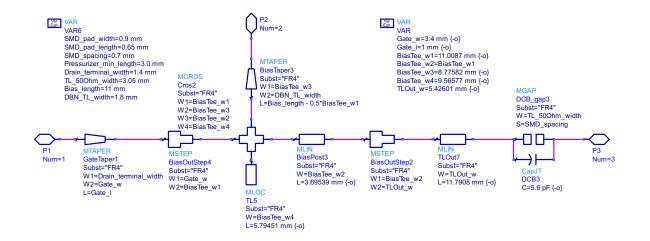

| 4.15 | Schematic simulation model of the Output Matching Network (OMN)                | 57 |

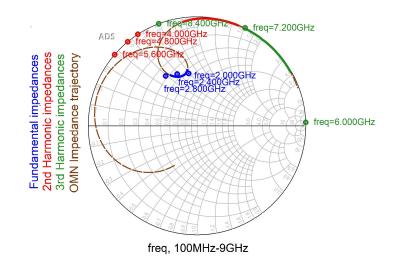

| 4.16 | OMN impedance trajectory match for the desired load impedances from the        |    |

|      | OMN network in figure 4.15                                                     | 58 |

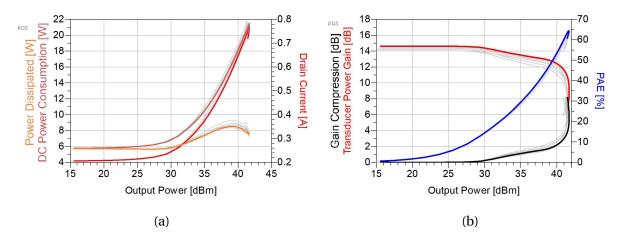

| 4.17 | (a) Power Dissipated, DC Power Consumption and Drain Current, and (b)          |    |

|      | Transducer Power Gain, Gain compression and PAE of the stabilized transis-     |    |

|      | tor with OMN, for the frequency range 2.0-2.8GHz, highlighting the center fre- |    |

|      | quency of 2.4GHz.                                                              | 58 |

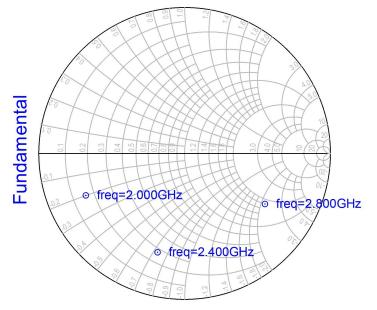

| 4.18 | Desired source impedances of the of the driver stage                           | 59 |

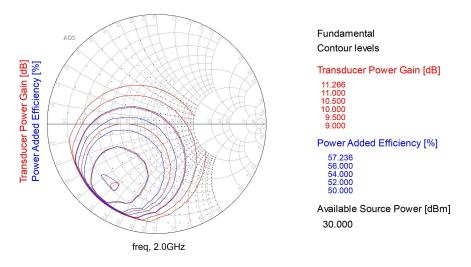

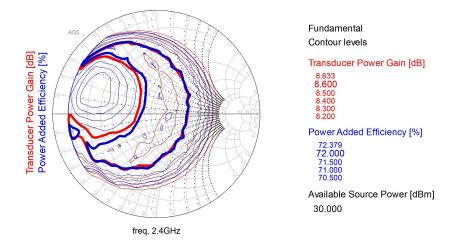

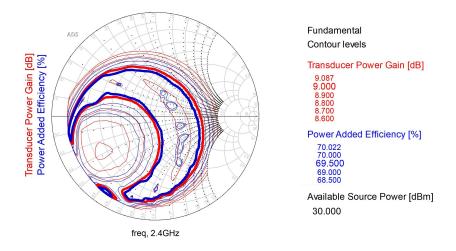

| 4.19 | Fundamental sourcepull contours for 30dBm available source power at 2.0GHz.    | 60 |

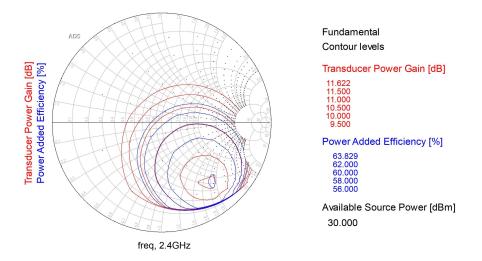

| 4.20 | Fundamental sourcepull contours for 30dBm available source power at 2.4GHz.    | 60 |

| 4.21 | Fundamental sourcepull contours for 30dBm available source power at 2.8GHz.    | 60 |

| 4.22 | The simulation schematic of the power stage Input Matching Network (IMN).      | 61 |

| 4.23 | Impedance trajectory of the IMN of the power stage.                            | 62 |

| 4.24 | Impedances presented to the intrinsic nodes of the transistor.                 | 62 |

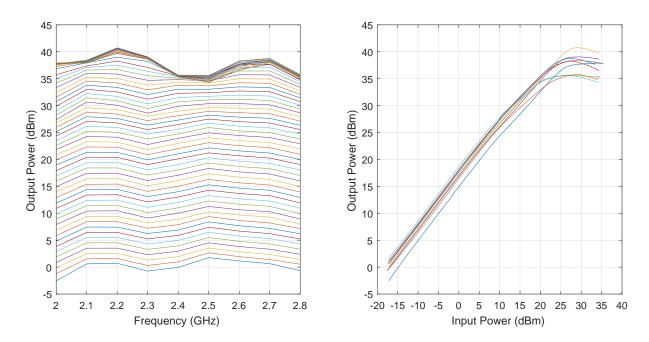

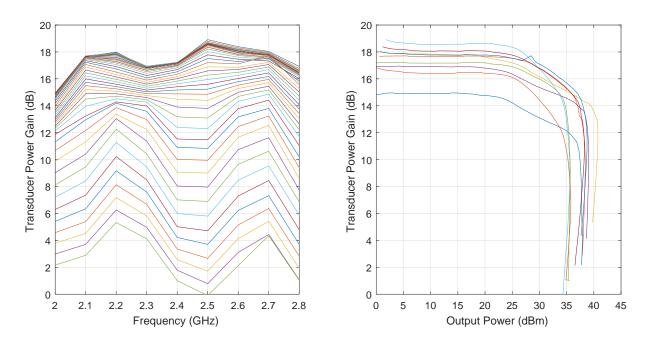

| 4.25 | (a) Power Dissipated, DC Power Consumption and Drain Current, and (b)          |    |

|      | Transducer Power Gain, Gain compression and PAE of the power stage, for        |    |

|      | the frequency range 2.0-2.8GHz, highlighting the center frequency of 2.4GHz.   | 63 |

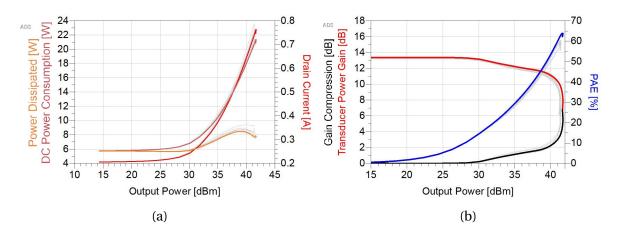

| 4.26 | The transducer power gain, gain compression and PAE for (a) 28dBm and (b)      |    |

|      | 41dBm desired output power, from 100MHz to 5GHz                                | 63 |

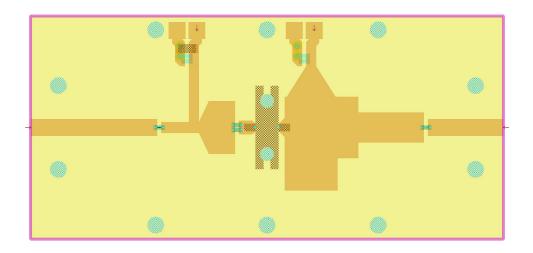

| 4.27 | Layout of the Power stage.                                                     | 63 |

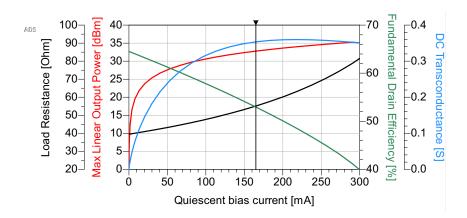

| 5.1  | $\label{eq:intermediate} I-VCharacteristicsoftheCGH40006Ptransistorwithsuperimposedmaximum$ |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | power dissipation, class A loadline and loadline at the desired quiescent bias              |    |

|      | at marker m1                                                                                | 68 |

| 5.2  | Maximum linear output power, fundamental drain efficiency and DC transcon-                  |    |

|      | ductance versus quiescent bias currents between class A and class B                         | 68 |

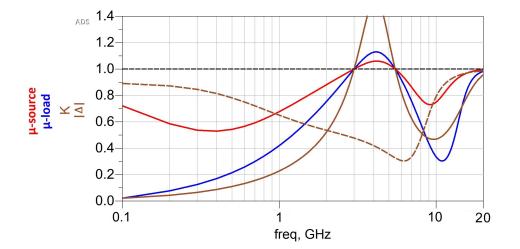

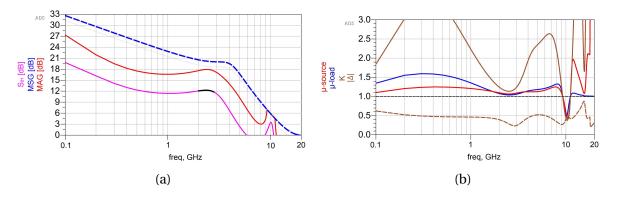

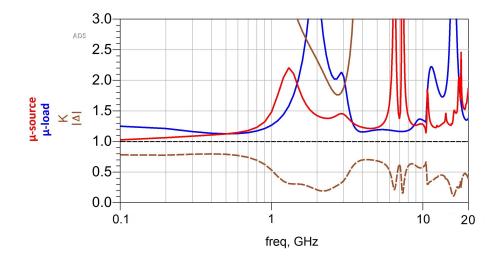

| 5.3  | Stability factors of the CGH40006P transistor at the most unstable bias; $I_{DQ}$ =         |    |

|      | $20mA, V_{GSQ} = -3.11V.$                                                                   | 69 |

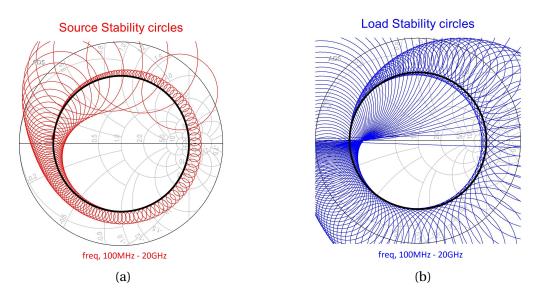

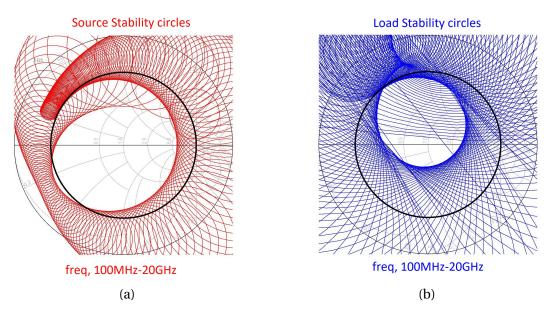

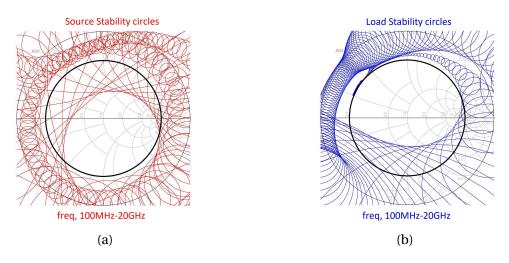

| 5.4  | The (a) source and (b) load stability circles at $I_{DQ} = 20 mA$                           | 70 |

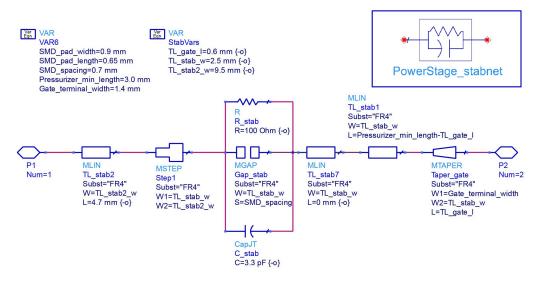

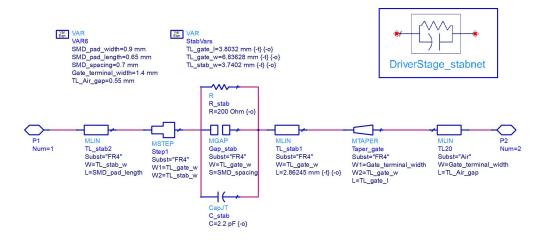

| 5.5  | Simulation schematic of the stabilization network for the CGH40006P transistor.             | 71 |

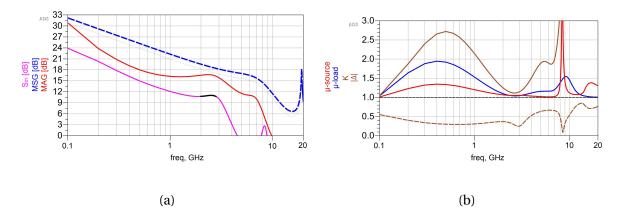

| 5.6  | (a) Small-signal gain and (b) stability factors of the CGH40006P transistor with            |    |

|      | the optimized stabilization network at $I_{DQ} = 20 mA$                                     | 71 |

| 5.7  | The (a) source and (b) load stability circles at $I_{DQ} = 20 mA$ , for the transistor      |    |

|      | with stabilization network as shown in figure 5.5                                           | 72 |

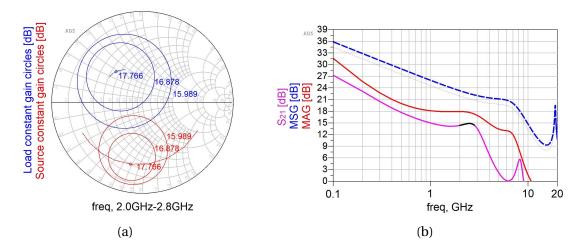

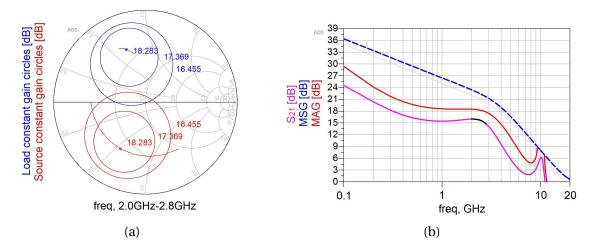

| 5.8  | (a) Constant matched gain circles and (b) small-signal gain at $I_{DQ} = 165 mA$ .          | 72 |

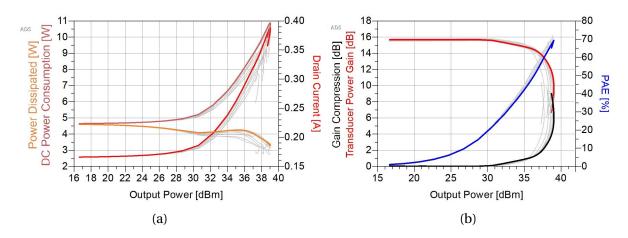

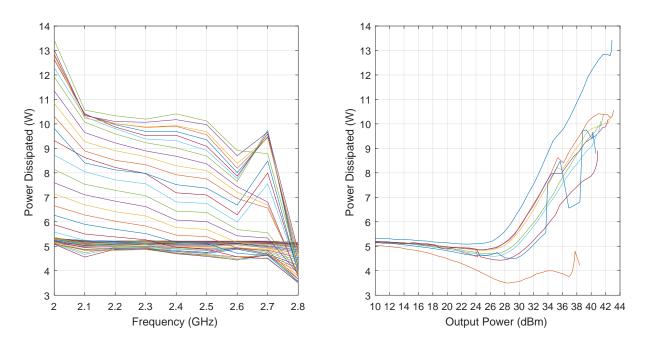

| 5.9  | (a) Power Dissipated, DC Power Consumption and Drain Current, and (b)                       |    |

|      | Transducer Power Gain, Gain compression and PAE of the stabilized transis-                  |    |

|      | tor, for the frequency range 2.0-2.8GHz, highlighting the center frequency of               |    |

|      | 2.4GHz                                                                                      | 73 |

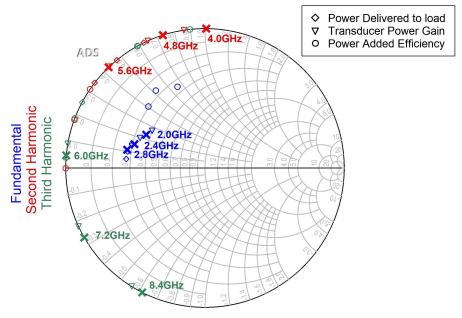

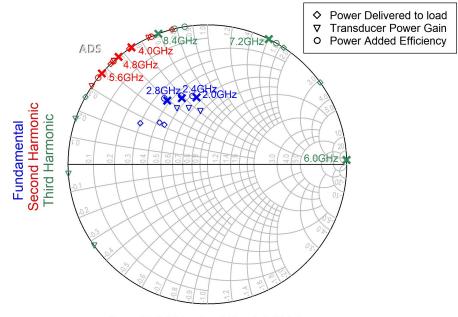

| 5.10 | Optimal Harmonic Loadpull data for Power delivered, Transducer Power Gain                   |    |

|      | and PAE at 2.0GHz, 2.4GHz and 2.8GHz                                                        | 74 |

| 5.11 | Desired load impedances, superimposed on the optimal impedances from fig-                   |    |

|      | ure 5.10                                                                                    | 76 |

| 5.12 | Fundamental loadpull contours for 39.2dBm desired power delivered at the                    |    |

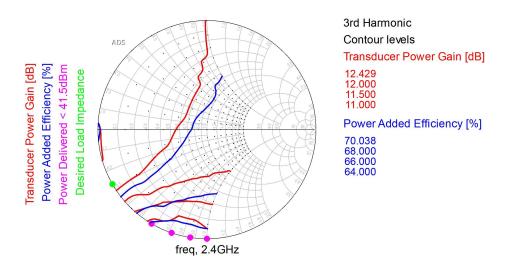

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .                | 77 |

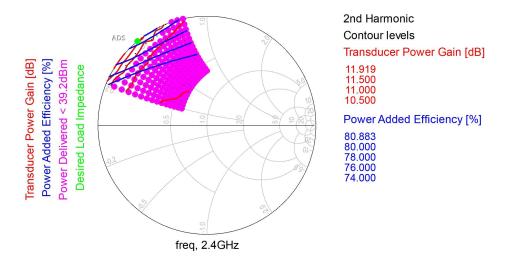

| 5.13 | 2nd Harmonic loadpull contours for 39.2dBm desired power delivered at the                   |    |

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .                | 77 |

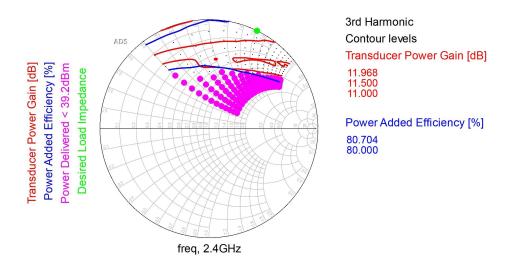

| 5.14 | 3rd Harmonic loadpull contours for 39.2dBm desired power delivered at the                   |    |

|      | center frequency, when terminated in the desired load impedances. $\ldots$ .                | 77 |

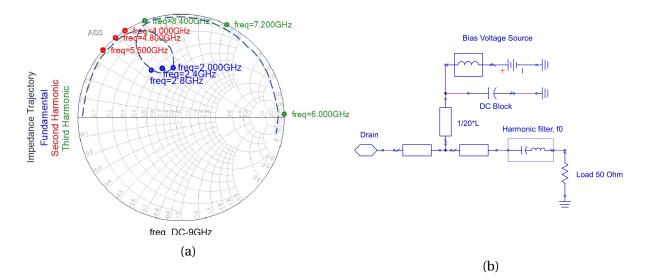

| 5.15 | The (a) desired impedance trajectory and the (b) preliminary schematic, of                  |    |

|      | the output matching network.                                                                | 78 |

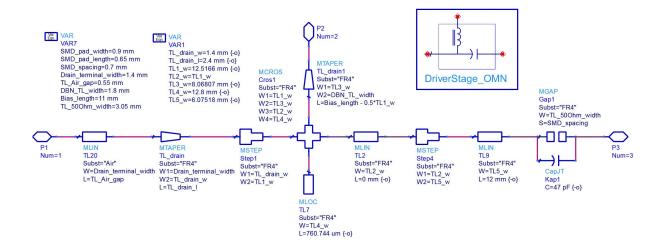

| 5.16 | Schematic simulation model of the OMN.                                                      | 79 |

| 5.17 | OMN impedance trajectory match for desired load impedances from the OMN           |    |

|------|-----------------------------------------------------------------------------------|----|

|      | network in figure 5.16                                                            | 80 |

| 5.18 | (a) Power Dissipated, DC Power Consumption and Drain Current, and (b)             |    |

|      | Transducer Power Gain, Gain compression and PAE of the stabilized transis-        |    |

|      | tor with OMN, for the frequency range 2.0-2.8GHz, highlighting the center fre-    |    |

|      | quency of 2.4GHz.                                                                 | 80 |

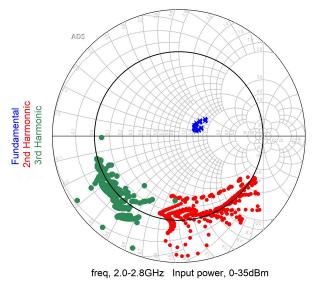

| 5.19 | Fundamental sourcepull contours for 30dBm available source power at 2.0GHz.       | 81 |

| 5.20 | Fundamental sourcepull contours for 30dBm available source power at 2.4GHz.       | 81 |

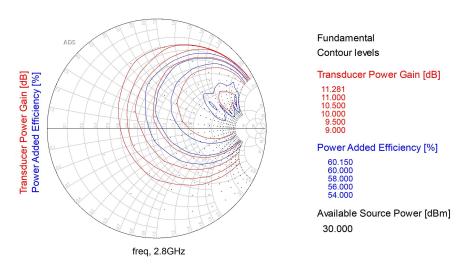

| 5.21 | Fundamental sourcepull contours for 30dBm available source power at 2.8GHz.       | 81 |

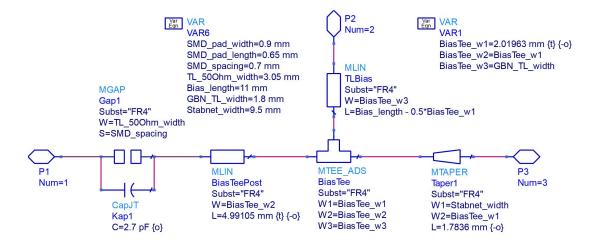

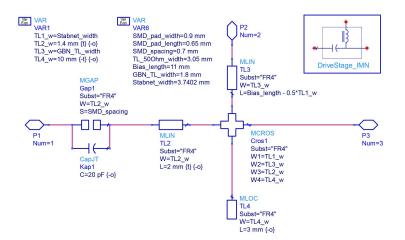

| 5.22 | Simulation schematic of the driver stage IMN.                                     | 82 |

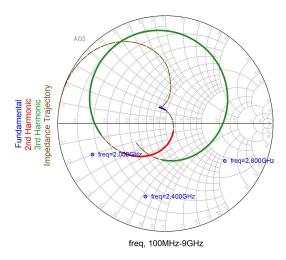

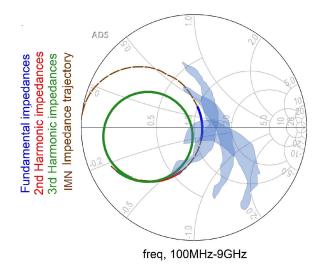

| 5.23 | Impedance trajectory of the driver stage IMN, and superimposed optimal fun-       |    |

|      | damental contour plots.                                                           | 83 |

| 5.24 | Caption                                                                           | 83 |

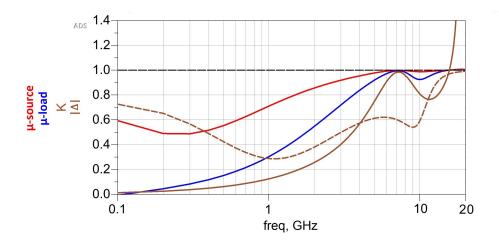

| 5.25 | The stability factors of the entire driver stage, showing unconditional stability |    |

|      | between 100MHz and 20GHz.                                                         | 84 |

| 5.26 | (a) Power Dissipated, DC Power Consumption and Drain Current, and (b)             |    |

|      | Transducer Power Gain, Gain compression and PAE of the power stage, for           |    |

|      | the frequency range 2.0-2.8GHz, highlighting the center frequency of 2.4GHz.      | 85 |

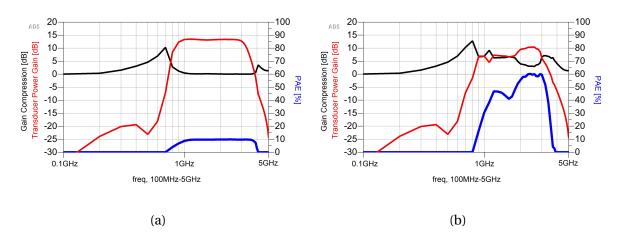

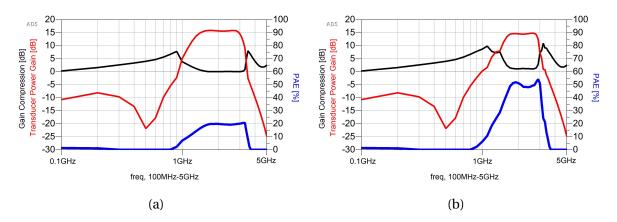

| 5.27 | The transducer power gain, gain compression and PAE for (a) 30dBm and (b)         |    |

|      | 36dBm desired output power, from 100MHz to 5GHz                                   | 85 |

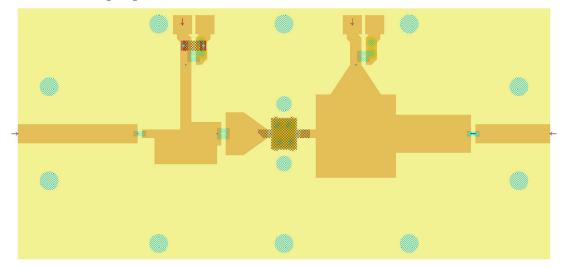

| 5.28 | Layout of the Driver stage.                                                       | 85 |

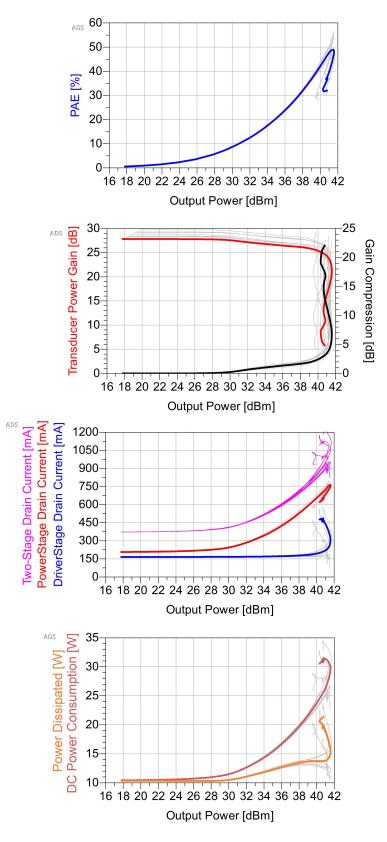

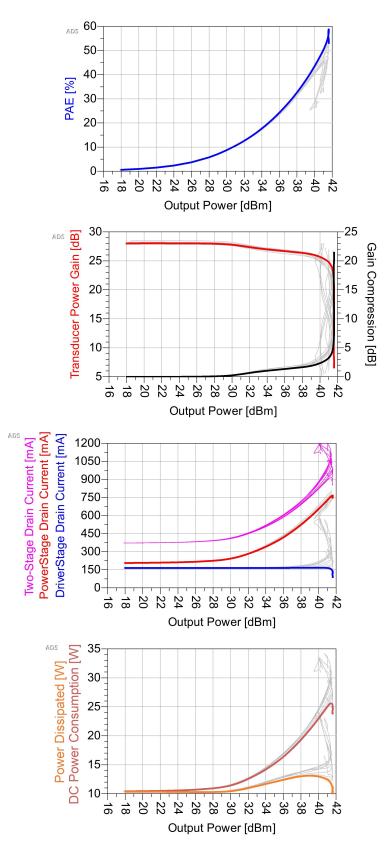

| 6.1  | PAE, Transducer Power Gain, Gain compression, Drain Current, Power Dissi-         |    |

|      | pated and DC Power Consumption of the cascaded two-stage amplifier, for           |    |

|      | the frequency range 2.0-2.8GHz, highlighting the center frequency of 2.4GHz.      | 90 |

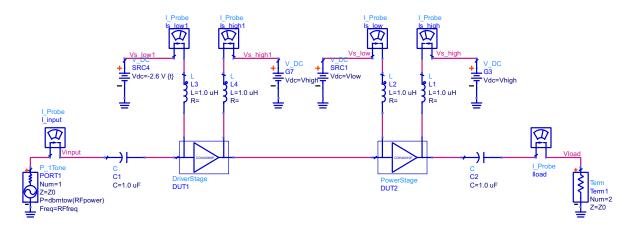

| 6.2  | The modified simulation schematic of the setup in figure A.3 for large-signal     |    |

|      | evaluation of the cascaded two-stage amplifier                                    | 91 |

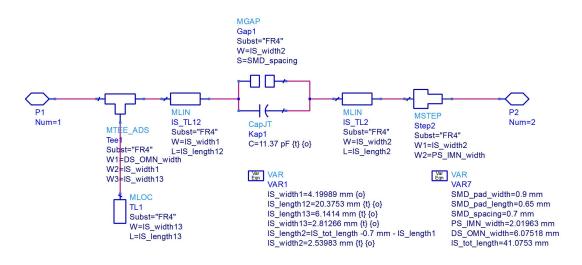

| 6.3  | The simulation schematic of the interstage network                                | 92 |

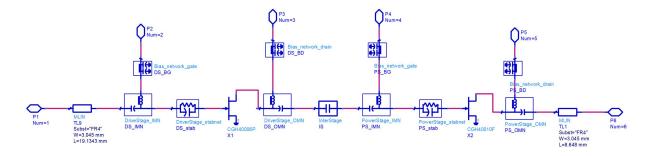

| 6.4  | A simulation schematic subcircuit overview of the two-stage amplifier             | 92 |

| 6.5  | PAE, Transducer Power Gain, Gain compression, Drain Current, Power Dis-           |

|------|-----------------------------------------------------------------------------------|

|      | sipated and DC Power Consumption of the two-stage amplifier with inter-           |

|      | stage network, for the frequency range 2.0-2.8GHz, highlighting the center        |

|      | frequency of 2.4GHz                                                               |

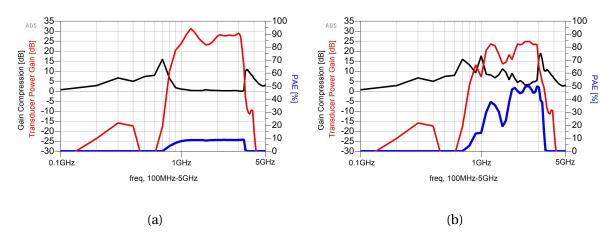

| 6.6  | The transducer power gain, gain compression and PAE for (a) 30dBm and (b)         |

|      | 41dBm desired output power, from 100MHz to 5GHz                                   |

| 6.7  | Layout of the two-stage amplifier with interstage network                         |

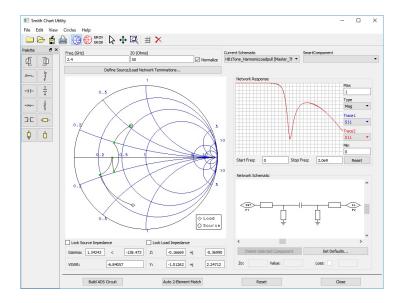

| 6.8  | A quick interstage network design for the desired impedances at 2.4GHz using      |

|      | the smith chart utility in ADS                                                    |

| 7.1  | Measurement setup for small-signals, using a series network analyzer and a        |

|      | power supply                                                                      |

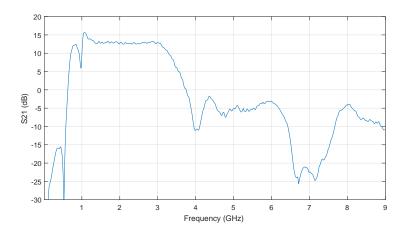

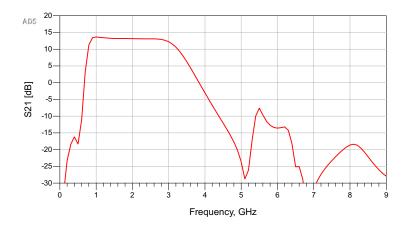

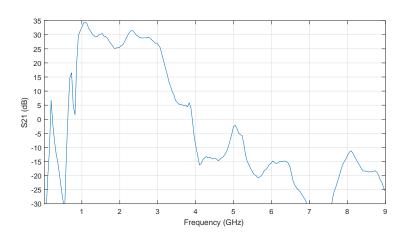

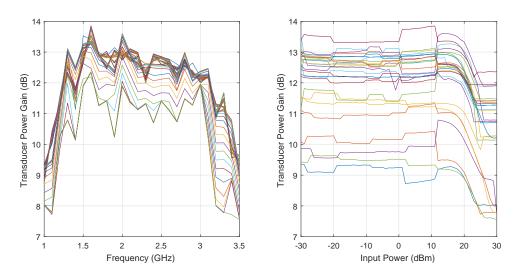

| 7.2  | Measured small-signal gain of the power stage amplifier from 10MHz to 9GHz. 100   |

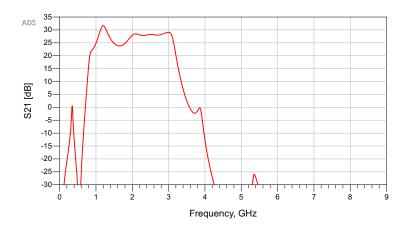

| 7.3  | Simulated small-signal gain of the power stage amplifier from 10MHz to 9GHz. 100  |

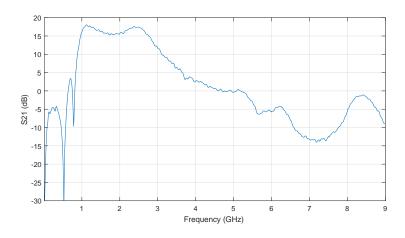

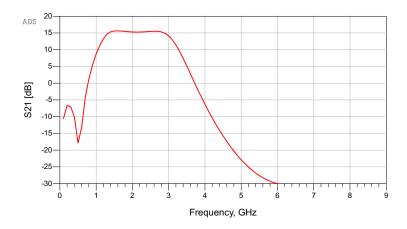

| 7.4  | Measured small-signal gain of the driver stage amplifier from 10MHz to 9GHz. 101  |

| 7.5  | Simulated small-signal gain of the driver stage amplifier from 10MHz to 9GHz. 102 |

| 7.6  | Measured small-signal gain of the two-stage amplifier from 10MHz to 9GHz 102 $$   |

| 7.7  | Simulated small-signal gain of the two-stage amplifier from 10MHz to 9GHz 103 $$  |

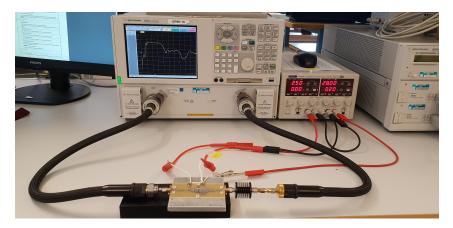

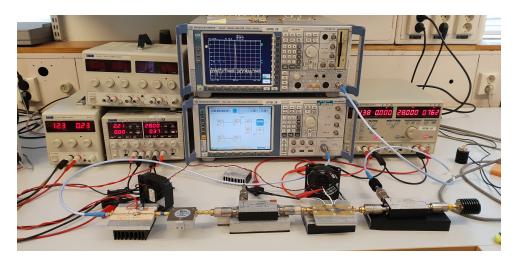

| 7.8  | Measurement setup for large-signals, using a signal generator, a signal ana-      |

|      | lyzer and some power supplies                                                     |

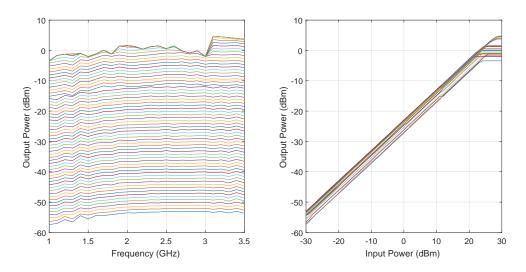

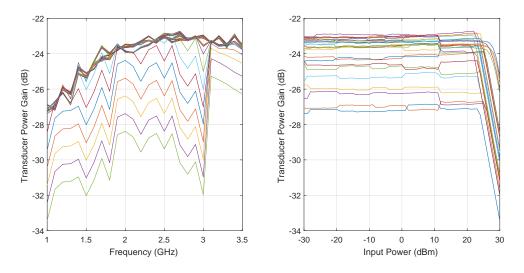

| 7.9  | Measurements of the output power versus input power and frequency for the         |

|      | output network                                                                    |

| 7.10 | Measurements of the transducer power gain versus input power and frequency        |

|      | for the output network                                                            |

| 7.11 | Measurements of the output power versus input power and frequency for the         |

|      | through network                                                                   |

| 7.12 | Measurements of the transducer power gain versus input power and frequency        |

|      | for the through network                                                           |

| 7.13 | Measurements of the output power gain versus input power and frequency for        |

|      | the input network.                                                                |

| 7.14 | Measurements of the transducer power gain versus input power and frequency        |

|      | for the input network                                                             |

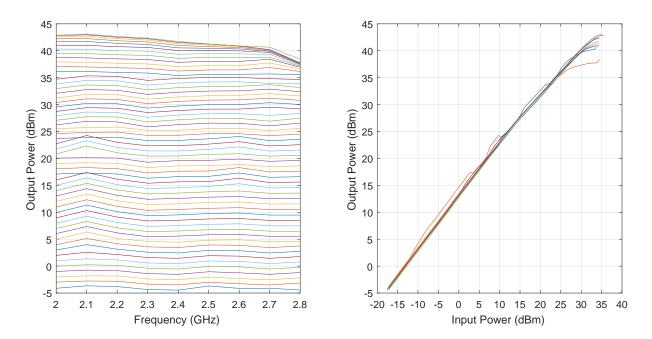

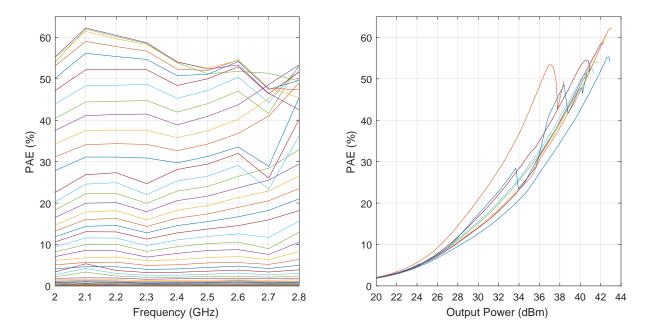

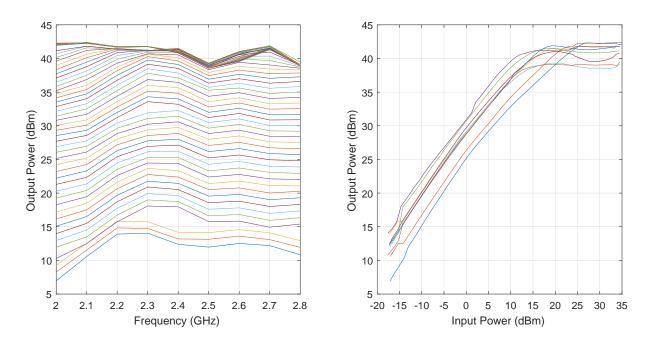

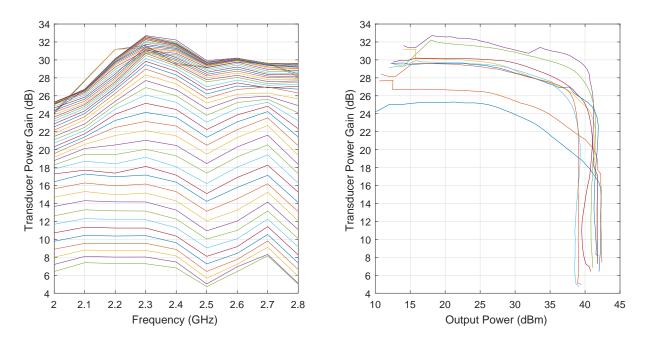

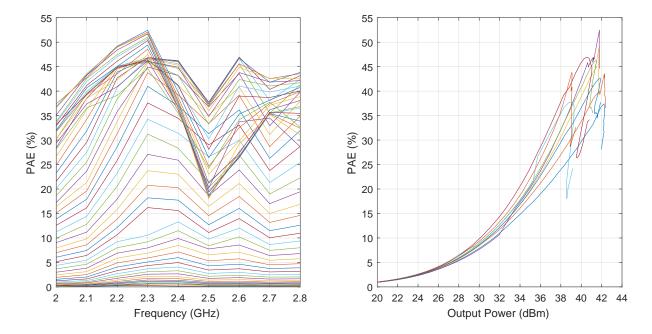

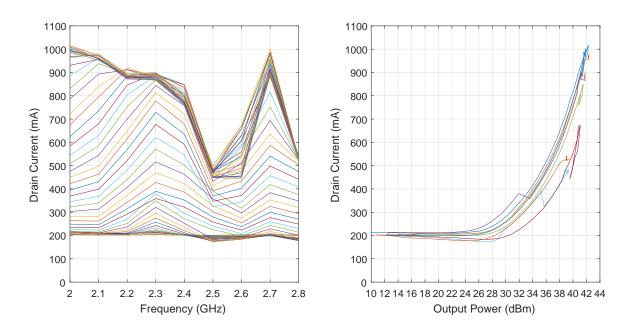

| 7.15 | Measured performance of the power stage amplifier extrapolated from the               |

|------|---------------------------------------------------------------------------------------|

|      | corresponding plots in the appendix                                                   |

| 7.16 | Measured performance of the driver stage amplifier extrapolated from the              |

|      | corresponding plots in the appendix                                                   |

| 7.17 | Measured performance of the two stage amplifier extrapolated from the cor-            |

|      | responding plots in the appendix                                                      |

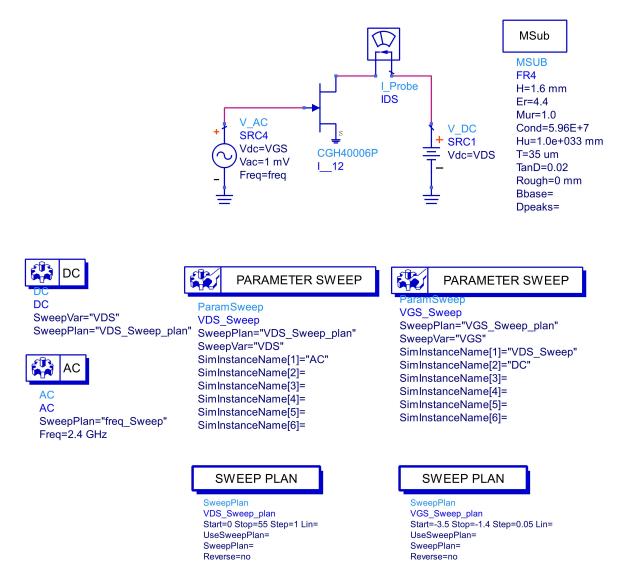

| A.1  | The schematic simulation setup for calculating the I-V characteristics of a           |

|      | transistor and determine the properties of the transistor at different quies-         |

|      | cent biases. Here, the CGH40006P transistor is evaluated for $0V \le V_{DS} \le 55$   |

|      | and $-3.5V \le V_{GS} \le -1.4$ at DC operations and for a input signal at 2.4GHz 126 |

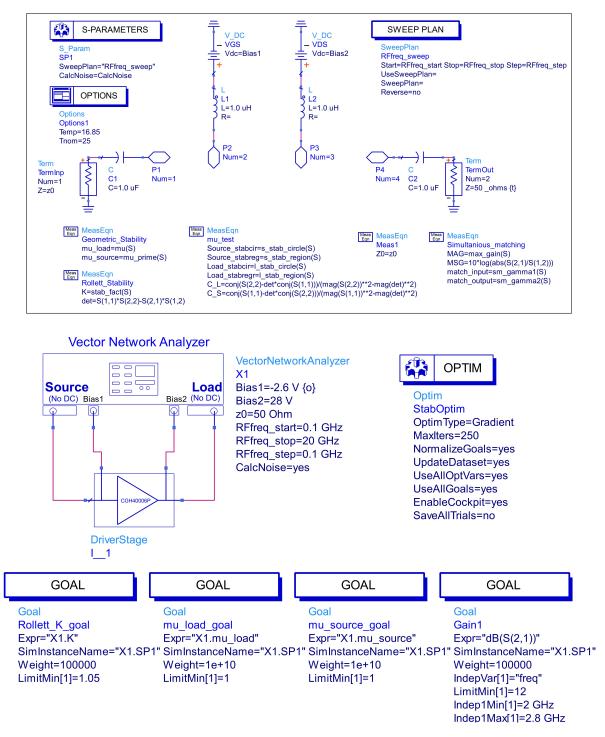

| A.2  | The schematic simulation setup for calculating the S-parameters of a network,         |

|      | also showing the internal simulation schematic of the VNA. Here, the driver           |

|      | stage is evaluated at the quiescent bias from 100MHz to 20GHz, and the sta-           |

|      | bility and small-signal gain optimization goals are shown                             |

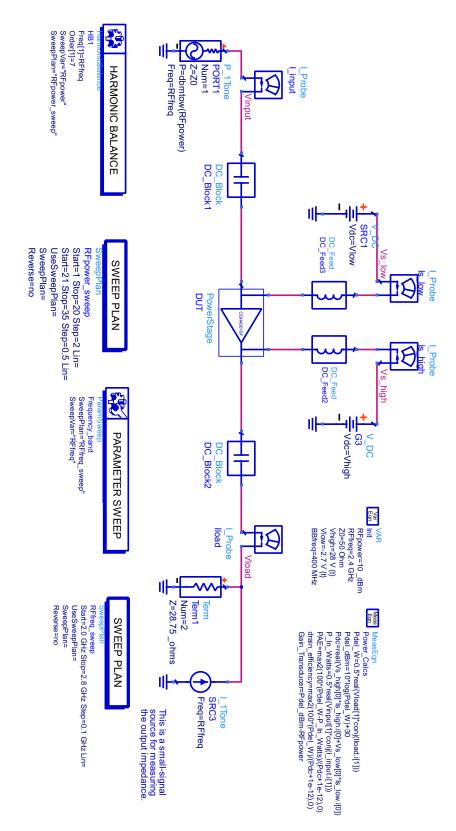

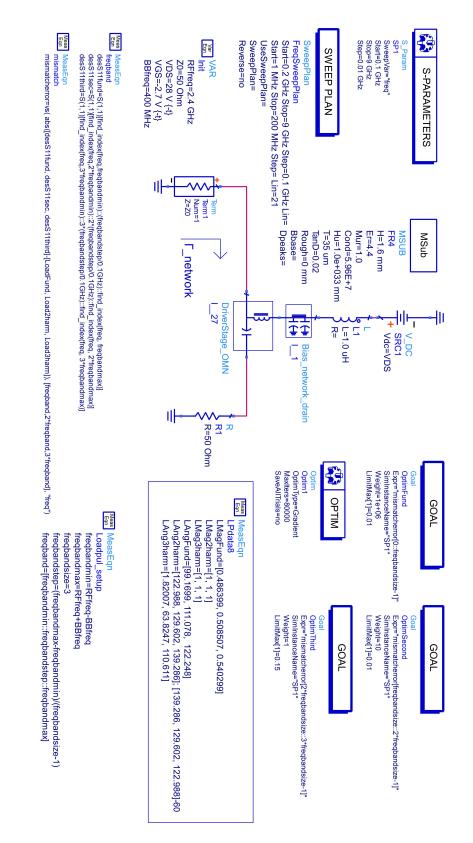

| A.3  | The schematic simulation setup for calculating the large-signal characteristics       |

|      | of a an amplifier. Here, the power stage is evaluated at the quiescent bias for       |

|      | input powers from 0dBm to 35dBm in the frequency band (2.0-2.8GHz) 128                |

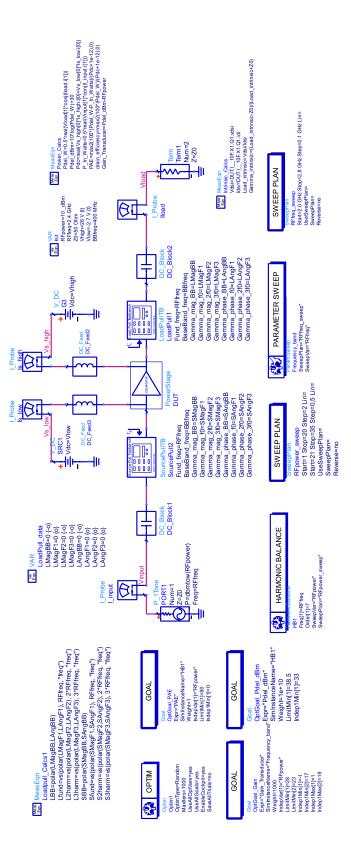

| A.4  | The schematic simulation setup for performing harmonic load- and sourcepull           |

|      | of a network. Here, the power stage is evaluated at the quiescent bias for in-        |

|      | put powers from 1dBm to 35dBm at 2.4GHz. A large-signal simulation can                |

|      | also performed with this setup                                                        |

| A.5  | The schematic simulation setup for optimization of the network input impedance.       |

|      | Here, the driver stage output matching network impedance trajectory is matched        |

|      | with the desired load impedances from the harmonic loadpull simulation 130            |

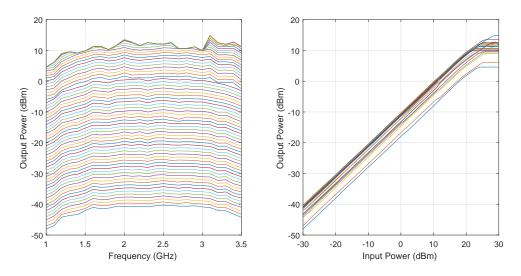

| B.1  | Measurements of the output power gain versus input power and frequency for            |

|      | the power stage                                                                       |

| B.2  | Measurements of the transducer power gain versus input power and frequency            |

|      | for the power stage                                                                   |

| B.3  | Measurements of the PAE versus input power and frequency for the power stage.133      |

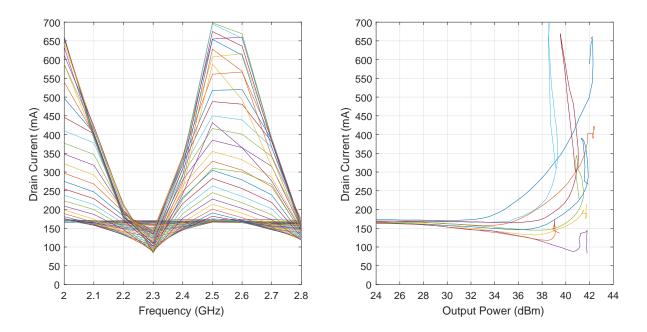

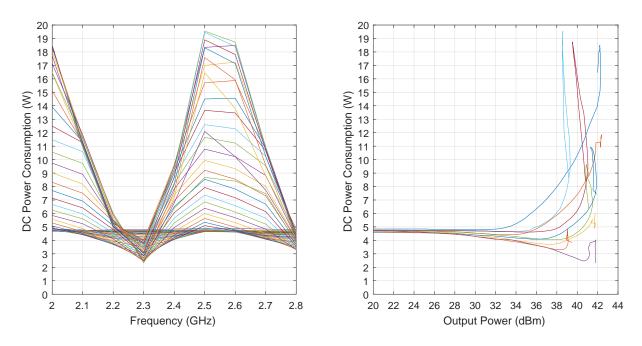

| B.4  | Measurements of the drain current versus input power and frequency for the        |

|------|-----------------------------------------------------------------------------------|

|      | power stage                                                                       |

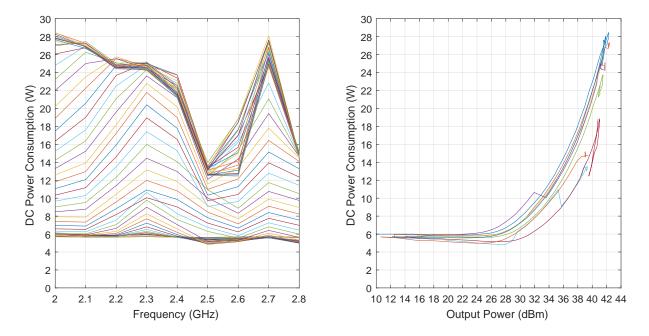

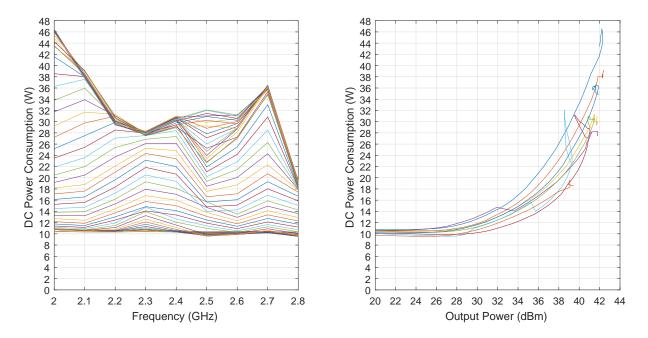

| B.5  | Measurements of the DC power consumption versus input power and fre-              |

|      | quency for the power stage                                                        |

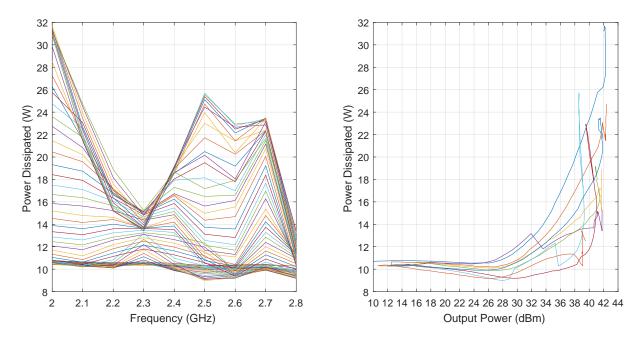

| B.6  | Measurements of the power dissipated versus input power and frequency for         |

|      | the power stage                                                                   |

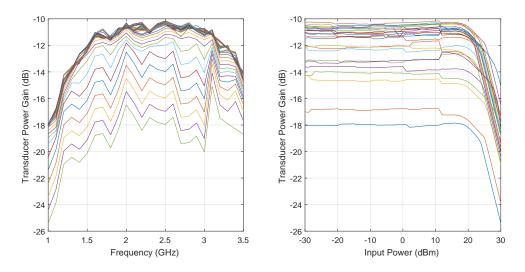

| B.7  | Measurements of the output power gain versus input power and frequency for        |

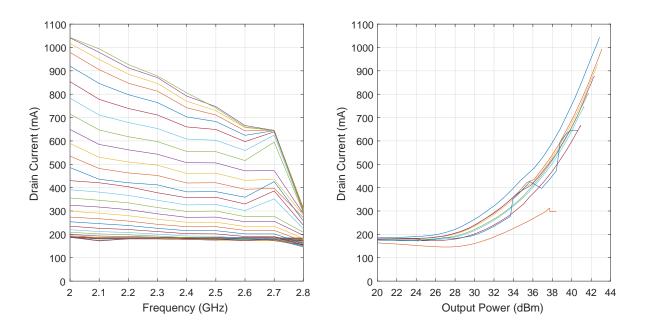

|      | the driver stage                                                                  |

| B.8  | Measurements of the transducer power gain versus input power and frequency        |

|      | for the driver stage                                                              |

| B.9  | Measurements of the PAE versus input power and frequency for the driver stage.136 |

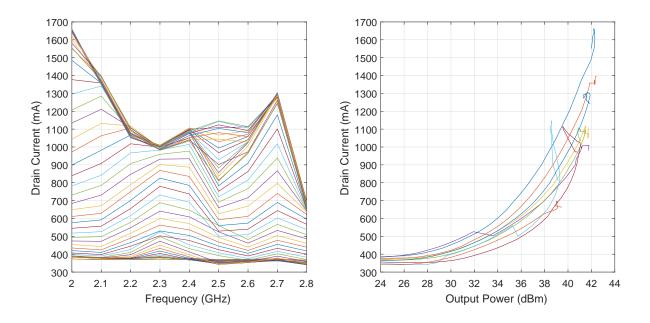

| B.10 | Measurements of the drain current versus input power and frequency for the        |

|      | driver stage                                                                      |

| B.11 | Measurements of the DC power consumption versus input power and fre-              |

|      | quency for the driver stage                                                       |

| B.12 | Measurements of the power dissipated versus input power and frequency for         |

|      | the driver stage                                                                  |

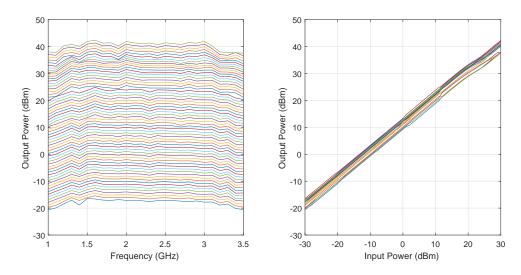

| B.13 | Measurements of the output power gain versus input power and frequency for        |

|      | the two-stage                                                                     |

| B.14 | Measurements of the transducer power gain versus input power and frequency        |

|      | for the two-stage                                                                 |

| B.15 | Measurements of the PAE versus input power and frequency for the two-stage. 139   |

| B.16 | Measurements of the power stage drain current versus input power and fre-         |

|      | quency for the two-stage                                                          |

| B.17 | Measurements of the driver stage drain current versus input power and fre-        |

|      | quency for the two-stage                                                          |

| B.18 | Measurements of the total drain current versus input power and frequency for      |

|      | the two-stage                                                                     |

| B.19 | Measurements of the power stage DC power consumption versus input power           |

|      | and frequency for the two-stage                                                   |

| B.20 | Measurements of the driver stage DC power consumption versus input power      |     |

|------|-------------------------------------------------------------------------------|-----|

|      | and frequency for the two-stage.                                              | 141 |

| B.21 | Measurements of the total DC power consumption versus input power and         |     |

|      | frequency for the two-stage.                                                  | 142 |

| B.22 | 2 Measurements of the total power dissipated versus input power and frequency |     |

|      | for the two-stage.                                                            | 142 |

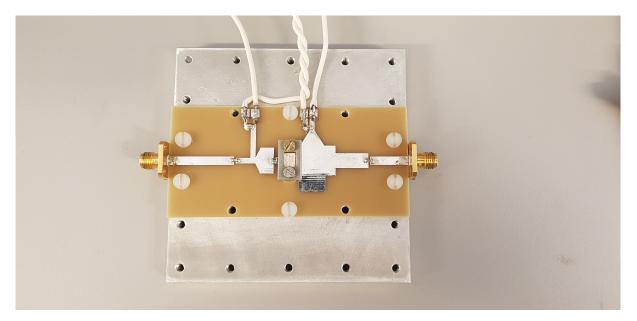

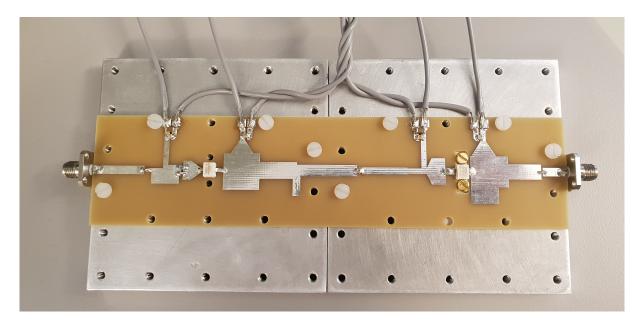

| C.1  | Photo of the power stage amplifier with the CGH40010F transistor and clamp.   | 143 |

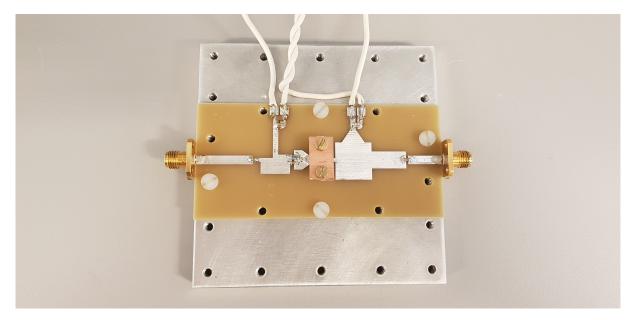

| C.2  | Photo of the driver stage amplifier with the CGH40006P transistor and clamp.  | 144 |

| C.3  | Photo of the two-stage amplifier with both the driver and amplifier stages    | 144 |

## List of Tables

| 1.1 | Initial PA design requirements                                                    | 4  |

|-----|-----------------------------------------------------------------------------------|----|

| 2.1 | A collection of key material properties for each of the semiconductors            | 10 |

| 3.1 | Excerpt from the datasheet of Wolfspeed's CGH40010F transistor, presenting        |    |

|     | its maximum ratings and electrical characteristics                                | 34 |

| 3.2 | Excerpt from the datasheet of Wolfspeed's CGH40006P transistor, presenting        |    |

|     | its maximum ratings and electrical characteristics                                | 36 |

| 3.3 | Electrical properties of the FR-4 substrate                                       | 37 |

| 3.4 | Available component values for the R14S capacitors in pico farad                  | 39 |

| 3.5 | Available component values for the L14 inductors in nano henry.                   | 39 |

| 3.6 | Available components from Murata.[17, 18, 19]                                     | 39 |

| 4.1 | I-V Properties of the CGH40010F transistor at the selected quiescent bias         | 46 |

| 4.2 | Properties of the stabilized transistor in accordance with the large-signal char- |    |

|     | acteristics in figure 4.8                                                         | 51 |

| 4.3 | The Transducer Power Gain, PAE and Power delivered to the load, when the          |    |

|     | load impedances are matched to the optimal load impedances for the center         |    |

|     | and outer frequencies.                                                            | 53 |

| 4.4 | The Transducer Power Gain, PAE and Power delivered to the load, when the          |    |

|     | load impedances are matched to the desired load impedances for the center         |    |

|     | and outer frequencies.                                                            | 54 |

| 5.1 | I-V Properties of the CGH40006P transistor at the desired quiescent bias. $\ldots$ | 68  |

|-----|------------------------------------------------------------------------------------|-----|

| 5.2 | Properties of the stabilized transistor in accordance with the large-signal char-  |     |

|     | acteristics in figure 5.9                                                          | 73  |

| 5.3 | The Transducer Power Gain, PAE and Power delivered to the load, when the           |     |

|     | load impedances are matched to the optimal load impedances for the center          |     |

|     | and outer frequencies.                                                             | 75  |

| 5.4 | The Transducer Power Gain, PAE and Power delivered to the load, when the           |     |

|     | load impedances are matched to the desired load impedances for the center          |     |

|     | and outer frequencies.                                                             | 76  |

| 6.1 | Comparison of the characteristics of the cascaded two-stage amplifier versus       |     |

|     | the driver and power stage amplifiers, in the frequency band 2.0-2.8GHz            | 91  |

| 7.1 | Properties of the power stage amplifier from the large-signal measurements         | 109 |

| 7.2 | Properties of the driver stage amplifier from the large-signal measurements.       | 110 |

| 7.3 | Properties of the driver stage amplifier from the large-signal measurements.       | 111 |

Introduction

### Chapter 1

### Introduction

In wireless receivers and transmitters the amplification of signals have a crucial role, and virtually all microwave and RF amplifiers today use three-terminal solid state devices such as gallium arsenide (GaAs) field effect transistors (FET), silicon (Si) or silicon germanium (SiGe) bipolar transistors, and lately gallium nitride (GaN) high electron mobility transistors (HEMT) [23]. GaAs has long been the automatic choice of semiconductor material for high frequency solid-state devices. However, during the last decade, GaN has become more popular in applications where high-frequency and high-power are required. It has certain traits that support smaller circuits for a given frequency and power level, allowing the higher power densities and efficiencies much sought after by designers of power-efficient wireless base stations and microcells. [6]. Both GaAs and GaN technologies have good performances in regards to both low-noise amplifiers (LNA) and power amplifiers (PA), and in companies developing radio equipment for wireless applications and in universities and science centers there are significant activities around these subjects. The PA is of great economical and technical significance because it constitute a substantial part of the costs in both development and production of radio equipment. In portable devices the PA is demanding a significant load on the batteries, and in base stations the PA consumes a considerable amount of energy and dissipates a substantial amount of power. Hence, good technical solutions are crucial for having a competitive advantage in the market.

Because transistors are nonlinear devices, the transistor amplifier exhibit nonlinear effects such as saturation and harmonic distortion. The former is due to a limited source of input power and the power handling capabilities of the transistor, while the latter is a more prevalent problem related to the fact that the harmonics of input signals are generated at the output of an amplifier. For multiple input signals a set of harmonic mixing products where some will lie within the baseband, which leads to distortion of the signals. Generally the power levels of these harmonics is very low, but as input power increases the effects can be significant. [5]

In order to overcome these problems and be able to design PAs that perform as desired, one must be able to understand the behavior of the transistor in the specific operating conditions of the application. The most widely used technique in the microwave industry to accurately characterize devices in power amplifier applications is the loadpull method, which extrapolates the loadline method described by the I-V curves of the transistor and the load impedance. An extension of this method is the harmonic loadpull (HLP), which also considers the impedances at the harmonic frequencies, and the harmonic sourcepull (HSP) which evaluates the input instead of the output of the PA. Correspondingly the design method of harmonic termination is adopted to conform to the restrictions of the harmonic impedances.

#### 1.1 Goals and requirements

The objective of this thesis is to design a two-stage broadband power amplifier for envelope tracking applications, while going in depth in the design process of a power amplifier using the harmonic loadpull and sourcepull techniques, and the harmonic termination design method. During the design process the focus is to find the optimal desired tradeoffs between gain, efficiency, output power and linearity. A comparison of the two-stage amplifier and each amplifier stage should be an integral part of the analysis. The power amplifier

| Parameter       | Requirement            |

|-----------------|------------------------|

| Frequency       | 2.4GHz                 |

| Bandwidth(-1dB) | 800MHz                 |

| Gain            | best possible tradeoff |

| Output power    | best possible tradeoff |

| Efficiency      | best possible tradeoff |

| Linearity       | best possible tradeoff |

Table 1.1: Initial PA design requirements

should be designed using the CGH40006P and CGH40010F transistors from Wolfspeed for 2.4GHz applications and have a bandwidth of 800MHz.

#### **1.2** Structure of the Thesis

The thesis is structured into 8 chapters, following each step in the design procedures chronologically, and additional appendices. **Chapter 1** serves as a short introduction to the subject of the master's thesis and presents the goals and requirements for the power amplifier design. **Chapter 2** contains the relevant theory for the design procedures and lays the theoretical foundation for the following chapter. **Chapter 3** elaborates on the preliminary design consideration. **Chapter 4** and **chapter 5** contains the design process and evaluations of the power and driver stage respectively. **Chapter 6** contains the design process and evaluation of the two-stage amplifier, and **chapter 7** presents the measurement results of the power, driver and two-stage amplifier. **Chapter 8** summarizes the entire process and discusses the results. **Appendix A** contains the schematic simulation setups used throughout the project, **appendix B** contains the large-signal measurement results, and **appendix C** contains photos of each of the amplifiers. **Background and Theory**

## **Chapter 2**

## **Background and Theory**

In this chapter we will elaborate on the transistor technology and the theoretical foundations for the design procedures of the amplifier stages in the following chapters. The theory includes definitions of the transistor properties, classes of operation, the loadline method and the loadpull methods. Harmonic termination are also discussed briefly in relation to class F amplifiers.

## 2.1 Transistor technology

There are several different materials and technologies used for high-frequency applications available on the market, such as the III-V materials like gallium-arsenide (GaAs), indium-phosphide (InP), gallium-phosphide (GaP) and gallium-nitride (GaN) along IV materials like silicon (Si) and silicon-carbide (SiC). Each material properties are suitable to different applications. For some time the choice of transistors in microwave applications was essentially between silicon and GaAs. However recently GaN have had an increasing dominance as a high-frequency solid-state power amplifier and the combination of GaN and SiC offers additional performance [26]. The material properties of the silicon, GaAs, SiC and GaN is shown in table 2.1. The main advantages of the GaN in high-frequency and high-voltage operations is the wide bandgap and the high saturated electron velocity [12]. GaN also has a higher thermal conductivity than both Si and GaAs and combining it with a SiC substrate, GaN on SiC can provide excellent thermal properties due to the high thermal conductivity of SiC, which is crusial in high-power applications.

| Semiconductor                |                    | Si   | SiC  | GaAs | GaN       |

|------------------------------|--------------------|------|------|------|-----------|

| Characteristics              | Units              |      |      |      |           |

| Bandgap                      | eV                 | 1.1  | 3.25 | 1.42 | 3.49      |

| Electron Mobility at 300°K   | $cm^2/Vs$          | 1500 | 700  | 8500 | 1000-2000 |

| Saturated Electron Velocity  | $\times 10^7 cm/s$ | 1    | 2    | 1.3  | 2.5       |

| Breakdown Field              | MV/cm              | 0.3  | 3    | 0.4  | 3.3       |

| Thermal Conductivity         | <i>W/cm</i> °K     | 1.5  | 4.5  | 0.5  | >1.5      |

| Relative dielectric constant | $\epsilon_r$       | 11.8 | 10   | 12.8 | 9         |

Table 2.1: A collection of key material properties for each of the semiconductors.

## 2.2 GaN Technology

The GaN technology appeared early in the 1990's and was deemed an excellent semiconductor material for high-power high-frequency transistors based on the material parameters of bandgap, electron mobility and saturated electron velocity, as shown in figure 2.1. The lack of a bulk GaN source material led to the need for GaN growth on mismatched substrates such as Si, SiC and sapphire, and further advancements in the growth of device-grade aluminum gallium nitride (AlGaN) led to record power density RF amplifiers. Both defense and commercial applications of RF power transistors demand more power and wider bandwidths at higher frequencies, where GaN technology has been proven to be an excellent choice. [26]

The wide bandgap of GaN (3.49eV) compared to GaAs (1.42eV) and Si (1.1eV) ensures a larger breakdown voltage of the GaN devices such that they can operate at higher voltages, and the high saturated electron velocity of  $2.5 \times 10^7 cm/s$  compared to GaAs  $(1.3 \times 10^7 cm/s)$  and Si  $(1.0 \times 10^7 cm/s)$  assures a higher current density. The high voltage and current density results in high power density and makes the GaN devices useful in high power applications. Because of the higher power density, the GaN devices can deliver more power using the same surface area, and for a given power application this property assures lower parasitic capacitance making it more suitable to wide bandwidth application. Smaller devices also have lower combining loss such that higher efficiency, gain and power are achievable. The GaN on SiC ensures excellent thermal properties due to the high thermal conductivity, which means that GaN on SiC will be significantly cooler than e.g. GaN on Si or GaAs on Si while dissipating the same amount of power. [12]

## 2.3 Transistor types

Transistors are usually divided into two classes; bipolar and unipolar transistors. The bipolar transistors induces currents of both major and minor carriers while the unipolar transistors induces currents of only the major carriers. In Bipolar Junction Transistors (BJTs) the output current is controlled by an input current, while in the unipolar Field Effect transistors (FETs) the output current is controlled by an input voltage. [12]

#### 2.3.1 Metal-Semiconductor Field Effect Transistors

The Metal-Semiconductor Field Effect Transistors (MESFETs) is a type of unipolar transistor consisting of four terminals - drain, source, bulk and gate. Because of the higher mobility of electrons compared to holes, the MESFETs are usually n-type devices, where the bulk and source are connected to ground. The transistor will therefore have two bias voltages - the gate-to-source and drain-to-source voltages. By applying a reverse gate voltage a depletion region is formed in the conducting channel between drain and source, modulating the thickness of the conducting channel and thereby also the current. Applying an increasing drain-to-source voltage with constant gate voltage increases the electric field, and thereby also the width of the depletion region, on the drain side, making the conducting channel narrower. Although the conducting channel is narrower the larger electric field causes a higher electron velocity and thereby increases the current until the depletion region spreads across the whole channel, in which the electron velocity and thereby also the drain current saturates. In the saturated region the current can still be modulated by the gate-to-source voltage and will therefore act as a voltage controlled current source. [12]

#### 2.3.2 High Electron Mobility Transistors

The HEMT or Heterostructure FET is a unipolar field-effect transistor, much like the MES-FET, but instead of using a doped region as the conducting channel, the channel is incorporated as a junction between two materials with different bandgaps.[7] The bandgap difference creates an electron-well such that electrons will diffuse to the adjacent narrow-band material until the potentials reach an equilibrium, which results in a thin layer with high electron density. This accumulated layer, usually known as the 2-dimensional electron gas

Figure 2.1: The (a) Band diagram [7] and (b) layer structure of an AlGaN/GaN on SiC HEMT.

(2DEG) layer, has a higher electron mobility because of the free electrons and can therefore support higher currents. The bandgap architecture of an AlGaN/GaN structure is shown in figure 2.1a. As seen from the figure the 2DEG layer is caused by the discontinuity between AlGaN and GaN conduction bands that dips under the Fermi level of the bands.

## 2.4 High-frequency Power Amplifier properties

The main goal of an amplifier is to replicate the input signal at the output with a greater magnitude, without distortion and as efficiently as possible. To manage this the amplifier needs an additional source of power that can be converted into the desired amplified signal. The high-frequency power amplifier makes use of a DC power source to generate the amplification of an RF signal, and optimizes the power conversion mainly based on the power delivered to the load of the amplifier. Practical amplifiers are not ideal and will produce non-linearities during the conversion which affect the performance of the amplifier. It is therefore necessary to evaluate the characteristics of the amplifier to be able to make the necessary tradeoffs for the specific application of the amplifier. Such parameters are e.g. stability, gain, linearity and efficiency as described in the following sections.

Figure 2.2: The general transistor amplifier circuit [23, p.198]

### 2.4.1 Stability

The stability of an amplifier refers to the amplifier's immunity to oscillations. Such oscillations are possible if either the input or output port impedance has a negative real part, which would imply that  $|\Gamma_{in}| > 1$  or  $|\Gamma_{out}| > 1$ . Because  $\Gamma_{in}$  and  $\Gamma_{out}$  depend on the input and output matching networks, they are also dependent on  $\Gamma_S$  and  $\Gamma_L$ , see figure 2.2. [23] For different values of  $\Gamma_s$  and  $\Gamma_L$  the stability will thereby be either stable or unstable, which leads to two types of amplifier stability:

■ **Unconditional stability**: The network is unconditionally stable if  $\Gamma_{in} < 1$  and  $\Gamma_{out} < 1$  for all passive source and load impedances (i.e.  $|\Gamma_S| < 1$  or  $|\Gamma_L| < 1$ ).

**Conditional stability**: The network is conditionally stable if  $\Gamma_{in} < 1$  and  $\Gamma_{out} < 1$  for a certain range of passive source and load impedances.

Both  $|\Gamma_S|$  and  $|\Gamma_L|$  are frequency dependant, which means that the impedance of the system also will change as the frequency changes.

#### **Stability Circles**

By inspection of the limit for unconditional stability described above we get the following conditions for  $\Gamma_S$  and  $\Gamma_L$ :

$$|\Gamma_{in,out}| = \left| S_{11,22} + \frac{S_{21}S_{12}\Gamma_{L,S}}{1 - S_{22,11}\Gamma_{L,S}} \right| = 1$$

(2.1)

which can also be written in the form  $|\Gamma - C| = R$ , representing a circle in the complex  $\Gamma$  plane with center C and radius R:

Figure 2.3: The regions of stability for a conditionally stable device where (a)  $|S_{11}| < 1$  and (b)  $|S_{11}| > 1$ . [23]

$$\left|\Gamma_{L,S} - \frac{(S_{22,11} - \Delta S_{11,22}^*)^*}{|S_{22,11}|^2 - |\Delta|^2}\right| = \left|\frac{S_{12}S_{21}}{|S_{22,11}|^2 - |\Delta|^2}\right|$$

(2.2)

where

$$C_{L,S} = \frac{(S_{22,11} - \Delta S_{11,22}^*)^*}{|S_{22,11}|^2 - |\Delta|^2} \qquad (\text{center})$$

(2.3a)

$$R_{L,S} = \left| \frac{S_{12}S_{21}}{|S_{22,11}|^2 - |\Delta|^2} \right|$$

(radius) (2.3b)

and  $\Delta$  is the determinant of the scattering matrix

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.4}$$

Considering the S-parameters of a transistor, we can plot the input and output stability circles for  $|\Gamma_{in}| = 1$  and  $|\Gamma_{out}| = 1$  where the inside and outside of the circle represent either a stable or unstable region. To determine which region is stable a test load (e.g  $Z_L = Z_0$ ) has to be applied to the transistor. If the transistor is stable, all other points in that region is stable and vice versa. If the stability circle intersects the smith chart, both regions are contained

within the smith chart and the transistor is conditionally stable <sup>1</sup>, as shown in figure 2.3. If the stability circle is completely outside the smith chart or encircles the whole smith chart the transistor is unconditionally stable.

#### Rollett's condition, K- $\Delta$ test

A simple test to figure out if an amplifier is unconditionally stable is the Rollett's conditions or K- $\Delta$  test, defined as

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2|}{2|S_{12}S_{21}|} > 1$$

(2.5)

and

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1 \tag{2.6}$$

The two conditions are sufficient to determine if an amplifier is unconditionally stable, but it says nothing about the relative stability of the device.

#### $\mu$ -parameter

Another test to check the stability of the amplifier is the  $\mu$ -parameter, defined as

$$\mu_{load,source} = \frac{1 - |S_{11,22}|^2}{|S_{22,11} - \Delta S^*_{11,22}| + |S_{12}S_{21}|} > 1$$

(2.7)

This parameter, as opposed to Rollett's conditions, includes a relative stability measure. If  $\mu > 1$  the amplifier is unconditionally stable, and greater values of  $\mu$  imply greater stability.

### 2.4.2 Power Gain

The power gain of a two-port network, in this case an amplifier, is defined as the ratio of the output power to the input power, but this can be defined in several ways. The three most common definitions are the transducer power gain ( $G_T$ ), the available power gain ( $G_A$ ) and the operating power gain ( $G_P$ ). The definitions are as follows: [5]

<sup>&</sup>lt;sup>1</sup>A conditionally stable transistor may also be referred to as potentially unstable

$$G_T = \frac{\text{power delivered to the load}}{\text{power available from the source}} = \frac{P_L}{P_{avs}}$$

(2.8a)

$$G_A = \frac{\text{power available from the network}}{\text{power available from the source}} = \frac{P_{avn}}{P_{avs}}$$

(2.8b)

$$G_P = \frac{\text{power delivered to the load}}{\text{power delivered to the network}} = \frac{P_L}{P_{in}}$$

(2.8c)

From the equations we see that the transducer power gain ( $G_T$ ) is dependent on both the source and load impedances, while the available power gain ( $G_A$ ) and the operating power gain ( $G_P$ ) are dependent only on the source and load impedances respectively. The difference between these gain definitions is how they define the impedance match between the device and the source and load networks. If both networks are conjugately matched the definitions give the same result. The transducer power gain is the most useful of these definitions as it accounts for impedance mismatch in both networks and it's the most commonly used definition for amplifier. The transducer power gain can be written as

$$G_T = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|1 - \Gamma_s \Gamma_{in}|^2 |1 - S_{22} \Gamma_L|^2} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|(1 - S_{11} \Gamma_S) (1 - S_{22} \Gamma_L) - S_{12} S_{21} \Gamma_S \Gamma_L|^2}$$

(2.9)

where the substitution  $\Gamma_{in} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1-S_{22}\Gamma_L}$  has been made. For a unilateral two-port network,

Figure 2.4: A two-port network with general source and load impedances, indicating power available and delivered in the components.

the reverse power gain is set to zero ( $|S_{12}| = 0$ ) and the transducer power gain becomes

$$G_{TU} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2) (1 - |\Gamma_L|^2)}{|(1 - S_{11}\Gamma_S) (1 - S_{22}\Gamma_L)|^2} = G_S G_0 G_L$$

(2.10)

where

$$G_{S,L} = \frac{(1 - |\Gamma_{S,L}|^2)}{|(1 - S_{11,22}\Gamma_{S,L})|^2} \quad \text{and} \quad G_0 = |S_{21}|^2$$

(2.11)

For the available power gain  $(G_A)$  and the operating power gain  $(G_P)$  they can be expressed as

$$G_A = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2)}{|1 - S_{11}\Gamma_S|^2 (1 - |\Gamma_{out}|^2)} = G_S G_0 \frac{1}{1 - |\Gamma_{out}|^2}$$

(2.12a)

$$G_P = \frac{|S_{21}|^2 (1 - |\Gamma_L|^2)}{(1 - |\Gamma_{in}|^2)|1 - S_{22}\Gamma_L|^2} = \frac{1}{1 - |\Gamma_{in}|^2} G_0 G_L$$

(2.12b)

#### Maximum Available and Stable Gain

The maximum power transfer between the input matching network and the transistor, and the transistor and the output matching network occurs when the networks are conjugately matched, that is

$$\Gamma_{in} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L} = \Gamma_S^*$$

(2.13a)

$$\Gamma_{out} = S_{22} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{11}\Gamma_S} = \Gamma_L^*.$$

(2.13b)

Solving these equations for  $\Gamma_S$  and  $\Gamma_L$  separately gives a quadratic equation with real solutions only for a positive square root, equivalent to the condition of K > 1. Thus, unconditionally stable devices can always be conjugately matched, while conditionally stable devices also must satisfy  $\Delta < 1$ . For an unconditionally stable transistor the quadratic terms of equations (2.13a) and (2.13b) can be inserted into equation (2.9) for a *K*-dependent expression of the maximum transducer power gain[23]:

$$MAG = G_{T_{max}} = \frac{|S_{21}|}{|S_{12}|} (K - \sqrt{K^2 - 1})$$

(2.14)

The maximum transducer power gain  $(G_{T_{max}})$  are equal to the maximum available power gain  $(G_{A_{max}})$  and the maximum operating power gain  $(G_{P_{max}})$ , as they describe the same case

of both conjugately matched input and output networks. The maximum gain, also referred to as matched gain or maximum available gain, is commonly denoted MAG. Since MAG does not make sense for K < 1, the limiting case where K = 1 is a useful figure of merit and is called the maximum stable gain (MSG):

$$MSG = (G_{T_{max}})\Big|_{K=1} = \frac{|S_{21}|}{|S_{12}|}$$

(2.15)

#### **Constant Gain Circles**

In many cases it is preferable to design for less than maximum gain in order to improve the bandwidth of the amplifier, obtain a specific amplifier gain or reduce device variations. This can be achieved by introducing an impedance mismatch. Assuming  $|S_{12}|$  is of negligible size, as in the unilateral case, the expressions for  $G_S$  and  $G_L$  from equation (2.11) can be used. The gain is maximized for conjugate matching;  $\Gamma_S = S_{11}^*$  and  $\Gamma_L = S_{22}^*$  resulting in

$$G_{S_{max}} = \frac{1}{1 - |S_{11}|^2} \tag{2.16a}$$

$$G_{L_{max}} = \frac{1}{1 - |S_{22}|^2} \tag{2.16b}$$

The normalized gain factor  $g_S = G_S/G_{S_{max}}$  and  $g_L = G_L/G_{L_{max}}$  would then represent constant

Figure 2.5: Constant source and load gain circles [23]

gain circles in the  $\Gamma_S$  or  $\Gamma_L$  plane, as shown in figure 2.5, with its center and radius given by

$$C_{S,L} = \frac{g_{S,L} S_{11,22}^*}{1 - (1 - g_{S,L}) |S_{11,22}|^2}$$

(center) (2.17a)

$$R_{S,L} = \frac{\sqrt{1 - g_{S,L}} (1 - |S_{11,22}|^2)}{1 - (1 - g_{S,L})|S_{11,22}|^2}$$

(radius) (2.17b)

## 2.4.3 Linearity

An amplifier is called linear if the output power of the amplifier increases linearly with the input power, and the linearity is defined by the level of distortion in the device. Some figure of merits that quantify the distortion are the 1dB compression point ( $P_{1dB}$ ), the intermodulation distorion (IMD) and the third-order intercept point (TOI or IP3).

#### **Gain Compression**

By the principle of conservation of energy, since the DC power supplied to an amplifier is limited the output power of the amplifier will also be limited. Thus, for higher input power levels the gain of the amplifier have to drop. This effect is called gain compression and leads to a non-linear amplification of the signal. This non-linearity can be modelled using a Taylor series and plotting output power versus input power. For a one-tone input signal

$$\nu_i = V_0 \cos \omega_0 t \tag{2.18}$$

the output power would be

$$v_{o} = a_{0} + a_{1}V_{0}\cos(\omega_{0}t) + a_{2}V_{0}^{2}\cos^{2}(\omega_{0}t) + a_{3}V_{0}^{3}\cos^{3}(\omega_{0}t) + \dots$$

$$= (a_{0} + \frac{1}{2}a_{2}V_{0}^{2}) + (a_{1}V_{0} + \frac{3}{4}a_{3}V_{0}^{3})\cos(\omega_{0}t)$$

$$+ \frac{1}{2}a_{2}V_{0}^{2}\cos(2\omega_{0}t) + \frac{1}{4}a_{3}V_{0}^{3}\cos(3\omega_{0}t) + \dots$$

(2.19)

and the voltage gain of the sinusoidal signal, limited to the third order terms, becomes

Figure 2.6: The 1 dB compression point for a nonlinear amplifier [11]

$$G_{\nu} = \frac{\nu_o}{\nu_i} = \frac{a_1 V_0 + \frac{3}{4} a_3 V_0}{V_0} = a_1 + \frac{3}{4} a_3 V_0^2.$$

(2.20)

The additional term containing  $a_3$  is usually negative and causes gain compression for increasing values of  $V_0$  [23]. To quantify the linear operating range of the amplifier one can define a point where the power level has decreased noticeably from the ideal case, such as the 1 dB compression point, as shown in figure 2.6.

#### **Intermodulation Distortion**

From the expansion of (2.19) we see that the single tone input creates harmonic frequencies of  $n\omega_0$ , where n = 0, 1, 2, ..., which usually would be outside the frequency band of the amplifier. For a two-tone signal such as

$$v_i = V_0(\cos(\omega_1 t) + \cos(\omega_2 t)) \tag{2.21}$$

a harmonic combination of the input frequencies  $m\omega_1 + n\omega_2$  is created, where  $m, n = 0, \pm 1, \pm 2, \pm 3, \dots$  The sums and differences between the harmonics of the two input frequencies are called intermodulation products. If the intermodulation products appear close to the desired output frequencies they will distort the output signal, hence the term intermodulation distortion (IMD). [23]

Figure 2.7: Output spectrum with intermodulation products [13]

#### **Third-order Intercept Point**

The third order products increase as  $V_0^3$ , and therefore also as the cube of the input power. Hence, on a  $P_o - P_i$  log-log scale the third-order products increase by a slope of three compared to the slope of one for the first-order products. Both first- and third-order responses exhibit compression, but a hypothetical point, using the intersections between the ideal responses, can be used to quantify the effects. This point is called the third-order intercept point, usually denoted TOI or IP3, and shown in figure 2.8.

Figure 2.8: Third-Order intercept point [11]

#### 2.4.4 Efficiency

The efficiency of a power amplifier is a measure of how well the amplifier can convert a given input power to a desired output power without waste, generally in the form of dissipated heat.

#### **Drain Efficiency**

The drain efficiency ( $\eta$ ) is the ratio of the output power of the power amplifier to the input power of the DC supply, and is a measure of how much DC power that is converted to usable output power. From the flow diagram in figure 2.9 the drain efficiency is

$$\eta = \frac{P_{out}}{P_{DC}} \tag{2.22}$$

where  $P_{DC} = V_{DC}I_{DC}$  and  $P_{out}$  is the power of the fundamental harmonic. A drawback of this measure is that it does not account for the input power of the incident RF signal into the device. The drain efficiency refers to FET devices, but can be interchanged by the equivalent collector efficiency for reference to bipolar devices.

#### **Power Added Efficiency**

The PAE is similar to the drain efficiency but takes into account the incident RF power. The input power can be significant in RF power amplifiers and the PAE is therefore a more accepted figure-of-merit than the drain efficiency. The PAE is the ratio of the difference in output and input RF power to the input power of the DC supply

Figure 2.9: Power flow diagram of a Power Amplifier

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \frac{P_{out} - \frac{P_{out}}{G}}{P_{DC}} = (1 - \frac{1}{G}) \cdot \eta$$

(2.23)

where  $G = P_{out}/P_{in}$  is the power gain of the power amplifier. The PAE is always less than the drain efficiency and for amplifiers that have less than 10dB transducer power gain, the input power significantly reduces the PAE compared to drain efficiency.

#### **Overall Efficiency**

The overall efficiency uses the input RF power in a different way than PAE, as in the ratio of output power to input powers.

$$\eta_{overall} = \frac{P_{out}}{P_{DC} + P_{in}} = \frac{P_{out}}{P_{DC} + \frac{P_{out}}{G}} = (\frac{1}{1 + \frac{\eta}{G}}) \cdot \eta$$

(2.24)

The overall efficiency makes more sense in a thermodynamic point of view and is always less than the drain efficiency. Note also that the overall efficiency can not be less than zero, as in the case for the PAE.

## 2.5 Amplifier Design Techniques

#### 2.5.1 Power Amplifier Classes

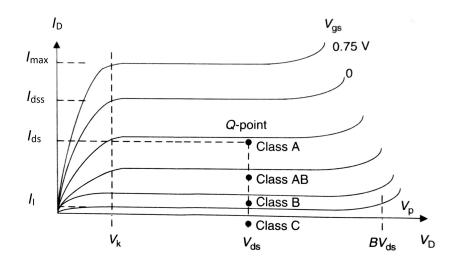

In amplifier design it is important to select a known bias or operating point for the transistor, known as the DC quiescent point or simply Q-point. This point determines the characteristics of the amplifier regarding noise figure, gain, bandwidth, output power, efficiency and linearity performance. The basic RF power amplifiers can from these characteristics be separated into certain classes. Class A is the linear amplifier while class AB, B and C are classes with reduced reduction angle. The Q-points for each class are superimposed on the I-V curves in figure 2.10. Class F amplifiers are based on switching transistors and often biased like class AB or B, and bring the concept of harmonic tuning by terminating harmonics in different loads.

Figure 2.10: DC quiescent bias point for the linear amplifier classes. [5]

#### **Class** A

The characteristics of a class A power amplifier is that it conducts over a full cycle (360°) of the input sinusoidal signal by selecting the quiescent point approximately at the center of the device currents  $(\frac{I_{max}}{2})$  and voltages  $(\frac{BV_{ds}-V_k}{2})$  as shown in figure 2.10. It presents a linear transfer characteristic and high power gain, but is limited to a maximum theoretical drain efficiency of 50%. [5]

#### **Class B**

The class B power amplifier quiescent point is positioned at the edge the device cutoff region and thereby conducts for only half a cycle (180°). Hence, the linearity performance is worse than class A, but it has greater efficiency performance with a theoretical maximum drain efficiency of 78.5%. [5]

#### **Class AB**

The class AB power amplifier quiescent point positioned between class A and class B and are in a sense a combination of both, conducting between a half and a full cycle. It achieves a better linearity than the class B power amplifier and a higher efficiency than the class A power amplifier. [5]

Figure 2.11: Harmonically tuned class F power amplifier

#### **Class** C

The class C power amplifier quiescent point is positioned within the device cutoff region and thereby conducts for less than half a cycle. These amplifiers are highly nonlinear, but have an efficiency performance greater than the other classes. Because of the nonlinear behavior of this amplifier it is mostly used in applications where linearity is not required. [5]

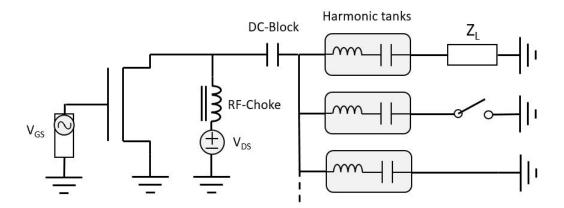

#### Harmonic termination, class F

Harmonic termination is an impedance matching technique where resonant tanks are used to terminate the harmonic frequencies in the desired loads. This technique is e.g. used in harmonically tuned class F power amplifiers to terminate the even harmonics in short circuits and the odd harmonics in open circuits to shape the voltage output to a square wave. A general model is shown in figure 2.11.

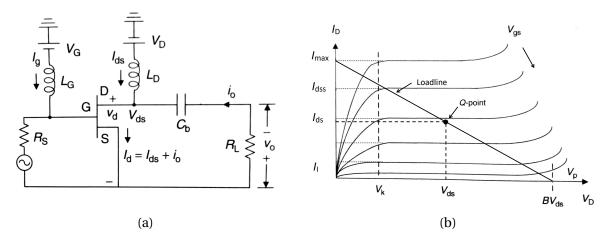

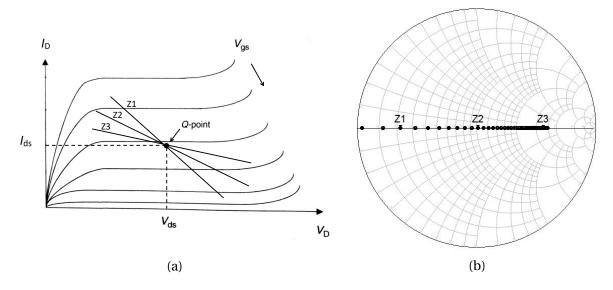

### 2.5.2 Loadline Method

Traditionally, a power amplifier can be designed using the loadline method, where the loadline determines the ac operating conditions for a given input signal and sets the maximum ratio of the peak-to-peak voltage and current for linear operations. The knee voltage, breakdown voltage, pinch-off voltage and maximum power that can be dissipated in the device put additional restrictions on the possible quiescent biases of the device. Considering the general transistor amplifier schematic in figure 2.12a and assuming that the transistor can be modelled as a voltage-controlled current-source with I-V characteristic as shown in fig-

Figure 2.12: (a) Schematic of general transistor amplifier [5] and (b) its class A loadline superimposed on the I-V characteristics.