# Sub Sea Power Electronics

Andreas Hoon Wenaas Kristoffersen

Master of Science in Energy and Environment Submission date: June 2007 Supervisor: Tore Marvin Undeland, ELKRAFT

Norwegian University of Science and Technology Department of Electrical Power Engineering

#### **Problem Description**

Fully submerged sub sea compression units in the several megawatt range are important to maintain reservoir pressure as the gas is extracted from a gas field. Electric motor drives are suitable for this kind of application, and existing solutions are available where the power electronics are encapsulated in thick walled tanks holding 1 atmosphere. As new gas fields are discovered at continually deeper waters, this tank is becoming costly and the interest for a new solution is increasing. A suggested solution is to encapsulate the power electronics in a tank with thin flexible walls and completely fill it with insulating oil allowing the pressure on the inside to be the same as on the outside. For this solution to work, the power electronic components must be compatible with oil and function under high hydrostatic pressure.

Some suitable electrical drive systems should be investigated for a high voltage sub sea compression application. The most likely to be used power semiconductor, the IGBT, is to be investigated in detail with suggested state of the art modules available from manufacturers. Description on how these modules are made and how the characteristics are improved is included in the theory along with packaging and discussion around if it is possible to apply hydrostatic pressure on the housings.

A description of the most important components in an experiment set up must be done. This for investigating compatibility of an IGBT module with silicon oil follows with test results by comparing characteristic waveforms obtained when operated in room environment and fully submerged.

The candidate should:

- Investigate suitable electric drives systems for the compression application.

- Include theory around the IGBT and available modules on the marked.

- Discuss whether or not some of these modules are suitable for high hydrostatic pressure applications.

- Construct a lab setup for testing compatibility of an IGBT module with silicon oil and document the results.

Assignment given: 22. January 2007 Supervisor: Tore Marvin Undeland, ELKRAFT

# Preface

This master thesis is a continuance of the project report "Sub Sea Power Electronics", and consists of a literature study and documentation from an experiment performed at the power electronics test laboratory at NTNU.

The thesis was initiated and financed by Norsk Hydro represented by Dr.ing. Snorre Frydenlund, and executed by graduate student Andreas H. W. Kristoffersen.

The report suggests solutions for power electronic drives at deep waters for a compression application, and theory around some of the semiconductor switches that may be used. The practical experiment investigates how a transistor behaves when fully submerged in oil and operated in a converter bridge configuration.

I would like to take this opportunity to thank people that have influenced my work.

Professor Dr.ing. Tore M. Undeland has been my advisor and supported me during my work.

Dr.ing. Snorre Frydenlund works for Norsk Hydro and has been my contact person with the initiators of the project. He has provided me with useful information and has also made sure that the finances were taken care of.

Magnar Hernes works for SINTEF Energy Research and is the project leader for the experimental set up.

Kjell Ljøkelsøy works for SINTEF Energy Research and was my laboratory partner through the whole project. With his knowledge and experience in practical work, a lot of time was saved during fail seeking and set up of the system.

All these people did not hesitate to help me whenever I stopped by or contacted them, and have been very supportive and helpful with my work.

Trondheim, June 12 2007

Andreas H. W. Kristoffersen

# Table of contents

| 1 | Intro | Introduction1                                                    |    |  |  |

|---|-------|------------------------------------------------------------------|----|--|--|

| 2 | Syste | m description                                                    | 2  |  |  |

|   | 2.1 l | Diode bridge rectifier                                           | 2  |  |  |

|   |       | NPC inverter                                                     |    |  |  |

|   |       | Active front end                                                 |    |  |  |

|   | 2.4 I | High voltage applications                                        | 6  |  |  |

|   | 2.4.1 | Voltage sharing between IGBTs in series                          | 6  |  |  |

| 3 | Semi  | conductors and switches                                          | 8  |  |  |

| 4 | Insul | ated gate bipolar transistor                                     | 10 |  |  |

|   | 4.1 I | Equivalent circuit representations                               | 10 |  |  |

|   | 4.2 I | Principal of operation                                           | 12 |  |  |

|   | 4.2.1 | Reverse blocking mode                                            | 12 |  |  |

|   | 4.2.2 |                                                                  |    |  |  |

|   | 4.2.3 | Conduction modes and conductivity modulation                     | 14 |  |  |

|   | 4.2.4 | i-v characteristics                                              | 15 |  |  |

|   | 4.3   | Switching behavior of IGBT                                       | 16 |  |  |

|   | 4.3.1 |                                                                  |    |  |  |

|   | 4.3.2 | Turn-off transient                                               | 17 |  |  |

| 5 | IGBT  | f power modules                                                  |    |  |  |

|   | 5.1 I | DBC solutions                                                    | 19 |  |  |

|   | 5.2 1 | Press pack modules                                               | 20 |  |  |

| 6 | Suita | ble semiconductor modules for the final solution                 | 22 |  |  |

|   | 6.1   | ABB's HiPak modules with next generation SPT <sup>+</sup> IGBTs  | 22 |  |  |

|   | 6.1.1 | -                                                                |    |  |  |

|   | 6.1.2 | Packaging                                                        | 25 |  |  |

|   | 6.1.3 |                                                                  |    |  |  |

|   | 6.2 l | Planar gate press pack Injection Enhanced Gate Transistor        | 27 |  |  |

|   | 6.2.1 | Packaging                                                        |    |  |  |

|   | 6.3   | Semikron's SEMIX IGBT module                                     | 29 |  |  |

| 7 | Expe  | rimental setup, components                                       | 30 |  |  |

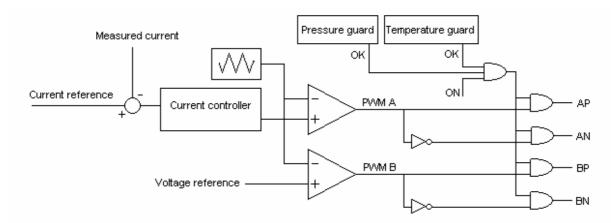

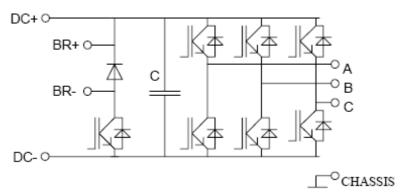

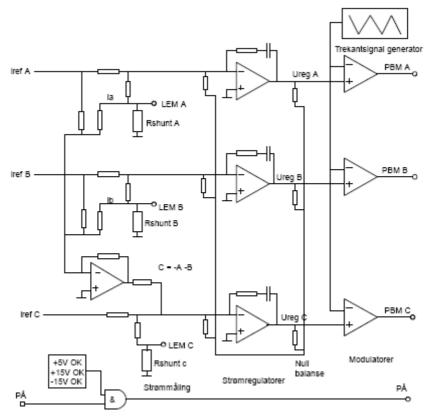

|   | -     | Electrical system                                                |    |  |  |

|   | 7.1.1 | IGBT converter leg                                               | 33 |  |  |

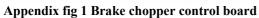

|   | 7.1.2 | Brake chopper control board                                      | 34 |  |  |

|   | 7.1.3 | Current control card                                             | 34 |  |  |

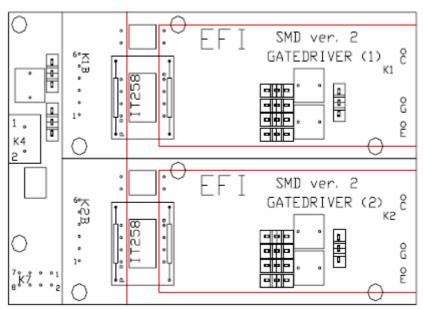

|   | 7.1.4 | Gate driver                                                      | 35 |  |  |

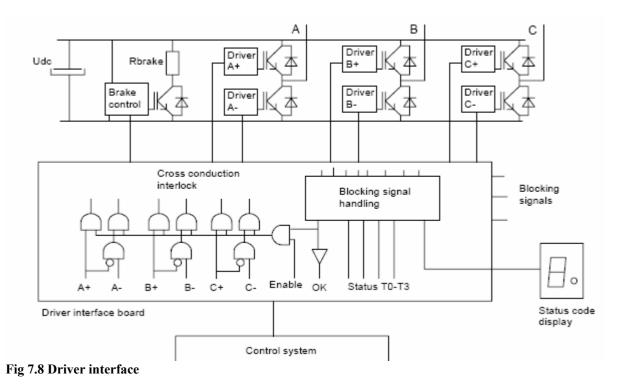

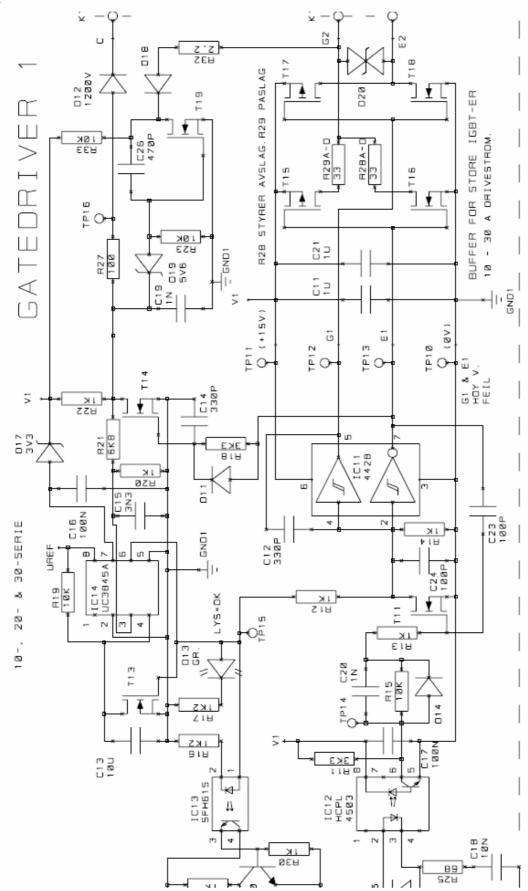

|   | 7.1.5 | Driver interface board                                           | 36 |  |  |

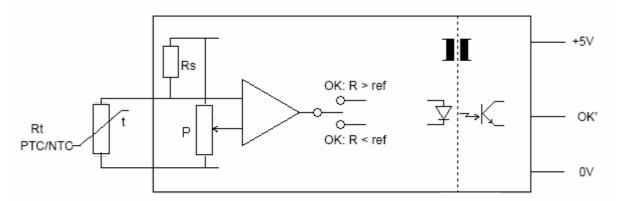

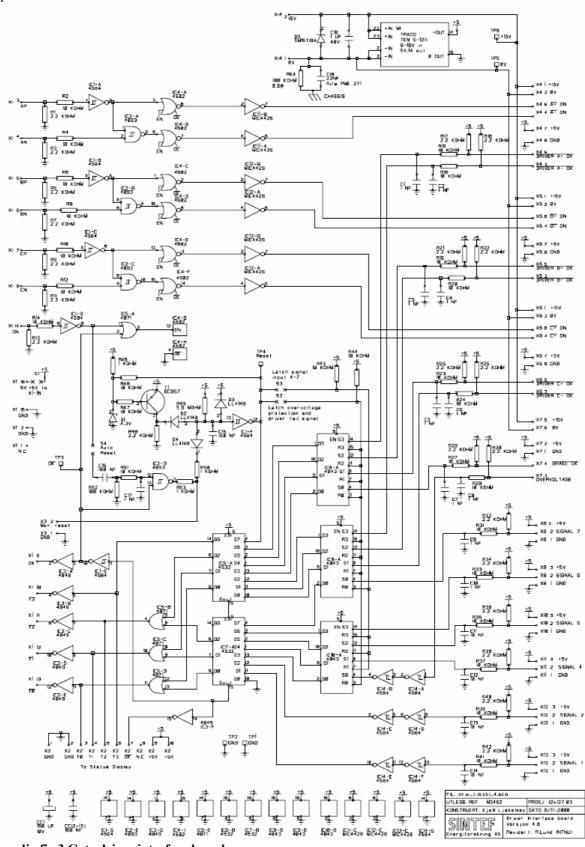

|   | 7.1.6 | Temperature surveillance                                         | 37 |  |  |

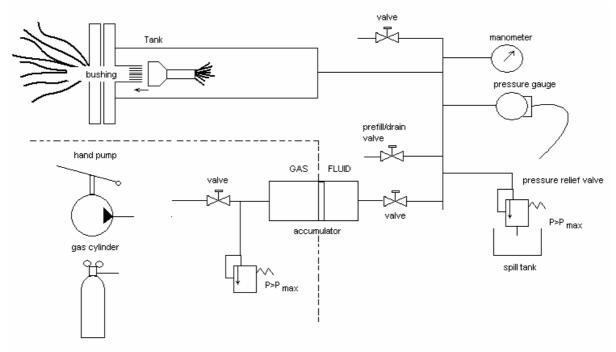

|   | 7.2 I | Pressurising system                                              | 38 |  |  |

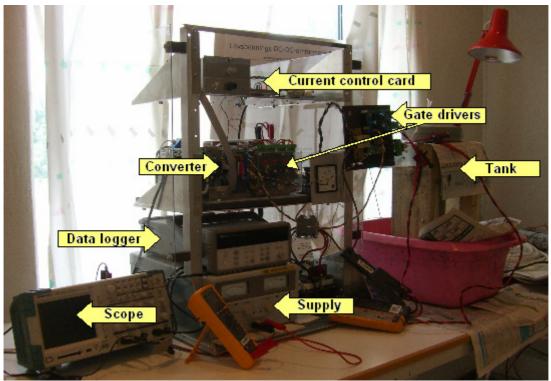

| 8 | Expe  | rimental set up, complete system                                 | 39 |  |  |

| 9 | Expe  | rimental set up, test results                                    | 41 |  |  |

|   | 9.1 I | nitial testing of behaviour                                      | 41 |  |  |

|   | 9.1.1 | Pulse tests with no voltage on DC-link                           | 41 |  |  |

|   | 9.1.2 | Pulse tests with voltage on the DC-link                          | 44 |  |  |

|   | 9.1.3 | Pulse tests; no voltage on DC-link and modified gate driver card | 46 |  |  |

|   | 9.1.4 | Pulse tests; voltage on DC-link and modified gate driver card    |    |  |  |

|   | 9.2 1 | mpact of modifying the gate resistance                           |    |  |  |

|   |       | Continuous switching tests                                       |    |  |  |

|   | 9.3.1 | Thermal testing                                                  | 49 |  |  |

# 🖸 NTNU

|     | 9.3.2          | Loss measurments                                 |  |  |  |

|-----|----------------|--------------------------------------------------|--|--|--|

| 9.  | 4              | Testing with the module submerged in silicon oil |  |  |  |

|     | 9.4.1          | Short term continuous switching test             |  |  |  |

|     | 9.4.2          | Intermittent operation with 20 Å pulses          |  |  |  |

|     | 9.4.3          | Intermittent operation with 30A pulses           |  |  |  |

|     | 9.4.4          | Intermittent operation with 40A pulses           |  |  |  |

|     | 9.4.5          | Continuous switching 10 hour durations           |  |  |  |

|     | 9.4.6          | Long term continuous switching submerged in oil  |  |  |  |

| 10  | Disc           | ussion                                           |  |  |  |

| 11  | Con            | cluding remarks                                  |  |  |  |

| 12  | 2 Further work |                                                  |  |  |  |

| Арр | ppendix        |                                                  |  |  |  |

# Abbreviations

| A:AmpereAC:Alternating currentAFE:Active front endBJT:Bipolar junction transistorDBC:Direct bonded copper | %THD <sub>v</sub> | : | Total harmonic voltage distortion                 |

|-----------------------------------------------------------------------------------------------------------|-------------------|---|---------------------------------------------------|

| AFE:Active front endBJT:Bipolar junction transistor                                                       | Α                 | : | -                                                 |

| BJT : Bipolar junction transistor                                                                         | AC                | : | Alternating current                               |

| r J J                                                                                                     | AFE               | : | Active front end                                  |

| DBC : Direct bonded copper                                                                                | BJT               | : | Bipolar junction transistor                       |

|                                                                                                           | DBC               | : | Direct bonded copper                              |

| DC : Direct current                                                                                       | DC                | : | Direct current                                    |

| EP-IGBT : Enhanced planar insulated gate bipolar transistor                                               | EP-IGBT           | : | Enhanced planar insulated gate bipolar transistor |

| ESR : Equivalent series resistance                                                                        | ESR               | : | Equivalent series resistance                      |

| IEGT : Injection Enhanced Gate Transistor                                                                 | IEGT              | : | Injection Enhanced Gate Transistor                |

| IGBT : Insulated gate bipolar transistor                                                                  | IGBT              | : | Insulated gate bipolar transistor                 |

| JFET : Junction gate field effect transistor                                                              | JFET              | : | Junction gate field effect transistor             |

| MLC : Monolithic capacitor                                                                                | MLC               | : | Monolithic capacitor                              |

| MOSFET : Metal oxide semiconductor field effect transistor                                                | MOSFET            | : | Metal oxide semiconductor field effect transistor |

| NPC : Neutral point clamped                                                                               | NPC               | : | Neutral point clamped                             |

| NPT : Non punch through                                                                                   | NPT               | : | Non punch through                                 |

| PCB : Printed circuit board                                                                               | PCB               | : | Printed circuit board                             |

| PWM : Pulse width modulation                                                                              | PWM               | : | Pulse width modulation                            |

| Rms:Root mean square                                                                                      | Rms               | : | Root mean square                                  |

| SOA : Safe operating area                                                                                 | SOA               | : | Safe operating area                               |

| SPT : Soft punch through                                                                                  | SPT               | : | Soft punch through                                |

| V : Volts                                                                                                 | V                 | : | Volts                                             |

| VSC : Voltage source converter                                                                            | VSC               | : | Voltage source converter                          |

| VSI : Voltage source inverter                                                                             | VSI               | : | Voltage source inverter                           |

## Abstract

Sub sea compression for maintaining reservoir pressure in a gas field is important to have a steady production of gas as it is extracted from the field. Electrical drives in the several megawatt range are suitable to control the compressor motor since it is not desirable to have gears which need maintenance. Problems related to the location on the sea bed have so far been overcome by using massive pressure tanks which hold 1 atmosphere. A new approach would be to allow the pressure on the sea bed to be applied on the electrical components. This will reduce and simplify the system only needing a thin walled casing filled with oil to contain the electronics, but the electronic components then need to be compatible with the oil and function at high hydrostatic pressure. This report include suitable electrical power systems for a compression application, theory around the most likely to be used switch, some available modules and an experimental set up for testing IGBT compatibility with oil.

Converters consisting of rectifiers and inverters are widely used in industrial motor drives and it is assumed that such a converter will be used consisting of a diode bridge rectifier and a neutral point clamped inverter. High voltage applications often operate with voltages above the rated value of many semiconductor components which means that switches must be series connected. A neutral point clamped inverter with series connected switches will be able to handle the high voltages and produce a good spectral output to the motor terminals.

The switches used in the inverter will probably be IGBTs. The IGBT evolved as the most successful device for high power, high switching frequency applications blending MOSFET switching capabilities with BJT on-state conduction properties. Development has produced a lot of versions of this kind of switch, and by modifying doping profiles and geometrical properties a set of devices with improved characteristics has been made. Packaging techniques make it possible to integrate the switches in different environments. Examples are the press pack modules which can be hermetically sealed and the standard DBC solutions.

To test compatibility with insulating oil, an experiment was set up. An IGBT inverter leg module was placed inside a tank which was filled with oil. The module was operated in an H-bridge configuration with another bridge leg on the outside of the tank. Thorough testing before submerging it was performed to ensure and document normal behaviour. When fully submerged the module was tested and the results compared with those from the initial testing. Short duration of continuous switching was also performed followed by intermittent operation with current pulses and long term continuous switching. None of the captured scope pictures or temperature measurements showed deviation from normal IGBT behaviour or change of characteristics. It can then be concluded that when submerging an IGBT module in insulating oil, no instant failure or change of electrical behaviour occurs.

# 1 Introduction

Oil and gas installations on the sea bed saves a lot of money compared to traditional platforms on the surface. Both environmentally and economically, there are a lot of benefits by putting components on the sea bed, but it also arises some challenges that need to be solved to get a reliable and efficient system. One of these challenges related to natural gas production is the need for a compressor unit in the several MW range on the sea bed to maintain production pressure in the reservoir as the gas is extracted from the field. Since access to the unit for maintenance is limited, the system should be as reliable as possible.

A compressor unit with electrical drives to control the performance is suggested as a good solution, but when placed on the sea bed, there is major difference in the working environment for the electronic components which are designed for surface conditions. A way to cope with this problem is to encapsulate the components in a tank holding one atmosphere and fill it with a fluid. This solution is used today, but as the depths increase along with larger physical size of the drives, the tank and penetration for wiring will become expensive. As an alternative, the tank could be completely filled with insulating oil with walls allowing the pressure on the inside to be the same as on the outside. The work in this report is based on that alternative and some aspects around it are investigated.

It will be briefly discussed different electrical drive configurations that may be suitable. Thorough investigation of the most likely to be used semiconductor switch, the IGBT will be given and available modules will also be presented with some of the theory leading to these state of the art devices. Switches and configurations involving power electronic components are the main focus and signal level devices will not be investigated. Description and documentation from the experimental set up where an IGBT power module is tested when fully submerged in oil will be given along with suggestion for further work.

The initial plan was to investigate the behaviour of the transistor under high hydrostatic pressure with an available pressure tank used for similar tests previously, but because of new rules and regulations along with lack of necessary documentation of the available pressure tank, the tank could not be used. Since this was a late discovery within the time frame of this project a compromise had to be made to get some results. The module was only tested submerged in silicon oil instead to test and verify that it will function when completely covered. This was a step back from the initial goal, but still an important step on the way.

# 2 System description

The work throughout this report will be narrowed down to closely investigate one type of power semiconductor. The initial chapters will however introduce the systems where these kinds of semiconductors can be used and that are most likely to be chosen in the final decision.

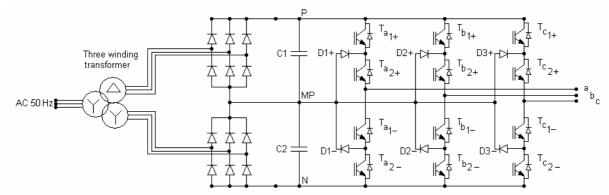

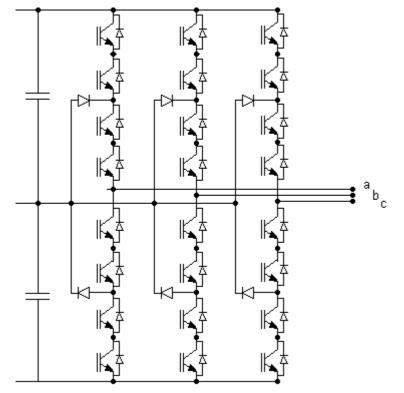

As described in [1] there are several possibilities when deciding what kind of converter topology which will suit the sub sea compression application best. The final decision will have to take into account all the technical details as well as economical and environmental issues. However, the industry has some solutions that are commonly used and perhaps more likely to be chosen than others. The VSI is well known and has proven to be both robust and reliable. NPC inverters also features these qualities and especially for high voltage applications. Since the choice is not made yet, it will be assumed that the converter topology will be a diode bridge based rectifier and a NPC inverter with IGBTs. This assumption corresponds with the assumptions of the initiators of the project [2]. A simplified drawing of the assumed system with diode rectifier and NPC inverter is presented in Fig 2.1. The figure only shows the power modules. Signal level devices in the control logic are left out since these are not the main scope of interest.

Fig 2.1 System description

Other possible solutions can be found in [1] where a short description of NPC and some other multilevel inverters are presented. Detailed information on other multilevel configurations can be found in [3].

### 2.1 Diode bridge rectifier

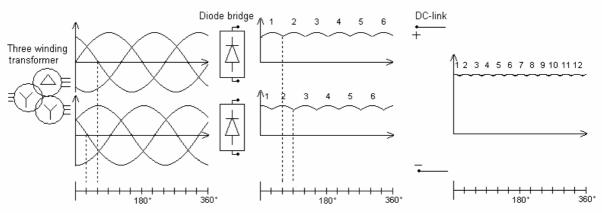

The diode rectifier bridge rectifies the sinusoidal voltages from the secondary and tertiary side of the three winding transformer to a DC-voltage with some ripple. In a 12 pulse configuration the output from the rectifier bridges will be as shown in Fig 2.2. Voltage from the supply is transformed through the three winding transformer where one of the secondary outputs is phase shifted 30 degrees. Each diode bridge produces a 6 pulse output phase shifted 30 degrees with respect to each other. When combined on the DC-link, a 12 pulse output is obtained. To further improve the DC-voltage supply for the inverter, a capacitor bank is installed between the positive- and the negative DC-bus.

Fig 2.2 Waveforms through rectification

Because of the 12 pulse configuration, the harmonic currents drawn from the main bus is significantly reduced. The dominant harmonics will be around the multiples of 12 i.e. 11<sup>th</sup> and 13<sup>th</sup>, 23<sup>rd</sup> and 25<sup>th</sup> and so on. The other harmonics will be cancelled out to a negligible degree. This is in most applications enough to fulfil the %THDv requirements stated by the Bureau Veritas in Norway or the American Bureau of Shipping in USA or other official authorities for classifications of offshore and maritime installations. A typical %THDv limit can be 5% on the main bus with no single harmonic larger than 3% up to the 100<sup>th</sup> [4].

If the 12 pulse configuration does not meet the requirements, a 24 pulse configuration can be used. With 24 pulse output on the DC-link, the dominant harmonics will be around the multiples of 24 with the first ones at  $23^{rd}$  and  $25^{th}$ . This will significantly reduce the total harmonic content in a typical installation and in most cases be more than sufficient to fulfil the requirements.

One way to obtain 24 pulse output is to use four diode bridge rectifiers and two three winding transformers. The three winding transformers primary sides then have to be phase shifted with respect to each other. A zigzag configuration on the primary side makes this possible as shown in Fig 2.3.

Fig 2.3 Configuration with 24 pulse output

The reason for wanting to reduce the harmonic distortion is to protect other sensitive equipment connected to the same network. If all other components connected are tolerant to higher levels of harmonic distortion, the %THDv can be allowed higher than previously stated. This is in fact the case for the planned sub sea compression application where the other consumers connected to the same isolated network all consist of components with a higher tolerance for harmonic distortion.

### 2.2 NPC inverter

The rectified output from the diode bridges serves as input to the inverter where the frequency and amplitude of the output can be controlled. The three-level, so called neutral point clamped, inverter has the advantage of dividing the maximum amplitude of the output voltage into two steps. This reduces the harmonic content and the line to line output achieves a very high content of the fundamental component. It also reduces iron losses in the motor. Other advantages are the ease of control where the gating electronics is very simple, no snubber circuit is necessary and that each switch is protected from the large DC-link voltage by the clamping diodes [3].

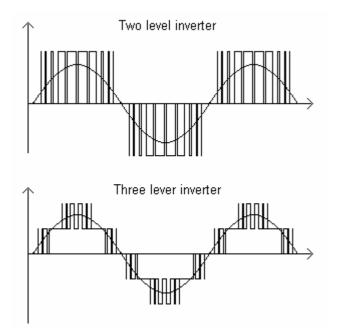

Line to line output in a NPC-inverter has five different voltage levels. These levels are obtained by the degree of freedom of switch statuses which allows the output to be switched via the neutral point. Compared to a two level inverter the NPC has 25 possible switching conditions whereas the two-level has 7 [5]. The output waveforms from a two-level inverter and a three-level inverter are plotted along with the fundamental component in Fig 2.4. It is clearly evident that the three-level output has a higher content of the fundamental component.

Fig 2.4 Voltage waveforms of two- and three-level inverter

There are a number of switching schemes available for a three-level inverter. One example is asynchronous sinusoidal PWM where the frequency of the triangular signal is kept constant. Other forms of PWM with vector control are also developed and are commonly used.

### 2.3 Active front end

Although it has previously been stated that the %THDv level can be allowed higher in the isolated network which the compressor unit is to be connected, the possibility of further lowering the harmonics is present by using an active front end.

The current fed to the motor from a three level inverter is near perfect and this feature is exploited for improving supply side current wave-shape. Using an identical converter configuration for the line-side rectifier a four-quadrant drive-converter configuration is created, that not only draws near perfect sinusoidal current from supply line, but also allows smooth reversal of power flow to provide motoring and regenerative braking. AFE uses fast internal switching together with an input choke. The AFE is commutation fault proof, which means no blown fuses with brown or black outs. A stable DC-link voltage is maintained even on very weak power supplies and at severe voltage dips. The configuration is illustrated in Fig 2.5 [5].

Fig 2.5 IGBT inverter with active front end

Should the mains dip during regeneration, the energy returned to the supply is maintained because the current increases proportional to the voltage decrease. This allows maintaining full capacity and speed even during phases of fluctuating supply voltage. The AFE is dimensioned so that even voltage increases associated with regeneration into weak supplies are trouble-free. Safe current limiting is also possible if the AFE regenerates into a short circuit [5].

Another feature of the AFE is power factor control in both motoring and regenerative mode. As standard, the AFE can compensate for system power factor in two power factor correction modes. It can either ensure constant VAr or constant power factor. In the constant VAr mode a percentage, 0% to 100%, of the AFE current capacity is utilized as a reactive current, leading or lagging, and the reactive current is independent of the motor load. However, in the constant power factor mode the power factor is set in the range 1.0 to 0.8 leading or lagging and the reactive current is dependent of the motor load. The power factor or VAr requirement is set as a fixed value on a parameter or a variable value changed via a communication bus or analogue input. This feature can be taken advantage of for compensation of other inductive or capacitive loads connected to the same line [5].

Whenever the drive is running at an output below its design rating the remaining reactive power can be used for compensation. This can also be designed by adequate selection of the respective converter size. Only the AFE rectifier and the DC-link capacitors have to be matched to the expected reactive power demand. This is of essential importance for networks, which due to weight and size of the electrical equipment have do be optimized most carefully with respect to the ratio of real power versus reactive power load. Ship propulsion and auxiliary drives or equipment on platforms are typical examples [5].

### 2.4 High voltage applications

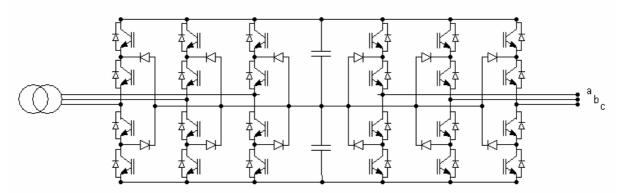

With high voltage applications, the three-level configuration with the clamping diodes effectively protects the IGBTs from getting all the DC-link voltage across the collector and emitter. Some applications might require even higher voltage levels above the rating of what is available of IGBTs. A solution is to series connect two IGBTs and operate the pair as one switch. The three-level configuration can still be used, but with some extra control that ensures that the switches switch simultaneously. The three level inverter with two series connected IGBTs operated as one switch is shown in Fig 2.6.

Fig 2.6 Three level inverter with series connection of IGBTs

There have been developed several different approaches to ensure even voltage dividing between the switches operating in series. A first approach is based on the use of turn-off snubbers in parallel to each device in order to force the slope of the voltage variation across them to be dominated by the charge of the capacitance and hence to become independent on the devices switching times. Dynamic voltage sharing can also be achieved with capacitors in parallel with the switches.

### 2.4.1 Voltage sharing between IGBTs in series

Test results from experiments with switches in series shows that the faster device will have all the supply voltage applied over its terminals for a short duration. This may bring the device out of its safe operating area. Although the switches are equal and the driving circuits are the same, the switching will not happen exactly at the same time. Parameter deviations within a

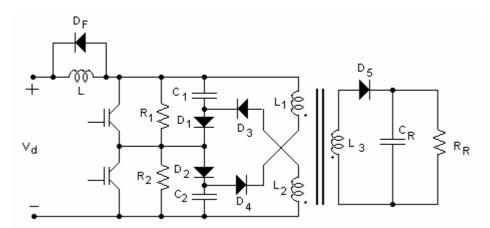

population of devices are inevitable, and when the number of components increases it is almost definite that the switching will not be exactly at the same time. The concept of voltage sharing with capacitors in parallel with the switches is investigated in [6], and the topology is reproduced in Fig 2.7.

Fig 2.7 Schematics of the circuit used for the series connection of two IGBTs

In the figure, the load inductance and the freewheeling diode are L and  $D_F$ , respectively. The resistances  $R_1$  and  $R_2$  provide for a uniform steady state voltage distribution, whereas the remaining part of the circuit is used to evenly share the voltage among the devices during switching operations.

If the upper switch is slightly faster than the lower switch, the load current is forced to charge the capacitance  $C_2$ . If the duration of the period of which the upper switch is on and the lower switch is off is small enough combined with a large capacitance of  $C_2$ , the voltage over the lower switch will be kept at about  $\frac{1}{2} V_d$ . When the lower switch turns on each capacitor is in parallel with one of the primary windings of the transformer through the diodes  $D_3$  and  $D_4$ .  $C_2$ , which has accumulated more energy than  $C_1$ , will transfer this energy to the inductor,  $L_1$ , and the voltage over  $C_2$  will decrease while the current through  $L_1$  increase linearly. When the faster upper switch turns off, the load current is forced to charge  $C_1$ , holding a voltage of approximately  $\frac{1}{2} V_d$  over the slower lower switch. When this switch turns off, the energy stored in the transformer will be transferred to the secondary side through  $R_R$  [6].

Another interesting approach makes use of active driving circuits which sense the voltage across each device and are able to affect their switching times in order to avoid unbalance of the voltage among them. More detailed information about this approach can be found in [7]

# 3 Semiconductors and switches

For an industrial electrical motor drive, there are many switches that are available on the marked today ranging from low power single units to high power modules.

Ideally, a semiconductor switch should possess all the characteristic features listed in Table 3.1 [8]. Although advances in power devices have revolutionized power electronics, there is by today still not a single switch which possesses all these characteristics. However, there is a wide spectrum of devices intended for different applications where a fair degree of similarity with some of the characteristics in Table 3.1 is obtained. An example is the thyristor, which can carry large currents in the forward direction, in the area of several kA, with less than 2 V voltage drop. It is also capable of blocking very large voltages in the reverse direction, in the area of more than 6 kV. A major drawback with the thyristor is that the turn-off is obtained by collector-emitter voltage reversal.

In applications where the load current is turned on and off by the input signal, power bipolar junction transistors (BJT) have been extensively used. A drawback with this device is the need of a high base current drive both in on-state and during turn-off, but the on state losses are very small.

The gate turn off thyristor (GTO) is another device that is able to turn on and off the load current, but with higher forward current capabilities. The drawback of this device is the excessively higher drive current along with limitations in switching frequency.

| Very low or zero driving losses              | Obtained with high input impedance so that    |  |

|----------------------------------------------|-----------------------------------------------|--|

|                                              | the drive current is infinitesimally small.   |  |

|                                              | Furthermore, the drive circuit should be      |  |

|                                              | simple an inexpensive.                        |  |

| Insignificant on-state or forward conduction | The forward voltage drop should be zero at    |  |

| losses                                       | the operating current. Additionally the       |  |

|                                              | operational current density large, making the |  |

|                                              | chip small in size and cost effective for a   |  |

|                                              | given current-carrying capability             |  |

| Minimal off-state or reverse blocking losses | The reverse blocking capability should be     |  |

|                                              | infinitely large even when exposed to         |  |

|                                              | elevated temperatures.                        |  |

| Extremely low switching losses               | Both the turn-on and turn-off times should    |  |

|                                              | approach zero.                                |  |

#### Table 3.1 Characteristics of a perfect switch

Other devices with gate turn-off capabilities evolved from the progressive development of the existing devices and include the integrated gate commutated thyristor (IGCT) and different types of metal oxide semiconductor field effect transistors (MOSFET). MOSFETs have high switching frequency capabilities along with ease of drive and capability to withstand high rates of rise in the on-state voltage. A major drawback is larger on-state losses and the limitations in voltage ratings because the device operates by unipolar conduction. With increasing voltage ratings, the inherent reverse diode shows increasing reverse recovery time causing more switching losses [8].

To obtain features closer to those listed for a perfect switch; it was worthwhile blending the properties of MOSFETs and bipolar devices. After some development, the insulated gate bipolar transistor (IGBT) evolved as the most successful device combining the best from each type. Another semiconductor worth mentioning is the injection enhanced gate transistor, the IEGT which is closely related to the IGBT, and shows excellent forward conduction capabilities.

The switches in the inverters discussed so far are illustrated as IGBTs, but could be one of the other types as well. IGCT is an alternative that could be argued is the best and it is hard to say if that is the case. A limitation with this device is that the gate driver must be as close as possible to the gate since en extremely large current is drawn out to turn it off. With large physical distance, the inductance in the wires would cause high voltage that could destroy the device. This means that it is hard to physically separate the control logic from the power semiconductor which limits the degree of freedom when placing components in the system. Because of the large power and switching requirements the switches will most probably be power IGBTs in the final solution. Simple gate control and low on state losses are other arguments for using the IGBT. Because the IGBT is the most likely to be used switch, the theory presented will focus on features and characteristics around this kind of transistor.

# 4 Insulated gate bipolar transistor

As a reference for subsequent experiments and to fully understand the mechanisms and processes leading to the results, theory around the IGBT is presented in this chapter.

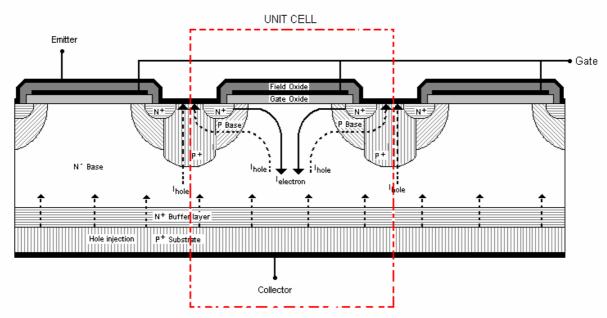

Fig 4.1 [8] shows, schematically, the cross section of the basic IGBT structure. This is one of the several structures possible for this device. In practice, the power IGBT essentially comprises a repetitive array of millions of unit cells, where one cell labelled red in the figure can be seen.

Fig 4.1 Cross section of the basic IGBT structure

As illustrated in Fig 4.1, the IGBT is made up of several different layers. The top  $N^+$  layer is the emitter, and the bottom  $P^+$  layer is the collector. Between the emitter and the collector there are two base regions known as the P-base and the N-base. In the illustrated figure the P-base also includes  $P^+$  wells that penetrate deeper into the N-base. The N-base is often referred to as the  $N^-$  drift region, and the thickness and resistance of the N-type material between the P wells control the voltage rating. In addition, there is an  $N^+$  buffer layer on top of the  $P^+$  collector layer. This layer is not essential, but including this layer introduces a feature that is well suited in some applications. This will be further discussed in a subsequent chapter.

Current paths are also included in Fig 4.1, where the dotted lines represent movement of holes while the continuous lines indicate electron movement.

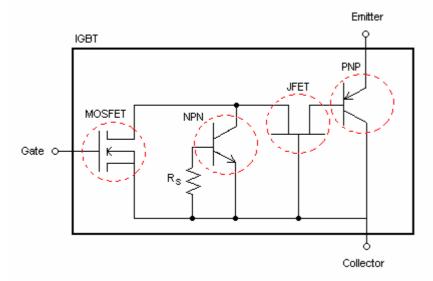

### 4.1 Equivalent circuit representations

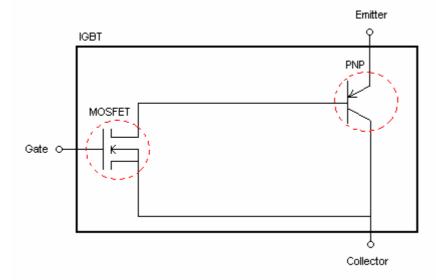

A clear perception of IGBT operation can be obtained by examining its equivalent circuit. A close investigation of the cross sectional illustration in Fig 4.1 reveals a pair of NPN and PNP transistors forming a parasitic thyristor. The collector of the NPN transistor is connected to the base of the PNP transistor, and likewise the collector of the PNP transistor supplies the

base current for the NPN transistor through a JFET which represents the constriction of current between any two neighbouring IGBT cells. The equivalent circuit can be drawn as shown in Fig 4.2, where the resistance  $R_s$  represents the shorting resistance between the base of the NPN transistor and the emitter. Emitter-base shorting is essential to ensure that the sum total gain of the NPN and PNP transistors does not exceed unity which will cause latch up of the parasitic thyristor. Furthermore, the MOSFET channel is formed in the P base below the gate oxide. This channel joins the N<sup>+</sup> emitter and N<sup>-</sup> collector of the NPN transistor, so this transistor is shunted by a MOSFET in the equivalent circuit [8].

Fig 4.2 Equivalent circuit models of IGBT

Simplifications in the equivalent circuit can be obtained by looking at the emitter-base shorting. For normal operation, it is absolutely necessary that the NPN-transistor does not turn on, and this is avoided by shorting the base of the NPN transistor and the emitter. This will effectively reduce the probability of the NPN transistor to turn on to a negligible degree, and thus the equivalent circuit can be simplified to that shown in Fig 4.3 [8].

Fig 4.3 Simplified equivalent circuit model of IGBT

The configuration in Fig 4.3 can be viewed as an N-channel enhancement mode MOSFET driving a PNP bipolar transistor.

### 4.2 Principal of operation

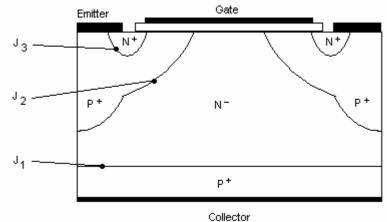

With zero gate bias applied, the IGBT structure shown in Fig 4.4, is equivalent to a PNPN break-over diode having an emitter short. The IGBT remains off when the collector is at a higher potential than the emitter. This is because the junction, J<sub>2</sub>, between the P-base and N<sup>-</sup> drift region is reversed biased. Similarly, the IGBT remains in the off state when the collector-emitter voltage is less than zero, due to reverse bias across the junction,  $J_1$ , between  $P^+$  substrate and  $N^-$  drift region layer.

Fig 4.4 IGBT structure

With positive collector-emitter voltage, the IGBT can be turned on by applying a positive gate-emitter voltage. The positive gate-emitter voltage induces an N-channel in the underlying P region, thereby connecting the  $N^+$  emitter with the  $N^-$  base. The junction,  $J_1$ , is then forward biased and hole-injection from the  $P^+$  collector substrate into the N<sup>-</sup> base starts. Consequently, conductivity modulation of this layer takes place, reducing its resistance and bringing about a large flow if collector emitter current

To turn off the IGBT, the gate-emitter voltage is made zero so that the channel in the P region is removed. Depending on the value of the collector-emitter voltage, V<sub>ce</sub>, three different regions of operation are observed in the IGBT. In the first regime, at a small value of  $V_{ce}$ ~0.7 V, the IGBT is a vertical diffused MOSFET in parallel with a PNP transistor. Current transport takes place by recombination of excess electrons and holes in the N<sup>-</sup> region. The second regime commences from  $V_{ce} > 0.7$  V where the characteristics portray MOSFET behaviour. At high V<sub>ce</sub> values, the excess holes injected from the emitter of the PNP transistor are not absorbed by recombination in the N<sup>-</sup> base and spill over to the P base contributing to PNP bipolar current. The MOSFET current I<sub>mos</sub> is the base current of the bipolar transistor, and the collector emitter current of the IGBT duplicates the general shape of MOSFET characteristics except that it is the amplified version of I<sub>mos</sub>. In the third regime, when the current exceeds a critical level, the device latches up like the ON state of a thyristor. Consequently, gate control is lost [8].

#### 4.2.1 Reverse blocking mode

With the gate terminal shorted to the emitter terminal, a positive bias is applied to the  $N^+$ emitter while a negative bias is applied to the  $P^+$  collector. In this condition, with reference to Fig 4.4, junctions  $J_1$  and  $J_3$  are reverse biased while the junction  $J_2$  is forward biased. The reversed biased junctions J<sub>1</sub> and J<sub>3</sub> inhibit the current flow through the device, imparting to it the reverse blocking capability. The voltage is supported mainly across the junction  $J_1$ . A large fraction of the depletion region extends across the low doped N<sup>-</sup> base and slightly across the P<sup>+</sup> collector due to its heavy doping. The reverse blocking voltage is determined by an open base transistor comprising P<sup>+</sup> collector, N<sup>-</sup> base and P-base regions. This transistor may suffer breakdown by reach-through for the thin N<sup>-</sup> base, or light doping of this region. The resistance and the thickness of the N<sup>-</sup> base must therefore be optimized for the required breakdown voltage. A rule of thumb is to choose the N<sup>-</sup> base thickness equal to the depletion layer width at the maximum operating voltage, plus one minority carrier diffusion length [8].

#### 4.2.2 Forward blocking mode

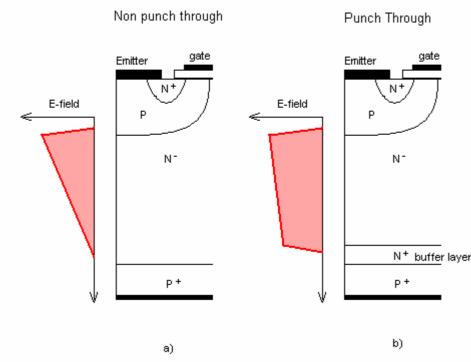

The forward blocking mode is obtained when the collector has a positive potential and the emitter negative while the emitter is shorted to the gate. In this condition, with reference to Fig 4.4, the junctions  $J_1$  and  $J_3$  are forward biased. The blocking occurs across junction  $J_2$  which is reversed biased. The depletion region stretches partly into the P-base, but most of it into the N<sup>-</sup> drift region. In Fig 4.5 a) the electric field is shown for a non punch through IGBT. As it can be seen, the field does not reach all the way to the P<sup>+</sup> substrate, and hence the name non punch through. The forward voltage blocking capabilities can be found as the shaded red area under the electric field curve.

Fig 4.5 a) Forward electric field in Non Punch through IGBT b) Forward electric field in Punch through IGBT

As mentioned previously and indicated in Fig 4.1, there is sometimes added an extra layer in the IGBT structure, the  $N^+$  buffer layer. This layer is added to improve the forward voltage blocking capabilities. As the forward voltage increases, the depletion layer will extend all the way through the  $N^-$  drift region and come in contact with the  $N^+$  buffer layer. When this occurs, further increases in voltage will not cause the depletion region to widen any further because the large doping density in the  $N^+$  layer effectively blocks further growth of the depletion layer. Instead the electric field profile begins to flatten out, as shown in Fig 4.5 b),

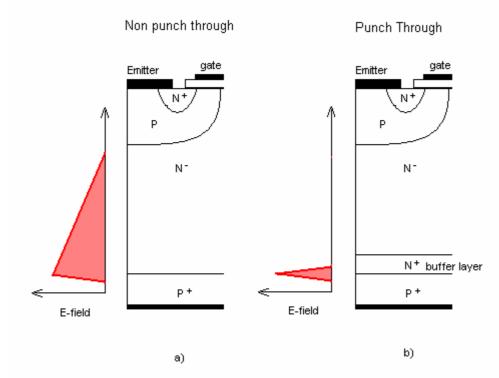

becoming less triangular and more rectangular. The area under the electric field curve is larger than for the non punch through, indicating a larger voltage blocking capability. If the forward voltage blocking capability is kept equal to the non punch through, the effect of the added  $N^+$  buffer layer will be lower on-state resistance. This is obtained because the length of the  $N^-$  drift region can be reduced. However, the increase in forward blocking capabilities or lowering of on-state resistance does not come without a cost. As illustrated in Fig 4.6 b), the reverse voltage blocking capability is severely reduced compared to the non punch through IGBT in Fig 4.6 a). This is caused by the junction between the highly doped P<sup>+</sup> substrate and the highly doped N<sup>+</sup> buffer layer, which is unable to block any voltage of significant degree [9]. This can be seen from the small shaded area under the electric field curve. A non punch through IGBT can be fabricated with reverse blocking voltage equal to forward blocking voltage because the highly doped P<sup>+</sup> substrate is in contact with the lightly doped N<sup>-</sup> drift region allowing growth of the depletion layer into it.

Fig 4.6 a) Reverse electric field in Non punch through IGBT b) Reverse electric field in Punch through IGBT

The disadvantage of having insignificant reverse blocking capabilities is in some applications not a problem. In inverter applications where the inverter is fed by a rectifier, the switches will never have to block any reverse voltages, so in high voltage, high power inverter applications the punch through IGBT will be very well suited.

#### 4.2.3 Conduction modes and conductivity modulation

An IGBT in forward blocking state can be transferred to the forward conducting state by removing the gate-emitter shorting and applying a positive voltage of sufficient level to invert the Si below in the P base. Under this condition the voltages at the terminals must be positive collector, negative emitter and positive gate. With these requirements satisfied, an n-channel develops in the underlying P-base connecting the  $N^+$  emitter to the  $N^-$  drift region. Through this channel electrons are transported from the emitter to the drift region. This flow of

electrons lowers the potential in the N<sup>-</sup> region, and the junction between the  $P^+$  collector substrate and the drift region becomes forward biased. Under these forward bias conditions, a high density of minority carrier holes is injected into the N<sup>-</sup> layer. When the injected carrier concentration is much larger than the background concentration, a condition of high-level injection is said to prevail in the N<sup>-</sup> region of the IGBT. A hole injected by the P<sup>+</sup> collector from a point directly below the emitter-base short traverses a rectilinear path through the N region/P-base and reaches the N<sup>-</sup> base/P-base space charge region. Finally it arrives at the emitter contact after crossing the  $P^+$  region. Another hole, which is ejected from a point directly below the gate region, travels vertically upwards and reaches under the gate. Here it is repelled by the positively charged accumulation layer below the gate and diverted toward the P-base/N<sup>-</sup> base space charge region. Moving underneath the N<sup>+</sup> emitter and through the P<sup>+</sup> region, it is captured by the emitter contact. Thus at high collector supply voltage, a plasma of holes builds up in the N<sup>-</sup> drift region. This plasma of holes attracts electrons from the emitter contact to maintain local charge neutrality. In this manner, approximately equal excess concentrations of holes and electrons are gathered in the N<sup>-</sup> base. These excess electron concentrations drastically enhance the conductivity of N<sup>-</sup> base. The mechanism of rise in conductivity is referred to as conductivity modulation of the N<sup>-</sup> drift region. The ON state resistance and thereby the forward voltage drop is then significantly reduced [8].

#### 4.2.4 i-v characteristics

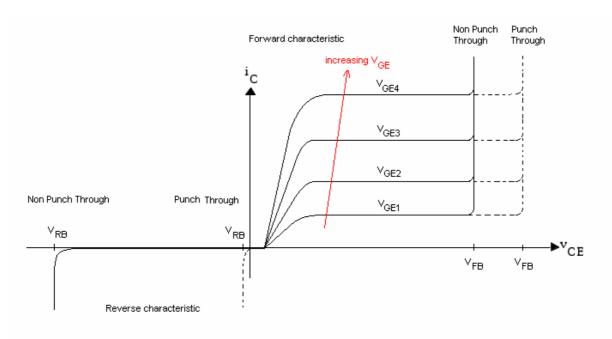

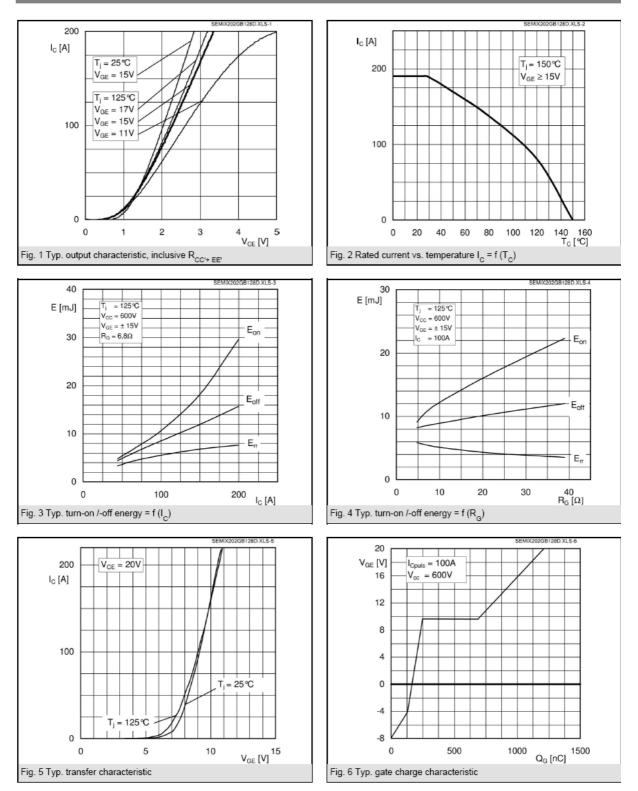

The i-v characteristics of IGBTs are shown in Fig 4.7, and consist of two operating regions, reverse and forward. The steady state forward characteristic show several lines plotted, each of which corresponds to a different gate-emitter voltage. Keeping the gate-emitter voltage fixed, the collector-emitter current is measured as a function of collector-emitter voltage.

Fig 4.7 i-v characteristics of IGBT

The reverse blocking capability for both punch through and non punch through IGBTs are indicated with  $V_{RB}$ . As it can be seen, the reverse blocking voltage of a non punch through IGBT can be as large as the forward voltage,  $V_{FB}$ , while the reverse blocking voltage of a punch through will be close to zero. If the N<sup>-</sup> drift region is kept equal in length in the punch

through and non punch through IGBTs, the forward blocking voltage will be larger for the punch through, as indicated in the figure.

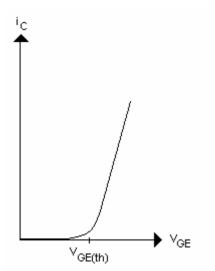

The transfer characteristics of an IGBT will be equal to that of a MOSFET. The transfer characteristic is shown in Fig 4.8. The IGBT will start conducting as soon as the gate-emitter voltage exceeds the threshold voltage  $V_{GE(th)}$ , and the N-channel is formed in the P-base.

Fig 4.8 Transfer characeteristic of IGBT

### 4.3 Switching behavior of IGBT

The IGBT is switched by applying gate pulses. When a pulse is applied, the IGBT turns on, while it turns off when the pulse ceases. The switching behaviour can be thoroughly described by looking at an IGBT in a power circuit.

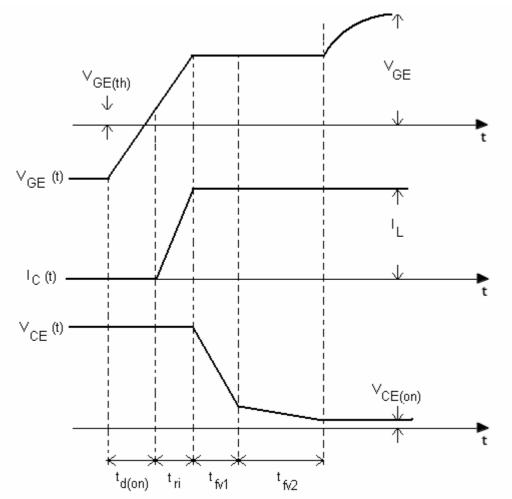

#### 4.3.1 Turn-on transient

The switching waveforms of an IGBT in a clamped inductive circuit are shown in Fig 4.9. The time constant (L/R) of the load is assumed to be large compared to the switching frequency so the load current can be considered to be constant. The IGBT turn-on switching performance is dominated by its MOS structure. During t<sub>d(on)</sub> the gate current charges the constant input capacitance with a constant slope until the gate-emitter voltage reaches the threshold voltage V<sub>GE(th)</sub> of the device. During t<sub>ri</sub>, load current is transferred from the diode into the device and increases to its steady state value. The gate voltage rise time and IGBT transconductance determine the current slope and as a result the length of the interval t<sub>ri</sub>. When the gate-emitter voltage reaches  $V_{GE(on)}$  that will support the steady state collector current, collector-emitter voltages starts to decrease. After this there are two distinct intervals during IGBT turn on. In the first interval the collector-emitter voltage drops rapidly as the gate-drain capacitance of the MOSFET portion of IGBT discharges. At low collector-emitter voltage the capacitance increases. A finite time is required for high level injection conditions to set in the drift region. The pnp transistor portion of the IGBT has a slower transition to its on state than the MOSFET. The gate voltage starts rising again only after the transistor comes out of its saturation region into the linear region, when complete conductivity modulation occurs and the collector-emitter voltage reaches its final on-state value [10].

Fig 4.9 IGBT turn on waveforms in a clamped inductive load circuit

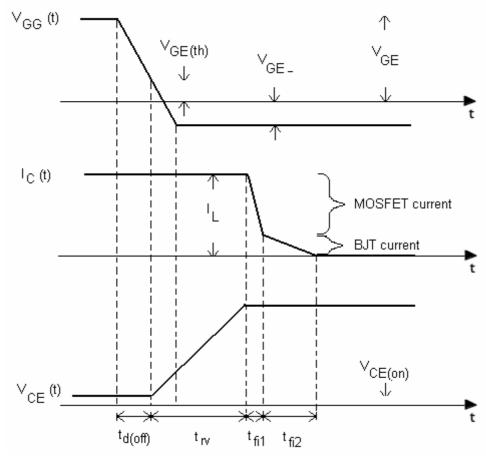

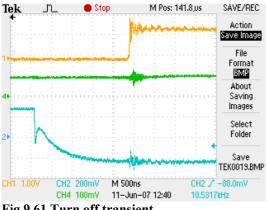

#### 4.3.2 Turn-off transient

Turn off begins by removing the gate-emitter voltage. Voltage and current remain constant until the gate voltage reaches  $V_{GE(on)}$  required to maintain the collector steady state current as shown in Fig 4.10. After this delay time, the collector voltage rises, while the current is held constant. The gate resistance determines the rate of collector voltage rise. As the MOS channel turns off, collector current decreases sharply during t<sub>fi1</sub>. The MOSFET portion of the IGBT determines the turn off delay time and the voltage rise time. When the collector voltage reaches the bus voltage, the freewheeling diode starts to conduct. However, the excess stored charge in the N<sup>-</sup> drift region during on state conduction must be removed for the device to turn off. Recombination of the minority carriers in the base region gradually decreases the collector current and results in a current tail. Because there is no access to the base of the PNP-transistor, the excess minority carriers can not be removed by reverse biasing the gate. The t<sub>fi2</sub> interval is long because the excess carrier lifetime in this region is kept high to reduce on-state voltage drop. Because the collector-emitter voltage has reached the bus voltage in this interval a significant power loss occur that increases with frequency. Therefore the current tail limits the IGBT operating frequency and there is a trade off between the on-state losses and faster switching times. For an on-state current of Ion, the magnitude of current tail, and time required for the collector current to decrease to 10% of its on-state value, turn-off (t<sub>off</sub>) time, are approximated as,

🖸 NTNU

(2)

$$I_{C}(t) = \alpha_{pnp} I_{on} e^{-(t/\tau_{HL})}$$

<sup>(1)</sup>

$t_{off} = \tau_{HL} \ln(10\alpha_{pnp})$

$$\alpha_{pnp} = \frac{1}{\cosh\left(\frac{l}{L_a}\right)} = \operatorname{sech}\left(\frac{l}{L_a}\right)$$

(3)

- I<sub>c</sub> = magnitude of collector current

- $t_{off}$  = turn-off time

- $\alpha_{pnp}$  = gain of PNP-transistor

- $\tau_{HL}$  = high level lifetime

- 1 = undepleted basewidth

- $L_a$  = ambipolar diffusion length

By reducing the life time and the gain of the PNP-transistor,  $\tau_{HL}$  and  $\alpha_{pnp}$  respectively, the magnitude of the current tail can be reduced. However, the conductivity modulation decreases, which increase the on-state voltage drop in the drift region. Therefore, higher speed IGBTs have lower current rating.

Fig 4.10 IGBT turn off waveforms in a clamped inductive load circuit

# 5 IGBT power modules

The compression application will have to use power modules with high ratings to ensure safe and reliable operating of the system.

The most suitable power semiconductor package for a high power sub sea compression application will probably be an IGBT power module with several paralleled chips or an IGBT press pack module. IGBT modules with paralleled chips have high current carrying capabilities and are well known and documented by numerous manufactures. The press pack is designed to have a very robust structure and can also handle large currents and voltages. Other types are also available and include the so called hockey puck package and discrete packages. The discrete package contains only one die and is constructed for medium voltage applications. The hockey puck package contains one large die and is used for very high power applications.

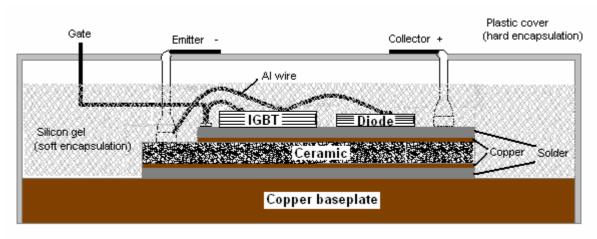

IGBT power modules with paralleled dice have current carrying capabilities depending on the size and the number of dice along with the current carrying capabilities of the wires paralleling the dice. The dice are mounted on a substrate or a lead frame which in turn is mounted on a copper baseplate or a thick film baseplate, forming a stacked formation. Stacking techniques such as direct bond copper (DBC), insulated metal substrate (IMS) and thick film stacking are common. Connection to gate, emitter and collector are provided and the paralleling of chips is carried out using aluminium bond wires. For protection from partial discharge and impurities, silicon gel is provided to cover all components and on top of that, hard plastic encapsulation with connection to external terminals.

One power module can consist of an inverter leg or a full inverter module with all the phase legs in one package. The heat sink will then be common for all legs. Electrical isolation of the baseplate from the semiconductor is necessary in order to contain multiple phases on the same heat sink. Another important reason for electrical isolation of the baseplate is safety where the heat sink can be held at ground potential [11].

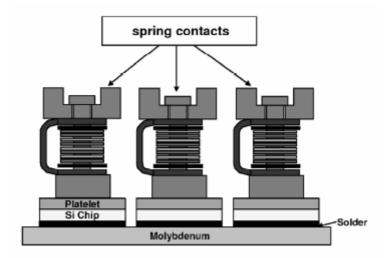

Flat- or press-pack encapsulation offers several advantages over the traditional module package. In a press-pack IGBT, electrical contact is established by pressing the IGBT chips between two high-planarity disks. An adequate stress relief layer is included to forebear the compression. The outermost poles are the emitter and collector pads, both made of nickel plated copper. On the emitter side, a molybdenum washer and a nickel-plated copper foil are inserted between the emitter pole and the IGBT chip. Because the copper is a soft material, it ensures proper electrical contact and also enhances uniformity of pressure distribution.

### 5.1 DBC solutions

In Fig 5.1 a cross section of a DBC solution is illustrated where the copper baseplate, solder layers, ceramic layers, dice, silicon gel, bond wires and housing can be seen. In DBC solutions it is the ceramic layer that isolates the semiconductors from the baseplate.

Fig 5.1 Direct bonded copper packaging of IGBT power module

DBC substrates are composed of a ceramic insulator, typically aluminium oxide, Al<sub>2</sub>O<sub>3</sub>, or aluminium nitride, AlN, onto which pure copper metal is attached by a high temperature eutectic melting process and thus tightly and firmly joined to the ceramic. The process is carried out by forming a thin film of oxide on the copper and then bringing the copper into intimate contact with the ceramic at an elevated temperature. The thin oxide layer on the copper then chemically bonds to the substrate. The assembly is cooled back to room temperature which imparts additional strength to the stacked structure because the ceramic is under compression due to the higher thermal expansion coefficient (CTE) of the copper. The total thermal expansion coefficient of the stack is much closer to that of the silicon in the dice than pure copper if the thickness of the ceramic and copper are in proper proportion [11]. This can be seen from Table 5.1 [12], where some material properties are listed.

| Material                       | Thermal conductivity [W/mK] | CTE [µm/K] |

|--------------------------------|-----------------------------|------------|

| Al <sub>2</sub> O <sub>3</sub> | 30                          | 7.4        |

| AlN                            | 170                         | 4.2        |

| Cu                             | 385                         | 18.5       |

| Si                             | 124                         | 3.6        |

Table 5.1 Material properties

The unique usefulness of DBC substrates in power electronics include properties such as [13]:

- High thermal conductivity

- High insulating voltage (in the area of approximately 5-10 kV/mm)

- High heat dissipation

- Similarity of thermal expansion coefficient enables chip-on-board applications

#### 5.2 Press pack modules

Press-pack IGBT has been developed in recent years as a superior high power IGBT device to conventional IGBT module in reliability and performance. This type of IGBT is replacing GTOs or thyristors in such applications as traction, power transmission and industrial motor drive because of its excellent advantages such as high performance, high reliability, compactness due to the both-sided cooling and rupture free feature [14]. The press packs comes in round or square packages. The square package has a beneficial geometry due to the geometry of the chips inside which also has a square form. The module is hermetically sealed

and compressed to ensure electrical contact which principle is illustrated in Fig 5.2. Because the module is subjected to great forces, the mechanical ruggedness is design to be superior to the traditional modules [15].

Fig 5.2 Press pack principle

# 6 Suitable semiconductor modules for the final solution

A lot of high power semiconductor modules are developed by various manufacturers. A few selected is presented in this chapter that may be applicable in a high power application under high hydrostatic pressure.

Manufacturers continuously improve the characteristics of the IGBTs as the demand for higher power and reliability grows. Some state of the art IGBT modules include a new soft punch through device, ABB's HiPak Module with the next generation soft punch through IGBTs, and a new press pack IGBT module manufactured by Toshiba. Since a suggested solution is to have the modules at high hydrostatic pressure on the sea bed, the housing of the modules must either be strong enough to withstand the pressure, or be penetrated so that the insulating oil can completely fill it without any air pockets.

### 6.1 ABB's HiPak modules with next generation SPT<sup>+</sup> IGBTs

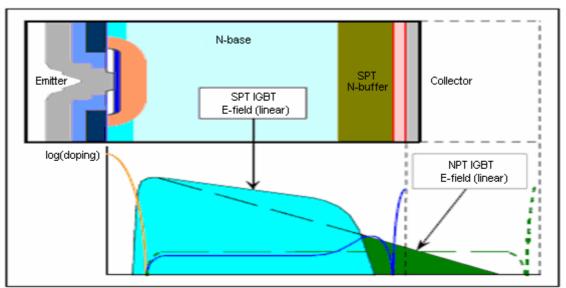

ABB Switzerland Ltd, semiconductor manufacturer has developed a high voltage soft punch through IGBT. The SPT concept is based on using a low doped N-buffer profile at the anode side of the IGBT. At a normal DC-link operating voltage, the space charge region does not reach the boundary of this buffer region with the high resistance N-base layer. Therefore, despite the much thinner base region, the dynamical electrical properties of the SPT-IGBT are almost comparable with those of a thicker non punch through IGBT. The soft punch through feature is especially applied with respect to the softness of the current and voltage curves during switching transients. Hence, the term "Soft" in SPT originates from this fact. In addition, the buffer acts as a field stopper for voltages higher than the DC-link voltage up to the nominal blocking voltage as shown in Fig 6.1 [16]. As mentioned above, the major benefits of the SPT-IGBT are resulting from a substantially (30%) thinner wafer thickness compared to a NPT-IGBT of the same nominal blocking voltage. As a consequence, both onstate voltage and turn-off losses are reduced simultaneously. However, the main advantages of the NPT structure are also maintained with regard to extreme ruggedness, low temperature dependence during IGBT turnoff transient and finally, a positive temperature coefficient for V<sub>ce(sat)</sub> during on-state [16].

Fig 6.1 SPT IGB doping profile and electric field distribution with respect to an NPT IGBT structure

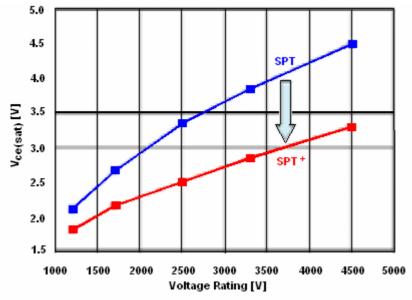

The new HiPak modules with the next generation  $SPT^+$  take advantage of the existing SPT technology, shown in Fig 6.1, with modifications to improve the performance and voltage levels. One of the new achievements is the planar technology which exploits an enhanced carrier profile through planar cell optimisation. This leads to a significant increase in plasma concentration at the emitter and thus a lower on state voltage is obtained for the same turn-off loss. In addition an optimised base region combined with soft punch through buffer allows the collector current to smoothly decrease during the turn off transient thanks to the progressive and controlled manner in which the depletion layer is established. To illustrate the improvement in performance, a comparison of the SPT<sup>+</sup> with the SPT is made in Fig 6.2 [17] for the voltage range 1200V to 4500V. The values for  $V_{ce(sat)}$  are obtained at the same current densities and for similar turn-off losses, for each voltage class [17].

Fig 6.2 SPT and SPT<sup>+</sup> IGBT on-state voltage vs. rated blocking voltage at 125°C

On-state losses in the SPT<sup>+</sup> are significantly reduced as can be seen from the above figure. The reduction in  $V_{ce(sat)}$  due to SPT<sup>+</sup> cell enhancement ranges from 15% for a 1200V IGBT up to 30% for a 4500V device, allowing corresponding increases in current ratings. ABB has also

reported testing of IGBTs with voltage ratings up to 6.5kV with approximately 30% in  $V_{ce(sat)}$  reduction. Switching waveforms and other electrical characteristics for the HiPak modules from ABB can be found in [17] where the module with the new SPT<sup>+</sup> technology is presented as a device which will give system designers greater freedom in achieving higher power and better efficiency for their applications.

#### 6.1.1 Enhanced Planar IGBT

As mention briefly in the previous chapter, one of the new achievements is the planar technology with planar cell enhancement. The Enhanced-Planar technology is integrated with the soft punch through buffer concept for ensuring controllable and soft switching behaviour. The improvements in the on state losses shown in Fig 6.2 were achieved through enhancement of the carrier profile near the emitter while maintaining the same drift region thickness as for the standard SPT design.

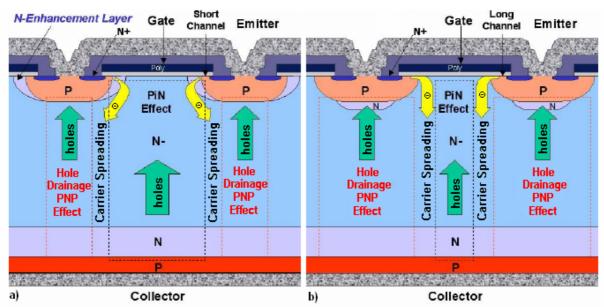

In order to design the enhancement N-layer for an optimum trade-off between low losses, high safe operating area and maximum blocking capability, the positioning and doping profile of the N-layer was investigated experimentally by ABB Switzerland Ltd, Semiconductors. Results were also confirmed through simulations carried out on the different structures. In addition to an n-layer fully surrounding the cell's P-well, prototype samples were fabricated where an N-layer was only placed laterally near the edge of the P-well, and in a third version it was centralised underneath the P-well as shown in Fig 6.3 [18]. The peak concentration for the N-layer was the same for all three versions. Major improvements in on-state losses were observed for the lateral version, similar to those achieved for the fully encompassed P-well structure. This was attributed to three main interacting effects;

- 1. Improved spreading of electrons from the MOS channel

- 2. Shorter channel length

- 3. Improved PiN effect between the cells due to the enhanced hole accumulation at the periphery of the cell

Due to the fact that the lateral n-layer does not extend beyond the maximum P-well depth, a favourable trade-off with blocking capability was achieved, thus allowing a higher doping for the enhancement N-layer to obtain even lower losses. These effects were all absent in the second centralised version, which only provided a hole barrier under the cell with a negligible contribution to plasma enhancement. However, the centralised N -layer design demonstrated a higher RBSOA capability compared to the other structures due to the positioning of the peak field directly below the contact. This was achieved at the expense of reduced blocking voltage capability. The final EP-IGBT design utilised an optimum doping profile for both the lateral and centralized regions for achieving the lowest on-state losses, maximum blocking capability and highest SOA limits. Cosmic ray measurements also showed that the EP-IGBT dose not result in a higher failure rate at the required DC voltage-levels when compared to the equivalent standard IGBT [18].

Fig 6.3 a) Conduction with lateral n-layer and b) centralised n-layer

### 6.1.2 Packaging

Five different HiPak modules are shown in Fig 6.4, and as it can be seen, the packaging follows conventional standards. From various datasheets for different HiPak modules it can not be determined if the housing is hermetically sealed or not. However, assuming that it is sealed, the housing will probably not withstand any significant hydrostatic pressure in a sub sea application where the module is submerged in oil. A way to solve this problem is to penetrate the housing so that the insulating oil can completely fill it. Any soft encapsulation of the chips then has to be removed, because it may dissolve when in contact with the oil. This is easy to test in the lab, but any new module has to undergo several tests and verifications before hitting the marked, and if modified the warranties will no longer apply.

Fig 6.4 HiPak module packaging

The HiPak module can be suitable for high pressure applications if it can be delivered with minor modifications, or guarantees that it is hermetically sealed and will withstand high hydrostatic pressure.

#### 6.1.3 ABB's Press packs

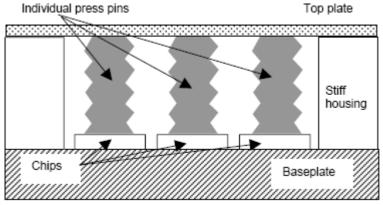

Another way of making the module pressure resistant is to integrate known packaging technology with the new  $SPT^+$  technology. Press pack modules are developed which shows excellent mechanical strength. ABB developed new pressure-contact technology which decouples the external clamping force from the direct pressure on the chip. This was achieved by the use of a flexible emitter contact (individual press-pin) in combination with a stiff housing as shown schematically in Fig 6.5 [19].

To further reduce the stress coming from mechanical unevenness, each chip is contacted by an individual flexible pin. During mounting, a certain amount of the applied pressure is transferred onto the chip by compression of the individual press-pin contacts whereas the excess pressure is taken over by the robust housing. At the same time, the robust housing limits the compression of the flexible contacts. With this design, the pressure on the chip can be adjusted by the stress-strain characteristic of the individual pressure contact. The significant advantage of this concept is that it is much less sensitive to pressure inhomogeneities compared to traditional hockey-puck designs with stiff copper pole-pieces and that it allows very high mounting force as well as much wider mechanical tolerances. The result is a gain in mechanical reliability at reduced costs [19].

Fig 6.5 Schematic view of the pressure scheme

An interesting test of the press pack is reported in [19]. The test is a so called explosion test, where the module is subjected to several hundred kA for several hundred microseconds. The test determines if the housing explodes when high vapour pressure builds up inside. Peak power of the test was 110MW and the housing was still intact after the test with no ejected parts. This implies that the housing is extremely robust, and that it very well may be suited for high hydrostatic pressure applications like a sub sea compressor unit with no pressure chamber holding 1 atmosphere.

Existing press pack units can also be used without the  $SPT^+$  technology. Data from the module used in the explosion test can be found in Table 6.1 and it shows high power capability. It should also be noted that the press pack has a square form and not a round hockey puck shape.

| Table 6.1 Press pack module data |                           |  |

|----------------------------------|---------------------------|--|

| Mechanical properties            |                           |  |

| Dimensions of press pack         | $260x220x26 \text{ mm}^3$ |  |

| Mounting force                   | 75 <b>±10 kN</b>          |  |

| Surface creepage distance        | 52 mm                     |  |

| Weight                           | 3.5 kg                    |  |

| Electrical properties            |                           |  |

| Max collector-emitter voltage    | 5200 V                    |  |

| Nominal collector current        | 2000 V                    |  |

| Switching safe operating SOA     | 3000 V, 4000 A            |  |

## 6.2 Planar gate press pack Injection Enhanced Gate Transistor

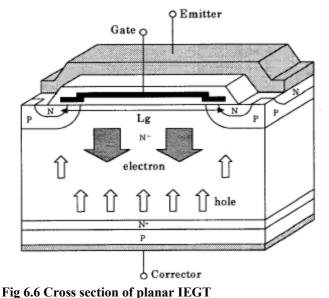

Toshiba developed a planar press pack injection enhanced gate transistor for high power applications. The vertical cross section of an IEGT cell is presented in Fig 6.6 [20]. It is similar to the standard IGBT cell but it has wider cell width, indicated with  $L_g$ , in the figure. In the presented cell, there has been added a highly doped N<sup>+</sup> buffer layer to form a punch through structure.

factors for a high voltage planar device design [20].

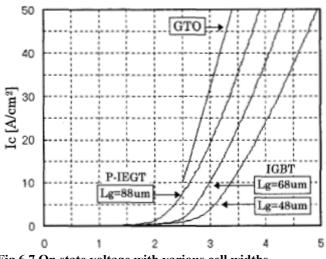

The wide  $L_g$  structure induces the injection enhancement effect of electrons on the emitter side of the N<sup>-</sup> high resistance layer. The high density of carrier is accumulated in the N<sup>-</sup> high resistance layer during on-state. By this effect, it makes possible that the IEGT achieves low on-state voltage drop close GTO thyristors with easy gate drivability and wide SOA of MOS transistors. Fig 6.7 shows the on-state voltage as function of  $L_g$ . In Fig 6.7,  $L_g = 88$ um is the gate-width design of P-IEGT and  $L_g = 68.48$ um is design of conventional IGBT. The figure shows that the gate width increases and the on-stage voltage decreases. This means that the conductance of the electron accumulation layer under the gate oxide is one of the major

Fig 6.7 On state voltage with various cell widths

#### 6.2.1 Packaging

The Toshiba module is press packed with a hockey puck shape. A picture of one module is shown in Fig 6.8.

Fig 6.8 Toshiba IEGT press pack module

The module seems compact and solid by visual inspection and it would be assumed that the explosion test previously described also has been done on this module. The packaging class SF6 indicates that the module is evacuated and then filled with a gas with slightly overpressure. A small sealed penetration pin on the side, not shown in the picture, has been used for evacuation and filling purposes. Perpendicular pressure on the planar surfaces would not be a problem since it is how the module is design to be installed, but hydrostatic pressure may compress the sides and either part the metal surfaces from the plastic sides or destroy the chip alignment on the inside causing destruction of device.

For hydrostatic pressure applications, the housing could be delivered filled with a fluid. This will probably be the best solutions causing the least modifications on the device.

#### 6.3 Semikron's SEMIX IGBT module

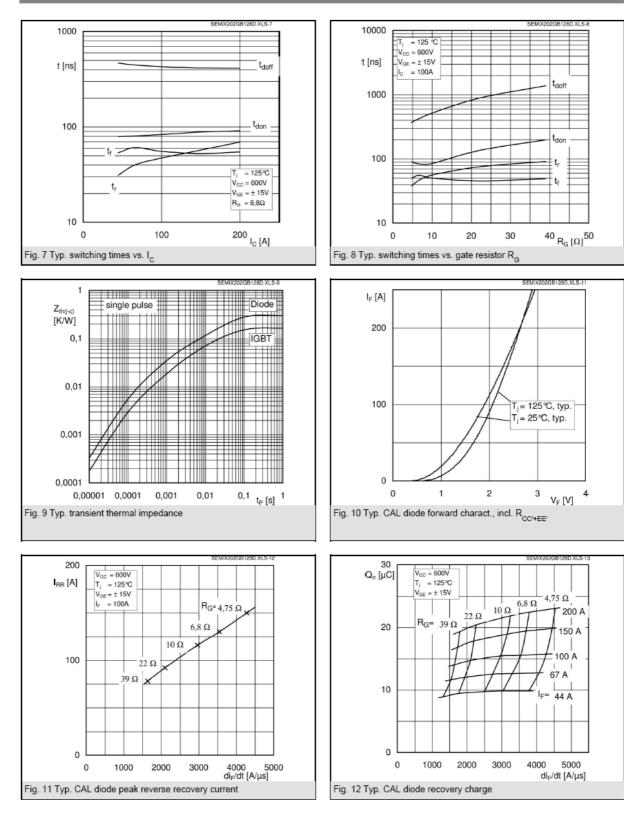

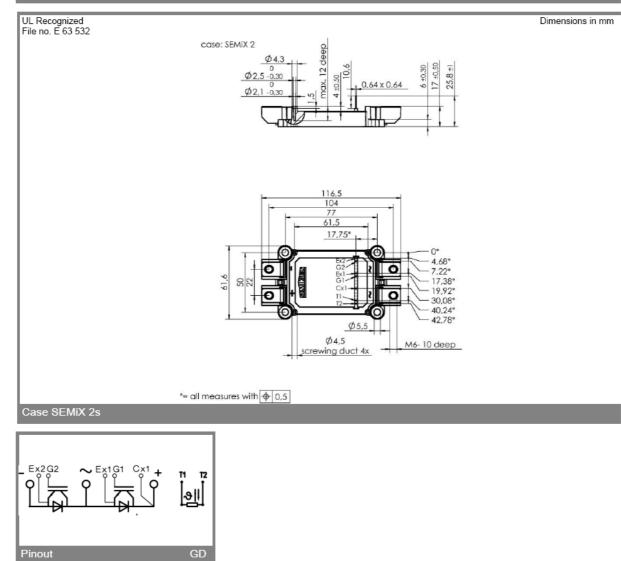

The module from Semikron, SEMIX 202GB128D, will not be suitable for the sub sea compression application. However, to test IGBT switching operation when the chips are submerged in oil, this unit was available with the necessary modifications to execute the experiment that follows.

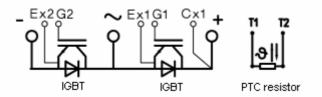

The SEMIX module is a DBC solution previously described with paralleled chips connected with bond wires inside the housing to improve current carrying capabilities. The casing is modified to allow fluid to fill the housing. The module was delivered without the silicon gel normally covering the chips. This was custom ordered for the testing purpose of this experiment. From the data sheet in appendix A, the equivalent circuit in Fig 6.9 shows that the module is one converter bridge leg.

Fig 6.9 Equivalent circuit of SEMIX module

The ohmic value of the PTC resistor indicated in Fig 6.9 will change as the temperature changes according to the formula,

$$R_{2} = R_{1} e^{\left[B\left(\frac{1}{T_{2}} - \frac{1}{T_{1}}\right)\right]}$$

(4)

| $R_1$ | = Initial resistor value | [Ohm] |

|-------|--------------------------|-------|

| $R_2$ | = Current resistor value | [Ohm] |

| В     | = Constant               | [-]   |

| $T_1$ | = Initial temperature    | [K]   |

| $T_2$ | = Current temperature    | [K]   |

|       |                          |       |

From the data sheet in appendix A, the constant, B, is given to be 3420. However, after temperature tests in the laboratory, a new value was calculated to be a little bit lower, but it was close enough to conclude that the tests done by the manufacturer probably is correct.

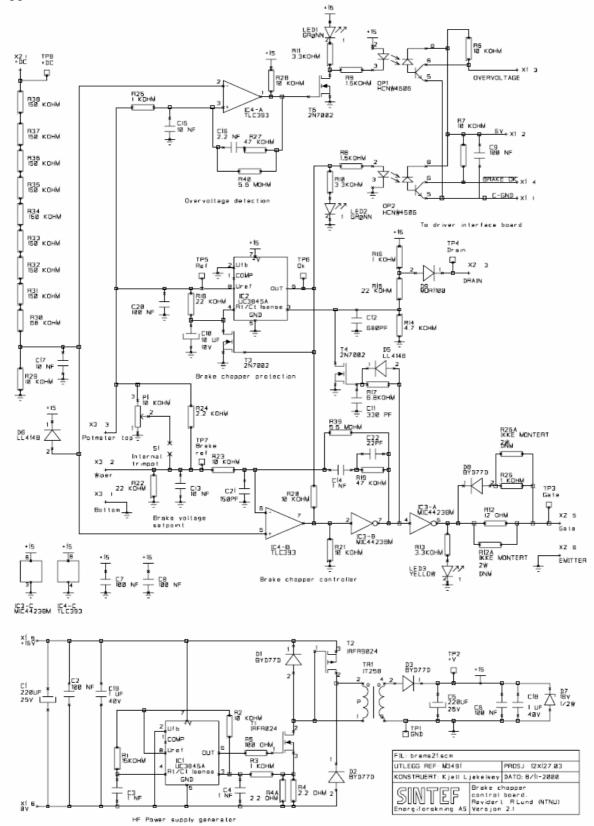

# 7 Experimental setup, components

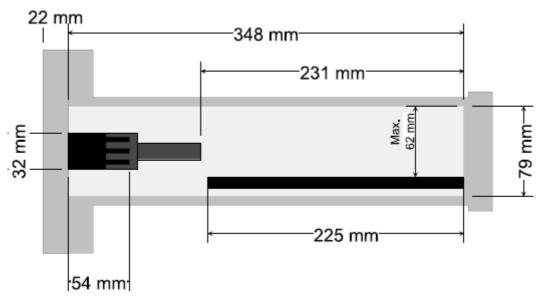

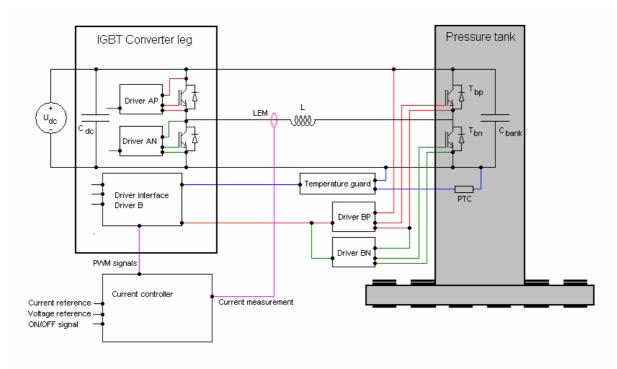

The experiment is set up to test operating capabilities of an IGBT module under high hydrostatic pressure, and consists of an electrical system and a pressurising system. As previously mentioned and explained no pressure was applied. However, the system will still be described as if pressure was applied as basis for further work.

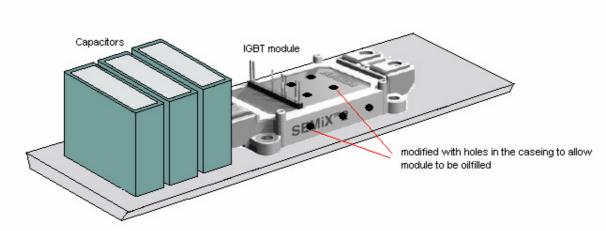

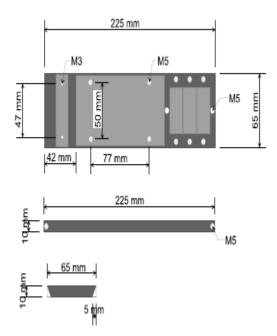

In Fig 7.1, a sketch of the test object is shown. It consists of an IGBT module mounted on a heat spreader and three capacitors forming a part of the total capacitor bank. The remaining part of the capacitor bank is located on the outside of the tank. Capacitors used in this experiment are manufactured by Evox Rifa with standard metallised film technology. Metallised film technology is further described in [1], and more information about the IGBT module can be found in the data sheet in appendix A.

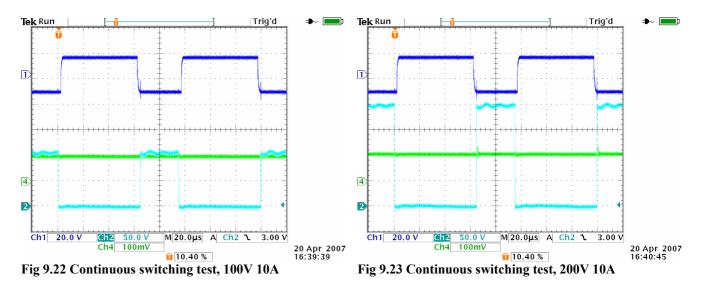

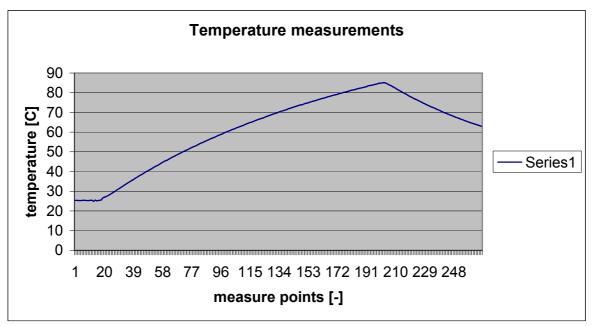

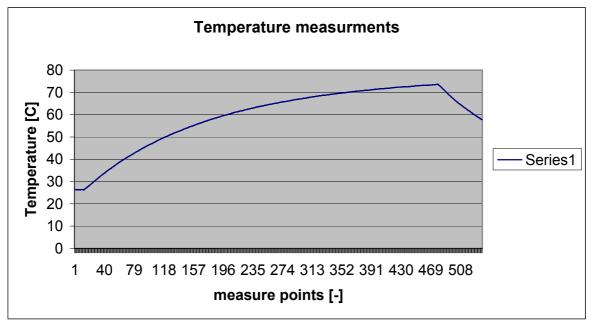

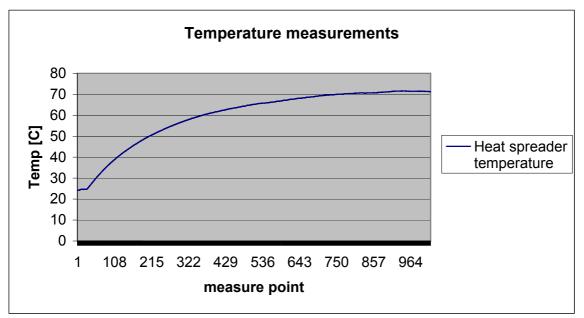

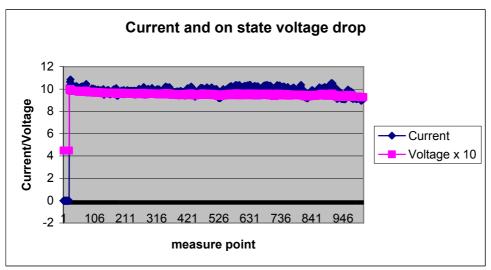

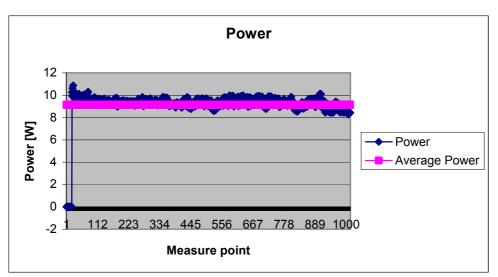

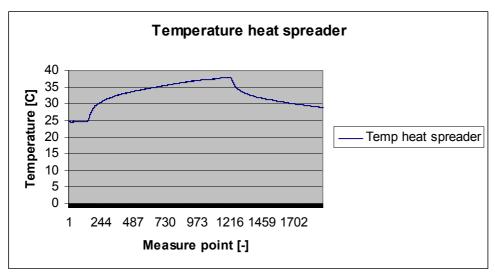

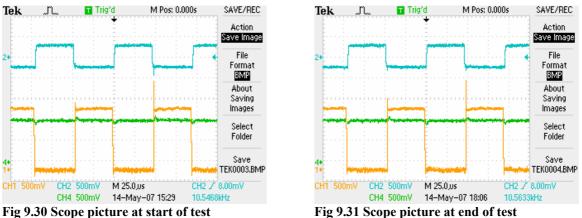

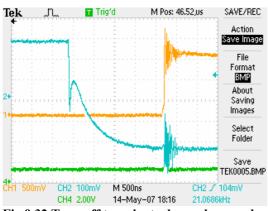

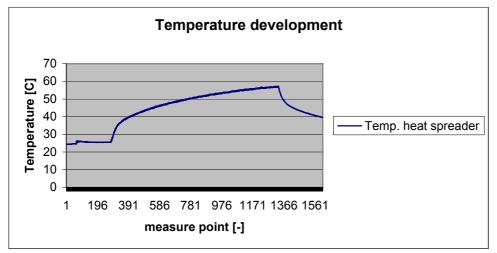

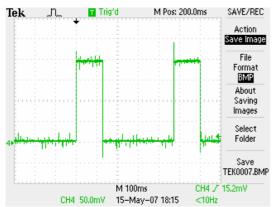

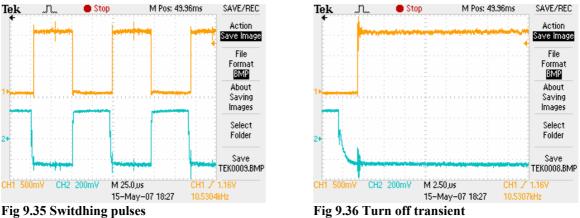

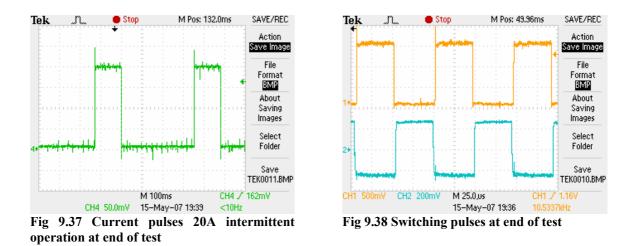

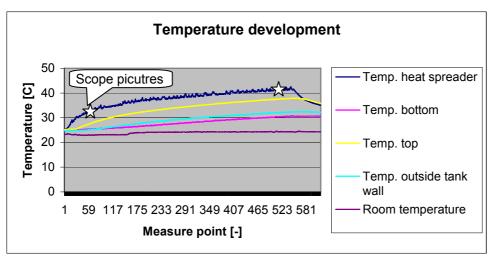

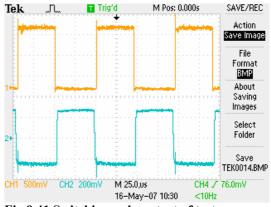

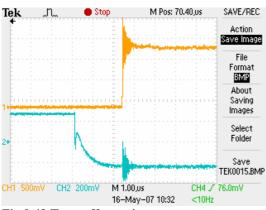

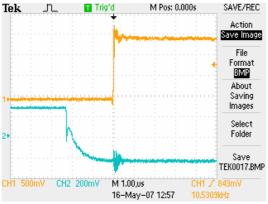

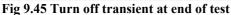

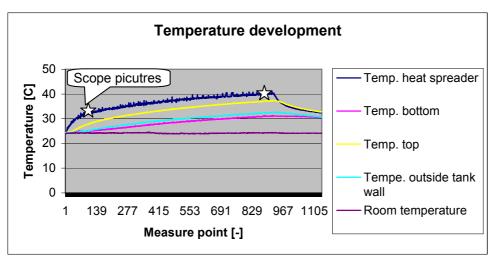

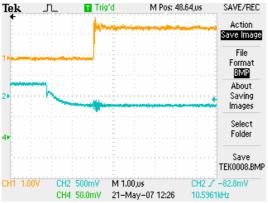

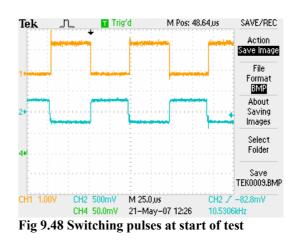

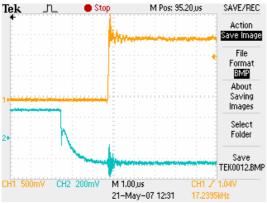

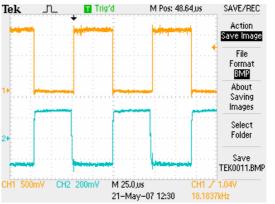

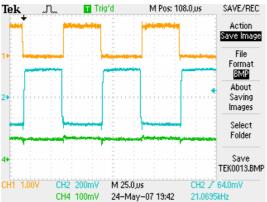

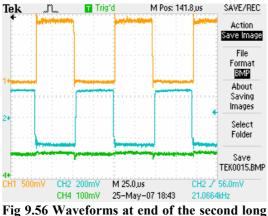

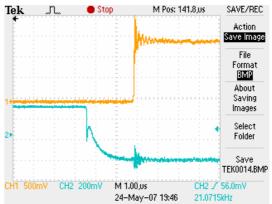

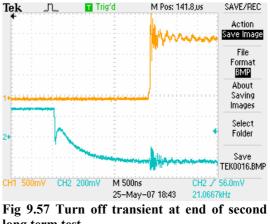

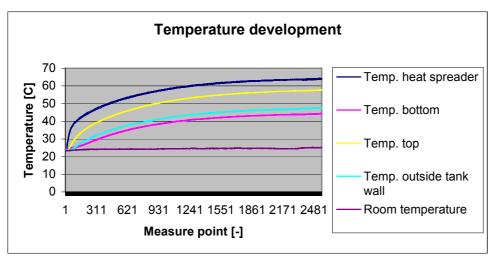

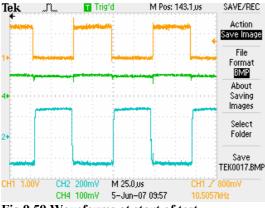

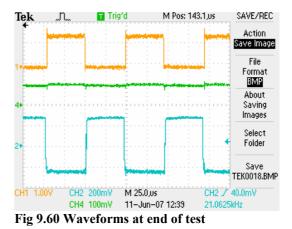

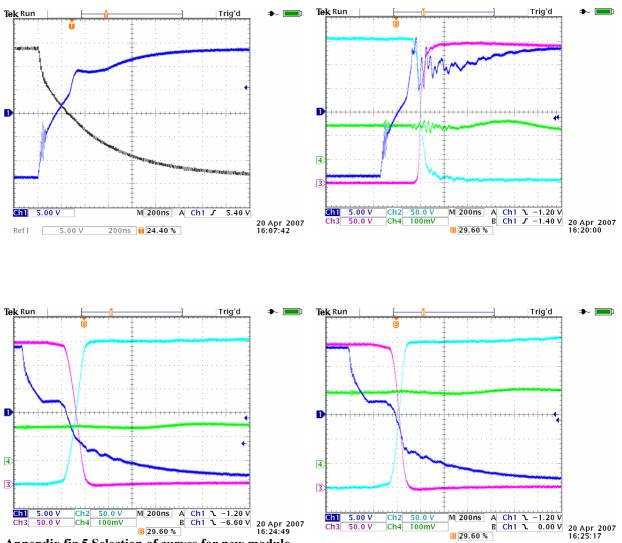

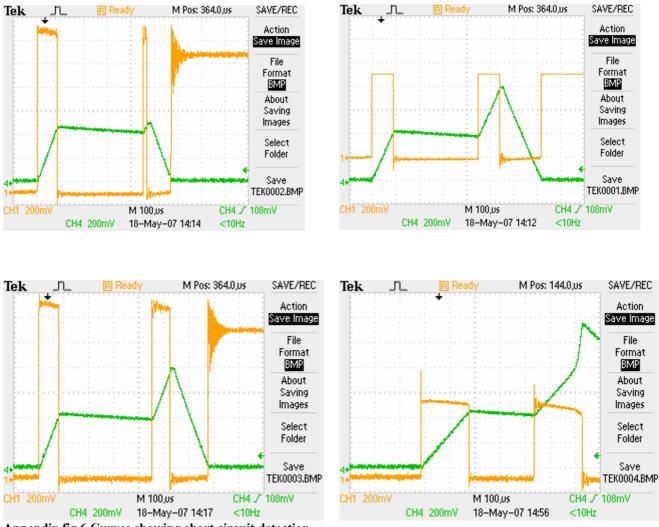

Fig 7.1 Test object