# Development of a Grid Connected PV System for Laboratory Use

Silje Odland Simonsen

Master of Science in Energy and Environment Submission date: July 2009 Supervisor: Lars Einar Norum, ELKRAFT Co-supervisor: Fritz Schimpf, ELKRAFT

Norwegian University of Science and Technology Department of Electric Power Engineering

# **Problem Description**

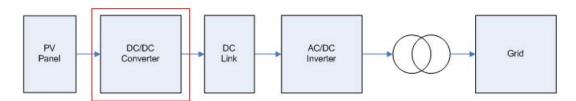

A laboratory setup of a grid connected PV inverter system is currently under development at NTNU. The system will consist of a PV panel input, a converter stage consisting of a DC-DC converter, DC link and DC-AC converter, and a transformer stage. The finished system is intended for implementation at the University of Dar Es Salaam in Tanzania for teaching purposes in Power Electronics and Digital Control in PV Systems.

The focus of this master thesis is development of a control design for a DC-DC converter implemented in the PV system. This includes consideration of the input from the PV panels and the DC-DC converter stage. A DC-DC converter design is already available. The focus will be on hardware testing and evaluation, software development and interconnection of the hardware and software modules.

Assignment given: 02. February 2009 Supervisor: Lars Einar Norum, ELKRAFT

## Acknowledgements

This master thesis is a part of the Master program in Technology at the Norwegian University of Science and Technology in Trondheim, Norway. It has been written upon request from Professor Lars E. Norum at the Department of Electrical Power Engineering and is a cooperation between NTNU, the University of Dar es Salaam in Tanzania, and Bose Research in India.

In this report a future PV system meant for laboratory use in the previous mentioned African University has been considered. The system will include PV modules for power input, a DC-DC converter for MPPT (Maximum Power Point Tracking) and a DC-AC inverter connected to the grid through a transformer. Previous to this master thesis Supratim Basu at Bose Research designed the circuit diagram for the DC-DC converter, and this prototype was built and tested during the fall 2008. The scope for this thesis has been on the control design of the DC-DC converter stage.

The theoretical background is written based on the assumption that the contents of this report will be read by people with some basic knowledge within the area. Some chapters are also a bit more comprehensive, with regards to students that will continue to work on this laboratory assignment in the future. Some information is based on knowledge gained through courses at the University as well as through working experience. Figures without reference I have mainly created myself or the reference is mentioned another place in the chapter.

I would like to give special thanks to my head supervisor Lars Norum for help and support and giving a push in the right direction at times when my focus has been unclear. The same applies for my co-supervisor Fritz Schimpf, to which I am very grateful for all the extra time spent on helping me and giving me useful advices along the way. Also thanks to Supratim Basu for designing the converter circuit, Vladimir Klubicka and Bård Almaas in the Servicelab and Ph.D. candidate Chee Lim for help and good advices. The work with my master thesis has been a highly instructive process. Especially the practical work has increased my knowledge about power electronics control and software development intended for this. Despite times of frustration I really recommend laboratory work as a way of working and learning.

Last, but not least, thanks to Ragnar Ulsund for providing social input throughout the spring of 2009 by arranging cake and coffee break once a week.

Silje Odland Simonsen Trondheim, 6 July 2009

# Contents

| 1        | Intr | duction                                       | <b>2</b> |

|----------|------|-----------------------------------------------|----------|

| <b>2</b> | Bac  | ground                                        | <b>4</b> |

|          | 2.1  | What is a PV system?                          | 4        |

|          |      | 2.1.1 Stand-alone system                      | 4        |

|          |      | 2.1.2 Grid connected system                   | 5        |

|          | 2.2  | The working principle of photovoltaics        | 6        |

|          |      | 2.2.1 The Photovoltaic cell                   | 6        |

|          |      |                                               | 10       |

|          |      |                                               | 11       |

|          | 2.3  |                                               | 12       |

|          |      | ·                                             | 12       |

|          |      |                                               | 14       |

|          |      | 5 5                                           | 21       |

|          |      |                                               | 22       |

|          |      |                                               | 23       |

|          |      | -                                             | 23       |

|          | 2.4  |                                               | 24       |

|          | 2.5  |                                               | 26       |

|          |      |                                               |          |

| 3        |      | ů –                                           | 29       |

|          | 3.1  | 0                                             | 29       |

|          |      |                                               | 30       |

|          |      |                                               | 32       |

|          |      | 3 ( )                                         | 34       |

|          |      | 1 0 0                                         | 34       |

|          |      | <i>i</i> 0                                    | 35       |

|          | 3.2  | 8                                             | 36       |

|          |      |                                               | 36       |

|          |      | 0                                             | 37       |

|          |      | 0 0                                           | 39       |

|          |      | 3.2.4 Digital control - Discrete time systems | 39       |

|          |      |                                               | 41       |

|          |      | 3.2.6 Other types of controllers              | 42       |

| 4        | Svst | em description                                | 43       |

|          | 4.1  | -                                             | 44       |

|          | 4.2  | 1                                             | 45       |

|          | _    |                                               | 45       |

|          |      |                                               | 46       |

|          |      |                                               | 47       |

|          |      | -                                             | 48       |

|          |      |                                               | -        |

### CONTENTS

|   |                    | 4.2.5          | Protection                                                                                                                                |

|---|--------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|   |                    | 4.2.6          | Control circuits                                                                                                                          |

|   |                    | 4.2.7          | Alterations of the circuit                                                                                                                |

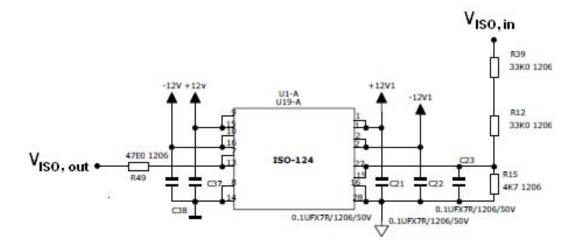

|   | 4.3                | Hardw          | vare interface $$                                                                                                                         |

|   |                    | 4.3.1          | Selection of suitable hardware interface circuits                                                                                         |

|   |                    | 4.3.2          | Current measurements                                                                                                                      |

|   |                    | 4.3.3          | Voltage measurements                                                                                                                      |

|   |                    | 4.3.4          | Upscaling the voltage of the PWM signal                                                                                                   |

|   |                    | 4.3.5          | Filtering of the signals                                                                                                                  |

|   |                    | 4.3.6          | Planning the interface circuits through the use of NI ELVIS II 59                                                                         |

|   |                    | 4.3.7          | HI - experimental results                                                                                                                 |

|   | 4.4                | TMS3           | 20F2808 DSP Controller                                                                                                                    |

| 5 | Dot                | alonm          | ent of the program code in CCS 63                                                                                                         |

| 0 | 5.1                | -              | al about DSP features and background                                                                                                      |

|   | 0.1                | 5.1.1          | The structure in the DSP                                                                                                                  |

|   |                    | 5.1.1<br>5.1.2 | Fixed point vs. floating point representation                                                                                             |

|   |                    | 5.1.2<br>5.1.3 | Representation of numbers                                                                                                                 |

|   |                    | 5.1.3<br>5.1.4 | Handling of variables                                                                                                                     |

|   |                    | 5.1.4<br>5.1.5 | Digital-to-Analog Conversion through PWM generation                                                                                       |

|   | 5.2                |                | amming tools                                                                                                                              |

|   | 0.2                | 5.2.1          | Code Composer Studio                                                                                                                      |

|   |                    | 5.2.1<br>5.2.2 | Blackhawk USB2000 Controller                                                                                                              |

|   | 5.3                | -              | tions and routines in the programming                                                                                                     |

|   | 0.0                | 5.3.1          | Basic operations and routines                                                                                                             |

|   |                    | 5.3.2          | High level routines   69                                                                                                                  |

|   | 5.4                |                | $ ppment of each block \dots \dots$ |

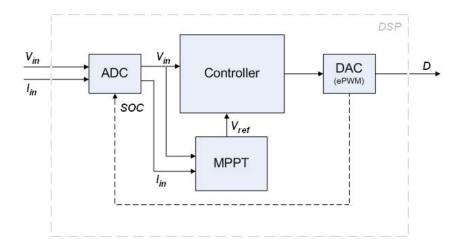

|   | 0.1                | 5.4.1          | Graphical overview over the DSP operation                                                                                                 |

|   |                    | 5.4.2          | ADC module                                                                                                                                |

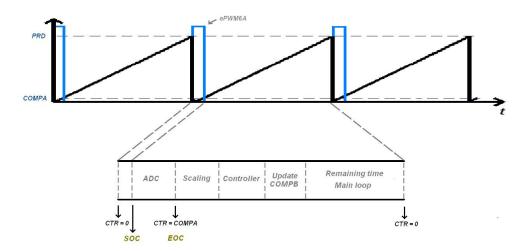

|   |                    | 5.4.3          | ePWM module setup                                                                                                                         |

|   |                    | 5.4.4          | Start-of-conversion (SOC) sequence trigger                                                                                                |

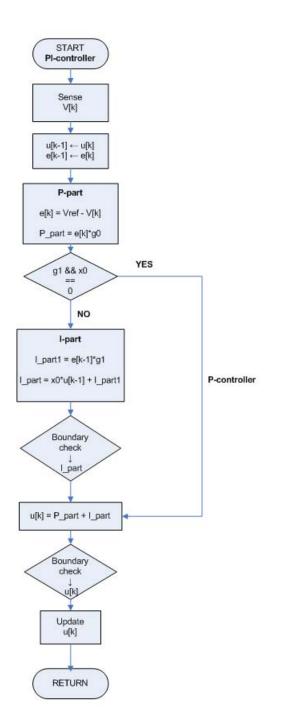

|   |                    | 5.4.5          | Controller                                                                                                                                |

|   |                    | 5.4.6          | MPPT                                                                                                                                      |

| C | <b>D</b>           | •              |                                                                                                                                           |

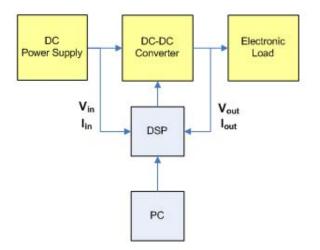

| 6 | <b>е</b> хр<br>6.1 |                | ntal setup and results     76       ment     76                                                                                           |

|   | 6.2                | Equip          |                                                                                                                                           |

|   | 6.2                |                |                                                                                                                                           |

|   |                    |                | 1 1                                                                                                                                       |

|   | 6.4                |                | imental results                                                                                                                           |

|   |                    | 6.4.1          | ADC                                                                                                                                       |

|   |                    | 6.4.2          | Ziegler-Nichols                                                                                                                           |

|   |                    | 6.4.3          | P-controller                                                                                                                              |

|   |                    | 6.4.4          | PI-controller                                                                                                                             |

|   |                    | 6.4.5          | P&O MPPT                                                                                                                                  |

## CONTENTS

| <b>7</b>     | Dise                                      | cussion                                                                                                     | <b>85</b>       |  |

|--------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|--|

|              | 7.1                                       | Boost converter as DC-DC converter topology                                                                 | $\frac{85}{85}$ |  |

|              | 7.2 Development of the hardware interface |                                                                                                             |                 |  |

|              | 7.3                                       | Development of the software                                                                                 | 87              |  |

|              |                                           | 7.3.1 Calibration $\ldots$ | 87              |  |

|              |                                           | 7.3.2 The voltage mode controller                                                                           | 88              |  |

|              |                                           | 7.3.3 MPPT                                                                                                  | 89              |  |

|              | 7.4                                       | General experience with the DSP Control Equipment                                                           | 90              |  |

|              | 7.5                                       | Evaluation of the development process                                                                       | 90              |  |

| 8            | Con                                       | clusion                                                                                                     | 92              |  |

| 9            | Rec                                       | ommended changes for next version of the PCB                                                                | 94              |  |

| 10           | Sco                                       | pe for further work                                                                                         | 95              |  |

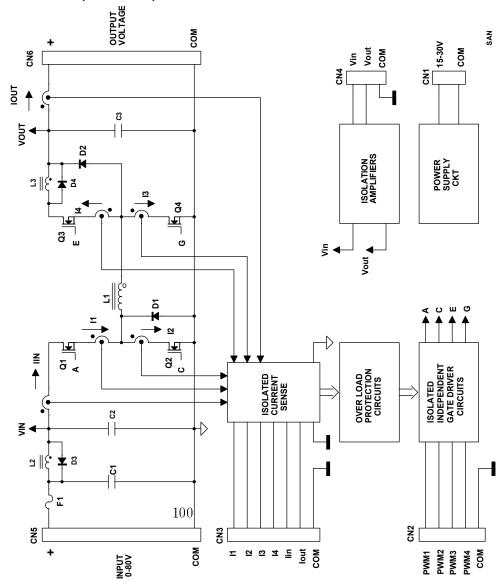

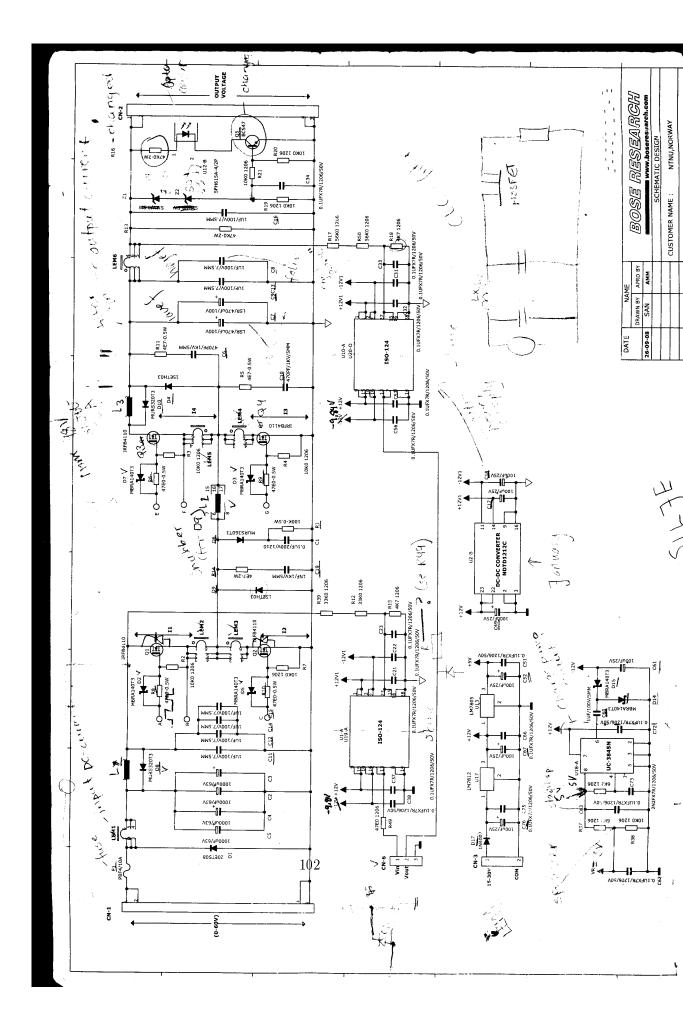

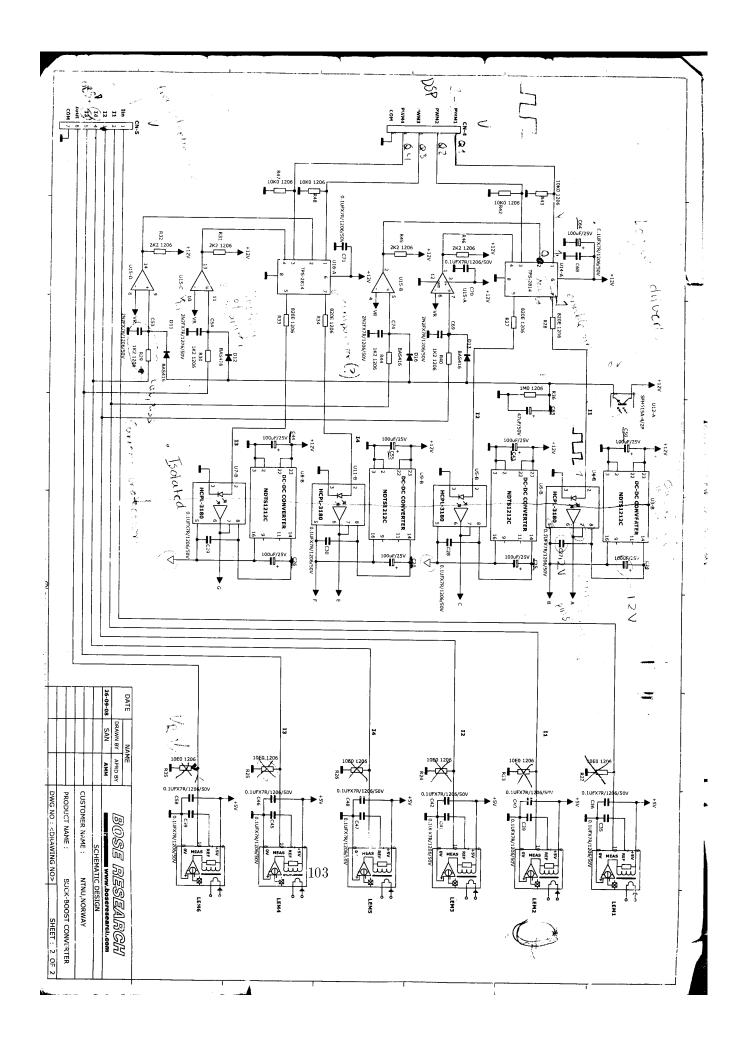

| A            | Ciro                                      | cuit diagram of the DC-DC converter design scheme                                                           | 100             |  |

| в            | $\mathbf{Des}$                            | ign of the PCB                                                                                              | 104             |  |

| С            | Con                                       | nponent list                                                                                                | 106             |  |

| D            | Alte                                      | ernated components                                                                                          | 116             |  |

| $\mathbf{E}$ | Pro                                       | gram code the control system                                                                                | 117             |  |

| $\mathbf{F}$ | DSI                                       | P relevant files                                                                                            | 126             |  |

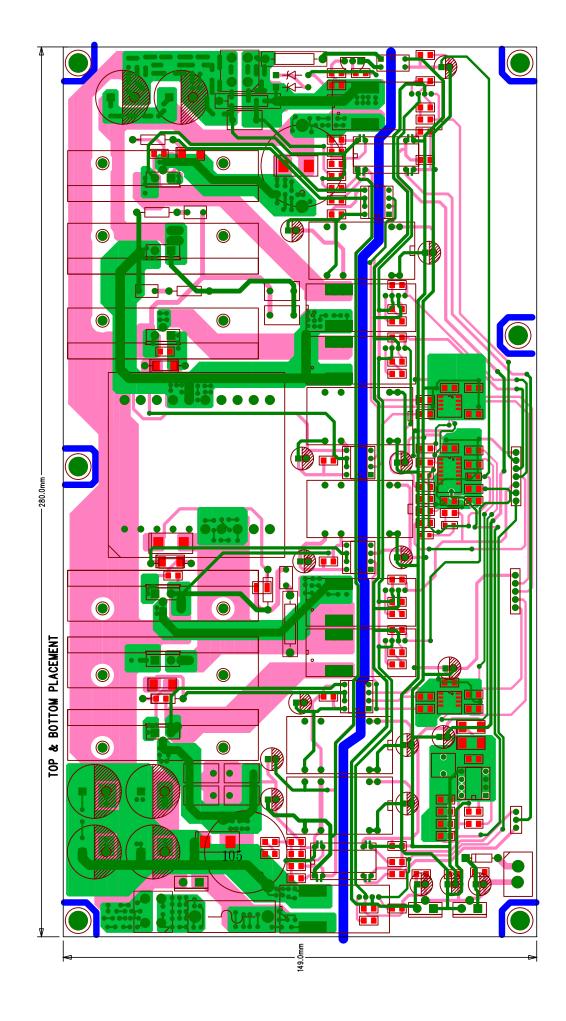

|              | F.1                                       | Circuit diagrams overview for TMS320F2808 Control Card                                                      | 126             |  |

|              | F.2                                       | Relevant documents for the TMS320F2808 Controller                                                           | 128             |  |

|              | F.3                                       | Example files for the DSP Controller                                                                        | 128             |  |

| $\mathbf{G}$ | Inst                                      | rument list                                                                                                 | 129             |  |

| н            | $\mathbf{PV}$                             | Simulator characteristics                                                                                   | 130             |  |

|              | H.1                                       | Changes in irradiance levels                                                                                | 130             |  |

|              | H.2                                       | Changes in temperature levels                                                                               | 131             |  |

| Ι            |                                           | v to develop a compensation network for a boost converter in a ${f PV}$                                     |                 |  |

|              | syst                                      | em                                                                                                          | 133             |  |

v

# List of Tables

| 1  | Standard test conditions (STC)                       | 9   |

|----|------------------------------------------------------|-----|

| 2  | Efficiency of different MPPT algorithms              | 35  |

| 3  | Ziegler-Nichols method                               | 39  |

| 4  | Numerical integration methods                        | 41  |

| 5  | PV Panel NT-175 specifications                       | 44  |

| 6  | Switch control for buck operation                    | 48  |

| 7  | Switch control for boost operation                   | 48  |

| 8  | Resistor values in the difference amplifier circuits | 57  |

| 9  | ADC pin allocation                                   | 72  |

| 10 | Rated values of PV simulator                         | 77  |

| 11 | PV Simulator variables                               | 78  |

| 12 | Parameters for P- and PI-controller by use of Z-N    | 79  |

| 13 | Relevant files from TI                               | 128 |

| 14 | Laboratory Equipment                                 | 129 |

| 15 | MPP for different irradiance levels                  | 131 |

| 16 | MPP for different temperature levels                 | 132 |

# List of Figures

| 1  | Simplified sketch of the circuit                                                 | 3  |

|----|----------------------------------------------------------------------------------|----|

| 2  | PV system with DC and AC load or grid connection                                 | 5  |

| 3  | Simplified equivalent circuit of a PV cell                                       | 7  |

| 4  | Ideal PV cell with maximum power point                                           | 8  |

| 5  | I-V characteristics for different levels of irradiation and temperature $\ldots$ | 9  |

| 6  | P-V characteristic of a PV cell                                                  | 10 |

| 7  | A PV module with bypass and blocking diodes                                      | 11 |

| 8  | Relation between the PV cell, a module and an array                              | 11 |

| 9  | Block diagram of a power electronic system                                       | 12 |

| 10 | Block diagram of a power processor                                               | 13 |

| 11 | The principle of switching                                                       | 14 |

| 12 | The principle of PWM control                                                     | 15 |

| 13 | Buck converter                                                                   | 16 |

| 14 | Buck converter circuit for a) $t_{on}$ and b) $t_{off}$ in CCM                   | 16 |

| 15 | Inductor voltage and current of the buck converter                               | 17 |

| 16 | Output voltage ripple in a buck converter                                        | 18 |

| 17 | Boost converter                                                                  | 18 |

| 18 | Boost converter circuit for a) $t_{on}$ and b) $t_{off}$ in CCM                  | 19 |

| 19 | Inductor voltage and current of the boost converter                              | 19 |

| 20 | The effect of parasitic elements in a boost converter                            | 20 |

| 21 | Output voltage ripple in a boost converter                                       | 21 |

| 22 | Operational amplifier                                                            | 24 |

| 23 | Equivalent circuit of the op amp                                             | 25  |

|----|------------------------------------------------------------------------------|-----|

| 24 | Difference amplifier circuit                                                 | 25  |

| 25 | First order low-pass RC filter circuit                                       | 26  |

| 26 | Second-order circuit in Butterworth cascade                                  | 27  |

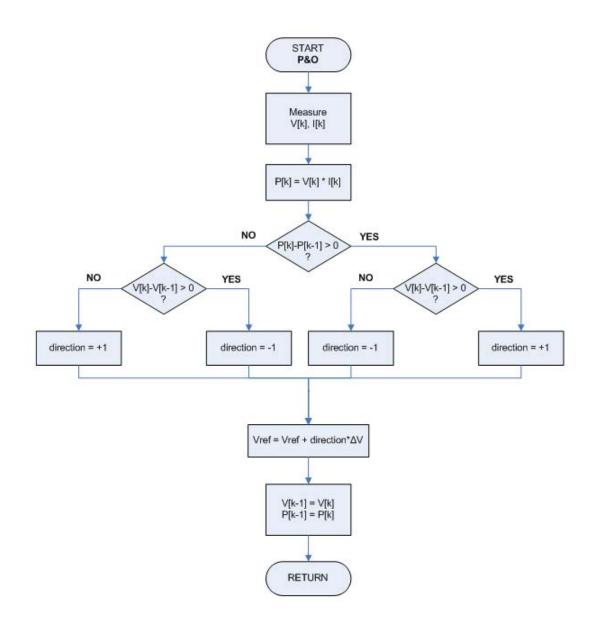

| 27 | Flowchart of the Perturb and Observe algorithm                               | 31  |

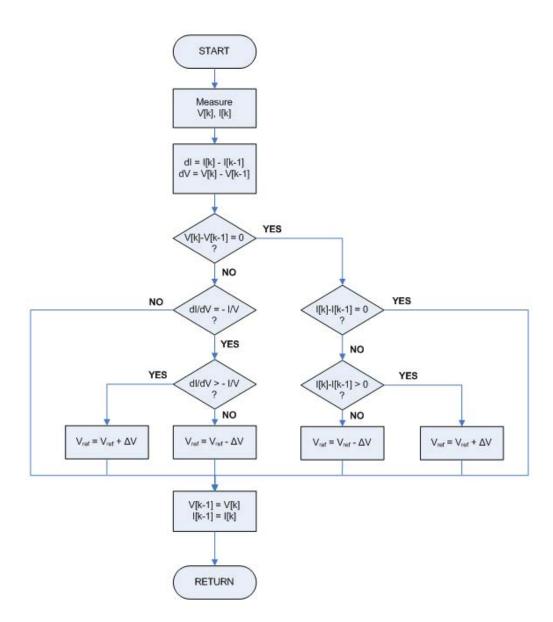

| 28 | Flowchart of the Incremental Conductance algorithm                           | 33  |

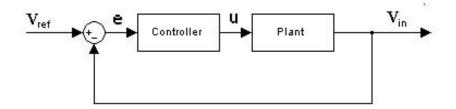

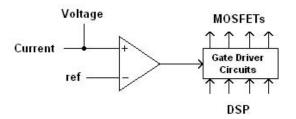

| 29 | Block diagram of the system with feedback from input                         | 36  |

| 30 | Analog vs. digital control                                                   | 37  |

| 31 | Simplified block diagram of the PV system                                    |     |

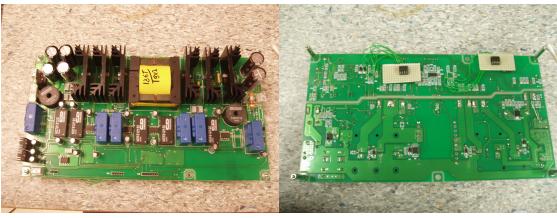

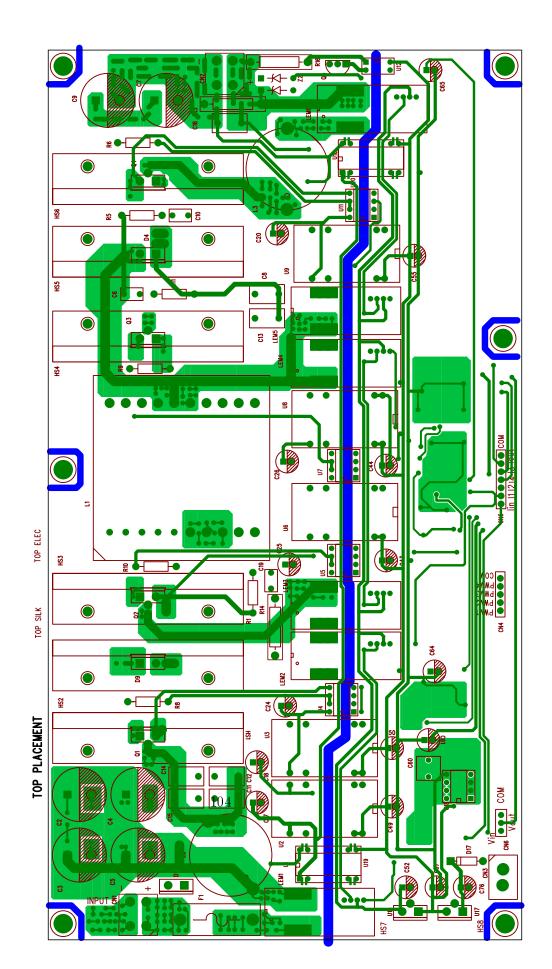

| 32 | The circuit board of the converter                                           |     |

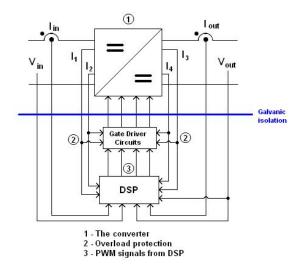

| 33 | Block diagram of the DC-DC converter structure                               |     |

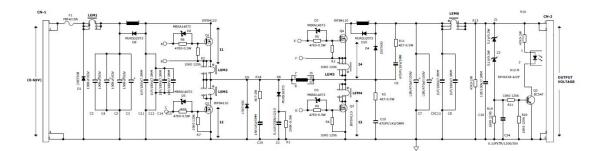

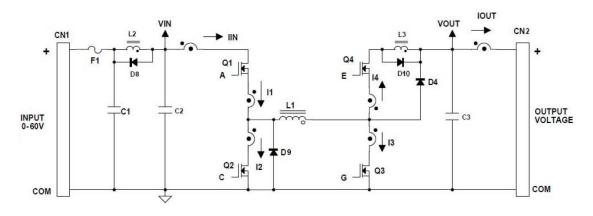

| 34 | Circuit scheme of the DC-DC converter                                        | 46  |

| 35 | The DC-DC converter circuit                                                  |     |

| 36 | Circuit scheme of the voltage measurement circuit                            | 49  |

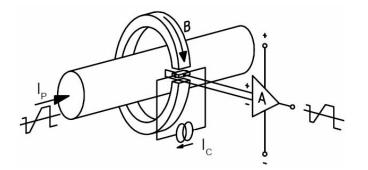

| 37 | Hall effect: Principle of operation of current transducers                   | 49  |

| 38 | Overload protection                                                          | 50  |

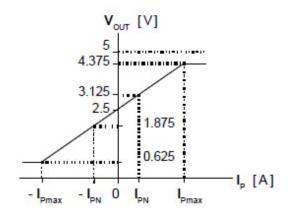

| 39 | Current transducers: Relationship between input current and voltage          | 54  |

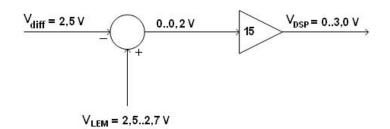

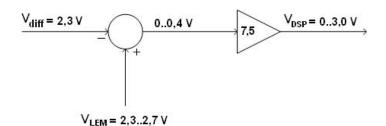

| 40 | Block diagram of voltage scaling, unidirectional flow                        | 55  |

| 41 | Block diagram of voltage scaling, bidirectional flow                         | 55  |

| 42 | Difference amplifier circuit for bipolar current direction, $I_{max} = 16$ A | 56  |

| 43 | Transistor circuit to upscale PWM voltage                                    | 58  |

| 44 | NI ELVIS II                                                                  | 60  |

| 45 | Setup with NI Elvis II                                                       | 61  |

| 46 | TMS320F2808 Control Card                                                     | 62  |

| 47 | The user interface of Code Composer Studio                                   |     |

| 48 | Block diagram of DSP contents                                                | 70  |

| 49 | Graphical overview of DSP operation                                          | 71  |

| 50 | Flow diagram of the implemented P-/PI-controller                             | 75  |

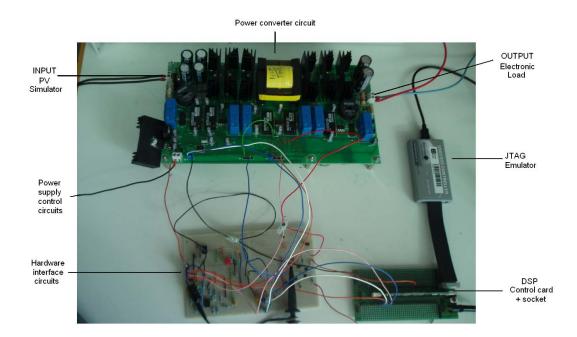

| 51 | Laboratory setup                                                             | 76  |

| 52 | Laboratory setup - real                                                      |     |

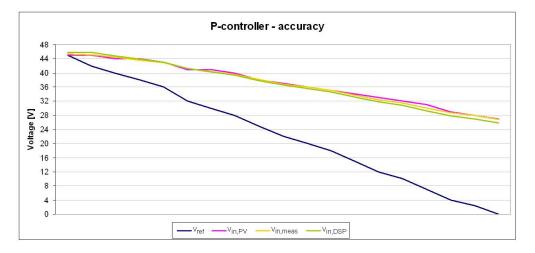

| 53 | Accuracy of the implemented P-controller                                     |     |

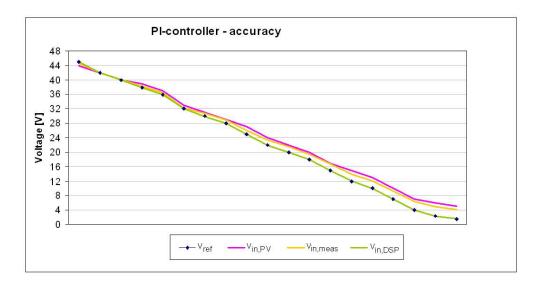

| 54 | Accuracy of the implemented PI-controller                                    | 82  |

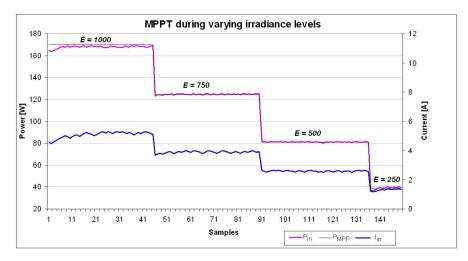

| 55 | MPPT for stepwise change in irradiance level                                 | 83  |

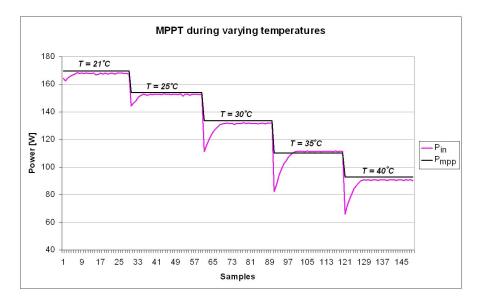

| 56 | MPPT for stepwise change in temperature level                                | 84  |

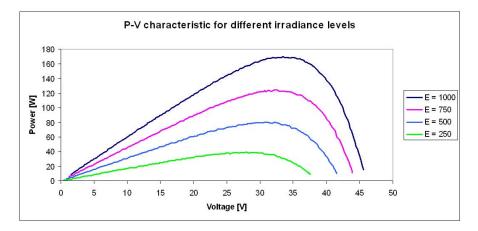

| 57 | I-V characteristic for different irradiance levels                           | 130 |

| 58 | P-V characteristic for different irradiance levels                           | 130 |

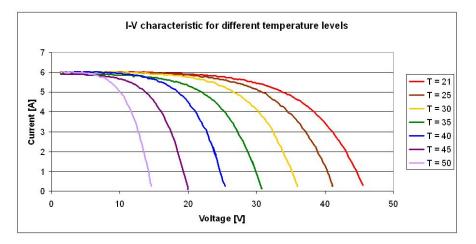

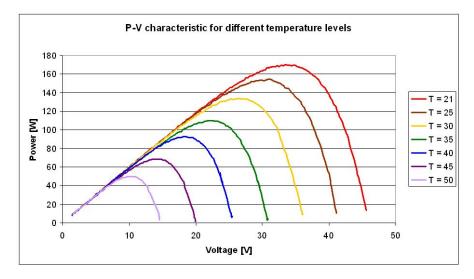

| 59 | I-V characteristic for different temperature levels                          | 131 |

| 60 | P-V characteristic for different temperature levels                          | 132 |

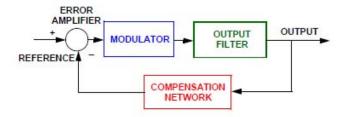

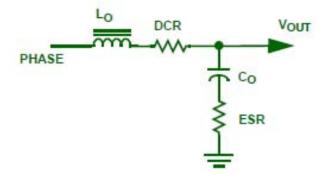

| 61 | Basic block of the buck regulator                                            | 133 |

| 62 | Output filter                                                                | 134 |

### LIST OF FIGURES

viii

# Abbreviations

| $\mathbf{AC}$          | Alternating Current                                        |

|------------------------|------------------------------------------------------------|

| ADC                    | Analog-to-Digital Converter/Conversion                     |

| $\operatorname{CCM}$   | Continuous Conduction Mode                                 |

| $\mathbf{C}\mathbf{C}$ | Constant Current                                           |

| CT                     | Continuous Time                                            |

| CV                     | Constant Voltage                                           |

| DC                     | Direct Current                                             |

| DCM                    | Discontinuous Conduction Mode                              |

| DSP                    | Digital Signal Processor                                   |

| EMD                    | Electromagnetic Discharge                                  |

| EOC                    | End of Conversion                                          |

| $\mathbf{ESR}$         | Equivalent Series Resistance                               |

| ePWM                   | Enhanced Pulse-Width Modulation                            |

| FCCM                   | Forced CCM                                                 |

| GPIO                   | ${\rm General} \ {\rm Purpose} \ {\rm Input}/{\rm Output}$ |

| IC                     | Integrated Circuit                                         |

| $\operatorname{ISR}$   | Interrupt Service Routine                                  |

| MOSFET                 | Metal Oxide Semiconductor Field-Effect Transistor          |

| MPP                    | Maximum Power Point                                        |

| MPPT                   | Maximum Power Point Tracking                               |

| MSB                    | Most Significant Bit                                       |

| P&O                    | Perturb and Observe                                        |

| Р                      | Proportional                                               |

| PI                     | ${ m Proportional} + { m Integral}$                        |

| POPI                   | Power In - Power Out                                       |

| PV                     | Photovoltaic                                               |

| PWM                    | Pulse-Width Modulation                                     |

| $\operatorname{SOC}$   | Start-of-Conversion                                        |

| $\operatorname{STC}$   | Standard Test Conditions                                   |

| $\mathbf{SMPS}$        | Switched mode power supplies                               |

| TI                     | Texas Instruments                                          |

|                        |                                                            |

### 1 Introduction

The world energy consumption has within the recent decades become an important topic in the society, both in a political and social aspect. The energy production has mainly been based on energy sources like oil, gas and coal, which until recently was looked upon as close to inexhaustible. As the world energy consumption is growing with a drastically high rate and the fossil fuels reserves are shrinking, the need for renewable energy resources has gained more focus. Both renewable and non-renewable energy resources are mostly created by the sunrays hitting the surface of the earth. The sun is a non-polluting resource responsible for the sustained life on earth, and while non-renewable energy resources has been generated over a long period, renewable energy resources is broadly speaking always available. Among the renewable energy resources are hydro power, wind power and solar energy. While hydro power has been a well known technology for a long time, there is a lot of research going on with wind and solar power today [13].

Solar energy as a energy source has a large theoretical potential, and can be utilized both directly and indirectly. The potential is especially large on the African continent. The climate change is a global environmental problem that might affect especially people in developing countries, as many of these human beings already suffer from difficult living conditions. The solar irradiance at the African continent is considerable and there is a great need of developing knowledge on how to utilize the solar energy to increase the living standards [10].

In this master thesis a grid connected PV inverter system will be studied. The PV system will utilize the solar energy as the power source and transfer the power into the grid through conditioning by power electronics. The power electronics is an essential part of a PV system, and it is necessary to understand how to utilize and control this part for optimization of the power generation. To support the teaching in control of the power electronics through digital signal processing, a laboratory setup of the PV inverter system is under development. The long term goal is to implement this laboratory setup in an African University, primarily in Dar es Salaam, Tanzania, and Makerere, Uganda. These two countries have a quite similar energy situation, where a mixture of grid connected and isolated systems has lead to tapped energy resources. This has again lead to a striving for utilization of renewable energy sources, with solar energy as the most important (more information about this can be found in [11], [9] and [34]).

The system to be considered is shown in figure 1. The low voltage level in the grid in Tanzania and Uganda, to which this system will be connected, is ranging from 240 V to over 400 V. But as this particular system is meant for laboratory use on a University level, the voltage level needs a modification for safety reasons. To ensure that the voltages are not dangerous for students doing experiments, the voltage level has been planned to be around 48 V. The panels will produce an output that lies within the range of 0-60 V. The same range will also be applied at the output of the DC-DC converter. The inverter stage must produce an output voltage proportional to the grid voltage level. Hence it must

consider both the grid voltage as well as the output voltage from the DC-DC converter and adjust the inverter operation from this information. To be able to connect to the grid, a transformer is included between the inverter stage and the grid.

Figure 1: Simplified sketch of the circuit

The system has a quite simple structure, consisting of the following parts:

- 1. A **PV panel** producing the power input

- 2. A DC-DC converter creating a potential difference between input and output

- 3. A DC link for energy storage and filtering

- 4. An inverter for interconnection to the grid

- 5. A transformer for transformation from low voltage (LV) to grid voltage (HV)

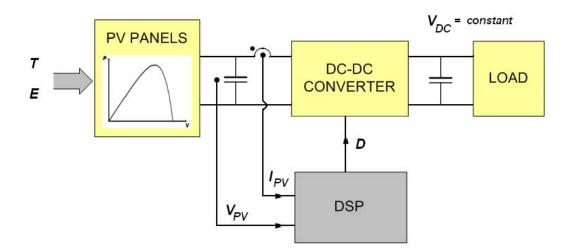

The system can be divided in three main parts which are to be considered; these are the PV panels, the power electronics and the control system. The PV panels are the point of power input and the main emphasis will be on how to extract the maximum power from the panels at any time through power conditioning by the power electronics stage. This stage includes the DC-DC converter, the DC link and the inverter. The DC-DC converter is responsible for Maximum Power Point Tracking, while the inverter is keeping the DC link voltage on a constant level. The DC link is decoupling each of the converter stages and its purpose is to act as an energy storage element and filter. To obtain a stable system operation the voltages in the system need to be monitored and controlled. This is accomplished by implementing a control system through digital signal processing.

Previous to this master thesis a master project was performed. In this project the main emphasis was on exploring and developing parts of the hardware needed in the PV system. A DC-DC converter designed by Supratim Basu at Bose Research in India was built and tested, with regards to functionality and possible improvements. The project resulted in a operating converter, suitable for the purpose intended. With the hardware part of the specified part of the system in operation, the next step is to look at the software.

In this master thesis the main focus will be on developing software suitable for control of the DC-DC converter stage in addition to a hardware interface between the converter and the hardware of the control system.

## 2 Background

In this section a presentation of a PV system together with some additional theory will be given. Part of the theory is similar to the one given in the previous master project. This is done to be able to present the master thesis as a complete piece of work, independent of the master project. Some parts have also been altered and extended.

#### 2.1 What is a PV system?

The term PV is short for photovoltaic, which means that the system is designed around the photovoltaic cell. This cell by itself has a small power output and has a maximum power generation of less than 3 W (normally between 1 and 2 W)<sup>1</sup>. The required power output is in most realistic situations a lot higher than this, and to produce this amount of power many PV cells are connected in series to PV modules. For even higher power output PV modules are connected together to PV arrays. A more detailed description of each of these units will be given later in this chapter. The theoretical background about the PV system is mainly based on the references [32], [42], [40] and [41].

The photovoltaic part alone does not represent a whole PV system; a connection to other elements called BOS ("Balance of system") components is required [38]. The BOS components are typically energy storing mechanisms (like batteries or capacitors), charge control and power electronics conditioning the input power to a preferred output (DC-DC converters or DC-AC inverters). It is important to note that the load is also considered a part of the PV system.

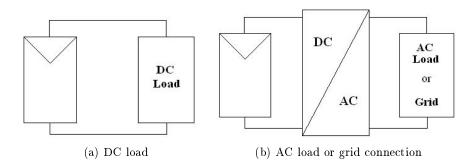

The PV cell produces a DC output, which indicates that the choice of components in a PV system must be done based on the area of application. In a stand-alone system (solar home system) the photovoltaic part is often directly connected to a DC load. In a system connected directly to the grid or an AC load an inverter is needed to get a suitable power output. Figure 2 shows the most basic structures of each of the system structures.

#### 2.1.1 Stand-alone system

In a stand-alone system the simplest structure will be as in figure 2a with the PV panel connected directly to the load. This system will in most situations produce a power output dissimilar to the optimal output available. As will be shown later in this chapter other components must be added to get a more efficient system. Because of the varying power input in solar cells, it is typical to add energy storing components (i.e. batteries) to ensure a continuous output. When batteries are implemented in the system, charge controllers have to be added. These controllers avoid discharge and overcharge of the

$<sup>^1\</sup>mathrm{The}$  normal rating of a PV cell is normally 0.5-0.6 V and 2.0 A

Figure 2: PV system with DC and AC load or grid connection

batteries. When the batteries are fully charged, the PV panels are disconnected to avoid overcharging, and when the batteries are discharged the load is disconnected. The charge controllers will provide for optimal charging and discharging depending on several parameters, as temperature, load conditions and power input from the PV panels.

#### 2.1.2 Grid connected system

In a DC-AC grid connected system it is not so common to add batteries as energy storage. This is due to the fact that the grid can be utilized as an "unlimited" energy source or sink, thus additional energy storage is unnecessary.

#### 2.2 The working principle of photovoltaics

It is important to understand how the photovoltaic system is compounded and how it works when exposed to sunlight. As mentioned earlier, the photovoltaic part is the power source in the system. The task of the photovoltaic part is direct transformation of the solar irradiance into electricity, and the physics behind this transformation will now be examined.

#### 2.2.1 The Photovoltaic cell

The photovoltaic (PV) cell is the smallest constituent in a photovoltaic system. A PV cell is a specially designed pn junction (a semiconductor), mainly silicon based and the power input is made possible by a phenomenon called the photoelectric effect. The characteristic of photoelectric effect was discovered by the French scientist, Edmund Bequerel, in 1839, when he showed that some materials produce electricity when exposed to sunlight. The photons in the light are absorbed by the material and electrons are released, which again creates a current and an electric field because of charge transfer. The nature of light and the photoelectric effect has been examined by several scientists the last century, for instance Albert Einstein, which has lead to the development of the solar cell as it is today [32].

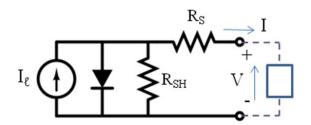

An ideal PV cell can be modeled as an ideal current source in anti-parallel with a diode. The current on the terminals of the PV cell will then be the difference between the photon current  $I_l$  and the diffusion current through the diode. This can be expressed as:

$$I = I_l - I_o(e^{\frac{q_V}{mkT}} - 1)$$

(1)

where:

$I_l$  is the component of cell current due to photons [A]

$I_o$  is the reverse saturation current[A]

$\mathbf{V}$  is the cell voltage [V]

$\mathbf{T}$  is the cell temperature [K]

$$q = 1.6e-19 [C^{\circ}]$$

$\mathbf{k} = 1.38\text{e-}23$  [j/K] Boltzmann's constant

**m** is the ideality factor (m=1 for an ideal cell)

The current equation shows that the PV cell is limited both in current and voltage. For low voltage or during short circuit the exponential term will have a minor influence on the current, which gives an approximately constant current equal to the sum of the cell current  $I_l$  and the reverse saturation current  $I_o$ . As the voltage is increased the exponential term will increase accordingly and eventually the voltage will reach a maximum where the cell current equals zero (open circuit). The current in the cell can not go negative.

This representation of the PV cell can be made more realistic as shown in figure 3 (reference [23]). Here  $R_S$  and  $R_{SH}$  are the series and shunt resistances respectively and account for the parasitic losses in the PV cell. Ideally the shunt resistance should be close to infinity and the series resistance close to zero.

Figure 3: Simplified equivalent circuit of a PV cell

With the inclusion of the parasitic losses, the current equation will be slightly different. A current will also flow through the shunt resistance and an extra term will be subtracted from the original equation. As the series resistance is rather small, the extra term will reduce due to the negligible voltage loss over  $R_s$ . This can be seen in equation 2. However, as the shunt resistance is assumed close to infinity this term is disregarded in further examinations.

$$I = I_l - I_o(e^{\frac{qV}{mkT}} - 1) - \frac{V + I \cdot R_s}{R_{sh}} = I_l - I_o(e^{\frac{qV}{mkT}} - 1) - \frac{V}{R_{sh}}$$

(2)

The limitations on voltage and current mean that the cell is not harmed when operating under open circuit or short circuit conditions. The short circuit is the maximum current appearing when the voltage is set to zero, for a given irradiance and temperature. This leads to  $I_{sc} = I_l$  (see equation 1).

The open circuit voltage is the maximum voltage for a given light and temperature when the cell current is set equal to zero:

$$V_{OC} = \frac{kT}{q} ln \frac{I_l + I_o}{I_o} \cong \frac{kT}{q} ln \frac{I_l}{I_o}$$

(3)

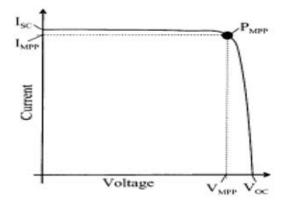

The power output of a PV cell is given by multiplying the current and the voltage that belongs together on the I-V characteristic. On background of the high cost and general request for high efficiency it is desired to optimize the power output from the PV cell, and the maximum power point (MPP) in a solar cell is given by:

$$P_{MPP} = V_{MPP} \cdot I_{MPP} \tag{4}$$

The characteristic of an ideal PV cell with the maximum power point is shown in figure 4 (reference [40]).

Figure 4: Ideal PV cell with maximum power point

A general rule for the MPP is that it is always found on the knee of the characteristic, where the hyperbola of "I\*V = constant" is tangent to the I-V characteristic in only one point. If a hyperbola strikes the characteristic in more than one point, the maximum power point for that particular characteristic is not yet found. Another common way of finding the maximum power point is to plot the cell power vs. cell voltage. It's worth to add that the value of  $V_{MPP}$  is normally around 80 % of  $V_{OC}$  and  $I_{MPP}$  is around 91 % of  $I_{SC}$ .

The quality of the cell is given in terms of the fill factor FF. The fill factor gives the share of the theoretically maximum power output that is actually produced:

$$FF = \frac{P_{MPP}}{I_{SC} \cdot V_{OC}} \tag{5}$$

The fill factor is dependent of the internal resistance of the cell, where the ideal cell will have a FF = 1 (this is not yet possible with today's technology). In real cells today the fill factor varies between 0.5-0.8.

#### Conditions that influence the working operation of PV cells

• Temperature

The temperature of the PV cell is an important parameter that has to be taken into consideration in PV system operation. The PV cell has given temperature coefficients for both the current ( $\beta$ ) and the voltage (- $\alpha$ ). The current coefficient is mostly negligible, hence it is mainly the voltage temperature coefficient that is considered during calculations. For silicon based cells the coefficient  $\alpha = 2.3 \frac{mV}{C^{\circ}}$ per cell. This can also be seen in equation 1, where the diode is used to include the temperature coefficient. • Irradiance

In this case the impact of irradiance on the cell voltage is negligible, and thus it is the short circuit current that is considered in calculations. This current is normally set proportional to the irradiance E (given in  $\frac{kW}{m^2}$ ):

$$I_{SC}(E) = I_{SC}(at\_STC) \cdot E \tag{6}$$

Standard Test Conditions (STC) [12] is the universal industrial standard of laboratory test conditions under which PV cells can be used. There are three factors in this standard<sup>2</sup>:

|                  | Notation | Value | Unit             |

|------------------|----------|-------|------------------|

| Irradiance       | Е        | 1     | $\frac{kW}{m^2}$ |

| Air mass         | AM       | 1.5   | -                |

| Cell temperature | Т        | 25    | C°               |

Table 1: Standard test conditions (STC)

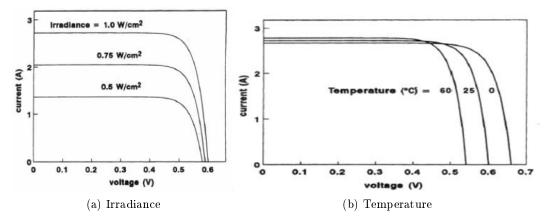

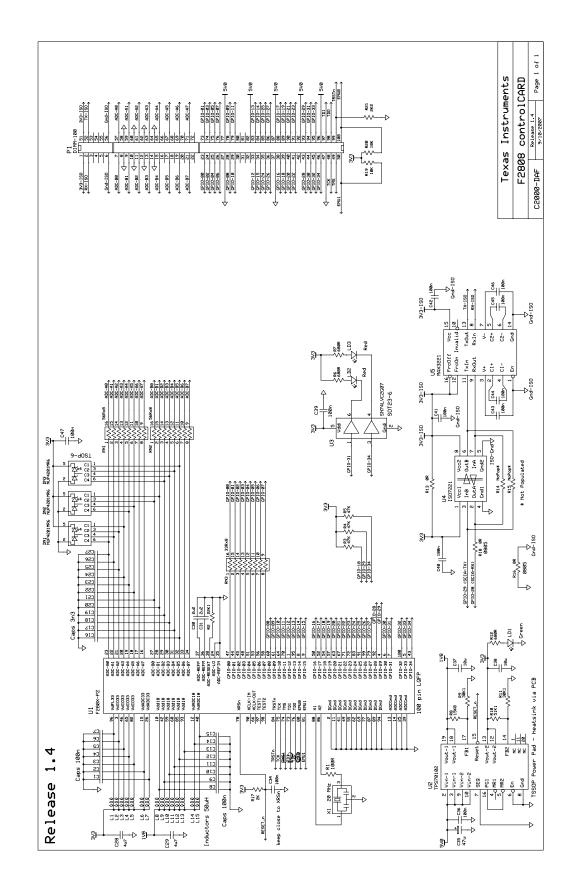

Figure 5 shows the I-V characteristics for different values of irradiance and temperature. While changing the irradiance level the temperature is assumed constant, and vice versa. Here it is quite evident that when the PV cell is operated away from the MPP the cell in reality operates as either a constant voltage source or a constant current source.

Figure 5: I-V characteristics for different levels of irradiation and temperature

It should be emphasized that during the open circuit or short circuit conditions there is no power production, given as one of the parameters is zero in each case.

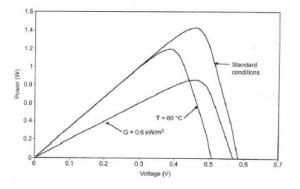

The power vs. voltage characteristic for STC, as well as different levels of irradiance and temperature is shown in figure 6. Both figures 5 and 6 are taken from reference [40].

<sup>&</sup>lt;sup>2</sup>Air mass indicates the clarity of the air that the sunlight passes trough

Figure 6: P-V characteristic of a PV cell

#### 2.2.2 The Photovoltaic Module

In most practical situations the output from a single PV cell is smaller than the desired output. To get the adequate output voltage, the cells are connected in series into a PV module. The industry standard is 12 V PV modules, and with a voltage output of 0.5-0.6 V of each cell it would be fair to assume a series connection of about 20-24 cells. But as the goal is to keep the voltage  $V_{MPP}$  within a satisfactory range (around 12 V) during average irradiance, a safety margin must be included. The standard number of cells connected in series to get 12 V in a module is around 36, and the module is able to generate around 70-100 W.

When making a module, there are a couple of things that need consideration.

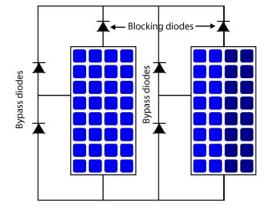

• No or partly illumination of the module

During the night, when none of the modules are illuminated, an energy storage (like a battery) connected directly in series with the modules makes the cells forward biased. This might lead to a discharge of the energy storage. To prevent this from happening a **blocking diode** can be connected in series with the module. But during normal illumination level this diode represents a significant power loss.

• Shading of individual cells

If any of the cells in a module is shaded, this particular cell might be forward biased if other unshaded parts are connected in parallel. This can lead to heating of the shaded cell and premature failure. To protect the system against this kind of failure, the modules contain **bypass diodes** which will bypass any current that cannot pass through any of the cells in the module.

It's important to emphasize the importance of connecting PV cells with the same I-V characteristic. To optimize the generation, the maximum available output should occur at the same irradiance level for all the modules. This implies equal voltage for parallel connection and equal current for series connection. If the characteristics vary, some cells

might generate power while others are dissipating power.

The placement of bypassing and blocking diodes in the system is shown in figure 7 [19].

Figure 7: A PV module with bypass and blocking diodes

#### 2.2.3 The Photovoltaic Array

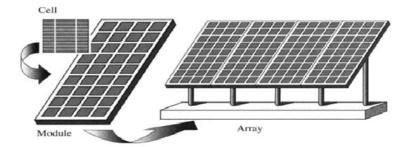

If the output voltage and current from a single module is smaller than desired, the modules can be connected into arrays. The connection method depends on which variable that needs to be increased. For a higher output voltage the modules must be connected in series, while connecting them in parallel in turn gives higher currents. It is important to know the rating of each module when creating an array. The highest efficiency of the system is achieved when the MPP of each of the modules occurs at the same voltage level.

The relation between each of the PV parts are shown in figure 8 (reference [41]).

Figure 8: Relation between the PV cell, a module and an array

The term PV panel will be used from now on when referring to the photovoltaics of the system, independent of what composition will be used later.

#### 2.3 Power electronics in a PV system

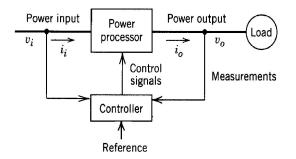

The voltage produced by the photovoltaic cells will vary according to the sunlight intensity (irradiance), but the system output requires a constant voltage value. To be able to process and control the electric energy in the system (i.e. the voltages, currents, frequency) there is a need for a power electronic interface. A typical setup of a power electronic system is shown in figure 9. The power flows from the input to the output through a processor stage, which is controlled through a negative feedback signal from either the input or the output (or both). The theory about the power electronics is mainly based on references [33], [14] and [30] and all the figures are collected from these references (some with modifications).

Figure 9: Block diagram of a power electronic system

The power input can be a DC as well as an AC signal. The output depends on the requirement from the load. In a PV system the power input will always be a DC signal given by the functionality of the PV cell (which is varying with the amount of energy absorbed from the sun).

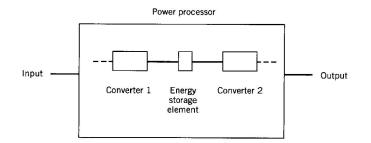

The power processor can be described as a power conversion stage. It typically consists of one or more converters, often with an energy storage element included. A PV system intended for grid connection usually has a power processor as shown in figure 10. In the system considered in this master thesis Converter 1 corresponds to a DC-DC converter, while Converter 2 is a DC-AC converter (inverter). This way the output is connected directly to an AC load or to the grid.

The controller can be implemented to control both the converters separately to ensure a stable interface between each of the stages, i.e. between the input and Converter 1, the two converter stages, and Converter 2 and the output.

#### 2.3.1 DC-DC Switch Mode Converters

The purpose of DC-DC Switch Mode Converters in general DC power supplies is to convert unregulated DC input to regulated or controlled DC output at a desired voltage

Figure 10: Block diagram of a power processor

level. In such systems the input is often fluctuating due to rectification and the output is requiring a constant output. In a PV system, on the other hand, the DC-DC converter is actually controlling the input by considering the unregulated output. By help of MPP Tracking (which will be explained later) the converter adjusts its operation according to the output value to find the optimal operating voltage of the PV module.

There are several different kinds of DC-DC converters in use in the industry today, but most of them are based on two basic converter topologies:

- Buck converter (step-down)

- Boost converter (step-up)

Each of the topologies will be explained later in the report.

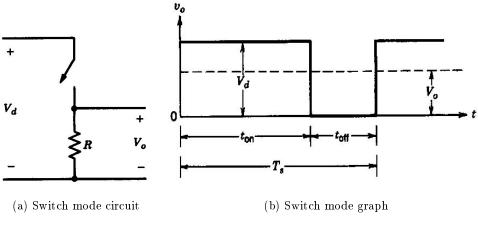

**Control of DC-DC converters** The voltage transformation in a DC-DC switch mode converter is done by utilizing switches, hence the name "switch mode converters". The switches are controlled to be on and off for a certain amount of time through a method called pulse width modulation (PWM). The switching period  $T_s = t_{on} + t_{off}$  (and hence the frequency) is held constant while the ratio of the on time to the switching time is varied. This ratio is called the switch duty ratio D, or duty cycle. By using switch mode control in the circuit in figure 11a, the output voltage  $v_o$  will be a constant pulse as shown in figure 11b. Because of inductive and capacitive circuit elements in the converter topologies the output voltage may have a certain amount of ripple, but the average output voltage should be constant (given as the dashed line  $V_o$ ).

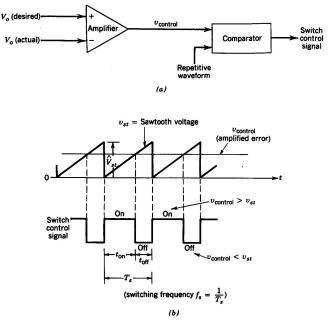

The switch control signal can be generated by comparing a control value (which most often is an amplified error) to a repetitive waveform  $v_{st}$ . The control value may be the difference between the actual and the desired output voltage  $V_o$  (as seen in figure 12. The effects of the comparison are:

- when  $v_{control} > v_{st}$ : switch on

- when  $v_{control} < v_{st}$ : switch off

Figure 11: The principle of switching

The duty cycle D can now be defined in two different ways:

$$D = \frac{t_{on}}{T_s} = \frac{v_{control}}{\hat{V_{st}}} \tag{7}$$

The frequency (and  $T_s$ ) can also be varied in a PWM switching mode. This method might make it hard to filter the ripple components in the converter waveforms, and will not be used in the master thesis. Thus there will be no further explanation on this subject.

Common for both the converter topologies is the direction of transferred energy. The energy is unidirectional, which means that it can be transferred in one direction only. As there is seldom a requirement of a bidirectional flow in a grid connected PV system, the buck and boost converter topologies are more than sufficient for this application.

In the following sections the converter topologies will be analyzed with steady state conditions, the switches are assumed to be ideal and losses in the capacitors and inductors are neglected. In addition the switching time is assumed much shorter than the electric time constant of the circuit. Then the model analysis will be extended to include perturbation in the converter operation.

#### 2.3.2 Steady state analysis

When analyzing each of the converter topologies, it is first assumed that they operate in steady state. This implies a constant duty cycle, which means that the current starts from the same value at the beginning of every switching cycle. Due to the inductor the current will charge and discharge through one cycle, and steady state condition implies that  $\Delta I_{on} = \Delta I_{off}$ . The change in current is the only factor deciding whether or not the

Pulse-width modulator: (a) block diagram; (b) comparator signals.

Figure 12: The principle of PWM control

system is in steady state. In a DC-DC converter with an optimal design it is assumed that the switching ripples are very small compared to the average values, often less than 1 %. This is often referred to as the small or linear ripple approximation.

#### • Buck converter

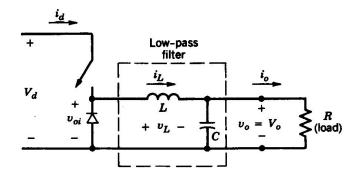

The buck converter is often referred to as a step-down converter, and as the name implies, the converter produces a lower DC voltage output than the input. The circuit of the buck converter can be seen in figure 13.

This circuit is an improved version of the circuit in figure 11a. The resistive load is replaced by a diode to overcome the problem of stored inductive energy that will normally appear in the circuit. In figure 11a this energy can harm the switch because there are no other components that can dissipate it. Secondly a low-pass filter is used to reduce the output voltage fluctuations as much as possible. This is achieved by wise selection of filter parameters to reduce the corner frequency  $f_c$  (this will also be explained later). The output voltage  $v_o$  will be as in figure 11b.

The buck converter will have different circuit schemes for each of the switch positions. To obtain the relationship between the input and output of the converter (and hence the duty cycle) the current through the inductor will be examined. The filter capacitor is assumed to be so large that  $v_o(t) = V_o$ , which means that no current will flow through it.

Figure 13: Buck converter

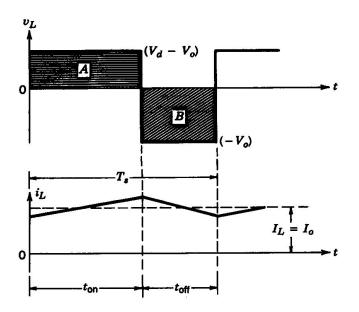

Thus it can be concluded that the inductor current equals the output current for both switch positions. The earlier assumption about the system being in steady state implies that the voltage and current waveforms repeat for each time period  $T_s$ . This can be seen by considering each of the circuits in figure 14.

Figure 14: Buck converter circuit for a)  $t_{on}$  and b)  $t_{off}$  in CCM

When the switch is on, the input voltage  $V_d$  leads to a linear increase in the inductor current. As the switch is turned off, the diode becomes forward biased and the stored energy in the inductor makes the current continue to flow. But as the energy is transferred from the inductor to the load, the current is decreasing again.

The inductor voltage is given as:

$$v_L = L \frac{di_L}{dt} \tag{8}$$

As the inductor voltage is repeating itself for each time period, the change for each period is zero:

$$(i_L)_{on} = (i_L)_{off}$$

$$\int_0^{t_{on}} v_L dx = \int_{t_{on}}^{T_s} v_L dx$$

By considering the voltage curve in figure 15 the equation can easily be solved:

$$(V_d - V_o)t_{on} = V_d(T_s - t_{on})$$

Figure 15: Inductor voltage and current of the buck converter

By some rearrangement, the relationship between the input and the output voltage is found:

$$\frac{V_o}{V_d} = \frac{t_{on}}{T_s} = D \tag{9}$$

The buck converter is actually equivalent to a transformer where the turns ratio is changed by varying the duty cycle. This can be shown mathematically by considering the power input and output. Neglecting the losses in the circuit gives the following relations:

$$P_{d} = P_{o}$$

$$V_{d}I_{d} = V_{o}I_{o}$$

$$\frac{V_{o}}{V_{d}} = \frac{I_{d}}{I_{o}} = D$$

(10)

This is also referred to as a POPI (Power In - Power Out) type converter [17].

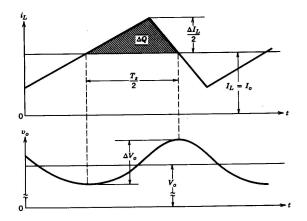

**Output voltage ripple in a buck converter** The theoretical value of the filter capacitor is assumed to be so large that the output voltage is constant. But in a realistic buck converter this will not be the case, and there will be produced a ripple in the output voltage.

Figure 16: Output voltage ripple in a buck converter

The inductor current consists of two components, an average component flowing through the resistive load, and a ripple component assumed to flow through the capacitor. The ripple current introduces an additional charge  $\Delta Q$ , which can describe the ripple voltage:

$$\Delta V_o = \frac{Q_c}{C} = \frac{1}{C} \left(\frac{1}{2} \frac{T_s}{2} \frac{\Delta I_L}{2}\right) = \frac{1}{8C} \Delta I_L T_s \tag{11}$$

To minimize the ripple, the low-pass filter has to be selected so that the corner frequency  $f_c = \frac{1}{2\pi\sqrt{LC}} \ll f_s$ . This deduction is done assuming the ESR, which is the resistive part of the capacitor and inductor impedances, to be negligible.

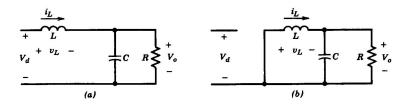

#### • Boost converter

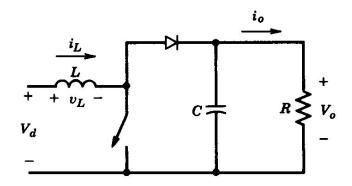

As opposed to the buck converter, the boost converter produces an output voltage which is higher than the input voltage. The circuit is according to figure 17.

Figure 17: Boost converter

This topology also has different circuit schemes depending on the state of the switch, as seen in figure 18. When the switch is on the output stage is isolated from the input caused by the reverse biased diode. The input will supply the inductor with a constant voltage, and the inductor current will increase according to equation 8. When the switch is turned off, the output will be supplied both by the input and the inductor, and the current through the inductor will decrease because of this energy transfer.

Figure 18: Boost converter circuit for a)  $t_{on}$  and b)  $t_{off}$  in CCM

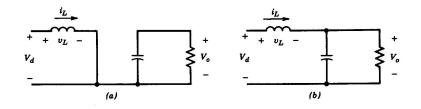

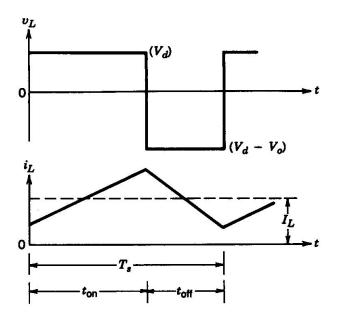

The voltage and current graphs of the inductor through one time period is shown in figure 19. The shapes are equal to those of the buck converter, but the voltage of the inductor is different due to the placement of the switch and the diode.

Figure 19: Inductor voltage and current of the boost converter

The same considerations regarding the inductor current can be done for this converter as in the previous section, which leads to the connection:

$$V_d t_{on} = (V_o - V_d)(T_s - t_{on})$$

After some rearrangements the equation becomes:

$$\frac{V_d}{V_o} = (1+D) = \frac{I_o}{I_d} \tag{12}$$

The last term of the equation is yielded from the assumption of no power loss in the circuit (i.e.  $P_{in}$  equals  $P_{out}$ ), and as for the buck it is referred to as a POPI converter.

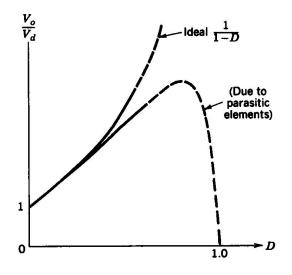

**Parasitic elements** In a boost converter there will be losses due to the switches, the diode, the capacitor and the inductor. When the duty cycle gets close to one, the output voltage will theoretically increase against infinity, but due to the parasitic elements the ratio of  $V_o$  on  $V_d$  will actually go to zero. The ideal and the real characteristic of the conversion ratio versus duty ratio is shown in figure 20.

Figure 20: The effect of parasitic elements in a boost converter

In general the parasitic elements will seldom have a big impact because the duty ratio goes into saturation before entering the steep slope of the parasitic curve.

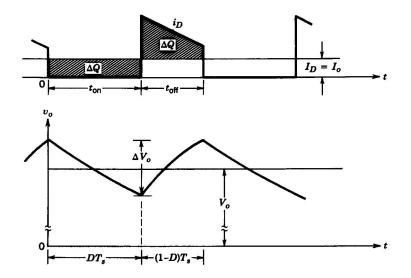

**Output voltage ripple in a boost converter** The output voltage ripple will also be present in a boost converter due to the capacitor value. When the switch is on the stored energy in the capacitor will be sent to the load, causing a discharge and decreased voltage. When the switch is off the capacitor is charged again by the input.

The ripple voltage  $\triangle V_o$  can be written as:

$$\Delta V_o = \frac{Q_c}{C} = \frac{I_o D T_s}{C} = \frac{V_o}{R} \frac{D T_s}{C}$$

(13)

Figure 21: Output voltage ripple in a boost converter

This equation can also be utilized to find a capacitor value suitable for the circuit, choosing a worst case tolerated value of the ripple  $\Delta V_o$ . Normally the values D and R are dependent on the operation, but when calculating for a specific point of operation these values are known.

#### 2.3.3 CCM cs. DCM

With steady state conditions the system can operate differently, depending on the starting point of the current. When the average of the current stays at a non-zero value throughout (which implies that  $i_L(kT_s) > 0$ ), the system is operating in so-called Continuous Conduction Mode (CCM). When the current on the other hand goes to zero before the end of every cycle, the system is in the Discontinuous Conduction Mode (DCM). The condition where the current starts and ends at zero every cycle with continuous conduction is referred to as the boundary conduction mode (BCM). For normal operation the CCM is most common, but at light loads (increased load resistance) the DCM is advantageous as it causes less power losses in the circuit. The transition from CCM to DCM happens when the load current decreases, hence the output power is reduced or the input voltage is increased. All of the deductions done with Buck and Boost converters up till now has assumed CCM.

Most conventional topologies goes by the name "non-synchronous", where a diode is included to prevent current from flowing in the wrong direction. The topologies described in the previous chapters belongs to this category. However, this diode is also the reason why the system goes from CCM to DCM, because any negative current is denied access through the diode. So-called "synchronous" topologies have become more common in the industry today, where the diode is replaced by a MOSFET switch in anti-parallel with the diode. By doing this, DCM is prevented from happening because the current is allowed to go negative through the switch and hence away from the load. The power loss in the MOSFET is a lot lower than across a diode and the conduction losses is reduced. So when the output power is lowered, the converter will not go into DCM, but rather Forced CCM [30].

#### 2.3.4 Small signal AC modeling

In a dynamic system with closed loop (feedback) control where either the input or the output conditions change over time, there will be transitions between steady state operating points. This is due to the perturbation in duty cycle requested by the control system. The analysis of DC-DC converters must be extended from steady state analysis to consider the dynamic variations caused by the reactive circuit components (inductor and capacitor) when the system variables are susceptible to changes. This kind of analysis is referred to as small signal analysis, where the system is analysed when exposed to small variations. As for steady state conditions, the switching ripples in this analysis are assumed to be small compared to the average value and are further ignored.

In this analysis the system is linearized, assuming the signal disturbances so small that no parts of the system will go into saturation or become unstable (hence the name "small signal modeling"). By linearizing the power stage, a transfer function can be developed, and the controller of the system can be determined through utilization of the Nyquist stability criterion and Bode plots (these terms are explained in detail in the references [2] and [36]). It must be noted, however, that this method provides the tools for developing a transfer function only valid for either CCM or DCM.

When the duty cycle is exposed to perturbation, it will be a sum of the steady state duty cycle D and an introduced ac term:

$$d(t) = D + D_m \cdot \cos(\omega_m t) = D + \tilde{d} \tag{14}$$

where the  $\sim$  symbol indicates the perturbation, the value of  $D_m$  is a lot smaller than D and the frequency  $\omega_m$  is much smaller than the switching frequency of the converter. All variables in the system can be written like this, as the sum of a DC term and an AC perturbation term. In a PV system where the DC link voltage is assumed to be constant, the AC term will disappear.

The method for creating the small signal AC model for a converter in either CCM or DCM can be shortly summarized:

- 1. Average the waveforms over one switching period to remove the switching harmonics

- 2. Perturb and linearize the averaged model about a quiescent operating point

- 3. Separate the equations into DC and AC components

- 4. Transform the AC equations into the Laplace domain

- 5. Solve for the transfer function

A method for developing the transfer function for a buck converter is found in the reference [27]. This method is also possible to use for a boost converter in a PV system, which is explained in appendix I.

#### 2.3.5 Buck versus boost in a PV system

In grid connected systems with varying input from the source (like PV or wind), the input voltage might be both higher or lower than the AC voltage. This makes both buck and boost operation necessary, depending on the input voltage. Both converter topologies are applicable for MPPT. In real systems, however, the boost converter is the one most utilized. Normally the DC link voltage will be at least 350 V, and if enough modules cannot be connected in series to obtain this voltage level in small systems, a boost stage is necessary.

It has been presented in earlier studies that the efficiency for a boost converter operating in CCM varies slightly for varying duty cycle, while the efficiency variation for a buck converter is considerable. For a closer study, turn to reference [17].

For a boost converter the current through the inductor will equal the input current, while for a buck converter it will equal the output current. This can also be seen in the figures 14 and 18.

#### 2.3.6 DC-AC Switch Mode Inverters

The purpose of DC-AC Switch Mode Inverters is to produce a sinusoidal AC output from a DC input through PWM. The inverter is able to control both the magnitude and the frequency of the AC output. Inverters that have an input assumed to be a DC voltage source is referred to as Voltage Source Inverters (VSIs), and can be divided into three categories: PWM inverters, square wave inverters and single-phase inverters with voltage cancellation. In a PV system PWM inverters are most frequently utilized and their purpose is to keep the DC-link voltage at a constant voltage level by adjusting the DC link current. The PWM in inverter circuits is more complex than for DC-DC Switch Mode Inverters shown in figure 12. To be able to produce a sinusoidal output voltage waveform with the required frequency, the control signal need to be sinusoidal as well. And the signal it is being compared to is a triangular waveform rather than a sawtooth signal. The frequency of the waveform creates the switching frequency and is ordinarily kept constant. For a more thorough explanation about DC-AC Switch Mode Inverters, see reference [33].

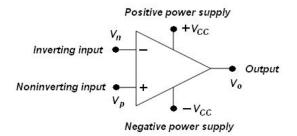

#### 2.4 Operational amplifier

The operational amplifier (normally called op amp) is an electronic circuit which is an important part of many circuits today, and it has many ranges of application for transforming a signal. It consists of two inputs, one output and positive and negative power supply, as shown in figure 22.

Figure 22: Operational amplifier

At the name implies, this circuit is providing an amplification of the input. The output of the op amp equals the difference between the non-inverting and the inverting input multiplied by a large gain A. This linear operation is valid as long as the output voltage stays within the limits of the positive and negative power supply. The power supplies do not need to be of the same magnitude. When the output exceeds the power supply limits, the device goes into saturation. Hence the op amp has three distinct regions of operation. These can be summed up as:

$$A(V_p - V_n) < -V_{CC}: \Rightarrow V_o = -V_{CC}$$

$$-V_{CC} \le A(V_p - V_n) \le +V_{CC} \Rightarrow V_o = A(V_p - V_n)$$

$$A(V_p - V_n) > +V_{CC}: \Rightarrow V_o = +V_{CC}$$

(15)

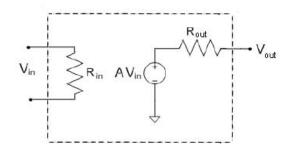

In an ideal op amp the equivalent resistance seen by the input is considered to be infinitely large. This implies that no current is flowing in the input port, and hence  $(V_p - V_n)$ equals zero. This is seen in the equivalent circuit in figure 23. Seen into the output the op amp appears as a source in series with an output resistance. This resistance is assumed to be negligible. In a real op amp, however, the equivalent input resistance is observed to be of finite magnitude, i.e. 1  $M\Omega$  or more, and the output resistance not completely negligible. The gain A, which in an ideal op amp is assumed constant, has also shown to be varying for different operating conditions.

Figure 23: Equivalent circuit of the op amp

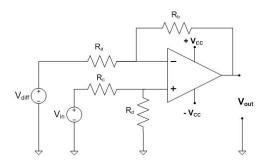

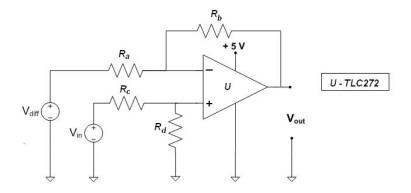

**Difference amplifier circuit** The difference amplifier circuit is a frequently used op amp circuit. The circuit gives an output which is proportional to the difference between the two input voltages (that is between the inverting and the non-inverting input). A circuit diagram is shown in figure 24.

Figure 24: Difference amplifier circuit

Through considering the sum of the currents away from the inverting input node, the output voltage is found to be:

$$V_{out} = \frac{R_d (R_a + R_b)}{R_a (R_c + R_d)} V_{in} - \frac{R_b}{R_a} V_{diff}$$

$$\tag{16}$$

So the output is proven to be the difference between a scaled  $V_{in}$  and a scaled  $V_{diff}$ . For simplification of this difference, the scaling of each of the voltages can be made equal by setting  $\frac{R_a}{R_b} = \frac{R_c}{R_d}$ . This replacement yields a more straightforward expression for the output voltage:

$$V_{out} = \frac{R_b}{R_a} (V_{in} - V_{diff}) \tag{17}$$

The ratio  $\frac{R_b}{R_a}$  can also be called the gain factor of the circuit.

To obtain a circuit where the output voltage equals the difference of the input voltages without any scaling, all the resistors must be given the same value.

The theoretical background on operational amplifiers is based on the references [5] and [36].

## 2.5 Filters

Ripple and noise in the signals can generate distortion in the measurements and thus create errors and unstable operation in the system. The noise can be removed by implementing filters, or frequency selective circuits. Depending on type of elements and placement in the circuit the filters can eliminate certain unwanted frequencies. The typical filter types are low-pass, high-pass, bandpass and bandreject. Noise is a typical high frequent distortion type and can be partly or totally removed by implementing a low pass filter between the input and the output of a circuit. Ideal filters will have a frequency limit where the passing of signal goes from maximum to zero, called the cutoff frequency  $\omega_c$ , but in real circuits this is not possible. At frequencies higher than the cutoff frequency the signals passed through the circuit will decay with a gradient of -20n dB per decade (when examined in a Bode diagram [2] [36]), where n is the order of the filter. So it is hard to remove all kinds of distortion from a signal.

Filters can be divided in two types, the passive and the active filters. The passive filters incorporate utilization of passive circuit elements like resistors, inductors and capacitors, while the active filters also include operational amplifiers (which is characterized as an active circuit element).

More theory on filters and how to design them is found in [5] and [36].

In the system analysed in this master thesis noise in the measurements is a typical issue, and a low-pass filter will be of interest.

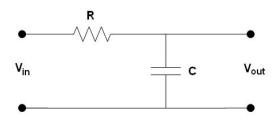

**RC** filter A simple, but often sufficient filter is the RC-filter, shown in figure 25.

Figure 25: First order low-pass RC filter circuit

The transfer function between the input and the output of the filter (in the Laplace domain) is:

$$H_f(s) = \frac{V_{out}}{V_{in}} = \frac{\frac{1}{RC}}{s + \frac{1}{RC}} = \frac{\omega_c}{s + \omega_c}$$

(18)

Thus the values of the resistor and the capacitor decides the cutoff frequency.

Butterworth Filter - design method The Butterworth filter is a design method which leads to maximal flatness in the passband. The filter might be both active and passive and of many different orders depending on the requirement. A normalized <sup>3</sup> first order Butterworth filter has the transfer function:

$$H_{B1}(s) = \frac{V_{out}}{V_{in}} = \frac{1}{s+1}$$

(19)

This filter equals the first order RC-filter with RC = 1.

The general unity gain equation of the Butterworth filter is given as:

$$\mid H_f(\omega) \mid = \frac{1}{\sqrt{1 + (\frac{\omega}{\omega_c})^{2n}}} \tag{20}$$

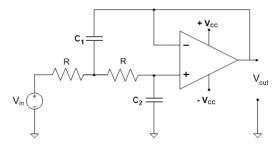

By increasing the order of the filter, the decay of the slope at frequencies higher than the cutoff frequency will be steeper. To obtain a circuit giving a higher order, first and second order filters are cascaded to get the desired order. A circuit that gives the second order transfer function of the Butterworth filter cascade is shown in figure 26.

Figure 26: Second-order circuit in Butterworth cascade

The transfer function for this filter is given as:

$$H_{B2}(s) = \frac{1}{s^2 + b_1 s + 1} \tag{21}$$

<sup>3</sup>when the cutoff frequency  $\omega_c = 1 \frac{rad}{s}$  and gain equal to 1 in the passband

This is obtained by choosing the resistor values to be  $R = 1\Omega$  and the capacitor values:

$$b_1 = \frac{2}{C_1} \tag{22}$$

$$1 = \frac{1}{C_1 C_2}$$

(23)

Only the Butterworth filter circuit of first order is utilized in this thesis, but the procedure of increasing the order might be useful for later development. A closer description is given in reference [36].

# 3 DC-DC Converter Control in PV Converter Systems