[SmallSat] Onboard Data Processing Pipeline and Software/Hardware Implementation of Extended Multiplicative Signal Correction

# Espen Moen

Master of Science in Electronics Submission date: June 2018

Supervisor: Kjetil Svarstad, IES Co-supervisor: Milica Orlandic, IES

Norwegian University of Science and Technology Department of Electronic Systems

#### 1 Abstract

This thesis concerns the data processing pipeline from an CMV2000v3 Image Sensor to memory in a Hyper-spectral imaging Application. A Low Voltage Differential Signal (LVDS) Receiver was implemented, consisting of a Deserializer Module and a Pixel Order Alignment Module to receive and organize the pixel data from the Image Sensor to the rest of the pipeline. Further a Binning Module was implemented to make simple binning operations on the pixel data to reduce minor observation errors as well as reducing the data size. Additionally the thesis presents an algorithm called Extended Multiplicative Signal Correction [8], and a proposal to how this can be implemented in a Software/Hardware Co-design executing on the Zynq-7000 platform. A pure software implementation was made to map which parts of the algorithm would benefit the most from being executed in hardware based on time consumption. Then a SW/HW co-design was implemented with the chosen parts accelerated in hardware. A speedup of 4.36 was achieved by the combined SW/HW implementation to the pure software version.

Denne masteroppgaven omhandler en pipeline for dataflyten fra en CMV2000v3 bildesensor til bildedataen lagres i minnet i en hyperspektral bilde applikasjon. Dette innebærer en implementasjon av en LVDS mottaker bestående av to moduler, en Deserializer og en  $Pixel\ Order\ Alignment\ Module$ . Førstnevnte er en modul for å motta og parallellisere data over LVDS og sistnevnte er en modul for organisere denne dataen i riktig rekkefølge før den sendes videre. Videre ble en  $Binning\ Module$  implementert for å redusere små unøyaktigheter og datastørrelse. I tillegg til dette presenterer denne masteroppgaven en algoritme som heter  $Extended\ Multiplicative\ Signal\ Correction\ [8]$ , og et forslag til hvordan denne kan implementeres i et  $Software/Hardware\ Co-design\ som\ skal\ kjøres\ på$  en  $Zynq-7000\ platform$ . En ren  $software\ versjon\ ble\ først\ implementert\ for å strukturer hvilke deler av algorithmen som ville tjene mest på å bli akselerert i maskinvare for å senke kjøretiden. Basert på dette ble en <math>Software/Hardware$  implementasjon designet som utførte algoritmen opptil 4.36 ganger raskere enn  $software\ versjonen$ .

# 2 Preface

I would like to thank my supervisor Milica Orlandic for her ability to motivate, as well as giving good advices. Additionally, i would like to thank my costudents in this project, Johan, Lars, Aysel and Martin for good cooperation through this year.

# Contents

| 1 | Abs                       | tract                                                    | 1                    |

|---|---------------------------|----------------------------------------------------------|----------------------|

| 2 | Pre                       | face                                                     | 2                    |

| 3 | Intr<br>3.1<br>3.2<br>3.3 | NTNU SMALLSAT                                            | 10<br>10<br>10<br>12 |

| 4 | Dat                       | a Processing Pipeline                                    | 13                   |

|   | 4.1                       | Prototype                                                | 13                   |

|   | 4.2                       | Carrier Board                                            | 14                   |

|   | 4.3                       | PicoZed                                                  | 14                   |

|   | 4.4                       | Image Sensor                                             | 14                   |

|   |                           | 4.4.1 Image Sensor Architecture                          | 15                   |

|   |                           | 4.4.2 Interfacing the Image Sensor                       | 16                   |

|   |                           | 4.4.3 SPI                                                | 18                   |

|   |                           | 4.4.4 Requesting Frames                                  | 19                   |

|   |                           | 4.4.5 Reading data from the sensor                       | 20                   |

|   | 4.5                       | LVDS receiver                                            | 23                   |

|   |                           | 4.5.1 Design Criterias                                   | 23                   |

|   |                           | 4.5.2 Simple Deserialiser                                | 23                   |

|   |                           | 4.5.3 IDELAYE2                                           | 26                   |

|   |                           | 4.5.4 ISERDESE2                                          | 26                   |

|   |                           | 4.5.5 Existing LVDS receiver designs                     | 28                   |

|   |                           | $4.5.5.1$ Design $1 \dots \dots \dots \dots \dots \dots$ | 28                   |

|   |                           | $4.5.5.2$ Design $2 \dots \dots \dots \dots \dots \dots$ | 29                   |

|   | 4.6                       | AXI protocols                                            | 30                   |

|   | 4.7                       | Cube DMA                                                 | 31                   |

|   |                           | 4.7.1 Pixel Order Alignement Module                      | 32                   |

|   | 4.8                       | Binning                                                  | 33                   |

| 5 | Ext                       | ended Multiplicative Signal Correction                   | 34                   |

|   | 5.1                       | Mathematical Model                                       | 34                   |

| 6 | Met                       | hod                                                      | 36                   |

|   | 6.1                       | Exploring the prototype                                  | 36                   |

|   | 6.2                       | LVDS Receiver                                            | 36                   |

|   |                           | 6.2.1 Simple Deserialiser                                | 36                   |

|   |                           | 6.2.2 LVDS Deserialiser with Xilinx Primitives           | 37                   |

|   |                           | 6.2.3 Pixel Order Alignment                              | 38                   |

|   |                           | 6.2.4 Connecting the parts                               | 41                   |

|   | 6.3                       | Binning                                                  | 44                   |

|              | 6.4                               | Extend        | ded Multiplicative Signal Correction                                 | 44 |  |  |

|--------------|-----------------------------------|---------------|----------------------------------------------------------------------|----|--|--|

|              |                                   | 6.4.1         | MATLAB script                                                        | 44 |  |  |

|              |                                   | 6.4.2         | Software implementation in C++                                       | 46 |  |  |

|              |                                   |               | 6.4.2.1 Profiling the C++ Implementation                             | 49 |  |  |

|              |                                   | 6.4.3         | Hardware implementation                                              | 49 |  |  |

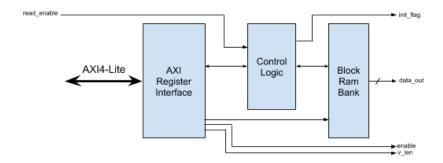

|              |                                   |               | 6.4.3.1 Block Ram Module                                             | 50 |  |  |

|              |                                   |               | 6.4.3.2 Dot Product Module                                           | 52 |  |  |

|              |                                   |               | 6.4.3.3 Output Module                                                | 55 |  |  |

|              |                                   |               | 6.4.3.4 Sequential EMSC HW design                                    | 56 |  |  |

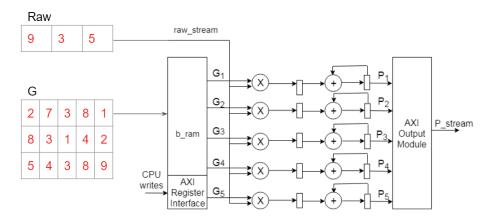

|              |                                   |               | 6.4.3.5 Parallel EMSC HW design                                      | 56 |  |  |

|              |                                   |               | 6.4.3.6 Design Choices                                               | 57 |  |  |

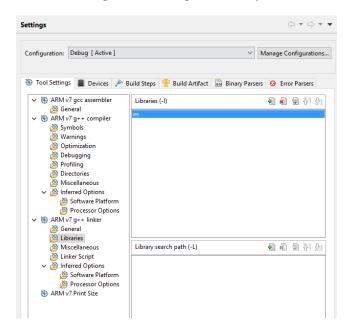

|              |                                   | 6.4.4         | Combining Hardware and Software                                      | 60 |  |  |

|              |                                   |               | 6.4.4.1 Software implementation                                      | 60 |  |  |

|              |                                   |               | 6.4.4.2 Testing the implementations                                  | 64 |  |  |

| 7            | Res                               | 1+a           |                                                                      | 65 |  |  |

| '            | 7.1                               |               | sensor pipeline                                                      | 65 |  |  |

|              | 1.1                               | 7.1.1         | LVDS Deserialiser                                                    | 65 |  |  |

|              |                                   | 7.1.1         | Pixel Order Alignement Module                                        | 66 |  |  |

|              |                                   | 7.1.2 $7.1.3$ | Binning Module                                                       | 67 |  |  |

|              | 7.2                               | EMSC          |                                                                      | 70 |  |  |

|              | 1.4                               | 7.2.1         | Software Implementation                                              | 70 |  |  |

|              |                                   | 1.2.1         | 7.2.1.1 MATLAB analysis of software implementation                   | 10 |  |  |

|              |                                   |               | results                                                              | 70 |  |  |

|              |                                   |               | 7.2.1.2 Profiling                                                    | 74 |  |  |

|              |                                   | 7.2.2         | Hardware Implementation                                              | 75 |  |  |

|              |                                   | 7.2.3         | HW/SW Implementation                                                 | 77 |  |  |

|              |                                   |               | 7.2.3.1 Sequential Design                                            | 77 |  |  |

|              |                                   |               | 7.2.3.2 Profiling                                                    | 79 |  |  |

|              |                                   |               | 7.2.3.3 Parallel implementation                                      | 81 |  |  |

|              |                                   |               | 7.2.3.4 Profiling                                                    | 83 |  |  |

|              |                                   |               | $7.2.3.5  {\rm MATLAB \ analysis \ of \ HW/SW \ Implementation} \ .$ | 83 |  |  |

| 8            | Disa                              | cussion       |                                                                      | 86 |  |  |

| O            | 8.1                               |               | Sensor Pipeline                                                      | 86 |  |  |

|              | 8.2                               | _             |                                                                      | 87 |  |  |

|              |                                   |               |                                                                      | 01 |  |  |

| 9            | Con                               | clusio        | 1                                                                    | 89 |  |  |

| 10           | Fut                               | ure Wo        | ork                                                                  | 89 |  |  |

| $\mathbf{A}$ | A EMSC Software Implementation 91 |               |                                                                      |    |  |  |

| В            | Tute                   | orials                                       | 94  |

|--------------|------------------------|----------------------------------------------|-----|

|              | B.1                    | EMSC software implementation on Zedboard     | 94  |

|              |                        | B.1.1 Building the Hardware in Vivado        | 94  |

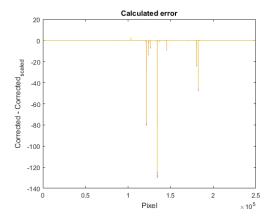

|              |                        | B.1.2 Setting up the SDK Environment         | 94  |

|              |                        | B.1.3 Launching EMSC                         | 95  |

|              | B.2                    | EMSC Software/Hardware co-design on Zedboard | 96  |

|              |                        | B.2.1 Building the Hardware in Vivado        | 96  |

|              |                        | B.2.2 Setting up debug cores                 | 97  |

|              |                        | B.2.3 Setting up the Xilinx SDK              | 98  |

|              |                        | B.2.4 Uploading data to memory               | 98  |

|              |                        | B.2.5 Executing the EMSC code                | 98  |

| $\mathbf{C}$ | $\mathbf{C}\mathbf{M}$ | V2000 Register Overview 1                    | .00 |

| D            | Cub                    | pe DMA register map                          | .03 |

| $\mathbf{E}$ | <b>Λ X</b> 1           | I Dependencies 1                             | .05 |

| Ľ            | E.1                    | Read transaction dependencies                |     |

|              |                        | Write transaction dependencies               |     |

|              | 2.2                    | Title trainaction dependences                |     |

| $\mathbf{F}$ |                        |                                              | 06  |

|              | F.1                    | Deserializer                                 |     |

|              |                        | F.1.1 Design File                            |     |

|              |                        | F.1.2 Test Bench                             |     |

|              | F.2                    | Pixel Order Alignment Module                 |     |

|              |                        | F.2.1 Design File                            |     |

|              | т.                     | F.2.2 Testbench                              |     |

|              | F.3                    | Binning                                      |     |

|              |                        | F.3.1 Design file                            |     |

|              | Б.4                    | F.3.2 Test Bench                             |     |

|              | F.4                    | Control Interface                            | 120 |

| $\mathbf{G}$ | $\mathbf{E}\mathbf{M}$ | · · / · · · ·                                | 20  |

|              | G.1                    | Sequential Implementation                    | 120 |

|              |                        | G.1.1 Software                               | 120 |

|              |                        | G.1.2 Top module design file                 | 125 |

|              |                        | G.1.3 Top module testbench                   | 128 |

|              |                        | G.1.4 Block ram bank design file             | 131 |

|              |                        | G.1.5 Block ram bank testbench               | 133 |

|              |                        | G.1.6 Block ram design file                  | 135 |

|              |                        | G.1.7 Dot product module design file         | 136 |

|              |                        |                                              | 137 |

|              |                        | - "                                          | 137 |

|              |                        | -                                            | 139 |

|              | G.2                    | · · · · · · · · · · · · · · · · · · ·        | 143 |

|              |                        | G.2.1 Software                               | 143 |

| G.2.2  | Top module design file             | 48 |

|--------|------------------------------------|----|

| G.2.3  | Top module testbench               | 53 |

| G.2.4  | FIFO module design file            | 56 |

| G.2.5  | FIFO module testbench              | 58 |

| G.2.6  | Block ram bank design file         | 59 |

| G.2.7  | Block ram design file              | 61 |

| G.2.8  | Dot product module design file     | 61 |

| G.2.9  | Dot product core design file       | 61 |

| G.2.10 | Output Module design file          | 62 |

| G.2.11 | AXI-register interface design file | 63 |

# List of Figures

| 1  | Illustration of Hyperspectral Image capture. [13] 10     |

|----|----------------------------------------------------------|

| 2  | Cube representation of hyperspectral image data          |

| 3  | Data processing pipeline                                 |

| 4  | 3D Render of the prototype. [15]                         |

| 5  | PicoZed Overview                                         |

| 6  | Relation between image sensor and hyperspectral image 15 |

| 7  | Block diagram of the architecture of CMV2000. [4] 16     |

| 8  | Start-up sequence. [4]                                   |

| 9  | Reset sequence. [4]                                      |

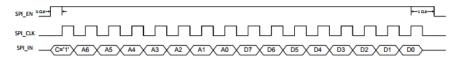

| 10 | Example of SPI write operation. [4]                      |

| 11 | Example of SPI read operation. [4]                       |

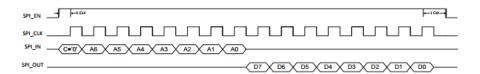

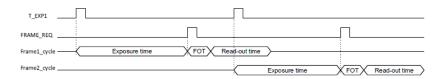

| 12 | Default frame request. [4]                               |

| 13 | A frame request which produce 2 frames. [4]              |

| 14 | Frame request with external exposure. [4]                |

| 15 | LVDS data channel with 12-bit image data. [4] 20         |

| 16 | Timing in 10-bit mode utilising 16-channels. [4] 20      |

| 17 | Timing in 12-bit mode utilising 4-channels. [4]          |

| 18 | Overview of channel outputs. [4]                         |

| 19 | Sample order for 4-channel mode output. [4]              |

| 20 | Scheme for capturing LVDS. [9]                           |

| 21 | Waveform of LVDS capture                                 |

| 22 | OPPOSITE_EDGE mode [17]                                  |

| 23 | SAME_EDGE mode [17]                                      |

| 24 | SAME_EDGE_PIPELINED mode [17]                            |

| 25 | Data eye sample diagram. [7]                             |

| 26 | Block diagram IDELAYE2. [17]                             |

| 27 | Block diagram ISERDESE2. [17]                            |

| 28 | Example when bitslip are needed                          |

| 29 | Block diagram of LVDS receiver. [3]                      |

| 30 | Block diagram of LVDS receiver                           |

| 31 | AXI read/write operations                                |

| 32 | Operation required on the output of LVDS receiver        |

| 33 | Overview of the implemented design                       |

| 34 | LVDS implementation                                      |

| 35 | Block diagram of implementation of LVDS receiver 38      |

| 36 | Block diagram of pipeline from LVDS receiver             |

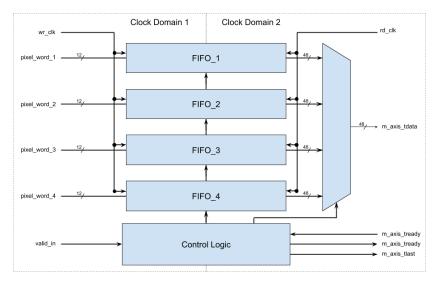

| 37 | Block diagram of implementation                          |

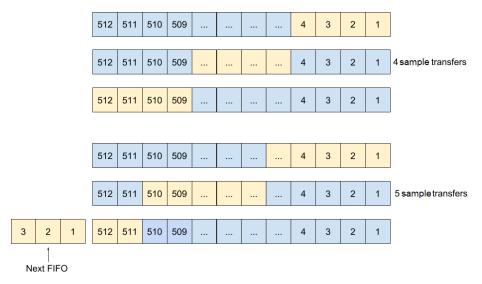

| 38 | Difference between 4 and 5 sample transfer               |

| 39 | Block diagram of all parts connected together            |

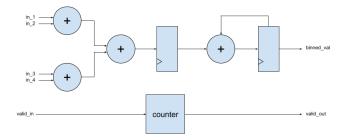

| 40 | Binning module                                           |

| 41 | Cube transformed to raw                                  |

| 42 | MATLAB function of EMSC                                  |

| 43 | Function prototype                                       |

| 44 | Declarations                                                               | 47 |

|----|----------------------------------------------------------------------------|----|

| 45 | Constructing the M matrix                                                  | 48 |

| 46 | Calculating the pseudo-inverse                                             | 48 |

| 47 | Calculate the corrected spectra                                            | 49 |

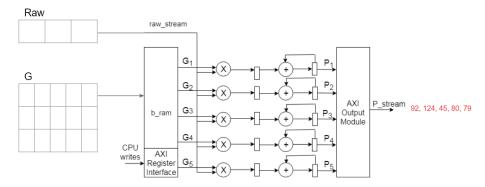

| 48 | Overview of the implemented EMSC accelerator                               | 50 |

| 49 | Block Ram Module Architecture                                              | 51 |

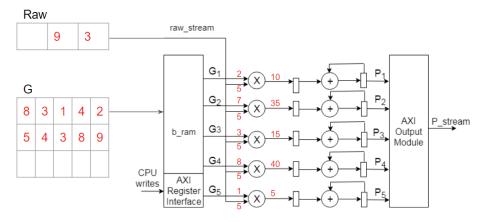

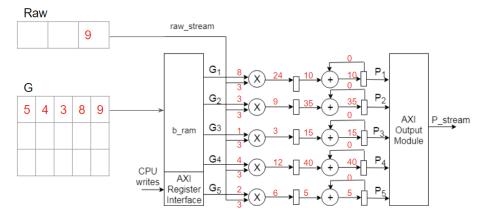

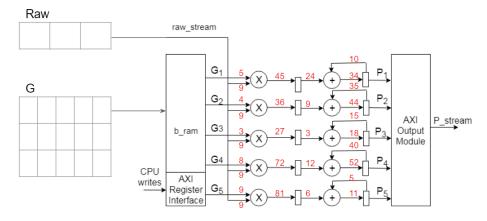

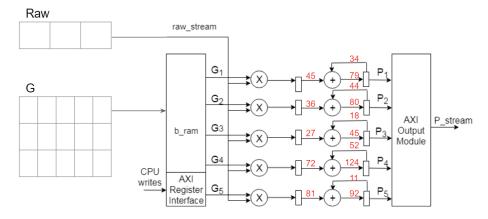

| 50 | Dot product operation, initial step                                        | 52 |

| 51 | Dot product operation, step 1                                              | 53 |

| 52 | Dot product operation, step 2                                              | 53 |

| 53 | Dot product operation, step 3                                              | 54 |

| 54 | Dot product operation, step 4                                              | 54 |

| 55 | Dot product operation, last step                                           | 55 |

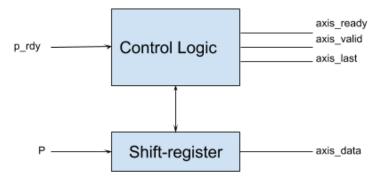

| 56 | Output module overview                                                     | 55 |

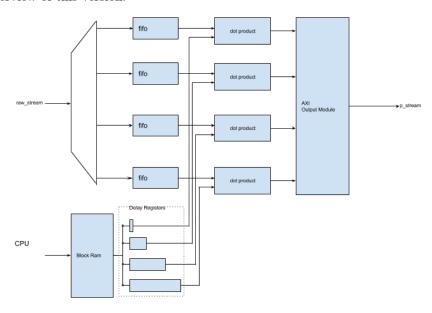

| 57 | Overview of parallel version                                               | 56 |

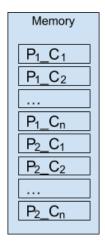

| 58 | Pixels stored in memory. $\mathbf{p}$ is pixel number and $C$ is component |    |

|    | number                                                                     | 57 |

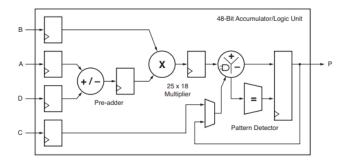

| 59 | Overview of a DSP48E1. [21]                                                | 58 |

| 60 | Overview of the first EMSC implementation                                  | 60 |

| 61 | Function Prototype                                                         | 61 |

| 62 | Initialising the Block Ram Module                                          | 61 |

| 63 | Initialising the Cube DMA                                                  | 62 |

| 64 | Calculate corrected spectra                                                | 63 |

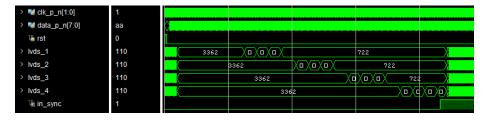

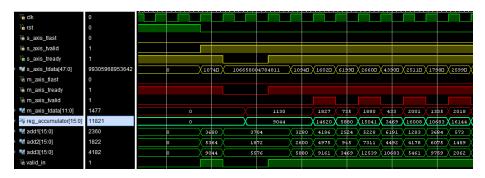

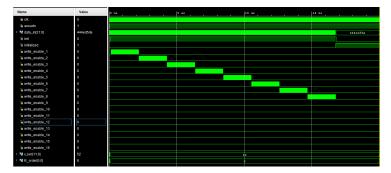

| 65 | Waveform of training state of receiver                                     | 65 |

| 66 | Waveform of transfer state of receiver                                     | 66 |

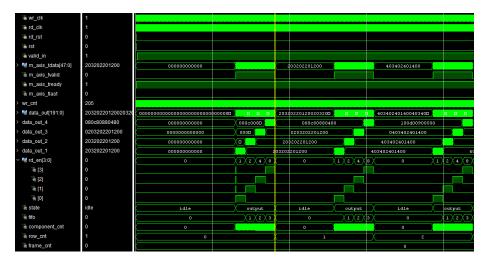

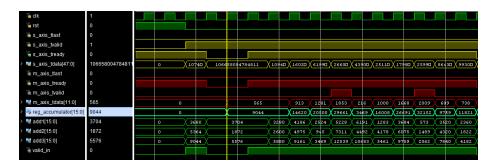

| 67 | Waveform from simulation of Pixel Order Alignement Module                  | 67 |

| 68 | Waveform from simulation Binning Module with Binning Factor                |    |

|    | equal to 4                                                                 | 68 |

| 69 | Waveform from simulation Binning Module with Binning Factor                |    |

|    | equal to 8                                                                 | 68 |

| 70 | Waveform from simulation Binning Module with Binning Factor                |    |

|    | equal to 16                                                                | 69 |

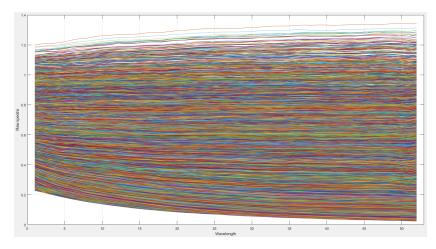

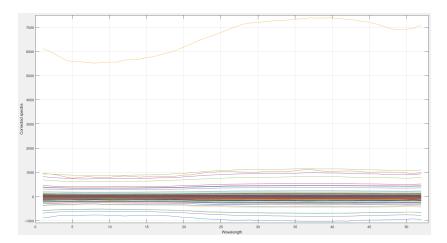

| 71 | Plot of the raw data for the large cube (500x500x52)                       | 71 |

| 72 | Plot of the corrected spectra for the cube produced with MATLAB            | 71 |

| 73 | Plot of the corrected spectra for the large cube produced by soft-         |    |

|    | ware implementation on Zynq                                                | 72 |

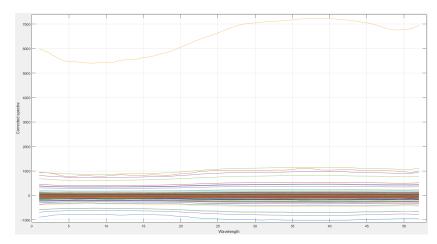

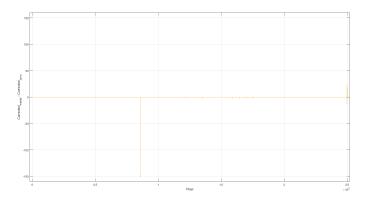

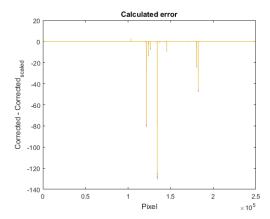

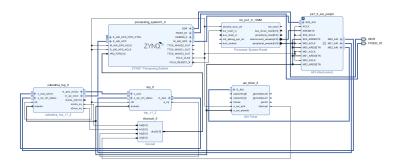

| 74 | Plot of the difference between corrected spectra produced in MAT-          |    |

|    | LAB and in Zynq for the large cube $(500x500x52)$                          | 72 |

| 75 | Plot of the difference between <b>p</b> produced in MATLAB and in          |    |

|    | Zynq for the large cube $(500x500x52)$                                     | 73 |

| 76 | Plot of the difference between <b>G</b> produced in MATLAB and in          |    |

|    | Zynq                                                                       | 74 |

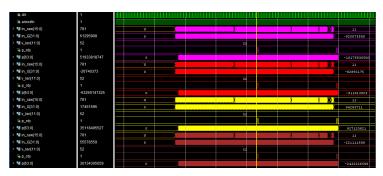

| 77 | Waveform from simulating the Block ram module                              | 76 |

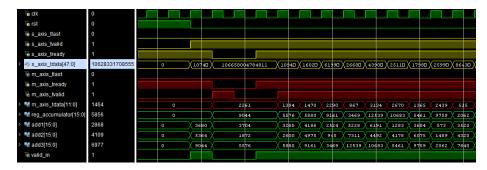

| 78 | Waveform from simulating the Dot Product Module                            | 76 |

| 79 | Waveform from simulating the Output Module                                 | 76 |

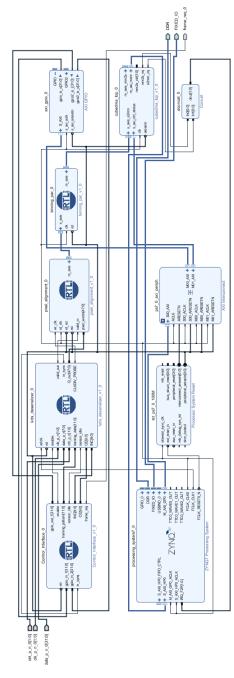

| 80 | Block diagram of design from vivado                                        | 77 |

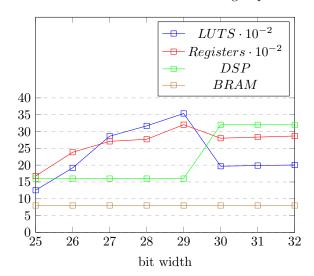

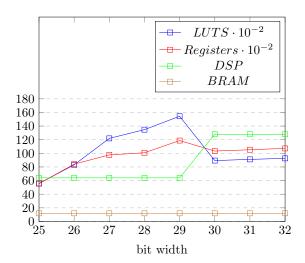

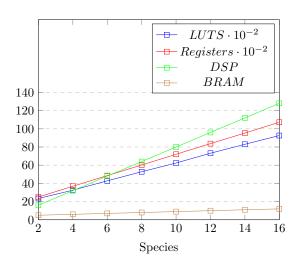

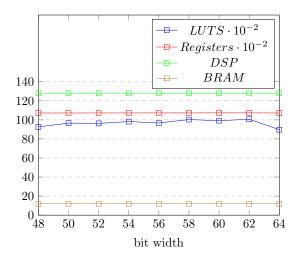

| 81 | Utilization by increasing bit width of G                                   | 78 |

| 82   | Utilization by increasing size of reference spectra           | 79  |

|------|---------------------------------------------------------------|-----|

| 83   |                                                               | 79  |

| 84   |                                                               | 81  |

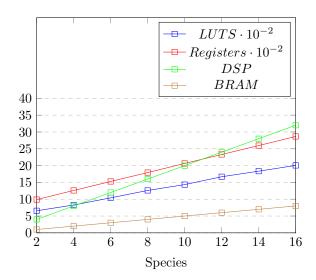

| 85   | Utilization by increasing size of reference spectra           | 82  |

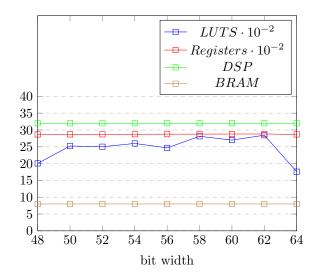

| 86   | Utilization by increasing bit width of P                      | 82  |

| 87   |                                                               | 83  |

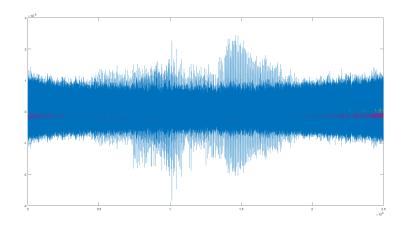

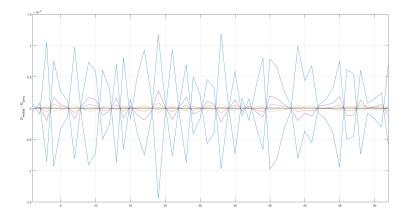

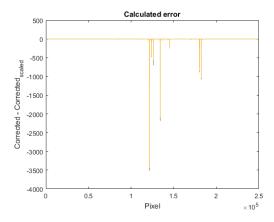

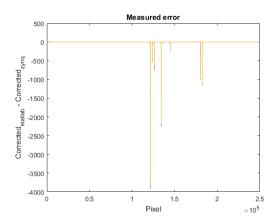

| 88   |                                                               | 84  |

| 89   | Measured results for factor $2^{18}$                          | 84  |

| 90   |                                                               | 85  |

| 91   | Measured results for factor $2^{25}$                          | 85  |

| 92   | 1                                                             | 94  |

| 93   | Ÿ                                                             | 95  |

| 94   |                                                               | 97  |

| 95   |                                                               | 99  |

| 96   | 6 1                                                           |     |

| 97   | O I I                                                         |     |

| 98   | Register overview [4]                                         | 102 |

|      |                                                               |     |

| List | of Tables                                                     |     |

|      |                                                               |     |

| 1    | External inputs/outputs to Image Sensor                       | 17  |

| 2    | Bits of the LVDS control channel [4]                          | 22  |

| 3    | Elements contained in FIFOs                                   | 41  |

| 4    | Description of variables and abbreviations                    | 46  |

| 5    | Block Ram register map                                        | 52  |

| 6    | Description of different used letters and abbreviations       | 59  |

| 7    | Memory Mapping EMSC software                                  | 64  |

| 8    | Utilization report Deserialiser                               | 66  |

| 9    | Utilization report Pixel Order Alignement Module              | 67  |

| 10   | Utilization report Binning Module                             | 69  |

| 11   | Results profiling of C++ implementation of small cube         | 75  |

| 12   | Results profiling of $C++$ implementation of large cube       | 75  |

| 13   | v                                                             | 78  |

| 14   | Results profiling of sequential SW/HW implementation of large |     |

|      | cube                                                          | 80  |

| 15   | Results profiling of the sequential SW/HW implementation of   |     |

|      | small cube                                                    | 80  |

| 16   |                                                               | 81  |

| 17   |                                                               |     |

|      | cube                                                          | 83  |

| 18   |                                                               |     |

|      | cube                                                          | 83  |

| 19   | O 1                                                           | 103 |

| 20   | Cube DMA register map S2MM. [6]                               | 104 |

|      |                                                               |     |

# 3 Introduction

# 3.1 NTNU SMALLSAT

The design problem for this thesis was issued by SmallSat - MASSIVE, a project collaboration between Department of Technical Cybernetics(ITK) and Department of Electronic Systems at the Norwegian University of Science and Technology. This project concerns development of a small satellite equipped with a hyperspectral camera. The information captured by this camera are planned to be used for supporting oceanographic applications. This could for example mean that the satellite captures images around a salmon farm, analyses these images to find indicators of water pollution, algae bloom and other metrics that may inflict the well being and quality of the salmons.

# 3.2 Hyperspectral Imaging

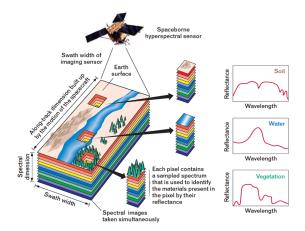

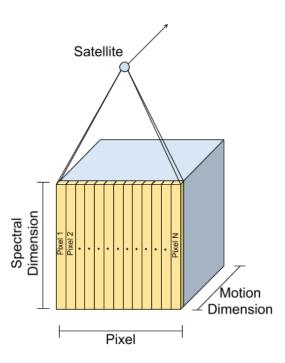

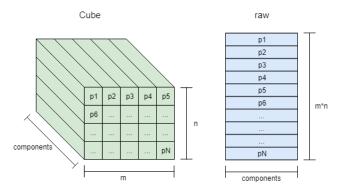

Hyperspectral imaging are a technique where you capture, for each pixel, hundreds or thousands of components spread across the electromagnetic spectrum. Different materials gives unique fingerprints in different spectrums which can be used to analyse and identify the materials captured in the image. This technique where you capture the frequency spectra using a camera is called spectrography [16]. Figure 1 illustrates how these images are captured. As the satellite moves over the scene it starts capturing rows of pixels where each pixel contains multiple components across the electromagnetic spectrum, referenced as *Spectral dimension* in the figure (figure 1). This will form a cube consisting of the number of pixels in one row, times the number of spectral components in one pixel, times the number of rows in the satellite motion dimension. This is illustrated in figure 2. As one probably would understand, this results in large amount of data which will be discussed further in this section.

Figure 1: Illustration of Hyperspectral Image capture. [13]

As mentioned above the satellite that is constructed in the SmallSat project contains a hyperspectral camera able to capture hyperspectral images. In regular photography meant for the human eye, each pixel consists of pixel components in the visible light spectrum, usually long wavelengths (red), medium wavelengths (green) and short wavelengths (blue). This means that if you capture a picture with all channels (RGB), with a resolution of 1920x1080 you will have 2,073,600 pixels, each with 3 components, giving a total of 6,220,800 components. Each component is represented with a given number of bits called bit depth, giving the resolution of how many possible values for each component. For example, using a bit depth of 12 bits gives  $2^{12} - 1 = 4095$  different representations, giving the example above a size of 6,220,800 components x 12 bit, or around 9.3 MB.

Figure 2: Cube representation of hyperspectral image data.

The example above demonstrates how large a digital image from regular photography becomes based on different choices or settings that are used. Even using only 3 components for each pixel, one get large amount of data if you increase the resolution and bit depths. For a Hyperspectral image this impacts the size even more due to hundreds or thousands of components per pixel. Adapting the RGB example above for a hyperspectral image containing 1000 components we get.  $1920 \times 1080 \times 1000 = 2,073,600,000$  components across all spectras, further giving  $2,073,600,000 \times 12$  bit = 24,883,200,000 bits, or around

3.1 GB. For a modern computer where one usually have several TB of storage and powerful CPUs and GPUs available, this amount of data would be handled with minimal effort. However, for a small satellite where the data is to be sent back to earth through radio links, a energy expensive operation, it should be as minimal as possible to save both time and energy. Therefore a lot of data processing will have to be executed on-board the satellite. This thesis will look at this on-board data processing pipeline from the capture of image data from the image sensor and storing this data directly to memory or via compression algorithms or other data processing algorithms. In addition, this thesis will present a data processing algorithm called *Extended Multiplicative Signal Correction*, and how this algorithm may be implemented in hardware.

#### 3.3 Main contributions

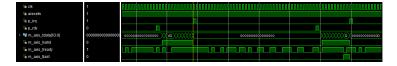

The main contributions of this thesis are achieved in communication between different parts of the hyperspectral payload, in particular building communication modules establishing data streaming between image sensor and memory. This consists of a hardware implementation of a LVDS receiver consisting of a Descrializer and a Pixel Order Alignment Module, the former a serial-to-parallel converter for the LVDS data from the image sensor and the latter a module to organise the order of this data before it is processed or stored in memory. Further a Binning Module that merges either 4, 8 or 16 data samples into one sample with an average value of the merged samples. Additionally the thesis presents an algorithm, Extended Multiplicative Signal Correction and proposals to how this may be implemented to execute on a Zyng-7000 platform. This includes a pure software implementation, and a SW/HW co-design implementation. The pure software implementation was analysed to find what parts would benefit the most being accelerated in hardware, which resulted in the SW/HW co-design. The thesis presents the process of transforming a software into a software/hardware co-design which may be perceived as a complicated process. Further the SW/HW co-design was analysed and compared to the software version both in terms of speed and precision. Both implementations was analysed and compared to a MATLAB script which was considered the solution of a correct EMSC operation. Additionally a proposal to increase parallelism of the SW/HW co-design was implemented which in theory would increase speedup by four times. Tutorials of how to use both the software and software/hardware co-design was created and can be found in the Appendix together with all design files and testbenches used in the project. To be able to achieve these implementations knowledge had to be built around the design tools, Vivado and Xilinx SDK together with the AXI-protocol, Cube DMA and the Image Sensor which is used in these implementations.

# 4 Data Processing Pipeline

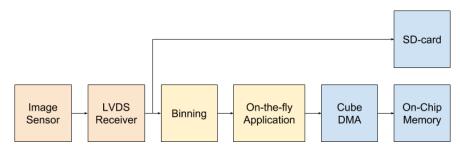

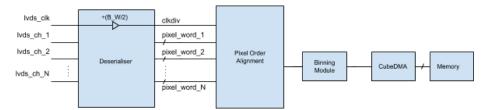

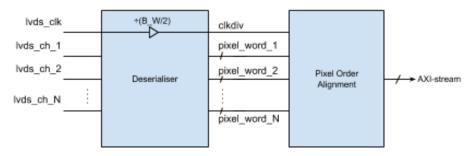

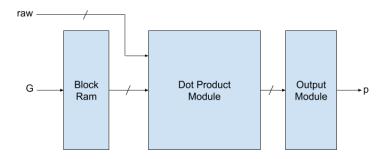

Figure 3 shows the main parts of the data processing pipeline mentioned in the previous section. The goal is to implement a Low Voltage Differential Signal (LVDS) receiver capable of capturing the data transmitted from the image sensor. On the output of the LVDS receiver there will be a stream of pixel components that either can be stored directly to a SD-card or sent further through a pipeline consisting of Binning, some On-the-fly Application and then stored on the on-chip memory by a Direct-Memory Access (DMA). Binning is a preprocessing technique and will be introduced later in this section (section 4.8). On-the-fly Applications simply means different algorithms that is necessary for the application. An example of this is Extended Multiplicative Signal Correction (EMSC) which will be presented further on in this paper (section 5).

Figure 3: Data processing pipeline

## 4.1 Prototype

The prototype produced for this project contains 3 major parts. A carrier board, a PicoZed and an image sensor with associated optics. Shown in figure 4 is a rendering from a 3D model of the prototype. The green board on the left side is the PicoZed, the microscope looking part on the right side is the optics mounted on top of image sensor and the black bottom layer board which is connected to both the optics and the PicoZed is the carrier board.

Figure 4: 3D Render of the prototype. [15]

# 4.2 Carrier Board

The carrier boards main task, is to connect the image sensor to the correct pins of the PicoZed, distribute the main power input into different voltage levels required by the different parts of the system, as well as providing a JTAG, USB-UART and SD card interface. The carrier board is powered through a 2.1 mm/5.5 mm barrel jack connector and this input is rated at 5-14.5 V at 6 A, meaning that any AC/DC adapter which fulfils these requirements may be used. The board contains 5 regulators, 1 x 5 V SMPS(switching mode power supply), 2 x 1500 mA LDO(Low-dropout) regulator and 2 x 500 mA LDO regulator providing the required voltages.

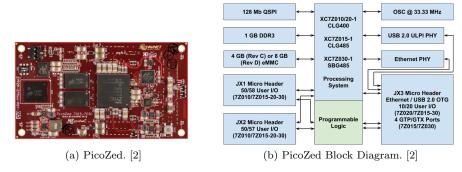

#### 4.3 PicoZed

The PicoZed from AVNET is a so called SOM (System-On-Module) based around the Xilinx Zynq-7000 All Programmable (AP) SoC. Figures 5 a-b show the PicoZed and a block diagram of the architecture within. As can be seen from the Processing System (PS) of the block diagram there are multiple versions of the PicoZed containing different versions of the Xilinx Zynq. The PicoZed used in this prototype is equipped with the Xilinx Zynq-7030 containing a Dual-core Arm Cortex-A9, and a Programmable logic (PL) with 125 K programmable logic cells and 78,600 LUTs for briefly mentioning some of the specs.

Figure 5: PicoZed Overview

## 4.4 Image Sensor

The image sensor used is the CMV2000v3 from CMOSIS. A CMOS image sensor with a resolution of 2048x1088, global shutter and a maximum frame rate of 340fps at a bit width of 10 bits. The image sensor is aimed for applications such as 3D-imaging, Machine Vision, Bar and 2D code, Motion capture and more, and should also be applicable for Hyperspectral Imaging given the necessary camera lens. The sensor is soldered directly on the carrier board and will be connected to the PicoZed through a LVDS interface for reading out data from

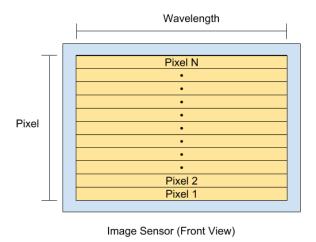

the image sensor, and a Serial Peripheral Interface (SPI) for programming the control registers of the image sensor. Figure 6 shows how the image sensor corresponds to the hyperspectral application. Each row of the image sensor correspond to one pixel and each column a spectral component. Using the numbers from the resolution gives, for each frame, a max of 1088 pixels, each with 2048 spectral components or samples.

Figure 6: Relation between image sensor and hyperspectral image

#### 4.4.1 Image Sensor Architecture

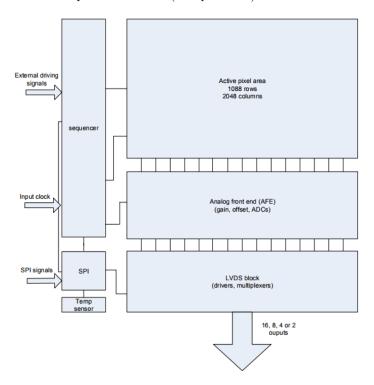

The architecture of the Image Sensor is illustrated in the block diagram shown in Figure 7. In the upper right corner of the figure we see the Active Pixel Area, this is a square consisting of 1088 rows and 2048 columns. In the hyperspectral application each row correspond to a pixel and each column to a spectral component. For clarification, the term sample is used with the same meaning as a pixel component. The image sensor has a global shutter meaning that all of the samples are exposed at once. When the samples have been exposed the specific amount of time defined by the exposure time, the analog values collected are written out row by row to the Analog front end shown in the figure. This block amplifies the sample values with a user defined gain and converts this amplified analog signal to a digital value, either 10-bit or 12-bit. Further on this digital representation of the samples is sent to the LVDS block. In this block the samples are converted into standard LVDS, defined by the TIA/EIA-644A [10], which can be transferred out of the image sensor using a LVDS interface, consisting of 18 LVDS channels; 1 clock channel, 1 control channel and 16 data channels. On the upper left side of the figure is the Sequencer. This block generates the required control signals to operate the sensor, based on the external input signals and the values programmed in its registers.

The *SPI* is used to read/write the registers in the *Sequencer* and to read the values from the Temperature sensor (*Temp sensor*).

Figure 7: Block diagram of the architecture of CMV2000. [4]

#### 4.4.2 Interfacing the Image Sensor

The Image sensor contains 10 external I/O pins which are used to control and configure the sensor from an external source. The I/O pins are as shown in table 1.  $CLK\_IN$  is the master clock input with a frequency equal to 10 or 12 times lower than the rate of the output data, depending on the bit width that is chosen. As the maximum output data rate is 480 Mbps the CLK\_IN may at a maximum be 48MHz at 10-bit and 40MHz at 12-bit. The minimum frequency is 5 MHz and all frequencies in between may be used.  $LVDS\_CLK\_IN\_N/P$  is a LVDS input clock that can be used to define the output rate of the LVDS interface of the image sensor. This signal is optional as the image sensor contains an internal PLL (Phase Locked Loop) which is able to generate this clock signal internally. The PLL is set to generate this clock signal by default, also the PLL has to be disabled to use the external LVDS input clock signal.  $SYS\_RES\_N$  is the system reset and is active low. This resets the sequencer and must be active during start-up. The  $FRAME\_REQ$  initiates the capture of a frame and can be considered the trigger if we compare the sensor to a handheld camera.

$SPI\_IN$  and  $SPI\_OUT$  is the data input/output pins for the SPI and is used to program and read values from the image sensors internal registers.  $SPI\_EN$  and  $SPI\_CLK$  is the enable pin and clock pin respectively for the SPI.  $T\_EXP1$  and  $T\_EXP2$  are pins used in external exposure mode which will be described later in this section.

| Signal name  | Description                |

|--------------|----------------------------|

| CLK_IN       | Master input clock 5-48MHz |

| LVDS_CLK_N/P | LVDS clock, 50-480MHz.     |

| SYS_RES_N    | System reset, active low   |

| FRAME_REQ    | Frame request              |

| SPILIN       | SPI data input             |

| SPLOUT       | SPI data output            |

| SPLEN        | SPI enable                 |

| SPI_CLK      | SPI clock                  |

| T_EXP1       | External exposure          |

| T_EXP2       | External exposure in HDR   |

Table 1: External inputs/outputs to Image Sensor

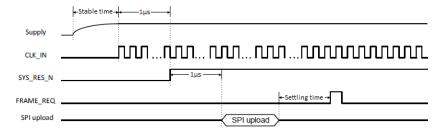

The datasheet for the image sensor describes some sequences in the signal flow which are recommended to prevent incorrect behaviour. These sequences are associated with the start-up of the sensor or when performing a reset. Figure 8 shows the start-up sequence. The master clock  $CLK\_IN$  should be started after the input supply is stable. After  $1\mu s$  the  $SYS\_RES\_N$  is set high, forcing the system out of reset state. As start-up may be a suited point to configure the image sensor, the SPI uploads should take place  $1\mu s$  after the system exits the reset state. The system then requires some settling time before any frames may be requested. The duration of this settling time varies and according to the datasheet the main factor for this is changes to the ADC gain. For example changing the ADC gain from default value to the maximum value, which is the worst case scenario, may increase the settling time to 20ms.

Figure 8: Start-up sequence. [4]

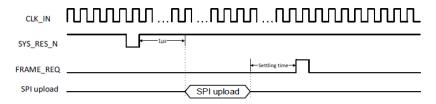

The reset sequence is similar to the start-up sequence except the power supply is stable and that the clock is already running. Figure 9 illustrates this

situation. The  $SYS\_RES\_N$  is sampled at rising edge of the  $CLK\_IN$  and should therefore be at least one clock period to make sure of detection.

Figure 9: Reset sequence. [4]

#### 4.4.3 SPI

As mentioned in the architecture of the image sensor, SPI is used to read and write the registers of the sequencer as well as the temperature sensor. A brief overview of what registers can be programmed and a description of these can be found in Appendix C. Writing to a register in the image sensor over SPI is shown in figure 10.

Figure 10: Example of SPI write operation. [4]

To initiate a write, the *SPI\_EN* is set high, half a period before sampling the first data bit on *SPI\_IN*, and stays high until one clock period after sampling the last data bit as shown in the figure. The 16 bits forming the write consists of one control bit, which is the first bit in the sequence. It tells if it is a write ('1') or a read ('0'). Then there is 7 bits forming the register address. The last 8 bits contains the data that is to be written to this register. For a read, a sequence of 8 bits has to be transferred. The control bit indicating a read ('0') and 7 bits forming the address of the register to read. Then, the clock cycle after the last address bit is sampled, the data contained in this register is outputted on the *SPI\_OUT*. The read operation is shown in Figure 11.

Figure 11: Example of SPI read operation. [4]

In case of multiple registers required to be written or read, this can be done

in burst transfers, meaning that after the last data bit of a read or write has been sampled, a new operation may start right away. Some of the registers may not be updated, unless the camera is currently in IDLE time, meaning when the sensor is not capturing or reading out frames. Changing values in the register while a frame is captured may create unwanted effects on the image, so this should be avoided.

#### 4.4.4 Requesting Frames

Requesting frames can be initiated by sending a pulse at FRAME\_REQ. By default the image sensor runs through the process of exposing the samples and read out 1 frame, this is illustrated in figure 12. The exposure process consist of the exposure time where the samples are exposed followed by a frame overhead time (FOT). When the FOT is completed the sensor is ready to initiate the next frame request. This means that 1 pulse on FRAME\_REQ produces 1 frame.

Figure 12: Default frame request. [4]

However, this process may be configured in several ways. Firstly, the user can program the number of frames the image sensor should produce when  $FRAME\_REG$  is pulsed. This is done by programming the  $Number\_frames$  (Figure 97) register using the SPI interface. Figure 13 shows an example of how this works when the image sensor is programmed to produce 2 frames when receiving a request.

Figure 13: A frame request which produce 2 frames. [4]

It should be noticed that the read-out of the previous frame is executed in parallel with the exposure of the current frame. This means that as long as the read-out time is less than the exposure time the total time to produce a frame, which directly influences the frame rate is only affected by the exposure time.

Both of the examples presented above utilise the internal exposure mode of the image sensor. This simply means that the duration of the exposure time is programmed as a value by the user within the image sensor. However, the image sensor also contains another exposure mode called external exposure which lets the user externally program the exposure time, changing the role of the  $FRAME\_REQ$ . In this exposure mode a new pin is introduced,  $T\_EXP1$ . This pin is used to start the exposure time of the frame, and  $FRAME\_REQ$  is

now used to end the exposure of the frame and start the read-out of the frame. This is illustrated in figure 14.

Figure 14: Frame request with external exposure. [4]

#### 4.4.5 Reading data from the sensor

Transfer of the image data from the sensor is done through the 16 data channels of the LVDS. In addition to these channels the LVDS got a control channel and a clock channel. The clock channel outputs a clock which are synchronous to the data outputted on the data channels. The clock is DDR (double data rate), meaning that sampling of data needs to be done on both rising and falling edge of the clock. An example of this is shown in Figure 15 where a 12-bit image data is sent over one of the LVDS data channels. The least significant bit (LSB) is sent first.

Figure 15: LVDS data channel with 12-bit image data. [4]

Data is read out from the sensor in bursts of 128 samples per channel. Between these bursts there are an overhead period that equals one period of the master input clock. If 16 of the data channels are utilised, one row will be read out for each burst. (16 channels x 128 samples = 2048). This correspond to one pixel in terms of the hyperspectral image. This is the maximum output rate and results in a frame rate of 340 fps. Figure 16 shows this behaviour for one channel. Here one can see the overhead (OH) between bursts and that one row is transferred each burst.

Figure 16: Timing in 10-bit mode utilising 16-channels. [4]

Only the 10-bit mode is compatible with transferring across 16 channels. If 12-bit mode is desired, a maximum of 4 channels may be used, giving a frame

rate of 70 fps. This is due to a restriction from the ADC, because the conversion takes 4 times longer to complete. This means that in 12-bit mode, 4 bursts is required to output a whole row (pixel). (4 channels x 128 samples x 4 burst = 2048). This behaviour is shown in figure 17, 4 burst is required to transfer one row.

Figure 17: Timing in 12-bit mode utilising 4-channels. [4]

Figure 18 shows how the outputs behave depending on the chosen number of channels. In 16 channel mode, each output represent one specific channel. However, if less than 16 channels are utilised the outputs are multiplexed and the same channel is represented over multiple outputs as illustrated in the figure (Figure 18). Operating in the 4 channel mode, it can be seen that all 16 channels is divided in four groups, where each group outputs the same channel. As multiple outputs for the same channel may be excessive and active outputs are power consuming, the image sensor contains a feature where the user may disable outputs that are not used. The datasheet for the image sensor states that disabling unused channels is the main source for power saving in the image sensor. Reducing from 16 to 4 outputs, may save up to 33% of the power, or 216mW. Each output consumes approximately 18 mW when enabled.

| MUX | OUT  | OUT  | OUT  | OUT  | OUT  | OUT  | OUT  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

| to  | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

| 16  | CH1 | CH2 | CH3 | CH4 | CH5 | CH6 | CH7 | CH8 | CH9 | CH10 | CH11 | CH12 | CH13 | CH14 | CH15 | CH16 |

| 8   | CH1 | CH1 | CH3 | CH3 | CH5 | CH5 | CH7 | CH7 | CH9 | CH9  | CH11 | CH11 | CH13 | CH13 | CH15 | CH15 |

| 4   | CH1 | CH1 | CH1 | CH1 | CH5 | CH5 | CH5 | CH5 | CH9 | CH9  | CH9  | CH9  | CH13 | CH13 | CH13 | CH13 |

| 2   | CH1 | CH9 | CH9  | CH9  | CH9  | CH9  | CH9  | CH9  | CH9  |

Figure 18: Overview of channel outputs. [4]

Figure 19 shows the ordering of the samples at the output when utilising 4 channels. It can be seen that one pixel, consisting of 2048 samples are divided in 4 sub-rows, the first sub row is outputted at channel 1 through 4 bursts, the second sub row on channel 2 and so on.

| Channel 1 (IDLE) | Sample 0 to 127     | Sample 128 to 255   | Sample 256 to 383          | Sample 384 to 511   |

|------------------|---------------------|---------------------|----------------------------|---------------------|

| Channel 5 (IDLE) | Sample 512 to 639   | Sample 640 to 767   | Sample 768 to 895          | Sample 896 to 1023  |

| Channel 9 (DLE)  | Sample 1024 to 1151 | Sample 1152 to 1279 | Sample 1280 to 1407        | Sample 1408 to 1535 |

| Channel 13 DLE   | Sample 1536 to 1663 | Sample 1665 to 1791 | Sample 1792 to 1919  Bow 1 | Sample 1920 to 2047 |

Figure 19: Sample order for 4-channel mode output. [4]

As mentioned the LVDS has a control channel. This channel is mainly used to achieve timing and synchronisation at the receiver side. Table 2 shows an

description of the 12 bits forming the control word transferred on this channel. Only the three first signals are required to know when the data is valid, the rest of the signal is pure informational. The DVAL signal is always high during a burst of valid data and low between bursts. The LVAL is high during the readout of a whole row, meaning that it is only low between bursts that separates the read-out of a row. Finally the FVAL is high during the read-out of a whole frame and is set low between bursts that separates frames. This means that DVAL can be used to identify when there is a valid burst of pixel data on the output. The LVAL is used to identify when a row has completed read-out and a new row is initiated and the FVAL the same for frames.

| Bit  | Function | Description                                                   |

|------|----------|---------------------------------------------------------------|

| [0]  | DVAL     | Indicates valid pixel data on the outputs                     |

| [1]  | LVAL     | Indicates validity of the read-out of a row                   |

| [2]  | FVAL     | Indicates validity of the read-out of a frame                 |

| [3]  | SLOT     | Indicates overhead period before 128-sample burst             |

| [4]  | ROW      | Indicates overhead period before the read-out of a row        |

| [5]  | FOT      | Indicates when the sensor in in FOT                           |

| [6]  | INTE1    | Indicates when samples of integration block 1 are integrating |

| [7]  | INTE2    | Indicates when samples of integration block 2 are integrating |

| [8]  | '0'      | Constant zero                                                 |

| [9]  | '1'      | Constant one                                                  |

| [10] | '0'      | Constant zero                                                 |

| [11] | '0'      | Constant zero                                                 |

Table 2: Bits of the LVDS control channel [4]

## 4.5 LVDS receiver

#### 4.5.1 Design Criterias

According to the requirements from the NTNU Smallsat the Image Sensor is desired to be used in 12-bit mode utilising 4 of the LVDS data channels. Therefore the focus will be on this mode of operation when presenting the existing solution in this section, but also when presenting the implementations that was done in this thesis in the *Method* section.

#### 4.5.2 Simple Deserialiser

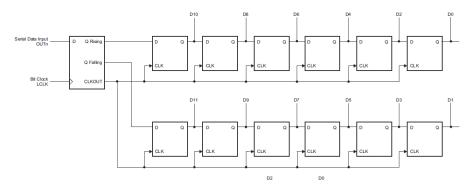

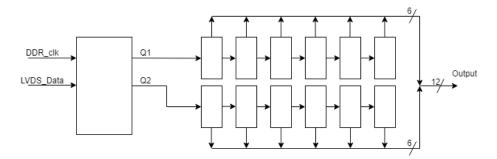

In the paper *Understanding Serial LVDS Capture in High-Speed ADCs* [9] a scheme for capturing a LVDS signal on a receiver is presented. It is shown in figure 20 and consists of a double data rate (DDR) flip flop which is fed into a shift register.

Figure 20: Scheme for capturing LVDS. [9]

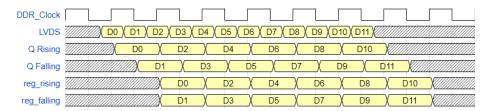

At the Q Rising and Q Falling in Figure 20, the values captured on the rising and falling edge of LVDS clock (Bit Clock) is outputted. Because both the registers connected to the Q Rising and Q Falling are connected to the same clock source CLKOUT they are updated at the same time. This means that the output Q Falling is changing half a clock period before it is captured into the register. This re-latches the falling edge values and synchronises the values captured at rising and falling edge. Figure 21 illustrates the mechanism of this design in a waveform. The LVDS signal is sampled at rising and falling edge of the  $DDR\_Clock$ . The inputs to the registers  $reg\_rising$  and  $reg\_falling$  samples the Q Rising and Q Falling at the same rising edge, making these two inputs synchronised.

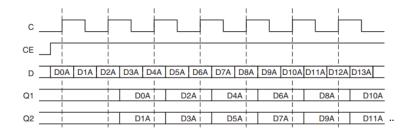

In Xilinx user guide 7 Series FPGAs SelectIO Resources [17] a DDR register called Input DDR (IDDR) was found to be available on all 7 series FPGAs. According to the user guide this register has three modes of operation. OP- $POSITE\_EDGE$ ,  $SAME\_EDGE$  and  $SAME\_EDGE\_PIPELINED$ . The  $OPPO-SITE\_EDGE$  mode outputs the values of Q1 and Q2 as they are sampled. This

Figure 21: Waveform of LVDS capture.

means that Q1 is set at rising edge and Q2 at falling edge. This is illustrated in figure 22.

Figure 22: OPPOSITE\_EDGE mode [17]

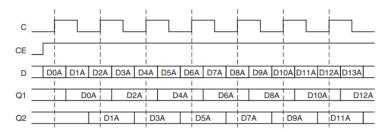

$SAME\_EDGE$  sets Q1 and Q2 at rising edge starting from the first rising edge. However because the first falling edge has not yet been sampled at the first rising edge the values of the rising edge and falling edge will not be synchronised. This means that the value of the first falling edge will not be outputted on Q2 before the second rising edge. This behaviour is shown in Figure 23.

Figure 23: SAME\_EDGE mode [17]

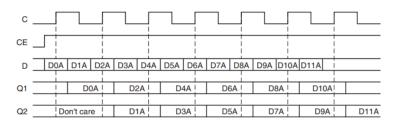

The last operation mode,  $SAME\_EDGE\_PIPELINED$ , was chosen for this implementation. In this mode the output of the first rising and falling edge is set at the next rising edge. In this case the outputs will be synchronised as pairs and this makes the rest of the design easy to implement. Figure 24 shows how this mode operates.

However, as LVDS signals are operating at a high speed, they are vulnerable to latencies. In Serial LVDS high-speed ADC interface [5] the author explains

Figure 24: SAME\_EDGE\_PIPELINED mode [17]

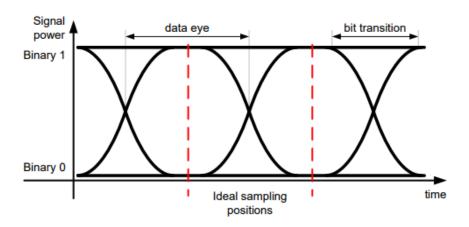

why this is a problem and why the simple scheme for capturing LVDS shown in Figure 20 in many cases is not sufficient enough. As both the LVDS data and clock are sent over independent LVDS channels it is important that these arrive synchronised enough at the receiver side. This is important so the receiver does not sample the data during a transition. However, as the data and clock channels typically experience different amount of delays this is not as simple as one should hope. In an ideal world the data transitions on the LVDS would occur instantly and the risk of sampling the data during a transitions is not present. However, in the real world this is not the case and Figure 25 illustrates this. The moment when data is stable on the channel and can be read is called the *Data Eye*, and is the desired place to sample the data, as shown with red dotted lines in the figure. If sampling is done inside a *bit transition* the result is unpredictable and may cause a corrupt sample.

Figure 25: Data eye sample diagram. [7]

Figure 25 shows why the LVDS capturing method shown in figure 20 may not work. It is not able to synchronise the data and clock channels if they arrive with a skew. Another approach utilising primitives *IDELAYE2* and *IS-ERDESE2* from Xilinx is found. Starting with a closer look at these primitives,

this approach will now be presented.

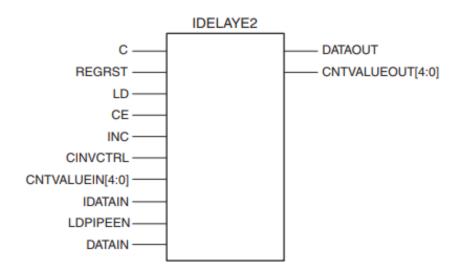

#### 4.5.3 IDELAYE2

Figure 26 shows the block diagram of the IDELAYE2 primitive which is a programmable delay block. It has 4 different operation modes, FIXED, VARI-ABLE,  $VAR\_LOAD$  and  $VAR\_LOAD\_PIPE$ . Modes FIXED and VARIABLE will be used and therefore these operations will be presented.

Figure 26: Block diagram IDELAYE2. [17]

In the FIXED mode the block is simply programmed with a fixed delay. This passes the input to the output with a delay corresponding to this fixed value. In the VARIABLE mode the delay can be varied. By assigning a '1' or '0' on the INC input together with a '1' on the CE (enable) the delay will be increased or decreased respectively. This increase or decrease has a unit called taps. There are in total 31 taps, and the resolution of these are decided by another module IDELAYCTRL. This is a independent module but has to be present in the same clock region as the IDELAYE2 to calibrate the taps. This module has two inputs REFCLK, RST and one output RDY. The frequency of the clock signal inputted on the REFCLK decides the tap precision. Frequency of 200 MHz gives a tap precision of  $\sim 75ps$ .

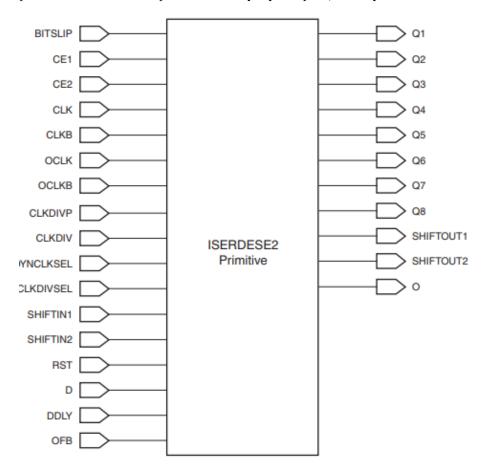

#### 4.5.4 ISERDESE2

Figure 27 shows a block diagram of the other Xilinx primitive, *ISERDESE2*. This is a serial-to-parallel converter which is suited to serialise the LVDS channels from the image sensor. The serial stream are inputted at either *D* or *DDLY* depending on if the stream comes from a FPGA IOB resource or an *IDELAYE2*.

In this case it will be connected to the delay module, *DDLY* will be used. The parallel data will be outputted at the Q1-Q8 outputs, with Q1 MSB.

Figure 27: Block diagram ISERDESE2. [17]

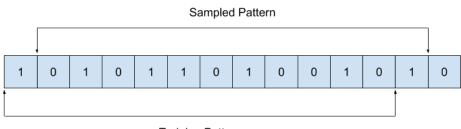

This primitive can be operated in SDR and DDR mode and each module are able to descrialise up to 8 bits. However, two modules can be chained into outputting 10 or 14 bits. As the image sensor is capable of outputting 12 bits this it is not compatible with the way these primitives are meant to be used according to the Xilinx documentation [17], but a workaround was found in Serial LVDS High-Speed ADC Interface [5]. In this paper two ISERDESE2 modules are used in SDR mode. One for capturing the rising edge values and one for capturing the falling edge values of the DDR clock. Two designs, one using the primitives according to the Xilinx documentation and the other one using the workaround mentioned above will be presented later in this section. It should also be mentioned that the ISERDESE2 primitive has a feature to align the bits captured. As it can be hard to synchronise the sampling of the

data words initially, *ISERDESE2* has a input called *BITSLIP* which helps with this. Lets assume that we have a training pattern of 2770 (b"1010 1101 0010") that are inputted to the primitive as shown in figure 28. However, the receiver may have captured another order of the bits than is expected. By using the *BITSLIP* the receiver *slips* bits to achieve the correct order. In SDR mode this is done by shifting the order to left by one, in DDR it is alternating between shift right by one and shift left by three.

Training Pattern

Figure 28: Example when bitslip are needed.

#### 4.5.5 Existing LVDS receiver designs

Two different designs utilising the described primitives suitable for the application in this paper were found.

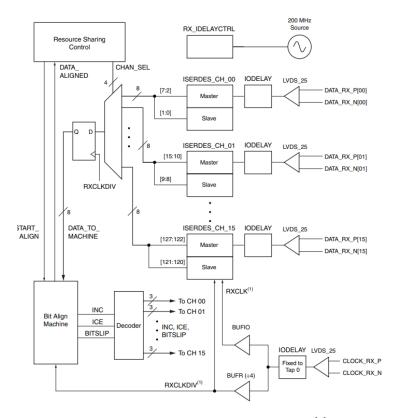

**4.5.5.1 Design 1** First in "16-Channel, DDR LVDS Interface with Per-Channel Alignment" [3] an implementation for a 16 channel DDR LVDS receiver is presented. This implementation is designed for data words of 8-bit but could be adapted to a 10 bit version to be applicable with the image sensor. However, this design is not directly compatible if the image sensor is operating in the 12 bit mode. Figure 29 shows a block diagram of this implementation. The LVDS signals are inputted on the right side, through the *DATA\_RX* and the clock through the *CLOCK\_RX*. All LVDS inputs are converted to a single ended signal and fed into a *IODELAY* primitive.

The clock signal delay has a fixed value and the data signal delays are variable and are configured by the *Bit Align Machine* to make sure the sampling occurs within the data eye of the signals. From the delay modules the signals are converted from serial to parallel data in the *ISERDES* primitive. As the *ISERDES* blocks used in this design is restricted to 6-bit, two of this primitives has to be connected in a Master-Slave chain to be able to process 8 bits. The *ISERDESE2* available in the Zynq-7000 series, can process 8-bit data before a chain of two modules are needed. The *Bit Align Machine* monitor the outputs of the *ISERDES* modules to configure the delay blocks as well as bit ordering by using the *BITSLIP* functionality mentioned before. To avoid implementing a *Bit Align Machine* for every channel, a *Resource Sharing Control* block is

Figure 29: Block diagram of LVDS receiver. [3]

distributing access to the *Bit Align Machine*. At the top of the figure there is an independent *IDELAYCTRL* primitive which is used to calibrate the *taps* for all of the *IODELAY* modules. It should also be mentioned that the clock from the LVDS clock channel is divided into two clocks. One with the same frequency as the LVDS clock (*RXCLK*), and one with the same period as the bit width, which in this case is the LVDS clock divided with 4 (*RXCLKDIV*). *RXCLKDIV* is used by the *ISERDES* to output the parallel data as well as to sample the *BITSLIP* input.

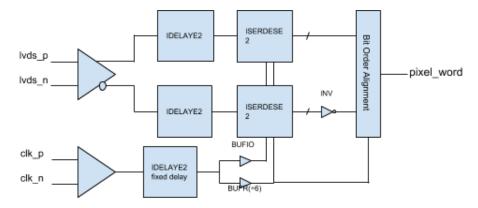

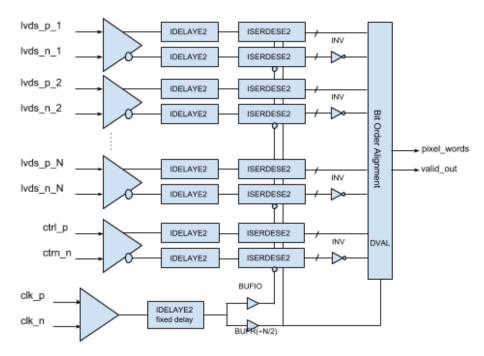

**4.5.5.2 Design 2** The next design is taken from *Serial LVDS High-Speed ADC Interface* [5] combined with the knowledge of users on Xilinxs own forum. This design was created as a workaround to achieve a 12-bit LVDS receiver as this is not supported by the primitives according to Xilinx documentations [17]. The interesting part of this design is how the *ISERDESE2* primitive is used. Figure 30 illustrates this for one LVDS data and clock channel.

The idea with this design is to have both *ISERDESE2* primitives in SDR and to use one for sampling rising edge values and one for sampling the falling

Figure 30: Block diagram of LVDS receiver.

edge values. It can be seen in the figure that instead of converting the signal into a single ended signal, it keeps the differential form where the p and n side are inputted directly to two different IDELAYE2 primitives. From here they are sampled in the ISERDESE2 blocks, the p side on rising edge and the n side on falling edge of the clock. It should be mentioned that the lower ISERDESE2 block in the figure requires an inverted clock input. This way of sampling the data will produce an inverted result from the ISERDESE2 on the n-side and it is therefore required to invert the output. In the end the even and odd bits of the words will have to be correctly ordered to form the  $pixel\ word$  on the output. Also the part calibrating the IDELAYE2 to make sure sampling happens inside the data eye has been omitted but this is done in a similar way as the previous design. It can be seen that the clock divider in the figure, divides the clock by 6, this is an example for a 12-bit implementation and should be changed to 5 for an 10 bit version. Because this version is adaptable to both 10 and 12 bits it is suited to use in an implementation with the image sensor.

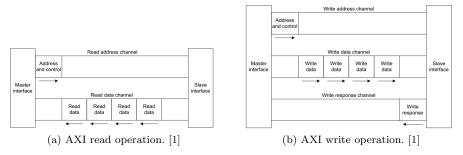

# 4.6 AXI protocols

A bus protocol that will be used in the implementations of this thesis is the Advanced eXstensible Interface (AXI) developed by ARM. This protocol defines a set of rules of how transactions of data between parts of a design should be executed.

This is a burst-based master-slave protocol and consists of five independent channels. **Read address**, **Read data**, **Write address**, **Write data**, **Write response**. During a read or a write the master provides the read or write address to the slave through the corresponding channels. The *Read data* and *Write data* channels are then used to transfer the data to read or write. After a write the *Write response* channel is used by the slave to inform the master about the status of this operation. Figure 31 show the mechanics of AXI read/write operations.

Figure 31: AXI read/write operations

The AXI protocol also use a simple but concise handshaking process. Using two signals, **VALID** and **READY**. The **READY** signal is asserted when the receiving part is ready to receive data and the **VALID** is asserted by the sender to indicate that valid data is present on the channel. When both signals are asserted it is called a handshake and the transfer is performed. In addition there are some rules for asserting the **VALID** and **READY**, these can be found in Appendix E.

There is three different AXI bus interfaces available, AXI, AXI-Lite and AXI-stream. These fulfil different use cases but consist of the same fundamentals. AXI is suited for memory mapped communication with high performance requirements. AXI-Lite is a simpler version of AXI where high performance is not crucial. It is fitted for low-throughput memory-mapped communication. AXI-stream is a interface for high speed streaming of data. It has been released multiple versions of AXI where the newest version is called AXI4 released in 2010. This is the version that will be used in this thesis.

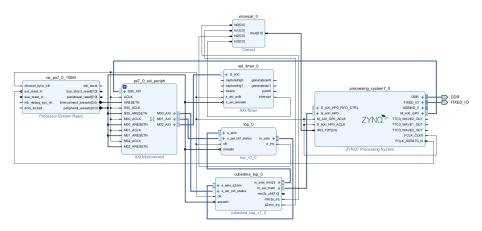

#### 4.7 Cube DMA

An important module for distributing data between the memory and different hardware designs is the Direct Memory Access (DMA). This module is commanded by the CPU to initiate data transfers from and to the memory, while the CPU executes something else. This is an important mechanism as the hyperspectral cube consists of large amount of data that will be transferred around to different hardware accelerators. These transfers will occupy the CPU if no DMA is present.

This concludes that a DMA will be necessary in the hyperspectral imaging application. However, there are some requirements that the DMA must be able to fulfil. In the paper *Direct Memory Access for Hyperspectral Imaging Applications* [6] the author looks into different DMA solutions for hyperspectral imaging applications. He starts by exploring the available solutions on the Zynq-7000 platform. He finds that the existing DMA solutions, *AXI DMA*, *AXI DMA*

in 2D mode and Video DMA are not suited for this application and designs a custom DMA he calls Cube DMA. He emphasises that the DMA should be able to access the cube sequential, block-wise and plane-wise, a requirement none of the existing DMA solutions was able to meet. The Cube DMA is able to provide all of these transfers and will therefore be the preferred DMA solution in light of hyperspectral imaging. The Cube DMA transfer uses two independent channels to transfer data over AXI stream, mm2s(memory to stream) and s2mm(stream to memory). Tables 19-20 in Appendix D shows the register map for the registers that was used in this thesis for both mm2s and s2mm channels.

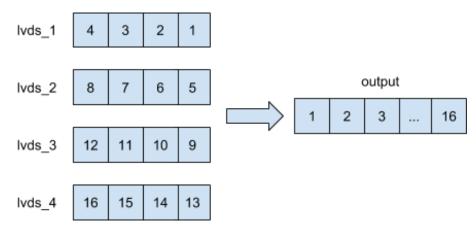

#### 4.7.1 Pixel Order Alignement Module

To store the LVDS data in memory it has to be passed to the Cube DMA through an AXI4-stream interface. Also the samples of the pixel will need to be organised in such a way that the Cube DMA is able to store them in the desired order in memory. The desired order is that the pixels are stored sequentially, meaning that all components from first pixel are stored first and then all components from the next pixel and so on. This means that the pixels will have to be passed to the Cube DMA in this order. From the previous figure 19 it can be seen that the LVDS data is not transferred in the correct order and therefore a mechanism to reorder and pass data through an AXI-stream interface will have to be implemented. Figure 32 shows the principle of the operation required from this module. In this figure, 16 samples from the LVDS Deserializer arrives. One sample from each LVDS channel arrive each clock cycle, meaning that 1, 5, 9 and 13 arrives in the first cycle. The right side of the arrow shows the desired ordering on the output. It is clear that to be able to output these samples in the correct order, one first has to wait 4 cycles to output all samples from lvds\_1 before starting on lvds\_2 and so on. This means that samples has to be buffered until the sample before has been outputted.

Figure 32: Operation required on the output of LVDS receiver.

# 4.8 Binning

A technique that is interesting in terms of hyperspectral imaging is binning. This is a technique where one try to reduce minor observation errors as well as reducing the amount of data without loosing too much information. The principle of binning is that multiple samples in a data set are merged together and given a new value based on the values of the individual samples. This value could be calculated as the summation, mean, median or other measures of the original values depending on the application. For the hyperspectral imaging application binning of the components of the pixels is useful, by merging multiple pixel components into a average of these samples. This because the lens that is used captures wavelengths in the interval 400-900 nm and 2048 components are not required to cover this. Therefore, by binning spectral components together reaching a point where there is enough components to represent the interesting data would be reasonable. The number of pixel components that will be merged together will be called the *Binning Factor*.

# 5 Extended Multiplicative Signal Correction

The Extended Multiplicative Signal Correction (EMSC) is a model-based preprocessing technique derived from the Multiplicative Signal Correction (MSC), and is used to reduce the impact of other phenomenons than the components that are of interest when capturing a spectra using spectroscopy. This could be phenomenons such as noise in form of light scattering or errors due to the instruments that are used. In the SmallSat Project the hyperspectral images are captured by a hyperspectral camera on a satellite. As the camera is capturing images of the earth from the space, light scattering may impact the images as the light captured travels through the clouds or other materials. Also the camera itself may contain sources inflicting the captured image in a erroneous way. This means that EMSC may be highly relevant for this application.

In the papers Light Scattering and Light Absorbance Separated by Extended Multiplicative Signal Correction. Application to Near-Infrared Transmission Analysis of Powder Mixtures [8] and Extended multiplicative signal correction in vibrational spectroscopy, a tutorial [11] the authors demonstrate the potential of EMSC in the Near Infrared Transmission spectra. In the former the authors explains that by using EMSC they are able to analyse different powder mixtures by separating the physical light scattering by the the chemical light absorption. In other words, when doing vibrational spectroscopy, each chemical bond in the material analysed emits unique vibrational energy levels, which is sampled and can be used as a fingerprint for this specific chemical bond [12]. However, in addition to these fingerprints, phenomenons as those mentioned above usually disrupts the information in these samples. It is here EMSC comes in, separating these fingerprints with light scattering and other sources of noise that are also captured.

### 5.1 Mathematical Model

In the paper Light Scattering and Light Absorbance Separated by Extended Multiplicative Signal Correction. Application to Near-Infrared Transmission Analysis of Powder Mixtures [8] the authors presents a way of calculating the EMSC for a given data set. Using Beer-Lambert's law as a starting point the authors states that the theoretical chemical absorbance spectrum of a sample can be considered as a sum of all contributions to this spectrum by all the constituents contained in the sample. This can be shown with equation 1, where  $z_{i,chem}$  is the chemical absorbance spectrum for the sample i, c is the concentration and k the vector representing the absorptivity spectrum of the j'th constituent contained in the sample.

$$\mathbf{z}_{i,chem} = c_{i,i}\mathbf{k}'_1 + \dots + c_{i,j}\mathbf{k}'_j + \dots + c_{i,J}\mathbf{k}'_J \tag{1}$$

The idea with the EMSC is to correct the measured absorbance spectrum by removing light scattering, path length and other wavelength dependent spectral effects, giving a result containing only the chemical absorbance information. The EMSC model is shown in equation 2 which is used to approximate the physical effects related to light scatter variations. The  $\mathbf{z}_i$  is the measured absorbance spectra of sample i.  $a_i$  and  $b_i$  are coefficients representing baseline offset and path length relative to the baseline offset and path length in a reference spectrum.  $\lambda$  is the wavelength. Because light-scattering effects depends on the wavelength, both a linear and quadratic term of the wavelength is taken into the account together with coefficients d and e allowing for wavelength dependent spectral variations from sample to sample.

$$\mathbf{z}_i \approx a_i + b_i \mathbf{z}_{i,chem} + d_1 \lambda + e_1 \lambda^2 \tag{2}$$

Then by estimating the coefficients in equation 2 this can be used to find the EMSC correction necessary to subtract all except the chemical absorbance information from the test data. This is shown in equation 3.

$$\mathbf{z}_{i,corrected} = (\mathbf{z}_i - a_i - d_1 \lambda - e_1 \lambda^2)/b_i \tag{3}$$

Even though the calculations are straight forward as shown in the equations above. The estimations of the coefficients are not. The authors presents a versatile solution for calculating the coefficients and applying the correction on the measured absorbance spectra. The solution starts by constructing a matrix **M** as follows:

$$\mathbf{M} = [1; m; k'; \lambda; \lambda^2] \tag{4}$$

The first row consists of ones and is according to the authors, introduced because of matrix formalities. Then  $\mathbf{M}$  contains the mean of the reference spectra m and the reference spectra itself k', the wavelength  $\lambda$  and wavelength squared  $\lambda^2$ . Now the EMSC coefficients can be estimated using least squares regression as shown:

$$\mathbf{z}_i = \mathbf{p}_i \mathbf{M} + \epsilon_i \tag{5}$$

where  $\mathbf{p}_i$  is a vector containing the coefficients that we estimates as follows:

$$\mathbf{p}_i = \mathbf{z}_i \mathbf{V} \mathbf{M}' (\mathbf{M} \mathbf{V} \mathbf{M}')^{-1}$$

(6)

This is weighted least squares estimator where  ${\bf V}$  is weights that can be defined by the user based on different criteria. This finally gives the solution that is an approximation spectra containing only the chemical absorbance information. Rearranging the terms in equation 5 gives equation 7 where  $\epsilon$  is the EMSC corrected spectra

$$\epsilon_i = \mathbf{z}_j - \mathbf{p}_i \mathbf{M} \tag{7}$$

## 6 Method

## 6.1 Exploring the prototype