Arkadiusz Kulka

# SENSORLESS DIGITAL CONTROL OF GRID CONNECTED THREE PHASE CONVERTERS FOR RENEWABLE SOURCES

Thesis for the degree of philosophiae doctor

Trondheim, March 2009

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Electric Power Engineering

# Abstract

Power electronic converters have become popular in the field of power transformation for renewable energy. Power electronics converters achieve high efficiency, and the price of their components is falling, thus making them even more beneficial for renewable energy applications. Those systems coupled to the grid need to withstand certain utility-defined circumstances which may occur during operation. Additionally the new net regulations for large generation plants specify that during specified severe grid disturbances the relatively delicate converters should stay connected supporting the system. For PV inverters the forthcoming standards may optionally add the possibility of reactive power compensation where for wind-power those standards are already in use.

This thesis focuses on reliable, sensor-less control of the PWM converters coping with varying grid conditions and existing problems. The thesis presents a variety of digital control solutions for interfacing PWM converter with the grid, synchronization, sensor-less operation and grid impedance detection.

The introductory chapter gives the fundamental theory about three-phase converters and control.

The following chapters deal with unbalanced condition and symmetric component decomposition, which is the tool to cope with unbalanced grid voltages or currents.

A sensor-less operation method using dual frame virtual flux model is presented with good results. In addition sensor-less synchronization to the grid is shown. Moreover an algorithm based on virtual flux for grid inductance estimation is also successfully demonstrated. Knowing the grid inductance is important during weak grid operation, since it is needed in order to provide unity power factor to the point of common connection.

At the end of the thesis, a control algorithm for voltage harmonic compensation during stand alone operation is presented. The presented algorithm gives the possibility to supply high quality power in isolated islands, where the load is unknown. Furthermore, this algorithm can be successfully used for UPS applications. The last chapter applies the voltage harmonic control to the Z-source converter having the possibility of achieving higher ac voltage than in conventional VSI, results are promising.

i

# Acknowledgement

At first I would like to thank Professor Tore Undeland for giving me the opportunity to start the PhD studies and being my supervisor for four years. His inspiration has been invaluable to me. The four years which I spend on this PhD was very interesting and educational. When I start PhD I knew the power converters and control only from theory. The possibilities of testing in laboratory DSP programs on grid connected systems also give me a good practical understanding of converter operation.

During my PhD studies I've had the pleasure to stay abroad two times. I would like to thank my friends at University of Seville, Spain. Special thanks to Jose Ignacio Leon Galvan and Sergio Vazques for being good friends, helping out in the new laboratory and numerous technical discussions. I learned a lot of things during 6 months.

Also I would like to thank Junji Kondoh at AIST, Tsukuba, Japan for providing great laboratory help, and being good partner in discussions. Thanks also go to Jan Wiik who worked with me in the laboratory, this give me the correct picture of right order during critical experiments when many persons are involved.

I would like to give thanks to the fellows at the ENO group: Marta, Giuseppe, Jon Are, Øystein, William, Bjarne, Pål, Thomas for technical discussion and social activities. Thanks also go to Eva and Inger for helping with administrative matters.

I would like to thank the Research Council of Norway and company Power-One for funding this work. This is the last and closing rapport in this project under grant 146524/210.

I also pay gratitude to Ingvar Apeland and others at EltekValere AS from Kristiansand for their time in proofreading of an early version and helping me to finish on time.

Thanks to Marek Baranowski for being open to discussions over past 4 years in Trondheim. I also would like to thank Isabel Lenzion for reminding me that there are other things in life than power electronics. At last I have to thank my close family: my parents and my sister for encouraging me and continuous support, their help was invaluable for me.

Trondheim, March 2009

Arkadiusz Kulka

# TABLE OF CONTENTS

| ABSTRACT                                                                                 | I              |

|------------------------------------------------------------------------------------------|----------------|

| ACKNOWLEDGEMENT                                                                          |                |

| TABLE OF CONTENTS                                                                        | V              |

| 1. INTRODUCTION                                                                          |                |

| 1.1. Preface                                                                             | 1              |

| 1.2. Background                                                                          |                |

| 1.3. Introduction to the three-phase converters                                          |                |

| 1.4. Motivation for the study                                                            |                |

| 1.5. State of the art study                                                              |                |

| 1.6. Publications                                                                        |                |

| 1.7. Contributions to the thesis                                                         | 9              |

| 1.8. List of abbreviations and symbols                                                   |                |

|                                                                                          |                |

| 2. INTRODUCTION TO THREE-PHASE CONVERTERS AND CONTROL                                    |                |

| 2.1. Transformations                                                                     |                |

| 2.1.1. The Clark transformation                                                          |                |

| 2.1.1.1. Current transformation                                                          |                |

| <ul><li>2.1.1.2. Voltage transformation</li><li>2.1.2. The Park transformation</li></ul> |                |

| 2.2. Modeling of the ideal converter bridge                                              |                |

| 2.3. Modulation strategies                                                               |                |

| 2.3.1. Sinusoidal modulation                                                             |                |

| 2.3.2. Sinusoidal modulation with the third harmonic                                     |                |

| 2.3.3. Space vector modulation                                                           |                |

| 2.3.4. Symmetrical sub-oscillation method                                                |                |

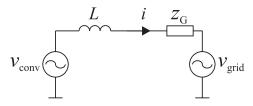

| 2.4. Mathematical model of the converter with L filter                                   |                |

| 2.4.1. Ac side model                                                                     |                |

| 2.4.2. Dc-side model with capacitor.                                                     |                |

| 2.4.3. Instantaneous power theory for symmetrical system                                 |                |

| 2.5. Mathematical model of the converter with L filter under unbalar                     | nced voltage32 |

| 2.5.1. Instantaneous power theory for unsymmetrical system                               |                |

| 2.6. Dead-time effects and its correction                                                |                |

| 2.6.1. Dead time effects correction algorithm                                            |                |

| 2.7. Synchronous sampling                                                                |                |

| 2.8. Voltage oriented control                                                            |                |

| 2.9. Chapter summary                                                                     |                |

| vi |  |

|----|--|

| 3. | SYMMETRIC COMPONENT DECOMPOSITION                                                                     | 41      |

|----|-------------------------------------------------------------------------------------------------------|---------|

|    | 3.1. Introduction                                                                                     | 41      |

|    | 3.1.1. Symmetric decomposition in three-phase systems                                                 | 42      |

|    | 3.1.2. Symmetric component decomposition for space vector                                             |         |

|    | 3.2. Discrete delay implementation based on circular buffer                                           |         |

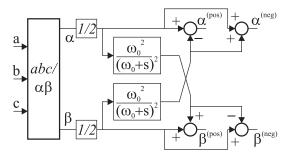

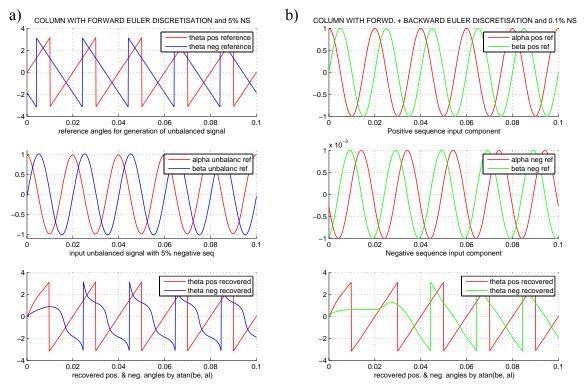

|    | 8.3. Proposed implementation based on adaptive filter                                                 | 45      |

|    | 3.3.1. Discretization                                                                                 | 46      |

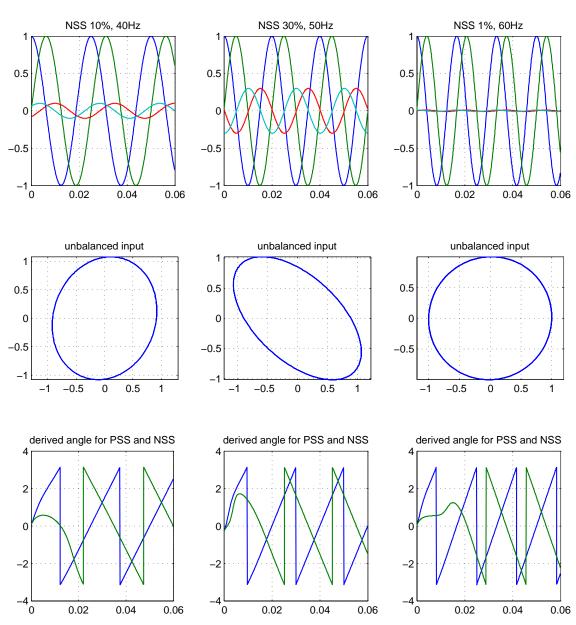

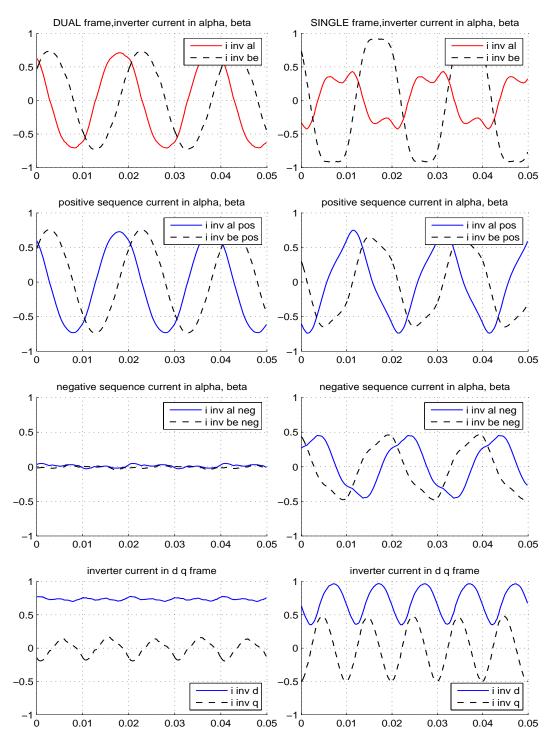

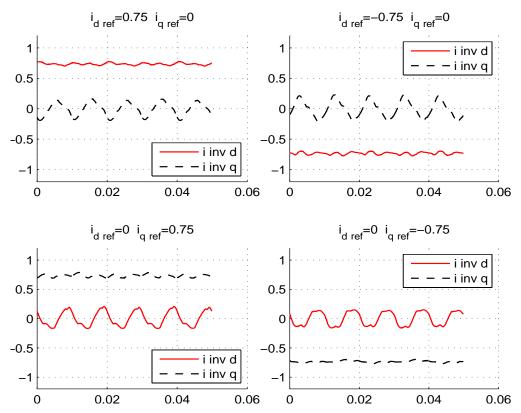

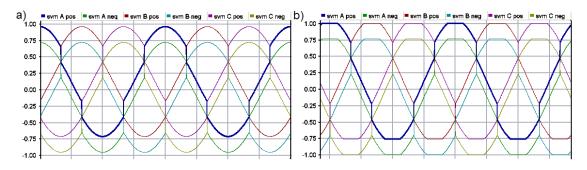

|    | 3.3.2. Simulation results of space vector decomposition                                               | 48      |

|    | 3.4. Chapter summary                                                                                  |         |

| 4. | DUAL VIRTUAL FLUX MODEL                                                                               | 51      |

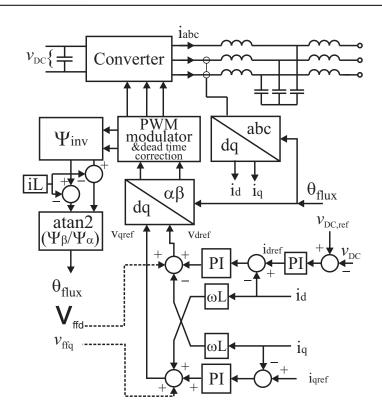

|    | 1. Introduction to virtual flux.                                                                      | 52      |

|    | 2. Proposed virtual flux model                                                                        | 55      |

|    | 4.2.1. Drift compensation                                                                             |         |

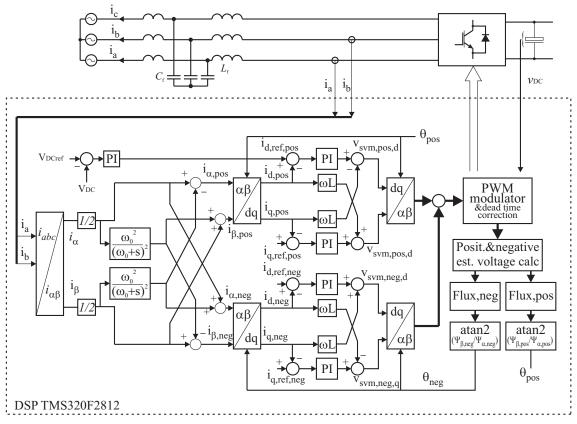

|    | Assembly of dual virtual flux model                                                                   |         |

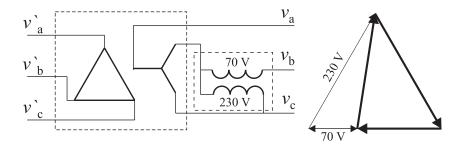

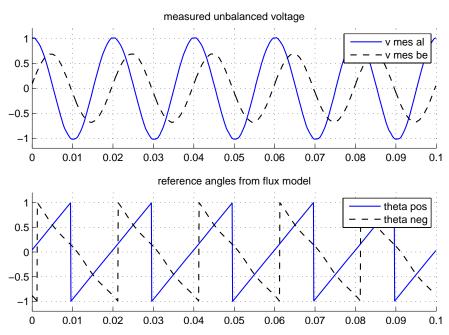

|    | 4.4. Evaluation of dual frame flux model under unbalanced voltage                                     |         |

|    | 4.4.1. Experimental results of supplying balanced currents into unbalance                             | ed grid |

|    | 4.4.1.1. Feasibility of removing voltage measurement sensors for feed-forward                         |         |

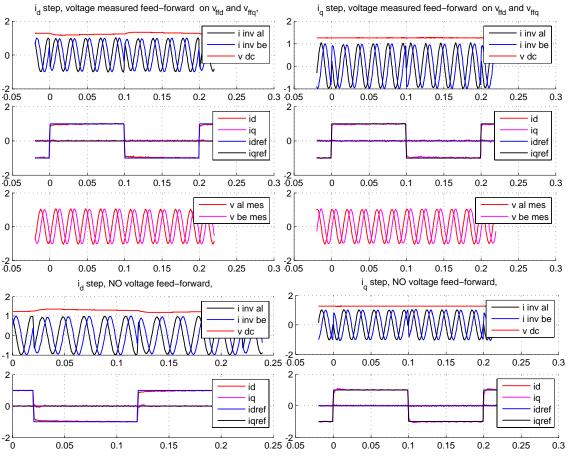

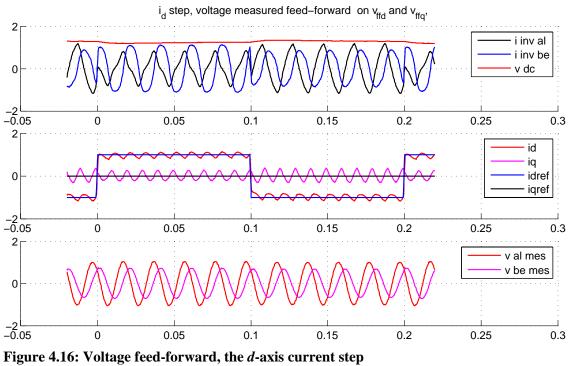

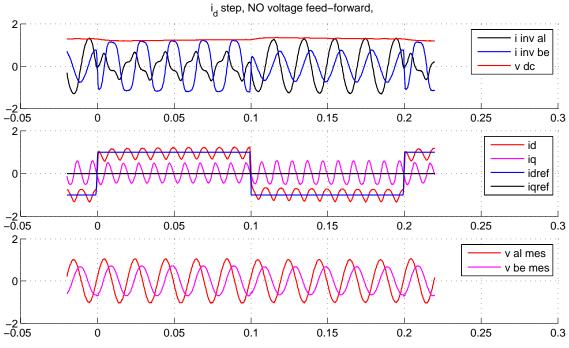

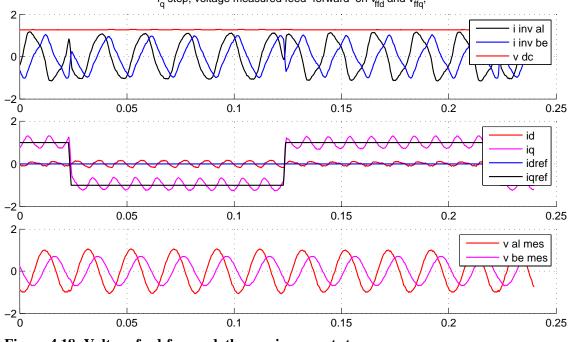

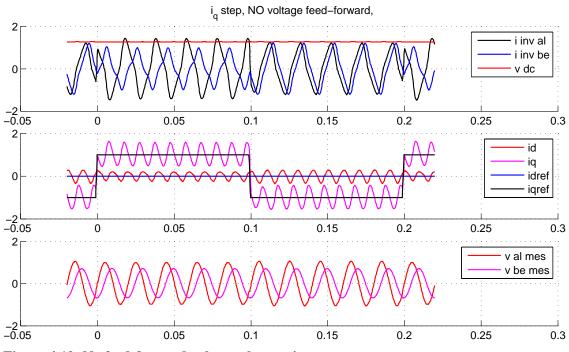

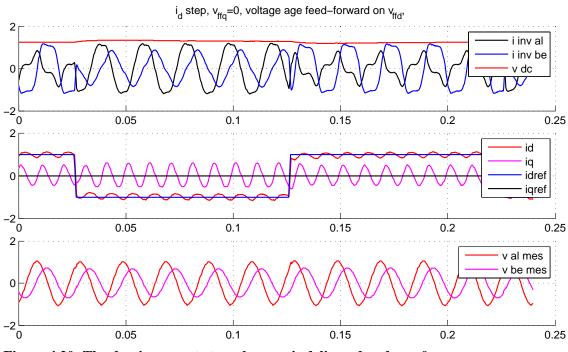

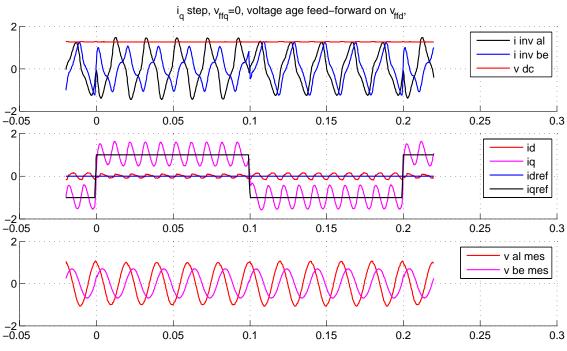

|    | 4.4.1.2. Influence of the voltage feed-forward term on single frame current control                   |         |

|    | balanced condition                                                                                    |         |

|    | 4.4.1.3. Influence of the feed-forward term during unbalanced condition for single orientation        | e frame |

|    | 4.4.1.4. Comparison of single and dual frame control under unbalanced voltage -<br>laboratory results |         |

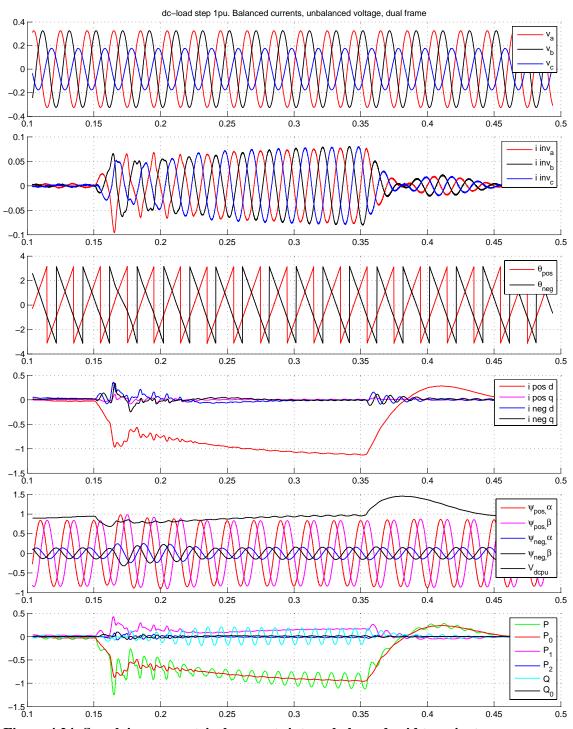

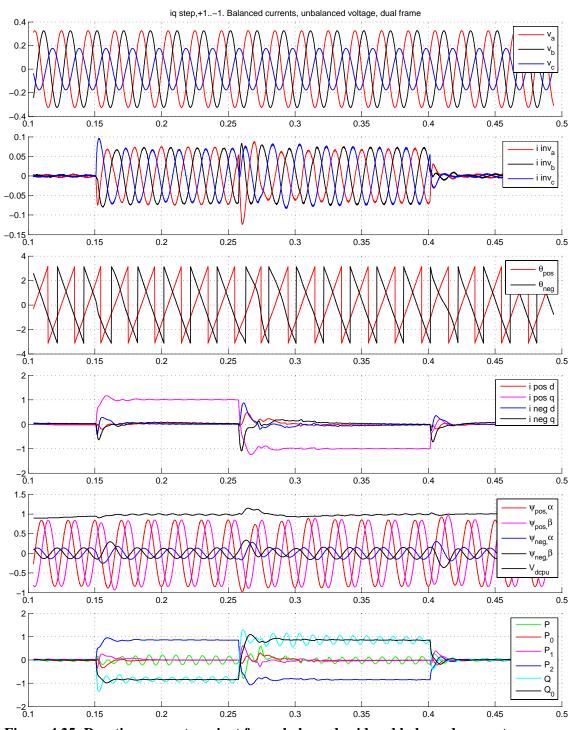

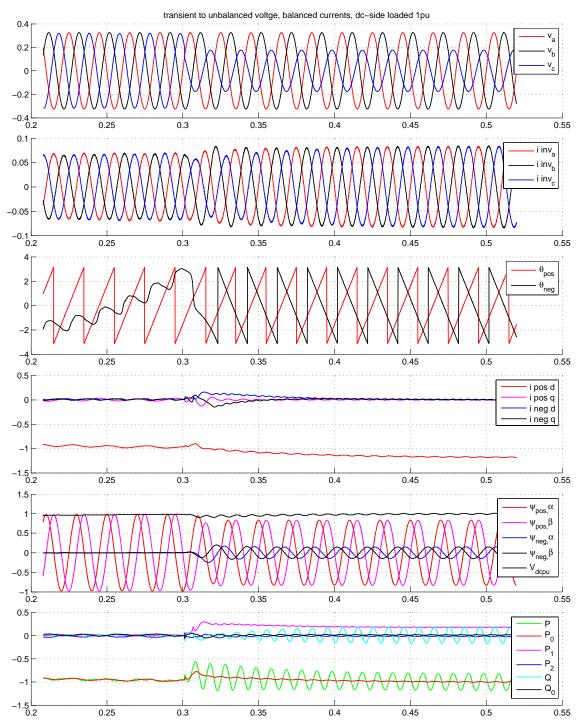

|    | 4.4.1.5. Simulation results of supplying balanced currents into unbalanced grid                       |         |

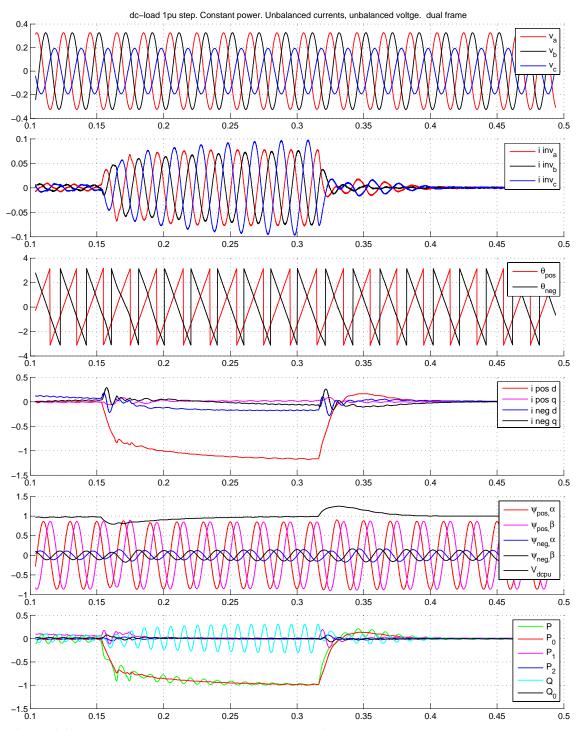

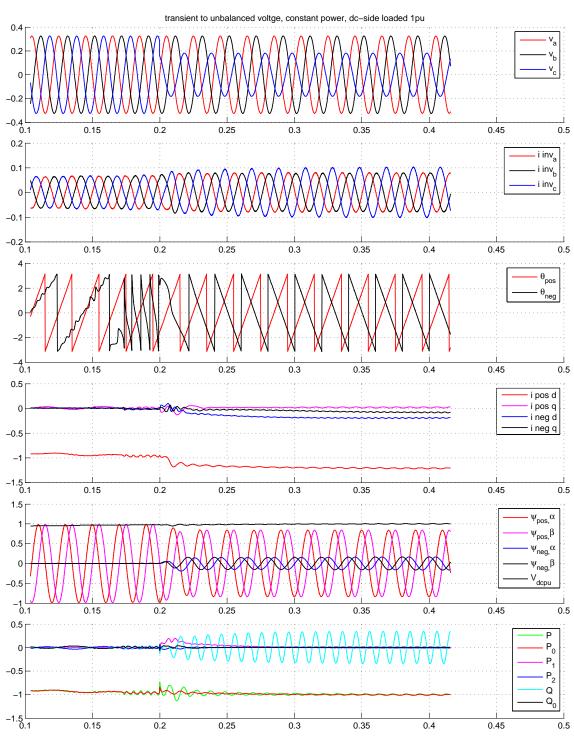

|    | 4.4.2. Simulation results of supplying constant instantaneous power for unbalanced grid               |         |

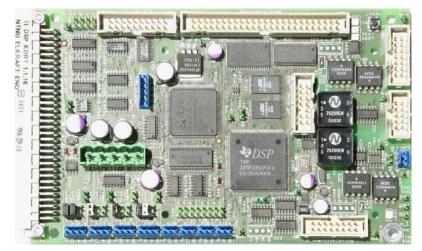

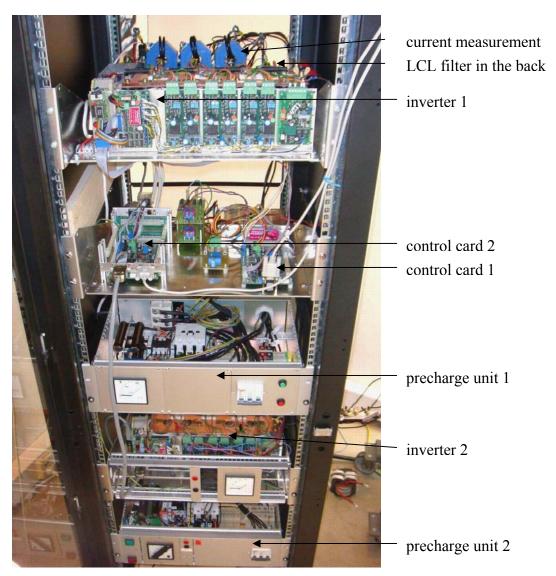

|    | L5. Laboratory setup                                                                                  |         |

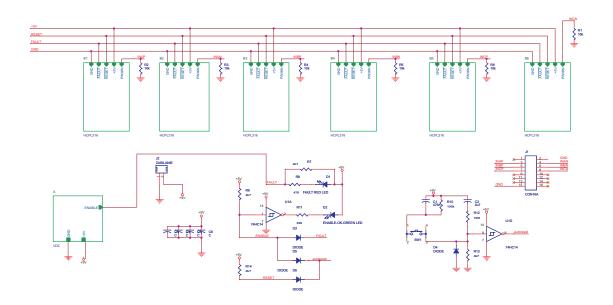

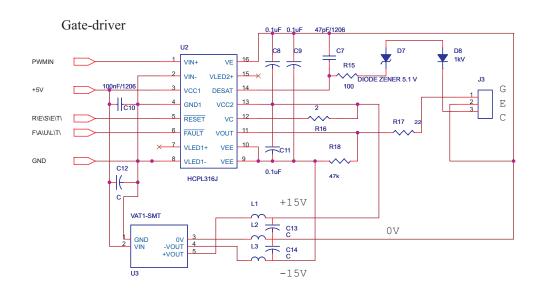

|    | 4.5.1. DSP system implementation                                                                      |         |

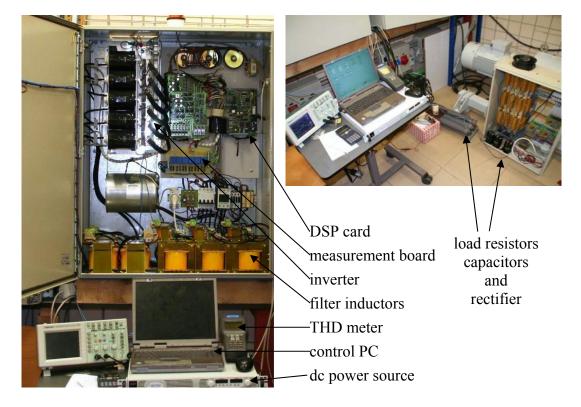

|    | 4.5.1.DST system implementation4.5.2.Photograph of the laboratory setup                               |         |

|    | 1.5.2.       1 notograph of the haboratory setup                                                      |         |

| 5. | SYNCHRONIZATION TO THE GRID                                                                           | 81      |

|    | 5.1. Synchronization to the grid without voltage sensors                                              | 81      |

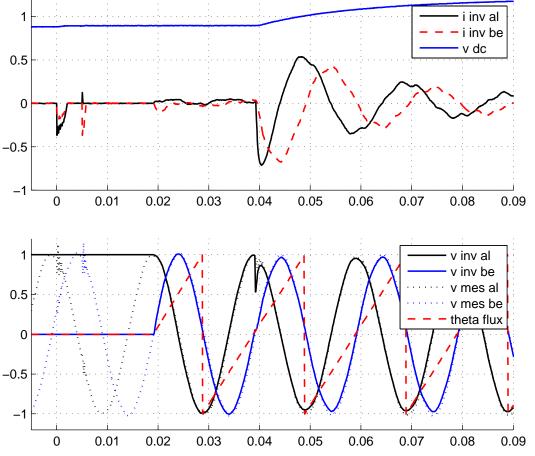

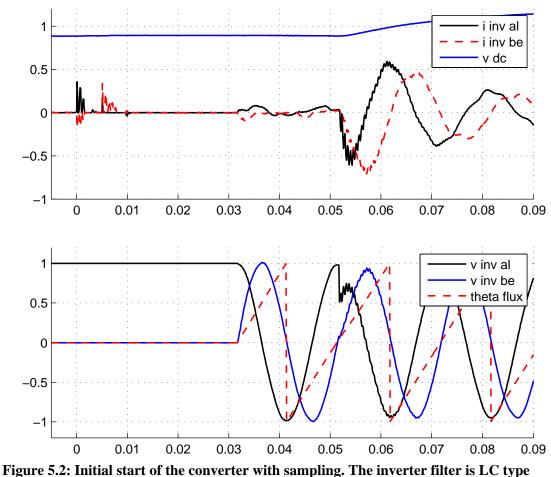

|    | 5.1.1. Standard synchronization with sampling for balanced voltage                                    |         |

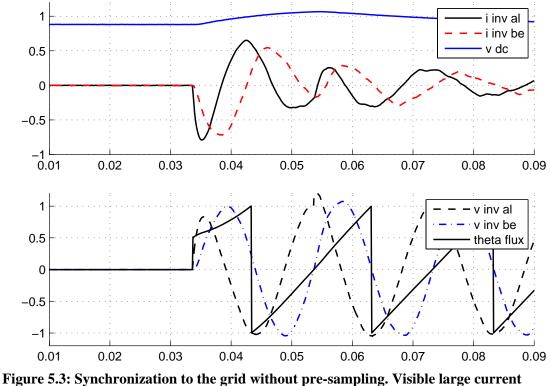

|    | 5.1.2. Synchronization without sampling or initialization for balanced vol                            |         |

|    | condition                                                                                             | -       |

|    | 5.1.3. Synchronization without sampling or initialization for unbalanced                              |         |

|    | voltage condition                                                                                     | 84      |

|    | 5.2. Chapter summary                                                                                  | 88      |

| 6. | GRID INDUCTANCE ESTIMATION                                                                            | 89      |

|    | 5.1. Introduction                                                                                     | 89      |

|    | 5.2. Existing impedance detection methods                                                             | 90      |

|    | 5.3. Proposed method                                                                                  | 90      |

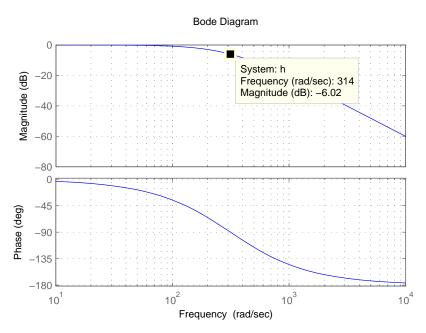

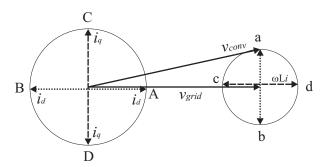

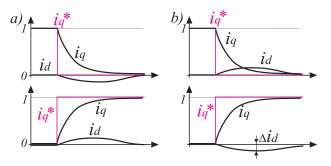

| 6.3.1.      | The cross coupling term                                       | 91  |

|-------------|---------------------------------------------------------------|-----|

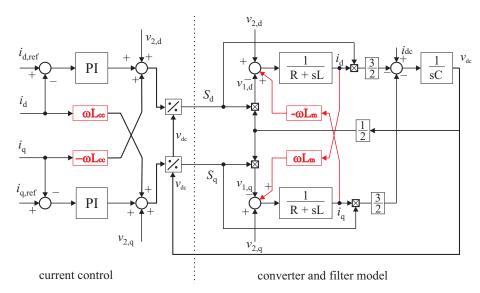

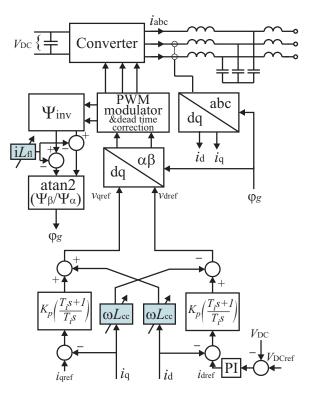

| 6.3.2.      | Current controller                                            |     |

| 6.3.3.      | Dc-bus controller                                             | 94  |

| 6.3.4.      | Virtual flux orientation                                      | 94  |

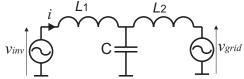

| 6.3.5.      | Usage of LCL filter                                           |     |

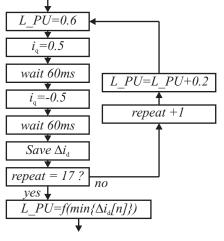

| 6.3.6.      | Realization of reactive perturbation method                   |     |

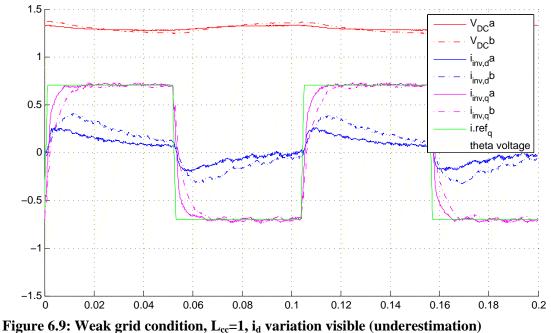

| 6.4. Exp    | perimental results                                            | 98  |

| 6.4.1.      | The sweep test results                                        |     |

| 6.5. Cha    | pter summary                                                  | 103 |

| 7. STANDA   | LONE INVERTER OPERATION AND VOLTAGE HARMONIC CONTROL          | 105 |

| 7.1. Intr   | oduction                                                      | 105 |

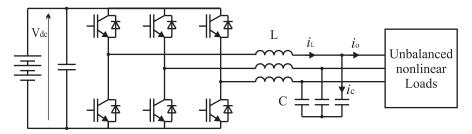

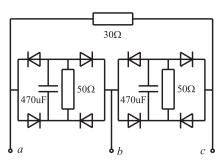

| 7.1.1.      | System description                                            |     |

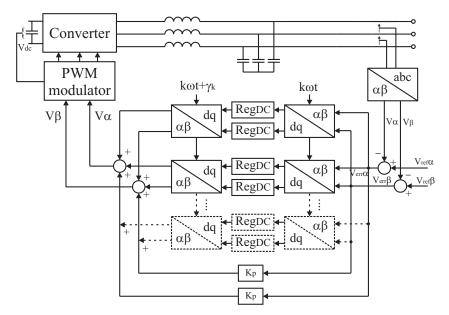

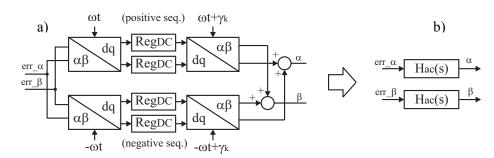

| 7.1.2.      | Conventional synchronous frame voltage harmonics compensation |     |

| 7.1.3.      | Stationary frame ac compensator – resonant compensator        |     |

|             | ntrol topology                                                |     |

| 7.2.1.      | Discrete implementation                                       |     |

| 7.2.2.      | Sharing of voltage harmonic in parallel operation             |     |

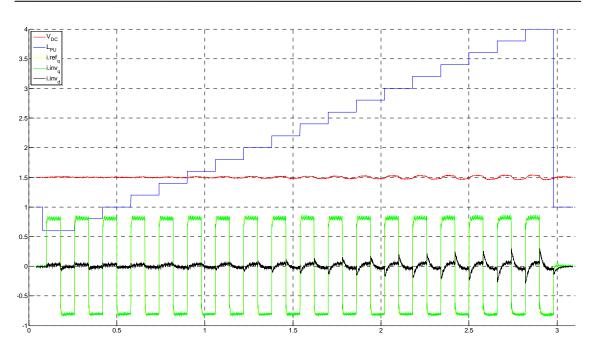

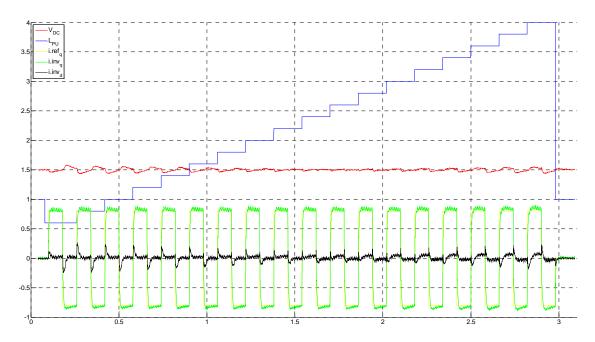

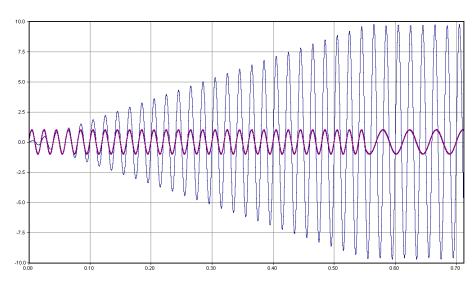

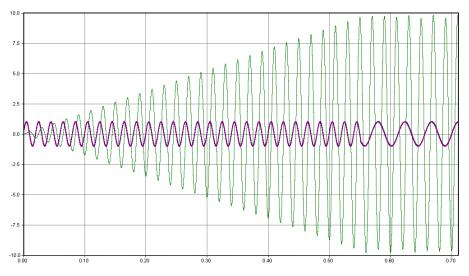

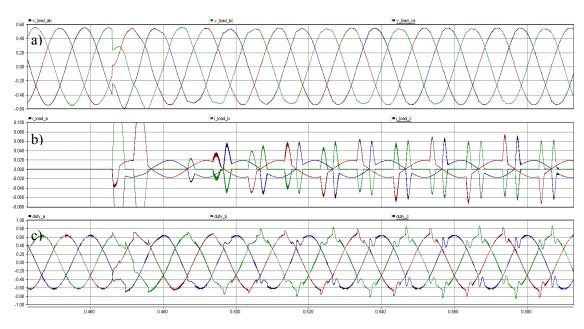

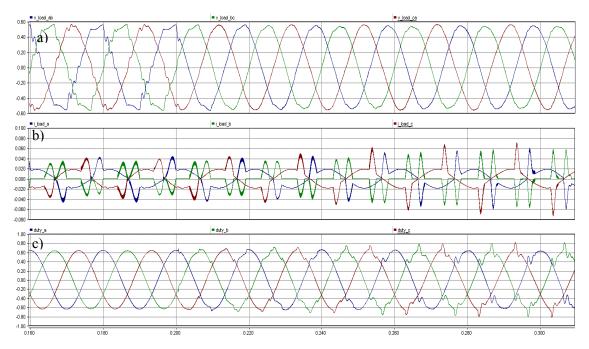

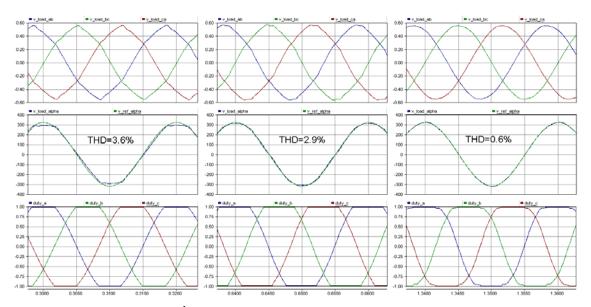

|             | nulation results for VSI                                      |     |

| 7.3.1.      | Influence of voltage third harmonic control on modulation     |     |

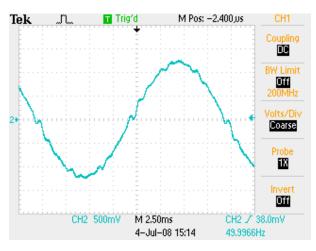

| -           | perimental results for VSI                                    |     |

| 7.4.1.      |                                                               |     |

| 7.5. Cha    | pter summary                                                  | 119 |

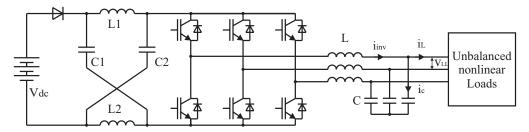

|             | TION OF Z-SOURCE INVERTER WITH VOLTAGE HARMONIC CONTRO        |     |

|             | oduction                                                      |     |

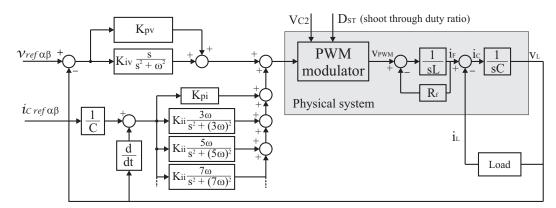

|             | voltage control                                               |     |

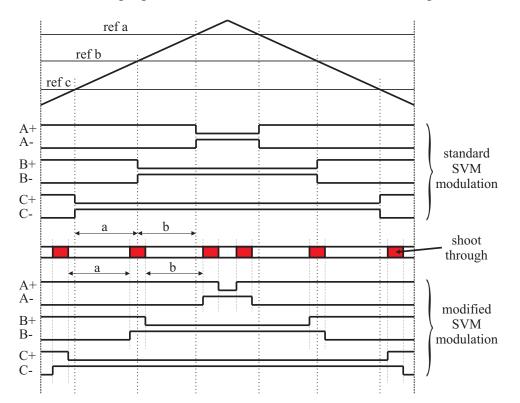

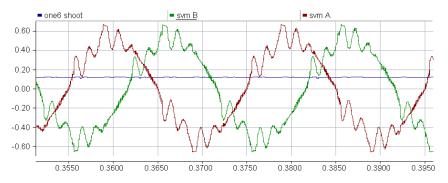

|             | dulator with shoot-through states                             |     |

| 8.3.1.      | Selection of boost inductor inductance                        |     |

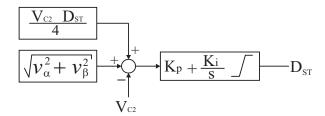

|             | tual Dc-link voltage controller                               |     |

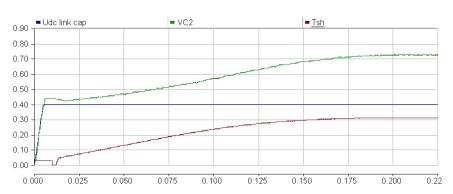

|             | nulation results                                              |     |

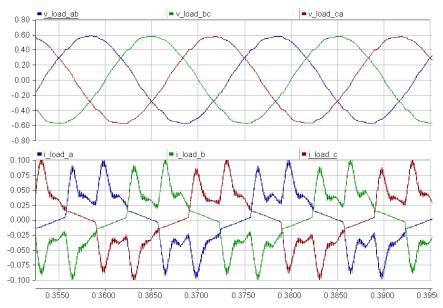

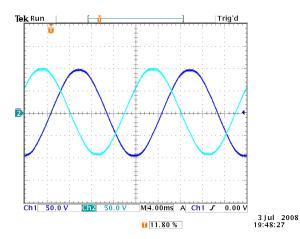

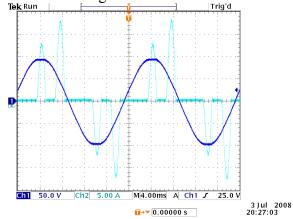

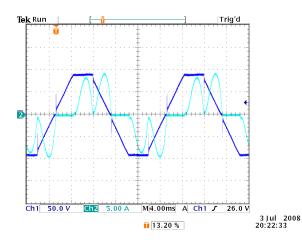

| -           | perimental results for ZSI                                    |     |

| 8.7. Cha    | pter summary                                                  | 131 |

| 9. SUMMAI   | RY AND FUTURE WORK                                            | 133 |

| 9.1. Con    | nclusion                                                      | 133 |

| 9.2. Sco    | pe of future work                                             | 136 |

| References  |                                                               | 137 |

| APPENDIX A: | Z-INVERTER SCHEMATICS                                         | 144 |

| APPENDIX B: | PER UNIT SYSTEM                                               | 146 |

| APPENDIX C: | POWER COMPONENTS IN UNBALANCED SYSTEM                         | 147 |

vii

# **1. INTRODUCTION**

### 1.1. Preface

This thesis is a part of the "Technologies for Reliable Distributed Generation of Electric Power from Renewable Energy Sources" project. The research project involves two departments at the Norwegian University of Science and Technology and one industrial partner. The research groups at NTNU are from the Marine Machinery Group in the Department of Marine Engineering and the Energy Conversion Group (ENO) at the Department of Electric Power Engineering.

The funding partners are the Research Council of Norway and industry partner-Powec AS/Power-One.

The project objectives are as follows:

Develop energy efficient solutions and optimal design/manufacturing that enable different distributed renewable energy sources to work as stand alone electric power supplies or to be optimally integrated within the electric power infrastructure.

Transfer this knowledge to industry or eventually establish new industry.

Improve scientific knowledge and develop a scientific competent staff in the field of renewable energy systems. When the project ends, a total of 4 PhD students will be ready to join the industry in the project field.

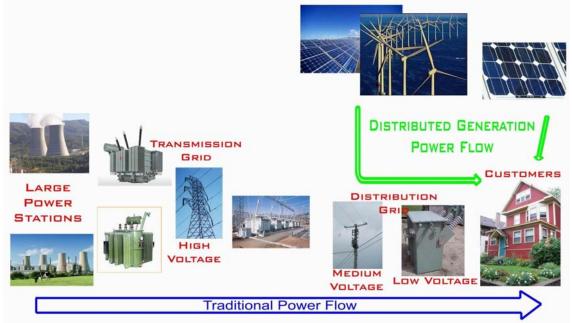

Figure 1.1: Overview of traditional power system and distributed generation

## 1.2. Background

In recent years power electronics has come with great help to efficiently harness the free energy of nature like wind-, solar- or wave-power. With increasing prices of fossil fuel, and excessive emission of gases causing global warming, researchers and politicians are facing the problem that the cheap energy sources are running out and new solutions are needed. Since the production of electric energy still consumes a large part of the total worldwide coal energy reserve, the traditional power system should be used to enable more green generation and meet environmental concerns. Conventional large power plants deliver electric power to the majority of the population, while emitting large amount of carbon-dioxides. In order to support and unload those plants, a strategy based on a large amount of generation sources, but relatively low power from renewable sources is gaining popularity – the distributed power generation (DG).

One of these solutions which can help to provide green electric power to distributed generation from renewably sources is to use power electronics as an efficient tool in the power conversion chain [bla1], [bla2]. The renewable sources tend to have electric power fluctuations dependent on the environment conditions. Many studies show that energy storage is needed in order to smooth out the power and stabilize the grid. Some examples of energy storage are water pumped solution, chemical battery, flywheel, hydrogen, or compressed air. Power electronic conversion is the key technology to increase efficiency for energy generation or storage. The advantage of distributed generation is that generation can occurs in proximity to the consumer, thus not suffering from transmission losses.

Due to political decisions we observe a large expansion of DG in many countries. For instance in 1991 in Germany, the government started its "1000 Roofs" program subsidizing solar energy. In 2001 the program was extended to "100 000 roofs". The changes in the law enable quicker PV implementation, the grid companies are also obliged to buy "green" power from any customer and the selling price is higher than from regular power. The plan for Germany and Sweden is also to slowly back out from nuclear power production. In Norway there is a goal to achieve 3 *TWh/year* from wind power until 2010. In Sweden in 2003 the government introduced a new legislation which intends to encourage and increase the production from renewable sources. In Spain the newly build family apartments are obligated to have solar heating systems on roof for water heating. In this way a significant amount of electric energy can be saved.

In a distributed system the important part is the power conversion and control. Modern IGBT transistors easily enable to build power electronics converters which are used to convert DC currents into AC and vice versa in range of hundreds *kW* [ber1]. The availability and cheap price of digital signal processors (DSP) enable digital control technique, which give wide possibilities for control, protection, data logging, statistics, prediction, communication and all kind of embedded intelligence. In the past mostly analog control was used and more advanced function were not available. When using a PWM converter with DSP control it is possible to mimic the synchronous generator used in conventional power plants, and even embed more advanced functions, like active impedance variation and detection, different characteristics of droop control, active damping of low frequency sub-oscillations, etc. More details with droop control

2

for DG can be read in [bra]. The thesis also not deals with DG impact on power system stability or weak grids. These topics can be found in [mag3].

Most of this PhD thesis presents digital control algorithms, transformations, regulations techniques, communications, detection algorithms which finally end up inside signal processor as a DSP program. Any digital control algorithm consists of a small block of code, and the final overall performance will depend on quality of those small blocks.

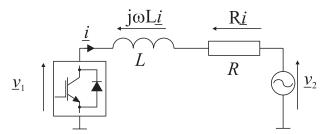

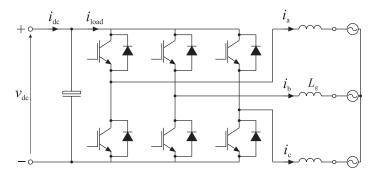

# **1.3.** Introduction to the three-phase converters

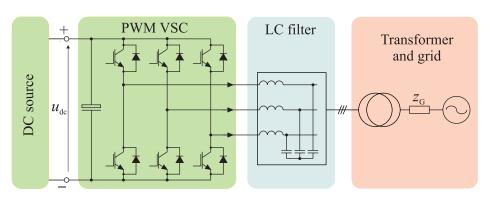

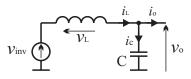

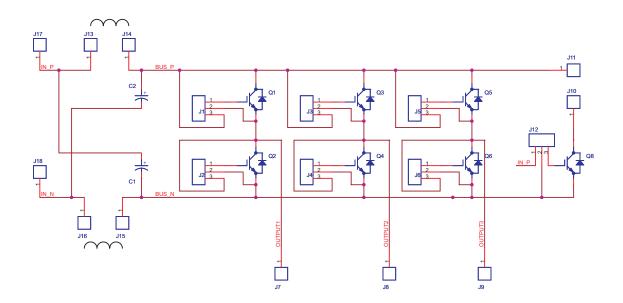

The three-phase voltage source converter (VSC) which is shown in Figure 1.2 is rather the name of topology and can be recognized dependent on the application under several different names like: grid connected converter, active rectifier, regenerative rectifier, PWM converter. Usually the hardware is the same, only different control schemes are used. Since the converter output voltage is a high frequency kind of square wave, some sort of filter that interconnects the converter to the grid is needed. The simplest filter consists only of an L choke, but due to its inefficiency LC or LCL filters are often employed. An LCL filter gives higher harmonic attenuation and cheaper cost [mal7]. The LCL filter is also vulnerable to resonance since it reassembles resonant circuit; active damping algorithms must be used [bla3], [lis3], [gul1].

The IGBT transistors are commonly used for powers from 5 kW and higher. It is common to assume the life time of an IGBT stage for around 20 years. The most common modulation strategy is PWM with constant frequency switching. To increase the output voltage to maximum and fully utilize voltage in the dc-link, space vector modulation or sinusoidal modulation with third harmonic injection can be used. Currently the dc-link electrolytic capacitor is limiting the life time of the whole converter. Some companies even assume that the DC capacitor should be replaced at certain intervals (e.g. 8 years). For three-phase balanced systems this is not such a problem as for single-phase application where the power is pulsating. Many attempts have been done to replace or minimize this electrolytic capacitor by other topologies (e.g. matrix converter topology) or control scheme (e.g. direct power control).

The most common converter topology used for three-phase renewable sources is shown in Figure 1.2. It employs three transistor bridges connected to a common dc-link bus with a dc capacitor. Further the converter ac output is connected with the grid through a filter.

Figure 1.2: The PWM converter placed inside the conversion chain system

Introduction of PWM, IGBT-based converter brings several advantages such as maximum energy extraction from controlled plant, very high efficiency, controllable reactive power, fast response, etc. In the large variety of renewable systems on the market, the power conversion is mostly realized by a PWM converter with IGBT transistors, only for high power and high voltage levels tyristors are still used (e.g. HVDC).

### **1.4.** Motivation for the study

All recent annual statistics shows a constantly increasing share of renewable sources in power generation. We have the luck of living in the century where a large amount of cheap energy is coming from oil, gas and coal, and consumption nowadays is at its peak. The exploration process become more difficult and thus the prices of fossil energy will increase. Like our fathers and grandfathers remember steam locomotives, in a matter of 40 years we will remember cars with internal combustion engine. The same transformation has to happen in electric energy generation, we have to harness more renewable energy from nature. However another scenario is also possible, the use of Nuclear Energy, which has large potential to reduce  $CO_2$  emission but the acceptance from society is low.

Figure 1.3: Nowadays and future energy production and share path.

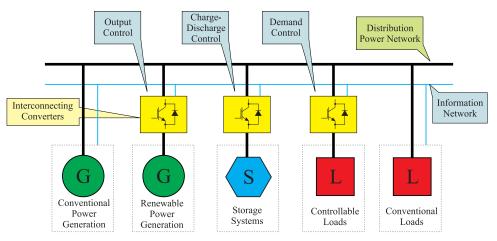

Still a lot of research and work has to be done in order to be self-sufficient in energy. One obvious solution is to maximize use of renewable energy combined with energy saving solutions. The quickest and easiest is to guide society how to not waste the electric energy. For sure in the future generation there will be much more wind-, solar or wave-energy but those are more expensive than conventional sources. Those green sources introduce challenges as power fluctuations, availability on demand and suffer in large investment cost. Figure 1.4 shows the trend in power systems, where renewable sources and storage system are integrated.

A good example of solution for storage is the state of the art water pumped system, which can operate with variable speed, resulting in high efficiency. In many flat or urban areas a use of hydro-based storage is impossible or expensive to build.

In those cases for power systems a relatively new type of battery can be used - the flow battery and the hot temperature battery [bar]. A good examples are two prototypes batteries which are built in Japan at Institute of Advanced Science and Technology (AIST), department of Research in Energy Technology, Tsukuba, Japan.

The first type battery consists of electrodes and exchangeable electrolyte, the power is limited by the area of electrodes (membranes) where the electrolyte during charging/discharging cycle is flowing. The energy is dependent on the volume of the electrolyte storage containers. The advantage of the system is when larger energy capacity is needed, it can be easily expanded by adding extra container with electrolyte. An operating example of Redox flow battery in Tsukuba can deliver  $170 \, kW$  for 8 hours, there are 4 pairs of  $28 \, m^3$  electrolyte tanks, the cell unit weight 12 tons (8 *m* by 2.5 *m* by 2.1 *m*), the converter and transformer unit dimension are 5 *m* by 2.4 *m* by 3.1 *m*. This battery is suitable for quick charge/discharge cycle.

Figure 1.4: Overview of the conventional system combined with controllable renewable and storage sources.

Another relatively new type of battery is a high temperature NaS battery (based on molten Sodium-Sulfur). This battery achieves high efficiency and energy density when nominal internal temperature is maintained (160 °C). When no power is taken an external heat source is needed, but when charged or discharged, the internal losses maintain the internal temperature, so it's suitable for a constant slow charge and discharge cycle. A prototype battery built in Japan can deliver 2000 kW for 8 hours; the

battery unit with transformer and converters has dimensions of 10.2 m by 5.5 m by 5.2 m, the total weight 206 tons. The cost today is high but with automated high-volume production the NaS battery could compete with hydro-storage. The producer of NAS batteries *NGK Insulators* claim the price to drop to 140/kWh.

All those solutions mentioned above need power conversion by means of power electronics. The study will look to minimize the overall cost of converter hardware and develop new control methods. Unnecessary sensors can always be removed and estimation can be calculated in a DSP based on remaining sensors. An reduced number of sensors also add reliability; the program is much less prone to fail than real hardware sensor to break. Some of the areas of the thesis scope are: sensor-less operation, grid synchronization, operation with unbalanced conditions, grid impedance detection, stand alone operation, resonant controllers, active damping of LCL grid filter resonances.

As there is growing need for electricity in underdeveloped countries (e.g. parts of Africa) one of possible solutions is to operate a hybrid generation combined of wind, solar, storage and diesel generator. This solution will be still cheaper than building and maintaining a power system grid, especially since the power needs are much lower than in developed countries. The island mode of power generation, bring the power close to the consumer. A voltage control algorithms for stand alone generation will be presented in this thesis in Chapter 7 and Chapter 8.

# **1.5.** State of the art study

Currently there are many ideas for distributed generation which need new control strategies, monitoring and planning. Up to now there is no established one standard for it, some researchers propose even DC current on the distribution level.

The general guide for design, operation and integration of distributed generation with electric power system can be found in [iee1] issued by IEEE.

A significant role in distributed generation is so-called droop control; the aim is to mimic the converter behavior as it would be a conventional synchronous generator. The inverter output voltage amplitude and frequency depends on the linear combination of active and reactive power. Significant work is done by K. De Brabandere, B. Bolsens, J. Van den Keybus and M. Chandorkar [bol1], [bra], [cha2], [kaw1] where the basics of parallel inverter operation take shape. Some work related to impact on power system and power quality is done by Fainan H. Magueed [mag3] and Hilmy Awad [awa].

In an aspect of regulation techniques and inverter advanced control a good reference is work done by D. Zmood and G. Holmes [zmo1]. Some innovative techniques are shown by M. Liserre in [lis5]. Passivity based and frequency domain methods are presented in [har1], [zmo3], and different current controllers strategies in [kaz2].

The research on Resonant Controller (RC) was mentioned first time in 1986 by Rowan, Kerkman. A good reference of using RC for current control presented in 1999 is D. N. Zmood and G.Holmes [zmo1], [zmo2], articles published by P. Mattavieli [mat]

presents voltage control with RC. In recent years highly popularization and different applications were done by R. Teodorescu and M. Liserre [teo2], [lis5], [key].

The repetitive control technique is also gaining the popularity. In operation it is similar to a bank of RC for infinite number of odd harmonic (bank or resonant filters). It can be used for compensation of harmonic distortion and correcting unbalanced condition. The majority of articles are from Gerardo Escobar [esc1], [esc2]. The implementation is very easy compared to the effort realizing the same functionality in synchronous frame or as a bank of individual resonant filter. The implementation uses feedback array and a delay line.

The problem of active damping of oscillation in LCL filters can be solved by many approaches, the most promising method based on virtual flux is proposed by Malinowski [mal2]. A method proposed by P. A. Dahono [dah1] based on "virtual resistor" requires extra capacitor current sensor. Another method suffering voltage capacitor feedback is lead-lag method proposed by Blasko [bla3]. A method proposed by Marco Liserre has no additional sensors, but generic algorithm is used [lis1], [lis3]. A proper controller tuning which will not lead to oscillations is presented [teo3] The EMI problems, common mode and diferencial associated with filters can be addressed in [bas].

A converter control based on the virtual flux concept first appears by S. Bhattacharya at. el in 1996 [bha1], M. Chandorkar published in 1999 [cha3], [cha1] and developed later by Malinowski in 2004 [mal1], [mal4], [mal5] for application of active rectifier. The virtual flux approach can also find application or can be used in direct torque control (DTC), hysteresis regulators or multilevel converters [mal4], [ser1], [yin1].

There are several publications for grid impedance estimation. One of the first papers on power system identification was presented by Z. Staroszczyk in 2000. In 2004 A. Tarikianen presented identification algorithm for the purpose of voltage feedback in active filter [tar2]. In 2007 M. Liserre published method based on excitation of LCL filter [lis4]. In 2006 A.V. Timbus and U. Borup presented algorithm based on interharmonic current injection for purpose of anti islanding detection [tim2], [tim3].

Different PLL structures for grid synchronization for balanced and unbalanced grid conditions were thoroughly presented by Alvaro Luna, Pedro Rodriguez and Remus Teodorescu [lun1], [cio1], [sil1], [tim1]. They allow implementing power control techniques, fulfilling the power quality requirements and overcoming the grid connection problems. Those PLL structures utilizes the positive and negative sequence decompositions, SOGI filters thus making them very robust against distorted voltage.

Several papers were published on the topic of unbalanced current control. They are based on pulsating power correction and single frame current control, full symmetric decomposition with double current controller [ngc1], [son1], [son2] or direct power control [mal1], [tar1].

For the renewably sources operating in stand alone mode or connected to the grid a good source can be [teo1], [mag2], [rod1]

# **1.6.** Publications

Publications on which I have been author or co-author:

- 1 A. Kulka, T. Undeland, Junji Kondoh, "Dual Frame Virtual Flux, Voltage Sensor-less Algorithm for Three-Phase VSC in Unbalanced Conditions – Experimental Study" submitted to IEEE Transaction on Power Electronics.

- 2 A. Kulka, T. Undeland, S. Vazquez, L. G. Franquelo, "Stationary Frame Voltage Harmonic Controller for Standalone Power Generation", Conference Proceedings, EPE 07, Aalborg, Denmark, 2-5 Sept., 2007

- A. Kulka, T. Undeland, "Grid Inductance Estimation by Reactive Power Perturbation for Sensor-less Scheme Based on Virtual Flux" NORPIE 2008, Espoo, Finland, 9 - 11 June 2008

- 4 A. Kulka, Tore Undeland, "Voltage harmonic control of Z-source inverter for UPS applications" Conference Proceedings, EPE-PEMC 08, Poznan, Poland,1-3 Sept. 2008

- 5 J. A. Wiik, A. Kulka, T. Isobe, M. Molinas, K. Usuki, T. Takaku, T. Undeland, R. Shimada, "Control design and experimental verification of a series compensated 50 kW permanent magnet wind power generator" IEEE Power Elec. Spec. Conf., PESC, 15-19 June, 2008.

- J. A. Wiik, A. Kulka, T. Isobe, K. Usuki, M. Molinas, T. Takaku, T. Undeland, R. Shimada, "Loss and Rating Considerations of a Wind Energy Conversion System with Reactive Compensation by Magnetic Energy Recovery Switch (MERS)", Wind Power to the Grid - EPE Wind Energy Chapter 1st Seminar, 2008. EPE-WECS 2008 27-28 March 2008

- 7 E. S. Hoff, T. P. Fuglset, A. Kulka, T. M. Undeland, "Power electronics laboratory combined with digital regulators", Power Electronics and Applications, European Conference, 2005

8

# **1.7.** Contributions to the thesis

The main contributions in the thesis are:

- A dual frame virtual flux model which can cope with unbalanced grid conditions. The model measures only two phase currents and the dc-bus voltage and thus can be named voltage sensor-less. The model uses proposed implementation method for separation of positive and negative sequence. The proposed new flux model is faster in time response, compared to those available in literature. The DC capacitor can be smaller due to possibility of supplying constant power for unbalanced grid condition.

- Instant synchronization to the grid without voltage sensors. Due to the fact that the proposed flux model is fast in time response, the synchronization can occur without pre-sampling the grid for detection of the voltage vector angle. The initial position of the voltage flux is not initialized (left zero). The transient synchronization current occurs during inverter start up procedure for less than half of the grid period and is smaller than 1 *p.u.* When the pre-sampling (shortcircuit of the grid) is used, and the flux model is initialized, the synchronization current is maintained under 0.05 *p.u.*

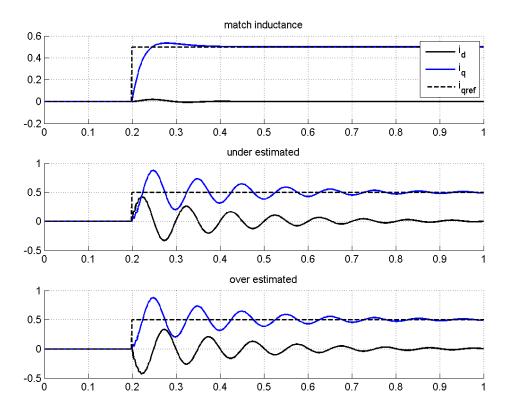

- A grid inductance detection algorithm by perturbation of the reactive power. It is based on insufficient dynamic of the current controller in synchronous frame when the cross-coupling term in current controller does not match the Thevenin equivalent inductance of the infinite grid. By injecting reactive power and observing the  $i_d$ ,  $i_q$  converter current responses the inductance can be estimated.

- A novel implementation method for separation of positive and negative sequence components of the unbalanced signal. The algorithm is computationally lightweight, easy to implement and can be adopted in a wide frequency range. It exploits the fact that the grid frequency variations are smaller compared to those found e.g. in a motor drive.

- Harmonic free voltage control algorithm for nonlinear and unbalanced loads for UPS or stand alone operation. The proposed algorithm uses a bank of resonant filters with quadrature output. For each harmonic, two orthogonal components are available enabling adjusting the phase for system delay cancellation. Because the system delay (important especially for higher harmonic) is taken account a high quality output voltage is achieved. The LC output filter is used.

- The concept of voltage harmonic control for Z-source inverter was implemented and tested for UPS application.

- The introduced ideas have been tested in laboratory for verifications. The experimental results are shown in the thesis at the end of the corresponding chapter.

<u>10</u>

| 1.8.  | List | of abbreviations and symbols                           |

|-------|------|--------------------------------------------------------|

| А     | -    | Ampere                                                 |

| AC    | -    | Alternating Current                                    |

| ADC   | -    | Analog to Digital Converter                            |

| AIST  | -    | Institute of Advanced Science and Technology in Japan  |

| В     | -    | Boost ratio of the Z-source inverter                   |

| CAN   | -    | Controller Area Network bus                            |

| CBM   | -    | Carrier Based Modulation                               |

| CC    | -    | Current Controller                                     |

| CCCC  | -    | Current Controller Cross Coupling                      |

| D     | -    | The distortion power                                   |

| DC    | -    | Direct Current                                         |

| DCC   | -    | Dual Current Controller                                |

| DFO   | -    | Dual Frame Orientation                                 |

| DG    |      | Distributed Generation                                 |

| DPC   | -    | Direct Power Control                                   |

| DSP   | -    | Digital Signal Processor                               |

| DSC   | -    | Delayed Signal Cancellation method                     |

| DVF   | -    | Dual Virtual Flux                                      |

| FPGA  | -    | Field Programmable Gate Array                          |

| GI    | -    | General Integrator                                     |

| HPF   | -    | High Pass Filter                                       |

| IGBT  | -    | Insulated Gate Bipolar Transistor                      |

| LPF   | -    | Low Pass Filter                                        |

| MOSFE | Γ-   | Metal-Oxide Semiconductor Field Effect Transistor      |

| NS    | -    | Negative Sequence                                      |

| NTNU  | -    | Norwegian University of Science and Technology         |

| NSS   | -    | Negative Sequence Signal/System                        |

| Р     | -    | The active power                                       |

| PCC   | -    | Point of Common Connection                             |

| PID   | -    | Proportional Integration Derivative type of controller |

| PLL   | -    |                                                        |

| PS    | -    | Positive Sequence                                      |

| PSS   | -    | Positive Sequence Signal/System                        |

| р.и.  | -    | Per-Unit                                               |

| PV    | -    | Photo Voltaic                                          |

| PWM   | -    | Pulse Width Modulation                                 |

| Q     | -    | The reactive power                                     |

| RC    | -    | Resonant Controller (known as: Resonant Filter or GI   |

| SFO   | -    | Single Frame Orientation                               |

| ST    | _    | Shoot through                                          |

| SVM   | -    | Space Vector Modulation                                |

| THD   | -    | Total Harmonic Distortion                              |

| VF    | -    | Virtual Flux                                           |

| VSC   | -    | Voltage Source Converter                               |

| - | Voltage Oriented Control                                                                     |

|---|----------------------------------------------------------------------------------------------|

| - | Z-Source Inverter<br>Zero Sequence Signal                                                    |

|   | The angle of the voltage grid derived from the flux model                                    |

|   | The <i>d</i> -axis, negative sequence current                                                |

|   | The <i>d</i> -axis, negative sequence voltage                                                |

| - |                                                                                              |

| - | The <i>d</i> -axis, positive sequence current                                                |

| - | The <i>d</i> -axis, positive sequence voltage                                                |

| - | The $q$ -axis, negative sequence current                                                     |

| - | The <i>q</i> -axis, negative sequence voltage                                                |

| - | The <i>q</i> -axis, positive sequence current                                                |

| - | The <i>q</i> -axis, positive sequence voltage                                                |

| - | Sampling frequency of the control system                                                     |

| - | Space vector, converter filter output voltage                                                |

| - | Space vector, converter terminal average output voltage                                      |

| - | Converter voltage in synchronous coordinate                                                  |

| - | Zero sequence voltage                                                                        |

| - | Space vector of converter voltage                                                            |

| - | Dead-time correction voltage                                                                 |

| - | Alpha component of inverter voltage                                                          |

| - | Beta component of inverter voltage                                                           |

| - | reference voltage for space vector modulation                                                |

| - | line to line voltage                                                                         |

| - | Switching frequency of the converter                                                         |

| - | Voltage space vector                                                                         |

| - | The 1 <sup>st</sup> voltage harmonic on inverter filter inductance                           |

| - | The 5 <sup>th</sup> voltage harmonic on inverter filter inductance                           |

| - | Capacitor voltage in Z-source inverter<br>The <i>d</i> -axis reference current               |

| _ | The dc-link current                                                                          |

| - | The <i>q</i> -axis reference current                                                         |

| - | The 1 <sup>st</sup> current harmonic of the load                                             |

| - | The 5 <sup>th</sup> current harmonic of the load                                             |

| - | Scaling factor for Clark transform<br>Integral gain of the negative sequence of PI regulator |

| - | Integral gain of the positive sequence of PI regulator                                       |

| - | Proportional gain of the positive sequence of PI regulator                                   |

| - | Proportional gain of the positive sequence of PI regulator                                   |

| - | Single frame current controller integral gain                                                |

| - | Single frame current controller proportional gain                                            |

|   |                                                                                              |

| 12                                                                                                                                                                      |                  |                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>cc</sub><br>L <sub>fl</sub><br>L <sub>sys</sub><br>L <sub>min</sub><br>L <sub>1</sub>                                                                            |                  | Inductance in the cross-coupling term of the current controller<br>Inductance in the flux model<br>Power system inductance (without converter filter inductance)<br>Inductance of the converter filter<br>Converter side inductor in LCL filter                                                                                                                                                            |

| $L_2 L_m M m_n$<br>$y_n$<br>$SW_x$<br>$S_x$<br>$S_{\alpha}, S_{\beta}$                                                                                                  | -                | Grid side inductor in LCL filter<br>Inductance of the grid and converter filter<br>Modulation index<br>The n intermediate sample in the digital filter implementation<br>The n output sample in the digital filter implementation<br>Binary signal controlling the inverter bridges, -1 or 1<br>Reference modulation signal where $x=\{a, b, c\}$ refers the phase<br>Components of switching space vector |

| $ \begin{array}{c}         a & y & p \\         T_i & \\         T_{ST} & \\         T_s & \\         T_{sw} & \\         U_{DC} & \\         v_{dc} & \\ \end{array} $ | -<br>-<br>-<br>- | Time constant of the integrator<br>Time duration of the shoot-through<br>Digital control sampling time<br>Inverter switching time                                                                                                                                                                                                                                                                          |

| $ \begin{array}{c} \nu_{\rm ffd} \\ \nu_{\rm ffq} \\ \underline{\Psi}_{conv} \\ \Psi_{g,\alpha} \\ \Psi_{g,\beta} \end{array} $                                         | -<br>-<br>-      | The <i>d</i> -axis feed-forward voltage<br>The <i>q</i> -axis feed-forward voltage<br>The converter flux space vector<br>The alpha component of grid flux<br>The beta component of grid flux                                                                                                                                                                                                               |

# 2. INTRODUCTION TO THREE-PHASE CONVERTERS AND CONTROL

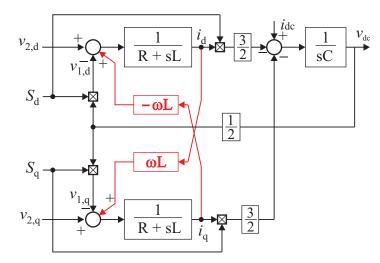

This chapter introduces the basics of three-phase voltage source converters. First orthogonal transformation is presented followed by modeling of VSC. Different modulation strategies will be shown based on average output voltages. Model with L filter in synchronous frame for balanced and unbalanced grid operation is described.

## 2.1. Transformations

In order to efficiently deal with the three-phase quantities this section introduce the Clark and Park transforms. The first one converts three-phase system to equivalent two phase notation, the second changes the time reference frame from stationary to synchronous. In literature there are many standards to align axes or scale the transformations which could lead to misunderstanding. Basically the selection can be arbitrary as long as the control keeps up with one standard.

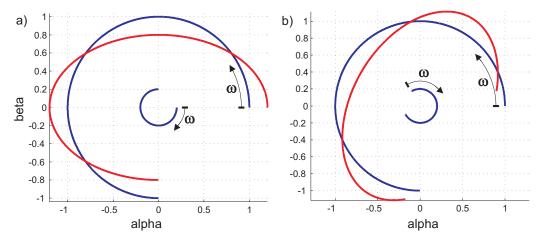

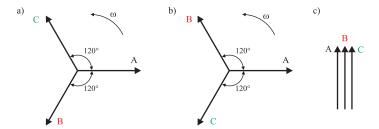

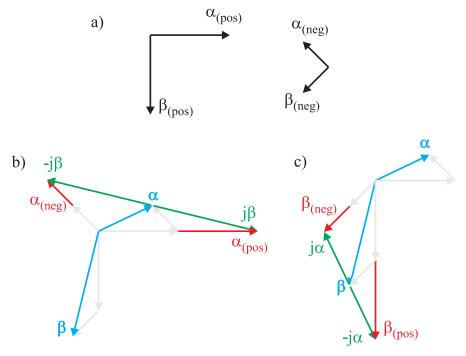

#### 2.1.1. The Clark transformation

The Clark transforms maps three-phase *a*, *b*, *c* components which are equally shifted by 120° into a two phase system. The new rotating vector is represented by two orthogonal components  $\alpha$  and  $\beta$  and is called space vector. The space vector consists of a real ( $\alpha$ ) and imaginary ( $\beta$ ) part which represents two sinusoids shifted by 90° in time. The  $\beta$  component is lagging 90° after  $\alpha$  for positive sequence system.

A natural property of the symmetrical three-phases system is that instantaneous sum of the three components is zero:

$$v_a(t) + v_b(t) + v_c(t) = 0$$

(2.1)

where the arbitrary  $v_a, v_b, v_c$  voltages represent an equal amplitude sinusoids shifted in space by 120°.

$$v_a(t) = V \cos(\omega_1 t) \tag{2.2}$$

$$v_b(t) = V \cos(\omega_1 t - 2\pi/3)$$

(2.3)

$$v_{c}(t) = V \cos(\omega_{1}t + 2\pi/3)$$

(2.4)

This enables to represent one of the components by the other two: e.g.  $v_c(t) = -(v_a(t) + v_b(t))$ , and description of the three-phase system in two phase is possible.

The general transformation from three to two phase system is given by (2.5):

$$\underline{v}(t) = v_{\alpha}(t) + jv_{\beta}(t) = \frac{2}{3}K \Big[ v_{a}(t) + v_{b}(t)e^{j2\pi/3} + v_{c}(t)e^{-j2\pi/3} \Big]$$

(2.5)

The zero sequence component is equal:

$$\underline{v}_{0}(t) = \frac{1}{3} \left( v_{a}(t) + v_{b}(t) + v_{c}(t) \right)$$

(2.6)

The selection of K can be arbitrary, depending on the application and implementation. One choice may be more convenient than another. The other commonly found in literature scaling factors are:

Peak value scaling:

$$K = 1$$

(2.7)RMS value scaling: $K = 1/\sqrt{2}$ Power invariant: $K = \sqrt{3/2}$

For K = 1 the amplitude of the *a* phase is equal to the  $\alpha$  component and both have the same phase. A zero angle is defined when  $\alpha$  is at the positive peak value and  $\beta$  is crossing zero. All transformations in this thesis uses peak valued scaled space vectors representation, often know as a non power invariant.

Since the  $v_a(t), v_b(t), v_c(t)$  are scalar values, and the rotation operator  $e^{j2\pi/3}$  can be expressed in scalar form too. The transformation can be expressed in equivalent matrix form as (2.8).

$$\begin{bmatrix} \alpha \\ \beta \\ o \end{bmatrix} = \frac{2}{3} K \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \cdot \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(2.8)

#### 2.1.1.1. Current transformation

The zero sequence component o does not exist in the current of the three-phase load provided that there is no neutral connection. The zero sequence voltage doesn't influence the load currents and it can be used to extend the linear operation of converter. Because in our system neutral wire is not used, o is not considered. Simplifying (2.8) and for K = 1 the  $\alpha$  and  $\beta$  component can be written as:

$$\alpha = a \tag{2.9}$$

$$\beta = \left(a + 2b\right) / \sqrt{3} \tag{2.10}$$

$$\beta = \left(-a - 2c\right)/\sqrt{3} \tag{2.11}$$

$$\beta = (b-c)/\sqrt{3} \tag{2.12}$$

The  $\beta$  equations (2.10), (2.11), (2.12) are redundant, and the selection depends on the number and phase position of sensors in the system. In most cases use of only two current sensors is sufficient. As far as there is no neutral wire the two current sensors can handle unbalanced and distorted conditions. The zero sequence current should be avoided, that means that the dc-link should not be coupled in any way with the output of the converter or load directly or by other components. This is true for most of the motor control. For detection of the leakage current adding the third sensor doesn't make sense, since the leakage current is usually very small and requires other more sensitive measuring circuits.

#### 2.1.1.2. Voltage transformation

When measuring three-phase voltage in the system without neutral connection, it is convenient to measure phase to phase voltage, since the neutral point is not accessible. Two sensors are required. Example of possible  $\alpha$ ,  $\beta$  transformation using two sensors in phases *ab* and *bc* result in:

$$\alpha = (2ab + bc)/3 \tag{2.13}$$

$$\beta = bc/\sqrt{3} \tag{2.14}$$

The  $\alpha$ ,  $\beta$  components from (2.13) and (2.14) do not contain the inherited 30° phase shift from phase-phase measurement, they are aligned with phase to neutral reference. The amplitude is scaled to mimics the phase to neutral measurement as well.

The transformation from  $\alpha$ ,  $\beta$  plane to three-phase system (*abc*) which is known as a reverse Clark transform is given by equation (2.15).

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 \\ -\frac{1}{2} & \frac{\sqrt{3}}{3} & 1 \\ -\frac{1}{2} & -\frac{\sqrt{3}}{3} & 1 \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \\ o \end{bmatrix}$$

(2.15)

#### 2.1.2. The Park transformation

The Park Transformation converts the stationary system into rotating system which is called synchronous coordinate or dq coordinates. A space vector which rotates in one

direction converted by Park transformation will be visible as a (not rotating, similar to the standard) complex phasor. The instantaneous angle of the space vector will be referenced to the  $\theta$  angle. This transform enables to see rotating vectors as dc quantities, thus simplifying analysis and control. The reference angle  $\theta$  for synchronous frame is usually synchronized with some other rotating quantity, e.g. voltage. It is important that the reference angle  $\theta$  rotates smoothly, therefore a PLL or virtual flux is often used. The Park and it's inverse transform are the foundation for regulation of rotating ac systems by using dc regulators. It is easier to design and analyze control for quantities which are constant (dc) rather than oscillating (ac) in the steady state.

The new system quantities are d (direct) and q (quadrate). The conversion from stationary system ( $\alpha$ ,  $\beta$ ) to synchronous (rotating) system is defined as:

$$\begin{bmatrix} d \\ q \end{bmatrix} = \begin{bmatrix} \cos(\theta) & \sin(\theta) \\ -\sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}$$

(2.16)

or in vector form:

$$\underline{v}_{dq} = e^{-j\omega t} \cdot \underline{v}_{\alpha\beta} \tag{2.17}$$

Where  $\theta = \omega t$ , and  $\omega$  is the angular speed of the synchronous reference frame,  $\underline{v}_{\alpha\beta}$  denote the space vector

The conversion from synchronous system to stationary is defined as:

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} d \\ q \end{bmatrix}$$

(2.18)

or in vector form:

$$\underline{v}_{\alpha\beta} = e^{j\omega t} \cdot \underline{v}_{dq} \tag{2.19}$$

In case of direct transformation from three-phase system (abc) to synchronous system (dq) the equation are given by:

$$\begin{bmatrix} d \\ q \end{bmatrix} = \frac{2}{3} K \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(2.20)

The reverse transformation to (2.20) are given by:

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{vmatrix} \cos(\theta) & -\sin(\theta) \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) \\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \end{vmatrix} \begin{bmatrix} d \\ q \end{bmatrix}$$

(2.21)

In the digital signal processing theory the Park transformation is known as a shift in frequency domain. Park transformation causes all frequency components to be shifted by a specified frequency. This is why 50  $H_z$  signal shifted with -50  $H_z$  become a DC signal; analogously the 250  $H_z$  signal becomes a 200  $H_z$ .

Considering the non-sinusoidal signals and transforming them to synchronous frame the sequence of the harmonic must me taken into account. The multiplies of  $3^{rd}$  harmonic (triplen harmonic) are the zero-sequence harmonics, thus even if they exist in the voltage they disappear from the currents. So in three-phase systems harmonics 5, 7, 11, 13, 19,... are those which needs to be taken care. An interesting observation is when signal contains 5th harmonics with negative sequence and  $7^{th}$  harmonic with positive sequence then they will appear in the synchronous frame as  $6^{th}$  harmonic (positive and negative). Analogously the same happens to the  $-11^{th}$  and +13 harmonic and so on.

#### **2.2.** Modeling of the ideal converter bridge

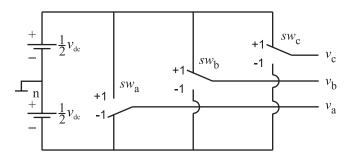

For the modeling and control purpose usually the ideal switch is assumed, Figure 2.1. The ideal switch changes position between positive and negative supply rail instantaneously and assumes that the voltage drop across the switches are zero. The neutral point is assumed to be in the middle of the splited dc-link voltage. For this configuration the  $sw_x$  signals can attain only two discrete values, +1 and -1 which corresponds to output phase connected to  $v_{dc}/2$  or  $-v_{dc}/2$ . Now we will introduce the continuous switching reference signals  $S_a$ ,  $S_b$ ,  $S_c$  which can be treated as a control signals. They define the proportion of the switch to be in the upper ( $sw_x = 1$ ) or lower ( $sw_x = -1$ ) position. Signal  $S_x$  equal of 0 means that the switch 50% of the time is in upper and 50% of the time in lower position. The output phase voltage is achieved by multiplying the reference signals  $S_a$ ,  $S_b$ ,  $S_c$  by  $v_{dc}/2$ . The  $v_a$ ,  $v_b$ ,  $v_c$  denote average converter output voltage related to n. In literature there are other reference configurations e.g. the reference ranges between 0 and 1 and the dc-link consist of one dc-source, with negative dc-bus rail as n.

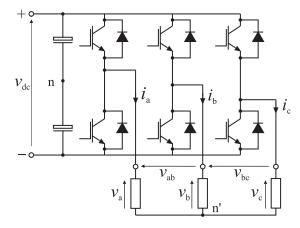

#### Figure 2.1: Switch model of three-phase VSC

The relationship between reference signal  $S_x$ , dc-link voltage and average output voltage is as follows:

$$v_a = \frac{1}{2} v_{dc} \cdot S_a \tag{2.22}$$

$$v_b = \frac{1}{2} v_{dc} \cdot S_b \tag{2.23}$$

$$v_c = \frac{1}{2} v_{dc} \cdot S_c \tag{2.24}$$

The phase to phase voltage relation to the reference signals are:

$$\begin{bmatrix} v_{ab} \\ v_{bc} \\ v_{ca} \end{bmatrix} = \begin{bmatrix} v_a - v_b \\ v_b - v_c \\ v_c - v_a \end{bmatrix} = \frac{1}{2} v_{dc} \begin{bmatrix} S_a - S_b \\ S_b - S_c \\ S_c - S_a \end{bmatrix}$$

(2.25)

In order to achieve three-phase symmetric voltages the  $S_x$  represents sinusoidal waveforms with equal amplitude, shifted by 120°.

$$v_a(t) = \frac{1}{2} v_{dc} M \cos(\omega_{\rm l} t)$$

(2.26)

$$v_{b}(t) = \frac{1}{2} v_{dc} M \cos(\omega_{1} t - 2\pi/3)$$

(2.27)

$$v_{c}(t) = \frac{1}{2} v_{dc} M \cos(\omega_{1} t + 2\pi/3)$$

(2.28)

Now the three-phase output voltage is characterized by two parameters,  $\omega_1$  and M. The  $\omega_1$  defines the angular frequency and M defines the maximum amplitude of the output voltage. The M is often called the modulation index and defines the linear range of converter operation. M range depends on the type of modulation used, in above case the range is ( $0 \le M \le 1$ ). The M > 1 causes saturation of the converter and distortion of the

output voltage (over-modulation). By adding zero sequence signals to  $S_a$ ,  $S_b$ ,  $S_c$  it is possible to extend the range of M. The discussion is below in this chapter.

Using the space vector notation, the voltage vector of the VSC  $\underline{v}_1$  can be expressed as:

$$\underline{v}_{1}(S_{a}, S_{b}, S_{c},) = \frac{v_{dc}}{2} \frac{2}{3} \left( S_{a} + S_{b} e^{j2\pi/3} + S_{c} e^{-j2\pi/3} \right)$$

(2.29)

And by introducing the switching reference space vector  $\underline{S} = Me^{j\omega_{1}t}$ , the (2.29) can be expressed as:

$$\underline{v}_1 = \frac{1}{2} v_{dc} \underline{S} \tag{2.30}$$

### 2.3. Modulation strategies

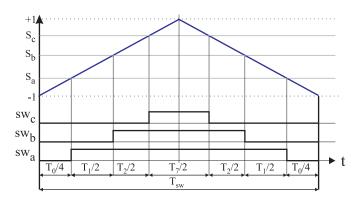

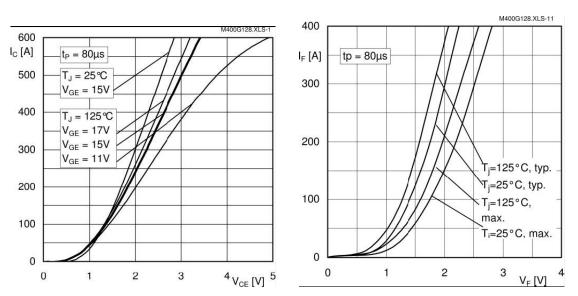

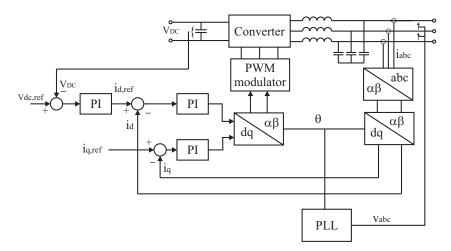

The modulation strategy will be discussed for the most common 2 level converter topology. A good reference for other modulation techniques is [mal5], [swe1] The modulator is responsible to produce timing pulses  $sw_a$ ,  $sw_b$ ,  $sw_c$  for the transistors from the switching reference signals  $S_a$ ,  $S_b$ ,  $S_c$ . There are many modulation strategies; the most common are: space vector modulation, sinusoidal modulation with 3<sup>rd</sup> harmonic, hysteresis. In Figure 2.2 the ideal switches from Figure 2.1 are replaced by two transistors and two anti-parallel diodes per bridge.

There are 6 signals that control the transistors. The two signals in each bridge are fully dependent of each other. If the top transistor is on state, the bottom transistor is off  $(sw_x=1)$ , and vice versa for  $(sw_x=-1)$ . From modeling point of view there is still three independent on/off signals belonging to each bridge  $(sw_a, sw_b, sw_c)$ .

Figure 2.2: Two level, three-phase converter with the load

With three binary control signals, there are 8 possible states in total. When all top or bottom transistors are on, the power is not supplied to the load. These two states are called zero vectors (or inactive states). The remaining 6 states are the active states. By

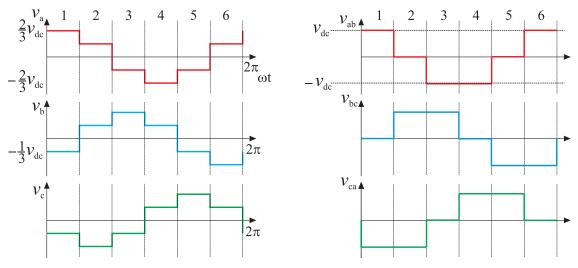

| applying consequent active vectors from Table 2.1 on the load from Figure 2.2 resultin | g |

|----------------------------------------------------------------------------------------|---|

| voltage can be seen in Figure 2.3.                                                     |   |

| Voltage<br>vector | <i>sw</i> a | <i>sw</i> <sub>b</sub> | <i>sw</i> <sub>c</sub> | Zero<br>Sequence            | $v_{\alpha}$    | $v_{\beta}$        |

|-------------------|-------------|------------------------|------------------------|-----------------------------|-----------------|--------------------|

| v0                | -1          | -1                     | -1                     | - <i>v</i> <sub>dc</sub> /2 | 0               | 0                  |

| v1                | 1           | -1                     | -1                     | - <i>v<sub>dc</sub></i> /6  | $v_{dc}^{2/3}$  | 0                  |

| v2                | 1           | 1                      | -1                     | <i>v<sub>dc</sub></i> /6    | $v_{dc}/3$      | $v_{dc}/\sqrt{3}$  |

| v3                | -1          | 1                      | -1                     | $-v_{dc}/6$                 | $-v_{dc}/3$     | $v_{dc}/\sqrt{3}$  |

| v4                | -1          | 1                      | 1                      | <i>v<sub>dc</sub></i> /6    | $-v_{dc}^{2/3}$ | 0                  |

| v5                | -1          | -1                     | 1                      | - <i>v<sub>dc</sub></i> /6  | $-v_{dc}/3$     | $-v_{dc}/\sqrt{3}$ |

| v6                | 1           | -1                     | 1                      | <i>v<sub>dc</sub></i> /6    | $v_{dc}/3$      | $-v_{dc}/\sqrt{3}$ |

| v7                | 1           | 1                      | 1                      | - <i>v<sub>dc</sub></i> /2  | 0               | 0                  |

Table 2.1: Individual vectors and associated states of converter bridges

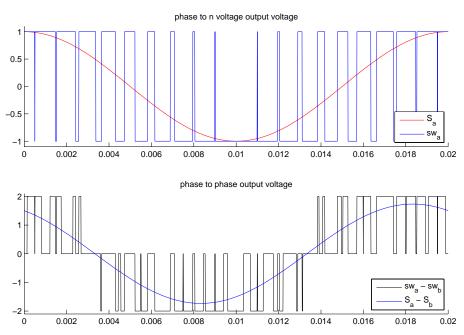

Figure 2.3: The phase output voltage related to dc-link voltage when a sequence of active vectors is applied. The left figure shows the voltage over resistor load when load phases are connected in star. The right figure shows the phase to phase output voltage.

This modulation strategy is called 6-step square modulation. There is no practical use of it for grid connected converters; however it serves the basics for space vector modulation. This modulation can be utilized in electric machines, e.g. brushless dc-motor (BLDC).

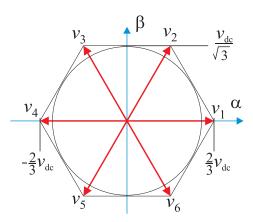

Figure 2.4: Red - active vectors in the  $\alpha$ ,  $\beta$  plane, that can only be obtained

It is visible in Figure 2.4 that by combining all switching states by using PWM including the zero vectors, any voltage inside the hexagon can be obtained. The zero vectors are placed in the origin of the Figure 2.4. The inscribed circle limits the linear modulation range, the radius of the circle is  $v_{dc}/\sqrt{3}$ . That leads to conclusion that the maximum obtainable phase voltage is:  $|\underline{v}_1|_{\text{max}} = v_{dc}/\sqrt{3}$

Extending modulation beyond the inscribed circle is called over-modulation. It results in distorted voltage waveforms and should not be used during steady state, however in transients can be used.

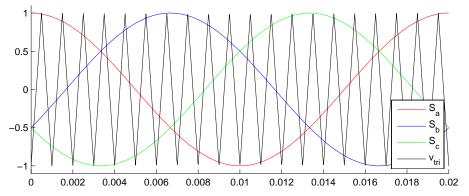

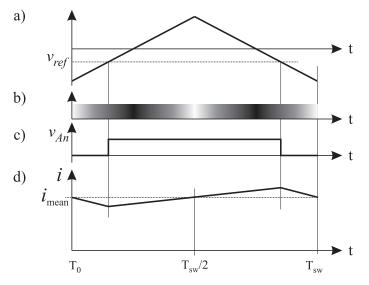

#### 2.3.1. Sinusoidal modulation

Sinusoidal modulation or carrier base modulation (CBM) is classical approach, often used in literature. Bases on comparison of triangular carrier signal with reference signals  $S_a$ ,  $S_b$ ,  $S_c$  seen in Figure 2.5. The comparison results are the logic signals ( $sw_a$ ,  $sw_b$ ,  $sw_c$ ) which switch on and off the transistors in given bridge (Figure 2.6). The three-phase reference signals are displaced in space by 120°.

Figure 2.5: Sinusoidal modulation signals. Black – triangular carrier signal, red, blue and green the modulation reference signals.

Figure 2.6: Modulation signal and gate signal which corresponds to output voltage. Upper - phase to neutral output voltage. Lower - phase to phase output voltage.

The switching frequency is constant and thus the voltage harmonics are concentrated around the carrier frequency and it's multiplies. The drawback is short linear operations range because the third harmonic zero sequence signals is not utilized.

The maximum peak phase output voltage is equal to half of dc-link voltage:

$$\left|\underline{v}_{1}\right|_{\max} = \frac{v_{dc}}{2} \tag{2.31}$$

or the maximum line to line peak voltage is:

$$\left|v_{l-l}\right| = \frac{\sqrt{3}v_{dc}}{2} = 0.866 \cdot v_{dc} \tag{2.32}$$

The reference control signals are calculated from modulation index M, and angular frequency  $\omega$ .

$$S_{a}(t) = M \cos(\omega_{1}t)$$

$$S_{b}(t) = M \cos(\omega_{1}t - 2\pi/3)$$

$$S_{c}(t) = M \cos(\omega_{1}t + 2\pi/3)$$

(2.33)

Linear range of operation is limited to  $0 \le M \le 1.0$ .

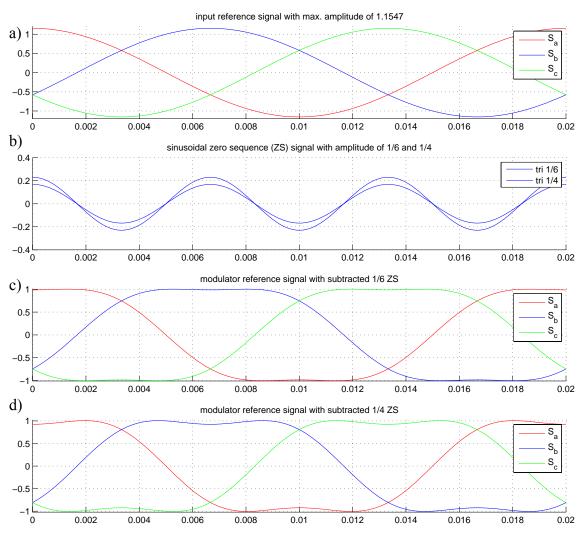

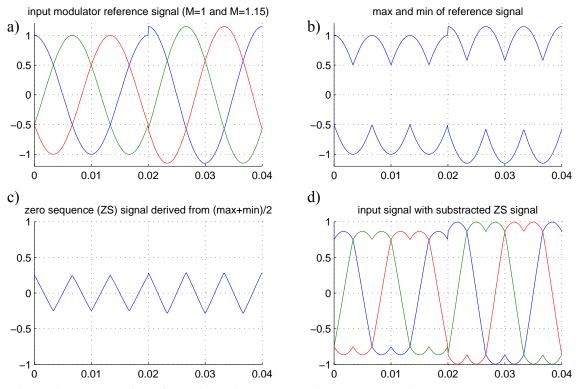

#### **2.3.2.** Sinusoidal modulation with the third harmonic

By adding the zero-sequence third harmonic signal to all three references the linear range can be expanded without causing over-modulation. The utilization of dc-link voltage is improved (Figure 2.7b) almost at no cost. The injected third harmonic zero sequence signals appears on each of the inverter terminal voltages  $v_{an}$ ,  $v_{bn}$ ,  $v_{cn}$  however it vanish from phase to phase voltage.

$$S_{a}(t) = M \cos(\omega_{1}t) + v_{0}$$

$$S_{b}(t) = M \cos(\omega_{1}t - 2\pi/3) + v_{0}$$

$$S_{c}(t) = M \cos(\omega_{1}t + 2\pi/3) + v_{0}$$

(2.34)

Where the zero sequence signal is:

$$v_0 = V_0 \cos(3\omega_1)$$

(2.35)

$V_0$  represents amplitude,  $V_0 \in \langle 0.166...0.25 \rangle$

Linear range of operation is  $0 \le M \le 1.15$ .

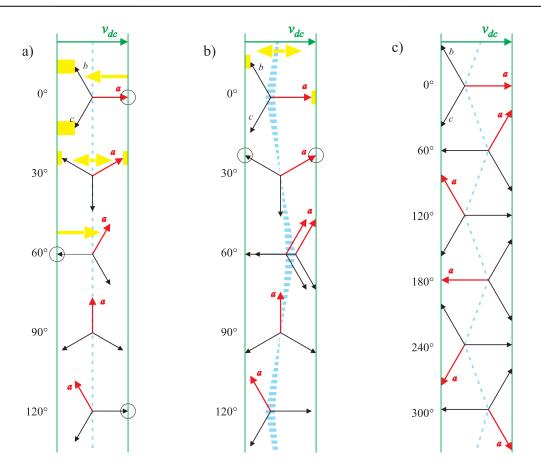

The zero sequence signals with the same amplitude and angle displacement cancel each other in each phase thus not causing line to line distortion. The Figure 2.7 is made in vertical fashion to illustrate the output voltage and boundary of the dc-link voltage. The horizontal axis reflects to real voltage (measurable) and thus the dc-link boundary can be placed vertical. This makes an easy visualization of the zero sequence signal, dc-link voltage and reference signals together. When the reference vector goes beyond the dc-link boundary the over-modulation occurs.

Figure 2.7: Different modulation strategies and different maximum reference voltages

The colors in the Figure 2.7 have the following meaning:

Green - available dc-link voltage span where the reference vector should be placed. Blue - the zero sequence component and its possible span.

Red - the reference a phase vector. The circle shows the limitation (end of linear range). Yellow - possibility of adding the zero sequence and its direction.

The following sub-figures in Figure 2.7 represents:

a) Sinusoidal modulation without third harmonic,  $|\underline{v}_1|_{\text{max}} = v_{dc} / 2$ .

b) Sinusoidal modulation with third harmonic,  $|\underline{v}_1|_{\text{max}} = v_{dc} / \sqrt{3}$ .

c) Six-step modulation and all its positions,  $|\underline{v}_1|_{\text{max}} = v_{dc} 2/3$

By adding the third harmonic ZSS the maximum phase to phase peak voltage is equal to the dc-link voltage,  $\hat{v}_{l-l} = v_{dc}$  thus the linear range is expanded by  $2/\sqrt{3}$ , which give 15.5 % gain compared to its version without ZSS.

The freedom in shape selection of zero-sequence signal is visible in Figure 2.7b as a blue vertical band. Based on Figure 2.7b the amplitude of the ZSS can be calculated and it should be in the range of 0.166 to 0.245 of the reference amplitude. In practice however this method is not so common due to extra effort to calculate the ZSS.

Figure 2.8: Sinusoidal modulation with it maximum and minimum allowed amplitude of sinusoidal zero sequence signal.

As it can be seen in Figure 2.8c the addition of ZSS with amplitude of 1/6 causes almost one phase to be continuously on. This is not desired, since the effective switching frequency is lower and the current ripple can increase. However if properly designed it can be used to decrease switching losses. This type of modulation is called discontinuous modulation. The addition of ZSS with amplitude of 0.25 (Figure 2.8d) improves the situation, but it is clear that the sinusoidal shaped ZSS is not optimal. This is because the shape (Figure 2.8d, blue, between 5 to 8 *ms*) on top side is different than on bottom (green and red).

From practical point of view it is important to keep references away from inverter saturation boundary. In those instances the sensor measurement normally is performed. For the most common symmetrical synchronous sampling method, prevention of switching in this region will cause less noise which can influence the sensor reading.

A good practice would be to limit the duty ratio slightly (e.g. to 99.5 %) to ensure that no switching is performed during measurement, this will not have any influence from control point of view.

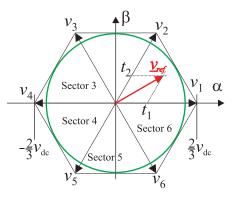

#### 2.3.3. Space vector modulation

The SVM bases on vector representation and the proportional selection of converter available states during the switching period. In two-level converter there are six active vectors and two zero vectors (Figure 2.9) to choose from. The states are the same as in the case of six-step modulation shown in Figure 2.7c. The main idea behind SVM is that it uses formula to calculate timing of active (2.36), (2.37) and zero (2.38) vectors. The  $t_1$  and  $t_2$  are the duration time of two neighbor's active states in given sector, the rest of the time  $t_0$  is used for zero vectors. So instead using reference triangular carrier, the equations below are used to calculate the duty ratio of the transistor bridges.

Figure 2.9: Space vector diagram of 2-level converter.

$$t_1 = \frac{\sqrt{3} \cdot T_{sw} \cdot v_{ref}}{v_{dc}} \cdot \sin\left(\frac{\pi}{3} - \theta\right)$$

(2.36)

$$t_2 = \frac{\sqrt{3} \cdot T \cdot_{sw} v_{ref}}{v_{dc}} \cdot \sin(\theta)$$

(2.37)

$$t_0 = T_{sw} - t_1 - t_2 \tag{2.38}$$

The maximum magnitude of the reference vector  $\underline{v}_{ref}$  corresponds to the radius of the largest circle inscribed within the hexagon shown in Figure 2.9. Since the hexagon is formed by six active vectors having a length of  $2v_{dc}/3$ , the maximum reference can be found as:  $\left|\underline{v}_{ref,max}\right| = \frac{2v_{dc}}{3} \cdot \frac{\sqrt{3}}{2} = \frac{v_{dc}}{\sqrt{3}}$ , which is the same result as carrier base modulation with ZSS.

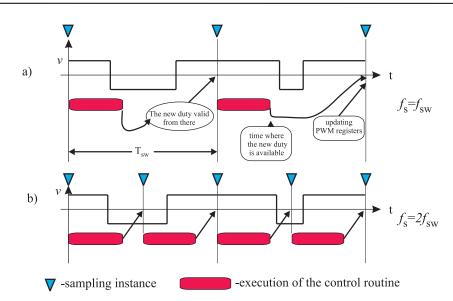

The implementation of SVM needs first to calculate the current sector and angle inside it. Based on the angle in the range of first sector the proportion of two active and one zero-vector is calculated as,  $t_1$ ,  $t_2$  and  $t_0$ . The zero state  $t_0$  is usually split into half ( $t_0$  and  $t_7$ ) for symmetrical PWM and minimum number of possible switching. The duty ratio is calculated for individual phases and then programmed into PWM registers. The implementation of the PWM unit in most microcontrollers consists of a timer and three compare units. When the counting timer value match the compare value a switching action occurs.

26

Figure 2.10 Symmetrical Space Vector Modulation, timing diagram

The SVM gives the same linear operation range as carrier based modulation with ZSS. The only difference is in the treatment of variables. In case of sinusoidal modulation the treatment is in natural coordinates and in case of SVM the timing are calculated based on equations (2.36), (2.37), (2.38). The SVM is probably the most common method to derive transistors timing due to its simplicity. More detail can be found in [mal5], [gul2].

There are various modifications of SVM, the aim is to decrease switching losses by introducing switching only in two phases, where the third bridge is continuously on. This group of modulations is called discontinuous SVM (DSVM) and is more described in [mal5]. The disadvantage is that the effective switching frequency is reduced by 33 % but at the same time the switching losses can be decreased up to 50 % dependent on the power factor.

There are some comments regarding implementing on low end DSP or microcontroller. The SVM calculations for the low end DSP system is quite demanding as for the job of only deriving timing pulses. It uses trigonometric functions which are often not available or time optimized on microcontrollers. Implementation often uses *switch* and multiple *case* statements, which are used to find the proper sector (0 to 5), those are causing slightly varying execution time. The simple method presented below presents similar functionality to SVM but with much less of computational burden.

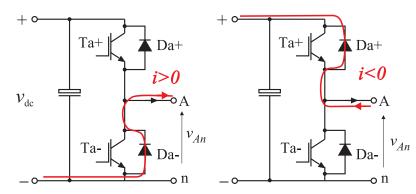

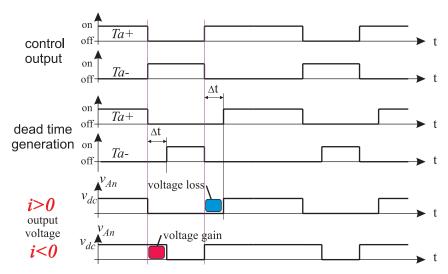

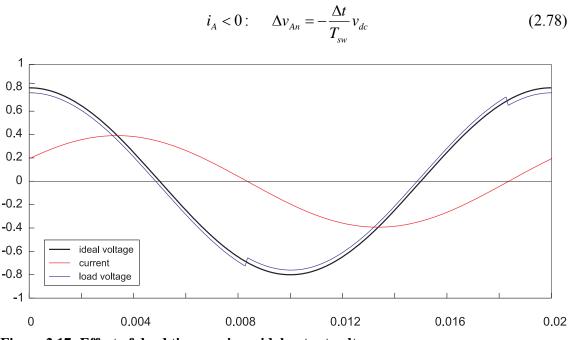

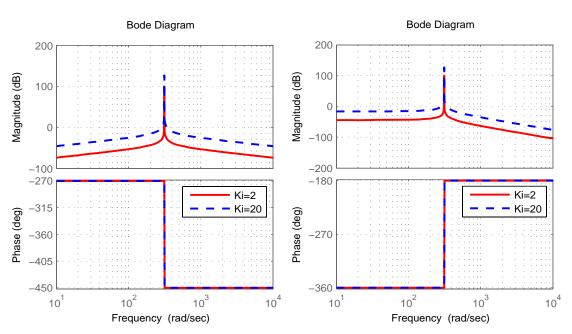

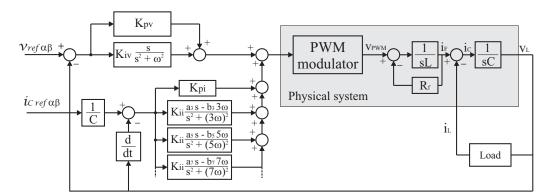

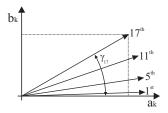

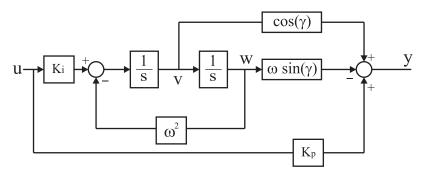

## 2.3.4. Symmetrical sub-oscillation method