Doctoral theses at NTNU, 2009:38

Giuseppe Guidi

# Energy Management Systems on Board of Electric Vehicles, Based on Power Electronics

Thesis for the degree of Philosophiae Doctor

Trondheim, March 2009

Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering Department of Electric Power Engineering

ISBN 978-82-471-1445-2 (printed ver.) ISBN 978-82-471-1446-9 (electronic ver.) ISSN 1503-8181

# Preface

The tale of the Electric Vehicle is an interesting one. The subject has generated passionate discussions since the advent of personal transportation for the masses, in the beginning of the 19<sup>th</sup> century. Since then, countless times the electric car has been announced as the next world-saving technology, and an equivalent number of times the same technology has been discarded as hopeless.

Now, on the verge of increasing oil prices and environmental awareness, once again there are enthusiasts convinced that the struggle may have come to an end, and the public can finally enjoy the pleasure of driving quiet, non-polluting vehicles. This thesis is intended to be a small contribution to the cause of this wonderful historical loser that is the electric car.

It has to be said that if it was not for Marta, the thesis would probably be about the application of power electronics to some kind of active filtering technique for power quality: certainly a technically sound and important subject, but not nearly as charming as automotive. It was Marta that convinced me that I should have dedicated myself to this theme and, as it is too often the case, she proved right: working on the thesis has been a stimulating and rewarding experience, to the point that I am almost sad that it has finally come to an end.

During the four-year-long stay at NTNU, I have become a richer person, and have struggled to become a better one. I have received the best gift a man could ask for, and her name is Virginia. I have seen our eldest daughter, Sofia, growing up and learning a number of languages that I would have not dreamed about when I was her age. I have witnessed Marta fulfilling one of her objectives as she was appointed with Professorship. Obviously, a single page is hardly enough to thank for all that.

Special thanks go to my supervisor, prof. Tore Undeland, who backed my decision of such a sudden shift in the working subject and has worked hard to establish contacts with the Norwegian electric car company Th!nk, whose economical help has been very helpful for building the experimental prototypes.

1

The support of my co-supervisor, prof. Yoichi Hori, has also been fundamental, bringing his knowledge and working experience with supercapacitors applied to electrical transportation, and hosting me in Tokyo University for three months.

During my research stay at ENO, I have enjoyed exchanging ideas with my fellow PhD candidates Erik, William and Pål, and with my friend Supratim: I thank them all for the time they have spent, listening to my problems and ideas, and for the suggestions that those discussions have brought forward.

Moreover, I wish to express my gratitude to Vladimir and Bård, who helped me building the experimental prototypes, and to Inger and Eva who have been my references for solving all kind of administrative matters.

The PhD project has been funded by the Department of Electric Power Engineering, Norwegian University of Science and Technology, NTNU. The last year of research has been funded by the NFR project N. 146524/210, "Technologies for reliable distributed generation of electric power from renewable energy sources."

Trondheim, December 2008

Ginsepe Guidi

Giuseppe Guidi

# Abstract

The core of any electric vehicle (EV) is the electric drive train, intended as the energy conversion chain from the energy tank (typically some kind of rechargeable battery) to the electric motor that converts the electrical energy into the mechanical energy needed for the vehicle motion.

The need for on-board electrical energy storage is the factor that has so far prevented pure electric vehicles from conquering significant market share. In fact electrochemical batteries, which are currently the most suitable device for electrical energy storage, have serious limitations in terms of energy and/or power density, cost and safety. All those characteristics reflect in pure electric vehicles being outperformed by standard internal combustion engine (ICE) based vehicles in terms of driving range, time needed to refuel and purchase cost.

Electric vehicles do have their distinctive advantages, being intrinsically much more efficient, operating at zero emissions at the pipe, and offering a higher degree of controllability that can potentially enhance driving safety. No wonder then, that electric energy storage technology has attracted considerable R&D investments, resulting in new traction battery packs that are getting closer and closer to the industrial targets.

In this scenario of EV technology gaining momentum, power electronics engineers have to come up with newer solutions allowing for more efficient and more reliable utilization of the precious on-board energy that comes in a form that cannot be directly utilized by the motor. At present, most of the research in the area of power electronics for automotive is focused in volume and cost reduction techniques. The increase in power density is pursued by developing components that can be operated at higher temperature, thus relieving the requirements on cooling.

In this thesis, the focus is on the development of alternative topologies for the power electronics converters that make use of some peculiarities of the energy storage components and of the electrical drive train in general, rather than being a mere component-level optimization of well established topologies.

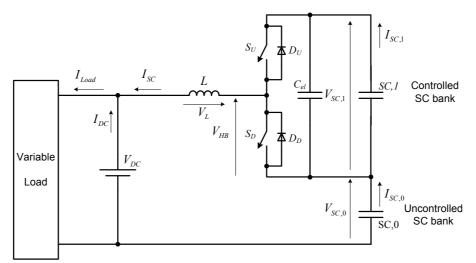

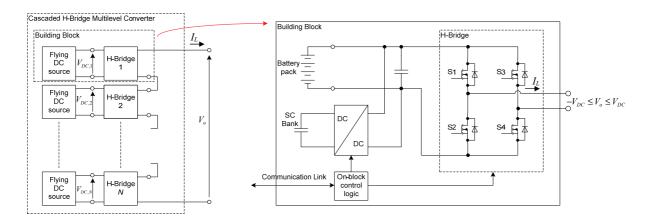

A novel converter topology is proposed for hybridization of the energy source with a supercapacitor-based power buffer being used to assist the main traction battery. From the functional point of view, the topology implements a bidirectional DC/DC converter.

Making use of the fact that the battery terminal voltage is close to constant, an arrangement for the supercapacitors is devised allowing for bidirectional power flow by using power electronics devices of lower ratings than the ones needed in conventional DC/DC converters. At the same time, much smaller magnetic components are needed. Theoretical analysis of the operation of the proposed converter is given, allowing for optimized design. A full-scale experimental prototype rated at 30 kW, intended for use in a pure EV, has been built and tested. Results validate the theory and show that no particular impediment exist to the deployment of the concept in practical applications. Another concept introduced in the thesis is an architecture where the traction inverter is embedded in the energy storage device. The latter is constituted by several modules, as in the case of modern Li-ion battery systems, and each module is equipped with a local power electronics interface, making it functionally equivalent to a controllable voltage source. The result is a modular, distributed system that can be engineered to have very high reliability and also to exhibit self-healing properties. A prototype with a minimum number of modules has been built and tested. Results confirm the effectiveness of the system, and make it a good candidate for deployment in applications where reliability is the most important requirement.

## Introduction

Power electronics plays an important role in the modern automotive industry, helping carmakers to improve the performance of their fleet while reducing energy consumption and emissions.

In electric vehicles (EV), where there is at least one electric motor contributing to the traction effort, power electronics converters are used to control the bidirectional power flow between the electrical energy tank (usually a rechargeable battery) and the motor. Additional converters are necessary when there are several electrical sources with different terminal characteristics that share the duty of supplying the motor. Due to the limited amount of energy per unit of mass that can be stored in electrochemical batteries, or in any other kind of electrical energy storage device to date, efficiency of the overall conversion chain is paramount. Moreover, on-board space is a very valuable commodity in automotive, leading to strict requirements in volume reduction, with resulting increase in power density of the required converters. Needless to say, higher efficiency and higher power density have to be achieved while decreasing the cost and increasing the reliability.

Taking the traction inverter as an example, the targets above are mainly being pursued by the introduction of advanced thermal management [1] and by the replacement of unreliable components like the electrolytic capacitors with analogous components built with a different technology [2]. New materials like SiC are also being investigated for the switching devices, in order to extend the working temperature range and to reduce losses [3,4]. However, from the topological point of view, the classical six-switches inverter structure is not likely to be replaced, and the only allowance for change is coming from the proposals of several soft switching techniques for loss reduction [5,6]. One aspect that influences the design of the overall power train is modularity, meaning that there is very little interaction at the design stage between the engineering teams working on the energy source (the advanced traction battery) and those working on the power electronics that should enable the energy exchange between that source and the traction motor. The battery module should make energy available at its terminals that should be possible to exchange at a sufficiently high rate (power) with sufficiently high efficiency, while the terminal voltage remains within reasonable range. The inverter should be able to supply the motor, over the whole terminal voltage range of the battery. It is clear that the modular approach introduces some constraints in the specifications at the boundary between blocks (the DC-link voltage, in this specific case) that are in principle not related to the main purpose of the drive train: simply exchange energy at a given rate between the source and the motor.

Following this line of reasoning, it is possible that blending the design of the battery pack with that of the traction inverter leads to different system topologies that are worth to investigate. One of them, based on modular architecture where there is no neat distinction between the battery pack as a whole and the traction inverter, is investigated in the thesis.

When combining two energy sources having different electrical characteristics at the terminals, a power electronics interface is needed to allow controllable power flow. Specifications of the required converter are often given in terms of min-max of the input and output voltage and current, according to the characteristics of the sources. A deeper understanding of the dynamic electrical behaviour of the sources may however lead to a more optimized converter design. A practical application of this approach, where the capacitive behaviour of supercapacitors, along with the constant voltage behaviour of battery is explicitly taken into account during the converter design stage, can be found in the thesis.

## Main contribution

The thesis has aimed at finding new methods for the interconnection of the classical components of an electrical traction system, based on dedicated power electronics topologies.

Throughout the thesis, the drive system as a whole has been considered, trying to take advantage of system-related aspects that are normally overlooked in a component-oriented approach.

Main contribution can be stated as follows:

- Introduction of a new power electronics converter topology for bidirectional power flow control between a supercapacitor-based power buffer and a battery, or any other energy source having DC terminal voltage characteristics.

- Detailed theoretical description of the concept, forming the basis for optimized converter design. It has been shown that the resulting converter uses considerably less silicon and much smaller magnetic components compared to standard topologies.

- Experimental verification of the power buffer on a real-scale prototype, showing that the concept is feasible and that the claimed advantages can be achieved in practice.

- Proposal of a distributed architecture where the traction inverter is embedded in the battery pack; in this vision, the energy tank is constituted by a large number of battery modules, each equipped with a power electronics interface, making it functionally equivalent to a controllable voltage source. Outstanding reliability is achieved due to the distributed nature of the system.

- Realization of the distributed architecture with a minimum number of modules, showing the self-healing property of such a distributed, intelligent system.

## Thesis outline

The thesis is logically divided into four parts.

Chapter 1 and Chapter 2 contain background information needed for the understanding of the original concepts introduced later in the thesis.

In particular, Chapter 1 focuses on basic description of the main components found in the electrical drive train of pure electric vehicles (EVs) and internal combustion – electric hybrid vehicles (HEV); Emphasis is put on the electrical energy storage devices (batteries and supercapacitors), and the modelling of their electrical characteristics. Readers that are already familiar with the basic characteristics of an electric drive train and have some basic knowledge about traction batteries and supercapacitors may consider skipping this introductory chapter.

Chapter 2 describes the hybridization of the source of electrical energy on board of EVs; the combination of battery and supercapacitor is analyzed in detail, and its advantages are highlighted.

Chapter 3 to Chapter 5 describe the newly developed power electronics converter for power flow control between a supercapacitor-based power buffer and a battery, and are therefore the core of the thesis.

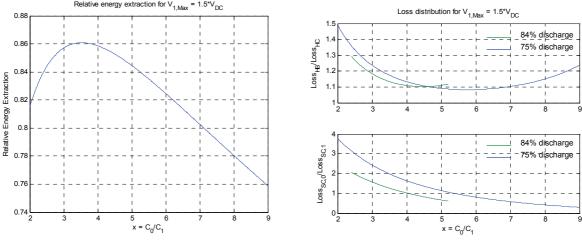

Chapter 3 gives the theoretical foundations of the proposed system and the equations governing its ideal operation are presented. Guidelines for optimal design of the system are also developed, based on an analytical approach.

Chapter 4 addresses the several issues arising when real-world components are utilized to build the converter, setting the basis for actual implementation of the proposed principle.

Chapter 5 contains details about the design and implementation of a real-scale prototype based on the proposed topology, intended for use in a small city vehicle like the Norwegian Th!nk EV. Experimental results are presented, demonstrating the feasibility and the advantages of the newly developed concept.

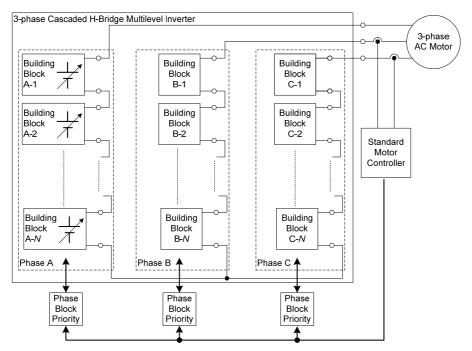

Chapter 6 describes the concept of a redundant, self-healing architecture for the implementation of the traction inverter in the drive system of an EV. A multilevel structure based on cascaded H-bridges, particularly well suited for battery EVs, is used to develop a decentralized, modular topology featuring a high degree of reliability. Both simulations and experimental results are presented, with some emphasis on the hardware design and on the communication system necessary to achieve redundancy and self-healing.

Finally, conclusions are drawn in Chapter 7, along with possibilities for further investigation and development in the field of power electronics applied to electrical transportation.

### Publications generated by the PhD research work

#### Journals

- 1. <u>G.Guidi</u>, T.Undeland, Y.Hori, "An Interface Converter with Reduced Volt-Ampere Ratings for Battery-Supercapacitor Mixed Systems". IEEJ Trans. on Ind. Applicat. (D), Vol.128, No.4, 2008.

- 2. <u>**G.Guidi**</u>, T.Undeland, "Redundant and Self-Healing Drive System for Pure EV Based on Low Voltage Building Blocks". The World Electric Vehicle Association Journal, WEVA, Vol.1, 2007.

#### International, peer-reviewed, conferences

- 1. <u>G.Guidi</u>, T.Undeland, Y.Hori, "Optimized Power Electronics Interface for Auxiliary Power Buffer Based on Supercapacitors". Proc. of IEEE Vehicular Power Propulsion Conference VPPC08, Harbin, China, 2008.

- 2. <u>G.Guidi</u>, T.Undeland, Y.Hori, "An Optimized Converter for Battery-Supercapacitor Interface". Proc. of Power Electronics Specialists Conference PESC07, Orlando, 2007.

- <u>G.Guidi</u>, T.Undeland, Y.Hori, "An Interface Converter with Reduced Volt-Ampere Ratings for Battery-Supercapacitor Mixed Systems". Proc. of Power Conversion Conference PCC07, Nagoya 2007. (Awarded as Best Paper in PCC '07).

- 4. <u>**G.Guidi**</u>, T.Undeland, "Redundant and Self-Healing Drive System for Pure EV Based on Low Voltage Building Blocks". Proc. of Electric Vehicle Symposium, EVS21, Yokohama, 2006.

- 5. <u>G.Guidi</u>, T.Undeland, Y.Hori, "Effectiveness of Supercapacitors as Power-Assist in Pure EV Using a Sodium Nickel-Chloride Battery as Main Energy Storage". Accepted for presentation at EVS24, 13-16 May, 2009, Stavanger, Norway.

- P.Anreassen, <u>G.Guidi</u>, T.Undeland, "Digital variable frequency control for zero voltage switching and interleaving of synchronous buck converters", Proc. of EPE-PEMC 2006, Portoroz, Slovenia, 2006

- 7. S.Basu, T.Undeland, <u>G.Guidi</u>, "Voltage and current ripple considerations for improving ultra-capacitor lifetime while charging with switch mode converters", European Conference on Power Electronics and Applications, EPE 2007, Aalborg, Denmark.

- 8. J.I.Leon, <u>G.Guidi</u>, L.Franquelo, T.Undeland, S.Vazquez, "Simple control algorithm to balance the DC-link voltage in multilevel, four-leg, four-wire diode clamped converters", Proc. of EPE-PEMC 2006, Portoroz, Slovenia, 2006

# LIST OF ABBREVIATIONS

| CAN    | Controller Area Network                           |

|--------|---------------------------------------------------|

| CRC    | Cyclic Redundancy Check                           |

| DOD    | Depth Of Discharge                                |

| DSP    | Digital Signal Processor                          |

| EDLC   | Electric Double Layer Capacitor                   |

| EMI    | Electro-Magnetic Interference                     |

| ESR    | Equivalent Series Resistance                      |

| EV     | Electric Vehicle                                  |

| FCV    | Fuel Cell Vehicle                                 |

| HB     | Half Bridge                                       |

| НС     | Half Controlled                                   |

| HEV    | Hybrid Electric Vehicle                           |

| IC     | Internal Combustion                               |

| ICE    | Internal Combustion Engine                        |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| IPM    | Intelligent Power Module                          |

| LPF    | Low Pass Filter                                   |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

| OCV    | Open Circuit Voltage                              |

| PWM    | Pulse Width Modulation                            |

| SC     | Supercapacitor                                    |

| SOC    | State Of Charge                                   |

# TABLE OF CONTENTS

\_\_\_\_

| Pri | EFACE |                                  |                                                                                                                                                                                                         | 1            |

|-----|-------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Ав  | STRAC | ст                               |                                                                                                                                                                                                         | 3            |

| ΙΝΤ | RODU  | CTION .                          |                                                                                                                                                                                                         | 5            |

| 1   | OVE   | RVIEW                            | OF EV TECHNOLOGY                                                                                                                                                                                        | 13           |

|     | 1.1   | Electric                         | c drive train                                                                                                                                                                                           | . 13         |

|     | 1.2   | <i>Batter</i> y<br>1.2.1         | <i>technology</i><br>Modelling of batteries for power electronics applications                                                                                                                          |              |

|     | 1.3   | <i>Superc</i><br>1.3.1           | apacitors<br>Modelling of supercapacitors for power electronics applications                                                                                                                            |              |

| 2   |       |                                  | ERGY SOURCES – COMBINATION OF BATTERIES WITH                                                                                                                                                            | 27           |

|     | 2.1   |                                  | energy sources                                                                                                                                                                                          |              |

|     | 2.2   | -                                | -Supercapacitor combination<br>Power flow control within systems with hybrid energy source                                                                                                              | . 29         |

|     |       | 2.2.2<br>2.2.3                   | Simulation of a battery-supercapacitor hybrid energy source<br>Effect of battery-supercapacitor hybridization on key performances of<br>a pure electric city vehicle                                    | . 33         |

|     | 2.3   |                                  | electronics solutions for controllable power flow in battery-supercapacitors<br>energy sources                                                                                                          | . 43         |

| 3   | Ορτι  | MIZED                            | CONVERTER FOR BATTERY-SUPERCAPACITOR INTERFACE                                                                                                                                                          | 47           |

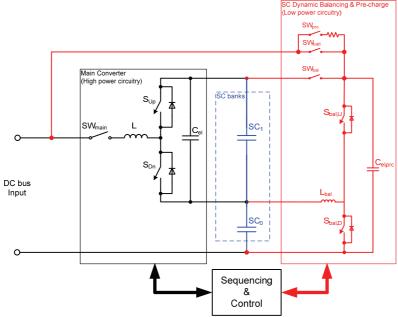

|     | 3.1   | Operat                           | ing Principle                                                                                                                                                                                           | . 48         |

|     | 3.2   | Energy                           | Cycling Capabilities                                                                                                                                                                                    | . 50         |

|     | 3.3   | Compa<br>3.3.1<br>3.3.2          | arison of the Proposed System to an Equivalent Half-Bridge Based System.<br>Required Volt-Ampere rating of converter switches<br>Idealized Voltage-Current waveforms during constant power<br>discharge | . 53         |

|     | 3.4   | Evalua                           | tion of System Losses                                                                                                                                                                                   | . 58         |

|     |       | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | Losses in the Supercapacitor Banks<br>Losses in the Solid State Switches<br>Losses in the smoothing inductor<br>Losses in the electrolytic capacitor                                                    | . 61<br>. 66 |

|     | 3.5   | Genera                           | alized equations of HC system for optimal design                                                                                                                                                        | . 69         |

|     |       | 3.5.1                            | Ideal limit for the utilization of the SC energy                                                                                                                                                        | . 73         |

| 4   | Issu  | ES FOR                           | ACTUAL CONVERTER IMPLEMENTATION                                                                                                                                                                         | 75           |

|     | 4.1   | The Ef                           | fect of Losses on Converter Operation                                                                                                                                                                   | . 75         |

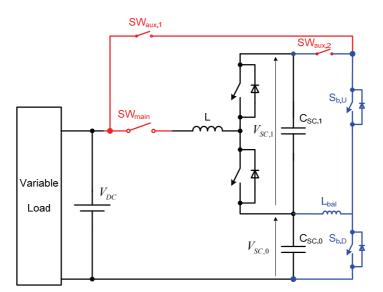

|     | 4.2   | Dynam                            | nic Voltage Balancing                                                                                                                                                                                   | . 80         |

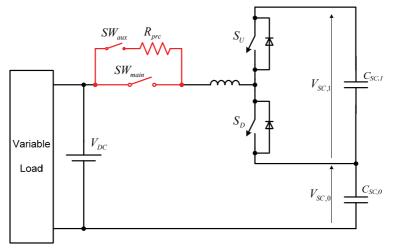

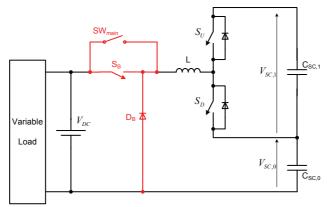

|          | 4.3  | Pre-charge of SC banks                                                     | 84  |

|----------|------|----------------------------------------------------------------------------|-----|

|          |      | 4.3.1 Pre-charge through a switched resistor                               | 85  |

|          |      | 4.3.2 Pre-charge through an auxiliary buck converter                       |     |

|          |      | 4.3.3 Pre-charge through the balancing circuit                             | 88  |

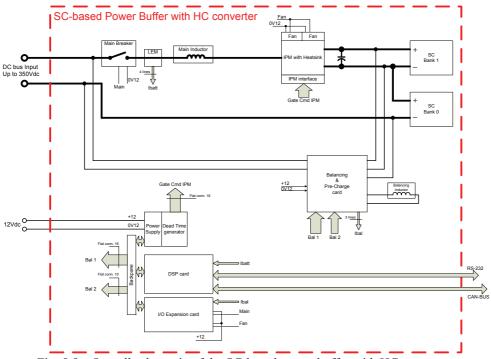

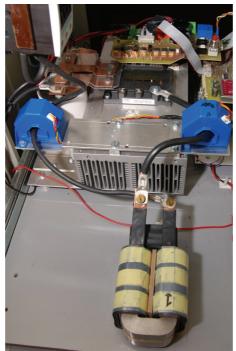

| 5        | Con  | IVERTER DESIGN FOR THE CITY CAR "TH!NK EV"                                 | 91  |

|          | 5.1  | System Specifications                                                      | 92  |

|          | 5.2  | SC-based power buffer design based on proposed optimized topology          | 95  |

|          |      | 5.2.1 SC bank design                                                       | 96  |

|          |      | 5.2.2 Smoothing inductor design                                            | 98  |

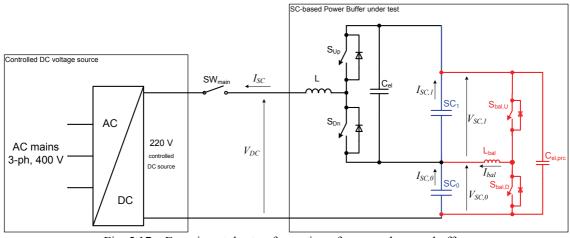

|          |      | 5.2.3 Design of the main power circuit for HC converter                    |     |

|          |      | 5.2.4 Design of the balancing and pre-charge circuit                       |     |

|          |      | 5.2.5 Digital controller board                                             | 104 |

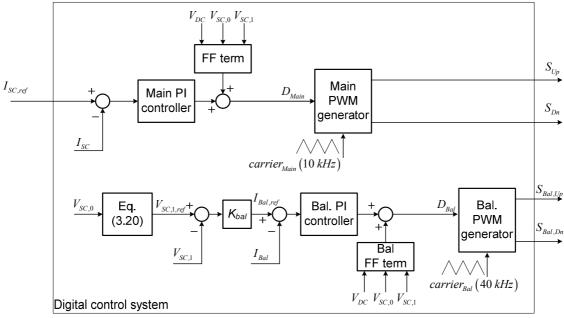

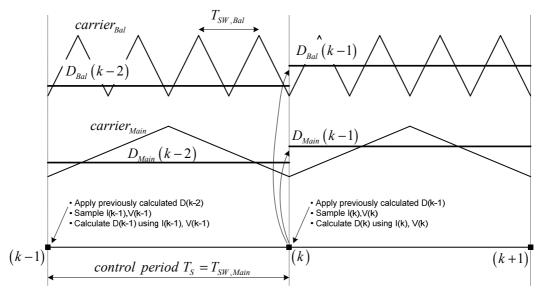

|          | 5.3  | Digital control system for the proposed SC-based power buffer              | 104 |

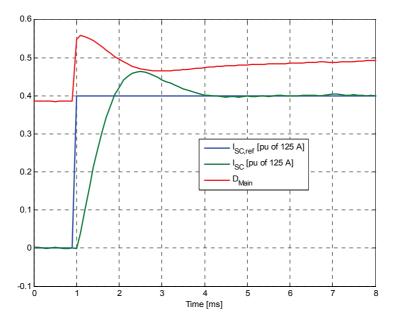

|          |      | 5.3.1 Main current controller                                              |     |

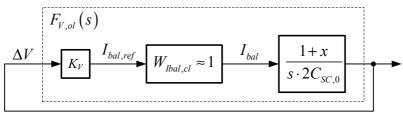

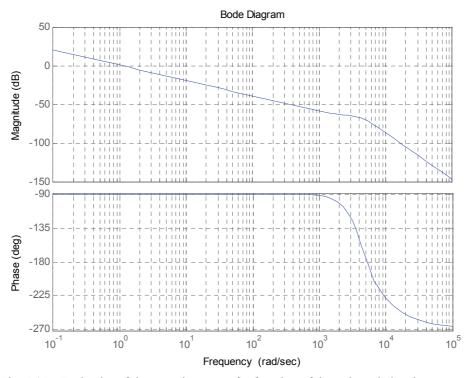

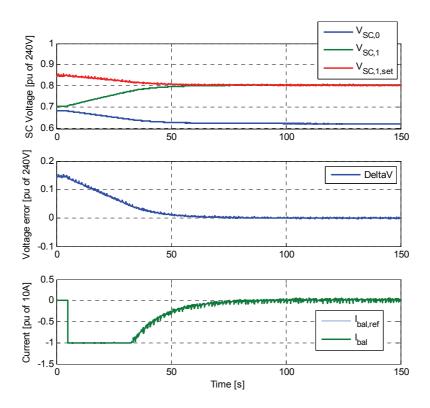

|          |      | 5.3.2 Voltage balancing algorithm                                          | 107 |

|          | 5.4  | Experimental Results                                                       | 110 |

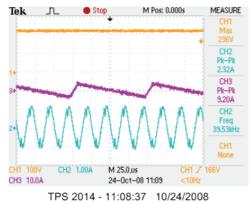

|          |      | 5.4.1 Switching waveforms                                                  | 111 |

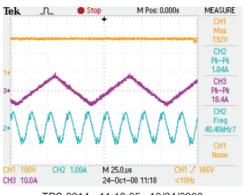

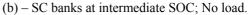

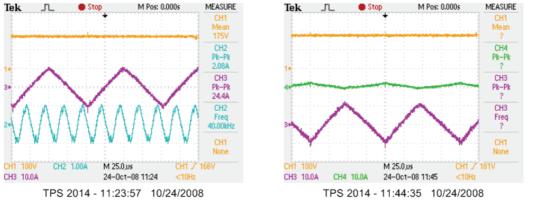

|          |      | 5.4.2 SC-based power buffer operation                                      | 112 |

|          |      | 5.4.3 SC-based power buffer efficiency                                     | 114 |

| 6        | Dist | FRIBUTED INVERTER STRUCTURE BASED ON CASCADED H-BRIDGE                     |     |

|          | Тор  | OLOGY                                                                      | 121 |

|          | 6.1  | Introduction                                                               | 121 |

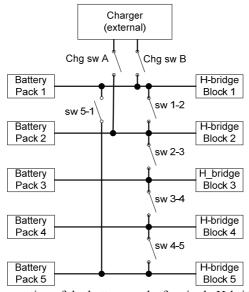

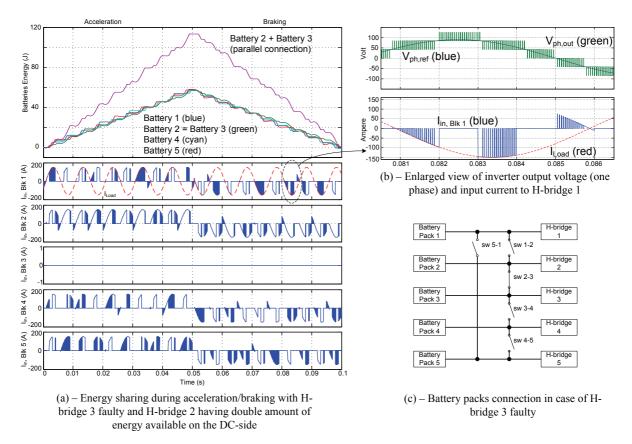

|          | 6.2  | System Description                                                         | 122 |

|          | 6.3  | Operating Principle and Dynamic Charge Balancing                           | 123 |

|          | 6.4  | Redundancy and Self-Healing properties                                     | 125 |

|          | 6.5  | Design considerations                                                      | 127 |

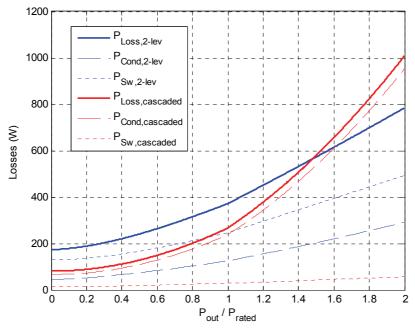

|          |      | 6.5.1 Selecting Number of Levels and Individual Voltage of Building Blocks |     |

|          |      | 6.5.2 Efficiency and EMI considerations                                    |     |

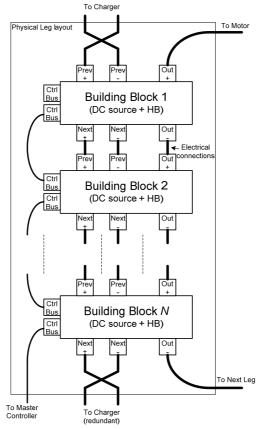

|          |      | 6.5.3 System Layout and Control Structure                                  | 130 |

|          | 6.6  | Serial Communication Protocol for Distributed Operation                    | 131 |

|          |      | 6.6.1 Communication protocol during converter operating phase              | 134 |

|          |      | 6.6.2 The physical layer of the bus and the practical implementation       | 136 |

|          | 6.7  | Experimental Setup and Results                                             | 137 |

|          | 6.8  | Concluding remarks                                                         | 140 |

| 7        | Сом  | ICLUSION                                                                   | 141 |

|          | 7.1  | Concluding remarks                                                         | 141 |

|          | 7.2  | Prospects for future investigation                                         |     |

| <b>-</b> |      | NCES                                                                       | 115 |

## **1** OVERVIEW OF EV TECHNOLOGY

#### 1.1 Electric drive train

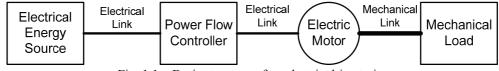

An electric drive train is a system that converts electrical energy into mechanical energy and, in its most classical form can be seen as constituted by four main elements:

- An electrical energy source;

- An electric power flow controller;

- An electric motor;

- A mechanical load

Fig. 1.1 – Basic structure of an electric drive train.

In some cases, the power flow can be reversed, allowing energy to be transferred back from the load to the electrical energy source. This operating mode in often referred to as "regenerative operation" or "regenerative braking".

All kinds of electric vehicles feature at least one electric drive train. In pure EV, the energy source is typically a rechargeable battery (secondary battery), and the electric motor is the only machine contributing to the traction effort. Fuel cell vehicles (FCV) have a very similar drive system, with the only difference that the primary source of electrical energy is a fuel cell; FCVs usually feature hybrid electric source (see chapter 2) to allow for regenerative operations and to achieve better efficiency. Hybrid vehicles (HEV) feature at least one additional internal combustion (IC) engine, contributing to the traction effort. In those vehicles, IC engine and electrical machine(s) can be coupled in a variety of ways, giving rise to several architectures whose description can be found in [7]. Detailed description of HEV is beyond the scope of the thesis, and the only characteristic that is pointed out here is that the structure of the electric drive trains can still be assumed to be same as in Fig. 1.1. Moreover, all kinds of HEVs include an

electrical energy storage device (typically a secondary battery) to allow for regenerative braking.

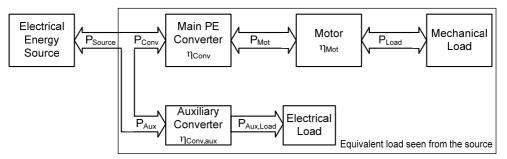

It is customary to model the drive train in terms of power flow between each component. Such an approach has the obvious advantage of being independent of the nature of the power itself (mechanical, electrical, thermal, and so on), allowing for complex systems to be analyzed within a simple theoretical frame.

Following this approach, the load is simply modelled as some kind of device asking for a given power profile; most of the power is used to originate the motion of the vehicle (traction effort), but some other part can be related to static electrical loads, like onboard air conditioning, lighting, and so on. In order for the power-flow model to describe accurately the system behaviour, efficiency of each component along the flow of power has to be properly modelled.

The electric motor is simply a reversible converter of electrical energy into mechanical energy, and its behaviour in the power-flow model is completely described by its conversion efficiency. Therefore, in principle, for power flow analysis it is not necessary to know the electrical details of the motor. In reality, there are many kinds of electrical motors that can be used for traction, the most widespread being DC motors, AC asynchronous motors, AC synchronous motors, switched reluctance motors. They all have different performance characteristics and all come with several design variations. What is common to them is that the efficiency is highly dependent on the operating conditions (speed, torque, voltage, current). The simple representation of the motor with its efficiency implies therefore a good deal of approximation, unless the power flow model is complemented with a more detailed description of the machine that can evaluate the efficiency at any given time.

The electric power flow controller is typically a power electronics converter that converts the electrical power at the terminals of the energy source into a form of electrical power that is suitable to supply the motor terminals in order to achieve the torque and speed at the shaft as required by the mechanical load. The power electronics converter is fully described by its efficiency in the power-flow model. Similarly to what was discussed for the motor, efficiency of any power converter is a complicated function of the operating conditions and detailed modelling of the converter topology may sometimes be necessary.

The electrical energy source can be modelled as a device that can either supply or store electrical energy with an operating efficiency that is normally a function of the power level. In the power flow model, in addition to the efficiency, at least a mean for establishing the amount of energy that can be supplied (or stored) by the source at any given time is necessary. As in the case of other components in the drive chain, efficiency of the energy source can be a complicated function of the operating conditions (terminal voltage, operating temperature, and so on).

From the aforementioned considerations, it is clear that starting from the high-level, macroscopic representation of the drive system in terms of power-flow, as shown in Fig. 1.2, any of the components' models can be refined to include detailed description of its structure and to give a means for precise evaluation of the efficiency to be used in the macroscopic model. The level of details that is needed is strictly dependent on the aim of the model.

Fig. 1.2 – Macroscopic modelling of the drive train in terms of power flow.

From chapter 2 to chapter 5, the focus is on the analysis and design of the power electronics needed to control the power flow between the different components constituting the electrical energy source and the rest of the system, generally referred to as load. In this context, the electrical link between the energy sources and the load has to be modelled in detail, while the rest of the system (the "load") is simply seen as a "black-box" electrical subsystem with DC-like terminal characteristics.

In chapter 6, the aim is the analysis and design of a particular kind of traction inverter, embedded with the energy source. In this case, detailed topological modelling of the power electronics in the inverter is necessary.

The rest of this chapter is dedicated to the description of some of the commonest kind of electrical energy sources used in EVs, and the models that can be used to describe them.

## 1.2 Battery technology

Battery is a key component for any kind of pure electric vehicle, since to date it is the only device that can store enough electric energy to give the vehicle a reasonable driving range. A basic understanding of how battery works and what are their basic electrical characteristics and their major drawbacks is therefore necessary when trying to design an electric drive train.

In simple terms, a battery is a device that converts chemical energy to electric energy. The basic element of any battery is called a "cell", and is typically constituted by two electrodes and the electrolyte; the chemical reaction between the electrodes and the electrolyte is responsible for the generation of electricity. In most batteries (secondary batteries, or rechargeable batteries), the chemical reaction can be reversed, and electrical energy can be stored into chemical form, charging the battery.

For traction applications, the most important functional parameters for a battery are as follows:

- Specific energy (and energy density); the amount of energy stored for unit of mass (unit of volume).

- **Specific power** (and power density); the amount of power per unit of mass (unit of volume) that can be drained from the battery.

- Cell voltage; terminal voltage of an elementary cell.

- **Efficiency**; the ratio between the energy supplied by the battery and the energy required to return the battery to the state before discharge.

- Operating temperature.

- Self discharge rate.

#### - Lifetime and cycle life.

- **Recharge rate**; the rate at which energy can be returned to the battery.

In addition to the functional requirements, safety and cost also play a key role in the choice of the most suitable battery for a given application.

The best known and most widely used battery for traction systems is the lead acid battery. Although those batteries have a long history and their technology is quite mature, achievable performance does not quite match the requirements of an electric vehicle. In particular, specific energy is typically limited to about 30 *Wh/kg*, making it virtually impossible to achieve a driving range of few hundred kilometres for an EV that would use such a battery as main energy storage. Moreover, the cycle life of lead acid batteries is relatively poor, if deep discharge is required. On the other hand, cost is quite low and no particular safety issues exist related to the use of those batteries for high power, traction applications.

As a matter of fact, virtually all modern designs tend to discard the use of lead acid, and the battery chemistry is usually chosen among one of the following:

- Nickel metal hydride (NiMH);

- Sodium metal chloride (ZEBRA<sup>®</sup>);

- Lithium ion (Li-ion).

NiMH batteries bring a roughly twofold improvement in specific energy with respect to lead acid and, although their introduction into the market is relatively recent, they are now being produced with quite high volume. This is mainly because NiMH is the battery employed in the most successful IC-electric hybrid vehicle, the Toyota Prius, and in virtually any other commercial car of the same kind. However, the energy content of such a battery is still quite low and, perhaps more important, there are some concerns about the cycle life when the battery is cycled very deeply. The latter is a key factor, especially in applications like pure EV, when utilization of most of the energy available in the battery is vital to achieve reasonable driving range. It is a fact that the cycling life of virtually any kind of battery decreases exponentially with the depth of discharge [8] and, so far, the designer of hybrid IC-electric vehicles have been forced to use largely oversized batteries and use just a tiny bit (no more than 20%) of their potential energy intensive vehicles, like plug-in hybrids or pure electric, the NiMH chemistry tends to be replaced by more energy-dense options.

Sodium-nickel chloride (ZEBRA<sup>®</sup>, Zero Emissions Battery Research Association) [9] is the most promising kind of battery within the family of sodium-based chemistries. Such a battery needs to operate at the relatively high temperature of about 320 °*C*, and therefore additional system components are required to install the battery on board of EVs. In spite of that, specific energy is among the highest available (about 100 *Wh/kg*), and battery packs specifically developed and fully tested for automotive applications are commercially available. On the downside, specific power is not very high, and recharge time can be long. Perhaps even more important, the technology is proprietary of a single company (MES-DEA) causing some difficulties for widespread utilization in high numbers; for the same reason, it is quite difficult to find independent data about the performance characteristic of such a battery. ZEBRA<sup>®</sup> battery is given particular attention in this thesis, since it is the one deployed on the Norwegian Th!nk EV used as basis for the design of the system proposed in chapter 5.

There seems to be consensus about the fact that lithium-based batteries have the highest potential in terms of achievable energy density. They have been used extensively in portable electronics, but higher power packs are being developed by several companies, trying to meet the expectations of the many car manufacturers willing to have them as the main electric energy storage devices in next-generation plug-in IC-electric hybrids [10,11] or pure EVs [12,14]. Lithium-based batteries can also be designed to have relatively high specific power, and prototypes have been built allowing for very quick recharge by use of state-of-the-art nanotechnologies [15]; however, it should be noted that the increase in power density is usually achieved by trading off energy density. Although several high-performance (and high price) prototypes [16,17] have been developed based on lithium batteries, there are still some significant hurdles to large scale deployment of such high-power battery stacks. To begin with, cost is still too high to be readily accepted by the automotive community. Moreover, there is still not enough data to ensure proper operation of those stacks over a sufficiently long period of time, compatible to the requirements of the automotive industry. Last, but very important, there are still some safety concerns, due to the thermal runaway experienced by some lithium-based battery packs [18] that can occasionally lead to dramatic failures, especially when trying to recharge the batteries at temperature below freezing; to prevent accidents and ensure proper battery life, modern packs are equipped with complex monitoring and protection circuitries, and modified design of the battery cells are also being proposed [19,20], claiming the virtual elimination of the likelihood of a catastrophic failure.

|                                             | Lead Acid      | NiMH         | ZEBRA     | Lithium-ion   |

|---------------------------------------------|----------------|--------------|-----------|---------------|

| Specific energy                             | 20-35<br>Wh/kg | 50-70 Wh/kg  | 120 Wh/kg | 100-200 Wh/kg |

| Energy density                              | 50-90 Wh/l     | 150-200 Wh/l | 180 Wh/l  | 150-250 Wh/l  |

| Specific power                              | 250 W/kg       | < 1000 W/kg  | 180 W/kg  | < 2000 W/kg   |

| Nominal cell voltage                        | 2.1 V          | 1.2 V        | 2.58 V    | 3.6 V         |

| Temperature range                           | -20C to 60C    | -20C to 50C  | N.A.      | -20C to 50C   |

| Number of cycles<br>@80% Depth Of Discharge | 700            | 2000         | 1500      | 2000          |

Table 1-1 – Nominal parameters of several battery technologies

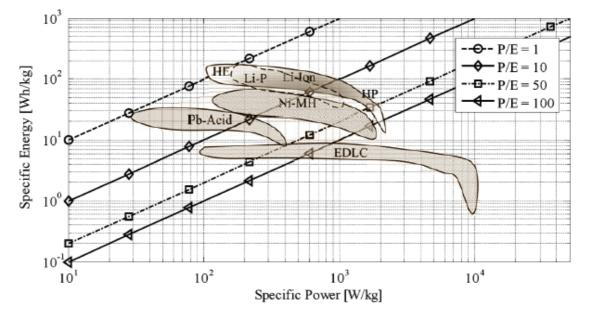

Basic performance indexes of the battery chemistries discussed so far are reported in Table 1-1, and their respective Ragone plots (energy versus power in logarithmic scale) are given in Fig. 1.3. It should be noted that while data for lead acid, NiMH and ZEBRA are believed to be quite accurate, Lithium batteries come in many different variations from several start-up companies that are now trying to conquer the market. Some of them are quite aggressive and have pretty bold claims in terms of energy and power density, as well as cycle life, and is therefore difficult to cite reliable, realistic figures. All figures have significant spread, as it is evident in the Ragone plot, depending on the particular technological process, and on the energy/power trade-off of a particular battery. It is possible that technological breakthrough in the very dynamic

field of lithium batteries may yield performances that significantly differ from the guideline in the table, especially regarding the operating temperature and the cycle life.

Fig. 1.3 – Ragone plot of several battery types (from [21]).

Data shows that from the point of view of achievable performance, both in terms of energy density and power density, lithium batteries are certainly superior to all other battery chemistries, and that is why virtually all automotive companies are investing in the technology. Only supercapacitors (EDLC) outperform lithium batteries for applications where very large power/energy (P/E) ratios are required.

However, Ragone plots give no information about achievable lifetime, safety issues and cost, that are at present the aspects preventing a widespread use of lithium batteries in automotive.

#### 1.2.1 Modelling of batteries for power electronics applications

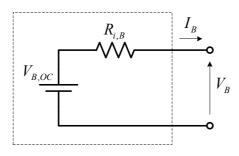

For the electrical engineer that has to design the drive system of an electric vehicle, it is important to have a model describing the behaviour of the battery at the terminals. Due to their electrical characteristics, batteries are often modelled as voltage sources with internal resistance, as shown in Fig. 1.4.

Fig. 1.4 – Basic Thevenin equivalent circuit of a battery.

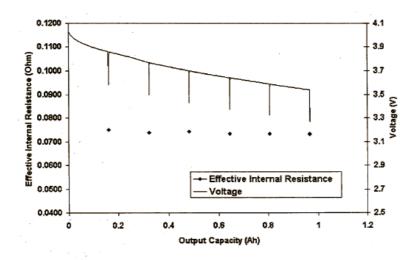

Such a circuit is apparently very simple, but in order for it to describe accurately the behaviour of a real battery, both the open circuit voltage (OCV) (indicated as  $V_{B,OC}$  in the figure) and the internal resistance  $R_{i,B}$  must be changed according to the state of charge (SOC) of the battery. This is true for all battery technologies, even though the dependency may be very different according to the particular chemistry and technology. As an example, Fig. 1.5 shows the OCV and the internal resistance of a ZEBRA cell as a function of the SOC. The same quantities are shown in Fig. 1.6 for a lithium-ion cell.

Fig. 1.5 – OCV and internal resistance (from [22]) variation of a ZEBRA cell with the SOC.

Fig. 1.6 – OCV and internal resistance variation of a lithium-ion cell with the SOC (from [23]).

OCV and internal resistance are in general dependent on temperature, too. If that is an issue, a thermal model of the battery has to be added to the electrical one. Fortunately, in the case of ZEBRA, the cell temperature is kept relatively constant by a thermal

management system embedded in the battery pack, and such complication is then unnecessary.

Since information about the battery SOC is needed to determine the electrical parameters to be used in the Thevenin-equivalent model, a means for calculating it must be included in the model. The most classical way of doing it is by using the so-called Peukert model of battery behaviour [24]. The method was developed originally to describe the behaviour of lead acid batteries, but has been extended also to other chemistries. As a starting point of this model, the constant value called "Peukert" capacity of the battery under study is defined as:

$$C_p = I^k \cdot T \quad (Ah) \tag{1.1}$$

In the definition above, I is the discharge current expressed in Ampere, T is the discharge time expressed in hours and k is an empirical coefficient (Peukert coefficient), which is a function of the particular battery technology. It is noticed that if such a coefficient is unity, then the Peukert capacity is same as the nominal capacity of the battery. Peukert coefficient is significantly higher than one in lead acid batteries (typically around 1.2), but is almost unity for ZEBRA and Li-ion. Lately, doubts have been raised about the applicability of the empirical Peukert method to modern batteries [25], but for the purpose of this thesis, the method is believed to yield sufficient accuracy.

In the elementary time interval dt (seconds), if the current flowing out from the battery terminals is I, then the incremental charge removed from the battery is:

$$dq_p = I^k \cdot dt \tag{1.2}$$

If the current is flowing into the battery (recharge), the same kind of equation is valid, but the correction due to the Peukert coefficient does not apply.

The total charge removed from the battery at time t is therefore:

$$Q_{rem}(t) = \int_{t_0}^{t} I(t)^k dt$$

(1.3)

Assuming the battery to be full at the initial time  $t_0$ , the SOC and depth of discharge (DOD) at time t are then calculated as:

$$DOD(t) = \frac{Q_{rem}(t)/3600}{C_p}; \quad SOC(t) = 1 - DOD(t)$$

(1.4)

The electrical model in Fig. 1.4, can then be used together with the SOC estimator defined by (1.1) to (1.4) and the parameter adaptation taken from battery characteristics, such as those given in Fig. 1.5 or Fig. 1.6. The result is a closed-form model describing the electrical behaviour of the battery throughout the whole discharging process.

Apart from the already mentioned dependency on the cell temperature, that has not been considered, the model above is also unable to predict the dynamic behaviour of the battery, due to pseudo-capacitance effects. To that purpose, more complex electrical equivalents have been developed in the literature [26-28]. However, as long as the battery model is used to predict performance of a vehicle in terms of achievable range, acceleration, and so on, those refinements have little effect and are therefore not further discussed.

### 1.3 Supercapacitors

Supercapacitors (SC) are also known in the literature as Ultracapacitors or, more scientifically, Electrical Double Layer Capacitors (EDLC). As the latter name suggests, charge storage in these devices is based on the double layer effect, first described in [29] by Helmholtz in 1861. Although the effect has been known for many years, and several refined models have been developed since then, its application to the development of devices with extremely high capacitance is relatively new [30]. The first commercial double layer capacitor was introduced in the '80s by NEC, and only in the late '90s the technology has received worldwide attention due to the many possible applications of such devices, leading to a considerable increase in performance and decrease in price. SCs are interesting to the automotive industry as energy storage device, since they have

the following basic characteristics:

- Very high specific power (typically 10-100 times higher than traction batteries);

- **Perfectly reversible operation**; their efficiency during charging is same as the efficiency during discharge.

- Long lifetime and good cycling capabilities, meaning that they can be fully charged and discharged an extremely high number of times without significant degradation of their electrical characteristics.

In all the aforementioned aspects, SCs largely outperform electrochemical batteries. What prevents SCs from actually replacing batteries in the design of the energy tank for pure electric propulsion systems is their relatively poor specific energy, which is in the order of 10 Wh/kg for the best commercially available devices (about one order of magnitude lower than good traction batteries).

Even though vehicles powered only by SCs have been built [31,32], the commonest application of those devices in automotive has been as power-assist for some other kind of energy source (typically a traction battery in pure EV applications). This kind of application will be extensively described in chapter 2.

Main characteristics of SCs as energy storage devices are reported in Table 1-2. The values refer to commercially available devices, and are therefore expected to undergo significant improvements in the near future.

An in-deep description of modern SC technology, along with a comprehensive theoretical analysis of the double layer, can be found in [33]; some of the most important characteristics of those devices are reported here, since they are very useful when trying to utilize those devices in applications related to energy storage.

SCs store energy in the electric field formed by two charge distributions of opposite polarity, and are therefore characterized by their capacitance  $C_{SC}$ . The amount of stored energy is a function of the terminal voltage, and is given by:

$$E = \frac{1}{2} C_{SC} V_{SC}^{2}$$

(1.5)

The concept behind SC is to maximize the energy storage capability by increasing the capacitance of the device. For a simple geometry of two conductive plates of surface S divided by an insulating material of width d and permittivity  $\varepsilon$ , the capacitance is expressed by:

$$C = \varepsilon \cdot \frac{S}{d} \tag{1.6}$$

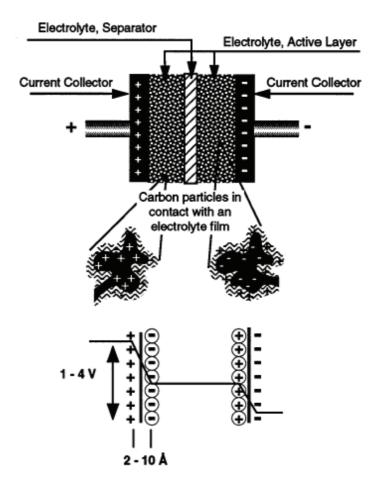

In a double layer capacitor the formula above does not apply exactly, due to the more complex spatial distribution of charge and related electric field, however the qualitative dependency on surface area and distance remain unchanged, and those are the factors that are exploited by the current SC technology to obtain very high capacitance values in limited volume.

Surface area is maximized by the use of very porous materials, with carbon being currently the choice in most commercial products. Improved materials, like carbon nanotubes [34,35], are also been investigated to further increase the active electrode surface.

Maximization of surface is important, but what is really peculiar of double layer capacitor is the absence of a real insulator; the charge distribution is only due to the surface interaction between a solid material (the electrode) and a liquid solution (the electrolyte), forming a layer of charge accumulation (the double layer) over a distance of few molecules, thus giving rise to strikingly high value of capacitance. Unfortunately, that is also the reason why the operating voltage of SC is limited to few volts (less than 3 V in commercial devices). In fact, due to the very short width of the charge distribution, even a relatively low voltage causes large electric field; moreover, unlike ordinary capacitors where most of the electric field is located within the insulating material (dielectric), in SCs the electric field is directly applied to the electrolyte and electrode (see Fig. 1.7). This will ultimately cause electrolyte (and in some cases electrode) decomposition, with subsequent pressure built-up and rapid decrease of component lifetime [36].

|                    | ••••••••••••••••••••••••••••••••••••••• |

|--------------------|-----------------------------------------|

| Specific energy    | < 10 Wh/kg                              |

| Energy density     | < 10 Wh/l                               |

| Specific power     | 10 kW/kg                                |

| Power density      | 10 kW/kg                                |

| Rated cell voltage | < 3.0 V                                 |

| Temperature range  | -40C to 70C                             |

| Number of cycles   | > 10 <sup>6</sup>                       |

Table <u>1-2 – Best-case typical parameters of commercial supercapa</u>citors.

Since, according to (1.5), increasing the operating voltage would cause a quadratic increase in energy density of the device, intensive research is ongoing to find new materials; however, the higher and higher electric field at the solid-electrolyte interface may give rise to local periodic material deformations as well as reduction-oxidation phenomena of the same nature of those normally exploited in electrochemical batteries. Although those effects add to the apparent "capacitance" of the device, they are not due to the simple charge accumulation as in ordinary capacitors, or in the pure double layer capacitor and are, for that reason, referred to as *pseudo-capacitance*. Devices that utilize actively these kinds of phenomena have been built [37], but some concerns are still present about their long-term stability, since they can be considered half-way between SCs and batteries.

Fig. 1.7 – Structure of double layer capacitor and corresponding simplified voltage distribution (taken from [38]).

#### 1.3.1 Modelling of supercapacitors for power electronics applications

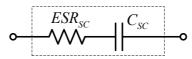

Electrical characteristics at the terminals of an actual supercapacitor are quite different from those of an ideal capacitor. Several resistive components appear in the current path of the device schematically shown in Fig. 1.7, giving rise to an equivalent series resistance (ESR). The simplest model for the device is therefore the one in Fig. 1.8.

Fig. 1.8 - Single R-C model for an actual supercapacitor

Some leakage current inevitably flows, tending to discharge the capacitor. That would require the addition of a parallel resistance in the R-C model above, to take self-discharge into account. However, such a phenomenon is typically quite slow (time constant of several hours) and in most cases where the interest is in modelling the dynamics of the charge/discharge process (several seconds), its contribution can be neglected.

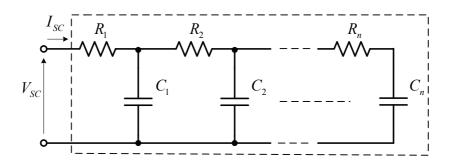

Deeper investigation on the physical structure of the device, taking into account the distributed nature of the resistance and capacitance of the porous electrode, suggests a more refined model made up of cascaded R-C pairs [38], as shown in Fig. 1.9.

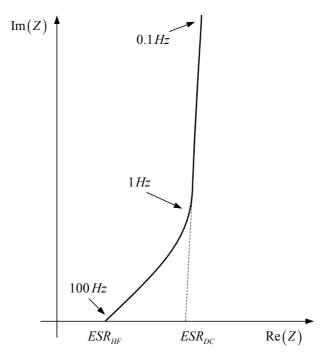

Such a model can be experimentally verified by executing spectroscopic analysis of the terminal impedance, as done for instance in [39,38]. Results are schematically shown in Fig. 1.10 and can be synthesized as follows:

- At very low frequency (less than about 1 Hz), the impedance is reasonably well described by a simple R-C series network with constant values of both capacitance (the DC-capacitance) and resistance (the DC-ESR).

- At relatively high frequency (above about 100 Hz), the capacitance is reduced to a very small fraction of its DC value, and the component behaviour is essentially resistive, with a "high frequency" ESR that is smaller than the DC-ESR.

- At intermediate frequency, both ESR and equivalent capacitance increase with decreasing frequency, giving rise to the distinctive 45 degree-slope region in the complex impedance plane.

Fig. 1.9 - Cascaded R-C model for an actual supercapacitor

Adding to the complexity of the system in Fig. 1.9 is the fact that R-C parameters are in general dependent on both temperature and operating voltage [40,41].

For the power electronics designer, the impedance characteristic in Fig. 1.10 has the important implication that in spite of the huge value of their DC-capacitance, SCs are of no help in filtering high frequency components typical of PWM converters, as they are almost purely resistive at those frequencies. In order to avoid excessive power dissipation within the SC cells and the consequent increase of temperature, it is good practice to connect a filtering capacitor with good high frequency characteristics in parallel with the SC bank [42,43]. The importance of this simple and relatively inexpensive countermeasure should not be overlooked, since it can significantly increase the lifetime of the SC bank in many applications.

This practical aspect also makes it possible to use the simplified R-C model of Fig. 1.8 with DC-values of both ESR and equivalent capacitance to describe the behaviour of a SC in an actual circuit. In fact, if a large, low ESR, bypass capacitor is placed in parallel with the SCs, high frequency components will be almost completely shunted away from the supercaopacitor, and the high frequency branch of the impedance characteristic can be neglected without significant loss of information.

However, if filtering capacitor is not present (or is not sufficient) and high frequency ripple current does flow through the SCs, the high-frequency ESR of the devices has to be used to evaluate the losses due to such high frequency components.

Fig. 1.10 – Schematic representation of Nyquist impedance plot of a typical SC cell.

# 2 HYBRID ENERGY SOURCES – COMBINATION OF BATTERIES WITH SUPERCAPACITORS

## 2.1 Hybrid energy sources

Generally speaking, any kind of arrangement that allows for use of energy from more than one source can be defined as hybrid. Considering the variety of fossil fuels, battery types, alternative fuels and so on, the number of possible combinations is overwhelming. Main factors behind the need for hybridization of the energy source in automotive are:

- Improved performance;

- Improved economy;

- Improved vehicle lifetime;

- Flexibility.

Except for the latter aspect, where for example a given IC engine is designed to run from different kind of fossil fuels or biofuels [44] just for the sake of increased availability, the basic idea behind hybridization is to utilize in a synergic way different sources of energy, with the aim to combine their individual advantages and, at the same time, mitigate their weak points.

A typical example is the combination of fossil fuel (used to supply an IC engine) with some kind of electrochemical energy storage (typically a battery driving an electric motor) used in the increasingly popular hybrid vehicles (HEV) of which the Japanese carmaker Toyota with its Prius has been the forerunner. In this arrangement, the superb energy density of the fossil fuel is combined with the ability to recuperate the kinetic energy of the vehicle into the battery for later use; also, vehicle efficiency can be improved by properly splitting the effort of the engine and the electric motor according to operating conditions. Overall, the hybridization results in a vehicle having better fuel economy and higher performance than the equivalent "IC only" counterpart.

Although HEVs are by now an industrial reality experiencing an exponential growth, they will not be further discusses in this context. The focus will instead be on pure

electric vehicles (no IC engine at all), where hybridization consists in the use of more than one type of electrical energy storage. Fuel cell vehicles (FCV) and the related problems of hydrogen production and storage, although recognized as being an extremely interesting technology, are also beyond the scope of this thesis. However, it is pointed out that most of the concepts related to hybridization discussed in the following will readily apply to FCV, since in virtually every implementation the slow dynamics of the fuel cell require the use of some kind of additional power source, like a battery or a supercapacitor bank.

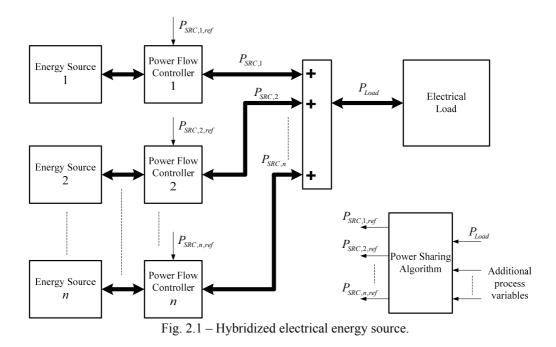

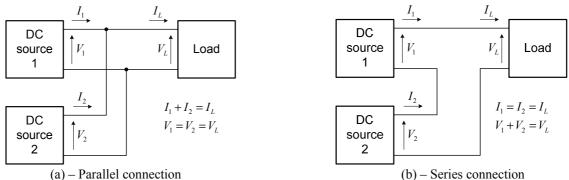

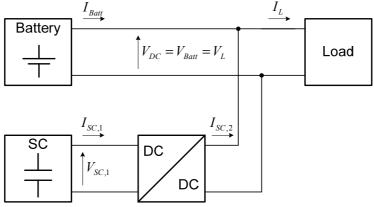

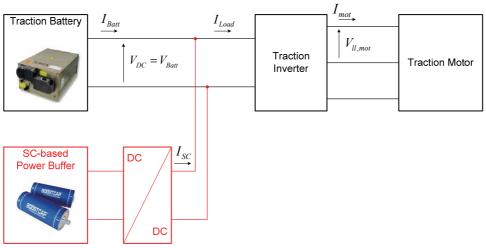

A typical drive system with hybridized electrical energy source is shown in Fig. 2.1. At this stage, the power flow controllers are assumed to be ideal, meaning that the power that flows from the *i*-th energy source  $P_{SRC,i}$  is exactly equal to the one commanded by the power sharing algorithm  $P_{SRC,i,ref}$ . It is hereby noticed that if there is no energy storage within the power flow controllers, energy conservation requires that:

$$P_{Load} = P_{SRC,1} + P_{SRC,2} + \ldots + P_{SRC,n}$$

(2.1)

Therefore, only (n-1) power flow controllers are strictly needed.

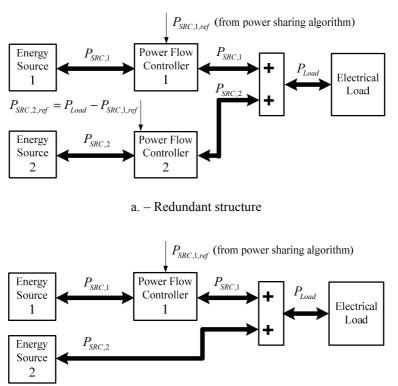

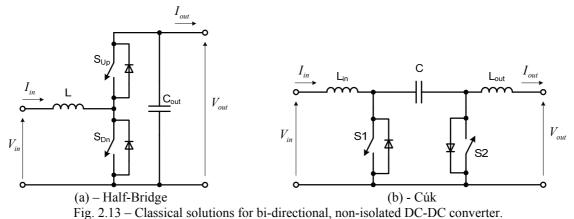

In general, the hybrid energy system can consist of any number of sources, although in most practical implementation n is limited to two. In this simple but significant case, the system can be implemented according to any of the topologies in Fig. 2.2. The redundant structure has the advantage of complete decoupling between the electrical characteristics (terminal voltage and current) of each source and those of the load, but needs more power processing components and its overall efficiency and cost may be negatively affected. On the other hand, in the case of the minimal structure, the load must share some of the electrical characteristics of the unprocessed source (either its terminal voltage or current, depending on the kind of connection). The choice of the topology depends on the particular application, taking into account the characteristics of each source as well as those of the load.

b. - Minimum structure

Fig. 2.2 – System with two energy sources – Architectures for independent power flow control.

#### 2.2 Battery-Supercapacitor combination

In a pure EV, the ideal energy tank should satisfy the following basic operational requirements:

- Sufficient amount of energy storage capability, in order to achieve a satisfactory driving range between recharges;

- Sufficient power capabilities, so that the necessary power required for propulsion can be supplied to the motor in any reasonable driving condition;

- Quick charging time, in order to increase vehicle availability;

- Sufficient lifetime, both in terms of calendar life and number of charge/discharge cycles.

In addition, there are a number of other requirements which are not directly related to the performance of the EV, but still are of utmost importance:

- Safety, both during normal operation and in case of accidents;

- Cost.

Having in mind the results of the review in chapter 1, it is apparent that at present the only kind of electrical energy storage device that can give sufficient energy density to achieve a reasonable driving range is the electrochemical battery. In particular, according to Table 1-1, Lithium batteries and Sodium-Chloride batteries have the best specific energy figures among all the rechargeable batteries to-date.

When considering power density, results are very different. Sodium-Chloride batteries have poor power density; Lithium batteries still score fairly well, but they are largely outperformed by supercapacitors.

In light of those very simple considerations, it seems that a combination of an energy dense battery pack with a power dense supercapacitor bank can combine the advantages of both technologies. Of course, the hybrid system is more complex, and possibly has higher initial cost than a classical battery-only design.

There is intensive research activity on Li-based batteries trying to increase their specific power, and some of them [45] are showing promising results; however, it should not be overlooked that there is always a design trade-off according to which, for a given technology, trying to increase the power density will always result in reduced energy density. The use of hybridization would allow for independent optimization of the two concurrent sources for highest specific energy and highest specific power, respectively.

Whether a hybrid energy source is really advantageous and, if yes, to what extent, is still very controversial, due to the many variables involved in the evaluation of those systems. In the following, some of the aspects related to the design of hybrid batterysupercapacitor systems are analyzed, trying to give answer to such a basic question.

### 2.2.1 Power flow control within systems with hybrid energy source

The power sharing algorithm used by the controller in Fig. 2.1 must be designed with the aim of getting the best out of each individual source. A proper strategy should be able to achieve one or more of the following objectives:

- Maximized driving range (can also be stated as maximized overall efficiency);

- Minimum component stress, resulting in extended system life-time.

Stated in simple terms, the operating principle of hybrid energy source is expressed by the following paradigms:

- The primary energy source (the battery) is the one with the highest energy content and should therefore supply the average power needed by the load; Steady power flow ensures minimum losses and reduced stress. Since the battery cycle-life is currently the most critical factor for the system overall life-time, the latter aspect is particularly important.

- The secondary energy source (the supercapacitor) should assist the battery by providing/absorbing the momentary load power peaks. Due to relatively low internal resistance, they can efficiently handle large power bursts; moreover, their life-time will not be significantly affected by this intermittent operation, provided their thermal limits are not exceeded.

Although apparently straightforward, those principles are not easy to implement in practice. In fact, the load requirement is not known a-priori, making the concept of ideal power sharing a non-deterministic one. In addition, optimal power sharing will depend on the state of the individual energy sources (SOC, internal resistance, etc.), introducing several additional variables and constraints to the optimization problem. Moreover, while efficiency and achievable driving range are relatively easy to measure, effects on system life-time are not as apparent.

To date, there is no standard solution to the problem of optimal power sharing described above. There is however plenty of publications on the subject, mainly divided in three categories according to the kind of algorithm used:

- Heuristic algorithms, based on simple practical assumptions reflecting the basic principles reported above [46-48]. Main advantage of those algorithms is that they do not need a-priori information about the particular driving pattern; only some general specifications of the system components are needed, making the strategy easy to implement.

- Deterministic algorithms based on analytical minimization of losses [49-52]. Typically, information about the driving pattern is needed for proper optimization, along with detailed information about the system structure and electrical specifications of each component. The optimization process is complicated by the physical constraints (limited energy available in the SCbuffer, maximum current in and out of the battery, etc.) present in the system.

- Non-deterministic algorithms, utilizing stochastic methods, fuzzy logic and/or neural networks trying to achieve a real time solution of the optimization problem [53-56]. These methods are very popular for solving complex optimization problems that are not easy to express in closed mathematical form; performance can be very dependent on the particular implementation and training and, in any case, optimality cannot be guaranteed for every particular driving pattern.

Although the design of an efficient power sharing algorithm is of great importance, it is not the aim of this thesis to discuss extensively on the subject.

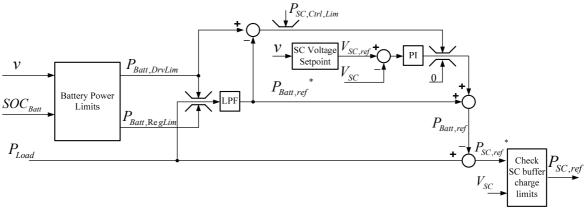

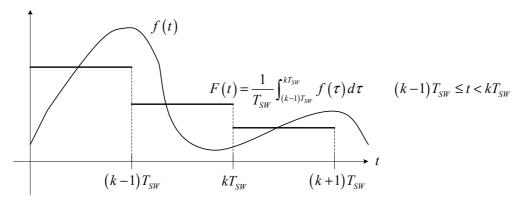

In order to illustrate the operating principle and highlights the main advantages and drawbacks of a hybrid system, an algorithm belonging to the first category above is developed. Such a power sharing algorithm is shown in Fig. 2.3 and its operating principle is explained in the following. The algorithm evaluates the share of the load power that must be handled by the SC-based power buffer  $P_{SC,ref}$ , using as input for the calculation the vehicle speed v, the SOC of the traction battery and the power required by the load  $P_{Load}$ .

Fig. 2.3 – Heuristic power sharing algorithm between a battery and a supercapacitor bank. In the simple case of only two energy sources, (2.1) is written as:

$$P_{Load} = P_{SC} + P_{Batt}$$

The load power requirements consist of the following components [57]:

- 1. Base load (on-board electrical loads, including air conditioning),  $P_{base}$ ;

- 2. Rolling resistance  $P_{roll}$ ;

- 3. Aerodynamic drag,  $P_{drag}$ ;

- 4. Gravitational load during uphill/downhill driving,  $P_{\sigma}$ ;

- 5. Inertial load during acceleration/braking,  $P_{acc}$ .

The first 4 components are "steady components", meaning that they can remain nearly constant for long time. Due to this characteristic, they should be supplied by the primary energy source, in order not to deplete the power buffer (secondary source). On the other hand, power for acceleration and braking, due to its quick transient nature, should come from (or be sunk by) the power buffer. With this strategy in mind, the first step is to estimate the "steady loads":

$$P_{Load,steady} = P_{base} + P_{roll} + P_{drag} + P_g = P_{base} + k_{roll} \cdot |v| \cdot Mg \cos \psi + k_{drag} \cdot |v|^3 + Mg \sin \psi$$

(2.3)

In the equation above, M, v are the total vehicle mass and speed, respectively;  $\psi$  is the inclination of the road surface. The coefficients  $k_{roll}$ ,  $k_{drag}$  are known from vehicle geometry and weight, and can be considered constant for the degree of accuracy that is here required.

Total steady power in (2.3) can be either positive (load requires power) or negative (load is giving power back to the sources), with the latter being possible only in the case of downhill driving. In principle, the amount of power defined by (2.3) is the one that should be supplied by the battery; however, it is first necessary to check for absolute power limitations given by the battery manufacturer that are normally a function of the SOC. It is noticed that if the system is properly designed, the battery should always be able to supply positive load requirements; however, in the case of regeneration, it is possible that especially at high SOC, the energy sent back by the load exceeds the battery's capability, and the negative value given by (2.3) has to be clamped.

The setpoint for the battery power is finally determined by multiplying the value obtained above by a coefficient  $k_{mar}$  slightly bigger than unity, in order to leave some margin for SOC control of the SC bank (as will be described later) and for unavoidable parameter mismatch in the evaluation of (2.3); the reference is also smoothed by a simple first order low pass filter, to avoid fast gradients that may have adverse effect on battery lifetime:

$$P_{Batt,ref}^{*} = \frac{k_{mar}}{1+\tau s} \cdot P_{Load,steady}$$

(2.4)

As a consequence, the SC bank will have to supply the rest, in order to satisfy (2.2). This can be done, unless the buffer has reached its SOC limits.

The problem with this algorithm is that it does not take into any account the limitation of the energy content in the SC-based power buffer. It is then possible that during operation, due to unavoidable parameter mismatch, the SC buffer becomes either

(2.2)

completely depleted or completely filled. When that happens, its contribution to the load power requirement disappears, leaving the battery as the only available source.

Ideally, the SC buffer should be operated so that in any given instant, it is able to accept energy from the load if sudden braking occurs or, conversely, it is able to supply acceleration power to the load as required by the driver. That means the SOC of the buffer should be controlled as a function of the speed, following the simple argument that if the vehicle is running at low speed, the power buffer should be kept close to full, in order to be prepared for sudden acceleration. Conversely, if the vehicle is running at high speed, the power buffer should be close to empty, so that it can readily accept the braking power that may be sent back from the load.

Braking energy that can be expected from the load at any given instant is at most equal to the kinetic energy of the vehicle, and is therefore varying with the square of the speed:

$$E_{\text{Reg},Max} = \frac{1}{2}M \cdot v^2 \tag{2.5}$$

On the other hand, the energy that can be accepted by the SC-based power buffer for a given SOC is expressed as:

$$\Delta E_{SC} = \frac{1}{2} C_{SC} \cdot \left( V_{SC,Max}^2 - V_{SC}^2 \right)$$

(2.6)

If the buffer has to be able to accept all the possible energy that could be sent back from the load, its terminal voltage should then be controlled to:

$$V_{SC}(v) \le \sqrt{V_{SC,Max}^{2} - \frac{M}{C_{SC}}v^{2}}$$

(2.7)

It is beneficial to apply (2.7) with the sign of equality so that, at the same time, the amount of energy already present in the power buffer is maximized. Such energy can be used for acceleration.

Once the desired SC voltage has been calculated by (2.7), a standard P-I controller can be used to force the actual SC voltage to track its reference. Obviously, the energy necessary for such a tracking process must come from the battery and it is therefore necessary to decide how much effort should be put into this process. This is done by properly shaping the upper and lower limits of the P-I controller generating the additional term of the battery power needed for SC voltage tracking, as shown in Fig. 2.3. The idea is to operate the voltage tracking as a low priority process, using as little battery energy as possible. In addition, the lower output limit of the voltage regulator is set to zero, meaning that no energy can be sent back directly from the SC bank to the battery; this is done in order to avoid unnecessary power loops within the system and their associated losses.

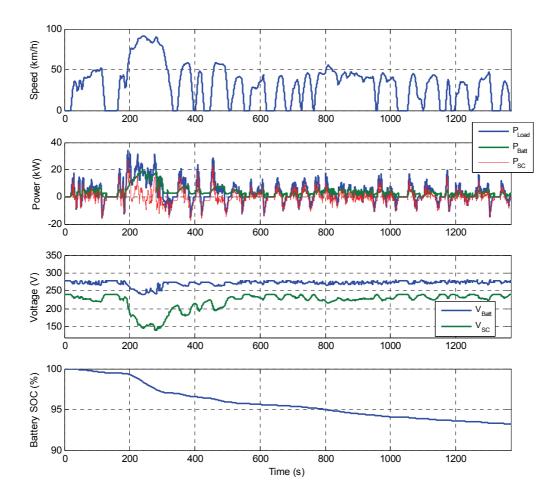

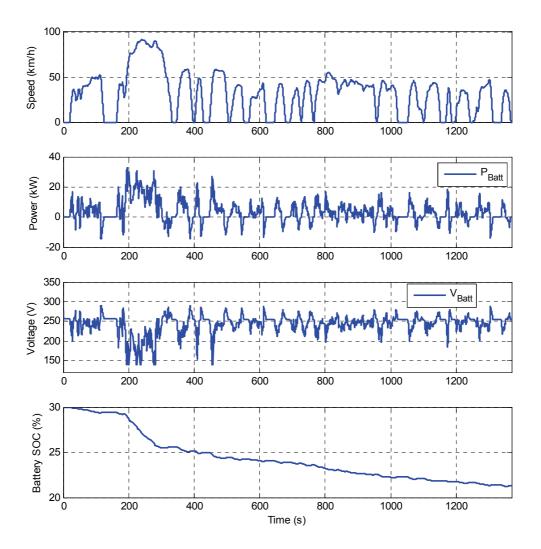

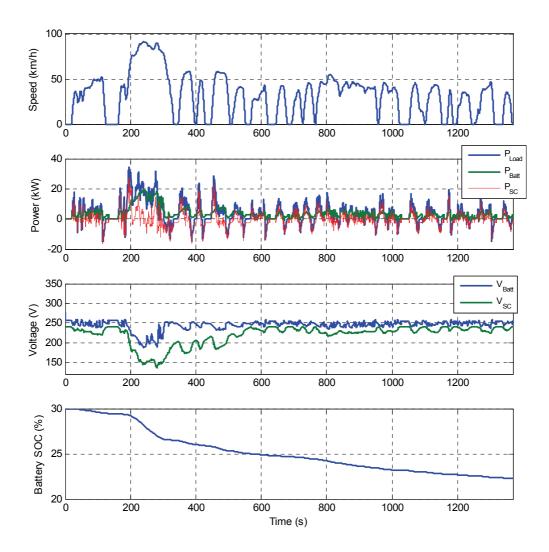

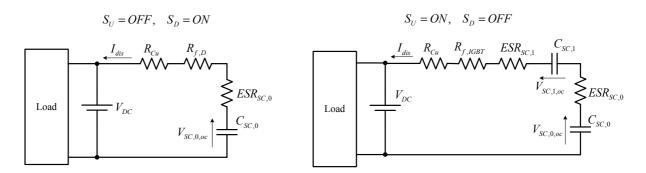

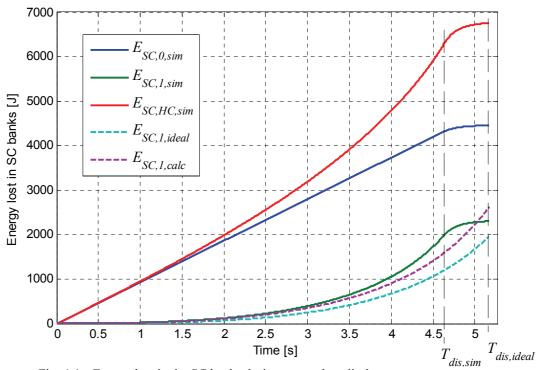

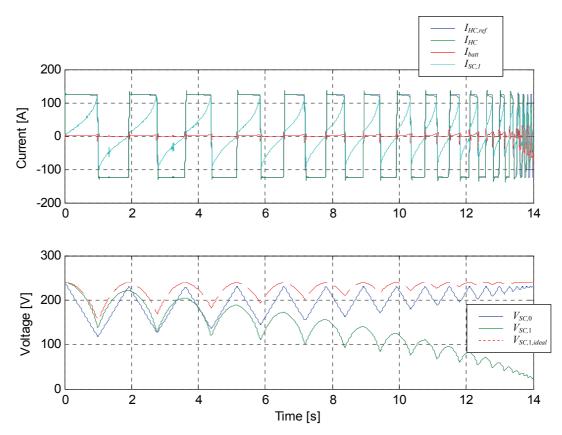

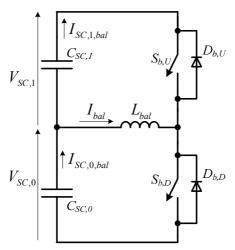

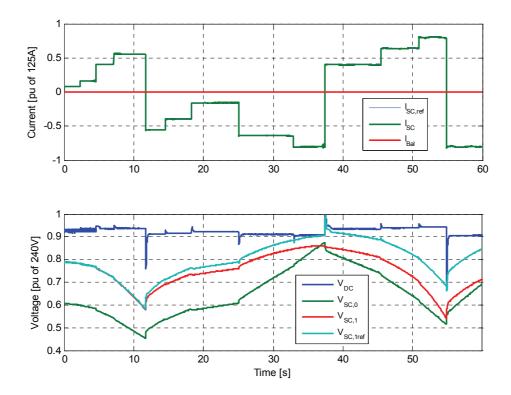

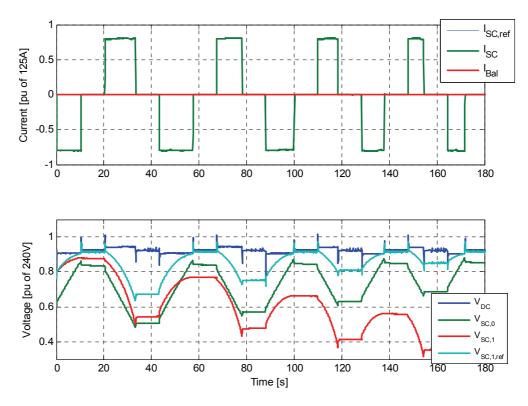

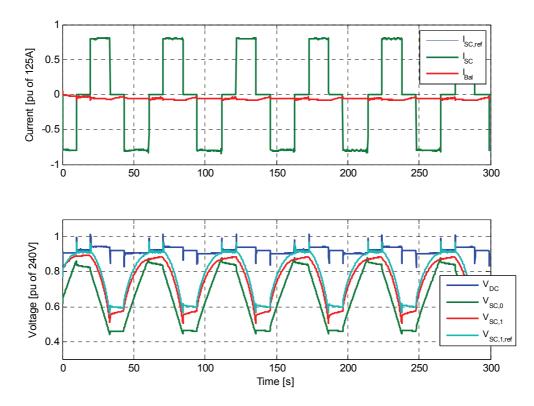

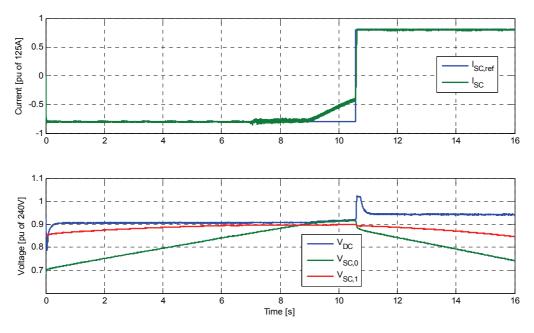

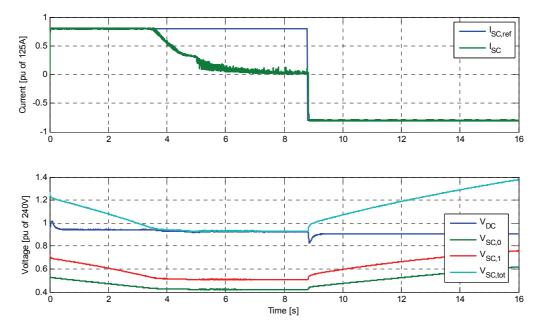

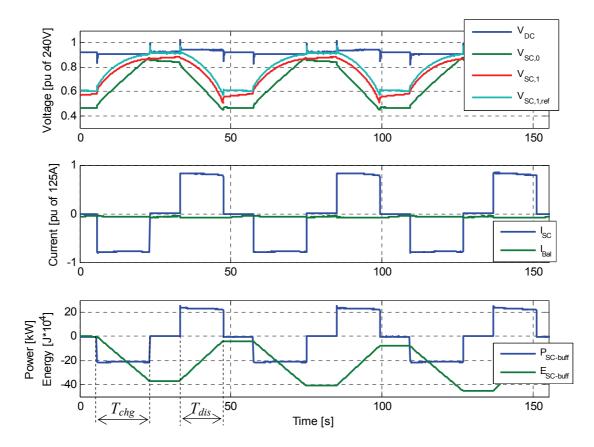

#### 2.2.2 Simulation of a battery-supercapacitor hybrid energy source

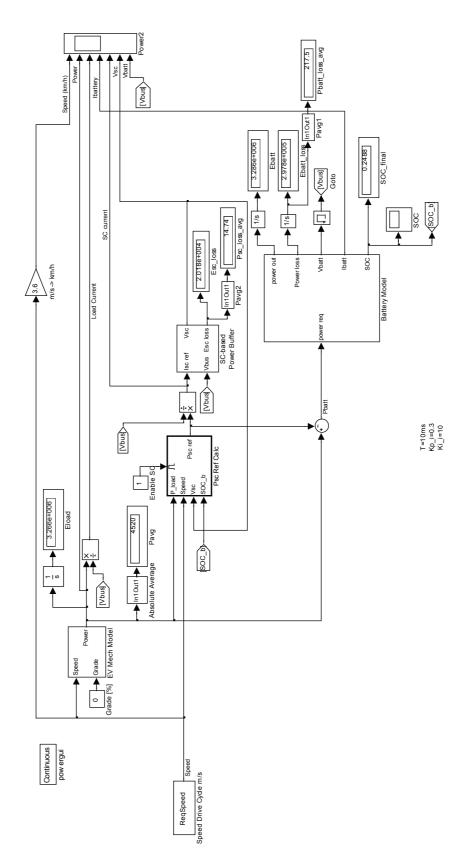

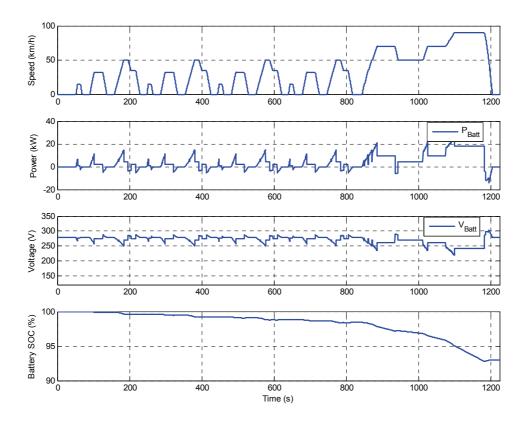

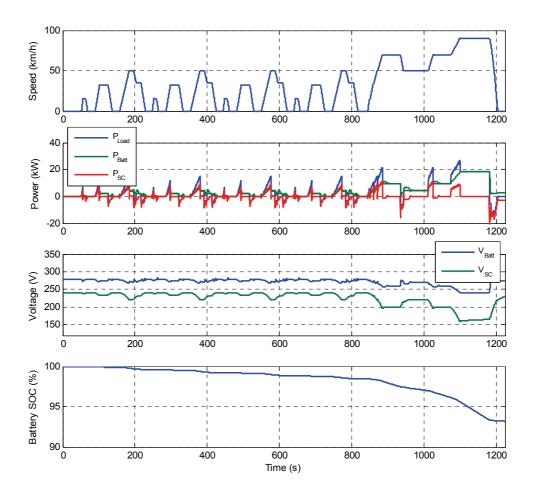

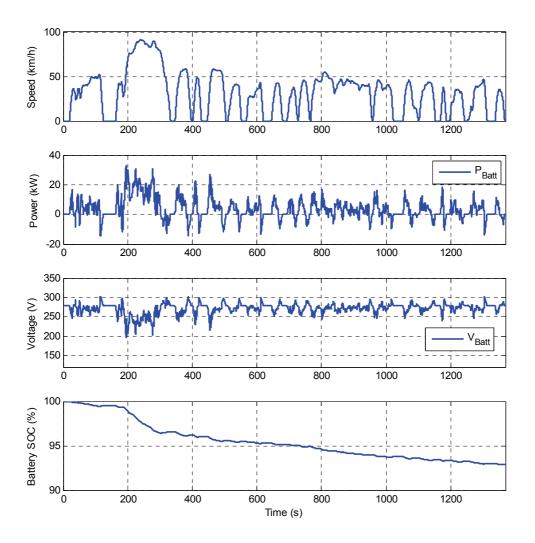

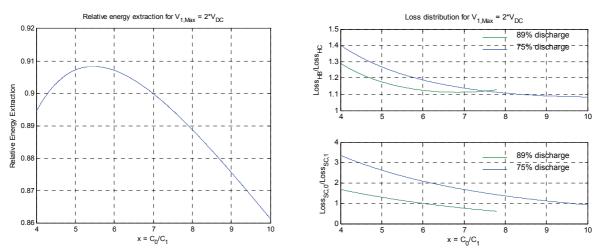

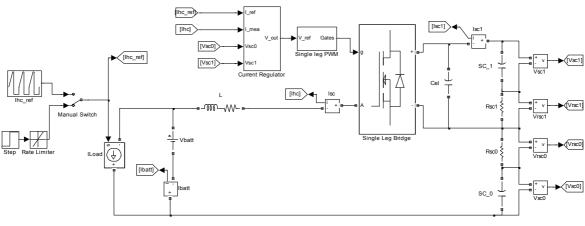

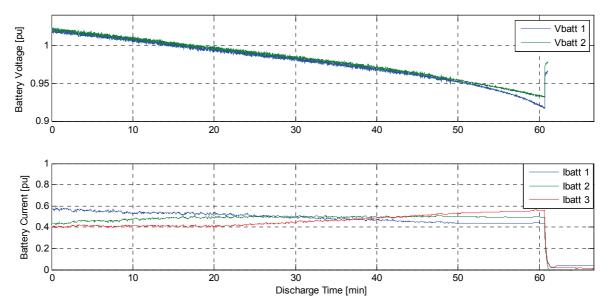

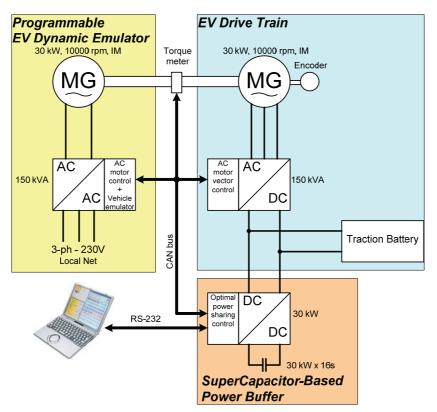

In order to highlight the advantages of a battery-supercapacitor energy source against a battery-only system, Matlab-Simulink<sup>®</sup> [13] simulations are performed, representing a particular case study of a small, pure electric, city vehicle. The overall model of the system is reported in Fig. 2.4.

Fig. 2.4 - Simulation model of a battery-supercapacitor .hybrid system.

Main modelling assumptions are as follows:

- Electric power required by the vehicle is calculated by imposing a given speed profile, taking into account a simplified vehicle dynamics, including rolling resistance, aerodynamic drag, grading and electric base load. When the SCbased power buffer is used, its weight is added to the vehicle mass;

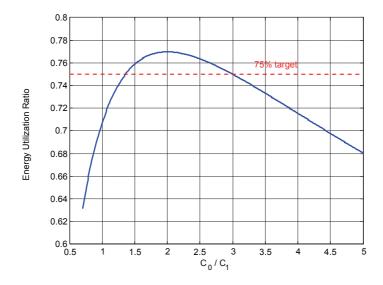

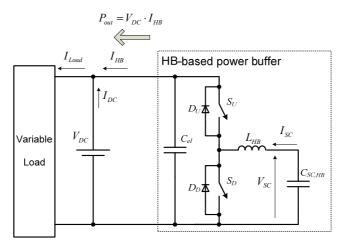

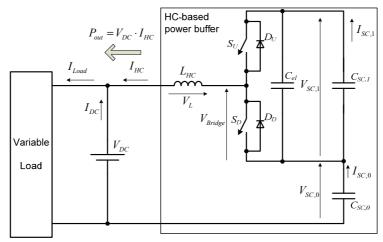

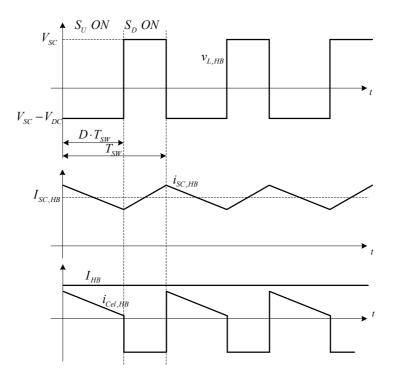

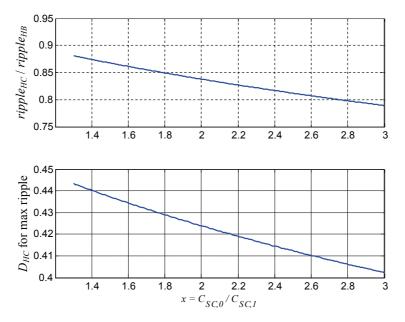

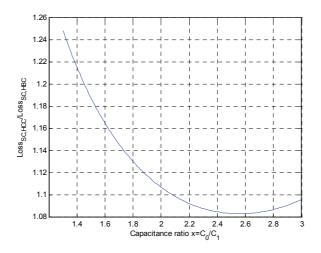

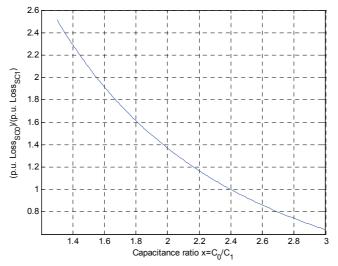

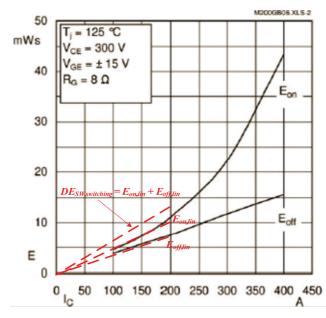

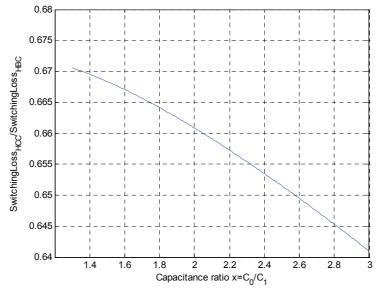

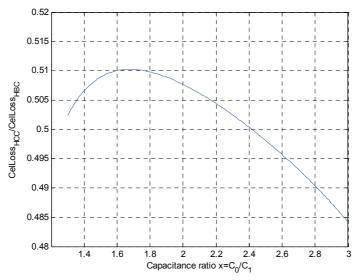

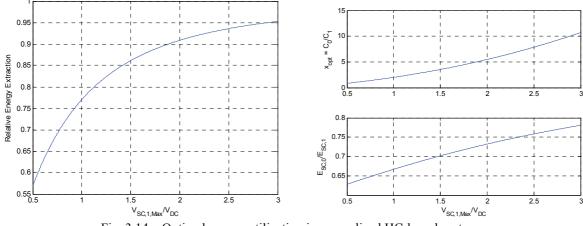

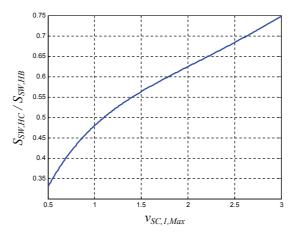

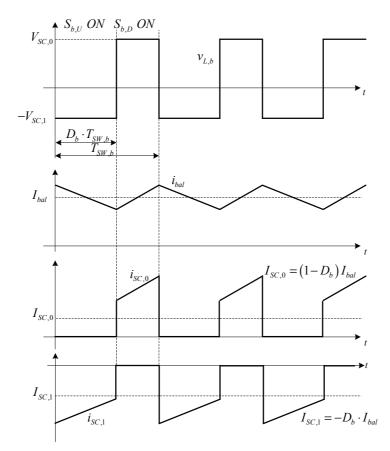

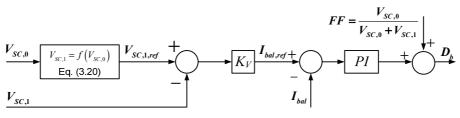

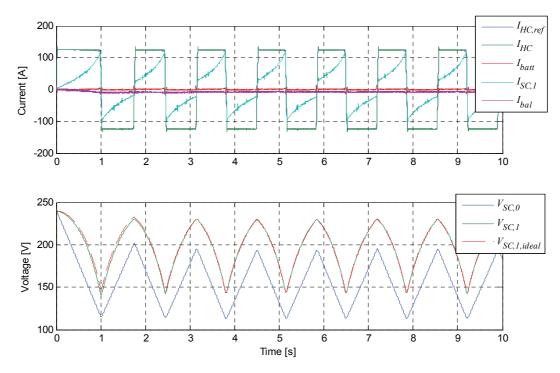

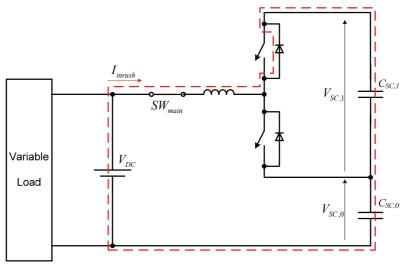

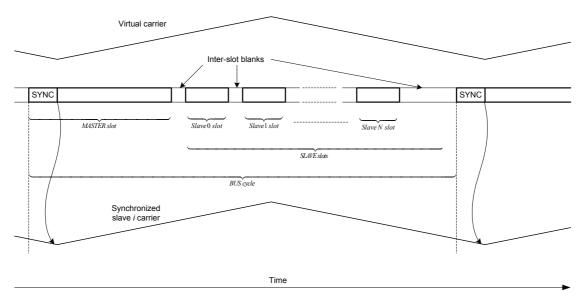

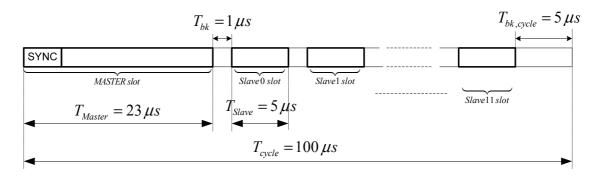

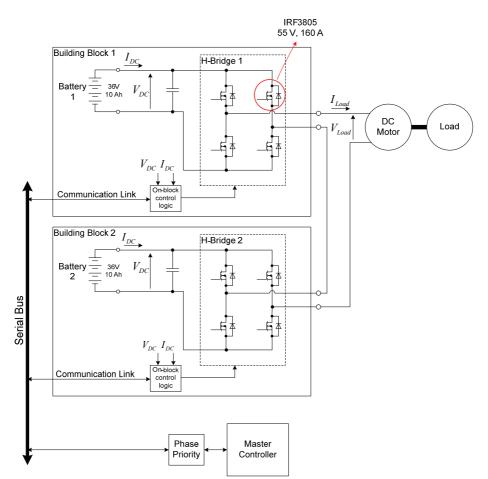

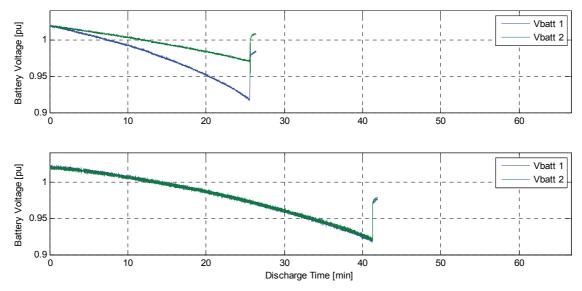

- Electric drive train (electric motor, inverter, transmission system) is assumed to have an overall efficiency of 80%, constant over the whole operating range;