### SAR ADC in 22 nm FDSOI

#### Henrik Fon

Master of Science in Electronics Submission date: June 2018 Supervisor: Trond Ytterdal, IES

Norwegian University of Science and Technology Department of Electronic Systems

## **Problem Description**

The continuous downscaling of CMOS technologies provides new challenges and opportunities for energy efficient SAR ADCs. The main objective of this project is to design an energy efficient SAR ADC in a 22 nm FDSOI CMOS technology for application in medical ultrasound imaging applications. The following work flow is suggested.

- Choose the most promising architecture and develop a behavioural model

- Use the model to derive specifications for the different building blocks

- Implement the ADC on transistor level

- Do the layout of the ADC

- Verify the ADC design based on netlist extracted from layout

The SAR ADC should satisfy the following specifications.

- Resolution: At least 10 bits ENOB

- Sampling rate: 100 MHz

- Power: Minimize

- Power supply: Optimize

- Bulk bias voltage: Optimize

- ADC category: Nyquist

The specifications of the SAR ADC needs to be verified post-layout by simulations on an extracted netlist of the ADC.

## Summary

Successive Approximation (SAR) Analog-to-Digital Converters (ADCs) are among the most energy efficient ADCs and has therefore received enormous attention in medical and wireless applications. The great energy efficiency of SAR ADCs are mainly attributed to the downscaling of Complementary Metal-Oxide-Semiconductor (CMOS) circuits, since the SAR architecture benefits greatly by going to smaller and smaller CMOS process nodes. Due to this excellent scaling, the introduction of smaller CMOS nodes opens up for new opportunities and challenges when designing SAR ADCs.

In this thesis, the speed limits of SAR ADCs have been pushed, while high resolution and energy efficiency are maintained. The SAR designed in this thesis is a Nyquist ADC intended for medical ultrasound applications and is designed in a 22 nm Fully Depleted Silicon-On-Insulator (FDSOI) process. The designed SAR ADC is simulated post-layout and the mean Monte Carlo results yields an Effective Number of Bits (ENOB) of 10.2 bits at a sample rate of 100 MS/s. The power consumption is 268  $\mu$ W and the resulting mean Monte Carlo Walden Figure of Merit (FoM) for the ADC is 2.29 fJ/conv.-step. This is currently better than all state-of-the-art ADCs with similar specifications. The ADC designed is also unique in the sense that no one else has managed similar speed and resolution with the same simple pure SAR ADC architecture.

These results are accomplished by using a popular dynamic latch comparator with capacitive loading, improving on already existing bootstrapped switch topology, improvement on already existing Capacitive Digital-to-Analog Converter (CDAC) architecture to greatly increase linearity and still achieve small unit capacitance, a custom made digital circuitry that has very low propagation delay and clock generation based on CDAC bottom plate.

## Sammendrag

Suksessiv Approksimasjon (SAR) Analog-til-Digital Konverter (ADC) er blant den mest energieffektive datakonverter arkitekturen og har derfor mottatt enormt mye oppmerksomhet innen medisinske og trådløse applikasjoner. Energieffektiviteten er hovedsakelig på grunn av nedskaleringen av Komplementær Metall-Oksid-Halvleder (CMOS) kretser, siden SAR arkitekturen skalerer utmerket med mindre og mindre CMOS prosessnoder. På grunn av denne eksepsjonelle skaleringen, vil introduksjon av nye prosessnoder gi nye muligheter og utfordringer ved design av SAR datakonvertere.

I denne masteroppgaven har hastighetsgrensen til SAR datakonvertere blitt presset til nye grenser, mens oppløsningen og energieffektivitet er vedlikeholdt. SAR datakonverteren i denne oppgaven er en Nyquist ADC beregnet for bruk innen medisinsk ultralyd applikasjoner designet i en 22 nm Fullstendig Utarmet Silisium-på-Isolator (FDSOI) prosess. Datakonverteren laget i denne masteroppgaven er simulert etter utlegg og oppnår en gjennomsnittlig Monte Carlo Effektiv Antall Bits (ENOB) på 10.2 bits med en punktprøvefrekvens på 100 MS/s. Effektforbruket til datakonverteren er på 268  $\mu$ W og resulterende gjennomsnittlig Monte Carlo Walden godhetstall på 2,29 fJ/conv.-step. Dette er per dags dato bedre enn all annen state-of-art datakonvertere med lignede spesifikasjoner. Datakonverteren laget i denne oppgaven er også unik da ingen har tidligere klart å lage en enkel ren SAR ADC med samme hastighet og oppløsning samtidig.

Disse resultatene er oppnådd ved å bruke en populær dynamisk komparator med kapasitiv last, forbedring av allerede eksisterende samplingsbryter topologi, forbedring av en allerede eksisterende Kapasitiv Digital-til-Analog Konverter (CDAC) arkitektur for å øke linearitet og likevel oppnå en liten enhetskapasitans, en tilpasset digital krets med veldig lav forplantningsforsinkelse og klokke generering basert på CDAC bunnplate.

## Preface

This master thesis concludes 5 years at Norwegian University of Science and Technology (NTNU) at Department of Electronic Systems (IES). The time frame for this project has been 20 weeks starting from January 15<sup>th</sup> and includes literature search, behavior modelling, schematic design, layout and post-layout verification of a SAR ADC. The project has been done under supervision of Professor Trond Ytterdal with IES.

I would like to thank Professor Trond Ytterdal for always being available for questions and for excellent guidance during our weekly meetings. It has been great and I look forward continue as your Ph.D. student starting fall 2018.

## Table of Contents

| Pr | oblen                      | n Description                                                                          | i                       |

|----|----------------------------|----------------------------------------------------------------------------------------|-------------------------|

| Su | mma                        | ry                                                                                     | ii                      |

| Sa | mme                        | ndrag                                                                                  | iii                     |

| Pr | eface                      |                                                                                        | iv                      |

| Та | ble of                     | f Contents                                                                             | vii                     |

| Li | st of ]                    | Tables                                                                                 | ix                      |

| Li | st of I                    | Figures                                                                                | xii                     |

| 1  | Intro<br>1.1<br>1.2<br>1.3 | oduction         Goal of This Thesis         Main Contributions         Thesis Outline | <b>3</b><br>4<br>4<br>5 |

| 2  | The                        | orv                                                                                    | 7                       |

| -  | 2.1<br>2.2                 | Transistors                                                                            | 7<br>7<br>8<br>9        |

|    | 2.2                        | Charge Redistribution SAR ADC Topology                                                 | 10                      |

|    | 2.4                        | CDAC Switching                                                                         | 11<br>11<br>13<br>14    |

|    | 2.5                        | Noise                                                                                  | 15<br>15<br>15          |

|   |      | 2.5.3     | Noise in Active Devices | 15        |

|---|------|-----------|-------------------------|-----------|

|   |      | 2.5.4     | Resistor Noise          | 16        |

|   | 2.6  | Distorti  | on                      | 17        |

|   |      | 2.6.1     | Settling Time           | 17        |

|   |      |           |                         | 17        |

|   |      | 2.6.3     | Switch Distortion       | 18        |

|   |      | 2.6.4     | CDAC Non-Linearity      | 19        |

|   |      | 2.6.5     | Gain Error              | 19        |

|   | 2.7  |           |                         | 19        |

|   |      |           |                         |           |

| 3 | 0    | n Level D | 0                       | 21        |

|   | 3.1  | Error B   | 6                       | 21        |

|   | 3.2  |           |                         | 23        |

|   |      |           |                         | 24        |

|   |      |           |                         | 25        |

|   |      |           | 1 7                     | 26        |

|   |      |           | e                       | 26        |

|   |      |           | e                       | 27        |

|   | 3.3  | CDAC S    | Switching               | 28        |

| 4 | Imp  | lementat  | tion 2                  | 29        |

| - | 4.1  |           |                         | 29        |

|   | 4.2  | -         |                         | 33        |

|   | 4.3  |           | 6                       | 36        |

|   |      |           | e                       | 36        |

|   |      |           |                         | 38        |

|   |      |           |                         | 38        |

|   |      |           |                         | 39        |

|   |      |           | 8                       | 41        |

|   | 4.4  |           | 6                       | 43        |

|   |      |           |                         | 43        |

|   |      |           |                         | 45        |

|   | 4.5  |           |                         | 45        |

|   |      | 5         |                         |           |

| 5 | Resu |           |                         | <b>49</b> |

|   | 5.1  |           |                         | 49        |

|   | 5.2  |           | 1 1                     | 52        |

|   | 5.3  |           |                         | 53        |

|   | 5.4  |           |                         | 54        |

|   | 5.5  | -         |                         | 56        |

|   | 5.6  |           |                         | 57        |

|   | 5.7  | Power C   | Consumption Breakdown   | 58        |

| 6            | Discussion                         | 61 |  |

|--------------|------------------------------------|----|--|

|              | 6.1 Comparison to State-of-the-art | 61 |  |

|              | 6.2 CDAC Mismatch                  | 62 |  |

|              | 6.3 Sampling Clock                 | 63 |  |

|              | 6.4 Digital Circuit                | 64 |  |

|              | 6.5 Digital Ports                  | 64 |  |

| 7            | Conclusion                         | 67 |  |

|              | 7.1 Future Works                   | 67 |  |

| Bibliography |                                    |    |  |

| A            | Schematics                         | 73 |  |

| B            | Layout                             | 83 |  |

## List of Tables

| 1.1        | Specifications for the ADC                                                                                              | 4        |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Quantization parameters needed for error budgeting.                                                                     | 22<br>22 |

| 4.1        | Relations between input and output during comparison phase of the com-<br>parator.                                      | 30       |

| 4.2        | Transistor multipliers for the strongARM latch. All transistors are unit analog transistors unless specified otherwise. | 32       |

| 5.1        | Test bench Settings.                                                                                                    | 51       |

| 5.2        | Simulation results over corners.                                                                                        | 53       |

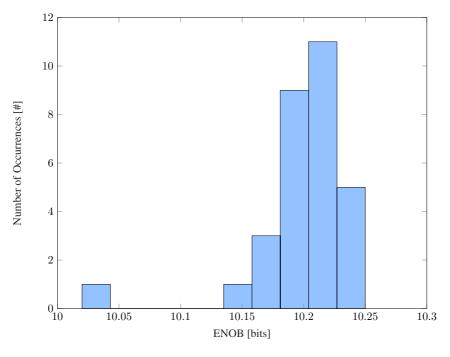

| 5.3        | Mismatch results obtained from 30 Monte Carlo simulations.                                                              | 55       |

| 5.4        | Simulation results for different sample rates $f_s$ with constant $V_{DD} = 700$ mV and $V_{BULK} = 500$ mV.            | 57       |

| 5.5        | Simulation results for various sample rates $f_s$ with different $V_{DD}$ and                                           |          |

|            | $V_{BULK}$                                                                                                              | 58       |

| 5.6        | Power consumption breakdown for a nominal process.                                                                      | 59       |

| 6.1        | State-of-the-art ADC comparison.                                                                                        | 62       |

## List of Figures

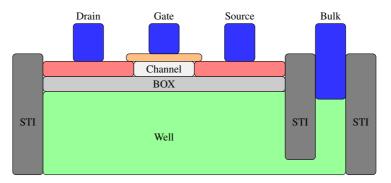

| 2.1                                                                                                                | General FDSOI transistor structure.                                                                                                           | 8                                                  |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

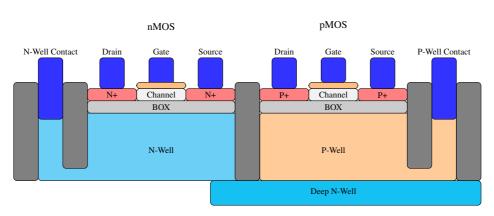

| 2.2                                                                                                                | Flip-well architecture for nMOS and pMOS.                                                                                                     | 9                                                  |  |  |

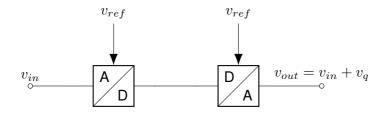

| 2.3                                                                                                                | Quantization of $v_{in}$ to obtain $v_{out}$ .                                                                                                | 9                                                  |  |  |

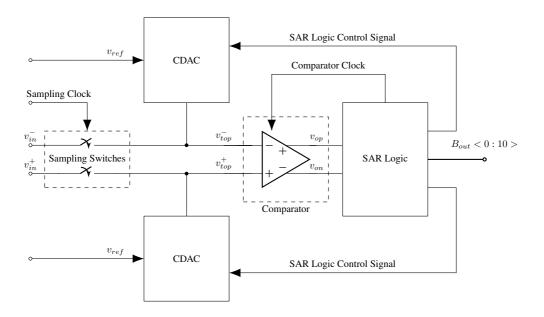

| 2.4                                                                                                                | General differential SAR topology.                                                                                                            | 11                                                 |  |  |

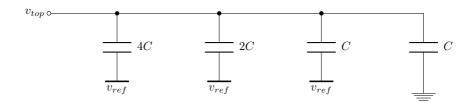

| 2.5                                                                                                                | 3 bit CDAC with top plate voltage $v_{top}$                                                                                                   | 12                                                 |  |  |

| 2.6                                                                                                                | 3 bit CDAC with top plate voltage $v'_{top}$                                                                                                  | 12                                                 |  |  |

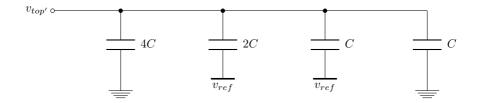

| 2.7                                                                                                                | Flow chart description of monotonic switching                                                                                                 | 13                                                 |  |  |

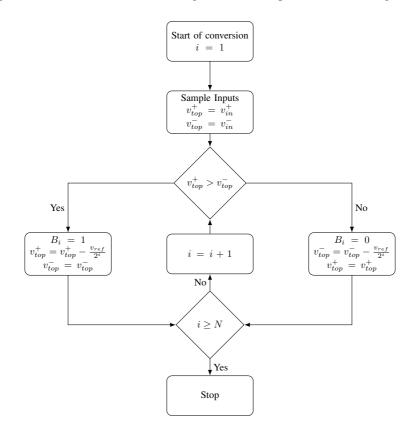

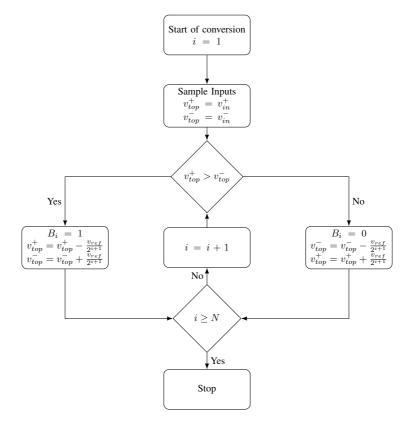

| 2.8                                                                                                                | Flow chart description of split-monotonic switching                                                                                           | 14                                                 |  |  |

| 2.9                                                                                                                | Noise models for a MOSFET device.                                                                                                             |                                                    |  |  |

| 2.10                                                                                                               | Resistor noise model with connection to capacitance for noise power cal-                                                                      |                                                    |  |  |

|                                                                                                                    | culation                                                                                                                                      | 17                                                 |  |  |

|                                                                                                                    | Sampling switch model with capacitive CDAC load                                                                                               | 18                                                 |  |  |

| 2.12                                                                                                               | Chain of inverters to drive a large capacitive load                                                                                           | 19                                                 |  |  |

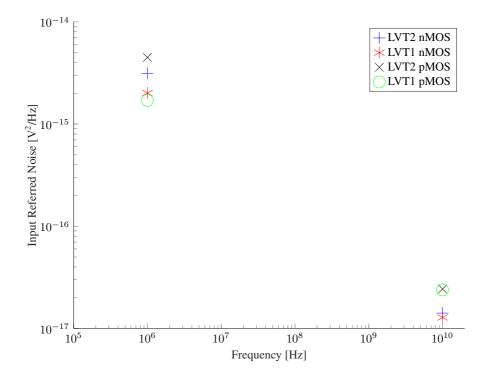

| 3.1                                                                                                                | Noise performance of various low threshold voltage devices. The spectral density magnitude is extracted for 1 MHz and 10 GHz to study flicker |                                                    |  |  |

| 3.2                                                                                                                | noise and thermal noise separately                                                                                                            | 24<br>25                                           |  |  |

| 3.2<br>3.3                                                                                                         | noise and thermal noise separately                                                                                                            |                                                    |  |  |

| 3.3                                                                                                                | noise and thermal noise separately                                                                                                            | 25<br>26                                           |  |  |

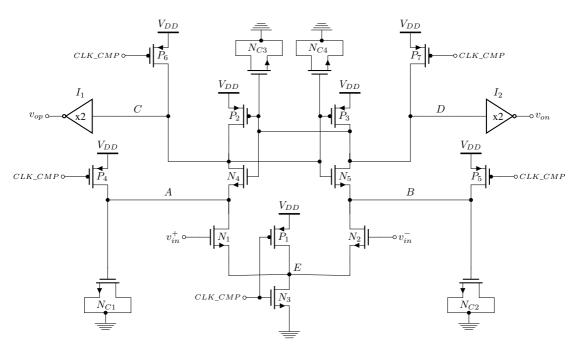

| <ul><li>3.3</li><li>4.1</li></ul>                                                                                  | noise and thermal noise separately                                                                                                            | 25<br>26<br>30                                     |  |  |

| <ul><li>3.3</li><li>4.1</li><li>4.2</li></ul>                                                                      | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33                               |  |  |

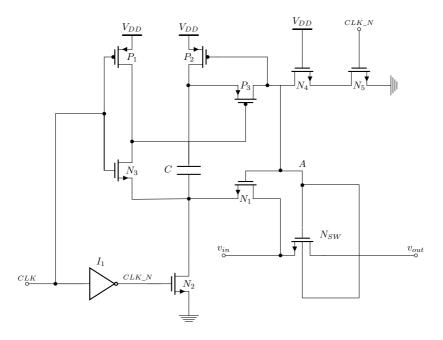

| <ul><li>3.3</li><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                          | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34                         |  |  |

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul>                                        | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35                   |  |  |

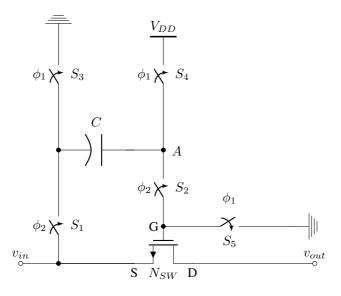

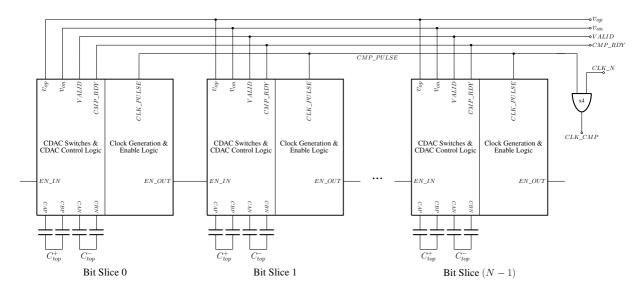

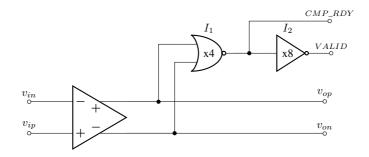

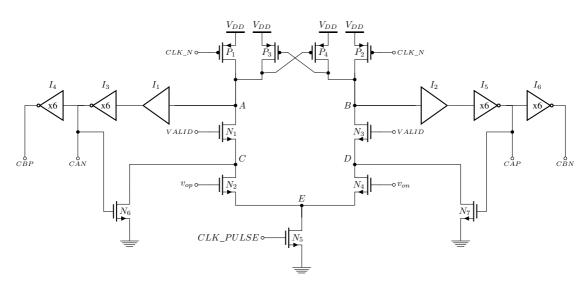

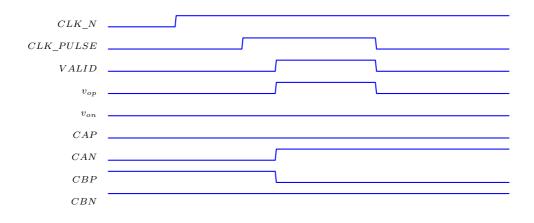

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                           | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35<br>37             |  |  |

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul>                                        | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35                   |  |  |

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35<br>37             |  |  |

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35<br>37<br>37       |  |  |

| <ul> <li>3.3</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul> | noise and thermal noise separately                                                                                                            | 25<br>26<br>30<br>33<br>34<br>35<br>37<br>37<br>38 |  |  |

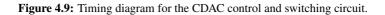

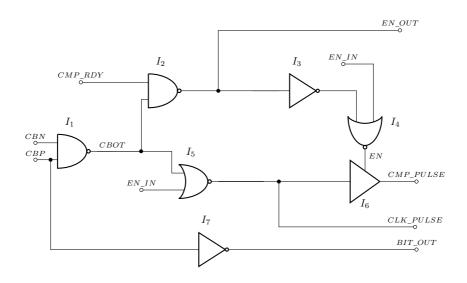

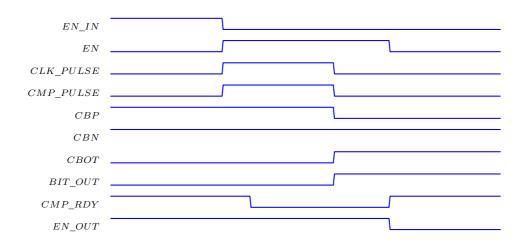

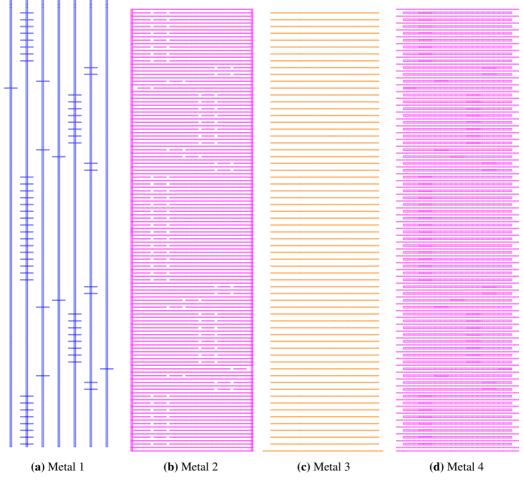

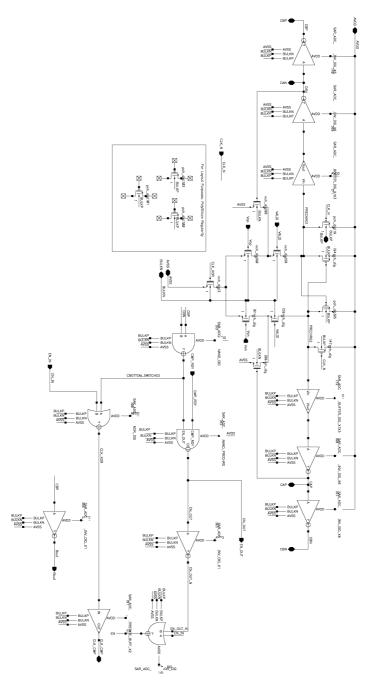

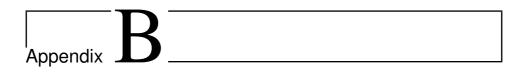

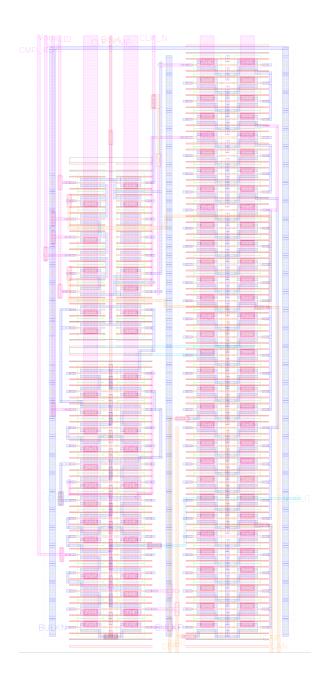

| 4.11<br>4.12 | Comparator clock generation and enable logic circuit.       42         Timing diagram for the clock generation logic and enable logic.       42         Metal stack of CAP64.       42 <b>Top-level layout of SAR ADC</b> – Digital Circuitry (A), Sampling Switches |    |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

|              | (B), Comparator (C), CDAC (D), Digital ports at comparator outputs and inverter for inverting sampling clock (E)                                                                                                                                                     | 46 |  |  |  |

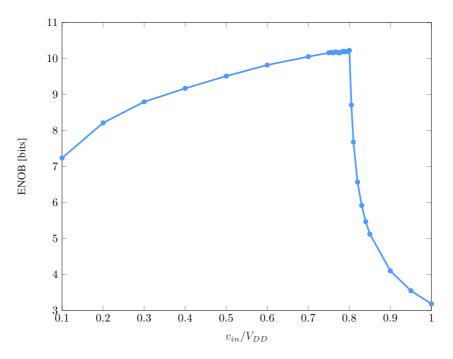

| 5.1          | ENOB for different values of $v_{in}/V_{DD}$ .                                                                                                                                                                                                                       | 52 |  |  |  |

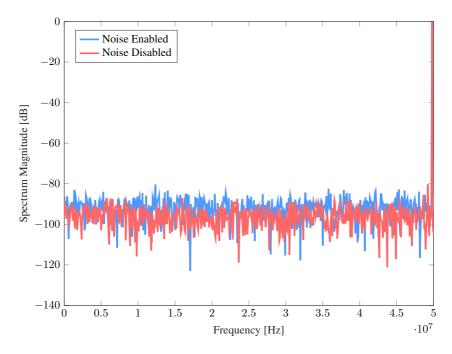

| 5.2          | 1024 point FFT for nominal corner with and without noise with input sinusoidal frequency $f_{in} = 49.71$ MHz                                                                                                                                                        |    |  |  |  |

| 5.3          | ENOB obtained from 30 Monte Carlo mismatch simulations. $\dots$                                                                                                                                                                                                      | 55 |  |  |  |

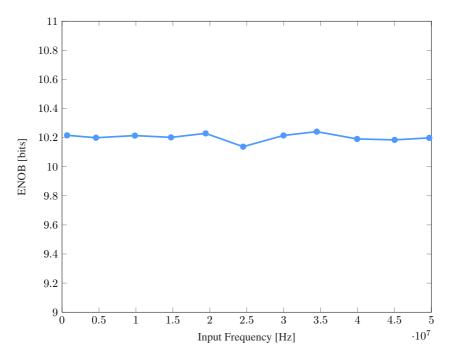

| 5.4          | ENOB versus input frequency.                                                                                                                                                                                                                                         | 56 |  |  |  |

| 5.4          |                                                                                                                                                                                                                                                                      | 50 |  |  |  |

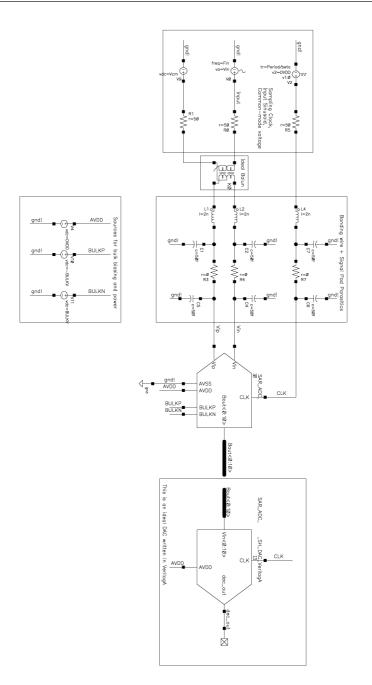

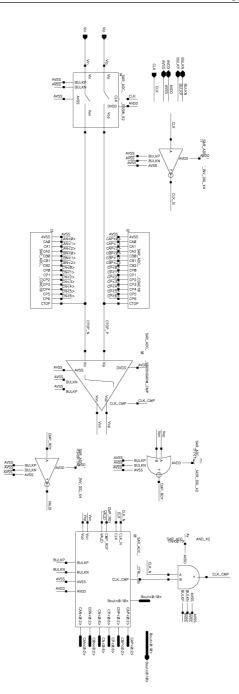

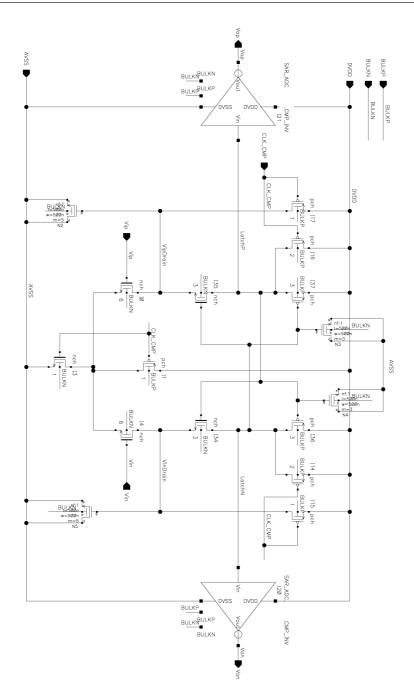

| A.1          | Schematic of test bench used for final verification.                                                                                                                                                                                                                 | 74 |  |  |  |

| A.2          | Schematic of top level SAR ADC.                                                                                                                                                                                                                                      | 75 |  |  |  |

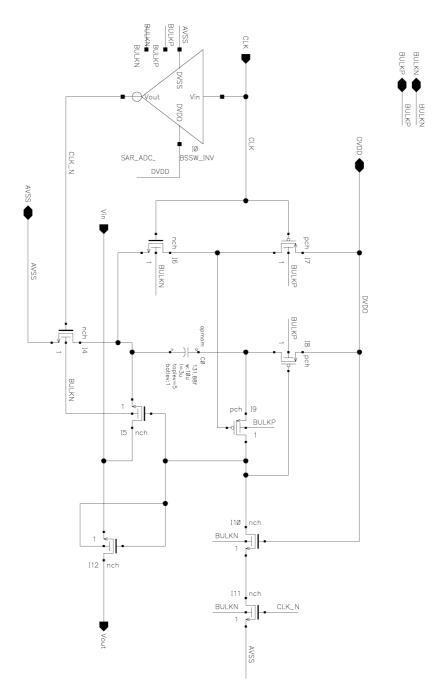

| A.3          | Schematic of comparator.                                                                                                                                                                                                                                             | 76 |  |  |  |

| A.4          | Schematic of bootstrapped switch.                                                                                                                                                                                                                                    | 77 |  |  |  |

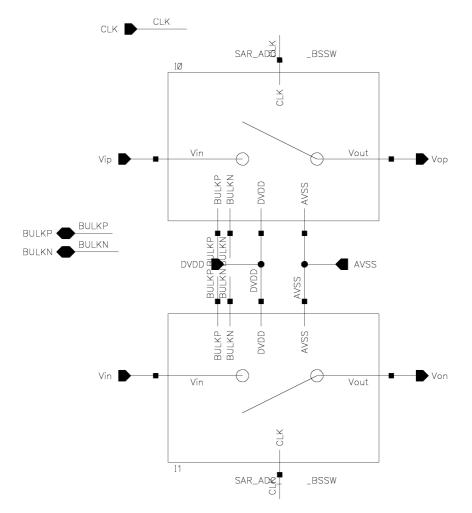

| A.5          | Schematic of bootstrapped switch for both inputs.                                                                                                                                                                                                                    | 78 |  |  |  |

| A.6          | Schematic of a single bitslice.                                                                                                                                                                                                                                      | 79 |  |  |  |

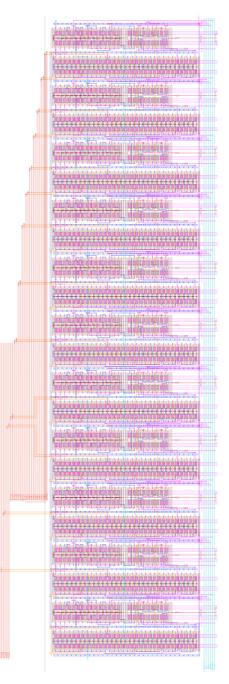

| A.7          | Schematic of all the bitslices.                                                                                                                                                                                                                                      | 80 |  |  |  |

| A.8          | Schematic of precharged NAND gate.                                                                                                                                                                                                                                   | 81 |  |  |  |

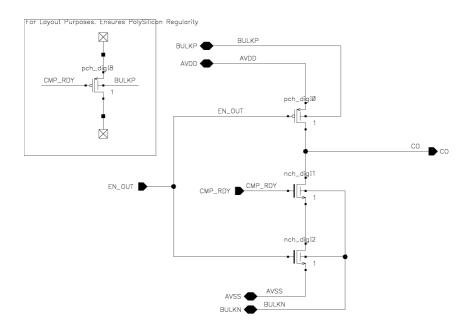

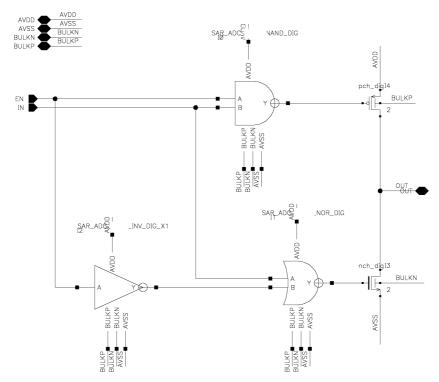

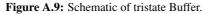

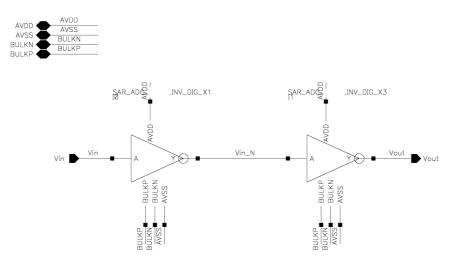

| A.9          | Schematic of tristate Buffer.                                                                                                                                                                                                                                        | 81 |  |  |  |

| A.10         | Schematic of digital buffer                                                                                                                                                                                                                                          | 82 |  |  |  |

| <b>B</b> .1  | Top-level layout of SAR ADC.                                                                                                                                                                                                                                         | 84 |  |  |  |

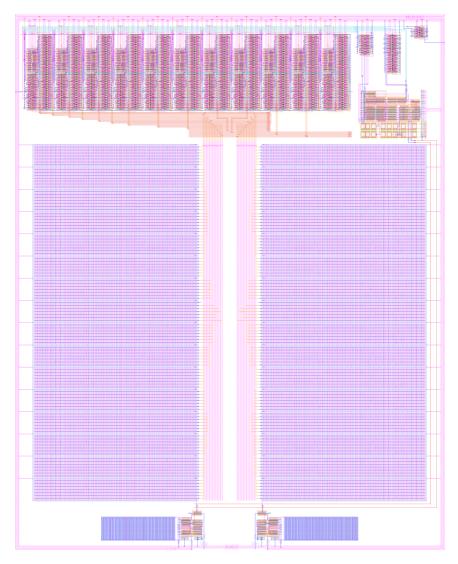

| B.2          | Layout of comparator.                                                                                                                                                                                                                                                | 85 |  |  |  |

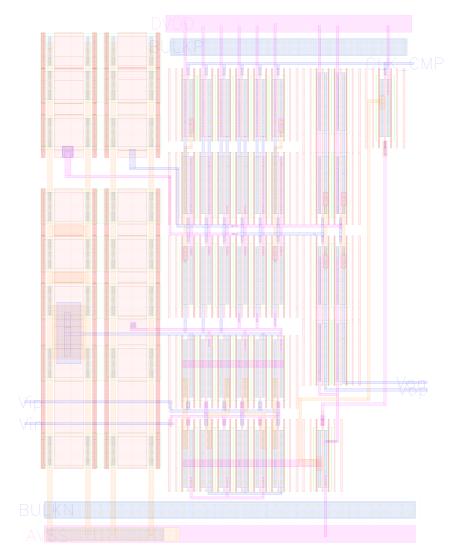

| B.3          | Layout of bootstrapped Switch.                                                                                                                                                                                                                                       | 86 |  |  |  |

| B.4          | Layout single bit slice.                                                                                                                                                                                                                                             | 87 |  |  |  |

| B.5          | Layout of all bit slices.                                                                                                                                                                                                                                            | 88 |  |  |  |

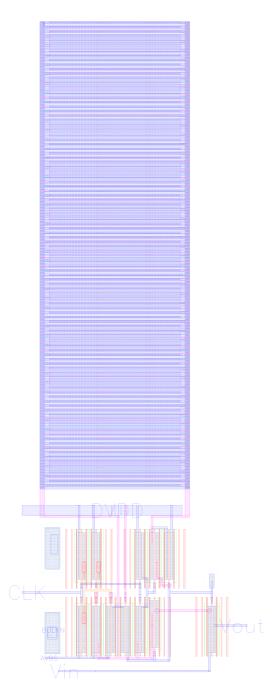

| B.6          | Layout of CAP64                                                                                                                                                                                                                                                      | 89 |  |  |  |

| B.7          | Layout of CDAC.                                                                                                                                                                                                                                                      | 90 |  |  |  |

### Glossary

- ADC Analog-to-Digital Converter. ii–iv, 3, 4, 7, 9–15, 17–19, 21–23, 27–29, 36, 38, 39, 41, 43, 45, 49–59, 61–64, 67, 83

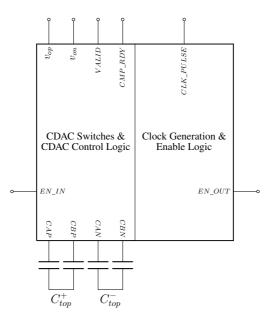

- BOX Buried Oxide. 7, 8

- **CDAC** Capacitive Digital-to-Analog Converter. ii, iii, 3, 4, 10, 11, 13, 14, 16–19, 21, 22, 28, 29, 36, 38–40, 42, 43, 45, 47, 54, 56, 58, 61–63, 67, 83

- CMOS Complementary Metal-Oxide-Semiconductor. ii, iii, 3, 8, 15, 16

- DAC Digital-to-Analog Converter. 9, 49, 50, 56

- **DNL** Differential Nonlinearity. 49

- DRC Design Rule Check. 23, 47

- **ENOB** Effective Number of Bits. ii, iii, 10, 14, 15, 17–19, 21, 23, 26, 36, 45, 46, 49–58, 61, 62, 64, 67

- **ESD** Electrostatic Discharge. 50

- FDSOI Fully Depleted Silicon-On-Insulator. ii, iii, 4, 7, 8, 23, 35, 62, 67

- **FFT** Fast Fourier Transform. 50, 56

- **FoM** Figure of Merit. ii, 23, 28, 50, 51, 53, 57–59, 61, 62, 67

- **IES** Department of Electronic Systems. iv

- **INL** Integral Nonlinearity. 49

- **ISSCC** International Solid-State Circuits Conference. 61

- LSB Least Significant Bit. 12, 28

- LSBs Least Significant Bits. 45

- LVT1 Low Treshold Voltage 1. 23–27, 33

- LVT2 Low Treshold Voltage 2. 23–27

- M1 Metal 1. 36, 43, 44, 47

- M2 Metal 2. 43, 44, 47

- M3 Metal 3. 43-45

- M4 Metal 4. 43–45

- M5 Metal 5. 36

- MOM Metal-Oxide-Metal. 36, 43, 62

- MOSFET Metal Oxide Semiconductor Field Effect Transistor. 15, 16, 18, 25, 33

- MSB Most Significant Bit. 12, 13, 17, 28

- **nMOS** n-channel MOSFET. 8, 23–27, 29–31, 33, 39, 51, 53

- NTNU Norwegian University of Science and Technology. iv, 67

- **PDK** Process Design Kit. 7, 8, 36, 51, 53, 62

- **pMOS** p-channel MOSFET. 8, 23–27, 29–31, 33, 39, 47, 51, 53

- **PVT** Process-Voltage-Temperature. 39, 64

- **RMS** Root Mean Square. 9, 10, 21, 22, 32

- **SAR** Successive Approximation. ii–iv, 3, 4, 7, 10–12, 14, 17–19, 21, 23, 28, 29, 36, 38, 39, 45, 49, 50, 58, 61, 62, 64, 67, 83

- SINAD Signal to Noise and Distortion Ratio. 10, 21–23, 49, 50, 52, 56

- **SPICE** Simulation Program for Integrated Circuits Emphasis. 23

- VLSI Very Large Scale Integration. 7, 61

## Chapter ]

## Introduction

The continuous downscaling of Complementary Metal-Oxide-Semiconductor (CMOS) technology is mainly motivated by more energy efficient digital circuits. While digital circuits benefit greatly from going to smaller process nodes, analog design in nanoscale CMOS nodes becomes increasingly more difficult. The trend is towards more and more digital chips, but analog circuits are still necessary. One such analog circuit is the Analog-to-Digital Converter (ADC) that provides the interface between the analog and digital domain. Many ADC topologies do exist, but when it comes to energy efficiency, the current trend would indicate that Successive Approximation (SAR) ADCs are among the most energy efficient ADCs [1]. The SAR ADC topology is very simple and consists of just a comparator, a Capacitive Digital-to-Analog Converter (CDAC), a digital control circuit and a sampling switch. The simple architecture makes SAR ADCs very attractive and suitable for smaller process nodes, as many of the blocks scale very well with smaller nodes, especially the digital circuitry.

The SAR topology has proven itself suitable for a wide range of specifications. The SAR handles low speed and high accuracy<sup>1</sup> applications [2], but is also suited for high speed and low accuracy<sup>2</sup> applications [3]. However, applications that may require high speed and high resolution using a pure simple SAR ADC has yet to emerge. If one considers hybrid solutions, then the SAR assisted digital slope ADC [4], interleaved subranging SAR ADC with  $\Delta\Sigma$  [5], two-step SAR ADC [6], pipelined SAR ADC [7] are topologies that can satisfy the requirement needed for a high speed and high resolution ADC. However, the ADCs mentioned are not pure SAR ADCs and this increases the design complexity. The SAR ADC presented in [8] is a pure SAR ADC with high resolution and high speed, but uses a dual reference voltage scheme and the ADC needs to be calibrated. This severely increases the power consumption and complexity of the ADC and makes the ADC less attractive. The approaches presented above are interesting, but a simple pure SAR ADC with similar specifications do not exists as of yet.

<sup>&</sup>lt;sup>1</sup>speed < 10 MS/s, resolution > 10 bits

$<sup>^{2}</sup>$ speed > 50 MS/s, resolution < 10 bits

#### 1.1 Goal of This Thesis

The goal of this thesis is to design a pure SAR ADC with efficiency comparable to state-ofthe-art ADC designs. The ADC should push the limits in terms of speed and still manage high resolution. The ADC should be verified post-layout using a commercially available 22 nm Fully Depleted Silicon-On-Insulator (FDSOI) process. The specifications for the ADC can be found in Table 1.1.

| Table 1.1 | : Spe | ecifications | for | the | ADC |

|-----------|-------|--------------|-----|-----|-----|

|-----------|-------|--------------|-----|-----|-----|

| Resolution         | > 10 bits ENOB |

|--------------------|----------------|

| Sampling frequency | 100 MS/s       |

| Power              | Minimize       |

| Power supply       | Optimize       |

| Bulk bias voltage  | Optimize       |

| ADC category       | Nyquist        |

#### **1.2 Main Contributions**

The main contributions of this thesis are.

- Behaviour modelling, schematic design, layout design and post-layout verification of a high speed, high accuracy SAR ADC in 22 nm FDSOI

- Error budgeting for error distribution and to obtain specifications for the different subcircuits

- Use of a popular comparator topology with capacitive loading at certain nodes to enhance noise performance

- Improvement on already existing bootstrapped switch topology by reducing transistor count and by bulk to gate connection of switching transistor. This saves power and area and the linearity of the switch is increased

- Improvement on already existing CDAC topology. The result is a very linear CDAC and small unit capacitance

- Clock generation based on CDAC bottom plate and with additional feed forwards from the comparator

- Custom made digital logic to achieve very low propagation delay and fast switching speed that is suitable for high speed

- Use of a hybrid switching technique using split-monotonic switching and monotonic switching with a common-mode decrease during switching

- Utilization of bulk biasing of digital circuitry for speed increase

#### 1.3 Thesis Outline

This thesis will be organized as follows.

- Chapter 2 Theory: Background theory needed for this thesis is covered.

- Chapter 3 High Level Design: High level design choices and error budget is presented.

- **Chapter 4 Implementation:** A detailed description of the different subcircuits implemented.

Chapter 5 - Results: Test bench and post-layout results are presented.

Chapter 6 - Discussion: Comparison to state-of-the-art and discussion of results.

Chapter 7 - Conclusion: Concluding remarks and future works are described.

# Chapter 2

## Theory

This chapter will cover with some of the background theory needed for this thesis. The subsequent sections will show the transistor architecture used in this thesis and some key parameters of a quantized signal. Thereafter, the SAR ADC will represented as a block diagram and explained briefly. The internal switching operation in a SAR ADC will be explained and analyzed, followed by presentation of two practical switching algorithms. Afterwards, some noise theory will be presented along with sources of distortion in a SAR ADC. Finally, digital buffers driving large capacitive loads will be covered.

#### 2.1 Transistors

This section will present the transistor technology used in this thesis. The general transistor structure will be presented, followed by theory on the flipped-well architecture available in the used Process Design Kit (PDK).

#### 2.1.1 Fully Depleted Silicon On Insulator

As Moore's law is approaching the end, transistor development has to take another path other than just reducing the gate length of the transistor. Not only is there a fundamental limit for the gate length, but leakage current is also a major issue in Very Large Scale Integration (VLSI), where millions (and billions) of transistors are put on a single chip. Facing these problems, it is obvious one has to move away from the conventional bulk process and develop new techniques to enhance transistor performance. One suggested contender to the well established bulk process is the FDSOI transistor structure. In a FDSOI process, a Buried Oxide (BOX) is grown directly on the substrate and then a very thin fully depleted silicon layer is deposited on the BOX as seen in Figure 2.1. The fully depleted silicon act as the transistor's channel and the small thickness of the channel lowers the doping effort needed. In some devices, the channel is even left undoped. The lower doping of the channel reduces the stochastic mismatch since the doping variability is lowered and it also increases the mobility of the transistor due to less impurities in the channel from doping. The lower amount of impurities in the channel also improves the flicker noise performance of the transistor due to fewer collisions.

Figure 2.1: General FDSOI transistor structure.

The leakage current is also reduced with this architecture, as the insulating nature of the BOX reduces the bulk leakage current compared to a conventional CMOS bulk process. Since the substrate is now insulated from the source/drain contacts by the BOX, the parasitic PN junctions between the substrate and source/drain are completely eliminated. This makes biasing of the bulk a much more viable option than in a conventional bulk process. Not only due to lack of the PN junctions, but also because the channel is more sensitive to bulk biasing. This allows for optimization of speed and power by just biasing the bulk of the transistor.

#### 2.1.2 Flipped-Well

FDSOI transistor technology offers much more variation when it comes to well placements for transistors. One example of this is the flipped-well architecture available in a FDSOI process. The flipped-well configuration allows n-channel MOSFET (nMOS) transistors to reside in a N-well, while the p-channel MOSFET (pMOS) reside in a P-well as seen in Figure 2.2. This well configuration is in contrast to normal bulk transistor technology where the well placement is opposite.

The main motivation for this well configuration is that it allows for enhancement of speed by biasing the bulks of the transistor at the cost of increased leakage current. For the Nwell, a positive voltage between 0 to +2V can be applied to the N-well contact to lower the threshold voltage of the transistor, while the P-well can be biased with voltage between -2V to 0 to lower the threshold voltage. The lowered threshold voltage increases the speed of the devices since the overdrive is increased. For the P-well, a deep N-well has to be utilized to avoid biasing the entire substrate. This is not necessary for the N-well, as the N-well is formed on top of the substrate in "isolated" patches. In the used 22 nm FDSOI PDK, the flip-well configuration is only available to certain low threshold devices. The conventional well configuration is of course also present for devices with higher threshold voltages.

Figure 2.2: Flip-well architecture for nMOS and pMOS.

#### 2.2 Quantization

Quantization is the process to quantize the amplitude of an analog signal for bit representation. The quantization process inherently introduces noise to the quantized signal due to the finite number of quantization intervals. To analyze certain properties of quantization, assume now that a signal  $v_{in}$  is first digitized by an N bit ADC and then converted back to the analog domain by an N bit Digital-to-Analog Converter (DAC) as in Figure 2.3.

Figure 2.3: Quantization of  $v_{in}$  to obtain  $v_{out}$ .

The output signal  $v_{out} = v_{in} + v_q$  now contains the input signal  $v_{in}$  along with a small error term  $v_q$ . The term  $v_q$  is not a constant, but is bound as

$$|v_q| \le v_{ref}/2^{N+1} \tag{2.1}$$

This bound shows that the best resolution we can get is no better than  $v_{ref}/2^N$  and this quantity is referred to as  $V_{LSB}$ . The term  $v_q$  is stochastic and is typically approximated as being white in the frequency domain. This is a good approximation if N is high and if  $v_{in}$  varies rapidly. With these assumptions, it can be shown [9] that  $v_q$  is a zero mean signal with Root Mean Square (RMS) value of

$$v_{q,RMS} = \frac{v_{ref}}{2^N \sqrt{12}} \tag{2.2}$$

Now that the RMS value of the quantization error has an analytical expression, it is possible to define a Signal to Noise and Distortion Ratio (SINAD) for the quantization process. In order to do this, assume an input sinusoid with input swing from 0 to  $v_{ref}$ . Such a sinusoid has a RMS value of  $v_{in,RMS} = v_{ref}/(2\sqrt{2})$  and the output SINAD is thus

$$SINAD = 20 \log_{10} \left( \frac{v_{in,RMS}}{v_{q,RMS}} \right)$$

(2.3)

$$= 20 \log_{10} \left( \sqrt{3/2} \cdot 2^N \right)$$

(2.4)

$$= 6.02N + 1.76 \quad [dB] \tag{2.5}$$

Eq. (2.5) shows that the SINAD only depends on the number of bits N. This result is only valid for an ideal ADC. A realistic ADC would have lower SINAD due to noise and distortion in the ADC that reduces SINAD that in turn also lowers the number of bits N. For a practical ADC, it is more common to define a new quantity Effective Number of Bits (ENOB) to reflect actual resolution of the converter. If one define N = ENOB for such an ADC and rearrange Eq. (2.5), one can obtain ENOB as

$$ENOB = \frac{SINAD - 1.76}{6.02} \quad [bits]$$

(2.6)

Eq. (2.6) gives ENOB in number of bits and the input SINAD is given in decibel.

#### 2.3 Charge Redistribution SAR ADC Topology

A SAR ADC architecture finds the digital output word  $B_{out}$  by doing a binary search internally in the ADC. This is typically done by using a CDAC and the operation of finding the output digital word is based on charge redistribution. To get a better understanding of the SAR ADC architecture, the SAR ADC in Figure 2.4 will be briefly be explained. For the differential architecture as seen in Figure 2.4, the following is done for each conversion:

- 1. The differential input voltage  $v_{in} = v_{in}^+ v_{in}^-$  is initially sampled at the CDAC top plates nodes  $v_{top}^+$  and  $v_{top}^-$  through the sampling switches.

- 2. The SAR Logic will then generate a clock signal to the comparator. The comparator then in turns compares the CDAC top plates voltages  $v_{top}^+$  and  $v_{top}^-$  that triggers either output  $v_{op}$  or  $v_{on}$  from the comparator high.

- 3. The output signals  $v_{op}$  and  $v_{on}$  are passed to the SAR Logic that generates control signals that go the CDAC. These control signals causes internal capacitors in the CDAC to have their bottom plates switched to a different potential.

- 4. This switching changes the differential voltage top plate voltage  $v_{top}^+ v_{top}^-$  by  $v_{ref}/2^i$  for i = 1, 2, 3, ..., (N 1), where N is the number of bits and  $v_{ref}$  is a reference voltage. The differential change in voltage gets smaller for each bit conversion.

- 5. After the voltage on the top plate has settled, this procedure is again repeated until all bits have been resolved.

Figure 2.4: General differential SAR topology.

The output digital word is then found at  $B_{out} < 0: 10 >$  and the ADC once again samples the differential input voltage for another conversion. It is seen that he conversion to the digital domain is done successively in a binary fashion by changing the top plate voltage by  $v_{ref}/2^i$ . This is how the SAR architecture gets its name. How the switching of the CDAC is performed is up to the designer as there exist many possibilities with different trade-offs such as complexity, power and common-mode voltage variations.

#### 2.4 CDAC Switching

A charge redistribution SAR ADC does the conversion to the digital domain by switching capacitors. In this section, charge redistribution will be analyzed and two switching algorithms will be reviewed.

#### 2.4.1 Charge Redistribution

A charge redistribution SAR ADC does the conversion from the analog domain to the digital domain by capacitor switching. To understand how this procedure work, the 3 bit CDAC shown in Figure 2.5 is used as an example without loss of generality, as the same principle is applicable for a N bit CDAC. Assume now that the top plate of the capacitors in Figure 2.5 has initially potential  $v_{top}$  and the total charge Q accumulated at the top plate is

$$Q = (4C + 2C + C)(v_{top} - v_{ref}) + Cv_{top}$$

(2.7)

Figure 2.5: 3 bit CDAC with top plate voltage  $v_{top}$ .

Figure 2.6: 3 bit CDAC with top plate voltage  $v'_{top}$ .

If the Most Significant Bit (MSB) capacitor is now switched to  $v_{ref}$  as seen in Figure 2.6, the top plate voltage is now changed to a different voltage potential  $v'_{top}$  due to charge conservation. The total charge Q on the top plate is in this case the same as in Figure 2.5 and can be written as

$$Q = (2C+C)(v'_{top} - v_{ref}) + (4C+C)v'_{top}$$

(2.8)

Due to charge conservation, the following holds true for the total charge Q on the top plate

$$3C(v'_{top} - v_{ref}) + 5C(v'_{top}) = 7C(v_{top} - v_{ref}) + Cv_{top}$$

(2.9)

Eq. (2.9) can be solved for  $v'_{top}$  to yield

$$v_{top}' = v_{top} - \frac{v_{ref}}{2}$$

(2.10)

Eq. (2.10) shows that this switching decreased the top plate voltage  $v_{top}$  by  $v_{ref}/2$ . This exercise is only done for the MSB capacitor, but similar calculation can be done for Least Significant Bits (LSBs) capacitors. The end result is that the top plate voltage decrements by the ratio  $\frac{v_{ref}}{2^i}$ , i = 1, 2, ..., (N - 1), for each capacitor switched. Lower values of capacitance switched decreases the top plate voltage by a smaller amount for each bit. It is this type of capacitor switching that is done internally in the SAR ADC to perform the binary search. The top plate voltage can also be incremented by  $\frac{v_{ref}}{2^i}$ . This is done by having all the capacitors' bottom plate initially at ground and then switch each capacitor one by one to  $v_{ref}$ .

#### 2.4.2 Monotonic Switching

Monotonic switching [10] is a non-differential charge redistribution switching technique. The algorithm is based on comparing both top plates voltages  $v_{top}^+$  and  $v_{top}^-$ , but only one of these voltages is changed for each bit conversion by capacitor switching. As an example, consider the MSB conversion, if  $v_{top}^+ > v_{top}^-$ , then  $v_{top}^+$  is decremented by  $\frac{v_{ref}}{2}$  and  $B_0 = 1$ . If  $v_{top}^+ < v_{top}^-$ , then then  $v_{top}^-$  is decremented by  $\frac{v_{ref}}{2}$  and  $B_0 = 0$ . This process is repeated for all the remaining bits, but the voltage subtracted from the top plate voltage is smaller for each bit. The full algorithmic description is shown in Figure 2.7.

Figure 2.7: Flow chart description of monotonic switching.

Since only one side of the input (positive or negative) has its CDAC switched for each bit, it's classified as a non-differential operation. The consequence is that it will affect the common-mode voltage of the differential signal. For the scheme used in Figure 2.7, the result would be a fall in the common-mode voltage during conversion. One of the great advantages of monotonic switching is that it utilize top plate sampling. In short, it means that only a (N-1) bit CDAC is required since a comparison is made before any switching is performed. However, the ADC still requires N comparisons for N bit resolution.

#### 2.4.3 Split-Monotonic Switching

The change in common-mode voltage makes monotonic switching troublesome to use, since it can be difficult for the comparator in the SAR ADC to handle. A large change in common-mode voltage might make the comparator too slow or increase the input referred noise, causing ENOB degradation. To preserve the common-mode voltage, a splitmonotonic switching [11] technique can be used. The switching procedure is identical to that of the monotonic-switching, but the switching operation is now done differentially. Since the operation is differential, each top plate of the CDAC is now decremented/incremented by  $\frac{v_{ref}}{2^{i+1}}$  instead of  $\frac{v_{ref}}{2^{i}}$ . The algorithmic description is seen in Figure 2.8.

Figure 2.8: Flow chart description of split-monotonic switching.

In terms of energy efficiency, behaviour simulations [12] show that split-monotonic switching on average require about twice the amount of switching energy compared to monotonic switching. Another disadvantage is that split-monotonic switching require more complicated routing since the number of nets to the CDAC doubles, which corresponds to area

<sup>&</sup>lt;sup>1</sup>The change in differential voltage is still  $\frac{v_{ref}}{2^i}$  for split-monotonic switching

and power increase. In a practical ADC, it is common to employ split-monotonic switching for the first few bits and do the rest of the conversion with monotonic switching. This gives a good trade-off between common-mode voltage variations and energy.

#### 2.5 Noise

All electronic devices are sources of noise which causes degradation in signal integrity in an electronic circuit. For an ADC, noise will cause a degradation in ENOB. These signals are stochastic in nature, so a statistical approach is used to characterize noise. One typically describes noise with parameters of a statistical probability function (like mean or variance) or by using frequency-domain analysis. In CMOS circuits, noise can roughly be divided into thermal noise and flicker noise.

#### 2.5.1 Thermal Noise

Thermal noise is due to the random motions of charge carriers due to their temperature. This kind of noise is proportional to absolute temperature and occurs in all resistors, even in semiconductor devices with resistivity<sup>2</sup>. The spectrum of thermal noise is modelled as being white in the frequency-domain and the time-domain amplitude of thermal noise follows a Gaussian probability density function.

#### 2.5.2 Flicker noise

Flicker noise occurs mainly in active devices and this type of noise is not fully understood. One can attribute some flicker noise due to impurities (doping) in a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) channel, but this is not the full picture. Flicker noise is a low frequency phenomena and the power spectrum is inversely proportional to frequency. There exists a simple empirical formula for the flicker noise's spectral density in MOSFET devices given by

$$v_{n,f}(f) = \frac{K}{WLC_{ox}f} \tag{2.11}$$

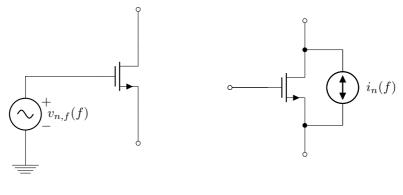

Where K is a constant dependent on device and process, WL is the gate area of the MOSFET and  $C_{ox}$  is the gate oxide capacitance. It is assumed that this noise source  $v_{n,f}(f)$  is connected in series with the device's gate as shown in Figure 2.9a.

#### 2.5.3 Noise in Active Devices

A MOSFET in the active region generates white noise due to the resistive channel. This noise can be modelled by a noisy drain current  $i_n$  as seen in Figure 2.9b. The spectral density of the current  $i_n$  has magnitude

$$i_n(f) = 4kT\gamma g_m \tag{2.12}$$

<sup>&</sup>lt;sup>2</sup>For example in the resistive channel of a MOSFET device.

(a) MOSFET flicker noise model.

(b) MOSFET thermal noise model

Figure 2.9: Noise models for a MOSFET device.

where  $\gamma$  is a white noise parameter and  $g_m$  is the transconductance of the device. A long channel device has  $\gamma = 2/3$ , but  $\gamma$  can be higher for devices with shorter channels. The noisy current  $i_n$  can be replaced by a noisy voltage source  $v_n(f)$  at the gate. This is done by dividing  $i_n$  by the transconductance squared  $g_m^2$  of the transistor.

#### 2.5.4 Resistor Noise

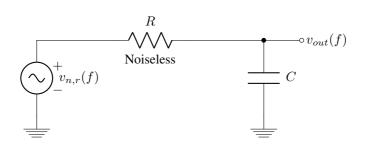

The noise in resistors and in MOSFET devices in the triode region can be modelled as being white in the frequency-domain with spectral density given by

$$v_{n,r}(f) = 4kTR \tag{2.13}$$

Where k is Boltzmann constant, T is the absolute temperature and R is the resistance of the device. This shows that the power spectral density  $v_{n,r}(f)$  is proportional to R and is constant for all frequencies f. A practical example would be to connect this resistor to a capacitor C as seen in Figure 2.10. This is realistic, because all nodes in a CMOS circuit have some non-zero capacitance to the substrate. To make the analysis easier, the resistor is considered noiseless and the resistor noise  $v_{n,r}(f)$  is put in series with the resistor. The connection in Figure 2.10 effectively forms a RC-filter that filters the noise. It can be shown that the total noise power  $\sigma_{n,r}$  at the node  $v_{out}(f)$  is now

$$\sigma_{n,r} = kT/c \tag{2.14}$$

The result in Eq. (2.14) is interesting, as the noise power  $\sigma_{n,r}$  is not dependent on R, but proportional to the absolute temperature T and inversely proportional to C. The dependency on R is gone, since the pole frequency of the filter decreases inversely with R, but the noise spectral density increases proportionally with R. The net effect is that R is cancelled. kT/c is fundamental formula, because it shows that all nodes in the circuit will produce noise with magnitude kT/c. This noise is important to consider when dimensioning the CDAC, since using too small capacitors might lead to excessive noise.

Figure 2.10: Resistor noise model with connection to capacitance for noise power calculation.

#### 2.6 Distortion

There exist several sources of ENOB degradation in the SAR ADC. Some of these sources will be described here mathematically and qualitatively.

#### 2.6.1 Settling Time

The CDAC top plate voltage can not change instantly in time, but its transient response is that of a RC-filter. This is due to the capacitance C from the CDAC and the resistance R from the switches at the bottom plate of the CDAC. When a unit step is applied to the RC-filter, the output response v(t) will be

$$v(t) = 1 - e^{-t/\tau} \tag{2.15}$$

Where  $\tau = RC$ . It is readily seen from 2.15 that the error from steady state is proportional to the term  $e^{-t/\tau}$ . For a N bit SAR ADC, it's required that the top plate of the CDAC settles within 1  $V_{LSB}$ . This is equivalent to

$$e^{(-t/\tau)} < 2^{-N} \tag{2.16}$$

The amount of time t needed for settling is thus given by

$$t = -\ln(2^{-N})\tau$$

(2.17)

It is seen that the required settling time is dependent on the number of bits, the CDAC capacitance C and the switch resistance R. For N = 11, the required time is  $t = 7.62\tau$ . This impose challenges for switching times, especially for SAR ADCs with high sampling frequency and many bits, since the MSB capacitor scales exponentially with N.

#### 2.6.2 Comparator Offset

Comparator offset is a phenomena where the threshold of the comparator has been shifted. The end result is that small differential inputs gives the wrong output due to this offset. This offset is typically caused by mismatch of the input transistors or a mismatch of capacitance in the comparator. This offset can be of systematic nature or of random nature. The systematic offset occurs when simulating post-layout, as perfect symmetrical layout is not possible. This offset can be corrected post-layout by simulations. The random offset is random in nature, it is not possible to correct this without calibration. However, one can increase the area of the input transistors or use more capacitance to reduce the effects of random offset.

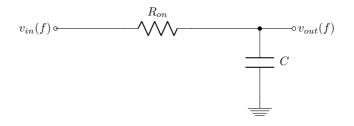

#### 2.6.3 Switch Distortion

The sampling switch in the SAR ADC is not ideal and it can be modelled as a resistor with resistance  $R_{on}$ . This resistance and the capacitance C from the CDAC forms a RC-filter as seen in Figure 2.11.

Figure 2.11: Sampling switch model with capacitive CDAC load.

If the switch is implemented by a MOSFET in the triode region, this resistance  $R_{on}$  can be approximated by

$$R_{on} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_t)}$$

(2.18)

Where  $\mu_n$  is the mobility of the transistor, W/L is the ratio between the gate width and gate length,  $V_{GS}$  is the potential difference between the gate and source terminal and  $V_t$  is the threshold voltage of the transistor. Eq. (2.18) shows that the switch resistance  $R_{on}$  is dependent on the input signal through  $V_{GS}^3$ , but also  $V_t$  through the body effect. The switch and the CDAC forms a RC-filter with transfer function

$$H(f) = \frac{v_{out}(f)}{v_{in}(f)} = \frac{1}{1 + \frac{j2\pi f}{2\pi R_{op}C}}$$

(2.19)

Where f is the input sinusoidal frequency to the switch and  $j = \sqrt{-1}$ . Since  $R_{on}$  now varies with the input signal, it is clear that the transfer function H(f) is also signal dependent which results in signal dependent attenuation and phase shift through the switch. It is this non-constant attenuation and phase shift that causes non-linearity and therefore loss of ENOB.

<sup>&</sup>lt;sup>3</sup>It doesn't matter where the source terminal is located, as both  $v_{in}(f)$  and  $v_{out}(f)$  will vary with the input signal  $v_{in}$ .

#### 2.6.4 CDAC Non-Linearity

The CDAC will also cause reduction of ENOB due to non-linearity in the capacitor array. These non-linearities can be divided into systematic mismatches and random mismatches in the capacitor array. The systematic mismatch of the capacitor array can be lowered by making the boundary conditions as uniform as possible and with careful routing. The random mismatch can only be reduced by making a larger unit capacitance.

#### 2.6.5 Gain Error

Gain errors in a SAR ADC causes saturation of the output decimal signal and leads to reduction of ENOB. Gain errors are caused by increased parasitic capacitance to ground at the CDAC top plate that accumulates extra charge during sampling. This extra capacitance leads slope change in the analog to digital transfer function of the ADC. Gain errors are easily alleviated, since the input signal to the ADC can have its amplitude lowered to avoid saturation, without loss of ENOB.

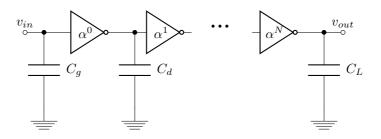

#### 2.7 Digital Buffers

When driving large capacitive loads with inverters and when switching speed is important, it's not true that a single inverter with high driver strength will minimize the switching speed. The switching time can be minimized by a chain of N inverters and where each inverter is scaled progressively by  $\alpha$ . Such a chain of inverters, or a buffer, is seen in Figure 2.12.

Figure 2.12: Chain of inverters to drive a large capacitive load.

If the first inverter has a input capacitance of  $C_g$  and an output capacitance of  $C_d$ , then the optimal scaling factor  $\alpha$  can be shown to follow [13]

$$\alpha(\ln \alpha - 1) = \frac{C_d}{C_g} \tag{2.20}$$

Eq. (2.20) has to be solved numerically for  $\alpha$ . If the inverter chain is terminated in a large load capacitance  $C_L$ , then the optimal number of stages N can be calculated as

$$N = \ln\left(\frac{C_L}{C_g}\right) / \ln \alpha - 1 \tag{2.21}$$

These formulas have been derived by minimizing the propagation delay through the chain of inverters.

## Chapter 3

## High Level Design

This chapter will present some high level design choices for the SAR ADC. The error budget for the SAR ADC will be presented and the devices used in this thesis will be justified from simulations results. Lastly, the switching scheme used in this thesis will be presented.

#### 3.1 Error Budget

An error budget was drafted at the start of this thesis to distribute the error over the different subcircuits, but also to obtain some specifications for each block. It is assumed that all the error sources are uncorrelated so that the sum of errors squared adds up to the total error squared. When dealing with uncorrelated errors like this, it is best to distribute the error as much as possible, since error sources that are large compared to other will be dominating and the total error will still be high even if the other error terms are small.

Since the budget will deal with some assumptions that can not be justified all that well, the budget will be overdesigned by a bit. For example, it is difficult to predict the systematic error caused by the CDAC and it is better to do conservative design. This might seem like a bad decision, but one still has the freedom of adjusting the supply voltage, switching algorithm and bulk biasing after the initial design is done to get to the wanted target ENOB.

In this thesis, the target ENOB is 10 bits and the ADC will therefore be designed to give out 11 bits. An ideal 11 bit ADC will give an output SINAD of 67.98 dB, as given by Eq. (2.5). In this thesis, the required ENOB is at least 10 bits, which corresponds to a SINAD > 61.96 dB. It was assumed initially that the supply voltage was set to 750 mV and the common-mode input voltage was set to half of this. An input sinusoid using the full dynamic range will then have a squared RMS amplitude value of 0.274 V<sup>2</sup>, or 0.53 V. With these assumptions and by using Eq. (2.6), one can find the required squared RMS error voltage to be 0.174  $\mu$ V<sup>2</sup>, or 417  $\mu$ V for 10 bits ENOB. This sets the upper bound

| Quantization Parameters |  |  |  |  |

|-------------------------|--|--|--|--|

| 11 bits                 |  |  |  |  |

| 67.98 dB                |  |  |  |  |

| 61.98 dB                |  |  |  |  |

| 750 mV                  |  |  |  |  |

| 750 mV                  |  |  |  |  |

| $366 \ \mu V$           |  |  |  |  |

| 0.53 V                  |  |  |  |  |

| 417 $\mu V$             |  |  |  |  |

|                         |  |  |  |  |

**Table 3.1:** Quantization parameters needed for error budgeting.

for the total error in the system. These values are summarized in Table 3.1 for convenience.

The error budget was drafted during initial circuit design of the comparator and design of the sampling switch. The initial plan was to design the comparator so that the input referred RMS noise would be close to  $V_{LSB}/2$ . Not only will the sampling switch distort the input signal, but some noise will couple to the input signal as well. This means that the sampling switch needs two error source contributions in the budget. The switch topology was also chosen early so that it would fit well in the wanted specifications and the initial goal was to try to keep the sum of squared error of the switch comparable to that of the comparator.

To make the error budget more or less complete, it was assumed that the unit capacitor  $C_{unit}$  of the CDAC had a value of 300 aF and that the systematic non-linearities in the CDAC gave a reduction of 1 dB SINAD. The systematic errors are difficult to predict for the CDAC and 1 dB has been chosen mainly because it is an easy number to work with and because it seems reasonable for an ADC that is thermally limited. The unit capacitance of the CDAC was chosen so that it corresponds reasonably well with state-of-the-art CDAC designs [14]. The reasoning for specifying the unit capacitance so early in the design is that allows one to calculate the kT/C noise and therefore complete the budget. The resulting error budget can be seen in Table 3.2. It is assumed that the temperature is  $27^{\circ}$ .

| Error Source        | Magnitude [ $\mu V^2$ ] | Magnitude [ $\mu$ V] | Relative Error [%] |

|---------------------|-------------------------|----------------------|--------------------|

| Comparator Noise    | 0.045                   | 212                  | 36                 |

| CDAC distortion     | 0.025                   | 158                  | 20                 |

| Switch Distortion   | 0.025                   | 158                  | 20                 |

| Switch Noise        | 0.018                   | 134                  | 14.4               |

| kT/C                | 0.012                   | 110                  | 9.6                |

| Sum                 | 0.125                   | -                    | 100                |

| $\sqrt{\text{Sum}}$ | -                       | 354                  | -                  |

**Table 3.2:** Initial error budget for the ADC.

The sum of errors squared in the budget equals 0.125  $\mu V^2$  and taking the square root of this result yields 354  $\mu V$ , which is less than the upper bound of 417  $\mu V$ . The error budget presented should give a theoretical SINAD of 63.33 dB. This corresponds to an ENOB of 10.23 bits.

# 3.2 Device Choice

The initial plan for this thesis was to design a compiled SAR ADC using ciccreator [15] developed by Carsten Wulff. Ciccreator compiles the layout of a Simulation Program for Integrated Circuits Emphasis (SPICE) netlist once a technology file<sup>1</sup> and a routing file has specified for the compiler. For a compiled design, it is a lot easier to work with standard transistor cells (unit transistors), than having devices with various  $\frac{W}{L}$  as the compiled layout needs some regularity to work well. Due to time constraints, the layout of the ADC was done manually, but unit transistors have still been utilized throughout the design.

In this thesis, an analog unit transistor and a digital unit transistor have been defined. The use of unit transistors might seems like a disadvantage when doing analog layout, as there is less freedom to dimensions transistors. This might be true in certain cases, but parallel and series connections can still be utilized for more flexibility.

Another advantage of using unit transistors is that it ensures more regularity when doing layout. For 22 nm FDSOI, the Design Rule Check (DRC) is very strict when it comes to polysilicon rules, especially for minimum gate length. The DRC needs to have 3 dummy polysilicon fingers on both sides of the gate finger for minimum gate length. However, if transistors are stacked, then 3 dummy polysilicon fingers only have to be put at the end of the transistor stack and each transistor only require 1 dummy polysilicon finger on each side of the gate. The 3 dummy polysilicon fingers are referred to as polysilicon termination and the DRC also requires that all polysilicon within a termination are of equal dimensions. This is only possible if all the transistors are identical within a termination. It is clear that the use of unit transistors allows for a huge reduction in dummy polysilicon, which results in reduced overall area.

It was theorized early in the design stage that low threshold devices would give the best Figure of Merit (FoM) due to the high speed requirement. This kit provides various low threshold devices, but only two low threshold devices have been tested for this thesis. These devices will in the following be referred to as Low Treshold Voltage 1 (LVT1) and Low Treshold Voltage 2 (LVT2), where the threshold voltage of LVT2 devices are lower than the threshold voltage of the LVT1 devices. These names are pseudonyms as to not reveal the process house. The following will present some simulation results of LVT1 and LVT2 devices and which devices that have been used for design. Test bench parameters will be given as  $V_{DS}$  and  $V_{GS}$  for nMOS devices and given as  $V_{SD}$  and  $V_{SG}$  for pMOS devices. All the devices in the following will have dimensions  $W = 1 \ \mu m$  and  $L = 20 \ nm$ .

<sup>&</sup>lt;sup>1</sup>The technology file very loosely said contains design rules and layer definitions.

#### 3.2.1 Noise

The noise in the devices was investigated by probing the drain current. Afterwards, this drain current was then referred to the gate as a voltage to obtain the input referred noise. All the simulations were done in a test bench with  $V_{DS} = V_{SD} = 750$  mV and  $V_{GS} = V_{SG} = 325$  mV. This is not the ideal setup, since the noise will depend on the biasing condition. This will make the test biased, since the devices have different threshold voltages and the overdrive for the devices will vary. However, the chosen values are early estimations of the final supply voltage and therefore common-mode voltage of the input signal. With this in mind, the results should give reasonable results so that a unit transistor can be picked. To make the results as easy as possible to visualize, only the flicker noise and the thermal noise have been simulated at the frequencies 1 MHz and 10 GHz and the power spectrum density magnitude has been extracted at these frequencies. The results from the noise simulations can be seen in Figure 3.1.

Figure 3.1: Noise performance of various low threshold voltage devices. The spectral density magnitude is extracted for 1 MHz and 10 GHz to study flicker noise and thermal noise separately.

The simulation results shows that the flicker noise for the LVT2 devices are bad compared to the LVT1 devices. This is most likely due to the doped channels of the LVT2 devices, while the LVT1 devices have undoped channels. Doping introduces impurities in the transistor channel and the increase in flicker noise is expected. It's also seen that the LVT1 nMOS devices have slightly worse flicker noise performance than LVT1 pMOS devices.

The LVT1 nMOS devices have about 15% percent higher flicker noise compared to LVT1 pMOS devices, so the difference is modest.

The simulations results also indicate that the nMOS devices have superior thermal noise performance compared to the pMOS devices. The pMOS devices have around 70% higher thermal noise compared to the nMOS devices, which is significant. The difference in thermal noise between the nMOS devices is also seen to be very small.

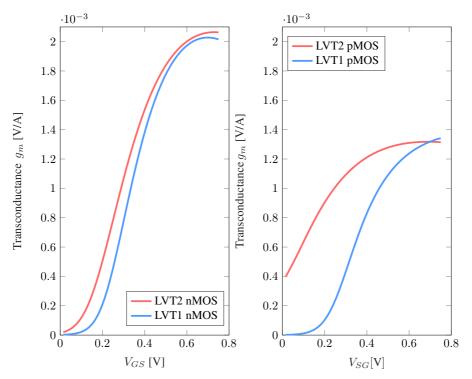

#### 3.2.2 Transconductance

The transconductance  $g_m$  for the simulated devices was obtained by using the definition  $g_m = \frac{\partial I_D}{\partial V_{GS}}$ . The simulations were performed with constant  $V_{DS} = V_{SD} = 750$  mV, while  $V_{SG}$  and  $V_{SG}$  were swept from 0V to  $V_{DD} = 750$  mV. The simulated results for  $g_m$  can be seen in Figure 3.2.

Figure 3.2: Transconductance  $g_m$  of the low threshold devices simulated.

It is seen that the nMOS transistors are "stronger" than the pMOS transistors due to the higher  $g_m$ , which is normal for MOSFET transistors. The higher  $g_m$  of the nMOS devices is beneficial, as the noisy drain current is moved to the gate as a voltage source by dividing by  $g_m^2$ . This is especially important when considering other noise sources in a circuit. Another interesting aspect is that LVT2 pMOS devices have high  $g_m$  for  $V_{SG} = 0$  V. This might suggest that the leakage current for LVT2 pMOS devices is abnormally high.

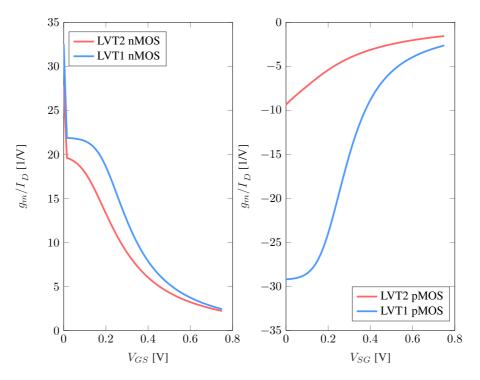

#### 3.2.3 Transistor Speed and Efficiency

The transistor efficiencies  $g_m/I_D$  for the simulated devices can be seen in Figure 3.3. The simulations were performed in parallel with the transconductance simulations, so the test benches are identical. Figure 3.3 reveals that the  $|g_m/I_D|$  for the LVT2 devices is smaller than the  $|g_m/I_D|$  of the LVT1 devices. This is to be expected, since the lower threshold voltage of LVT2 devices makes these devices faster and therefore more inefficient. The difference in  $|g_m/I_D|$  between the nMOS devices is seen to be very modest. An irregularity is seen for the LVT2 pMOS devices, where the  $|g_m/I_D|$  is relatively small even for small values of  $V_{SG}$ . The difference in  $|g_m/I_D|$  between the pMOS devices is also very large.

Figure 3.3: Transistor efficiency  $g_m/I_D$  of the low threshold devices simulated.

#### 3.2.4 Analog Unit Transistor

Due to the accuracy requirement of ENOB larger than 10 bits and the speed requirement of 100 MS/s, it is probably wise to pick an analog unit transistor that has good noise performance to achieve the target ENOB, but it is also important to consider the  $|g_m/I_D|$  due to the speed requirement. It is also probably a good choice to pick a transistor with good thermal noise properties, as flicker noise can be reduced by using a dynamic comparator. This is because a dynamic comparator has a reset phase and a comparison phase. The comparator will act like a highpass-filter<sup>2</sup> due to the reset phase and the effect of low frequency flicker noise will be reduced.

The thermal noise properties of LVT1 nMOS and LVT2 nMOS both stands out when compared to the pMOS transistors, but the LVT1 nMOS has much better flicker noise properties than the LVT2 counterpart. The LVT2 pMOS stands out as the worst noise performer and this transistor will not be used due to this. Comparing the transconductance  $g_m$  and transistor efficiency  $g_m/I_D$  between the nMOS transistors, it is seen that the difference is modest, so the LVT1 nMOS will be used as the n-channel device due to the superior flicker noise performance. Since the LVT2 pMOS transistor already has been excluded, the choice for p-channel device is the LVT1 pMOS. Another good reason to use the LVT1 devices is the undoped channel. Since the channel is undoped, one should expect a decrease in mismatch because the doping variability is removed.

The dimensions for the analog unit transistor were determined by using an ideal behaviour model of the ADC and a comparator transistor circuit. The dimensions of the input pair of the comparator were increased until a reasonable noise performance was achieved (the value in the budget). The input pair was simulated with a multiplier larger than unity due to matching considerations. The preliminary simulations showed that  $W = 1 \ \mu m$  and  $L = 20 \ nm$  would be fitting as an analog unit transistor. The nMOS and pMOS were dimensioned identically and a single finger device was used. The choice of these dimensions is also motivated by layout considerations to avoid abnormally large multipliers that makes layout work tedious.

#### 3.2.5 Digital Unit Transistor

When defining a digital unit transistor there are several aspects that should be considered. Speed is of course important, since the specification of 100 MS/s is so high. Leakage is also important, but speed and leakage tends to be correlated, so a compromise needs to be made. One should also make an effort to balance nMOS and pMOS as much as possible to avoid skewing. It is probably beneficial to either use LVT2 devices or LVT1 devices, i.e, do not mix devices. The LVT2 devices have lower  $g_m/I_D$  and the speed is therefore faster. However, the abnormally large leakage current of LVT2 pMOS makes using the LVT2 device little attractive. It is for these reasons that the LVT1 devices will be used in the digital circuitry.

The digital unit transistor has dimensions W = 350 nm and L = 20 nm. This applies for the both the nMOS and the pMOS transistor. The sizing was determined by post-layout simulations on the entire ADC where the netlist was edited until a reasonable performance was achieved.

$<sup>^{2}</sup>$ The overall response will be bandpass since the comparator has poles at high frequencies that will limit the bandwidth.

# 3.3 CDAC Switching

The decision of the switching scheme of the CDAC was based on simulations with a comparator and the sampling switch as a transistor circuits, while the remaining blocks were ideal. This ideal SAR ADC model was composed of ideal components and VerilogA code. This thesis will only model split-monotonic switching and monotonic switching due the simplicity and the good energy efficiency of these algorithms.

A pure monotonic switching scheme where the common-mode voltage was switched up and down was tested, as well as a combination of split-monotonic and monotonic switching was tested. The latter simulations was with 3, 4 and 6 MSBs switched with splitmonotonic switching and monotonic switching was performed for the remaining LSBs. The monotonic switching was performed by changing common-mode voltage up and down in this case as well.